# (19)대한민국특허청(KR) (12) 등록특허공보(B1)

(51) 。Int. Cl. H01L 29/786 (2006.01) (45) 공고일자 2006년12월01일 (11) 등록번호 10-0652817

2006년11월24일 (24) 등록일자

(21) 출원번호 (22) 출원일자 10-2000-0002554

(65) 공개번호

10-2000-0057776

심사청구일자

2000년01월20일

(43) 공개일자

2000년09월25일

2005년01월18일

(30) 우선권주장 11-013275 1999년01월21일 일본(JP)

(73) 특허권자

가부시키가이샤 한도오따이 에네루기 켄큐쇼 일본국 가나가와켄 아쓰기시 하세 398

(72) 발명자

야마자키순페이

일본국가나가와켄아쓰기시하세398반치가부시키가이샤한도오따이에네

루기켄큐쇼내

고야마준

일본국가나가와켄아쓰기시하세398반치가부시키가이샤한도오따이에네

루기켄큐쇼내

시바타히로시

일본국가나가와켄아쓰기시하세398반치가부시키가이샤한도오따이에네

루기켄큐쇼내

후쿠나가다케시

일본국가나가와켄아쓰기시하세398반치가부시키가이샤한도오따이에네

루기켄큐쇼내

(74) 대리인

황의만

(56) 선행기술조사문헌

ep0862077 ip10-274789 ip10-031235 us5966193

\* 심사관에 의하여 인용된 문헌

심사관: 최광섭

전체 청구항 수 : 총 8 항

## (54) 반도체장치

(57) 요약

요구되는 회로 기능에 따라 배열된 적절한 구조의 TFT를 갖는 높은 신뢰성의 반도체장치가 개시되어 있다. 이 반도체장치는 동일 기판상에 구동회로와 화소부를 갖는다. 본 발명은 차광막과 동일 층상에 형성된 제1 전극과 드레인 영역과 동일한 조성물의 반도체막으로 형성된 제2 전극 사이에 보유용량이 형성되고, 보유용량의 부분에서 제1 하지 절연막이 제거되어 제2 하지 절연막이 보유용량의 유전체로 사용되는 것을 특징으로 한다. 이러한 구조는 작은 면적에서 큰 보유용량을 제공한다.

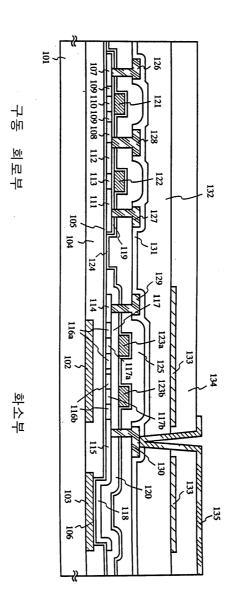

#### 대표도

도 1

## 특허청구의 범위

## 청구항 1.

각 화소에 화소 TFT와 보유용량을 가지는 화소부를 포함하는 반도체장치로서,

상기 화소 TFT는

차광막,

적어도 제1 절연층과 제2 절연층을 포함하는 절연막, 및

상기 절연막을 사이에 두고 상기 차광막 위에 형성된 활성막을 포함하고;

상기 보유용량은

상기 차광막과 동일한 층에 형성된 전극,

유전체 재료, 및

상기 화소 TFT의 드레인 영역과 동일한 재료로 된 반도체막을 포함하며;

상기 유전체 재료가 상기 절연막의 일부로 형성되어 있는 것을 특징으로 하는 반도체장치.

## 청구항 2.

각 화소에 화소 TFT와 보유용량을 가지는 화소부를 포함하는 반도체장치로서,

상기 화소 TFT는

차광막,

적어도 제1 절연층과 제2 절연층을 포함하는 절연막, 및

상기 절연막을 사이에 두고 상기 차광막 위에 형성된 활성막을 포함하고;

상기 보유용량은

상기 차광막과 동일한 층에 형성된 전극,

유전체 재료, 및

상기 화소 TFT의 드레인 영역과 동일한 재료로 된 반도체막을 포함하며;

상기 유전체 재료가 상기 절연막의 일부로 형성되고, 상기 절연막의 다른 부분은 제거되어 있는 것을 특징으로 하는 반도 체장치.

## 청구항 3.

각 화소에 화소 TFT와 보유용량을 가지는 화소부를 포함하는 반도체장치로서,

상기 화소 TFT는

차광막,

상기 차광막과 접촉하는 제1 절연막,

제2 절연막, 및

상기 제2 절연막을 사이에 두고 상기 차광막 위에 형성된 활성막을 포함하고;

상기 보유용량은

상기 차광막과 동일한 층에 형성된 전극,

상기 제2 절연막, 및

상기 화소 TFT의 드레인 영역과 동일한 재료로 된 반도체막을 포함하며;

상기 제2 절연막이 상기 활성막과 접촉하여 있는 것을 특징으로 하는 반도체장치..

## 청구항 4.

제 3 항에 있어서, 상기 제2 절연막이 상기 제1 절연막과 상기 제2 절연막의 전체 두께의 1/5 이하의 두께를 가지는 것을 특징으로 하는 반도체장치.

## 청구항 5.

제 1 항 내지 제 3 항 중 어느 한 항에 있어서, 상기 반도체장치가 상기 화소부와 동일 기판 위에 형성된 구동회로부를 포함 하고,

상기 구동회로부는 구동 TFT를 포함하고,

상기 구동 TFT의 게이트 절연막이 상기 화소 TFT의 게이트 절연막보다 얇은 것을 특징으로 하는 반도체장치.

## 청구항 6.

제 1 항 내지 제 3 항 중 어느 한 항에 있어서, 상기 반도체장치가 상기 화소부와 동일 기판 위에 형성된 구동회로부를 포함 하고,

상기 구동회로부는 구동 TFT를 포함하고,

상기 화소 TFT의 게이트 절연막이  $50\sim200$  nm 범위의 두께를 가지고, 상기 구동 TFT의 게이트 절연막이  $5\sim50$  nm 범위의 두께를 가지는 것을 특징으로 하는 반도체장치.

## 청구항 7.

제 1 항 내지 제 3 항 중 어느 한 항에 있어서, 상기 반도체장치가 EL(전계발광) 표시장치이고, EL 소자가 상기 화소 TFT에 전기적으로 접속되어 있는 것을 특징으로 하는 반도체장치.

## 청구항 8.

제 1 항 내지 제 3 항 중 어느 한 항에 있어서, 상기 반도체장치가, 비디오 카메라, 디지털 카메라, 프로젝터, 프로젝션 TV, 고글형 표시장치(헤드 장착형 표시장치), 내비게이션 시스템, 음향 재생 장치, 노트북형 퍼스널 컴퓨터, 게임기, 휴대형 정보 단말기(모바일 컴퓨터, 휴대 전화기, 휴대형 게임기, 및 전자 서적), 기록 매체를 가진 영상 재생 장치로 이루어진 군에서 선택되는 전자 기기인 것을 특징으로 하는 반도체장치.

## 청구항 9.

삭제

청구항 10.

삭제

청구항 11.

삭제

청구항 12.

삭제

청구항 13.

삭제

청구항 14.

삭제

청구항 15.

삭제

청구항 16.

삭제

청구항 17.

삭제

청구항 18.

삭제

청구항 19.

삭제

청구항 20.

삭제

청구항 21.

삭제

청구항 22.

삭제

청구항 23.

삭제

명세서

## 발명의 상세한 설명

### 발명의 목적

## 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 박막트랜지스터(이하, TFT라 칭함)로 구성된 회로를 가진 반도체장치에 관한 것이다. 보다 상세하게는, 본 발명은 액정 표시장치 및 EL(전계발광) 표시장치로 대표되는 전기광학장치, 및 반도체 회로에 관한 것이다. 또한, 본 발명은 본 발명에 따른 전기광학장치 또는 반도체 회로를 가진 전자 기기에 관한 것이다.

본 명세서에서 사용되는 용어 "반도체장치"는 반도체의 특성을 이용하여 기능하는 모든 장치를 가리키고, 전기광학장치, 반도체 회로, 전자 기기를 포함한다.

박막트랜지스터(이하, TFT라 칭함)는 투명 기판상에 형성될 수 있기 때문에, 액티브 매트릭스형 액정 표시장치(이하, AM-LCD라 칭함)에의 응용 개발이 활발하게 이루어지고 있다. 결정성 반도체막(대표적으로는 폴리실리콘막)을 이용한 TFT는 높은 이동도가 얻어지기 때문에, 동일 기판상에 기능 회로가 집적된 경우 미세한 화상 표시를 실현하는 것이 가능하게 되어 있다.

AM-LCD는 기본적으로, 화상을 표시하는 화소부(또는 화소 매트릭스 회로)와, 화소부에 배열된 각 화소의 TFT를 구동하는 게이트 구동회로(또는 게이트 드라이버 회로)와, 각 화소의 TFT에 화상 신호를 보내는 소스 구동회로(또는 소스 드라이버 회로), 및 데이터 구동회로(또는 데이터 드라이버 회로)로 구성되고, 이들 회로 모두는 동일 기판상에 형성된다. 한편, 게이트 구동회로 및 소스 구동회로가 형성되는 영역을 구동회로부라 칭한다.

최근에, 화소부 및 구동회로부에 추가하여, 신호 분할회로 및 y보정회로와 같은 신호 처리 회로도 동일 기판상에 형성된 시스템-온-패널(system-on-panel)이 제안되어 있다.

그러나, 화소부와 구동회로부는 회로가 요구하는 성능이 서로 다르기 때문에 동일 구조의 TFT로 모든 회로 요건을 만족시키는 것이 어렵다. 즉, 시프트 레지스터 회로를 포함하는 구동회로부는 고속 동작을 중시하고, 화소부를 구성하는 TFT(이하, 화소 TFT라 칭함)는 높은 내전압 특성을 중시한다. 지금까지는, 이들 모두를 만족시키는 TFT 구조가 확립되어 있지않다.

본 출원인은 구동회로부를 구성하는 TFT(이하, 구동 TFT라 칭함)와 화소 TFT에서 게이트 절연막 두께를 서로 다르게 한 것을 특징으로 하는 구성에 대한 특허출원을 하였다(일본 공개특허공고 평10-056184호 및 대응하는 미국 특허출원 08/862,895호). 구체적으로는, 구동 TFT의 게이트 절연막을 화소 TFT의 게이트 절연막보다 얇게 하는 것이다.

#### 발명이 이루고자 하는 기술적 과제

본 발명은 상기 선행출원의 공보에 개시된 구성을 기본으로 하여 화소부를 개선하는 것이다. 구체적으로는, 본 발명의 목적은 작은 면적에서 큰 커패시턴스를 확보하는 보유용량을 형성하기 위한 구조를 제공하는데 있다.

본 발명의 다른 목적은, 각 회로의 기능에 따라 적절한 구조의 TFT로 구성된 신뢰성이 높은 전기광학장치(AM-LCD로 대표되는)를 제공하는데 있다. 본 발명의 또 다른 목적은 표시부로서 전기광학장치를 가지는 신뢰성이 높은 반도체장치(전자기기)를 제공하는데 있다.

본 발명의 제1 양태에 따르면, 화소부가 각 화소마다 화소 TFT와 보유용량을 가지는 유형의 반도체장치에 있어서, 상기화소 TFT는 2 이상의 적층으로 된 절연막을 사이에 두고 차광막 위에 형성된 활성층을 가지고, 상기 보유용량은 상기 차광막과 동일한 층에 형성된 전극과, 유전체 재료, 및 상기 화소 TFT의 드레인 영역과 동일한 조성으로 된 반도체막으로 구성되며, 상기 유전체 재료는 2 이상의 적층으로 된 상기 절연막의 일부 층인 것을 특징으로 하는 반도체장치가 제공된다.

본 발명의 제2 양태에 따르면, 화소부가 각 화소마다 화소 TFT와 보유용량을 가지는 유형의 반도체장치에 있어서, 상기화소 TFT는 2 이상의 적층으로 된 절연막을 사이에 두고 차광막 위에 형성된 활성층을 가지고, 상기 보유용량은 상기 차광막과 동일한 층에 형성된 전극과, 유전체 재료, 및 상기 화소 TFT의 드레인 영역과 동일한 조성으로 된 반도체막으로 구성되며, 상기 유전체 재료는 2 이상의 적층으로 된 상기 절연막의 일부의 제거 후에 남는 절연막인 것을 특징으로 하는 반도체장치가 제공된다.

본 발명의 제3 양태에 따르면, 화소부가 각 화소마다 화소 TFT와 보유용량을 가지는 유형의 반도체장치에 있어서, 상기화소 TFT는 차광막과 접촉하는 제1 절연막과 활성층과 접촉하는 제2 절연막을 사이에 두고 차광막 위에 형성된 활성층을 가지고, 상기 보유용량은 상기 차광막과 동일한 층에 형성된 전극과, 상기 제2 절연막, 및 상기 화소 TFT의 드레인 영역과 동일한 조성으로 된 반도체막으로 구성되는 것을 특징으로 하는 반도체장치가 제공된다.

또한, 제3 양태의 반도체장치는, 상기 제2 절연막이 상기 제1 절연막과 제2 절연막으로 이루어진 적충막의 두께의 1/5 이하(바람직하게는 1/100 내지 1/10)의 두께를 가지는 것을 특징으로 한다.

본 발명의 제4 양태에 따르면, 화소부가 각 화소마다 화소 TFT와 보유용량을 가지는 반도체장치를 제작하는 방법으로서, 기판상에 차광막 및 그 차광막과 동일한 재료의 전극을 형성하는 공정, 상기 차광막 및 상기 전극을 덮는 제1 절연막을 형성하는 공정, 상기 제1 절연막을 에칭하여 상기 전극에 개구부를 형성하는 공정, 상기 제1 절연막과 상기 개구부를 덮는 제2 절연막을 형성하는 공정, 및 상기 제2 절연막상에 반도체막을 형성하는 공정을 포함하는 것을 특징으로 하는 반도체장치 제작방법이 제공된다.

본 발명의 제5 양태에 따르면, 구동회로부와, 각 화소마다 화소 TFT와 보유용량을 가지는 화소부를 가지는 반도체장치를 제작하는 방법으로서, 기판상에 차광막 및 그 차광막과 동일한 재료의 전극을 형성하는 공정, 상기 차광막 및 상기 전극을 덮는 제1 절연막을 형성하는 공정, 상기 제1 절연막을 에칭하여 상기 전극에 개구부를 형성하는 공정, 상기 제1 절연막과 상기 개구부를 덮는 제2 절연막을 형성하는 공정, 상기 제2 절연막상에 반도체막을 형성하는 공정, 상기 반도체막을 덮는 게이트 절연막을 형성하는 공정, 상기 게이트 절연막의 일부를 에칭하여 상기 구동회로부의 반도체막과 상기 화소부의 반도체막의 일부를 노출시키는 공정, 및 열산화를 행하여, 상기 게이트 절연막의 에칭에 의해 노출된 반도체막의 표면상에 열산화막을 형성하는 공정을 포함하는 것을 특징으로 하는 반도체장치 제작방법이 제공된다.

본 발명의 제6 양태에 따르면, 구동회로부와, 각 화소마다 화소 TFT와 보유용량을 가지는 화소부를 가지는 반도체장치를 제작하는 방법으로서, 기판상에 차광막 및 그 차광막과 동일한 재료의 전극을 형성하는 공정, 상기 차광막 및 상기 전극을 덮는 제1 절연막을 형성하는 공정, 상기 제1 절연막을 에칭하여 상기 전극에 개구부를 형성하는 공정, 상기 제1 절연막과 상기 개구부를 덮는 제2 절연막을 형성하는 공정, 상기 제2 절연막상에 반도체막을 형성하는 공정, 상기 반도체막을 덮는 게이트 절연막을 형성하는 공정, 상기 게이트 절연막의 일부를 에칭하여 상기 구동회로부의 반도체막과 상기 화소부의 반도체막의 일부를 노출시키는 공정, 열산화를 행하여, 상기 게이트 절연막의 에칭에 의해 노출된 반도체막의 표면상에 열산화막을 형성하는 공정, 및 상기 구동회로부의 LDD 영역과 상기 화소부의 LDD 영역의 길이가 서로 다르도록 상기 구동회로부의 반도체막과 상기 화소부의 반도체막과 상기 화소부의 반도체막에 LDD 영역을 형성하는 공정을 포함하는 것을 특징으로 하는 반도체장치 제작방법이 제공된다.

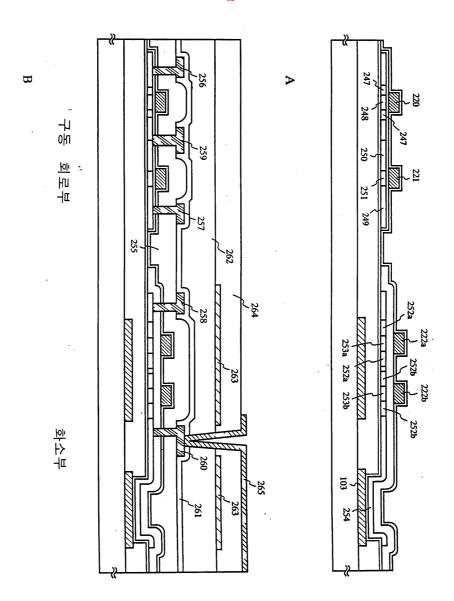

#### 발명의 구성

동일 기판상에 구동회로부와 화소부가 일체로 형성된 AM-LCD의 단면도를 나타내는 도 1을 참조하여 본 발명의 일 실시 형태를 설명한다. 본 실시형태에서, 구동회로를 구성하는 기본 회로는 CMOS 회로이고, 화소 TFT는 이중 게이트 구조의 TFT이다. 이 TFT는 단일 게이트 구조이거나 또는 삼중 게이트 구조와 같은 멀티게이트 구조일 수도 있다. 도 1에는, 내열성 기판(101)이 도시되어 있고, 이 기판은 석영 기판, 규소 기판, 세라믹 기판, 또는 금속 기판(대표적으로는 스테인리스 강 기판)일 수 있다. 어떤 기판이든, 기판은 필요에 따라 하지막(바람직하게는 규소를 주성분으로 하는 절연막)을 가질 수 있다.

동일 층에 동일 재료로 형성된 차광막(102)과 보유용량의 하부 전극(103)이 도시되어 있다. 차광막(102)과 하부 전극(103)은 800~1150℃(바람직하게는 900~1100℃)의 온도에 견디는 내열성의 전기 전도성 막이다.

그러한 막은 대표적으로는, 전도성의 규소막(예를 들어, 인이 첨가된 규소막 및 붕소가 첨가된 규소막), 금속막(예를 들어, 텅스텐막, 탄탈막, 몰리브덴막, 티탄막), 및 상기 금속막의 성분으로 구성된 합금막을 포함한다. 그 막은 규화물막 또는 질화막(예를 들어, 질화 탄탈막, 질화 텅스텐막, 및 질화 티탄막)의 형태일 수도 있다. 이들은 적층을 형성하도록 조합하여 사용될 수도 있다.

상기 금속막은 금속막의 산화를 방지하기 위해 규소막과의 적층 형태로 사용되는 것이 바람직하다. 또한, 산화를 효과적으로 방지하기 위해 그 금속막은 규소를 주성분으로 하는 절연막으로 덮일 수도 있다. 한편, 본 명세서에서 사용되는 용어 "규소를 주성분으로 하는 절연막"은 산화규소막, 질화규소막, 또는 소정의 비율로 규소, 산소, 및 질소를 함유하는 절연막을 가리킨다.

또한, 두께  $0.3\sim1$   $\mu$ m, 바람직하게는  $0.6\sim0.8$   $\mu$ m의 하지막(104)도 도시되어 있다. 이 하지막을 이후 제1 절연막이라 칭한다. 이 막은 규소를 주성분으로 하는 절연막이다. 이 제1 절연막(104)상에, 나중에 보유용량이 되는 개구부가 형성된다. 그리고, 그 위에, 규소를 주성분으로 하는 절연막(105)이 다시 형성된다. 이 절연막을 이후 제2 절연막이라 칭한다.

여기에는, 하나의 층이 차광막과 접촉하는 제1 절연막(104)이고, 다른 층은 화소 TFT의 활성층과 접촉하는 제2 절연막 (105)인 2층 구조의 것으로 도시되어 있다. 또한, 다층 구조일 수도 있다. 따라서, 최종적인 구조는, 화소 TFT의 활성층이 절연막(적어도 2개의 층을 가지는 적층의 형태임)을 사이에 두고 차광막(102) 위에 형성되는 구조로 된다. 그 적층된 절연막의 일부 층(1층 이상)이 보유용량의 유전체를 구성한다. 즉, 적층된 절연막에서 일부 층이 제거된 후 남는 층들이 보유용량의 유전체가 된다.

#### 삭제

본 실시형태에서, 제2 절연막(105)은 보유용량의 유전체(106)로서 기능한다. 제2 절연막(105)(또는 보유용량의 유전체 (106))은 두께가  $5\sim75$  nm, 바람직하게는  $20\sim50$  nm이다. 제2 절연막이 얇을수록, 보유용량의 커페시턴스가 커진다. 그러나, 내전압은 누설 전류 방지를 고려해야 한다. 내전압을 증가시키는 효과적인 방법은 그 막을 2층의 적층으로 형성하는 것이다.

제1 절연막(104)은 차광막(102)이 위의 TFT와 함께 기생용량을 형성하지 않도록 충분히 두꺼운 막 두께를 가져야 한다. 보유용량의 부분에 개구부를 형성함으로써, 보유용량의 유전체를 얇게 할 수 있다. 따라서, 용량이 형성되는 면적을 증가시키기 않고 커페시티(capacity)를 얻는 것이 가능하다. 보유용량의 이러한 구성은 상기한 일본 공개특허공고 평10-56184호 공보에는 개시되어 있지 않다.

또한, 도 1에 도시된 구조에서 특징적인 것은, 화소 TFT의 활성층과 차광막(102) 사이에 형성된 절연막(또는 제1 절연막(104)과 제2 절연막(105)으로 이루어진 적층 막)의 막 두께와, 보유용량의 상부 전극(118)(반도체막으로 되어 있음)과 보유용량의 하부 전극(103) 사이에 형성된 제2 절연막(105)(보유용량의 유전체(106))의 막 두께가 다르다는 점이다. 구체적으로는, 후자의 두께가 전자의 두께의 1/5 이하(바람직하게는  $1/100 \sim 1/10$ )이다.

이렇게 하여, 화소 TFT와 차광막(102) 사이에 기생용량이 형성되게 함이 없이 큰 커패시턴스의 보유용량을 형성하는 것이 가능하다.

또한, 화소 TFT 아래에 형성된 차광막(102)은 부유 상태로 남아 있을 수 있고 또는 고정 전위로 유지될 수 있다. 고정 전위는 비디오 신호의 최저 전위보다 낮아야 하며, 바람직하게는 기판상에 형성된 전체 회로의 최저 전원 전위와 같거나 그보다 낮아야 한다.

예를 들어, AM-LCD의 경우, 구동회로부, 다른 신호 처리 회로, 및 화소부에 다양한 전원 공급선이 형성되고, 각각에 소정의 전위가 제공된다. 즉, 어떤 기준이 되는 최저 전위가 있고, 그것을 기준으로 하여 다양한 전압이 형성된다. 최저 전원 전위란, 모든 회로에서 기준이 되는 최저 전위를 가리킨다.

차광막(102)을 부유 상태로 하거나 고정 전위로 함으로써, TFT 동작에 영향을 미치지 않는(또는 기생용량을 형성하지 않는) 차광부를 형성하는 것이 가능하다.

상기한 바와 같이 화소 TFT 아래에 형성된 차광막은 기판측으로부터의 미광(迷光)(stray light)으로 인한 광 누설 전류의 발생을 방지한다. 광에 노출되지 않는 구동회로측에 차광막을 형성하는 것은 필요하지 않다. 이것은 기생용량을 가능한 한 작게 한다는 관점에서 바람직하다.

제1 절연막(104)과 제2 절연막(105)상에는, 구동 TFT의 활성층, 화소 TFT의 활성층, 및 보유용량의 상부 전극이 되는 반도체막이 형성된다. 한편, 본 명세서에서 사용되는 용어 "전극"은 "배선"의 일부로서, 다른 배선과의 전기 접속을 위한 부분 또는 반도체막과 교차하는 부분을 가리킨다. 따라서, "배선"은 항상 "전극"을 포함하지만, 설명의 편의상 이들이 별개로 사용한다.

도 1에서, 구동 TFT의 활성층은 N채널형 TFT(이하, NTFT라 함)의 소스 영역(107), 드레인 영역(108), LDD(저농도 도 핑 드레인) 영역(109), 및 채널 형성 영역(110)과, P채널형 TFT(이하, PTFT라 함)의 소스 영역(111), 드레인 영역(112), 및 채널 형성 영역(113)으로 구성된다.

화소 TFT(본 설명에서는 NTFT)의 활성층은 소스 영역(114), 드레인 영역(115), LDD 영역(116a, 116b), 및 채널 형성 영역(117a, 117b)으로 형성된다. 또한, 드레인 영역(115)으로부터 연장하는 반도체막이 보유용량의 상부 전극(118)으로 사용된다. 즉, 보유용량의 상부 전극(118)은 드레인 영역(115)과 동일한 조성의 반도체막으로 구성된다.

#### 삭제

상기한 바와 같이, 본 발명에 따르면, 보유용량은 차광막(102)과 동일한 층에 형성된 전극(또는 보유용량의 하부 전극 (103)), 유전체(또는 제2 절연막(105)), 및 화소 TFT의 드레인 영역과 동일한 조성의 반도체막(또는 화소 TFT의 드레인 영역(115))으로 형성된다.

그러나, 드레인 영역이 보유용량의 상부 전극에 직접 접속되는 것이 항상 필요한 것은 아니고, 이들은 다른 배선을 통해 서로 전기적으로 접속될 수도 있다. 또한, 항상 이들이 동일한 조성으로 될 필요는 없고, 다른 도전형의 반도체막 또는 드레인 영역과 동일한 불순물을 다른 농도로 함유하는 반도체막일 수도 있다.

도 1의 경우, 구동 TFT와 화소 TFT에서 LDD 영역의 폭(또는 길이)이 다르다. 동작 속도가 중시되는 구동 TFT는 저항을 최소화 하기 위해 얇아야 하고, 낮은 오프 전류(또는 TFT가 오프 상태일 때 흐르는 전류)가 중시되는 화소 TFT는 어느 정도 긴 LDD 영역이 요구된다. 따라서, 구동 TFT의 LDD 영역은 화소 TFT의 LDD 영역과 폭이 같거나 그보다 좁은 것이 바람직하다.

다음에, 활성층과 보유용량의 상부 전극을 덮도록 게이트 절연막이 형성된다. 본 발명에 따르면, 구동 TFT의 게이트 절연막(119)의 두께가 화소 TFT의 게이트 절연막(120)의 두께보다 얇게 형성된다. 대표적으로는, 게이트 절연막(120)의 두께는  $50\sim200~\text{nm}$ (바람직하게는  $100\sim150~\text{nm}$ )이고, 게이트 절연막(119)의 두께는  $5\sim50~\text{nm}$ (바람직하게는  $10\sim30~\text{nm}$ )이다.

또한, 구동 TFT의 게이트 절연막은 일 종류의 두께일 필요는 없다. 즉, 구동 TFT는 구동회로부 내에 다른 두께의 절연막을 가질 수 있다. 그러한 경우, 동일 기판상에 두께가 상이한 게이트 절연막을 갖는 3종류 이상의 TFT가 존재하게 된다. 즉, 구동회로부에 포함된 구동 TFT의 적어도 일부의 절연막은 화소 TFT의 게이트 절연막보다 얇다고 말할 수 있다.

다음에, 게이트 절연막(119, 120)상에, 구동 TFT의 게이트 배선(121, 122)과 화소 TFT의 게이트 배선(123a, 123b)이 형성된다. 이들 게이트 배선(121, 122, 123a, 123b)은 800~1500℃(바람직하게는 900~1100℃)의 온도에 견디는 내열성의 전기 전도성 막으로 형성된다. 구체적으로는, 재료는 상기한 차광막(102) 또는 보유용량의 하부 전극(103)과 동일한 것 중에서 선택된다.

즉, 그 재료는 전도성 규소막(예를 들어, 인 첨가 규소막 및 붕소 첨가 규소막), 금속막(예를 들어, 텅스텐막, 탄탈막, 몰리 브덴막, 및 티탄막), 및 상기 금속막의 성분으로 이루어진 합금막을 포함한다. 이들은 규화물막 또는 질화막(질화 탄탈막, 질화 텅스텐막, 및 질화 티탄막)의 형태일 수도 있고, 적층을 형성하도록 조합되어 사용될 수도 있다.

또한, 상기 금속막은 그 금속막의 산화를 방지하기 위해 규소막과의 적층 형태로 사용되는 것이 바람직하다. 또한, 그 금속 막은 그의 산화를 효과적으로 방지하기 위해 규소를 주성분으로 하는 절연막으로 덮일 수 있다. 도 1에서는, 게이트 배선의 산화를 방지하기 위해 보호막(124)이 형성되어 있다.

다음에, 제1 층간절연막(125)이 형성된다. 이는 규소를 주성분으로 하는 절연막(단층 또는 적층)이다. 규소를 주성분으로 하는 절연막은 산화규소막, 질화규소막, 산화질화규소막(산소보다 질소의 함유량이 많음), 또는 질화산화규소막(질소보다 산소의 함유량이 많음)일 수 있다.

다음에, 제1 층간절연막(125)에 콘택트 홀이 형성되고, 구동 TFT의 소스 배선(126, 127) 및 드레인 배선(128)과 화소 TFT의 소스 배선(129)과 드레인 배선(130)이 형성된다. 그 위에 패시베이션막(131)과 제2 층간절연막(132)이 형성되고, 또 그 위에 차광막(블랙 마스크)(133)이 형성된다. 그리고, 차광막(133)상에 제3 층간절연막(134)이 형성된 다음, 콘택트 홀이 형성되고, 화소 전극(135)이 형성된다.

제2 충간절연막(132)과 제3 충간절연막(134)은 비유전율이 작은 수지막인 것이 바람직하다. 수지막의 예로서는, 폴리이미드막, 아크릴막, 폴리아미드막, 및 BCB(benzocyclobutene)막을 들 수 있다.

그리고, 화소 전극(135)은 투과형 AM-LCD를 제작하는 경우에는 ITO 막으로 대표되는 투명 도전막일 수 있고, 반사형 AM-LCD를 제작하는 경우에는 알루미늄막으로 대표되는 반사율이 높은 금속막일 수 있다.

한편, 도 1에서는, 화소 전극(135)이 드레인 전극(130)을 통해 화소 TFT의 드레인 영역(115)에 전기적으로 접속되어 있으나, 화소 전극(135)이 드레인 영역(115)에 직접 접속될 수도 있다.

상기한 바와 같이 구성된 AM-LCD는, 구동 TFT의 게이트 절연막이 화소 TFT의 게이트 절연막보다 얇고, 제1 절연막이 보유용량의 일부에서 선택적으로 제거되고, 얇은 제2 절연막이 보유용량의 유전체로서 기능하는 것을 특징으로 한다. 이경우, 화소 TFT 아래에 형성된 차광막(102)과 활성층 사이에 충분히 두꺼운 제1 절연막이 존재한다. 따라서, 기생용량의 문제가 없다.

이렇게 하여, 회로의 성능에 가장 적합한 TFT를 배치하는 것이 가능하고, 동시에 적은 면적에서 큰 커패시티를 확보하는 보유용량을 실현하는 것이 가능하다.

이하, 상기한 바와 같이 구성된 본 발명을 실시예에 의거하여 더 상세히 설명한다.

#### <u>실시예 1</u>

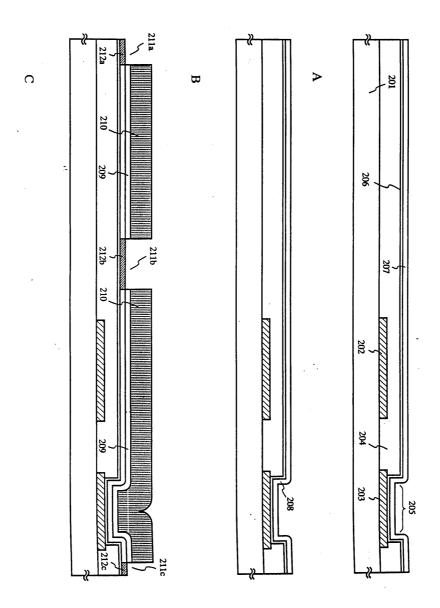

본 실시예에서는, 앞의 실시형태에서 설명한 도 1의 구조를 실현하기 위한 제작공정에 대하여 도  $2\sim$ 도 5를 참조하여 설명한다.

먼저, 기판으로서 석영 기판(201)을 준비한다. 이 기판상에 차광막(202)과 보유용량의 하부 전극(203)을 형성한다. 차광막(202)과 보유용량의 하부 전극(203) 각각은 하층으로부터 규소막, 질화 텅스텐막, 텅스텐막이 배열된 적층, 또는 하층으로부터 규소막, 규화 텅스텐막, 규소막이 배열된 적층일 수 있다. 물론, 앞의 실시형태에서 설명한 다른 전도성 막을 사용하는 것도 가능하다. 본 실시예에서는, 막 두께를 200 nm로 한다.

다음에, 차광막(202)과 보유용량의 하부 전극(203)을 덮도록, 산화규소로 된 제1 절연막(204)(두께 0.6 戶四)을 형성한다. 보유용량의 일부(보유용량의 하부 전극(203) 위)를 선택적으로 에칭하여 개구부(205)를 형성한다. 그리고, 제1 절연막(204)과 개구부(205)를 덮도록, 산화규소로 된 제2 절연막(206)(두께 20 nm)과 비정질 규소막(207)을 감압 열 CVD법에 의해 형성한다. 이 공정은 대기에의 노출없이 연속적으로 행해진다. 이렇게 하여, 불순물(예를 들어, 대기중에 함유된 붕소)이 비정질 규소막의 저면에 흡착하는 것을 방지할 수 있다.

한편, 본 실시예는 비정질 규소막을 이용하지만, 그 대신, 미(微)결정질 규소막 및 비정질 실리콘 게르마늄막과 같은 다른 반도체막이 이용될 수도 있다.

제2 절연막(206)은 보유용량의 유전체로서 기능한다. 따라서, 본 실시예에서는, 제2 절연막이 800  $^{\circ}$  에서 실란(SiH $_4$ ) 및 아산화질소(N $_9$ O)로 형성된다. 따라서, 고품질의 산화규소막(유전체)이 얻어진다.

다음에, 비정질 규소막(207)을 결정화한다. 결정화는 공지의 기술로 수행될 수 있다. 본 실시예에서는 일본 공개특허공고 평9-312260호 공보에 기재된 방법을 사용한다. 이 기술은 결정화를 조장하는 촉매원소로서 니켈, 코발트, 팔라듐, 게르마늄, 백금, 철, 및 구리로부터 선택된 원소를 사용한다. 비정질 규소막의 결정화는 고상(固相) 성장에 의해 달성된다.

본 실시예에서는, 촉매원소로서 니켈을 사용하여, 비정질 규소막(207)상에 니켈함유층(도시되지 않음)을 형성한다. 그리고, 결정화를 위해 550℃에서 4시간 가열처리를 행한다. 그리하여, 결정성 규소(폴리실리콘)막(208)이 형성된다. 이 공정까지의 상태가 도 2(B)에 도시되어 있다.

한편, 결정성 규소막(208)에는 TFT의 스레시홀드 전압을 제어하기 위해 불순물(인 또는 붕소)이 혼입될 수도 있다. 인과 붕소가 개별적으로 첨가되거나 또는 어느 하나만이 첨가될 수도 있다.

다음에, 결정성 규소막(208)상에 산화규소로 된 마스크막(209)(두께 100 nm)을 형성하고, 그 위에 레지스트 마스크(210)를 형성한다. 레지스트 마스크(210)를 마스크로 사용하여 마스크막(209)을 에칭하여 개구부(211a~211c)를 형성한다.

이 상태에서, 주기율표 15족에 속하는 원소(본 실시예에서는 인)를 첨가하여 인 첨가 영역(인이 도핑된 영역) (212a~212c)을 형성한다. 첨가되는 인의 농도는  $5\times10^{18}\sim1\times10^{20}$  atoms/cm<sup>3</sup>(바람직하게는  $1\times10^{19}\sim5\times10^{19}$  atoms/cm<sup>3</sup>)인 것이 바람직하다. 그러나, 첨가되는 인의 농도는 이 범위에 한정되는 것은 아니고, 후의 게터링 공정의 온도와 시간에 따라 그리고 인 도핑 영역의 면적에 따라 변한다.(도 2(C) 참조)

다음에, 레지스트 마스크(210)를 제거하고, 결정성 규소막에 잔존하는 니켈의 게터링를 위해 450~650℃(바람직하게 500~600℃)에서 2~16시간 가열처리를 행한다. 효과적인 게터링을 위한 온도는 열 이력(heat history)의 최고 온도보다 50℃ 더 높거나 더 낮다. 결정화를 위한 가열처리가 550~600℃에서 행해지기 때문에, 만족스런 게터링을 위해서는 500~650℃에서의 가열처리가 바람직하다.

본 실시예에서는, 600℃, 8시간의 가열처리를 행함으로써 니켈이 화살표 방향으로 이동하여, 니켈이 인 첨가 영역 (211a~212c)에 의해 게터링(포획)된다. 이렇게 하여, 결정성 규소막(213, 214)에 잔존하는 니켈의 농도가 2×10<sup>17</sup> atoms/cm<sup>3</sup>(바람직하게는 1×10<sup>16</sup> atoms/cm<sup>3</sup>) 이하로 감소된다. 이 농도는 2차 이온 질량 분석(SIMS)에 의해 확인된다. 상기 값은 측정가능한 한계이다.(도 3(A) 참조)

니켈의 게터링 공정에 이어, 결정성 규소막(213, 214)의 패터닝을 행하여 구동 TFT의 활성층(반도체막)(215)과 화소 TFT의 활성층(216)을 형성한다. 이 공정에서, 포획된 니켈을 가지는 인 첨가 영역을 완전히 제거하는 것이 바람직하다.

다음에, 플라즈마 CVD법 또는 스퍼터링법에 의해 게이트 절연막(217)을 형성한다. 이 게이트 절연막은 화소 TFT의 게이트 절연막으로 기능하고, 그의 두께는 50~200 nm이다. 본 실시예에서는, 두께 100 nm의 산화규소막이다. 이 산화규소막에 질화규소막이 적층되거나 또는 산화질화규소막을 얻기 위해 질소가 혼입될 수도 있다.

게이트 절연막(217)의 형성 후, 레지스트 마스크(도시되지 않음)를 형성한다. 게이트 절연막을 에칭하여, 구동회로부의 활성층 및 화소부의 활성층의 일부를 노출시킨다. 즉, 화소 TFT상에 게이트 절연막(217)이 남고, 구동 TFT가 되는 영역에서는 제거된다. 이 공정까지의 상태가 도 3(B)에 도시되어 있다.

다음에, 산화성 분위기에서 800~1150℃(바람직하게는 900~1100℃)로 15분~8시간(바람직하게는 30분~2시간) 가열 처리를 행한다(열산화 공정). 본 실시예에서는 산소 분위기에서의 950℃, 30분간의 열산화 공정을 행하였다. 한편, 산화성 분위기는 건조 산소 분위기 또는 습윤 산소 분위기일 수 있다. 전자는 반도체막 중의 결정 결함의 감소에 적합하다. 산소 분위기에는 할로겐이 함유될 수도 있다. 할로겐 함유 분위기에서의 열산화 처리는 니켈을 제거하는 효과를 기대할 수 있다.

열산화 처리에 의해, 상기한 게이트 절연막의 에칭에 의해 노출된 반도체막의 표면에 두께  $5\sim50$  nm(바람직하게는  $10\sim30$  nm)의 산화규소막(열산화막)(218)이 형성된다. 최종적으로, 이 산화규소막(218)은 구동 TFT의 게이트 절연막으로 기능한다.

게이트 절연막(217)(화소 TFT에 잔존하는 산화규소막)과 그 아래의 반도체막(216) 사이의 계면에서 산화반응이 진행한다. 따라서, 최종적으로, 화소 TFT의 게이트 절연막(219)은 50~200 nm(바람직하게는 100~150 nm)의 두께를 가진다.

열산화 공정의 종료 후, 구동 TFT의 게이트 배선(220(NTFT에 인접한), 221(PTFT에 인접한)과 화소 TFT의 게이트 배선(222a, 222b)을 형성한다. 게이트 배선(222a, 222b)은 화소 TFT가 이중 게이트 구조이기 때문에 2개로 나타내어져 있으나, 실제로는 동일 배선이다.

본 실시예에서, 게이트 배선(220~222b) 각각은 하층으로부터 규소막, 질화 텅스텐막, 텅스텐막으로 이루어진 적층 막이거나, 또는 하층으로부터 규소막, 규화 텅스텐막으로 이루어진 적층 막이다. 물론, 앞의 실시형태에서 설명된 다른 전도성 막을 사용할 수도 있다. 본 실시예에서는 게이트 배선의 두께가 250 nm이다.

또한, 본 실시예에서는, 규소막의 최하층이 감압 열 CVD법에 의해 형성되었다. 구동회로의 게이트 절연막이 5~50 nm로 얇기 때문에, 스퍼터링법 또는 플라즈마 CVD법은 조건에 따라서는 반도체막(활성층)에 손상을 야기할 수 있다. 따라서, 화학적 기상 반응에 의해 막을 형성하는 열 CVD법이 바람직하다.

다음에, 게이트 배선(220~222b) 각각을 덮도록 두께 25~50 nm의 SiNxOy 막(223)(x = 0.5~2, y = 0.1~0.8)을 형성한다, 이 SiNxOy 막(223)은 게이트 배선(220~222b)의 산화를 방지하고, 또한 나중에 측벽(규소막)이 제거될 때 에칭 스톱퍼로서 기능한다. 이 공정은 핀홀을 효과적으로 줄이기 위해 2번 반복될 수 있다.

SiNxOy 막(213)을 형성하는 전(前)처리로서, 수소 함유 가스(본 실시예서는 암모니아)를 사용한 플라즈마 처리가 행해질 수 있다. 이 전처리에 의해, 활성층(반도체막)내에 수소(플라즈마에 의해 활성화 또는 여기된)가 감금되어, 수소 종단이 효과적으로 달성된다.

또한, 수소 함유 가스에 추가하여 아산화질소 가스가 추가되면, 발생한 수분에 의해 피처리 물체의 표면이 세정되어, 대기중에 함유된 붕소 등에 의한 오염을 효과적으로 방지할 수 있다. 이 공정까지의 상태가 도 3(C)에 도시되어 있다.

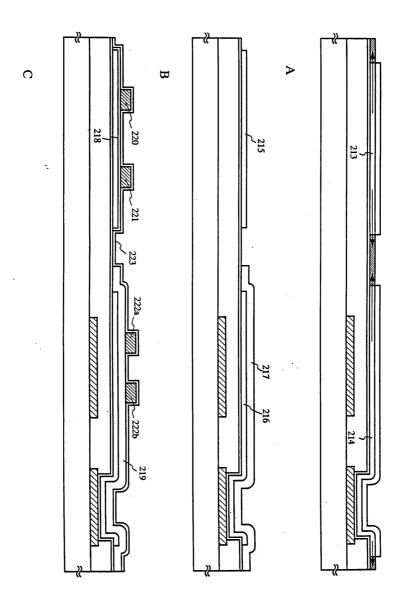

다음에, 비정질 규소막(도시되지 않음)을 형성한다. 염소계 가스에 의해 이방성 에칭을 행하여, 측벽(224, 225, 226a, 226b)을 형성한다. 그후, 레지스트 마스크(227a, 227b)를 형성한다. 그 다음, 반도체막(215, 216)에 주기율표 15족에 속하는 원소(본 실시예서는 인)를 도핑(첨가)한다.

이때, 게이트 배선(220~222b), 측벽(224~226), 및 레지스트 마스크(227a, 227b)가 마스크로서 기능하여, 불순물 영역(228~232)이 형성된다. 불순물 영역(228~232)에 첨가되는 인의 농도는  $5\times10^{19}\sim1\times10^{21}$  atoms/cm<sup>3</sup>이다. 본 명세서에서는, 이때의 인의 농도를 n+로 표시한다.(도 4(A) 참조)

이 공정은 구동 TFT(얇은 게이트 절연막을 가진)와 보유용량이 되는 영역과 구동 TFT(두꺼운 게이트 절연막을 가진)가되는 영역에 대해 분리하여 또는 동시에 행해질 수 있다. 또한, 인 도핑 공정은 이온 주입법(질량 분리를 행하는) 또는 플라즈마 도핑법(질량 분리를 행하지 않는)에 의해 달성될 수 있다. 가속 전압과 도즈량은 실시자에 의해 적절히 설정될 수 있다.

#### 삭제

그리하여, 도 4(A)에 도시된 상태가 얻어진다. 다음에, 레지스트 마스크(227a, 227b) 및 측벽(224~226b)을 제거하고, 인도핑 공정을 반복한다. 이 공정은 인 도즈량이 이전 공정에서보다 낮게 되도록 행해진다. 이렇게 하여, 이전 공정에서 인이

도핑되지 않은 영역에, 저농도로 도핑된 영역(저농도 불순물 영역)이 형성된다. 이 공정은 저농도 불순물 영역에 첨가된 인의 농도가  $5\times10^{17}\sim5\times10^{18}$  atoms/cm<sup>3</sup>로 되도록 행해진다. 본 명세서에서는, 이때의 인의 농도를 n-로 표시한다.(도 4 (B) 참조)

물론, 이 공정도 구동 TFT(얇은 게이트 절연막을 가진)와 보유용량이 되는 영역과 구동 TFT(두꺼운 게이트 절연막을 가진)이 되는 영역에 대해 분리하여 또는 동시에 행해질 수 있다. 또한, 인 도핑 공정은 이온 주입법(질량 분리를 행하는) 또는 플라즈마 도핑법(질량 분리를 행하지 않는)에 의해 행해질 수 있다. 가속 전압과 도즈량은 실시자에 의해 적절히 설정될수 있다.

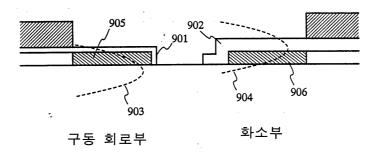

이 저농도 불순물 영역이 LDD 영역으로 기능하기 때문에, 인의 농도를 주의깊게 조절할 필요가 있다. 본 실시예에서는, 플라즈마 도핑법을 행하여, 첨가된 인이 도 9에 도시된 바와 같은 농도 분포(또는 농도 프로파일)를 가지게 한다.

도 9에서, 구동회로부에 인접한 게이트 절연막(901)과 화소부에 인접한 게이트 절연막(902)은 두께가 다르다. 따라서, 첨가된 인은 깊이방향으로 농도 분포가 다르게 된다.

본 실시예에서는, 첨가된 인이 구동회로부에서는 903으로 나타낸 농도 분포를 가지고, 화소부에서는 904으로 나타낸 농도 분포를 가지도록, 인 도핑을 위한 조건(가속 전압 등)을 제어하였다. 이 경우, 폭 방향으로의 농도 분포는 변하지만, 저 농도 불순물 영역(905, 906)에서의 인의 농도는 거의 동일하다.

한편, 도 9에 도시된 공정은 본 명세서에서 언급된 불순물 도핑을 모든 다른 공정에도 적용될 수 있다.

이 공정에 의해, CMOS 회로를 구성하는 NTFT의 소스 영역(233), LDD 영역(234), 및 채널 형성 영역(235)이 획정(劃定) 된다. 또한, 이 공정에 의해, 화소 TFT의 소스 영역(236), 드레인 영역(237), LDD 영역(238a, 238b), 및 채널 형성 영역 (239a, 239b)도 획정된다.

또한, 보유용량의 하부 전극(240)이 획정된다. 본 실시예에서는, 보유용량의 하부 전극(240)에는, 제1 인 도핑(n+) 공정과 제2 인 도핑(n-) 공정에 의해 소스 영역 또는 드레인 영역과 동일한 농도로 인이 첨가된다. 따라서, NTFT의 소스 영역 또는 드레인 영역과 동일한 조성을 가지는 전도성 반도체 영역이 된다.

이 공정에서는, NTFT의 것과 유사한 저농도 불순물 영역(241)이 CMOS 회로의 PTFT가 되는 영역에 형성된다.

다음에, CMOS 회로의 PTFT가 되는 영역을 제외한 영역을 레지스트 마스크(242a, 242b)로 덮고, 주기율표 13족에 속하는 원소(본 실시예에서는 붕소)의 도핑을 행한다. 이 도핑 공정은 붕소 농도가 이전에 도핑된 인의 농도보다 높게 되도록 행해진다. 구체적으로는, 붕소가  $1\times10^{20}\sim3\times10^{21}$  atoms/cm<sup>3</sup>의 농도로 첨가된다. 본 명세서에서는, 이 공정에서의 붕소 농도를 p++로 표시한다. 그 결과, PTFT가 되는 영역에 형성된 N형 도전성을 가지는 불순물 영역은 붕소에 의해 도전형이 반전되어 P형 도전성을 나타낸다.(도 4(C) 참조)

물론, 이 공정은 이온 주입법(질량 분리를 행하는) 또는 플라즈마 도핑법(질량 분리를 행하지 않는)에 의해 행해질 수 있다. 가속 전압 및 도즈량은 실시자에 의해 적절히 설정될 수 있다.

이 공정에 의해, CMOS 회로를 구성하는 PTFT의 소스 영역(244), 드레인 영역(245), 및 채널 형성 영역(246)이 획정된다. 또한, 이 공정에 의해, CMOS 회로의 NTFT의 드레인 영역(243)이 획정된다.

이렇게 하여, 모든 불순물 영역이 형성된다. 그 다음, 레지스트 마스크(242a, 242b)를 제거한다. 그리고, 750∼1150℃에서 20분∼12시간 가열처리를 행한다. 본 실시예에서는, 이 가열처리를 불활성 분위기에서 950℃로 2시간 행하였다.(도 5 (A) 참조)

이 공정에 의해, 각 불순물 영역에 첨가된 인 또는 붕소가 활성화된다. 또한, LDD 영역을 안쪽으로(또는 채널 형성 영역 쪽으로) 확장시켜, LDD 영역이 게이트 절연막을 사이에 두고 게이트 배선과 겹치는 구조를 실현한다.

즉, 구동 TFT의 LDD 영역(247)에서는, LDD 영역(247)에 함유된 인이 채널 형성 영역(248)쪽으로 확산한다. 이것에 의해, LDD 영역(247)이 게이트 절연막을 사이에 두고 게이트 배선(220)과 겹치는 상태가 된다. 이 구조는 핫 캐리어 주입에의한 열화(劣化)를 효과적으로 방지한다.

마찬가지로, 구동 TFT의 PTFT에서는, 소스 영역(249) 및 드레인 영역(250)이 채널 형성 영역(251)쪽으로 확산하고 게이트 배선(221)과 겹친다. 또한, 화소 TFT에서는, LDD 영역(252a, 252b)이 각각 채널 형성 영역(253a, 253b)쪽으로 확산하고 각각 게이트 배선(222a, 222b)과 겹친다.

불순물의 확산 거리는 가열처리의 온도 및 시간에 의해 제어될 수 있다. 따라서, LDD 영역(또는 PTFT의 소스 영역 및 드레인 영역)이 게이트 배선과 겹치는 거리(길이)로 원하는 대로 제어할 수 있다. 본 실시예에서는, 중첩 거리가  $0.05\sim1~\mu$  (바람직하게는  $0.1\sim0.3~\mu$ )가 되도록 조절하였다.

또한, 이 공정에 의해, 보유용량의 상부 전극(254)에 첨가된 인이 활성화되어, N형 도전성을 갖는 영역이 된다. 즉, 캐리어를 유도하도록 보유용량의 하부 전극(103)에 전압을 인가함이 없이 반도체막이 상부 전극(254)으로서 기능하게 할 수 있다.

이 공정까지의 상태가 도 5(A)에 도시되어 있다. 그 다음, 제1 층간절연막(255)을 형성한다. 본 실시예에서는, 그 제1 층간절연막이 플라즈마 CVD법에 의해 형성된 산화규소막(두께  $1 \, \mu$ )이다. 그리고, 콘택트 홀을 형성한 다음, 소스 배선  $(256\sim258)$  및 드레인 배선(25, 260)을 형성한다. 이들 각 배선은 알루미늄을 주성분으로 하는 도전성 막이 2개의 티탄막사이에 보유된 적층 막이다.

소스 배선 및 드레인 배선의 형성 후, 수소화 처리를 행한다. 이 공정은 플라즈마 또는 열에 의해 활성화된(여기된) 수소에 전체 기판을 노출시키는 것으로 되어 있다. 열 활성화된 수소의 경우, 수소화 처리의 온도는 350~450℃(바람직하게는 380~420℃)이다.

그후, 패시베이션막(261)을 형성한다. 이 패시베이션막(261)으로는, 질화규소막, 산화질화규소막, 질화산화규소막, 및 이들 절연막 중 하나와 산화규소막의 적층 막이 사용될 수 있다. 본 실시예에서는, 패시베이션막으로서 질화규소막(두께 300 nm)을 사용하였다.

또한, 본 실시예에서는, 질화규소막을 형성하는 전처리로서, 암모니아 가스를 사용한 플라즈마 처리를 행하여 패시베이션 막(261)을 형성하였다. 이 전처리에 의해, 패시베이션막(261)내에 플라즈마 활성된(여기된) 수소가 감금된다. 또한, 아산화질소 가스와 함께 수소 함유 가스가 사용되면, 발생한 수분에 의해 피처리 물체의 표면이 세정된다. 이것은 대기 중에 함유된 붕소 등에 의한 오염을 방지하는데 효과적이다.

이렇게 하여 패시베이션막(261)을 형성한 후, 약 400~420℃의 가열처리를 행한다. 가열처리 분위기는 불활성 분위기 또는 수소 함유 분위기일 수 있다. 이 공정에 의해, 패시베이션막(261)(질화규소막)으로부터 수소가 방출되고, 이 수소가 하방으로 확산된다. 또한, 이 공정에 의해, 이전의 수소화 공정에 의해 제1 층간절연막(255)에 다량 함유된 수소가 하방으로 확산한다(상방으로의 확산은 패시베이션막(261)에 의해 차단된다). 그리하여, 활성층(반도체막)이 수소 종단된다. 그 결과로, 활성층 내의 댕글링 본드(dangling bond)를 효과적으로 불활성화시킬 수 있다.

수소화 처리가 종료된 후, 두께 1 ﷺ 아크릴막인 제2 충간절연막(262)을 형성하고, 그 위에 티탄막(두께 200 nm)을 형성하고 패터닝을 행하여 차광막(블랙 마스크)(263)을 형성한다.

그 다음, 두께 1 ﷺ 아크릴막인 제3 충간절연막(264)을 형성하고, 콘택트 홀을 형성하고, ITO 막으로 된 화소전극(265)을 형성한다. 그리하여, 도 5(B)에 도시된 바와 같은 구조의 AM-LCD가 완성된다.

본 발명에 따른 AM-LCD는 동일 기판 상에 형성된 구동회로부(또는 신호 처리 회로부)와 화소부의 게이트 절연막의 두께가 다른 것을 특징으로 한다. 대표적으로는, 구동회로부에 사용되는 구동 TFT의 게이트 절연막이 화소부에 사용되는 화소 TFT의 게이트 절연막보다 얇다.

또한, 화소부에서는, 화소 TFT 아래에 두꺼운 하지막(제1 절연막)을 사이에 두고 차광막이 제공되어, 기생용량의 형성을 방지한다. 또한, 보유용량이 될 부분에서 하지막을 선택적으로 제거하고, 새로운 얇은 유전체(제2 절연막)를 형성하여, 큰 커패시턴스를 가지는 보유용량을 형성한다.

본 실시예의 제작공정에 의하면, 최종적으로 형성된 TFT의 활성충(반도체막)은 결정 격자에 연속성을 가지는 특이한 결정 구조의 결정성 규소막으로 형성된다. 이하, 이 특징에 대하여 설명한다.

제1 특징은, 상기한 공정에 의해 형성된 결정성 규소막은 미시적으로 보면 다수의 침상(針狀) 또는 봉상(棒狀) 결정(이하, 총괄적으로 봉상 결정이라 부른다)이 모여 늘어선 결정 구조를 가진다는 것이다. 이 결정 구조는 투과형 전자현미경(TEM)에 의한 관찰로 쉽게 확인된다.

제2 특징은, {220} 면의 배향비가 X선 회절측정(엄밀하게 말하면, θ-2θ법의 X선 회절측정)으로 계산하여 0.7, 대표적으로는 0.85보다 크다는 것이다. 이 배향비는 일본 공개특허공고 평7-321339호 공보에 기재된 방법에 따라 계산된 것이다.

제3 특징은, 결정입계에서 결정 격자에 연속성이 있다는 것이다. 본 발명자들은 개개의 봉상 결정이 서로 접촉하는 결정입계를 HR-TEM(고분해능 투과형 전자현미경)으로 관찰함으로써, 결정입계에서 결정 격자에 연속성이 있다는 것을 확인하였다. 이것은 관찰된 격자 스트라이프(stripe)들이 결정입계에서 서로 연속적으로 결합되어 있는 것으로부터 쉽게 확인된다.

결정입계에서의 결정 격자의 연속성은 그 결정입계가 "평면상(狀) 입계"로 불리는 입계라는 것에 기인한다. 본 명세서에서 사용되는 용어 '평면상 입계'의 정의는 Japanese Journal of Applied Physics vol. 27, No.5, pp751-758, 1988년의 류이 치 시모카와 및 유타카 하야시의 논문 "Characterization of High-Efficiency Cast-Si Solar Cell Wafers by MBIC Measurement"에 기재된 정의를 따른 것이다.

상기 논문에 의하면, 평면상 입계에는, 쌍정(雙晶) 입계, 특수한 적층 결함, 및 특수한 트위스트 입계가 포함된다. 이 평면 상 입계의 특징은 전기적으로 불활성이라는 것이다. 즉, 이 평면상 입계는 결정입계이더라도 캐리어의 이동을 저해하는 트 랩으로 기능하지 않기 때문에 실질적으로 존재하지 않는 것으로 간주될 수 있다.

결정 축(결정 면에 수직인 축)이 <110>축인 경우, {211} 쌍정 입계는 ∑3의 대응 입계로도 불린다. ∑값은 대응 입계의 정합성의 정도를 나타내는 지침이 되는 파라미터이다. 예를 들어, 결정 면의 방위가 {110}이고, {111} 면에 대응하는 격자스트라이프의 각(Θ)이 70.5°인 경우, 2개의 결정립 사이에 형성된 결정입계는 ∑3의 대응 입계라는 것이 알려져 있다.

본 실시예에서의 결정성 규소막은 다음의 특징을 갖는다. <110>축을 가지는 2개의 결정 사이의 결정입계의 대부분은 인접하는 결정립의 격자 스트라이프가 약  $70.5^{\circ}$ 의 각도에서 연속하여 있도록 형성된다. 이것은 HR-TEM에 의한 관찰로 밝혀졌다. 따라서, 결정입계는  $\Sigma$ 3의 대응 입계, 즉,  $\{211\}$  쌍정 입계인 것으로 판명되었다.

상기한 결정 구조(보다 정확하게는, 결정입계의 구조)는 2개의 상이한 결정립이 매우 양호한 정합성을 가지고 서로 접합되어 있는 것을 나타낸다. 즉, 결정입계에서 결정 격자가 연속적으로 연결되어, 격자 결함에 기인한 트랩 준위가 거의 일어나지 않는다. 따라서, 상기한 결정 구조를 갖는 반도체막에는 결정립이 거의 존재하지 않는다고 볼 수 있다.

또한, 700~1150℃의 고온에서의 가열처리(또는 본 실시예에서는 열산화 공정)에 의해 결정립 내의 결함이 거의 완전히 소멸된다는 것이 TEM에 의한 관찰로 확인되었다. 이 가열처리 공정 후에 결함의 수가 크게 감소되는 것이 명백하다.

결함의 수의 차이는 ESR(전자 스핀 공명분석)에 의해 측정된 스핀 밀도의 차이로서 나타난다. 본 실시예의 공정에 따라 형성된 결정성 규소막은  $5\times10^{17}$  spins/cm<sup>3</sup> 이하(바람직하게는  $3\times10^{17}$  spins/cm<sup>3</sup> 이하)의 스핀 밀도를 가진다는 것이 판명되었다. 이 측정값은 현존하는 측정장치의 검출 한계에 가깝기 때문에, 실제의 스핀 밀도는 더 작을 것으로 예상된다.

상기로부터, 본 실시예에서 얻어진 결정성 규소막은 결정입계가 실질적으로 존재하지 않기 때문에 단결정 규소막 또는 실질적으로 단결정 규소막으로 간주될 수 있다는 결론이 얻어진다.

[TFT의 전기적 특성에 관한 지견(知見)]

본 실시예에서 제작된 TFT는 MOSFET에 필적하는 양호한 전기적 특성을 나타낸다. 본 발명자들이 시작(試作)한 TFT(두 께 35 nm의 활성층과, 두께 80 nm의 게이트 절연막을 가지는)로부터 다음의 데이터가 얻어졌다.

(1) 스위칭 성능(온/오프 스위칭의 신속성)의 지표가 되는 서브스레시홀드 계수가 N채널형 TFT와 P채널형 TFT 모두에서  $80\sim150~\text{mV/decade}$ (대표적으로는  $100\sim120~\text{mV/decade}$ )로 작다.

- (2) TFT의 동작 속도의 지표가 되는 전계효과 이동도( $\mu_{FE}$ )가 N채널형 TFT에서는  $150\sim650~cm^2/Vs$ (대표적으로는  $200\sim500~cm^2/Vs$ ), P채널형 TFT에서는  $100\sim300~cm^2/Vs$ (대표적으로는  $120\sim200~cm^2/Vs$ )으로 크다.

- (3) TFT의 구동 전압의 지표가 되는 스레시홀드 전압( $V_{th}$ )이 N채널형 TFT에서는  $-0.5\sim1.5$  V, P채널형 TFT에서는  $-1.5\sim0.5$  V로 작다.

상기한 바와 같이, 매우 양호한 스위칭 특성과 고속동작 특성이 실현될 수 있음이 확인되었다.

#### <u>실시예 2</u>

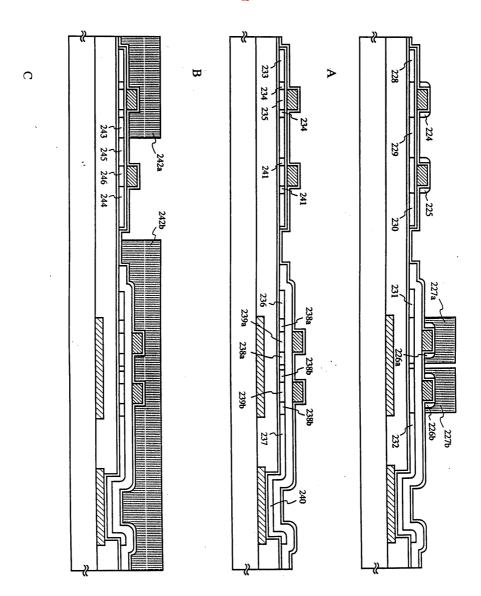

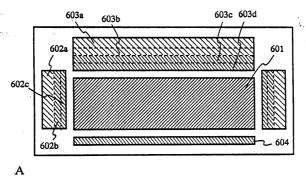

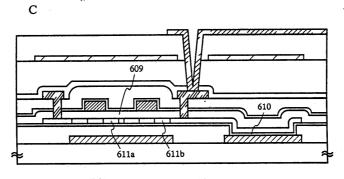

본 실시예에서는, 구체적으로 어떠한 회로에 어떠한 구조의 TFT를 사용하는가를 도 6(A)~도 6(D)를 참조하여 설명한다.

AM-LCD는 회로에 따라 최소로 필요한 동작 전압(전원 전압)이 다르다. 화소부에서의 동작 전압은 액정에 인가되는 전압과 화소 TFT를 구동시키는 전압을 함께 고려하면  $14\sim20~\rm V$ 로 높다. 따라서, 그러한 고전압에 견디는 TFT를 사용할 필요가 있다.

한편, 약 5~10 V의 동작 전압은 소스 구동회로와 게이트 구동회로에 사용되는 시프트 레지스터 회로에 충분하다. 낮은 동작 전압은 외부 신호와의 양호한 호환성과 낮은 소비전력의 이점(利點)을 가진다. 그러나, 고전압에 견딜 수 있는 TFT는 동작 속도가 희생되므로, 고속 동작을 요하는 시프트 레지스터 회로와 같은 회로에는 적합하지 않다.

상기한 바와 같이, 기판상에 형성된 회로는 목적에 따라 2가지 그룹, 즉, 양호한 내전압 특성을 중시하는 TFT용의 회로와 고속 동작을 중시하는 TFT용의 회로로 나누어진다.

본 실시예에서의 대표적인 구성이 도 6(A)~도 6(D)에 도시되어 있다. 도 6(A)는 AM-LCD의 블록도(상면도)이다. 각 화소에 화소 TFT와 보유용량을 가지는 화소부(601)가 도시되어 있다. 이것은 화상 표시부로서 기능한다. 또한, 시프트 레지스터 회로(602a), 레벨 시프터 회로(602b), 및 버퍼 회로(602c)가 도시되어 있다. 이들 회로가 전체로서 게이트 구동회로를 구성한다.

도 6(A)에 도시된 AM-LCD는 화소부를 사이에 두고 2개의 게이트 구동회로를 가지고 있고, 각각의 게이트 구동회로는 동일한 게이트 배선을 가진다. 즉, 게이트 구동회로들 중 어느 한쪽에 고장이 발생하여도 게이트 배선에 전압이 인가될 수 있도록 용장성을 가지고 있다.

또한, 시프트 레지스터 회로(603a), 레벨 시프터 회로(603b), 버퍼 회로(603c), 및 샘플링 회로(603d)가 도시되어 있다. 이들 회로는 전체로서 소스 구동회로를 구성한다. 또한, 화소부를 사이에 두고 소스 구동회로의 반대측에는 프리차지 (precharge) 회로(604)가 설치되어 있다.

상기한 바와 같이 구성된 AM-LCD에서, 시프트 레지스터 회로(602a, 603a)는 고속 동작을 중시하는 회로이다. 그 회로는  $3.3 \sim 10 \text{ V}$ (대표적으로는  $3.3 \sim 5 \text{ V}$ )의 전압에서 작동하고, 높은 내전압 특성을 필요로 하지 않는다. 따라서, 게이트 절연 막은 두께가  $5 \sim 50 \text{ nm}$ (바람직하게는  $10 \sim 30 \text{ nm}$ )로 얇다.

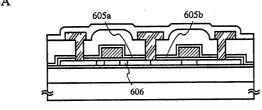

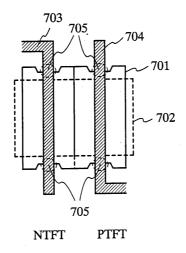

도 6(B)는 고속 동작을 중시하는 시프트 레지스터 회로 및 다른 신호 처리 회로와 같은 회로에 사용되는 CMOS 회로의 개략도이다. 도 6(B)에는, NTFT의 게이트 절연막(605a)과 PTFT의 게이트 절연막(605b)이 도시되어 있다. 이들은  $5\sim50$  nm(바람직하게는  $10\sim30$  nm)의 얇은 두께를 가진다.

LDD 영역(606)의 길이는 바람직하게는  $0.1 \sim 0.5$  /때(대표적으로는  $0.2 \sim 0.3$  /때)이다. 동작 전압이  $2 \sim 3$  V로 낮으면, LDD 영역은 생략될 수도 있다.

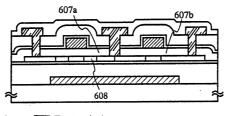

도 6(C)에 도시된 CMOS 회로는 레벨 시프터 회로(602b, 603b), 버퍼 회로(602c, 603c), 샘플링 회로(603d), 및 프리차 지 회로(604)에 적합하다. 이들 회로는 다량의 전류를 통과시킬 수 있도록  $14\sim16$  V의 고전압에서 작동하도록 설계되어 있다. 특히, 게이트 구동회로측은 19 V의 동작 전압을 요하는 경우도 있다. 따라서, 매우 양호한 내전압 특성을 갖는 TFT 가 필요하게 된다.

도 6(C)에 도시된 CMOS 회로는 NTFT의 게이트 절연막(607a)과 PTFT의 게이트 절연막(607b)이  $50\sim200$  nm(바람직하게는  $100\sim150$  nm)의 두께를 가지도록 설계되어 있다. 양호한 내전압 특성을 요하는 이 회로는 도 4(B)에 도시된 시프트 레지스터 회로보다 두꺼운 게이트 절연막을 가지는 것이 바람직하다.

LDD 영역(608)의 길이는  $0.5\sim3$   $\mu$ m(대표적으로는  $2\sim2.5$   $\mu$ m)인 것이 바람직하다. 도 6(C)에 도시된 CMOS 회로는 버퍼 회로와 같은 고전압(화소의 전압과 동일)을 받는다. 따라서, LDD 영역의 길이는 화소 길이와 같거나 비슷한 것이 바람직하다.

도 6(D)는 화소부(601)의 개략도이다. 화소 TFT는 액정에 인가되는 전압을 포함하여  $14 \sim 16$  V의 동작 전압을 필요로 한다. 또한, 액정 및 보유용량에 저장된 전하를 1프레임 기간 보유하여야 하기 때문에 오프 전류가 최소이어야 한다.

상기한 이유로, 본 실시예에서는 NTFT를 이용한 이중 게이트 구조로 하고, 게이트 절연막(609)의 두께는  $50\sim200$  nm(바람직하게는  $100\sim150$  nm)이다. 이 막두께는 도 6(C)에 도시된 CMOS 회로의 것과 같거나 다를 수 있다.

또한, 보유용량의 유전체(610)의 막 두께는 5~75 nm(바람직하게는 20~50 nm)이다.

LDD 영역(611a, 611b)의 길이는  $1\sim 4$   $\mu$ m(대표적으로는  $2\sim 3$   $\mu$ m)인 것이 바람직하다. 도 6(D)에 도시된 화소 TFT는  $14\sim 16$  V의 고전압을 받으므로, LDD 영역의 길이는 길어야 한다.

또한, 화소 TFT는 오프 전류(TFT가 오프 상태에 있을 때 흐르는 드레인 전류)가 가능한 한 낮아야 한다. 따라서, 각 LDD 영역(611a, 611b)은 게이트 배선과 겹치지 않는 영역(1~3 டி)을 가져야 한다. 이 영역은 통상의 LDD 영역으로 기능한다.

AM-LCD를 참조하여 위에 설명된 바와 같이, 동일 기판 상에 다양한 회로가 형성되고, 이들은 필요로 하는 동작 전압(또는 전원 전압)이 다르다. 이러한 경우에 대처하는 효과적인 방법은 본 실시예의 경우에서와 같이, 게이트 절연막의 두께가 상이하거나 또는 구동회로부와 화소부에서 LDD 영역의 길이가 상이하도록 설계된 TFT를 배치하는 것이다.

본 실시예에 나타낸 구성은 실시예 1에 나타낸 회로를 사용하여 효과적으로 실현된다.

#### 실시예 3

실시예 1에 나타낸 방법은 게이트 절연막을 선택적으로 제거하는 공정을 포함한다. 구동 TFT가 되는 영역에서는, 이 공정이 도 7에 도시된 바와 같이 행해지는 것이 바람직하다. 도 7에는, 활성층(701), 게이트 절연막(217)의 단부(702), 및 게이트 배선(703, 704)이 도시되어 있다. 도 7에 도시된 바와 같이, 게이트 배선이 부호 705에서 활성층을 넘어 있다. 게이트 절연막이 활성층(701)의 단부에 부분적으로 남아 있는 것이 바람직하다.

활성층(701)의 단부에는, 나중에 행해지는 열산화 공정에서 "엣지 씨닝(edge thinning)"이라 불리는 현상이 일어난다. "엣지 씨닝"은, 활성층 단부 아래로 잠입하는 것처럼 산화반응이 진행하여 그 단부가 얇아지는 동시에 위쪽으로 굽어지는 현상이다. 이 현상이 일어나면, 게이트 배선이 얇아진 엣지를 넘을 때 쉽게 절단되는 문제가 생긴다.

게이트 절연막이 도 7에 도시된 방법으로 제거되면, 게이트 배선이 게이트 절연막을 넘는 부분(705)에서 엣지 씨닝 현상이 일어나는 것을 방지할 수 있다. 따라서, 게이트 배선 절단 문제를 미리 방지할 수 있다. 또한, 본 실시예의 구성은 실시예 1에서 효과적으로 이용될 수 있다.

#### 실시예 4

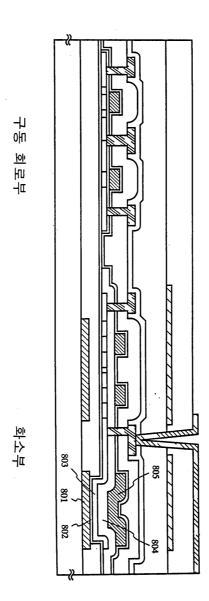

본 실시예는 도 1에 도시된 AM-LCD 구조의 변형을 나타낸다. 변형된 구조가 도 8에 도시되어 있다. 이 구조에서는, 게이트 배선과 동시에 형성된 용량 배선이 보유용량의 전극으로 사용된다.

도 8에 도시된 구조에서, 제1 전극(801), 제1 유전체(802), 및 제2 전극(803)이 제1 보유용량을 형성하고, 제2 전극(803), 제2 유전체(804), 및 제3 전극(805)이 제2 보유용량을 형성한다. 제2 유전체(804)는 게이트 절연막의 연장부이고, 제3 전극(805)은 게이트 배선과 동시에 형성된다.

병렬 접속된 2개의 보유용량이 큰 커패시티를 가지는 보유용량을 제공한다. 이 경우, 제1 전극(801)과 제3 전극(805)은 상이하거나 또는 동일한 고정 전위을 가진다.

본 실시예의 구조는 실시예 1에서 제3 전극을 제공하는 것만으로 실현될 수 있다. 본 실시예의 구성이 실시예 2 및 3의 구성과 자유롭게 조합될 수 있다.

#### 실시예 5

본 실시예는 실시예 1에 도시된 공정에 따라 기판상에 TFT가 형성된 AM-LCD를 실제로 제작하는 예를 나타낸다.

도 5(B)에 도시된 상태에서, 화소 전극(265)상에 배향막(두께 80 nm)을 형성한다. 유리 기판상에 컬러 필터, 투명 전극(대 향 전극), 및 배향막을 형성함으로써 대향 기판을 제작하고, 배향막을 러빙처리한다. TFT가 형성된 기판과 대향 기판을 시일재로 접합하고, 그 사이에 액정을 보유시킨다. 셀 조립 공정은 공지된 어떤 방법으로도 달성될 수 있으므로, 그에 대한 상세한 설명은 생략한다.

셀 갭을 유지하기 위해 스페이서가 이용될 수 있다. 스페이서는 대각선이 1인치보다 작은 AM-LCD의 경우에는 생략될 수도 있다.

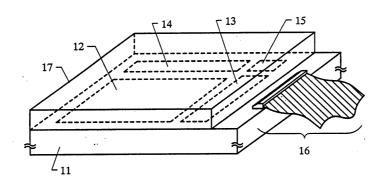

상기한 바와 같이 제작된 AM-LCD는 도 10에 도시된 바와 같은 외관을 가진다. 액티브 매트릭스 기판(11)(TFT가 형성된 기판)이 도시되어 있고, 이 기판 위에 화소부(12), 소스 구동회로(13), 게이트 구동회로(14), 및 신호 처리 회로(15)(신호 분할회로, D/A 변환회로, γ-보정회로, 차등 증폭회로 등)가 형성되어 있고, FPC(flexible print circuit)(16)가 설치되어 있다. 대향 기판(17)도 도시되어 있다.

또한, 본 실시예는 실시예 1~4의 어느 것과도 자유롭게 조합될 수 있다.

#### 실시예 6

본 실시예는 실시예 1과 상이한 방법으로 결정성 규소막을 형성하는 경우를 나타낸다.

구체적으로, 본 실시예는 비정질 규소막을 결정화하기 위해 일본 공개특허공고 평7-130652호(대응 미국 특허출원 08/329,644호)의 실시예 2에 기재된 기술을 이용한다. 이 기술은 결정화를 위한 촉매원소(대표적으로는 니켈)를 비정질 규소막의 표면에 선택적으로 보유시킨다. 선택된 부분이 결정성장의 핵으로 기능한다.

이 기술에 따르면, 특정 방향으로 결정을 성장시킬 수 있어, 매우 높은 결정성을 갖는 결정성 규소막을 형성하는 것이 가능하다.

촉매원소를 선택적으로 보유시키기 위해, 마스크용 절연막이 제공된다. 이 절연막은 게터링을 위해 첨가되는 인에 대한 마스크로도 사용될 수 있다. 이것은 공정 수의 감소를 돕는다. 이 기술의 상세한 설명에 대해서는, 본 출원인이 출원한 일본 공개특허공고 평10-247735호(대응 미국 특허출원 09/034,041호) 공보에 기재되어 있다.

또한, 본 실시예는 실시예 1~5의 어느 것과도 자유롭게 조합될 수 있다.

#### 실시예 7

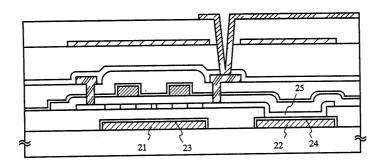

본 실시예는 실시예 1의 것과는 구조가 다른 보유용량을 형성하는 예에 대하여 도 11을 참조하여 설명한다. 구체적으로, 보유용량의 유전체는 보유용량의 하부 전극을 산화시켜 얻어진 산화막이다.

먼저, 기판 상에 차광막(21)과 보유용량의 하부 전극(22)을 형성한다. 재료로서는, 실시예 1에서 사용된 것과 동일한 재료가 사용될 수 있다. 본 실시예에서는, 상부 표면이 산화된 때 양호한 절연막을 형성하는 재료가 바람직한 재료이다.

본 실시예에서는, 3층 구조의 적충 막이 사용되었다. 즉, 하층으로부터 규소막, 텅스텐막(또는 텅스텐 규화물막), 및 규소 막이 배열된 적충 막이나, 또는, 하층으로부터 탄탈막, 질화탄탈막, 및 탄탈막이 배열된 적충 막이 사용된다. 차광막(21)과 보유용량의 하부 전극(22)을 형성한 후, 가열처리, 플라즈마 처리, 또는 양극산화 처리에 의해 그 표면상에 산화막(23, 24)을 형성한다. 본 실시예에서는, 그 산화막이 산화규소막이고, 900℃에서 30분의 가열처리에 의해 형성되었다. 또한, 산화막(23, 24)은 요구되는 산화막의 두께 및 질에 따라 선택되는 적절한 조건 하에 형성될 수 있다.

본 실시예에서, 보유용량이 보유용량의 하부 전극(22), 산화규소막(24)(열산화에 의해 형성된), 및 보유용량의 상부 전극 (반도체막)(25)으로 형성되었다.

보유용량의 하부 전극(22)이 하층으로부터 탄탈막, 질화탄탈막, 탄탈막으로 이루어진 3층 구조의 적층 막인 경우, 산화막 (24)은 산화탄탈막이고, 따라서, 매우 높은 비유전율을 갖는 유전체를 얻는 것이 가능하다. 따라서, 작은 면적에서 매우 큰 커패시티를 가지는 용량을 제공한다.

또한, 본 실시예는 실시예 1~6의 어느 것과도 자유롭게 조합될 수 있다.

#### 실시예 8

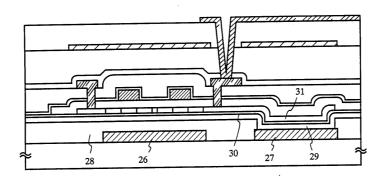

본 실시예는 실시예 1의 것과는 구조가 다른 보유용량을 형성하는 예를 도 12를 참조하여 설명한다. 구체적으로, 보유용량의 유전체는 산화탄탈막이다.

도 12에, 차광막(26), 보유용량의 하부 전극(27), 및 하지막(산화규소막)(28)이 도시되어 있다. 그들의 재료에 대한 설명은 실시예 1에서 볼 수 있다. 본 실시예에서는, 하지막(28)에 개구부를 형성한 다음, 스퍼터링법에 의해 산화탄탈막(29)을 형성한다. 막 두께는  $10\sim100$  nm(바람직하게는  $30\sim50$  nm)이다.

다른 방법으로는, 개구부를 형성한 다음, 보유용량의 노출된 하부 전극(27)을 가열처리, 플라즈마 처리, 또는 양극산화 처리에 의해 산화시켜, 산화탄탈막을 형성한다.

산화탄탈막(29)의 형성 후, 보유용량의 얇은 산화규소막(30)(두께 약 10 nm)과 상부 전극(31)을 형성한다. 대기에의 노출 없이 산화규소막(30)과 비정질 규소막(또는 후에 보유용량의 상부 전극이 되는 반도체막)을 연속적으로 성막하는 것이 바람직하다. 이러한 방법에 의해, 활성층의 하면(상부 전극과 인접한)이 대기중에 함유된 붕소 등으로 오염되는 것을 방지할 수 있다.

또한, 이 산화규소막(30)은 반도체막(또는 규소막)인 보유용량의 상부 전극(31)과 산화탄탈막(29)의 상호 반응을 방지하는 배리어(barrier) 층으로 기능한다.

상기한 바와 같이, 본 실시예는 보유용량의 유전체로서 산화탄탈막(29)과 산화규소막(30)의 적층을 사용한다. 산화탄탈막(29)이 큰 비유전율(약 25)을 가지기 때문에, 유전체는 그의 두께가 약 100 nm이더라도 충분히 큰 커패시티를 제공한다. 그 두께는 절연 내압을 고려하여 30~50 nm로 얇은 것이 바람직하다.

또한, 본 실시예는 실시예 1~7의 어느 것과도 자유롭게 조합될 수 있다.

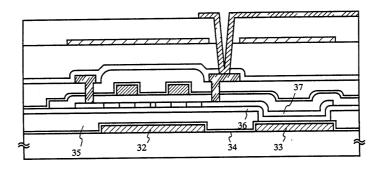

#### 실시예 9

본 실시예는 실시예 1의 것과는 구조가 다른 보유용량을 형성하는 예를 도 13을 참조하여 설명한다. 구체적으로, 보유용량의 유전체가 형성되기 전에, 에칭 스톱퍼로서 절연막을 형성한다.

도 13에, 차광막(32), 보유용량의 하부 전극(33), 및 이들을 덮는 산화탄탈막(34)(두께 20 nm)이 도시되어 있다. 차광막(32) 및 보유용량의 하부 전극(33)의 재료에 대한 설명은 실시예 1에서 볼 수 있다. 산화탄탈막은 스퍼터링법에 의해 또는 보유용량의 하부 전극(33)을 산화시켜 형성할 수 있다.

그 위에 하지막(35)(산화규소막)을 형성하고, 그 하지막(35)에 개구부를 형성한다. 하지막(35)의 에칭은 산화탄탈막(34)에 의해 완전히 정지된다. 따라서, 아래에 있는 전극(33)은 에칭되지 않고, 산화탄탈막(34)의 개구부에서 막 두께가 균일하다.

개구부를 형성한 후, 보유용량의 유전체(본 실시예에서는 산화규소막)(36)를 형성하고, 그 유전체 위에 보유용량의 상부 전극(반도체막)(37)을 형성한다.

본 실시예에서는, 에칭 스톱퍼가 산화탄탈막이고, 하지막은 산화규소막이다. 그러나, 막(에칭 스톱퍼로서의)과 하지막이 충분히 큰 에칭 선택비(10 이상, 바람직하게는 100 이상)를 갖는 경우, 다른 절연막들을 조합하여 사용할 수도 있다.

예를 들어, 하지막이 산화규소막인 경우, 에칭 스톱퍼는 질화규소막일 수 있다.

본 실시예에서는, 하지막(35)에 개구부를 형성한 다음, 다시 산화규소막(보유용량의 유전체로서)을 형성하였다. 그러나, 보유용량의 유전체로서 산화탄탈막(에칭 스톱퍼로서)만을 사용할 수도 있다. 이 경우, 보유용량의 상부 전극과 산화탄탈막 사이에 얇은 산화규소막(배리어 층으로서)을 개재시키는 것이 바람직하다.

물론, 질화규소막이 에칭 스톱퍼로서 사용되는 경우, 유전체를 특별히 형성하지 않고 보유용량의 유전체로서 질화규소막만을 사용하는 것이 가능하다.

또한, 본 실시예는 실시예 1~8의 어느 것과도 자유롭게 조합될 수 있다.

#### <u>실시예 10</u>

실시예 1에서는 니켈(규소막을 결정화시키는 촉매원소로서)의 게터링을 위해 인을 사용하였으나, 본 실시예에서는 니켈의 게터링을 위해 인 외에 다른 원소를 에 사용한다.

도 2(B)에 도시된 상태에 도달할 때까지 실시예 1의 공정을 행한다. 도 2(B)에, 결정성 규소막(208)이 도시되어 있다. 본실시예에서는, 결정화를 위한 니켈이 극히 낮은 농도로 사용된다. 구체적으로,  $0.5\sim3$  ppm(중량으로)의 니켈을 함유하는 층을 비정질 규소막상에 형성한 다음, 가열처리를 행하여 결정화한다. 결정성 규소막 중의 니켈 농도는  $1\times10^{17}\sim1\times10^{19}$  atoms/cm<sup>3</sup>(대표적으로는  $5\times10^{17}\sim1\times10^{18}$  atoms/cm<sup>3</sup>)이다.

결정성 규소막을 형성한 후, 할로겐을 함유하는 산화성 분위기에서  $800 \sim 1150 \, \mathbb{C}$ (바람직하게는  $900 \sim 1000 \, \mathbb{C}$ )로  $10 \in \mathbb{C}$   $0 \in \mathbb{C}$  가열처리를 행한다.

본 실시예에서는, 산소와 3~10 vol%의 염화수소로 이루어진 분위기에서 950℃로 30분간 가열처리를 했하였다.

이 가열처리에 의해, 결정성 규소막 중의 니켈이 휘발성 염화니켈로 되어 처리 분위기 내로 이탈한다. 즉, 할로겐의 게터링 작용에 의해 니켈이 제거될 수 있다. 니켈이 결정성 규소막 중에 고농도로 존재하는 경우, 니켈이 편석하는 부분에서 변칙 적인 산화가 일어난다. 따라서, 니켈 농도는 결정화 단계에서 가능한 한 낮게 유지되어야 한다.

또한, 본 실시예는 실시예 1~9의 어느 것과도 자유롭게 조합될 수 있다.

#### <u>실시예 11</u>

본 실시예는 CMOS 회로 및 화소부의 구조가 실시예 1과 상이한 다른 AM-LCD에 대하여 설명한다. 구체적으로는, AM-LCD가 회로에서 요구하는 사양에 따라 다르게 배치된 LDD 영역을 가지는 예를 나타낸다.

CMOS 회로 및 화소부의 기본 구조는 도 1에 도시된 것과 같다. 따라서, 본 실시예에서는 필요 부분에만 참조 부호를 붙여 설명한다.

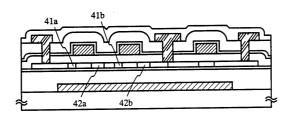

도 14(A)에 도시된 회로는, NTFT가 이중 게이트 구조이고 PTFT가 단일 게이트 구조인 버퍼 회로용 CMOS 회로이다. 본실시예에서는, 소스측의 LDD 영역(41a, 41b)은 측벽만이 마스크로서 사용되는 자기정합 프로세스에 의해 형성된다. 드레인측의 LDD 영역(42a, 42b)은 레지스트 마스크를 사용하여 형성된다. 후자의 LDD 영역들 각각은 전자의 LDD 영역들 각보다 큰 폭(길이)을 갖는다.

구동회로와 신호 처리 회로에 사용되는 CMOS 회로는 고속 동작을 필요로 한다. 따라서, 동작 속도를 낮추는 저항 성분이 가능한 한 많이 제거되어야 한다. 그러나, 핫 캐리어 내성(耐性)을 높이기 위해 필요한 LDD 영역이 저항 성분으로서 기능하므로, 동작 속도가 희생된다.

그러나, 핫 캐리어가 주입되는 것은 채널 형성 영역의 드레인 영역측 단부이다. 따라서, 게이트 절연막을 사이에 두고 게이트 전국과 겹치는 LDD 영역을 그 부분에 형성하는 것이 핫 캐리어에 대한 양호한 대책이다. 따라서, 채널 형성 영역의 소스 영역측 단부에는 필요 이상으로 LDD 영역을 형성하는 것이 필요하지 않다.

또한, 도 14(A)에 도시된 구조는 소스 영역과 드레인 영역이 서로 바뀐 화소 TFT와 같은 동작을 하는 경우에는 적용될 수 없다. CMOS 회로의 경우, 통상 소스 영역과 드레인 영역이 고정되어 있으므로, 도 14(A)에 도시된 바와 같은 구조를 실현하는 것이 가능하다.

상기한 바와 같은 구조는 소스 영역측의 LDD 영역에 기인한 저항 성분을 제거하고, 이중 게이트 구조는 소스 및 드레인을 가로질러 인가되는 전계를 분산시켜 완화시킨다.

도 14(B)는 일 실시예에 따른 화소부의 구조를 나타낸다. 도 14(B)에 도시된 구조의 경우, 소스 영역 또는 드레인 영역에 가까운 일 측에만 LDD 영역(43a, 43b)이 형성된다. 즉, 2개의 채널 형성 영역(44a, 44b)들 사이에는 LDD 영역이 형성되지 않는다.

화소 TFT의 경우, 충전과 방전이 반복되기 때문에 소스 영역과 드레인 영역이 빈번하게 바뀌게 된다. 따라서, 도 14(B)에 도시된 구조는 어느 것이 드레인 영역이 되어도 채널 형성 영역의 드레인 영역측에 LDD 영역을 형성하는 것과 같다. 반대로, 채널 형성 영역(44a, 44b)들 사이의 영역에 전계가 집중되지 않기 때문에, LDD 영역(저항 성분이 되는)을 제거하는 것이 온(on) 전류(TFT가 온 상태일 때 흐르는 전류)를 증가시키는 효과적인 방법이다.

또한, 본 실시예는 실시예 1~10의 어느 것과도 자유롭게 조합될 수 있다.

#### <u>실시예 12</u>

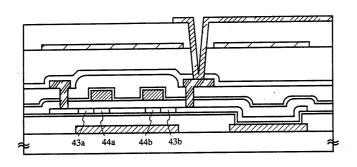

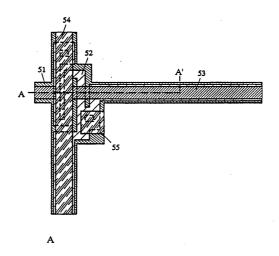

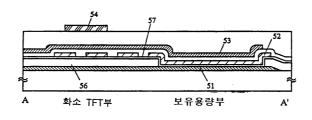

본 실시예는 화소부에서 보유용량이 형성되는 위치에 관한 예를 도 15(A) 및 도 15(B)를 참조하여 설명한다. 도 15(B)는 도 15(A)의 A-A'선을 따라 취한 단면도이다. 도 15(A)와 도 15(B)에서 동일한 부분에 동일한 부호를 사용한다.

도 15(A)에, 차광막과 동시에 형성되는 보유용량의 하부 전극(51), 반도체막(52), 게이트 배선(53), 소스 배선(54), 및 드레인 배선(드레인 전극)(55)이 도시되어 있다.

보유용량의 하부 전극(51)이 게이트 배선(53) 및 소스 배선(54)과 겹치도록 형성되고, 메시(mesh) 패턴(매트릭스 형태)을 가진다. 즉, 보유용량의 모든 하부 전극(51)은 동일 전위(바람직하게는 최저 전원 전위)로 되어 있다.

그 위에 절연막(57)을 사이에 두고 하지막(56)과 반도체막(52)이 형성된다(그 절연막(57)은 나중에 보유용량의 유전체가된다). 또한, 보유용량부에서, 하지막(56)이 제거되고, 보유용량의 하부 전극(51), 절연막(57), 및 반도체막(52)에 의해 보유용량이 형성된다.

본 실시예는 보유용량부가 게이트 배선(53) 및 소스 배선(54) 아래에 형성되는 것을 특징으로 한다. 그러한 구조는 개구율을 증가시키고, 밝은 화상의 표시를 가능하게 한다. 또한, 보유용량으로부터의 전하의 누설이 방지되도록 보유용량이 광으로부터 보호되어 있다.

본 실시예에서는, 화소 TFT가 삼중 게이트 구조로 되도록 반도체막이 패터닝되지만, 본 실시예가 이것에 한정되는 것은 아니다.

또한, 본 실시예는 실시예 1~11의 어느 것과도 자유롭게 조합될 수 있다.

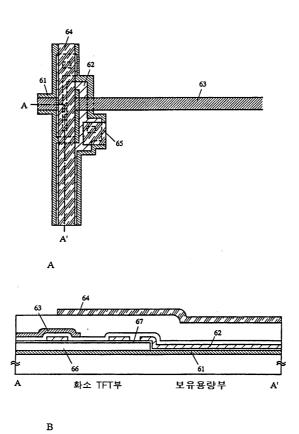

#### 실시예 13

본 실시예는 화소부에서 보유용량이 형성되는 위치에 관한 예를 도 16(A) 및 도 16(B)를 참조하여 설명한다. 도 16(B)는 도 16(A)의 A-A'선을 따라 취한 단면도이다. 도 16(A)와 도 16(B)에서 동일한 부분에 동일한 부호를 사용한다.

도 16(A)에, 차광막과 동시에 형성되는 보유용량의 하부 전극(61), 반도체막(62), 게이트 배선(63), 소스 배선(64), 및 드레인 배선(드레인 전극)(65)이 도시되어 있다.

보유용량의 하부 전극(61)이 소스 배선(64)과 겹치도록 형성되고, 메쉬 패턴(매트릭스 형태)을 가진다. 즉, 보유용량의 모든 하부 전극(61)은 동일 전위(바람직하게는 최저 전원 전위)로 되어 있다.

그 위에 절연막(67)을 사이에 두고 하지막(66)과 반도체막(62)이 형성된다(그 절연막(67)은 나중에 보유용량의 유전체가된다) 또한, 보유용량부에서, 하지막(66)이 제거되고, 보유용량의 하부 전극(61), 절연막(67), 및 반도체막(62)에 의해 보유용량이 형성된다.

본 실시예는 보유용량부가 소스 배선(64) 아래에 형성되는 것을 특징으로 한다. 그러한 구조는 개구율을 증가시키고, 밝은 화상의 표시를 가능하게 한다. 또한, 보유용량으로부터의 전하의 누설이 방지되도록 보유용량이 광으로부터 보호되어 있다.

본 실시예에서는, 화소 TFT가 삼중 게이트 구조로 되도록 반도체막이 패터닝되지만, 본 실시예가 이것에 한정되는 것은 아니다.

또한, 본 실시예는 실시예 1~11의 어느 것과도 자유롭게 조합될 수 있다.

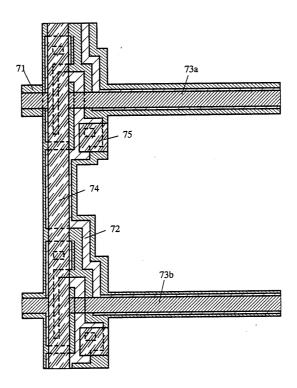

#### <u>실시예 14</u>

본 실시예는 화소부에서 보유용량이 형성되는 위치에 관한 예를 도 17에 의거하여 설명한다.

도 17에, 보유용량의 하부 전극(71), 반도체막(72), 게이트 배선(73a, 73b), 소스 배선(74), 및 드레인 배선(드레인 전극) (75)이 도시되어 있다.

보유용량의 하부 전극(71)이 게이트 배선(73a, 73b) 및 소스 배선(74)과 겹치도록 형성되고, 메쉬 패턴(매트릭스 형태)을 가진다. 즉, 보유용량의 모든 하부 전극(71)은 동일 전위(바람직하게는 최저 전원 전위)로 되어 있다.

그 위에 하지막과 보유용량의 유전체를 사이에 두고 반도체막(72)을 형성한다. 또한, 보유용량부에서, 하지막이 제거되고, 보유용량의 하부 전극(71), 보유용량의 유전체, 및 반도체막(72)에 의해 보유용량이 형성된다.

본 실시예는 보유용량부가 제2 배선(73b) 및 소스 배선(74) 아래에 형성되는 것을 특징으로 한다. 본 실시예는, 선택되지 않은 게이트 배선(또는 선택된 게이트 배선(73a)에 인접한 게이트 배선(73b)) 아래에 보유용량이 형성되는 점에서 실시예 12 및 13과 다르다.

본 실시예의 경우, 전하가 보유용량부에 저장될 때, 그 위의 게이트 배선은 선택되지 않는다. 따라서, 기생용량에 기인하여 보유용량에 저장된 전하가 변동하는 것을 방지할 수 있다.

그러한 구조는 개구율을 증가시키고, 밝은 화상의 표시를 가능하게 한다. 또한, 보유용량으로부터의 전하의 누설이 방지되도록 보유용량이 광으로부터 보호되어 있다

본 실시예에서, 반도체막은 화소 TFT가 삼중 게이트 구조가 되도록 패턴화된다. 그러나 본 실시예는 여기에 제한되지 않는다.

또한, 본 실시예는 실시예 1~11의 어느 것과도 자유롭게 조합될 수 있다.

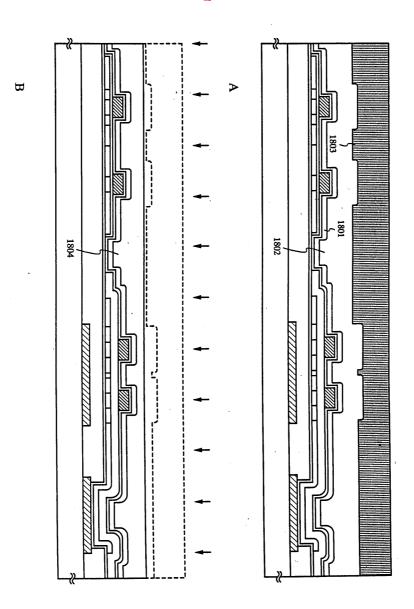

#### 실시예 15

본 실시예는 제1 층간절연막이 실시예 1과 상이한 방법으로 형성되는 예를 도 18(A) 및 도 18(B)에 의거하여 설명한다.

도 5(A)에 도시된 활성화 공정이 완료될 때까지 실시예 1의 방법이 행해진다. 그 다음, 두께 50~100 nm(본 실시예에서는 70 nm)의 질화산화규소막 A(1801)를 형성하고, 그 위에 두께 600 nm~1  $\mu$ m(본 실시예에서는 800 nm)의 질화산화규소 막 B(1802)를 형성하며, 또 그 위에 레지스트 마스크(1803)를 형성한다.(도 18(A) 참조)

또한, 질화산화규소막 A(1801)와 질화산화규소막 B(1802)는 그에 함유된 질소, 산소, 수소, 규소의 조성이 서로 다르다. 질화산화규소막 A(1801)는 질소 7%, 산소 59%, 수소 2%, 규소 32%로 이루어져 있고, 질화산화규소막 B(1802)는 질소 33%, 산소 15%, 수소 23%, 규소 29%로 이루어져 있다. 그러나, 이러한 조성에 한정되는 것은 아니다.

레지스트 마스크(1803)는 질화산화규소막 B(1802)의 표면을 완전히 평탄화하도록 두껍다.

다음에, 레지스트 마스크(1803)와 질화산화규소막 B(1802)에 대하여, 탄소 테트라플루오라이드와 산소의 혼합 가스로 건식 에칭을 행한다. 이 건식 에칭은 레지스트 마스크(1803)와 질화산화규소막 B(1802) 모두에 거의 동일한 에칭률로 진행하다.

이 에칭으로, 도 18(B)에 도시된 바와 같이, 레지스트 마스크(1803)가 완전히 제거되고, 질화산화규소막 B(1802)는 부분적으로(본 실시예에서는 표면에서부터 300 nm 깊이까지) 제거된다. 그 결과, 레지스트 마스크(1803)의 표면 평탄도가 에 칭된 질화산화규소막 B의 표면 평탄도에 직접 영향을 미친다.

그리하여, 극도로 평탄한 제1 충간절연막(1804)이 얻어진다. 본 실시예에서는, 제1 충간절연막(1804)이 500 nm의 두께를 가진다. 이후의 공정에 대해서는 실시예 1을 참조하기 바란다.

또한, 본 실시예는 실시예 1~14의 어느 것과도 자유롭게 조합될 수 있다.

#### <u>실시예 16</u>

본 발명은 종래의 MOSFET상에 층간절연막을 형성하고 그 위에 TFT를 형성할 때에도 적용될 수 있다. 즉, 반도체 회로상에 반사형 AM-LCD가 형성된 3차원 구조의 반도체장치를 실현하는 것이 가능하다.

또한, 상기 반도체 회로는 SIMOX, Smart-Cut(SOITEC사의 등록상표), 및 ELTRAN(Canon사의 등록상표)과 같은 SOI 기판 상에 형성된 것일 수도 있다.

또한, 본 실시예는 실시예 1~14의 어느 것과도 자유롭게 조합될 수 있다.

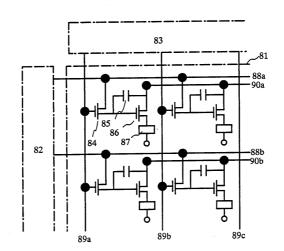

## 실시예 17

본 발명은 액티브 매트릭스형 EL(전계발광) 표시장치에도 적용될 수 있다.

도 19는 액티브 매트릭스형 EL 표시장치의 회로도이다. 표시 영역(81), X방향(게이트) 구동회로(82), 및 Y방향(소스) 구동회로(83)가 도시되어 있다. 표시 영역(81)의 각 화소는 스위칭용 TFT(84), 용량(85), 전류 제어용 TFT(86), 및 유기 EL소자(87)를 가지고 있다. 스위칭용 TFT(84)는 X방향(게이트) 신호선(88a)(또는 88b) 및 Y방향(소스) 신호선(89a)(도는 89b, 89c)에 접속되어 있다. 전류 제어용 TFT(86)는 소스선(90a, 90b)에 접속되어 있다.

본 실시예의 액티브 매트릭스형 EL 표시장치는 X방향 구동회로(82) 및 Y방향 구동회로(83)에 사용되는 TFT의 게이트 절 연막이 스위칭용 TFT(84) 및 전류 제어용 TFT(86)의 것보다 얇은 것을 특징으로 한다. 용량(85)은 실시예 1, 4, 7, 8 및 9에 도시된 것과 동일한 구조의 보유용량이다.

본 실시예의 액티브 매트릭스형 EL 표시장치는 실시예 1~16의 어느 구조와도 조합될 수 있다.

#### <u>실시예 18</u>

본 실시예는 본 발명에 따라 제작된 EL(전계발광) 표시장치를 설명한다. 도 20(A)는 그 EL 표시장치의 상면도이고, 도 20(B)는 그의 단면도이다.

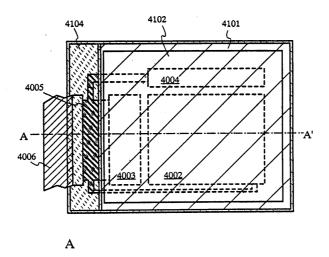

도 20(A)에, 기판(4001), 화소부(4002), 소스측 구동회로(4003), 및 게이트측 구동회로(4004)가 도시되어 있다. 각 구동 회로는 배선(4005) 및 FPC(flexible print circuit)(4006)를 통해 외부 장치에 접속된다.

화소부(4002), 소스측 구동회로(4003), 및 게이트측 구동회로(4004)는 제1 시일재(4101), 커버링재(covering材)(4102), 충전재(4103), 및 제2 시일재(4104)로 둘러싸여 있다.

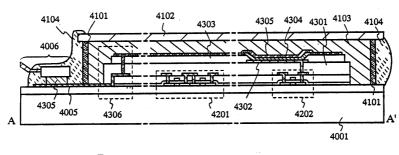

도 20(B)는 도 20(A)의 A-A'선을 따라 취한 단면도이다. 기판(4001)상에 구동 TFT(4201)와 화소 TFT(4202)가 형성되어 있다. 구동 TFT(4001)(여기서는 n채널형 TFT와 p채널형 TFT가 도시되어 있다)는 소스측 구동회로(4003)에 포함되어 있고, 화소 TFT는 화소부(4002)에 포함되어 있다.(여기서는 EL 소자에 대한 전류를 제어하는 TFT가 도시되어 있다)

본 실시예에서, 구동 TFT(4201)는 도 1에 도시된 구동회로와 동일한 구조의 TFT이고, 화소 TFT(4202)는 도 1에 도시된 화소부와 동일한 구조의 TFT이다.

구동 TFT(4201) 및 화소 TFT(4202)상에 층간절연막(평탄화막)(4301)이 형성되고, 그 위에, 화소 TFT(4202)의 드레인에 전기적으로 접속된 화소 전극(음극)(4302)가 형성되어 있다. 화소 전극(4302)은 차광 도전막(대표적으로는, 알루미늄, 구리 또는 은을 주성분으로 하는 도전막, 또는 다른 도전막과의 적층 막)일 수 있다. 본 실시예에서는, 화소 전극으로 알루미늄 합금 막이 사용되었다.

화소 전극(4302)상에 절연막(4303)이 형성된다. 이 절연막(4303)은 화소 전극(4302)상에 형성된 개구부를 가진다. 이 개구부에서, 화소 전극(4302)상에 EL(전계발광) 층(4304)이 형성된다. EL 층(4304)은 공지의 유기 EL 재료 또는 무기 EL 재료로 형성될 수 있다. 유기 EL 재료는 저분자 재료(모노머) 또는 고분자 재료(폴리머)일 수 있다.

EL 층(4303)은 공지의 기술로 형성될 수 있다. EL 층은 정공 주입층, 정공 수송층, 발광층, 전자 수송층, 및 전자 주입층으로 이루어진 적층 구조 또는 단층 구조일 수 있다.

EL 층(4303) 위에 투명 도전막으로 된 양극(4305)이 형성된다. 투명 도전막은 산화인듐과 산화주석의 혼합물 또는 산화인듐과 산화아연의 혼합물로 형성될 수 있다. 양극(4305)과 EL 층(4304) 사이의 계면으로부터 수분과 산소를 가능한 한 많이 제거하는 것이 바람직하다. 따라서, 그들은 진공에서 연속적으로 형성되어야 한다. 다른 방법으로는, EL 층(4304)이 질소 또는 희가스 분위기에서 형성되고, 양극(4305)은 산소 및 수분과 접촉하지 않도록 형성된다. 본 실시예는 상기한 바와 같이 성막(成膜)할 수 있게 하는 멀티체임버형(클러스트 툴형)의 성막 장치를 사용한다.

양극(4305)은 부호 4306으로 나타낸 영역에서 배선(4005)에 전기적으로 접속되어 있다. 그 배선(4005)은 양극(4305)에 소정의 전압을 인가하는 것이고, 전기 전도성 재료(4307)을 통해 FPC(4006)에 전기적으로 접속된다.

이렇게 하여, 화소 전극(음극)(4302), EL 층(4304), 및 양극(4305)으로 이루어진 EL 소자가 형성된다. 이 EL 소자는 제1시일재(4101) 및 커버링재(4102)(제1시일재(4101)에 의해 기판(4001)에 접합된)로 둘러싸이고, 충전재(4103)로 봉입된다.

커버링재(4102)는 유리판, FRP(섬유유리 보강 플라스틱) 판, PVF(폴리비닐 플루오라이드) 막, Mylar 막, 폴리에스터 막, 또는 아크릴 막일 수 있다. 본 실시예에서는, EL 소자가 커버링재(4102)쪽으로 광을 방출하기 때문에 투명 재료가 사용되었다.

그러나, EL 소자가 커버링재의 반대측으로 광을 방출하는 경우에는 투명 재료를 사용할 필요가 없다. 이 경우에는, 금속판 (대표적으로는 스테인리스 강판), 세라믹 판, 또는 알루미늄 포일이 PVF 막 또는 Mylar 막의 충들 사이에 보유되는 구조의 시트를 사용하는 것이 가능하다.

또한, 충전재(4103)는 UV광 경화 수지 또는 열경화 수지일 수 있고, 또한, PVC(폴리비닐 클로라이드), 아크릴, 폴리이미드, 에폭시 수지, 실리콘 수지, PVB(폴리비닐 부티랄), 또는 EVA(에틸렌 비닐 아세테이트)일 수도 있다. 충전재(4103)에는, EL 소자의 열화(劣化)를 방지하기 위해 흡습제(바람직하게는 산화바륨)가 혼입될 수도 있다. 또한, 본 실시예에서는, EL 소자로부터의 광이 충전재(4103)를 통과하도록 투명 재료가 사용되었다.

또한, 충전재(4103)는 스페이서를 포함할 수도 있다. 스페이서는 산화바륨으로 형성될 수 있고, 이 경우, 스페이서 자체가수분을 흡수할 수 있다. 스페이서가 사용되는 경우, 스페이서로부터의 압력이 양극(4305)상에 형성된 수지막인 버퍼층에의해 완화될 수 있다.

배선(4005)은 전도성 재료(4305)를 통해 FPC(4006)에 전기적으로 접속된다. 배선(4005)은 FPC(4006)로 신호를 전송하고, 그 신호는 화소부(4002), 소스측 구동회로(4003), 및 게이트측 구동회로(4004)로 보내진다. 배선(4005)은 FPC (4006)를 통해 외부 장치에 전기적으로 접속된다.

본 실시예에서는, 제2 시일재(4104)가 제1 시일재(4101)의 노출된 부분과 FPC(4006)의 일부를 덮도록 제공되어, EL 소자가 외기로부터 완전히 격리되어 있다. 얻어진 EL 표시장치는 도 20(B)에 도시된 바와 같은 단면 구조를 가진다. 본 실시예의 EL 표시장치는 실시예  $1\sim4$  및 실시예  $6\sim16$ 의 어느 구조와도 조합될 수 있다.

#### 실시예 19

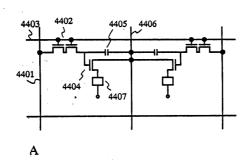

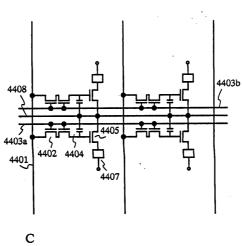

본 실시예는 실시예 18에 나타낸 EL 표시장치의 화소부에 사용될 수 있는 화소 구조의 예를 설명한다. 이 화소 구조가 도 21(A)~도 21(C)에 도시되어 있다. 스위칭용 TFT(4402)의 소스 배선(4401), 스위칭 TFT(4402)의 게이트 배선(4403), 전류 제어용 TFT(4404), 용량(4405), 전류 공급 배선(4406, 4408), 및 EL 소자(4407)가 도시되어 있다.

도 21(A)는 전류 공급 배선(4406)이 2개의 화소에 공통으로 사용되는 경우를 나타낸다. 즉, 2개의 화소가 전류 공급 배선 (4406)에 대하여 대칭이 되도록 형성되어 있다. 이 경우, 전류 공급 배선의 수를 줄일 수 있어, 화소부를 더욱 미세하게 만들 수 있다.

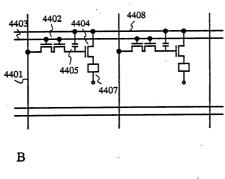

또한, 도 21(B)는 전류 공급 배선(4408)이 게이트 배선(4403)과 평행하게 배열된 경우를 나타낸다. 도 21(B)는 전류 공급 배선(4408)이 게이트 배선(4403)과 겹치지 않는 구조를 나타낸다. 그러나, 이들이 상이한 층에 형성되는 경우, 이들이 절연막을 사이에 두고 서로 겹치도록 형성될 수도 있다. 이 경우, 전류 공급 배선(4408)과 게이트 배선(4403)이 공통으로 소정의 면적을 차지하여, 화소부를 더욱 미세하게 제조하는 것이 가능하다.

도 21(C)는 도 21(B)와 동일한 구조를 나타낸다. 전류 공급 배선(4408)이 게이트 배선(4403)과 평행하게 형성되고, 2개의화소가 전류 공급 배선(4408)에 대하여 대칭이다. 전류 공급 배선(4408)은 게이트 배선(4403)과 겹칠 수도 있다. 이 경우, 전류 공급 배선의 수를 줄이는 것이 가능하여 화소부를 더욱 미세하게 제조하는 것이 가능하다.

#### <u>실시예 20</u>

본 발명에 따른 전기광학장치, 또는 보다 상세하게는 본 발명에 따른 액정 표시장치는 네마틱 액정 이외에 다양한 액정을 사용할 수 있다. 그러한 액정이, 예를 들어, 다음의 문헌에 기재되어있다.

1998, SID, "Characteristics and Driving Scheme of Polymer-Stabilized Monostable FLCD Exhibiting Fast Response Time and High Contrast Ratio with Gray-Scale Capability" by H. Eurue at al.; 1997, SID DIGEST, 841, "A Full-Color Thresholdless Antiferroelectric LCD Exhibiting Wide Viewing Angle with Fast Response Time" by T. Yoshida et al.; 1996, J. Mater. Chem.6(4), 671-673, "Thresholdless antiferroelectricity in liquid crystals and its application to displays" by S Inui et al.; 미국 특허 제5,594,569호 공보.

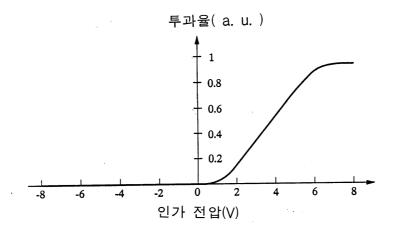

도 22는, 액정이 등방상(相)-콜레스테릭 상-카이랄 스멕틱 상 전이를 나타내는 강유전성 액정(FLC)이고, 콜레스테릭 상-카이랄 스멕틱 상 전이는 DC 전압의 인가 하에서 일어나고, 콘(cone) 엣지가 대략 러빙 방향과 정렬된 단안정 FLC의 전기 광학 특성을 나타낸다.

강유전성 액정이 도 22에 도시된 바와 같이 발생하는 표시 모드가 "Half-V자형 스위칭 모드"라 불린다. 도 22에서, 세로 좌표는 투과율(임의의 단위)을 나타내고, 가로 좌표는 인가 전압을 나타낸다. "Half-V자형 스위칭 모드"에 대한 더 상세한 것은 다음 문헌을 참조하기 바란다.

Terada et al., "Half-V자형 스위칭 모드 FLCD". Preprints for 제46차 Lecture Meeting of Applied Physics, March 1999, p.1316; Yoshihara et al., "Time-sharing full-color LCD by ferroelectric liquid crystal", Liquid Crystal, vol.3, No.3, p.190.

강유전성 혼합 액정이 저전압 구동과 계조 표시를 가능하게 한다는 것을 도 22에서 볼 수 있다. 본 발명에 따른 액정 표시 장치는 그러한 전기광학 특성을 나타내는 강유전성 액정을 사용할 수 있다.

액정이 어떤 온도 범위에서 반강유전 상을 나타내는 경우 반강유전성 액정(AFLC)이라 불린다. 반강유전성 액정을 함유하는 혼합 액정은 전계에 따라 투과율이 연속적으로 변하는 전기광학 응답 특성을 나타낸다. 그것이 스레시홀드레스 (thresholdless) 반강유전성 혼합 액정으로 불린다. 그 액정은 구동 전압이 대략  $\pm 2.5~\mathrm{V}(44~\mathrm{FM})$  약  $1\sim 2~\mathrm{pm}$ )일 때 소위 V 자형 전기광학 응답 특성을 나타내는 몇몇 종(種)을 포함한다.

대개, 스레시홀드레스 반강유전성 혼합 액정은 강한 자발분극 경향을 나타내고, 또한 높은 유전율을 가진다. 따라서, 액정 표시장치에 사용되는 경우, 화소는 비교적 큰 보유용량을 갖는다. 따라서, 자발분극 걍향이 약한 것을 사용하는 것이 바람 직하다.

상기한 스레시홀드레스 반강유전성 혼합 액정이 본 발명에 따른 액정 표시장치에 사용되는 경우, 낮은 전압에서 표시장치를 구동시키는 것이 가능하다. 이것은 소비전력을 절감시킨다.

또한, 본 실시예에서 설명한 액정은 실시예  $1\sim16$ 에 나타낸 구조를 갖는 액정 표시장치에 사용될 수 있다.

#### 실시예 21

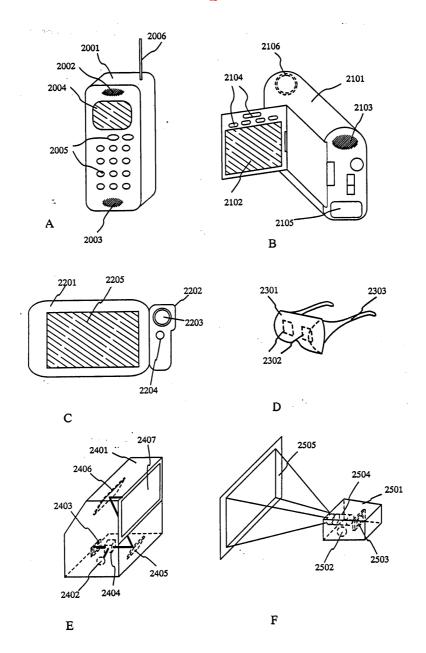

본 발명에 따른 전기광학장치 및 반도체 회로는, 비디오 카메라, 디지털 카메라, 프로젝터, 프로젝션 TV, 고글형 표시장치 (헤드 장착형 표시장치), 내비게이션 시스템, 음향 재생 장치, 노트북형 퍼스널 컴퓨터, 게임기, 휴대형 정보 단말기(휴대 전화기, 휴대형 게임기, 및 전자 서적), 및 기록 매체를 가진 영상 재생 장치와 같은 전자 기기의 표시 및 신호 처리 회로로서 사용될 수 있다. 이들의 예를 도 23~도 25에 나타내었다.

#### 삭제

도 23(A)는, 본체(2001), 음성 출력부(2002), 음성 입력부(2003), 표시장치(2004), 조작 스위치(2005), 및 안테나(2006)로 구성된 휴대 전화기를 나타낸다. 본 발명에 따른 전기광학장치는 표시장치(2004)에 적용될 수 있고, 본 발명에 따른 반도체 회로는 음성 출력부(2002), 음성 입력부(2003), CPU, 및 메모리에 적용될 수 있다.

도 23(B)는, 본체(2101), 표시장치(2102), 음성 입력부(2103), 조작 스위치(2104), 배터리(2105), 및 수상(受像)부 (2106)로 구성된 비디오 카메라를 나타낸다. 본 발명에 따른 전기광학장치는 표시장치(2205)에 적용될 수 있고, 본 발명에 따른 반도체 회로는 음성 입력부(2103), CPU 및 메모리에 적용될 수 있다.

도 23(C)는, 본체(2201), 카메라부(2202), 수상부(2203), 조작 스위치(2204), 및 표시장치(2205)로 구성된 모바일 컴퓨터를 나타낸다. 본 발명에 따른 전기광학장치는 표시장치(2205)에 적용될 수 있고, 본 발명에 따른 반도체 회로는 CPU 및 메모리에 적용될 수 있다.

도 23(D)는, 본체(2301), 표시장치(2302), 및 암(arm)부(2303)로 구성된 고글형 표시장치를 나타낸다. 본 발명에 따른 전 기광학장치는 표시장치(2302)에 적용될 수 있고, 본 발명에 따른 반도체 회로는 CPU 및 메모리에 적용될 수 있다.

도 23(E)는, 본체(2401), 광원(2402), 액정 표시장치(2403), 편광 빔 스플리터(2404), 반사기(2405, 2406), 및 스크린 (2407)으로 구성된 리어(rear)형 프로젝터(프로젝션 TV)를 나타낸다. 본 발명에 따른 전기광학장치는 액정 표시장치 (2403)에 적용될 수 있고, 본 발명에 따른 반도체 회로는 CPU 및 메모리에 적용될 수 있다.

도 23(F)는, 본체(2501), 광원(2502), 액정 표시장치(2503), 광학계(2504), 및 스크린(2505)으로 구성된 프론트(front)형 프로젝터를 나타낸다. 본 발명에 따른 전기광학장치는 액정 표시장치(2502)에 적용될 수 있고, 본 발명에 따른 반도체 회로는 CPU 및 메모리에 적용될 수 있다.

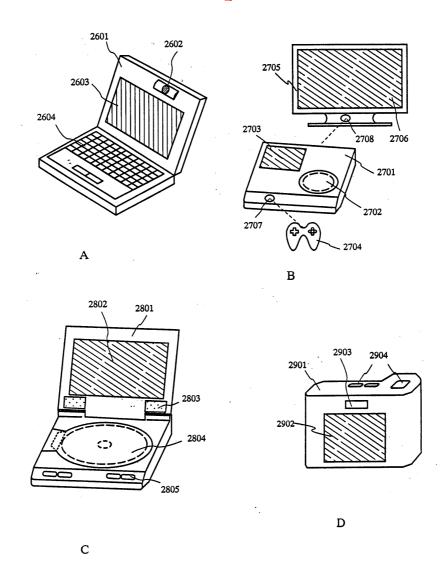

도 24(A)는, 본체(2601), 화상 입력부(2602), 표시장치(2603), 및 키보드(2603)로 구성된 퍼스널 컴퓨터를 나타낸다. 본 발명에 따른 전기광학장치는 표시장치(2603)에 적용될 수 있고, 본 발명에 따른 반도체 회로는 CPU 및 메모리에 적용될 수 있다. 도 24(B)는, 본체(2701), 기록 매체(2702), 표시장치(2703), 및 콘트롤러(2704)로 구성된 전자 게임기를 나타낸다. 이 전자 게임기는 디스플레이 장치(본체(2705)와 표시장치(2706)를 포함)에서 재생되는 음성 및 화상을 생성한다. 콘트롤러 (2704)와 본체(2701) 사이의 통신 또는 전자 게임기와 디스플레이 장치 사이의 통신은 배선, 무선, 또는 광으로 달성된다. 본 실시예의 게임기는 적외선이 센서(2707, 2708)에 의해 검출되도록 구성되어 있다. 본 발명에 따른 전기광학장치는 표시장치(2703, 2706)에 적용될 수 있고, 본 발명에 따른 반도체 회로는 CPU 및 메모리에 적용될 수 있다.

도 24(C)는, 본체(2801), 표시장치(2802), 스피커(2803), 기록 매체(2804), 및 조작 스위치(2805)로 구성된, 프로그램 기록 매체(또는 기록 매체)를 가진 플레이어(영상 재생 장치)를 나타낸다. 이 플레이어는 기록 매체로서 DVD(Digital Versatile Disc) 또는 CD를 사용한다. 이 플레이어는 음악, 영화, 게임, 및 인터넷을 즐길 수 있게 한다. 본 발명에 따른 전기광학장치는 표시장치(2802)에 적용될 수 있고, 본 발명에 따른 반도체 회로는 CPU, 및 메모리에 적용될 수 있다.

도 24(D)는, 본체(2901), 표시장치(2902), 송신기(2903), 조작 스위치(2904), 및 수상부(도시되지 않음)로 구성된 디지털 카메라를 나타낸다. 본 발명에 따른 전기광학장치는 표시장치(2902)에 적용될 수 있고, 본 발명에 따른 반도체 회로는 CPU, 및 메모리에 적용될 수 있다.

도 25(A) 및 도 25(B)는 리어형 프로젝터(도 23(E))와 프론트형 프로젝터(도 23(F))에 사용되는 광학 엔진의 세부를 나타 낸다. 도 25(A)는 광학 엔진을 나타내고, 도 25(B)는 광학 엔진에 포함된 광원 광학계를 나타낸다.

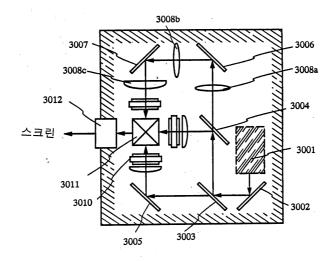

도 25(A)에 도시된 광학 엔진은 광원 광학계(3001), 거울(3002, 3005, 3006, 3007), 다이크로익 거울(3003, 3004), 광학 렌즈(3008a~3008c), 프리즘(3011), 액정 표시장치(3010), 및 투사(投射) 광학계(3012)로 구성된다. 투사 광학계(3012)는 투사 렌즈를 가지고 있다. 본 실시예에서 도시된 것은 3 셋트의 액정 표시장치(3010)를 가진 3판형이지만, 단판형도 가능하다. 도 25(A)에 화살표로 나타낸 광로에 광학 렌즈 또는 필름이 배치된다. 그 필름은 편광 기능을 가진 것 또는 위상차를 조절하는 것일 수 있다. 그 필름은 IR 막일 수도 있다.

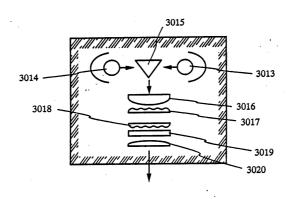

도 25(B)에 도시된 바와 같이, 광원 광학계(3001)는 광원(3013, 3014), 합성 프리즘(3015), 콜리메이터 렌즈(3016, 3020), 렌즈 어레이(3017, 3018), 및 편광 변환 소자(3019)로 구성된다. 도 25(B)에 도시된 광원 광학계는 2개의 광원을 가지고 있으나, 1개의 광원도 충분하고, 또는 3개의 광원도 사용가능하다. 광원 광학계에서의 광로에는, 광학 렌즈, 편광기능을 가진 막, 위상차를 조절하는 필름, IR 막이 제공될 수 있다.

상기한 바와 같이, 본 발명은 그 응용분야가 매우 넓고, 어떠한 분야의 전자 기기에도 적용가능하다. 본 실시예의 전지 기기는 실시예  $1\sim20$ 에 도시된 구조의 조합에 의해 실현될 수 있다.

#### 발명의 효과

#### 삭제

본 발명에 의하면, 동일 기판상에 상이한 두께를 갖는 2개의 게이트 절연막을 가진 TFT를 제작할 수 있다. 따라서, 전기광학장치(대표적으로는 AM-LCD) 또는 표시장치로서 그러한 전기광학장치를 가진 전자 기기에 적용될 경우, 본 발명은 요구되는 사양 및 성능에 따라 적절한 회로를 배치하는 것을 가능하게 한다. 따라서, 반도체장치의 성능 및 신뢰성을 크게 향상시킬 수 있다.

본 발명에 의하면, 전기광학장치의 화소부에서 보유용량의 유전체가 얇게 될 수 있다. 즉, 작은 면적에서 큰 커패시턴스를 가지는 보유용량이 형성될 수 있다. 또한, 보유용량이 게이트 배선 및 소스 배선 아래에 은폐될 수 있어, 대각선 1인치 이하 의 전기광학장치에서도 개구율을 감소시키지 않고 충분한 보유용량을 확보하는 것이 가능하다.

#### 도면의 간단한 설명

도 1은 본 발명의 AM-LCD의 단면 구조를 나타내는 도면.

도 2(A)~도 2(C)는 실시예 1의 AM-LCD의 제작공정을 나타내는 도면.

도 3(A)~도 3(C)는 실시예 1의 AM-LCD의 제작공정을 나타내는 도면.

- 도 4(A)~도 4(C)는 실시예 1의 AM-LCD의 제작공정을 나타내는 도면.

- 도 5(A) 및 도 5(B)는 실시예 1의 AM-LCD의 제작공정을 나타내는 도면.

- 도 6(A)~도 6(D)는 실시예 2의 AM-LCD의 블록도와 회로 배치를 나타내는 도면.

- 도 7은 실시예 3의 구동 TFT(CMOS 회로)의 구조를 나타내는 도면.

- 도 8은 실시예 4의 AM-LCD의 단면 구조를 나타내는 도면.

- 도 9는 실시예 1에서 불순물 원소를 첨가한 때의 농도 분포를 나타내는 도면.

- 도 10은 실시예 5의 AM-LCD의 단면 구조를 나타내는 도면.

- 도 11은 실시예 7의 AM-LCD의 단면 구조를 나타내는 도면.

- 도 12는 실시예 8의 AM-LCD의 단면 구조를 나타내는 도면.

- 도 13은 실시예 9의 AM-LCD의 단면 구조를 나타내는 도면.

- 도 14(A) 및 도 14(B)는 실시예 11의 구동회로 및 화소부의 단면 구조를 나타내는 도면.

- 도 15(A) 및 도 15(B)는 실시예 12의 화소부의 상면 구조 및 단면 구조를 나타내는 도면.

- 도 16(A) 및 도 16(B)는 실시예 13의 화소부의 상면 구조 및 단면 구조를 나타내는 도면.

- 도 17은 실시예 14의 화소부의 상면 구조를 나타내는 도면.

- 도 18(A) 및 도 18(B)는 실시예 15의 AM-LCD의 제작공정을 나타내는 도면.

- 도 19는 실시예 17의 EL 표시장치의 회로 구성을 나타내는 도면.

- 도 20(A) 및 도 20(B)는 실시예 18의 EL 표시장치의 상면 구조 및 단면 구조를 나타내는 도면.

- 도 21(A)~도 21(C)는 실시예 19의 EL 표시장치의 화소부를 나타내는 도면.

- 도 22는 실시예 20의 액정의 광학 응답 특성을 나타내는 도면.

- 도 23(A)~도 23(F)는 실시예 21의 전자 기기의 예를 나타내는 도면.

- 도 24(A)~도 24(D)는 실시예 21의 전자 기기의 예를 나타내는 도면.

- 도 25(A) 및 도 25(B)는 실시예 21의 광학 엔진의 구성을 나타내는 도면.

B 로 표시된 CMOS 회로

◯◯◯ 로 표시된 CMOS 회로

고 로 표시된 화소부 D

도면7

도면10

도면11

도면12

도면13

도면14

A

В

도면15

В

도면17

도면19

도면21

도면22

A

В