(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4759944号

(P4759944)

(45) 発行日 平成23年8月31日(2011.8.31)

(24) 登録日 平成23年6月17日(2011.6.17)

(51) Int.Cl.

F 1

|              |           |

|--------------|-----------|

| HO1L 21/8247 | (2006.01) |

| HO1L 27/115  | (2006.01) |

| HO1L 29/788  | (2006.01) |

| HO1L 29/792  | (2006.01) |

| HO1L 27/10   | (2006.01) |

|            |       |

|------------|-------|

| HO1L 27/10 | 4 3 4 |

| HO1L 29/78 | 3 7 1 |

| HO1L 27/10 | 4 8 1 |

請求項の数 2 (全 16 頁)

(21) 出願番号

特願2004-200913 (P2004-200913)

(22) 出願日

平成16年7月7日(2004.7.7)

(65) 公開番号

特開2006-24705 (P2006-24705A)

(43) 公開日

平成18年1月26日(2006.1.26)

審査請求日

平成19年6月18日(2007.6.18)

前置審査

(73) 特許権者

302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人

100082175

弁理士 高田 守

(74) 代理人

100106150

弁理士 高橋 英樹

(74) 代理人

100148057

弁理士 久野 淑己

(72) 発明者

清水 秀

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

審査官 粟野 正明

最終頁に続く

(54) 【発明の名称】不揮発性半導体記憶装置の製造方法

(57) 【特許請求の範囲】

【請求項 1】

メモリセルと、該メモリセルに隣接する周辺回路とを有する不揮発性半導体記憶装置の製造方法であって、

基板の活性領域を分離する素子分離であって、その上面が該基板の表面よりも高い素子分離を該基板に形成する工程と、

前記素子分離の間の前記基板上にシリコン酸化膜を形成する工程と、

前記素子分離の間の前記シリコン酸化膜上にポリシリコン膜を自己整合的に形成する工程と、

前記周辺回路を覆う第1レジストパターンを形成した後、前記メモリセルにおける前記素子分離を所定の膜厚だけエッチングする工程と、 10

前記基板全面に多層絶縁膜を形成する工程と、

前記メモリセルを覆う第2レジストパターンを形成した後、前記素子分離の表面を前記基板の表面よりも落ち込ませることなく、前記周辺回路における前記素子分離の上面を前記基板の表面と同等の高さとなるように若しくは前記基板の表面よりも高くなるように、前記周辺回路における前記多層絶縁膜と前記ポリシリコン膜と前記シリコン酸化膜とを除去する工程と、

前記周辺回路の前記基板上にゲート絶縁膜を形成する工程と、

前記基板の全面に導電膜を形成する工程と、

前記周辺回路及び前記メモリセルにおける前記導電膜をパターニングする工程と、

10

20

前記メモリセルにおいて、パターニングされた前記導電膜をマスクとして前記多層絶縁膜及び前記ポリシリコン膜をパターニングする工程とを含み、

前記メモリセルにおける活性領域は、短手方向に複数並んで配置された短冊状の第1活性領域と、該第1活性領域の端部を相互に接続すると共に前記メモリセルを取り囲むように配置された第2活性領域とを有し、

前記第1レジストパターンの端部が前記第2活性領域に位置するように前記第1レジストパターンを形成することを特徴とする不揮発性半導体記憶装置の製造方法。

【請求項2】

メモリセルと、該メモリセルに隣接する周辺回路とを有する不揮発性半導体記憶装置の製造方法であって、

基板の活性領域を分離する素子分離であって、その上面が該基板の表面よりも高い素子分離を該基板に形成する工程と、

前記素子分離の間の前記基板上にトンネル酸化膜となるシリコン酸化膜を形成する工程と、

前記素子分離の間の前記シリコン酸化膜上にフローティングゲート電極となるポリシリコン膜を自己整合的に形成する工程と、

前記周辺回路を覆う第1レジストパターンを形成した後、前記メモリセルにおける前記素子分離を所定の膜厚だけエッチングすることにより、前記メモリセルにおける前記ポリシリコン膜の側面上部を露出させる工程と、

前記第1レジストパターンを除去した後、前記基板全面に多層絶縁膜を形成する工程と、

前記メモリセルを覆う第2レジストパターンを形成した後、前記素子分離の表面を前記基板の表面よりも落ち込ませることなく、前記周辺回路における前記素子分離の上面を前記基板の表面と同等の高さとなるように若しくは前記基板の表面よりも高くなるように、前記周辺回路における前記多層絶縁膜と前記ポリシリコン膜と前記シリコン酸化膜とを除去する工程と、

前記周辺回路における前記シリコン酸化膜を除去した後、周辺回路の前記基板上にゲート絶縁膜を形成する工程と、

前記基板の全面にゲート電極又はコントロールゲート電極となる導電膜を形成する工程と、

前記周辺回路及び前記メモリセルにおける前記導電膜をパターニングすることにより、前記周辺回路の前記ゲート絶縁膜上にゲート電極を形成すると共に、前記メモリセルの前記多層絶縁膜上にコントロールゲート電極を形成する工程と、

前記コントロールゲート電極をマスクとして前記メモリセルの前記多層絶縁膜及び前記ポリシリコン膜をパターニングすることにより、フローティングゲート電極を形成する工程とを含み、

前記メモリセルにおける活性領域は、短手方向に複数並んで配置された短冊状の第1活性領域と、該第1活性領域の端部を相互に接続すると共に前記メモリセルを取り囲むように配置された第2活性領域とを有し、

前記第1レジストパターンの端部が前記第2活性領域に位置するように前記第1レジストパターンを形成することを特徴とする不揮発性半導体記憶装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、不揮発性半導体記憶装置及びその製造方法に係り、特にメモリセルに隣接する周辺回路の素子分離におけるエッチング残渣の発生防止に関するものである。

【背景技術】

【0002】

不揮発性半導体記憶装置のメモリセルのカップリング比を向上させる方法が提案されている（例えば、特許文献1参照）。

10

20

30

40

50

## 【0003】

また、公知技術ではなく、出願人が知っているメモリセルのカップリング比を向上させる方法として、素子分離としての分離酸化膜を所定の厚さだけエッチングすることによりコントロール電極の側面を露出させて、コントロールゲート電極に対向するフローティングゲート電極の表面積を増大させる方法がある。以下、この方法について説明する。

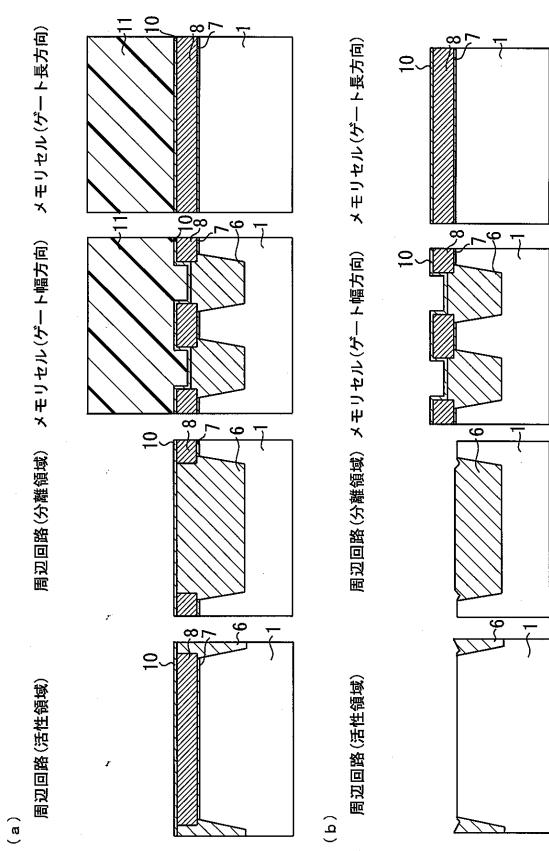

## 【0004】

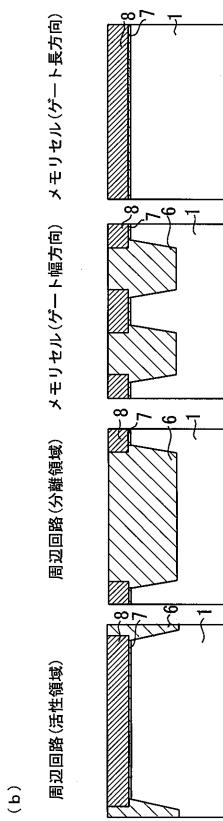

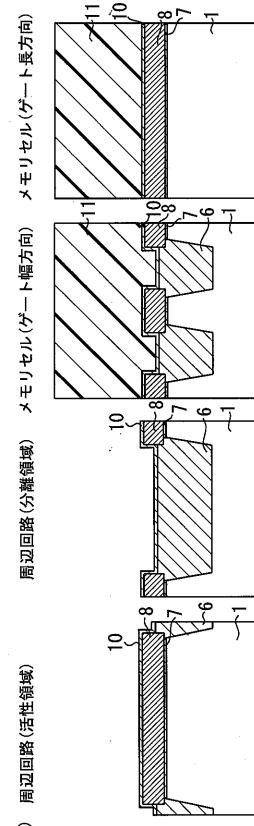

図17～図24は、従来の不揮発性半導体記憶装置の製造方法を説明するための工程断面図である。

先ず、図17(a)に示すように、シリコン基板1上に熱酸化膜2を形成し、熱酸化膜2上にシリコン窒化膜3を形成する。さらに、シリコン窒化膜3上に、素子分離領域に対応する部分が開口するレジストパターン4を写真製版により形成する。10

## 【0005】

次に、レジストパターン4をマスクとして、シリコン窒化膜3及び熱酸化膜2を順次ドライエッチングする。その後、レジストパターン4を除去する。続いて、パターニングされたシリコン窒化膜3をマスクとして、シリコン基板1をエッチングする。これにより、図17(b)に示すように、シリコン基板1内にトレンチ5が形成される。

## 【0006】

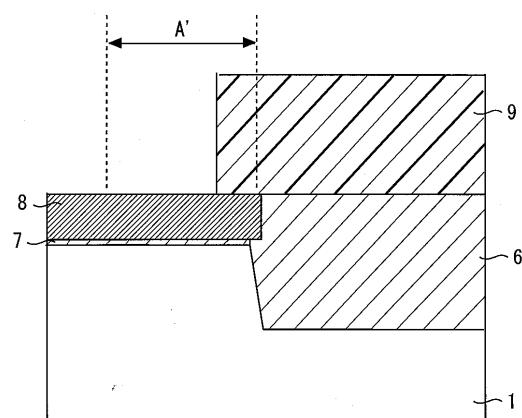

次に、トレンチ5内壁に熱酸化膜(図示せず)を形成し、その後、図18(a)に示すように、基板1全面に分離酸化膜となるシリコン酸化膜6を形成する。次に、図18(b)に示すように、シリコン窒化膜3をストップ膜としてシリコン酸化膜6をCMP法により平坦化する。20

## 【0007】

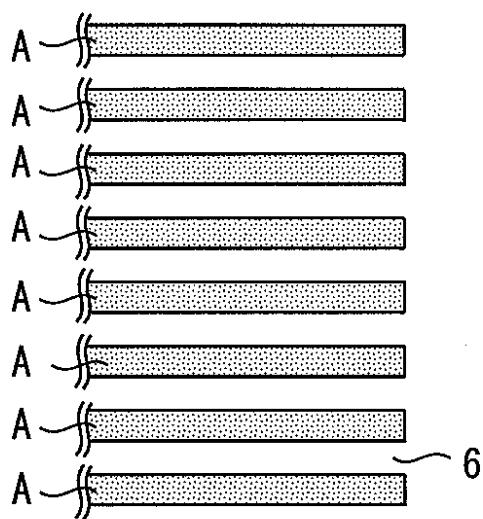

次に、シリコン窒化膜3を熱リン酸により除去すると、図19(a)に示す構造が得られる。さらに、熱酸化膜2をフッ酸により除去すると、図19(b)に示す構造が得られる。図25は、メモリセルアレイにおける活性領域を示す上面図である。図25に示すように、短冊状の活性領域Aがその短手方向に複数並んで形成されている。この活性領域Aを分離するように、素子分離としての分離酸化膜6が形成されている。

## 【0008】

次に、図20(a)に示すように、基板1表面にトンネル酸化膜となる熱酸化膜7を形成し、基板1全面にメモリセルのフローティングゲート電極となるポリシリコン膜8を形成する。30

## 【0009】

次に、図20(b)に示すように、分離酸化膜6をストップ膜としてポリシリコン膜8をCMP法により平坦化する。これにより、シリコン酸化膜6の表面と、ポリシリコン膜8の表面が同じ高さになる。ここで、ポリシリコン膜8は、分離酸化膜6に対して自己整合的に位置決めされる。

## 【0010】

次に、図21(a)に示すように、分離酸化膜6をフッ酸により所定の膜厚だけ選択的にエッチングする。これにより、ポリシリコン膜8の側面上部が露出し、コントロールゲート電極に対向するフローティングゲート電極8の表面積を増大させることができ、メモリセルのカップリング比を向上させることができる。40

その後、図21(b)に示すように、基板1全面にONO膜10を形成する。

## 【0011】

次に、図22(a)に示すように、メモリセル領域を覆うレジストパターン11を写真製版により形成する。

そして、図22(b)に示すように、レジストパターン11をマスクとして、周辺回路のONO膜10及びポリシリコン膜8を順次ドライエッチングする。さらに、周辺回路の熱酸化膜7をフッ酸により除去する。その後、レジストパターン11を除去すると、図23(a)に示す構造が得られる。ここで、図23(a)に示すように、周辺回路において、分離酸化膜6表面が基板1表面よりも落ち込むことにより段差Bが生じ、この段差Bに50

起因して後述する問題が発生する。

【0012】

次に、図23(b)に示すように、周辺回路において基板1表面にゲート酸化膜となる熱酸化膜12を形成する。そして、基板1全面に、メモリセルのコントロールゲート電極及び周辺回路のゲート電極となる導電膜としてのポリシリコン膜13及びWSi膜14を順次形成する。WSi膜14上にシリコン窒化膜15を形成し、シリコン窒化膜15上に、コントロールゲート電極部分及びゲート電極部分を覆うレジストパターン16を写真製版により形成する。

【0013】

次に、図24に示すように、レジストパターン16をマスクとしてシリコン窒化膜15をドライエッチングする。その後、レジストパターン16を除去する。続いて、パターニングされたシリコン窒化膜15をマスクとしてWSi膜14とポリシリコン膜13を順次ドライエッチングする。このとき、上述したように周辺回路の素子分離6上には段差Bが存在するため、この段差Bの部分にエッチング残渣(ポリシリコン残渣)13aが生じる可能性が高い。

【0014】

【特許文献1】特開2003-23115号公報

【発明の開示】

【発明が解決しようとする課題】

【0015】

上記製造方法では、メモリセルのカップリング比を向上させるために分離酸化膜6をエッチングする際、周辺回路における分離酸化膜6もエッチングしていた。このため、周辺回路におけるONO膜10及び熱酸化膜7を除去する際に、分離酸化膜6がさらにエッチングされ、分離酸化膜6表面が基板1表面よりも大きく落ち込んでしまい、段差Bが生じてしまうという問題があった。このため、その後のゲート電極のパターニングを行う際に、この段差Bにエッチング残渣13aが生じてしまうという問題があった。この残渣13aを介して本来絶縁すべき回路要素が導通してしまい、回路不良が発生してしまう問題があった。

【0016】

本発明は、上述のような課題を解決するためになされたもので、周辺回路の分離酸化膜上にエッチング残渣を発生させることなく、高いカップリング比を有するメモリセルを有する不揮発性半導体記憶装置を製造することを目的とする。

【課題を解決するための手段】

【0017】

本発明に係る不揮発性半導体記憶装置の製造方法は、メモリセルと、該メモリセルに隣接する周辺回路とを有する不揮発性半導体記憶装置の製造方法であって、

基板の活性領域を分離する素子分離であって、その上面が該基板の表面よりも高い素子分離を該基板に形成する工程と、

前記基板上にシリコン酸化膜を形成する工程と、

前記素子分離の間の前記シリコン酸化膜上にポリシリコン膜を自己整合的に形成する工程と、

前記周辺回路を覆う第1レジストパターンを形成した後、前記メモリセルにおける前記素子分離を所定の膜厚だけエッチングする工程と、

前記基板全面に多層絶縁膜を形成する工程と、

前記メモリセルを覆う第2レジストパターンを形成した後、前記周辺回路における前記多層絶縁膜と前記ポリシリコン膜と前記シリコン酸化膜とを除去する工程と、

前記周辺回路の前記基板上にゲート絶縁膜を形成する工程と、

前記基板の全面に導電膜を形成する工程と、

前記周辺回路及び前記メモリセルにおける前記導電膜をパターニングする工程と、

前記メモリセルにおいて、パターニングされた前記導電膜をマスクとして前記多層絶縁

10

20

30

40

50

膜及び前記ポリシリコン膜をパターニングする工程とを含むことを特徴とするものである。

【発明の効果】

【0019】

本発明は、以上説明したように、第1レジストパターンをマスクとしてメモリセルにおける素子分離のみをエッティングすることにより、周辺回路における多層絶縁膜とポリシリコン膜とシリコン酸化膜とを除去する際に、周辺回路の素子分離上に基板表面に対する段差の発生を抑制することができ、該段差にエッティング残渣が発生することを防止することができる。

【発明を実施するための最良の形態】

10

【0020】

以下、図面を参照して本発明の実施の形態について説明する。図中、同一または相当する部分には同一の符号を付してその説明を簡略化ないし省略することがある。

【0021】

以下、図を参照して、本発明の実施の形態による不揮発性半導体記憶装置の製造方法を説明する。

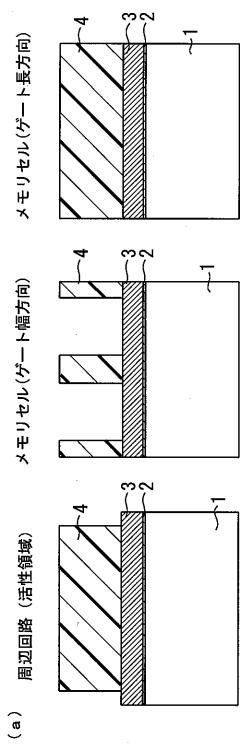

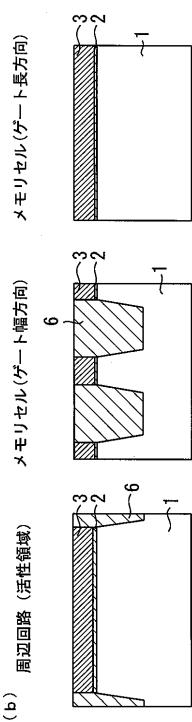

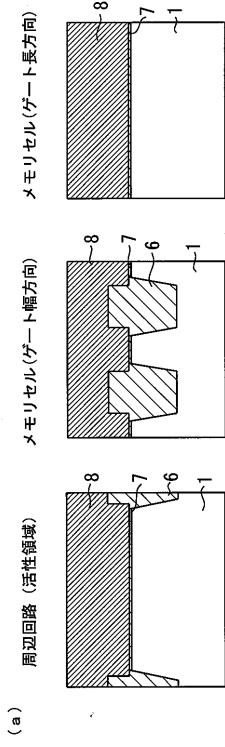

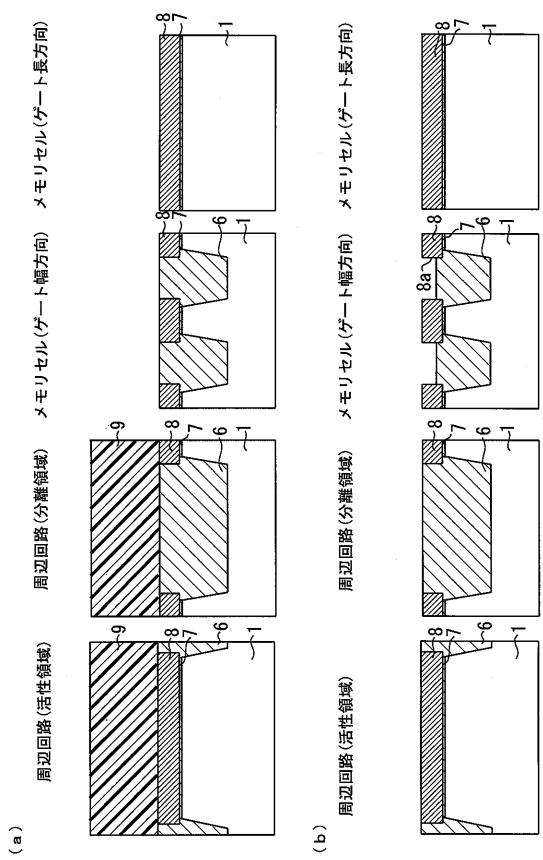

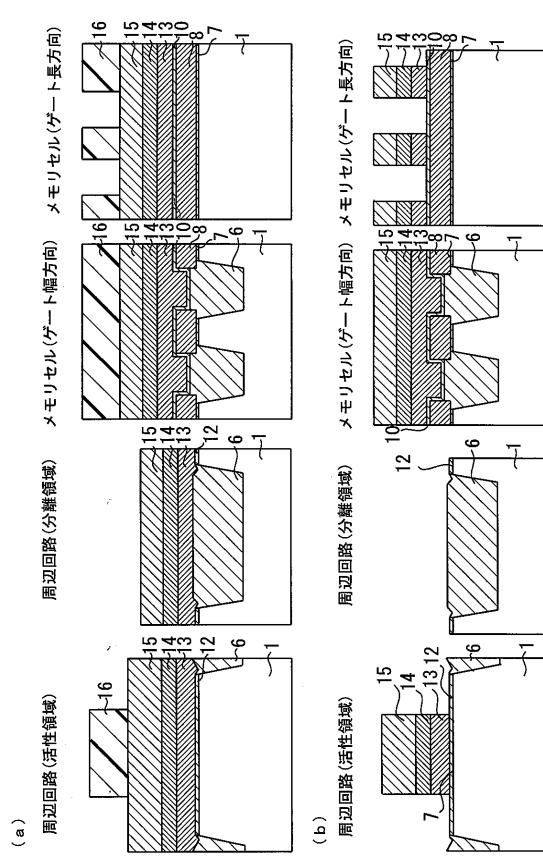

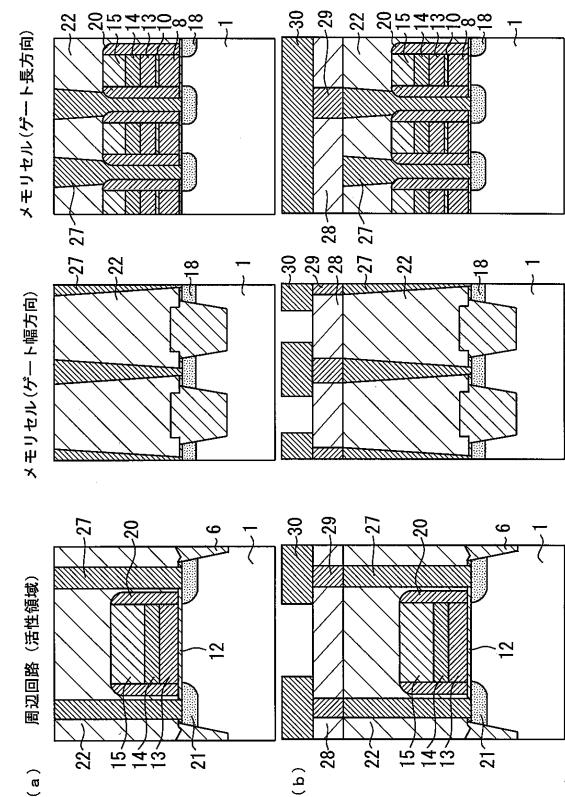

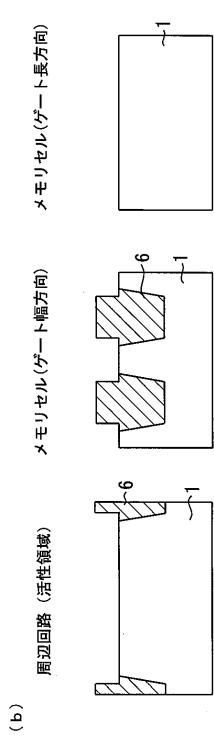

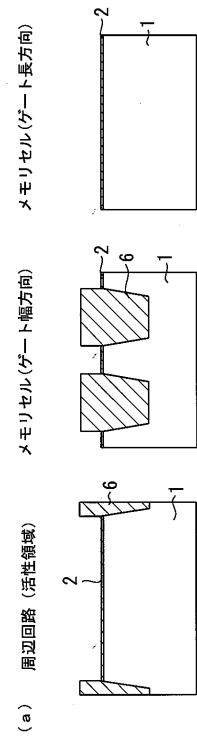

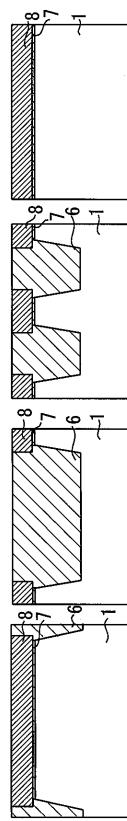

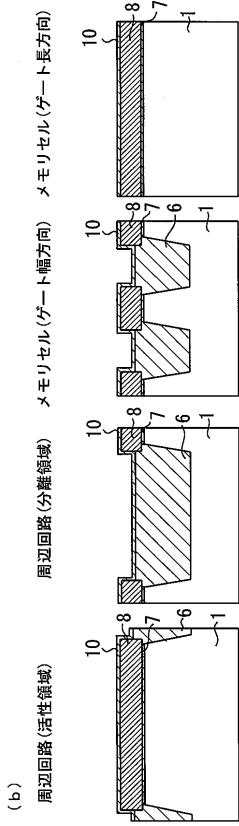

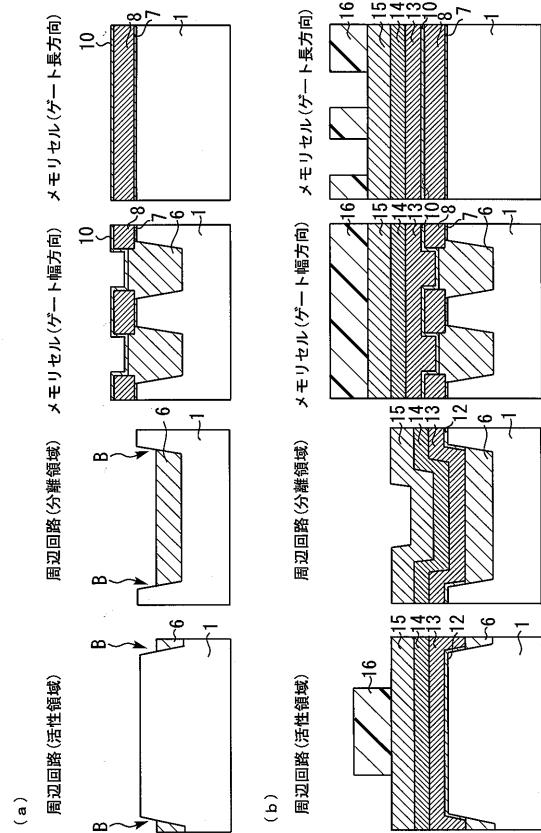

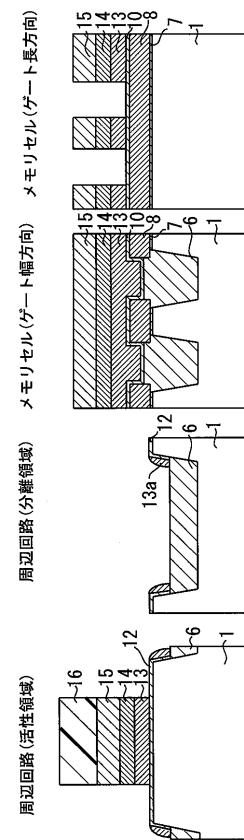

図1～図11は、本実施の形態による不揮発性半導体記憶装置の製造方法を説明するための工程断面図である。

各図において、周辺回路の活性領域の断面と、メモリセルのゲート幅方向及びゲート長方向の断面を示している。また、必要に応じて、周辺回路の素子分離領域の断面を示している。

20

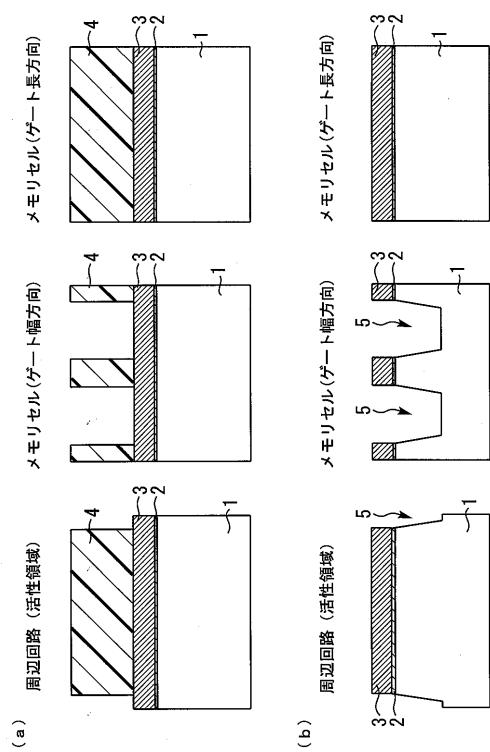

【0022】

先ず、図1(a)に示すように、基板(例えばシリコン基板)1上にシリコン酸化膜(以下「熱酸化膜」という。)2を熱酸化法により、例えば10nm程度の膜厚で形成する。そして、熱酸化膜2上にシリコン窒化膜3をCVD法により、例えば100nm程度の膜厚で形成する。さらに、シリコン窒化膜3上に、活性領域に対応する部分を覆い、かつ、素子分離領域に対応する部分が開口するレジストパターン4を写真製版により形成する。

【0023】

次に、レジストパターン4をマスクとして、シリコン窒化膜3及び熱酸化膜2を順次ドライエッティングする。その後、レジストパターン4を除去する。続いて、パターニングされたシリコン窒化膜3をマスクとして、基板1をエッティングする。これにより、図1(b)に示すように、基板1内に200nm～300nm程度の深さのトレンチ5が、シリコン窒化膜3の開口に連通して形成される。

30

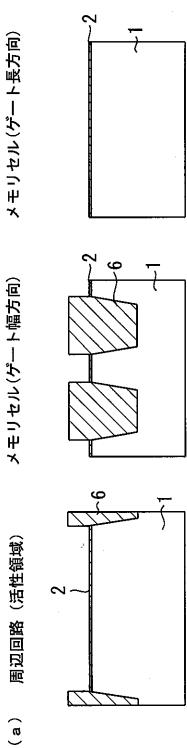

【0024】

次に、図示しないが、トレンチ5の内壁に熱酸化膜を形成する。その後、図2(a)に示すように、基板1全面に分離酸化膜となるシリコン酸化膜6を、例えば500nm程度の膜厚で形成する。これにより、トレンチ5及びシリコン窒化膜3の開口がシリコン酸化膜6で埋め込まれる。

次に、図2(b)に示すように、シリコン窒化膜3をストップ膜としてシリコン酸化膜6をCMP法により平坦化する。これにより、シリコン窒化膜3の表面と、シリコン酸化膜6の表面とが同じ高さになる。

40

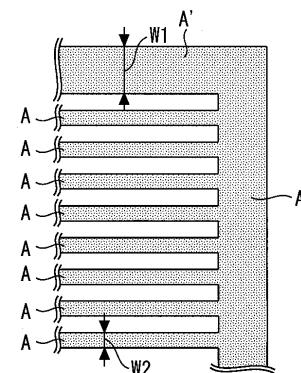

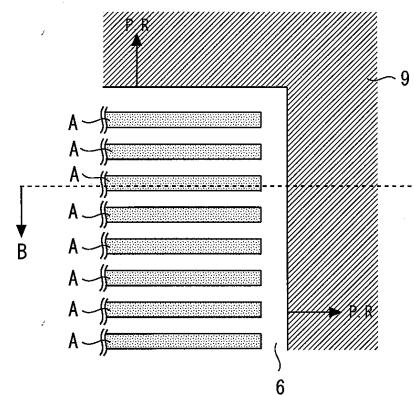

次に、シリコン窒化膜3を熱リン酸により除去すると、図3(a)に示す構造が得られる。さらに、熱酸化膜2をフッ酸により除去すると、図3(b)に示す構造が得られる。これにより、上面が基板1表面よりも高い分離酸化膜6、すなわち基板1表面から上面が突き出た分離酸化膜6が形成される。図12は、メモリセルアレイにおける活性領域を示す上面図である。図12に示すように、短冊状の活性領域Aがその短手方向に複数並んで形成されており、活性領域Aを分離するように素子分離としての分離酸化膜6が形成されている。図25に示す従来のメモリセルアレイと異なり、本実施の形態ではメモリセルアレイの端部に活性領域A'が形成されたことにより、メモリセルアレイが活性領域A'に

50

より取り囲まれている。すなわち、メモリセルと周回路との境界部分に活性領域 A' が形成されている。活性領域 A' の周囲には周回路との素子分離が形成されている。このメモリセルアレイ端部に形成された活性領域 A' は、短冊状の活性領域 A の端部を相互に接続する。活性領域 A' の幅 W1 は、少なくとも短冊状の活性領域 A の幅 W2 よりも広い幅にする。なお、活性領域 A の端部には、ダミーゲート等を形成することができる。

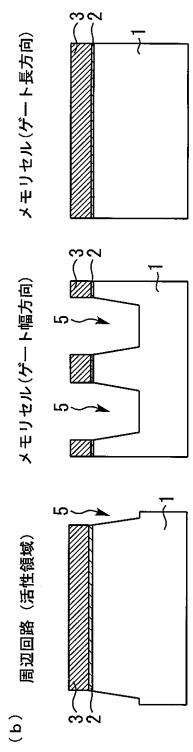

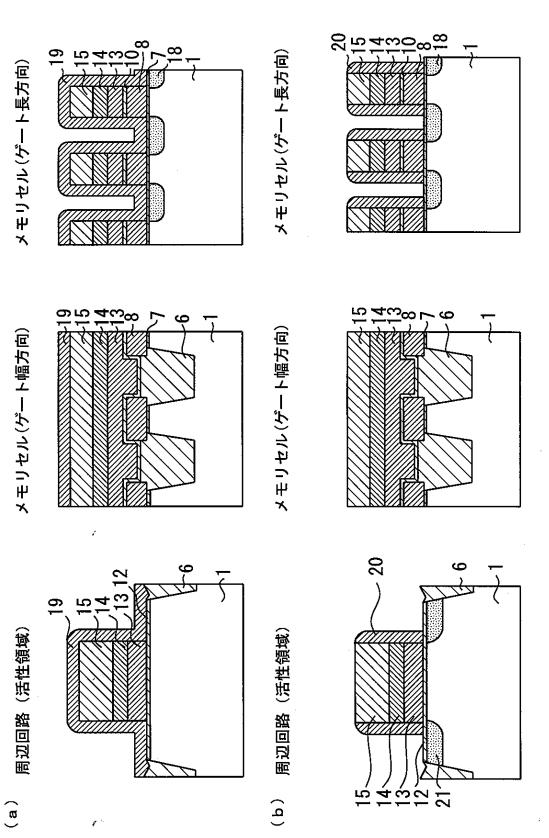

#### 【0025】

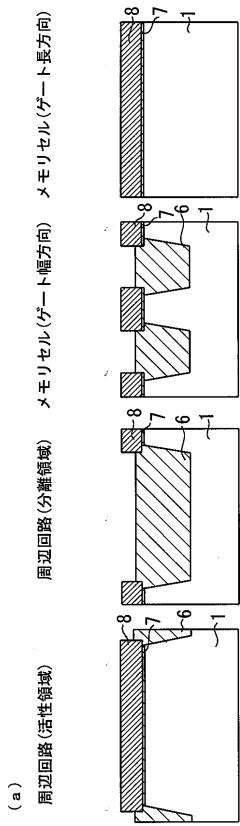

次に、図 4 (a) に示すように、基板 1 表面にトンネル酸化膜となるシリコン酸化膜 7 を熱酸化法により形成し、その後、メモリセルのフローティングゲート電極となるポリシリコン膜 8 を、例えば、150 nm 程度の膜厚で形成する。これにより、分離酸化膜 6 がポリシリコン膜 8 により覆われる。

10

次に、図 4 (b) に示すように、分離酸化膜 6 をストップ膜としてポリシリコン膜 8 を CMP 法により平坦化する。これにより、分離酸化膜 6 の表面と、ポリシリコン膜 8 の表面とが同じ高さになる。ここで、ポリシリコン膜 8 の位置は、分離酸化膜 6 に対して自己整合的に決められる。よって、フローティングゲート電極 8 が分離酸化膜 6 に対して自己整合的に形成されたことになり、写真製版を用いる場合に必要な分離酸化膜とフローティングゲート電極との高精度な位置合わせが不要になる。

#### 【0026】

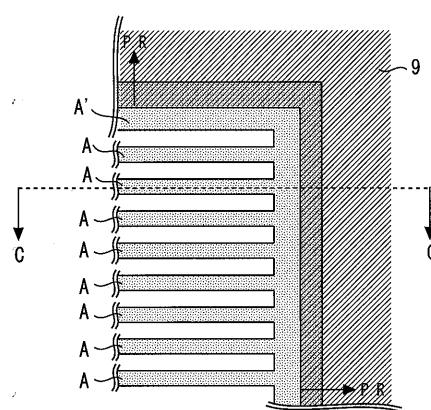

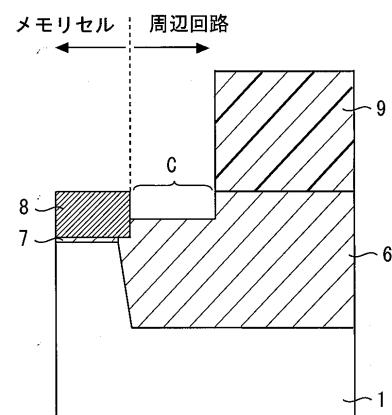

次に、図 5 (a) に示すように、周回路を覆うレジストパターン 9 を形成する。ここで、メモリセルアレイ端部に太い活性領域 A' を形成することは上述したが（図 12 参照）、本工程では、図 13 及び図 14 に示すように、レジストパターン 9 端部が活性領域 A' 上に位置するように、レジストパターン 9 を配置する。これにより、メモリセルとの境界近傍の周回路における分離酸化膜 6 表面がレジストパターン 9 に覆われる。活性領域 A' の幅 W1 は、レジストパターン 9 の重ね合わせ余裕や寸法バラツキを考慮した幅に設定し、必ずレジストパターン 9 端部が活性領域 A' を踏み外さないようにする。

20

#### 【0027】

次に、メモリセルにおける分離酸化膜 6 をフッ酸により所定の膜厚だけエッチングする。その後、レジストパターン 9 を除去すると、図 5 (b) に示す構造が得られる。分離酸化膜 6 のエッチングによりポリシリコン膜 8 の側面 8a の一部が露出するため、コントロールゲート電極（後述）に対向するフローティングゲート電極 8 の表面積が増大し、メモリセルのカップリング比が向上する。このとき、周回路はレジストパターン 9 によりマスクされているため、周回路における分離酸化膜 6 はエッチングされない。

30

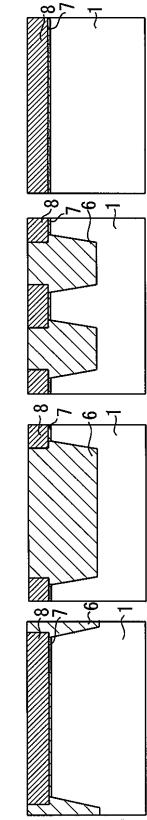

#### 【0028】

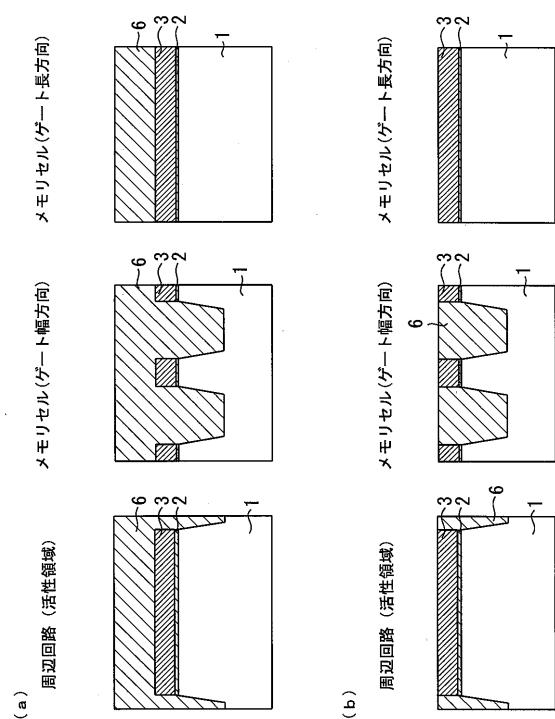

次に、図 6 (a) に示すように、基板 1 全面に多層絶縁膜としての ONO 膜 10 を形成する。ONO 膜 10 は、シリコン酸化膜、シリコン窒化膜、シリコン酸化膜を積層した 3 層の絶縁膜である。なお、ONO 膜 10 に代えて、シリコン酸化膜とシリコン窒化膜とを積層した 2 層の絶縁膜（ON 膜又はNO 膜）や、シリコン酸化膜とシリコン窒化膜とを交互に積層した 4 層の絶縁膜（ONON 膜又はNONO 膜）を形成することができる。

そして、メモリセル領域を覆い、かつ、周回路領域に対応する部分が開口するレジストパターン 11 を写真製版により形成する。

40

#### 【0029】

次に、図 6 (b) に示すように、周回路領域の ONO 膜 9 及びポリシリコン膜 8 を順次ドライエッチングする。続いて、周回路領域の熱酸化膜 7 をフッ酸により除去する。ここで、メモリセルにおける分離酸化膜 6 をエッチングする際、周回路の分離酸化膜 6 はレジストパターン 9 によりマスクされておりエッチングされていない。よって、この熱酸化膜 7 を除去する際、従来のように分離酸化膜 6 表面が基板 1 表面よりも落ち込まない。すなわち、通常のエッチング処理を行うことにより、図 22 (a) に示すような従来周回路に生じていた段差 B が、本発明では生じない。換言すれば、周回路の分離酸化膜 6 の上面が、基板 1 の表面と同等の高さであるか若しくは該表面よりも高い。

その後、レジストパターン 11 を除去する。

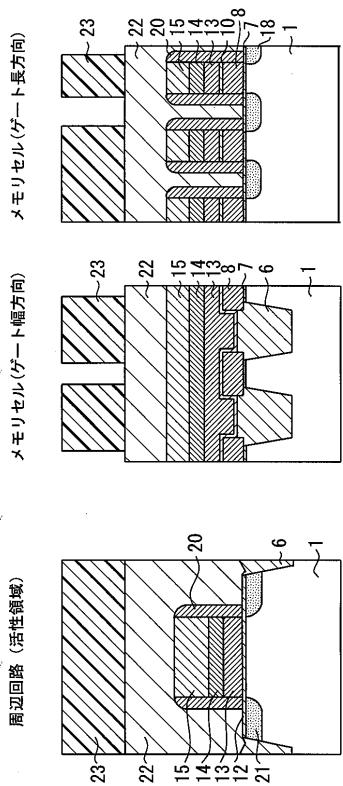

#### 【0030】

50

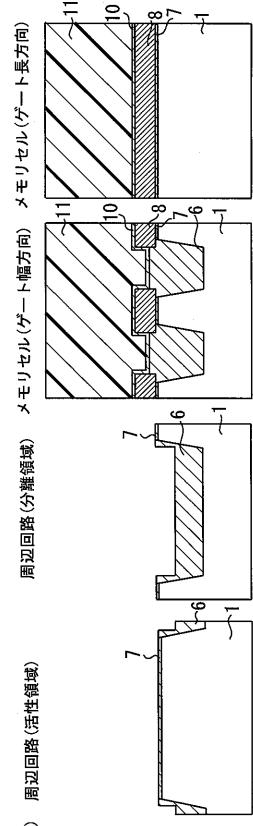

次に、図7(a)に示すように、周辺回路にゲート絶縁膜となるシリコン酸化膜12を熱酸化法により、例えば15nm程度の膜厚で形成する。続いて、基板1全面に、メモリセルのコントロールゲート電極及び周辺回路のゲート電極となる導電膜としてポリシリコン膜13とタングステンシリサイド膜(以下「WSi膜」という。)14を積層する。さらに、WSi膜14上にシリコン窒化膜15を形成し、その上にメモリセルのコントロールゲート電極部分と、周辺回路のゲート電極部分とを覆うレジストパターン16を写真製版により形成する。

#### 【0031】

次に、図7(b)に示すように、レジストパターン16をマスクとしてシリコン窒化膜15をドライエッチングする。その後、レジストパターン16を除去する。続いて、パターニングされたシリコン窒化膜15をマスクとしてWSi膜14とポリシリコン膜13を順次ドライエッチングする。これにより、メモリセルにコントロールゲート電極(13, 14)が形成され、周辺回路にゲート電極(13, 14)が形成される。このとき、上述したように周辺回路の分離酸化膜6上には段差が存在しないため、エッチング残渣の発生を抑制することができる。

#### 【0032】

次に、周辺回路を覆うレジストパターンを写真製版により形成する。そして、パターニングされたシリコン窒化膜15、WSi膜14及びポリシリコン膜13をマスクとしてONO膜9及びポリシリコン膜8を順次ドライエッチングする。その後、イオン注入法によりメモリセルの基板1上層にソース/ドレイン領域18を形成する。続いて、レジストパターンを除去する。次に、ゲート側壁を熱酸化した後、基板全面にシリコン窒化膜19を形成すると、図8(a)に示す構造が得られる。

#### 【0033】

次に、シリコン窒化膜19をエッチバックすることにより、ゲート電極側壁を覆うサイドウォール20が自己整合的に形成される。そして、メモリセルを覆うレジストパターンを写真製版により形成した後、イオン注入法により周辺回路の基板1上層にソース/ドレイン領域21を形成する。これにより、図8(b)に示すような構造が得られる。

#### 【0034】

次に、図9に示すように、基板1全面に層間絶縁膜となるBPSG膜22を形成する。そして、BPSG膜22上にコンタクトホール形成部分が開口するレジストパターン23を写真製版により形成する。さらに、図10(a)に示すように、レジストパターン23をマスクとしてBPSG膜22をドライエッチングすることにより、ソース/ドレイン領域19に達するコンタクトホール24が形成される。その後、レジストパターン23を除去する。同様の手法で、図10(b)に示すように、ソース/ドレイン領域18, 21に達するコンタクトホール25, 26を形成する。なお、図1-図9におけるメモリセル(ゲート幅方向)断面はゲート電極部分の断面を示したが、図10-図11におけるメモリセル(ゲート幅方向)断面はコンタクト部分の断面を示す。

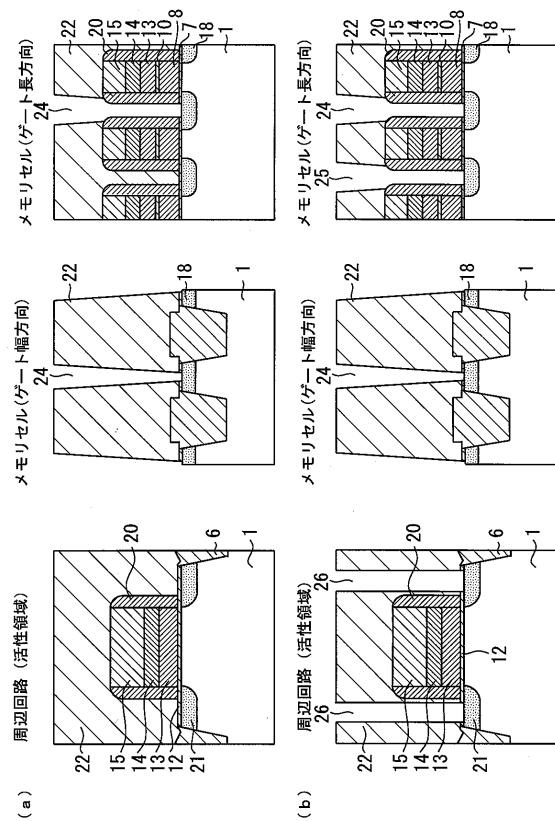

#### 【0035】

次に、基板1全面にタングステン膜を堆積し、BPSG膜22をストップ膜としてCMP法による平坦化又はエッチバックを行う。これにより、図11(a)に示すように、コンタクトホール24, 25, 26内にタングステンプラグ27が形成される。

次に、BPSG膜22及びプラグ27上に層間絶縁膜としてのBPSG膜28を形成する。そして、BPSG膜28上にヴィアホール形成部分が開口するレジストパターンを写真製版により形成する。さらに、このレジストパターンをマスクとしてBPSG膜28をドライエッチングすることにより、所望のプラグ27に達するヴィアホールが形成される。その後、レジストパターンを除去する。続いて、基板1全面にタングステン膜を堆積し、BPSG膜28をストップ膜としてCMP法による平坦化又はエッチバックを行うことにより、ヴィアホール内にタングステンプラグ29が形成される。最後に、タングステンプラグ29に接続されたアルミニウム配線30を形成する。これにより、図11(b)に示すような構造が得られる。

10

20

30

40

50

## 【0036】

以上説明したように、本実施の形態では、レジストパターン9をマスクとしてメモリセルにおける分離酸化膜6をエッチングすることにより、その後に周辺回路におけるONO膜10とポリシリコン膜8と熱酸化膜7を除去する際に、周辺回路の分離酸化膜6上に基板1表面に対する段差の発生を抑制することができる。よって、周辺回路の分離酸化膜6上にポリシリコン膜のエッチング残渣が発生することを防止でき、不揮発性半導体記憶装置の信頼性を向上させることができる。

## 【0037】

次に、上記実施の形態に対する比較例について説明する。

図15は、本比較例において、メモリセルの活性領域と、周辺回路を覆うレジストパターンとの位置関係を示す上面図である。 10

上記実施の形態では、図13及び図14に示すように、メモリセルアレイ端部を取り囲む活性領域A'上にレジストパターン9端部を配置した。これにより、メモリセルと周辺回路の境界部分の分離酸化膜6がエッチングされず、段差の発生を防止することができる。すなわち、上記実施の形態による方法を用いて製造された不揮発性半導体記憶装置において、メモリセルと周辺回路の境界部分の分離酸化膜6上面が、基板1の表面と同等の高さであるか若しくは該表面よりも高い。

これに対して、本比較例では、図15に示すように、短冊状活性領域Aの端部を接続する活性領域A'を形成せず、メモリセルと周辺回路の境界部分の分離酸化膜6上にレジストパターン9端部を配置した。この場合、図16に示すように、レジストパターン9で覆われていない部分の分離酸化膜6がエッチングされてしまい、その結果として段差Cが生じる。この段差Cに起因して、その後にメモリセルをマスクして行う周辺回路のONO膜9、ポリシリコン膜8、熱酸化膜7の除去によって、メモリセルと周辺回路の境界部分において従来周辺回路で発生したような分離酸化膜6上の段差が発生してしまう。 20

本実施の形態では、活性領域A'上にレジストパターン9端部を配置することにより、かかる段差Cの発生を防止することができる。このため、メモリセルと周辺回路の境界部分において分離酸化膜6上の段差の発生を防止することができ、さらにエッチング残渣の発生を防止することができる。

## 【図面の簡単な説明】

## 【0038】

30

【図1】本発明の実施の形態による不揮発性半導体記憶装置の製造方法を説明するための断面図である（その1）。

【図2】本発明の実施の形態による不揮発性半導体記憶装置の製造方法を説明するための断面図である（その2）。

【図3】本発明の実施の形態による不揮発性半導体記憶装置の製造方法を説明するための断面図である（その3）。

【図4】本発明の実施の形態による不揮発性半導体記憶装置の製造方法を説明するための断面図である（その4）。

【図5】本発明の実施の形態による不揮発性半導体記憶装置の製造方法を説明するための断面図である（その5）。 40

【図6】本発明の実施の形態による不揮発性半導体記憶装置の製造方法を説明するための断面図である（その6）。

【図7】本発明の実施の形態による不揮発性半導体記憶装置の製造方法を説明するための断面図である（その7）。

【図8】本発明の実施の形態による不揮発性半導体記憶装置の製造方法を説明するための断面図である（その8）。

【図9】本発明の実施の形態による不揮発性半導体記憶装置の製造方法を説明するための断面図である（その9）。

【図10】本発明の実施の形態による不揮発性半導体記憶装置の製造方法を説明するための断面図である（その10）。 50

【図11】本発明の実施の形態による不揮発性半導体記憶装置の製造方法を説明するための断面図である（その11）。

【図12】本発明の実施の形態において、メモリセルアレイにおける活性領域を示す上面図である。

【図13】本発明の実施の形態において、メモリセルの活性領域と、周辺回路を覆うレジストパターンとの位置関係を示す上面図である。

【図14】図13におけるC-C断面図である。

【図15】本発明の実施の形態に対する比較例において、メモリセルの活性領域と、周辺回路を覆うレジストパターンとの位置関係を示す上面図である。

【図16】本発明の実施の形態に対する比較例における問題点を示す断面図である。

10

【図17】従来の不揮発性半導体記憶装置の製造方法を説明するための断面図である（その1）。

【図18】従来の不揮発性半導体記憶装置の製造方法を説明するための断面図である（その2）。

【図19】従来の不揮発性半導体記憶装置の製造方法を説明するための断面図である（その3）。

【図20】従来の不揮発性半導体記憶装置の製造方法を説明するための断面図である（その4）。

【図21】従来の不揮発性半導体記憶装置の製造方法を説明するための断面図である（その5）。

20

【図22】従来の不揮発性半導体記憶装置の製造方法を説明するための断面図である（その6）。

【図23】従来の不揮発性半導体記憶装置の製造方法を説明するための断面図である（その7）。

【図24】従来の不揮発性半導体記憶装置の製造方法を説明するための断面図である（その8）。

【図25】メモリセルアレイにおける活性領域を示す上面図である。

【符号の説明】

【0039】

1 基板（シリコン基板）、2 熱酸化膜、3 シリコン窒化膜、4 レジストパターン、5 トレンチ、6 分離酸化膜（シリコン酸化膜）、7 トンネル酸化膜（シリコン酸化膜）、8 フロー・ティングゲート電極（ポリシリコン膜）、9 レジストパターン、10 ONO膜、11 レジストパターン、12 ゲート絶縁膜（シリコン酸化膜）、13 ポリシリコン膜、14 WSi膜、15 シリコン窒化膜、16 レジストパターン、19 シリコン窒化膜、20 サイドウォール、21 ソース／ドレイン領域、22 層間絶縁膜（BPSG膜）、23 レジストパターン、24, 25, 26 コンタクトホール、27 プラグ、28 層間絶縁膜（BPSG膜）。

30

【図 1】

【図 3】

【図 2】

【図 4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図14】

【図16】

【図15】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

---

フロントページの続き

(56)参考文献 特開2003-078047(JP,A)

特開2000-150834(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8247

H01L 27/10

H01L 27/115

H01L 29/788

H01L 29/792