(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6276721号

(P6276721)

(45) 発行日 平成30年2月7日(2018.2.7)

(24) 登録日 平成30年1月19日(2018.1.19)

|              |                    |

|--------------|--------------------|

| (51) Int.Cl. | F 1                |

| H 01 L 25/07 | (2006.01)          |

| H 01 L 25/18 | (2006.01)          |

| H 01 L 23/48 | (2006.01)          |

| H 01 L 21/60 | (2006.01)          |

|              | HO 1 L 25/04 C     |

|              | HO 1 L 23/48 G     |

|              | HO 1 L 21/60 321 E |

請求項の数 14 (全 26 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2015-22257 (P2015-22257)    |

| (22) 出願日  | 平成27年2月6日 (2015.2.6)          |

| (65) 公開番号 | 特開2016-146398 (P2016-146398A) |

| (43) 公開日  | 平成28年8月12日 (2016.8.12)        |

| 審査請求日     | 平成28年12月22日 (2016.12.22)      |

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 509186579<br>日立オートモティブシステムズ株式会社<br>茨城県ひたちなか市高場2520番地 |

| (74) 代理人  | 110002365<br>特許業務法人サンネクスト国際特許事務所                     |

| (72) 発明者  | 山下 志郎<br>東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内                |

| (72) 発明者  | 高木 佑輔<br>茨城県ひたちなか市高場2520番地 日立オートモティブシステムズ株式会社内       |

| (72) 発明者  | 志村 隆弘<br>茨城県ひたちなか市高場2520番地 日立オートモティブシステムズ株式会社内       |

最終頁に続く

(54) 【発明の名称】パワーモジュール

## (57) 【特許請求の範囲】

## 【請求項 1】

ベース板と、

四つの辺を有する第一の半導体チップと、

前記第一の半導体チップの第1の辺に隣接して配置された一辺を含む四つの辺を有し、前記ベース板にはんだ付けされた第二の半導体チップと、

前記第一の半導体チップの第2の辺に隣接して配置された一辺を含む四つの辺を有し、前記ベース板にはんだ付けされた第三の半導体チップとを備え、

前記第一の半導体チップの第3の辺または第4の辺の少なくとも一方は、前記ベース板の側端に隣接して配置され、

前記第一の半導体チップの前記第1の辺から前記第二の半導体チップの前記一辺までの距離の1/2の距離と、前記第一の半導体チップの前記第2の辺から前記第三の半導体チップの前記一辺までの距離の1/2の距離と、前記ベース板の前記側端に隣接して配置された前記第一の半導体チップの前記第3の辺または前記第4の辺から前記ベース板の前記側端までの距離とのうち、最も短い距離となる箇所の辺に形成された前記第一の半導体チップのはんだフィレットの長さが最も短く形成されている、パワーモジュール。

## 【請求項 2】

請求項1に記載のパワーモジュールにおいて、

前記第一の半導体チップの前記第1の辺から前記第二の半導体チップの前記一辺までの距離の1/2の距離および前記第一の半導体チップの前記第2の辺から前記第三の半導体

チップの前記一辺までの距離の 1 / 2 の距離が、前記ベース板の前記側端に隣接して配置された前記第一の半導体チップの前記第 3 の辺または前記第 4 の辺から前記ベース板の前記側端までの距離より短く、

前記第一の半導体チップの前記第 1 の辺および前記第 2 の辺に形成された前記はんだフィレットの長さが、それぞれ、前記ベース板の前記側端に隣接する前記第一の半導体チップの前記第 3 の辺または前記第 4 の辺に形成された前記はんだフィレットの長さよりも短く形成されている、パワーモジュール。

#### 【請求項 3】

請求項 2 に記載のパワーモジュールにおいて、

前記第一の半導体チップの前記第 1 の辺と前記第 2 の辺とは、相互に隣接する辺であり、前記第一の半導体チップの前記第 3 の辺および前記第 4 の辺は、それぞれ、前記ベース板の相互に隣接する第 1 の側端および第 2 の側端に隣接して配置されており、前記第一の半導体チップの前記第 1 の辺および前記第 2 の辺に形成された前記はんだフィレットの長さが、それぞれ、前記第一の半導体チップの前記第 3 の辺および前記第 4 の辺に形成された前記はんだフィレットの長さのいずれよりも短く形成されている、パワーモジュール。 10

#### 【請求項 4】

請求項 2 に記載のパワーモジュールにおいて、

前記第一の半導体チップの前記第 1 の辺と前記第 2 の辺とは、相互に対向する一対の辺であり、前記第一の半導体チップの前記第 3 の辺または前記第 4 の辺の少なくとも一方が、前記ベース板の前記側端に隣接して配置されており、前記第一の半導体チップの前記第 1 の辺および前記第 2 の辺に形成された前記はんだフィレットの長さが、前記ベース板の前記側端に隣接して配置された前記第一の半導体チップの前記第 3 の辺または前記第 4 の辺に形成された前記はんだフィレットの長さよりも短く形成されている、パワーモジュール。 20

#### 【請求項 5】

請求項 4 に記載のパワーモジュールにおいて、

前記第一の半導体チップの前記第 3 の辺および前記第 4 の辺は、それぞれ、前記ベース板の前記側端に隣接して配置されており、

前記第一の半導体チップの前記第 1 の辺および前記第 2 の辺に形成された前記はんだフィレットの長さが、それぞれ、前記第一の半導体チップの前記第 3 の辺および前記第 4 の辺に形成された前記はんだフィレットの長さのいずれよりも短く形成されている、パワーモジュール。 30

#### 【請求項 6】

請求項 4 に記載のパワーモジュールにおいて、

さらに、前記第一の半導体チップの前記第 3 の辺に隣接して配置された第四の半導体チップを備え、

前記第一の半導体チップの前記第 4 の辺が前記ベース板の前記側端に隣接して配置され、

前記第一の半導体チップの前記第 1 の辺および前記第 2 の辺に形成された前記はんだフィレットの長さが、それぞれ、前記第一の半導体チップの前記第 3 の辺および前記第 4 の辺に形成された前記はんだフィレットの長さのいずれよりも短く形成されている、パワーモジュール。 40

#### 【請求項 7】

請求項 1 に記載のパワーモジュールにおいて、

前記第一の半導体チップの前記第 1 の辺と前記第 2 の辺とは、相互に対向する一対の辺であり、

前記第一の半導体チップの前記第 3 の辺と前記第 4 の辺とは、相互に対向する他の一対の辺であり、

前記第一の半導体チップの前記第 3 の辺および前記第 4 の辺の少なくとも一方は、前記ベース板の前記側端に隣接して配置され、

10

20

30

40

50

前記第一の半導体チップの前記第1の辺に形成された前記はんだフィレットの長さが、前記第一の半導体チップの前記第2の辺、および前記ベース板の前記側端に隣接して配置された前記第3の辺または前記第4の辺に形成された前記はんだフィレットの長さのいずれよりも短く形成されている、パワーモジュール。

#### 【請求項8】

請求項1に記載のパワーモジュールにおいて、

前記第一の半導体チップの前記第1の辺と前記第2の辺とは、相互に対向する一対の辺であり、

前記第一の半導体チップの前記第3の辺と前記第4の辺とは、相互に対向する他の一対の辺であり、

前記第一の半導体チップの前記第3の辺または前記第4の辺の少なくとも一方は、前記ベース板の側端に隣接して配置され、

前記ベース板の前記側端に隣接して配置された前記第一の半導体チップの前記第3の辺または前記第4の辺から前記ベース板の前記側端までの距離は、前記第一の半導体チップの前記第1の辺から前記第二の半導体チップの前記一辺までの1/2の距離および前記第一の半導体チップの前記第2の辺から前記第三の半導体チップの前記一辺までの1/2の距離のいずれよりも短く、

前記ベース板の前記側端に隣接して配置された前記第一の半導体チップの前記第3の辺または前記第4の辺に形成された前記第一の半導体チップの前記はんだフィレットの長さが、前記第一の半導体チップの前記第1の辺および前記第2の辺に形成された前記はんだフィレットの長さのいずれよりも短く形成されている、パワーモジュール。

#### 【請求項9】

請求項8に記載のパワーモジュールにおいて、

前記第一の半導体チップの前記第3の辺および前記第4の辺は、それぞれ、前記ベース板の前記側端に隣接して配置されており、

前記第一の半導体チップの前記第3の辺および前記第4の辺に形成された前記はんだフィレットの長さが、前記第一の半導体チップの前記第1の辺および前記第2の辺に形成された前記はんだフィレットの長さよりも短く形成されている、パワーモジュール。

#### 【請求項10】

請求項9に記載のパワーモジュールにおいて、

さらに、前記第一の半導体チップの前記第3の辺に隣接して配置された第四の半導体チップを備え、

前記第一の半導体チップの前記第4の辺が前記ベース板の前記側端に隣接して配置され、

前記第一の半導体チップの前記第3の辺および前記第4の辺に形成された前記はんだフィレットの長さが、それぞれ、前記第一の半導体チップの前記第1の辺および前記第2の辺に形成された前記はんだフィレットの長さよりも短く形成されている、パワーモジュール。

#### 【請求項11】

請求項1乃至10のいずれか1項に記載のパワーモジュールにおいて、

前記第一の半導体チップの前記四つの辺に形成された前記はんだフィレットは、前記第一の半導体チップの二辺に形成された長さが、それぞれ、前記第一の半導体チップの他の二辺に形成された前記はんだフィレットの長さのいずれよりも短く形成されている、パワーモジュール。

#### 【請求項12】

請求項11に記載のパワーモジュールにおいて、

さらに、前記ベース板に対向して配置された別のベース板を備え、

前記第一、第二、第三の半導体チップは、それぞれ、一面が前記ベース板にはんだ付けされ、他面が前記別のあるベース板にはんだ付けされ、

前記第一の半導体チップの各辺に形成された前記はんだフィレットのうち、少なくとも

10

20

30

40

50

最も長い前記はんだフィレットに対向する前記別のベース板の前記ベース板との対向面側に凹部が形成されている、パワーモジュール。

【請求項 1 3】

第 1 のベース板と、

前記第 1 のベース板に対向して配置され、前記第 1 のベース板との対向面側に突出部が形成された第 2 のベース板と、

第 1 の面および前記第 1 の面に対向する第 2 の面を有し、前記第 1 の面が第 1 のはんだにより前記第 1 のベース板にはんだ付けされ、前記第 2 の面が第 2 のはんだにより前記第 2 のベース板の前記突出部にはんだ付けされた、四辺を有する半導体チップとを備え、

前記半導体チップの前記第 1 の面の前記四辺のそれぞれに形成された前記第 1 のはんだのはんだフィレットは、少なくとも前記半導体チップの一辺に形成された長さが他の三辺のいずれかに形成された長さとは異なっており、10

前記半導体チップの前記第 2 の面の前記四辺のそれぞれに形成された前記第 2 のはんだのはんだフィレットの長さは、前記半導体チップの前記第 1 の面の前記四辺のそれぞれに形成された前記第 1 のはんだの前記はんだフィレットの長さのいずれよりも短く形成されている、パワーモジュール。

【請求項 1 4】

請求項 1 3 に記載のパワーモジュールにおいて、

前記半導体チップの前記第 1 の面の前記四辺のそれぞれに形成された前記第 1 のはんだの前記はんだフィレットは、前記半導体チップの前記第 1 の面の二辺に形成された長さが、それぞれ、前記半導体チップの前記第 1 の面の他の二辺に形成された前記はんだフィレットの長さのいずれより短く形成されている、パワーモジュール。20

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、パワー用の半導体チップを備えるパワーモジュールに関する。

【背景技術】

【0 0 0 2】

ハイブリッド車やプラグインハイブリッド車、電気自動車などの車両には、動力駆動用の高電圧蓄電池と、高電圧蓄電池の直流高電圧出力を交流高電圧出力に電力変換してモータを駆動するためのインバータ等が搭載される。インバータには、パワー用の半導体チップを内蔵するパワーモジュールを備えている。30

【0 0 0 3】

パワーモジュールとして、放熱板に熱結合される一対の導体板間に半導体チップが実装された構造が知られている。なお、導体板を放熱板と兼用するパワーモジュールを知られている。半導体チップは、一面および一面に対向する他面を有し、一対の導体板間に挟まれた状態で、半導体チップの一面および他面が、それぞれ、一対の導体板の一方または他方にはんだ付けされる。高実装密度化を図り、一対の導体板間に複数の半導体チップが実装されることもある。また、一対の導体板間における半導体チップの周囲に封止樹脂が充填されることもある（例えば、特許文献 1 参照）。40

【先行技術文献】

【特許文献】

【0 0 0 4】

【特許文献 1】特開 2005 - 244166 号公報

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 5】

高実装密度化を図り、導体板上に実装される半導体チップ間の距離または半導体チップと導体板の周囲外線との距離をより小さくすることが求められている。しかし、従来では、半導体チップ相互間の距離および半導体チップと導体板の周囲外線との距離は、すべて50

等しくされていた。このため、半導体チップ相互間の距離および半導体チップと導体板の周囲外線との距離の一部でも所定の距離より小さくなると、半導体チップと導体板を接合するはんだフィレットの形成領域からはんだが溢れることにより半導体チップ同士が短絡したり、導体板の周囲外線からはんだフィレットの形成領域からはんだが溢れ出たりする可能性が生じる。はんだフィレットの形成領域のはんだが導体板の周囲外線から溢れ出ると、他の部材との間で短絡が生じたり、溢れたはんだが落剥して導電性異物となり故障や性能の低下を起こす要因となったりする。

**【課題を解決するための手段】**

**【0006】**

本発明のパワーモジュールは、ベース板と、四つの辺を有する第一の半導体チップと、第一の半導体チップの第1の辺に隣接して配置された一辺を含む四つの辺を有し、ベース板にはんだ付けされた第二の半導体チップと、第一の半導体チップの第2の辺に隣接して配置された一辺を含む四つの辺を有し、ベース板にはんだ付けされた第三の半導体チップとを備え、第一の半導体チップの第3の辺または第4の辺の少なくとも一方は、ベース板の側端に隣接して配置され、第一の半導体チップの第1の辺から第二の半導体チップの一辺までの距離の1/2の距離と、第一の半導体チップの第2の辺から第三の半導体チップの一辺までの距離の1/2の距離と、ベース板の側端に隣接して配置された第一の半導体チップの第3の辺または第4の辺からベース板の側端までの距離とのうち、最も短い距離となる箇所の辺に形成された第一の半導体チップのはんだフィレットの長さが最も短く形成されている。

10

**【発明の効果】**

**【0007】**

本発明によれば、はんだフィレット形成領域からのはんだの溢れにより半導体チップが短絡したり、ベース板の側端から溢れ出たりするのを抑制することができる。

**【図面の簡単な説明】**

**【0008】**

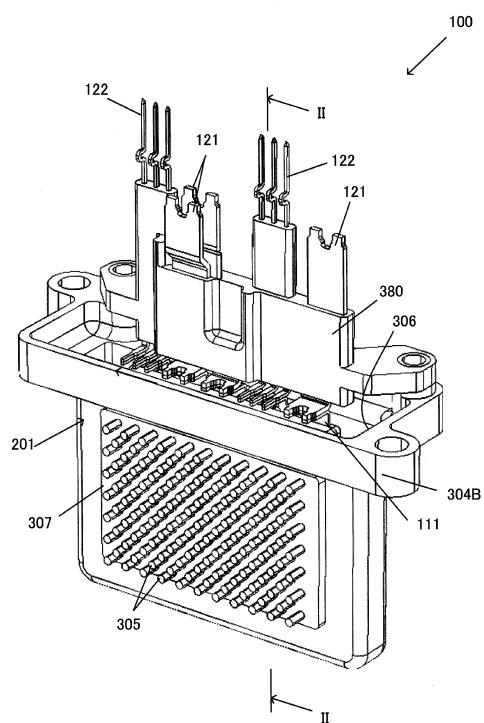

**【図1】**本発明のパワーモジュールの一実施の形態を示す外観斜視図。

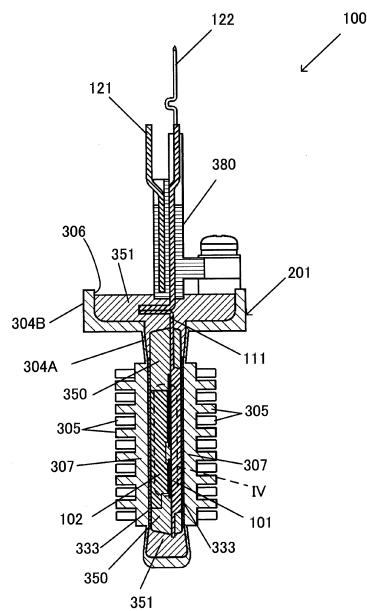

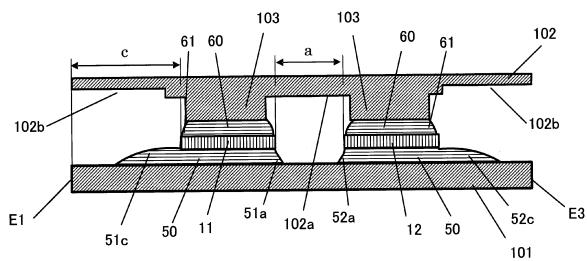

**【図2】**図1に示すパワーモジュールのII-II線断面図。

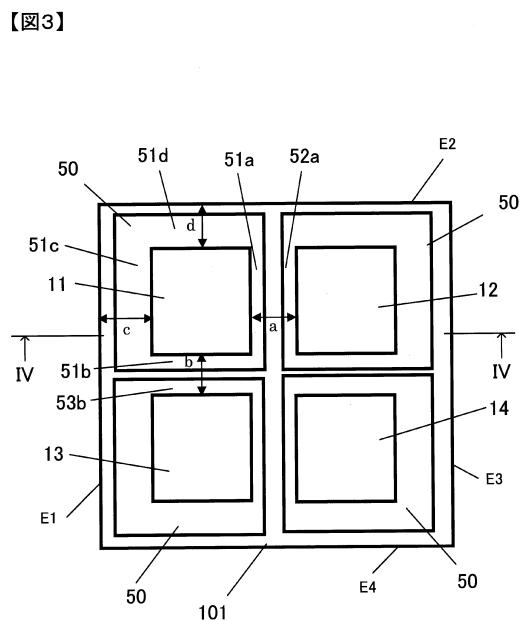

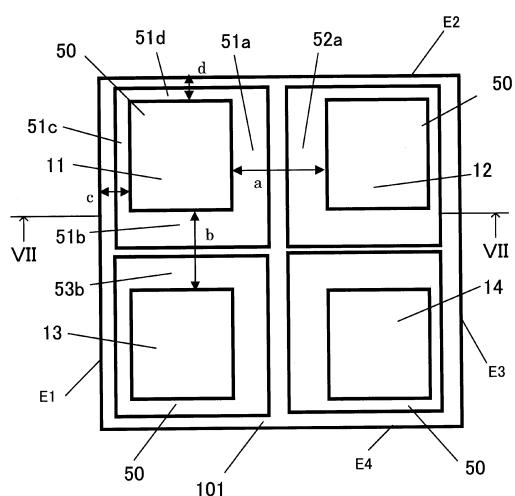

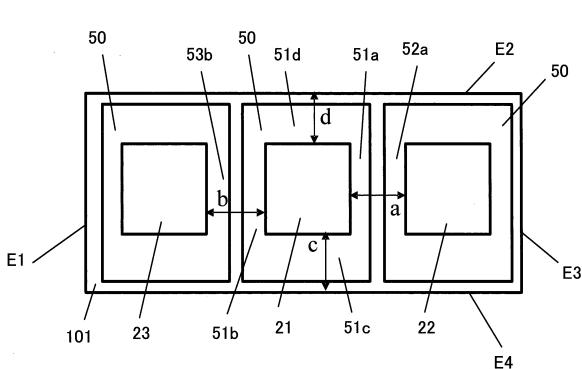

**【図3】**半導体チップの実装構造を示す模式的平面図。

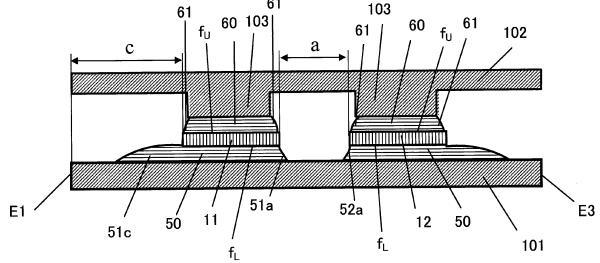

**【図4】**図2の領域IVの拡大断面図であり、図3のIV-IV線断面図。

30

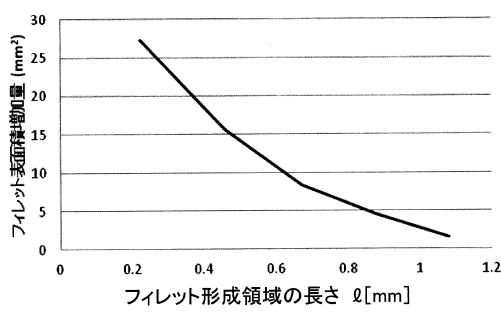

**【図5】**はんだフィレット表面積の増加量とはんだフィレット形成領域の長さとの関係を説明するための図であり、(a)は、半導体チップのはんだ付け構造の基準を示すための断面図、(b)は、はんだフィレット表面積増加量とはんだフィレット形成領域の長さとの関係を示す特性図。

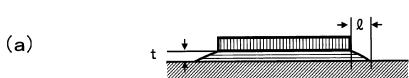

**【図6】**本発明の実施形態2を示し、パワーモジュールに設けられた半導体チップの実装構造の模式的平面図。

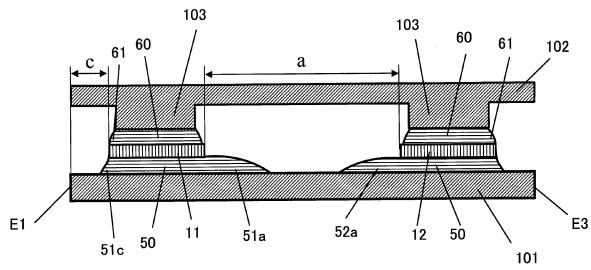

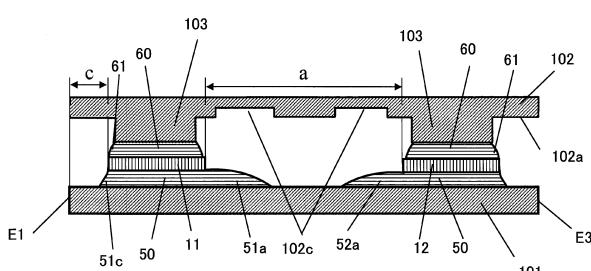

**【図7】**図6のVII-VII線断面図。

**【図8】**本発明の実施形態3を示し、パワーモジュールに設けられた半導体チップの実装構造の断面図。

**【図9】**本発明の実施形態4を示し、パワーモジュールに設けられた半導体チップの実装構造の断面図。

40

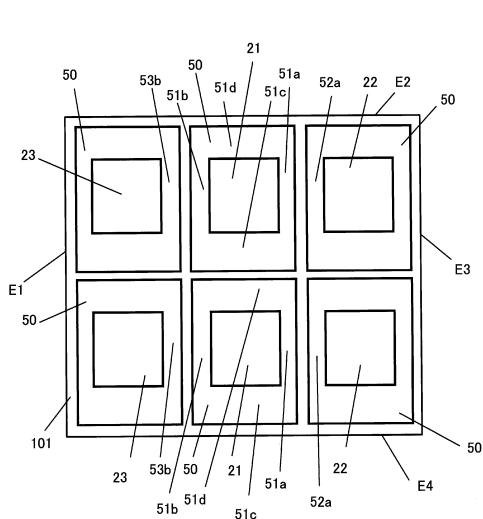

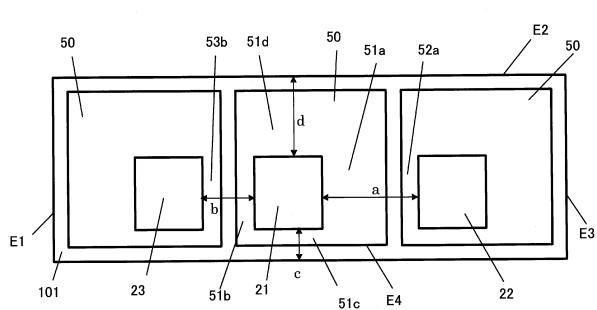

**【図10】**本発明の実施形態5を示し、パワーモジュールに設けられた半導体チップの実装構造の模式的平面図。

**【図11】**実施形態5の変形例を示す図。

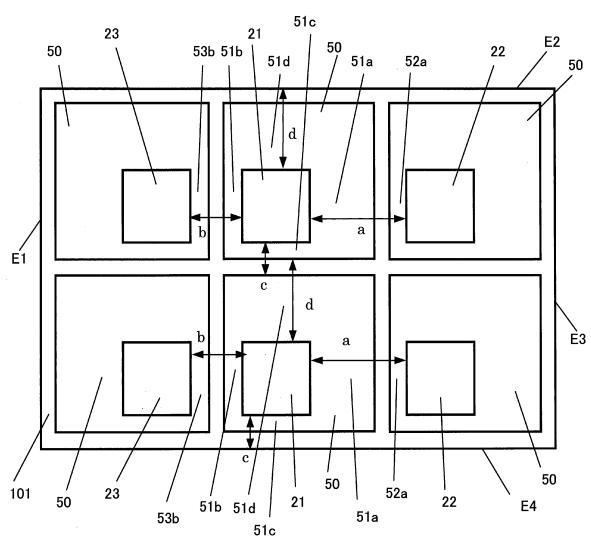

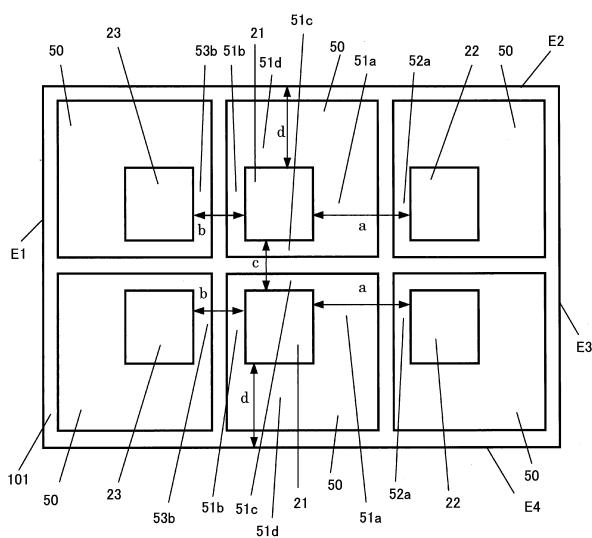

**【図12】**本発明の実施形態6を示し、パワーモジュールに設けられた半導体チップの実装構造の模式的平面図。

**【図13】**実施形態6の変形例1を示す図。

**【図14】**実施形態6の変形例2を示す図。

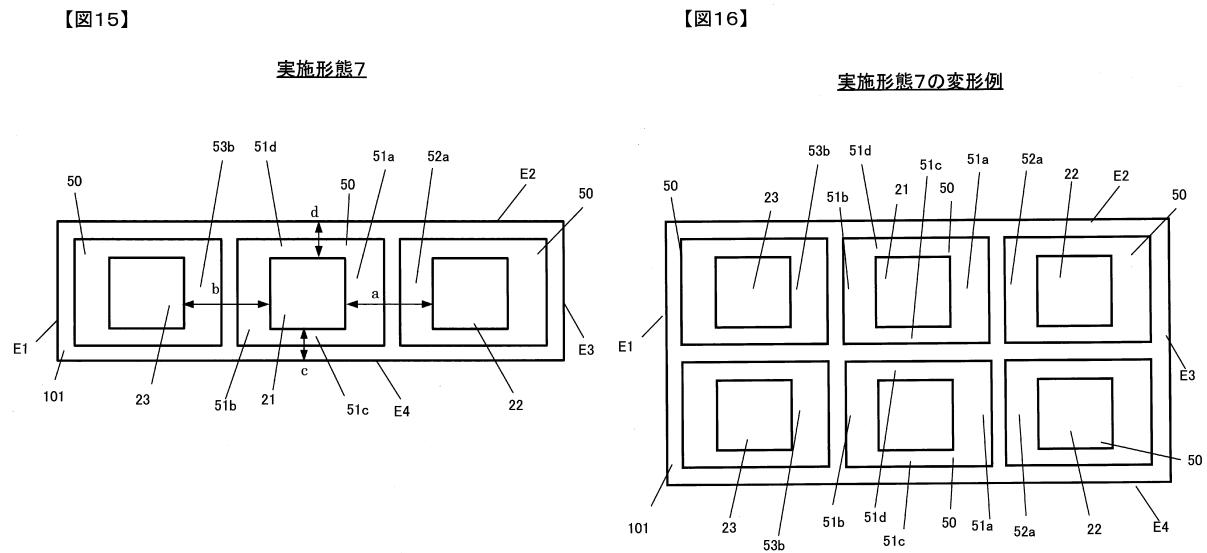

**【図15】**本発明の実施形態7を示し、パワーモジュールに設けられた半導体チップの実装構造の模式的平面図。

50

【図16】実施形態7の変形例を示す図。

【図17】本発明の第1の効果を示す図であり、本発明の実施例1における半導体チップ間の短絡の発生頻度を示す。

【図18】本発明の第2の効果を示す図であり、本発明の実施例2におけるフレーム側端へのはんだ溢れの発生頻度を示す。

【発明を実施するための形態】

【0009】

- 実施形態1 -

(パワーモジュールの全体構造)

以下、図1乃至図4を参照して、本発明のパワーモジュールの実施形態1を説明する。

10

図1は、本発明のパワーモジュールの一実施の形態を示す外観斜視図であり、図2は、図1に示すパワーモジュールのII-II線断面図である。

本発明の実施形態に係るパワーモジュール100は、例えば、自動車に搭載される回転電機駆動システムの車載用電力変換装置等に用いることができる。

パワーモジュール100は、第1のリードフレーム101および第2のリードフレーム102間に実装された、後述する、複数のパワー用の半導体チップ11~14(図3等参照)が収容されたモジュールケース201を備えている。

【0010】

モジュールケース201は、アルミ合金材料、例えばAl、AlSi、AlSiC、Al-C等から構成され、かつ、つなぎ目の無い一体成形された、キャン型(以下CAN型と記す)の形状をなす。ここで、CAN型とは、所定の一面に挿入口306を備え、かつ有底の略直方体形状の容器を指す。また、モジュールケース201は、挿入口306以外に開口を設けない構造であり、挿入口306は、フランジ304Bに、その外周を囲まれている。

20

【0011】

このような形状の金属性のケースとすることで、モジュールケース201を水や油などの冷却媒体が流れる流路内に挿入しても、冷却媒体に対するシールをフランジ304Bにて確保できる。つまり、冷却媒体がモジュールケース201の内部及び端子部分に侵入するのを、簡易な構成にて防ぐことができる。

【0012】

30

モジュールケース201のフランジ304Bの下方は、フィン305が均一に配置された一対の放熱ベース307を有する薄型の直方体形状とされている。各放熱ベース307のフランジ304Bとの接続部には、厚みが極端に薄くなっている湾曲部304Aが形成されている。放熱ベース307の内面と第1、第2のリードフレーム101、102との間には、それぞれ、熱伝導性が高い絶縁シート333が介装されている。パワー用の半導体チップ11~14は動作時に発熱して高温となる。本実施形態のパワーモジュール100では、半導体チップ11~14の動作時の発熱が、第1、第2のリードフレーム101、102で拡散して絶縁シート333に伝わる。そして、モジュールケース201に形成された放熱ベース307、および放熱ベース307に設けられたフィン305から冷却媒体に放熱される。このため、高い冷却性能を実現することができる。

40

【0013】

半導体チップ11~14は、第1のリードフレーム101および第2のリードフレーム102間にはんだ付けにより実装され、その周囲は、一次封止材350により封止されている。半導体チップ11~14と、第1のリードフレーム101および第2のリードフレーム102との実装構造については後述する。

【0014】

第1のリードフレーム101は、上方に延出される複数のリード111を有する。各リード111の先端は一次封止材350の外部に露出している。つまり、リード111の先端が露出され状態で、第1のリードフレーム101は一次封止材350に一体成形される。リード111の先端には、それぞれ、直流正・負極端子、交流端子121、および複数

50

の外部信号端子 122 がはんだ付け等により接合されている。直流正・負極端子および交流端子 121、複数の外部信号端子 122、および第1のリードフレーム 101 のリード 111 は、補助モールド体 380 に一体成形されている。

#### 【0015】

第1のリードフレーム 101 が一体に形成された一次封止材 350 は、補助モールド体 380 に一体に形成された直流正・負極端子および交流端子 121、複数の外部信号端子 122 が、それぞれ、第1のリードフレーム 101 の対応するリード 111 に接続された状態でモジュールケース 201 内に収容される。この状態で、フランジ 304B の挿入口 306 から二次封止材 351 が充填される。二次封止材 351 は、フランジ 304B の内側および第1、第2のリードフレーム 101、102 の周側縁と一次封止材 350 との隙間に充填される。また、二次封止材 351 は、モジュールケース 201 の底面と一次封止材 350 の下面との間にも充填される。パワーモジュール 100 は、このような構造を有しており、高電圧蓄電池の直流高電圧出力を交流高電圧出力に電力変換して、例えば、モータを駆動するためのインバータの機能を果たす。10

#### 【0016】

(半導体チップの実装構造)

図3は、半導体チップの実装構造を示す模式的平面図であり、図4は、図2の領域IVの拡大断面図であり、図3のIV-IV線断面図である。なお、図3では、第2のリードフレーム 102 を取り除いた状態で図示されている。また、図4では、リード 111 等、20 図2の領域IVの外部の図示が省略されている。

第1のベース板、すなわち第1のリードフレーム 101、および第2のベース板、すなわち第2のリードフレーム 102 は、金属板を打ち抜き加工して形成されている。金属板としては、銅系、アルミニウム系、鉄系等の材料を用いることができる。第1、第2のリードフレーム 101、102 は熱伝導率が高いことが好ましい。このため、熱伝導率に優れている、特に、銅系、アルミニウム系の材料が好ましい。

#### 【0017】

第1、第2のリードフレーム 101、102 は、離間対向して配置されており、第1、第2のリードフレーム 101、102 の間に四つの半導体チップ 11~14 が配置されている。図4に示すように、第2のリードフレーム 102 には、半導体チップ 11~14 のそれぞれに対向する四つの突出部 103 が形成されている。四つの突出部 103 は、2行×2列のマトリックス状に配置されている。30

#### 【0018】

半導体チップ 11~14 は、薄い直方体形状を有し、例えば、IGBT（絶縁ゲート型バイポーラトランジスタ）により構成されている。IGBTと共にダイオードや受動素子が含まれていてもよい。各半導体チップ 11~14 は、図4では下面となる一面  $f_L$  と、図4では上面となる他面  $f_U$  を有している。各半導体チップ 11~14 の他面  $f_U$  には、例えば、IGBTのコレクタ電極が形成されている。また、各半導体チップ 11~14 の一面  $f_L$  には、IGBTのエミッタ電極および複数の制御電極が形成されている。各制御電極は、図示はしないが、ボンディングワイヤにより、リード 111 に接続されている。40

#### 【0019】

各半導体チップ 11~14 の一面  $f_L$  は、第1のリードフレーム 101 の第1のはんだ 50 によりはんだ付けされている。各半導体チップ 11~14 の他面  $f_U$  は、第2のリードフレーム 102 の突出部 103 に、第2のはんだ 60 によりはんだ付けされている。突出部 103 は、平面視で、半導体チップ 11~14 より少し小さい矩形形状に形成されている。各半導体チップ 11~14 の他面  $f_U$  が第2のリードフレーム 102 の突出部 103 にはんだ付けされる構造であるので、半導体チップ 11~14 も、突出部 103 と同様、2行×2列のマトリックス状に配置されている。

#### 【0020】

第1、第2のはんだ 50、60 のはんだ材としては、Snを多く含むSn系の他、Au系、Zn-A1系、A1系を用いることができる。また、はんだ材の他、Agペースト、50

Cuペースト、焼成Ag、焼成Cu等の樹脂を含む材料を用いることもできる。樹脂を含む材料では、粘性が低いものが好ましい。

#### 【0021】

図3、図4に図示される半導体チップの実装構造は、例えば、下記の手順で形成される。

第1のリードフレーム101に、第1のはんだ50として固化するはんだ素材を供給する。このはんだとして、シートはんだを用いることができる。または、はんだペーストを印刷により形成したり、溶融はんだを供給したりする方法を用いることもできる。第1のはんだ50として固化するはんだ素材上に、半導体チップ11～14を載置する。各半導体チップ11～14上に第2のはんだ60として固化するはんだ素材を供給する。このはんだ素材の供給は、第1のはんだ50として固化するはんだ素材と同様に行うことができる。第2のはんだ60として固化するはんだ素材に突出部103を位置合わせして、第2のリードフレーム102を第2のはんだ60として固化するはんだ素材上に載置する。第1のリードフレーム101に対して第2のリードフレーム2を加圧しながら加熱して、第1、第2のリードフレーム101、102に各半導体チップ11～14をはんだ付けする。これにより、図3、図4に図示される半導体チップ11～14の実装構造が作製される。

10

次に、半導体チップ11～14の実装構造を、より詳細に説明する。

#### 【0022】

(半導体チップと第1のリードフレームとのはんだ付け構造)

図3、図4に図示されるように、各半導体チップ11～14は、第1のはんだ50の中央部に配置されておらず、中央部よりも隣接する他の半導体チップ11～14に接近する位置に配置されている。

20

図示の距離a～dを下記のように定義する。なお、第1のリードフレーム101の四辺、すなわち側端E1～E4を、図3に図示された通りとする。

半導体チップ11と半導体チップ12との間の距離、すなわち、半導体チップ11と半導体チップ12が互いに対向する辺の間の距離をaとし、

半導体チップ11と半導体チップ13との間の距離、すなわち、半導体チップ11と半導体チップ13が互いに対向する辺の間の距離をbとし、

半導体チップ11の左辺と第1のリードフレーム101の左側の側端E1との間の距離をcとし、

30

半導体チップ11の上辺と第1のリードフレーム101の上側の側端E2との間の距離をdとする。

#### 【0023】

半導体チップ11と半導体チップ12との間には、半導体チップ11のはんだフィレット51aと半導体チップ12のはんだフィレット52aとが形成される。半導体チップ11と半導体チップ13との間には、第一の半導体チップ11のはんだフィレット51bと半導体チップ13のはんだフィレット53bとが形成される。

#### 【0024】

はんだフィレット51aの長さとはんだフィレット52aの長さとが同一であり、はんだフィレット51bの長さとはんだフィレット53bの長さとが同一であるとする。この場合、はんだフィレット51a、52aの各長さは、a/2以下とし、はんだフィレット51b、53bの各長さはb/2以下とする必要がある。なお、本明細書において、はんだフィレットの長さとは、図5(a)に図示されるように半導体チップの辺からはんだフィレットの先端までの長さとする。

40

#### 【0025】

各半導体チップ11～14は、第1のリードフレーム101上にほぼ四等分されたチップ実装領域の中央部よりも隣接する他の半導体チップ11～14に接近する位置に配置されている。ここで、第2のリードフレーム102の4つの突出部103の中心は、各チップ実装領域で偏って実装された半導体チップ11～14の中心と合致する。距離a/2、b/2は、それぞれ、距離c、dよりも短くなっている。半導体チップ間の距離が短いほ

50

ど、または半導体チップとベース板の側端との距離が短いほど、はんだフィレットの溢れにより半導体チップ同士が短絡したり、ベース板の側端からはんだフィレットが溢れたりする可能性が大きくなる。

#### 【0026】

そこで、半導体チップ11、12それぞれにおける、他の半導体チップ12、11に隣接する辺に形成されるはんだフィレット51a、52aの長さを、第1のリードフレーム101の側端E1、E2に隣接する半導体チップ11の2つの辺に形成されるはんだフィレット51c、51dの長さよりも短く形成する。換言すれば、はんだフィレット51c、51dの長さを、はんだフィレット51a、52aの長さより長く形成する。これにより、はんだフィレット51a、52aの形成領域からのはんだの溢れによる半導体チップ11、12の短絡を抑制することができる。10

#### 【0027】

同様に、各半導体チップ11、13それぞれにおける、他の半導体チップ13、11に隣接する辺に形成されるはんだフィレット51b、53bの長さを、第1のリードフレーム101の側端E1、E2に隣接する半導体チップ11の2つの辺に形成されるはんだフィレット51c、51dの長さよりも短く形成する。換言すれば、はんだフィレット51c、51dの長さを、はんだフィレット51b、53bの長さより長く形成する。これにより、はんだフィレット51b、53bの形成領域からのはんだの溢れによる半導体チップ11、13の短絡を抑制することができる。

#### 【0028】

また、距離aと距離bとを比較して、短い方に形成されるはんだフィレットの長さを短くする。例えば、距離aが距離bよりも短い場合は、はんだフィレット51aの長さをはんだフィレット51bの長さよりも短く形成する。20

また、距離cと距離dとを比較して、短い方に形成されるはんだフィレットの長さを短く形成するようにしてもよい。例えば、距離cが距離dよりも短い場合は、はんだフィレット51cの長さをはんだフィレット51dの長さよりも短く形成するようにしてもよい。。

#### 【0029】

上記実施形態において、はんだフィレット51a、51b、52a、53bの長さを短くすることができる理由を説明する。30

液体の表面は表面張力が働くため、表面積を小さくするように、すなわち表面エネルギーが小さくなるように表面張力が働く。よって、表面積が大きくなろうとする場合、表面張力に対抗して大きくなるためのエネルギーが必要である。はんだの表面積の増加量が多くなるほど、その増加のために必要なエネルギーは多くなる。

#### 【0030】

はんだフィレットが形成される際のはんだ溢れは、所定のはんだ体積に対し、はんだフィレット形成領域の長さが短いことに起因して、はんだ内の圧力が上昇し、はんだフィレット形成領域においてはんだが膨らむことにより発生する。はんだフィレットを形成するはんだ体積を同一とした場合、はんだフィレットの長さに依存して、はんだの表面積の増加量は変化する。40

#### 【0031】

はんだフィレットの長さとはんだの表面積の増加量との相関の一例を図5に示す。図5(a)は、半導体チップのはんだ付け構造の基準を示すための断面図であり、図5(b)は、はんだフィレット表面積増加量とはんだフィレット形成領域の長さとの関係を示す特性図である。

図5(a)に示す半導体チップとベース板とのはんだ付け構造において、チップサイズは10mm角である。はんだの厚さtは0.2mmである。

図5(b)におけるはんだフィレット表面積増加量は、半導体チップがはんだの表面から0.05mm沈んだ場合にははんだフィレット表面積の増加量を導出したものである。はんだ表面積は、はんだフィレットが円弧状に膨らむと仮定している。50

## 【0032】

図5(b)により、はんだフィレット形成領域の長さ $l$ が長くなるほど、はんだ表面積の増加量は少なくなることが解る。換言すれば、はんだフィレット形成領域の長さ $l$ が短いほど、はんだフィレットのはんだ表面積の増加量は増加する。上述したように、はんだ表面積の増加量が多くなればなるほど、その増加のために必要なエネルギーは多くなる。この現象を利用して、半導体チップ11を第1のリードフレーム101に加圧した際に、第1のはんだ50が溶融した状態のはんだ素材にかかるエネルギーを、はんだフィレット形成領域の長さ $l$ が長いはんだフィレット51c、51dの表面積を増加させることに消費させることで、はんだフィレット形成領域の長さ $l$ が短いはんだフィレット51a、51bの表面積の増加、換言すれば、はんだフィレット形成領域からのはんだの溢れを抑制することが可能となる。10

## 【0033】

図4を参照して、各半導体チップ11～14は、突出部103と同心に配置されている。すなわち、半導体チップ11～14それぞれの四つの辺の各辺と突出部103の四つの辺の各辺との間隔は、ほぼ同一である。従って、各半導体チップ11～14と突出部103とを接合する第2のはんだ60は、半導体チップ11～14それぞれの四つの辺の各辺には、同じ長さのはんだフィレット61が形成されている。20

## 【0034】

はんだフィレット61の長さは、はんだフィレット51a、51bのいずれよりも短く形成することができる。この理由は、以下の通りである。20

上述した通り、半導体チップ11～14は、第1のリードフレーム101、第1のはんだ、半導体チップ11～14、第2のはんだ60および第2のリードフレーム102が積層された状態で、加熱・加圧してはんだ付けされる。すなわち、はんだ付け時には、第1のはんだ50および第2のはんだ60が共に溶融状態となっている。この状態では、第1のはんだ50と第2のはんだ60とは、分離して形成されているが、はんだフィレット表面積増加量とはんだフィレット形成領域の長さとの関係では、図5(b)に示された関係を有している。このため、第1、第2のはんだ50、60が溶融した状態のはんだ素材にかかるエネルギーを、はんだフィレット形成領域の長さ $l$ が長いはんだフィレット51c、51dおよび51a、51bの表面積を増加させることに消費させることで、はんだフィレット形成領域の長さ $l$ が短いはんだフィレット61の表面積の増加、換言すれば、はんだフィレット形成領域からのはんだの溢れを抑制することが可能となる。30

なお、はんだフィレット61の長さは、必ずしも、はんだフィレット51a、51b、の長さのいずれよりも短くする必要は無い。

## 【0035】

なお、上記では半導体チップ11について説明したが、半導体チップ12～14に関し半導体チップ11の場合と同様である。つまり、半導体チップ12～14それぞれにおいても、他の半導体チップ11～14に隣接する辺に形成されるはんだフィレットの長さは、第1のリードフレーム101の側端E1～E4に隣接する辺に形成されるはんだフィレットの長さよりも短く形成されている。40

## 【0036】

上記実施形態によれば、下記の効果を奏する。

(1) 第1のリードフレーム101に、半導体チップ11～14を、それぞれ、第1のはんだ50によりはんだ付けした。半導体チップ11～14それぞれにおいて、第1のリードフレーム101の側端E1～E4に隣接する辺に形成されたはんだフィレットの長さを、他の半導体チップ11～14に隣接する辺に形成されたはんだフィレットの長さよりも長く形成した。

このため、各半導体チップ11～14の、他の半導体チップ11～14に隣接する辺に形成されるはんだフィレットの形成領域からはんだが溢れるのを抑制し、半導体チップ11～14が相互に短絡するのを防止することができる。50

## 【0037】

- 実施形態 2 -

図 6 は、本発明の実施形態 2 を示し、パワーモジュールに設けられた半導体チップの実装構造の模式的平面図あり、図 7 は、図 6 の V I I - V I I 線断面図である。

実施形態 2 において、第 1、第 2 のリードフレーム 101、102、半導体チップ 11 ~ 14、および第 1、第 2 のはんだ 50、60 は、実施形態 1 と同じ部材である。実施形態 2 が実施形態 1 と異なる点は、半導体チップ 11 ~ 14 それぞれが、第 1 のはんだ 50 の中央部よりも、第 1 のリードフレーム 101 の各コーナー部に接近する位置に配置されている点である。

【 0 0 3 8 】

すなわち、実施形態 2 における距離 a、b、c、d の定義を実施形態 1 と同じとする 10

、下記の構成となっている。

半導体チップ 11 を一例に説明する。第 1 のリードフレーム 101 の側端 E1、E2 に隣接する 2 つの辺に形成されたはんだフィレット 51c、51d の長さは、半導体チップ 11 における他の半導体チップ 12 に隣接する辺に形成されたはんだフィレット 51a の長さと、半導体チップ 12 における他の半導体チップ 11 に隣接する辺に形成されたはんだフィレット 52a の長さよりも短く形成されている。換言すれば、各半導体チップ 11、12 に形成されたはんだフィレット 51a、52a の長さは、半導体チップ 11 の 2 つの辺に形成されたはんだフィレット 51c、51d の長さより長く形成されている。これにより、はんだフィレット 51c、51d の形成領域からはんだが第 1 のリードフレーム 101 の側端 E1、E2 に溢れ出るのが抑制される。 20

【 0 0 3 9 】

同様に、第 1 のリードフレーム 101 の側端 E1、E2 に隣接する半導体チップ 11 の 2 つの辺に形成されるはんだフィレット 51c、51d の長さは、半導体チップ 11 における他の半導体チップ 13 に隣接する辺に形成されたはんだフィレット 51b と、半導体チップ 13 における他の半導体チップ 11 に隣接する辺に形成されたはんだフィレット 53b の長さよりも短く形成されている。換言すれば、各半導体チップ 11、13 に形成されたはんだフィレット 51b、53b の長さは、半導体チップ 11 の 2 つの辺に形成されたはんだフィレット 51c、51d の長さより長く形成されている。これにより、はんだフィレット 51c、51d の形成領域からはんだが第 1 のリードフレーム 101 の側端 E1、E2 に溢れ出るのが抑制される。 30

【 0 0 4 0 】

また、距離 c と距離 d とを比較して、短い方に形成されるはんだフィレットの長さを短くする。例えば、距離 c が距離 d よりも短い場合は、はんだフィレット 51c の長さをはんだフィレット 51d の長さよりも短く形成する。

また、距離 a と距離 b とを比較して、短い方に形成されるはんだフィレットの長さを短くするようにしてもよい。例えば、距離 a が距離 b よりも短い場合は、はんだフィレット 51a の長さを、はんだフィレット 51b の長さよりも短く形成するようにしてもよい。

【 0 0 4 1 】

なお、半導体チップ 12 ~ 14 に関しても、半導体チップ 12 ~ 14 それぞれの各辺から隣接する他の半導体チップ 11 ~ 14 の各辺までの距離 a の 1 / 2、距離 b の 1 / 2 と、半導体チップ 12 ~ 14 それぞれの各辺から第 1 のリードフレーム 101 の側端 E1 ~ E4 までの距離 c、d との関係は、半導体チップ 11 の場合と同様である。また、半導体チップ 12 ~ 14 それぞれの各辺に形成されるはんだフィレットの長さは、半導体チップ 11 の各辺に形成されるはんだフィレットと同様である。すなわち、半導体チップ 12 ~ 14 に関しても、第 1 のリードフレーム 101 の側端 E1 ~ E4 に隣接する辺に形成されるはんだフィレットの長さは、他の半導体チップ 11 ~ 14 に隣接する辺に形成されるはんだフィレットの長さより短く形成されている。 40

【 0 0 4 2 】

実施形態 2 によれば下記の効果を奏する。

( 1 ) 第 1 のリードフレーム 101 に、半導体チップ 11 ~ 14 を第 1 のはんだ 50 によ 50

りはんだ付けした。各半導体チップ 11～14 それぞれにおいて、他の半導体チップ 11～14 に隣接する辺に形成されたはんだフィレットの長さを、第 1 のリードフレーム 101 の側端に隣接する辺に形成されたはんだフィレットの長さよりも長く形成した。

このため、各半導体チップ 11～14 における、第 1 のリードフレーム 101 の側端に隣接する辺に形成されるはんだフィレットの形成領域から第 1 のリードフレーム 101 の側端にはんだが溢れ出るのを抑制することができる。

#### 【0043】

##### - 実施形態 3 -

図 8 は、本発明の実施形態 3 を示し、パワーモジュールに設けられた半導体チップの実装構造の断面図である。図 8 は、パワーモジュールの実施形態 1 の図 4 に対応する領域の図である。10

実施形態 3 のパワーモジュール 100 は、第 2 のリードフレーム 102 における、第 1 のリードフレーム 101 に対向する内面 102a に凹部 102b が形成されている点で、実施形態 1 と相違する。実施形態 3 のパワーモジュール 100 の他の構成は、実施形態 1 と同様である。

#### 【0044】

実施形態 1 で説明した通り、はんだフィレット 51c、51d は、第 1 のリードフレーム 101 の側端 E1、E2 に隣接する辺に形成されており、その長さは半導体チップ 11、12 それぞれの、他の半導体チップ 12、11 に隣接する辺に形成されたはんだフィレット 51a、52a の長さより長く形成されている。従って、はんだフィレット 51c、20 51d の形成領域からはんだが溢れ易い。

#### 【0045】

実施形態 3 では、第 2 のリードフレーム 102 の内面 102a における、はんだフィレット 51c、52c が対向する部分に凹部 102b が形成されている。図 8 では、第 2 のリードフレーム 102 の側端 E1、E3 について説明しているが、側板 E2、E4 についても同様に凹部 102b が形成されている。上述した通り、はんだフィレット形成領域の長さが長いとはんだが溢れ易い。このため、はんだフィレット形成領域の長さが長いのはんだフィレット 51c、52c、51d、52 の形成領域からはんだが溢れて第 2 のリードフレーム 102 に接触し、第 1、第 2 のリードフレーム 101、102 が短絡することができる。実施形態 3 では、はんだが溢れ易い箇所に対応して第 2 のリードフレーム 102 に凹部 102b が形成されているため、第 1、第 2 のリードフレーム 101、102 が短絡を防止することができる。30

#### 【0046】

実施形態 3 における他の構造は、実施形態 1 と同一であるので、実施形態 1 の効果 (1) と同じ効果を奏する。

また、上述したように、実施形態 3 では、半導体チップ 11～14 の各辺に形成されたはんだフィレットのうち、第 1 のリードフレーム 101 に隣接する辺に形成されたはんだフィレット、すなわち、長い方のはんだフィレットに対向する第 2 のリードフレーム 102 の部分に凹部 102b を形成した。このため、長い方のはんだフィレットの形成領域からはんだが溢れた場合でも、第 1、第 2 のリードフレーム 101、102 の短絡を防止することができる。40

#### 【0047】

##### - 実施形態 4 -

図 9 は本発明の実施形態 4 示し、パワーモジュールに設けられた半導体チップの実装構造の断面図である。図 9 は、パワーモジュールの実施形態 2 の図 7 に対応する領域の図である。

実施形態 4 パワーモジュール 100 は、第 2 のリードフレーム 102 に、第 1 のリードフレーム 101 に対向する内面 102a に凹部 102c が形成されている点で、実施形態 2 と相違する。実施形態 4 のパワーモジュール 100 の他の構成は、実施形態 2 と同様である。50

## 【0048】

実施形態2で説明した通り、はんだフィレット51a、52aは、それぞれ、半導体チップ11、12における、他の半導体チップ12、11に隣接する辺に形成されており、その長さは、半導体チップ11における、第1のリードフレーム101の側端E1、E2に隣接する辺に形成されたはんだフィレット51c、51dの長さより長く形成されている。従って、はんだフィレット51a、52aの形成領域からはんだが溢れ易い。

## 【0049】

実施形態4では、第2のリードフレーム102の内面102aにおける、はんだフィレット51a、52aに対向する部分に凹部102cが形成されている。図9では、半導体チップ11、12の間のはんだフィレット51a、52aについて説明しているが、半導体チップ11、13の間のはんだフィレット、半導体チップ12、14の間のはんだフィレット、半導体チップ13、14の間のはんだフィレットにそれぞれ対向する部分に凹部102cが形成されている。このため、はんだフィレット51a、52aの形成領域からはんだが溢れて第2のリードフレーム102に接触し、第1、第2のリードフレーム101、102が短絡するのを防止することができる。10

## 【0050】

実施形態4における他の構造は、実施形態2と同一であるので、実施形態2の効果(1)と同じ効果を奏する。

また、上述したように、実施形態4では、半導体チップ11～14それぞれの各辺に形成されたはんだフィレットのうち、他の半導体チップ11～14に隣接する辺に形成されたはんだフィレット、すなわち長い方のはんだフィレットに対向する第2のリードフレーム102に凹部102cを形成した。このため、長い方のはんだフィレットが溢れた場合でも、第1、第2のリードフレーム101、102の短絡を防止することができる。20

## 【0051】

## - 実施形態5 -

図10は、本発明の実施形態5を示し、パワーモジュールに設けられた半導体チップの実装構造の模式的平面図である。

実施形態5のパワーモジュール100は、直線状に配列された3つの半導体チップ21～23を備えている。各半導体チップ21～23を固定する第1のはんだ50は、平面視で、配列方向、すなわち左右方向の長さが、それに直交する方向、すなわち上下方向の長さよりも長い矩形形状を有する。各半導体チップ21～23は平面視が正方形である。各半導体チップ21～23は、第1のはんだ50における左右方向及び上下方向のほぼ中央部に配置されている。30

図示の距離a～dを下記のように定義する。

半導体チップ21における、半導体チップ22に隣接する辺から半導体チップ22の半導体チップ21に隣接する辺までの距離をaとし、

半導体チップ21における、導体チップ23に隣接する辺から半導体チップ23の半導体チップ21に隣接する辺までの距離をbとし、

半導体チップ21における、第1のリードフレーム101の下方側の側端E4に隣接する辺から第1のリードフレーム101の下方側の側端E4までの距離をcとし、40

半導体チップ21における、第1のリードフレーム101の上方側の側端E2に隣接する辺から第1のリードフレーム101の上方側の側端E2までの距離をdとする。

## 【0052】

実施形態5では、距離a/2、b/2は、それぞれ、距離c、dよりも短くなっている。

半導体チップ21、22それぞれの、他の半導体チップ22、21に隣接する辺に形成されたはんだフィレット51a、52aの長さは、第1のリードフレーム101の側端E2、E4に隣接する半導体チップ21の辺に形成されたはんだフィレット51c、51dの長さよりも短く形成されている。換言すれば、半導体チップ21に形成されたはんだフィレット51c、51dの長さは、半導体チップ21、22それぞれに形成されたはんだ

フィレット 5 1 a、5 2 a の長さよりも長く形成されている。これにより、はんだフィレット 5 1 a、5 2 a の形成領域からのはんだの溢れによる半導体チップ 2 1、2 2 の短絡を抑制することができる。

#### 【0053】

同様に、各半導体チップ 2 1、2 3 それぞれの、他の半導体チップ 2 3、2 1 に隣接する辺に形成されたはんだフィレット 5 1 b、5 3 b の長さは、第 1 のリードフレーム 1 0 1 の側端 E 2、E 4 に隣接する半導体チップ 2 1 の辺に形成されたはんだフィレット 5 1 c、5 1 d の長さよりも短く形成されている。換言すれば、各半導体チップ 2 1 に形成されたはんだフィレット 5 1 c、5 1 d の長さは、半導体チップ 2 1、2 3 に形成されたはんだフィレット 5 1 b、5 3 b の長さよりも長く形成されている。これにより、はんだフィレット 5 1 b、5 3 b の形成領域からのはんだの溢れによる半導体チップ 2 1、2 3 の短絡を抑制することができる。10

#### 【0054】

また、距離 a と距離 b とを比較して、短い方に形成されるはんだフィレットの長さを短くする。例えば、距離 a が距離 b よりも短い場合は、はんだフィレット 5 1 a の長さをはんだフィレット 5 1 b の長さよりも短くする。

また、距離 c と距離 d とを比較して、短い方に形成されるはんだフィレットの長さを短くするようにしてもよい。例えば、距離 c が距離 d よりも短い場合は、はんだフィレット 5 1 c の長さをはんだフィレット 5 1 d の長さよりも短くするようにしてもよい。20

#### 【0055】

実施形態 5 では、半導体チップ 2 1 における、第 1 のリードフレーム 1 0 1 の側端 E 2、E 4 に隣接する辺に形成されたはんだフィレット 5 1 c、5 1 d の長さを、他の半導体チップ 2 2、2 3 に隣接する辺に形成されたはんだフィレット 5 1 a、5 1 b の長さよりも長く形成した。20

このため、実施形態 1 の効果（1）と同様に、半導体チップ 2 1 における、半導体チップ 2 2、2 3 に隣接する辺に形成されたはんだフィレット 5 1 a、5 1 b の形成領域からはんだが溢れるのを抑制し、半導体チップ 2 1 ~ 2 3 が短絡するのを防止することができる。

#### 【0056】

なお、実施形態 5 において、実施形態 3（図 8 参照）に示したと同様に、第 2 のリードフレーム 1 0 2 の内面 1 0 2 a に凹部 1 0 2 b を形成するようにしてもよい。すなわち、各半導体チップ 2 1 ~ 2 3 における、第 1 のリードフレーム 1 0 1 の側端 E 2、E 4 に隣接する辺に形成するはんだフィレット 5 1 c、5 1 d に対応する第 2 のリードフレーム 1 0 2 の内面 1 0 2 a の部分に、凹部 1 0 2 b を形成してもよい。30

#### 【0057】

##### - 実施形態 5 の変形例 -

図 1 1 は、図 1 0 に図示された実施形態 5 の変形例である。

図 1 1 に示された変形例では、半導体チップ 2 1 ~ 2 3 が 2 列に配列されている。

各列に配置された半導体チップ 2 1 の各辺に形成されるはんだフィレット 5 1 a ~ 5 1 d の相互の長さ関係は、図 1 0 について説明した関係と同一である。従って、実施形態 5 の変形例は、実施形態 5 と同様な効果を奏する。40

半導体チップ 2 1 ~ 2 3 は、3 列以上に形成することもできる。

また、各列に配置する半導体チップ 2 1 ~ 2 3 の数を 4 つ以上とすることもできる。

#### 【0058】

##### - 実施形態 6 -

図 1 2 は、本発明の実施形態 6 を示し、パワーモジュールに設けられた半導体チップの実装構造の模式的平面図である。

実施形態 6 のパワーモジュール 1 0 0 も、実施形態 5 と同様に、直線状に配列された 3 つの半導体チップ 2 1 ~ 2 3 を備えている。しかし、各半導体チップ 2 1 ~ 2 3 は、第 1 のはんだ 5 0 の中央部から外れた位置に配置されている。50

## 【0059】

図示の距離  $a \sim d$  の定義を、実施形態 5 と同一とするとき、実施形態 6 では、距離  $b / 2$ 、 $c$  は、それぞれ、距離  $a$ 、 $d$  よりも短くなっている。また、距離  $b / 2$  と距離  $c$  とは、ほぼ等しく、距離  $a$  と距離  $d$  とは、ほぼ等しくなっている。

各半導体チップ 21、23 それぞれにおける、他の半導体チップ 23、21 に隣接する辺に形成されたはんだフィレット 51b、53b の長さ、および半導体チップ 21 における、第 1 のリードフレーム 101 の側端 E4 に隣接する辺に形成されたはんだフィレット 51c の長さはほぼ同一である。半導体チップ 21 における、半導体チップ 22 に隣接する辺に形成されたはんだフィレット 51a の長さと、半導体チップ 21 における、第 1 のリードフレーム 101 の側端 E2 に隣接する辺に形成されたはんだフィレット 51d の長さは、ほぼ同一である。半導体チップ 21、23 それぞれに形成されたはんだフィレット 51b、53b の長さおよび半導体チップ 21 に形成されたはんだフィレット 51c の長さは、半導体チップ 21 に形成されたはんだフィレット 51a、51d の長さより短く形成されている。10

## 【0060】

換言すれば、半導体チップ 21 に形成されたはんだフィレット 51a、51d の長さは、半導体チップ 21、23 それぞれに形成されたはんだフィレット 51b、53b の長さおよび半導体チップ 21 に形成されたはんだフィレット 51c の長さより長く形成されている。なお、半導体チップ 22 における、半導体チップ 21 に隣接する辺に形成されたはんだフィレット 52a の長さは、はんだフィレット 51b、53b の長さとほぼ同一である。20

## 【0061】

実施形態 6 では、半導体チップ 21 に形成されたはんだフィレット 51a、51d の長さが、半導体チップ 21 と半導体チップ 23 との間に形成されたはんだフィレット 51b、53b の長さよりも長く形成されている。このため、半導体チップ 21 と 23 とが、はんだフィレット 51b、53b により短絡するのを防止することができる。また、半導体チップ 21 に形成されたはんだフィレット 51a、51d の長さが、半導体チップ 21 に形成されたはんだフィレット 51c の長さよりも長く形成されている。このため、半導体チップ 21 に形成されたはんだフィレット 51c の形成領域から第 1 のリードフレーム 101 の側端 E4 にはんだが溢れ出るのを抑制することができる。30

## 【0062】

なお、実施形態 6 において、実施形態 3、4（図 8、図 9 参照）に示したように、第 2 のリードフレーム 102 の内面 102a に凹部 102b または 102c を形成するようにしてもよい。すなわち、半導体チップ 21 における、半導体チップ 22 に隣接する辺に形成されるはんだフィレット 51a および第 1 のリードフレーム 101 の側端 E2、E4 に隣接する辺に形成するはんだフィレット 51d に対応する第 2 のリードフレーム 102 の内面 102a の部分に、凹部 102c、102b を形成してもよい。また、半導体チップ 22、23 それぞれにおける、第 1 のリードフレーム 101 の側端 E1 および E2、または E2 および E3 に隣接する辺に対応する第 2 のリードフレーム 102 の内面 102a に、凹部 102b を形成してもよい。40

## 【0063】

## - 実施形態 6 の変形例 1 -

図 13 は、図 12 に図示された実施形態 6 の第 1 の変形例を示す図である。

図 13 では、図 12 に示された半導体チップ 21～23 が 2 列に配列されている。図 13 に示された実施形態 6 の変形例 1 において、隣接する半導体チップ 21～23 間または第 1 のリードフレーム 101 の側端 E1～E4 との距離  $a \sim d$  の相互の関係は、1 列目および 2 列目共に、図 12 に示された実施形態 6 と同一である。また、半導体チップ 21～23 それぞれの四つの辺に形成されたはんだフィレット（51a～51d、52a、53b 等）の長さの相互の関係も、1 列目および 2 列目共に、図 12 に示された実施形態 6 と同一である。従って、変形例 1 においても、図 12 に示された実施形態 6 と同様な効果を50

奏する。

なお、半導体チップ 21～23 は、3列以上に形成することもできる。また、各列に配置する半導体チップ 21～23 の数を 4つ以上とすることもできる。

#### 【0064】

##### - 実施形態 6 の変形例 2 -

図 14 は、図 12 に図示された実施形態 6 の変形例 2 を示す図である。

図 14 でも、図 12 に示された半導体チップ 21～23 が 2列に配列されている。しかし、図 13 に示された第 1 の変形例とは異なり、2列目の半導体チップ 21～23 は、それぞれ、1列目の半導体チップ 21～23 に対して上下が反転した状態で配置されている。

10

#### 【0065】

図 14 に示された実施形態 6 の変形例 2において、隣接する半導体チップ 21～23 間または第 1 のリードフレーム 101 の側端 E1～E4 との距離 a～d の相互の関係は、1列目および 2列目共に、図 12 に示された実施形態 6 と同一である。また、半導体チップ 21～23 それぞれの四つの辺に形成されたはんだフィレット (51a～51d、52a、53b 等) の長さの相互の関係も、1列目および 2列目共に、図 12 に示された実施形態 6 と同一である。従って、変形例 2 においても、図 12 に示された実施形態 6 と同様な効果を奏する。

#### 【0066】

なお、図 14において、1列目および 2列目の半導体チップ 21～23 の配置を交互に付加して、3列以上とすることもできる。また、各列に配置する半導体チップ 21～23 の数を 4つ以上とすることもできる。

20

#### 【0067】

##### - 実施形態 7 -

図 15 は、本発明の実施形態 7 を示し、パワーモジュールに設けられた半導体チップの実装構造の模式的平面図である。

実施形態 7 のパワーモジュール 100 は、実施形態 5 と同様、直線状に配列された 3つの半導体チップ 21～23 を備えており、各半導体チップ 21～23 は、第 1 のはんだ 50 における左右方向及び上下方向のほぼ中央部に配置されている。しかし、各半導体チップ 21～23 をはんだ付けする第 1 のはんだ 50 は、左右方向の長さが、上下方向の長さよりも大きい矩形形状を有している。

30

#### 【0068】

つまり、距離 a～d を、実施形態 5 と同様に定義するとき、実施形態 7 では、下記の構成を有している。

半導体チップ 21 の半導体チップ 22 に隣接する辺から半導体チップ 22 の半導体チップ 21 に隣接する辺までの距離 a と、半導体チップ 21 の半導体チップ 23 に隣接する辺から半導体チップ 23 の半導体チップ 21 に隣接する辺までの距離 b は、ほぼ等しい。半導体チップ 21 の第 1 のリードフレーム 101 の側端 E2 に隣接する辺から第 1 のリードフレーム 101 の側端 E2 までの距離 d と、半導体チップ 21 における、第 1 のリードフレーム 101 の側端 E4 に隣接する辺から第 1 のリードフレーム 101 の側端 E4 までの距離 c は、ほぼ等しい。距離 c、d は、それぞれ、距離 a/2、b/2 より短く形成されている。

40

#### 【0069】

半導体チップ 21、22 それぞれにおける、他の半導体チップ 22、21 に隣接する辺に形成されたはんだフィレット 51a、52a の長さは、半導体チップ 21、23 それぞれにおける、他の半導体チップ 23、21 に隣接する辺に形成されたはんだフィレット 51b、53b の長さと、ほぼ同一に形成されている。半導体チップ 21 における、第 1 のリードフレーム 101 の側端 E4 および E2 に隣接する辺に形成されるはんだフィレット 51c および 51d の長さは、ほぼ同一に形成されている。はんだフィレット 51a、51b、52a、53b は、はんだフィレット 51c、51d より長く形成されている。

50

## 【0070】

従って、実施形態7では、はんだフィレット51a、51b、52a、53bは、はんだフィレット51c、51dよりも、はんだフィレット形成領域からはんだが溢れ易くなっている。これにより、はんだフィレット51c、51dの形成領域から第1のリードフレーム101の側端E2、E4にはんだが溢れ出るのが抑制される。

## 【0071】

なお、実施形態7において、実施形態4(図9参照)に示したと同様に第2のリードフレーム102の内面102aに凹部102cを形成するようにしてもよい。すなわち、半導体チップ21～23それぞれにおける、他の半導体チップ21～23に隣接する辺に形成されるはんだフィレット51a、51b、52a、53bに対応する第2のリードフレーム102の内面102aの部分に凹部102cを形成してもよい。10

## 【0072】

## - 実施形態7の変形例 -

図16は、図15に図示された実施形態7の変形例である。

図16に示された変形例では、半導体チップ21～23が2列に配列されている。

各列に配置された半導体チップ21の各辺に形成されるはんだフィレット51a～51dの相互の長さ関係は、図15について説明した関係と同一である。従って、実施形態7の変形例は、実施形態7と同様な効果を奏する。

半導体チップ21～23は、3列以上に形成することもできる。

また、各列に配置する半導体チップ21～23の数を4つ以上とすることもできる。20

## 【0073】

## - 効果の検証 -

以下、本発明の実施例による効果の具体例を示す。

## [実施例1]

図17は、本発明の第1の効果を示す図であり、本発明の実施例1における半導体チップ間の短絡の発生頻度を示す。

実施例1は、実施形態1として図3および図4に示される第1、第2のリードフレーム101、102と半導体チップ11～14のはんだ付け構造を有する。詳細には、第1、第2のリードフレーム101、102は銅板により形成した。第2のリードフレーム102には、四つの突出部103を形成し、四つの半導体チップ11～14をそれぞれ、各突出部103に対応して実装した。各半導体チップ11～14は、10mm角の直方体形状を有する。隣接する半導体チップ11～14間それぞれの距離(aおよびb等)を1.0mmとした。各半導体チップ11～14と第1のリードフレーム101の側端E1～E4までの距離(cおよびd等)を2.0mmとした。30

## 【0074】

各半導体チップ11～14における、他の半導体チップ11～14に隣接する辺に形成するはんだフィレット(51a、51b、52a、53b等)の長さを0.3mmとした。各半導体チップ11～14における、第1のリードフレーム101の側端E1～E4に隣接する辺に形成するはんだフィレット(51c、51d等)の長さを1.0mmとした。はんだ50は、シート状のSn3Ag0.5Cuはんだを用いた。リフローは真空リフロー装置を用い、250℃ピーカの温度プロファイルを用いて接続した。40

## 【0075】

比較例1として、下記に示す、第1、第2のリードフレーム101、102と半導体チップ11～14のはんだ付け構造を作製した。

各半導体チップ11～14における、他の半導体チップ11～14に隣接する辺に形成するはんだフィレット(51a、51b、52a、53b等)の長さを0.3mmとした。各半導体チップ11～14における、第1のリードフレーム101の側端E1～E4に隣接する辺に形成するはんだフィレット(51c、51d等)の長さを0.3mmとした。すなわち、各半導体チップ11～14の四つの辺に形成されるはんだフィレットの長さをすべて0.3mmとした。50

上記以外は、すべて実施例 1 と同じである。

#### 【0076】

実施例 1 および比較例 1 を、それぞれ、20 個作製した。実施例 1 と比較例 1 について、半導体チップ 11 ~ 14 間の短絡発生個数および半導体チップ 11 ~ 14 における、第 1 のリードフレーム 101 の側端へのはんだフィレット形成領域からのはんだの溢れの発生個数を調べた。その結果を図 17 に示す。

比較例 1、すなわち半導体チップ 11 ~ 14 の四つの辺それぞれに形成するはんだフィレットの長さをすべて 0.3 mm にした実装構造では、20 個中 7 個に半導体チップ 11 ~ 14 相互の短絡が発生した。

これに対し、実施例 1、すなわち、各半導体チップ 11 ~ 14 における、他の半導体チップ 11 ~ 14 に隣接する辺に形成するはんだフィレット (51a、51b、52a、53b 等) の長さを 0.3 mm とし、各半導体チップ 11 ~ 14 における、第 1 のリードフレーム 101 の側端に隣接する辺に形成するはんだフィレット (51c、51d 等) の長さを 1.0 mm とした実装構造では、半導体チップ 11 ~ 14 相互の短絡は、20 個中 0 個であった。10

なお、実施例 1 および比較例 1 共に、半導体チップ 11 ~ 14 における、第 1 のリードフレーム 101 の側端 E1 ~ E4 へのはんだフィレットからのはんだ溢れの発生個数は、20 個中 0 個であった。

#### 【0077】

上記により、本発明の実施例 1 によれば、半導体チップ 11 ~ 14 における、他の半導体チップ 11 ~ 14 に隣接する辺に形成されるはんだフィレットの形成領域からはんだが溢れるのが抑制され、半導体チップ 11 ~ 14 が相互に短絡するのを防止することができる事が確認された。20

#### 【0078】

##### [実施例 2]

図 18 は、本発明の第 2 の効果を示す図であり、本発明の実施例 2 における半導体チップ間の短絡の発生頻度を示す。

実施例 2 は、実施形態 2 として図 6 および図 7 に示される第 1、第 2 のリードフレーム 101、102 と半導体チップ 11 ~ 14 のはんだ付け構造を有する。詳細には、第 1、第 2 のリードフレーム 101、102 は銅板により形成した。第 2 のリードフレーム 102 には、四つの突出部 103 を形成し、四つの半導体チップ 11 ~ 14 をそれぞれ、各突出部 103 に対応して実装した。各半導体チップ 11 ~ 14 は、10 mm 角の直方体形状を有する。隣接する半導体チップ 11 ~ 14 間それぞれの距離 (a および b 等) を 3.0 mm とした。各半導体チップ 11 ~ 14 と第 1 のリードフレーム 101 の側端 E1 ~ E4 までの距離 (c および d 等) を 1.0 mm とした。30

#### 【0079】

各半導体チップ 11 ~ 14 における、他の半導体チップ 11 ~ 14 に隣接する辺に形成するはんだフィレット (51a、51b、52a、53b 等) の長さを 1.0 mm とした。各半導体チップ 11 ~ 14 における、第 1 のリードフレーム 101 の側端 E1 ~ E4 に隣接する辺に形成するはんだフィレット (51c、51d 等) の長さを 0.3 mm とした。はんだ 50 は、シート状の Sn3Ag0.5Cu はんだを用いた。リフローは真空リフロー装置を用い、250 ピークの温度プロファイルを用いて接続した。40

#### 【0080】

比較例 2 として、下記に示す、第 1、第 2 のリードフレーム 101、102 と半導体チップ 11 ~ 14 のはんだ付け構造を作製した。

各半導体チップ 11 ~ 14 における、他の半導体チップ 11 ~ 14 に隣接する辺に形成するはんだフィレット (51a、51b、52a、53b 等) の長さを 0.3 mm とした。各半導体チップ 11 ~ 14 における、第 1 のリードフレーム 101 の側端 E1 ~ E4 に隣接する辺に形成するはんだフィレット (51c、51db 等) の長さを 0.3 mm とした。すなわち、各半導体チップ 11 ~ 14 の四つの辺に形成されるはんだフィレットの長50

さをすべて0.3mmとした。

上記以外は、すべて実施例2と同じである。

#### 【0081】

実施例2および比較例2を、それぞれ、20個作製した。実施例2と比較例2について、半導体チップ11～14間の短絡発生個数および半導体チップ11～14における、第1のリードフレーム101の側端にはんだフィレットの形成領域からはんだが溢れ出した発生個数を調べた。その結果を図18に示す。

比較例2、すなわち半導体チップ11～14の四つの辺それぞれに形成するはんだフィレットの長さを0.3mmにした実装構造では、20個中11個に、半導体チップ11～14に形成されたはんだフィレットの形成領域のいずれかから、第1のリードフレーム101の側端E1～E4のいずれかにはんだが溢れた。

10

#### 【0082】

これに対し、実施例2、すなわち、各半導体チップ11～14における、他の半導体チップ11～14に隣接する辺に形成するはんだフィレットの長さを1.0mmとし、各半導体チップ11～14における、第1のリードフレーム101の側端E1～E4に隣接する辺に形成するはんだフィレットの長さを0.3mmとした実装構造では、半導体チップ11～14に形成されたはんだフィレットの形成領域のいずれかから、第1のリードフレーム101の側端E1～E4にはんだが溢れたのは、20個中0個であった。

なお、実施例2および比較例2共に、半導体チップ11～14が相互に短絡する不具合の発生個数は0個であった。

20

#### 【0083】

上記により、本発明の実施例2によれば、各半導体チップ11～14における、第1のリードフレーム101の側端E1～E4に隣接する辺に形成されるはんだフィレットの形成領域から第1のリードフレーム101の側端E1～E4にはんだが溢れ出るのを抑制することができる。

#### 【0084】

なお、上記実施例1では、各半導体チップ11～14における、他の半導体チップ11～14に隣接する辺に形成するはんだフィレット(51a、51b、52a、53b等)の長さを0.3mmとし、各半導体チップ11～14における、第1のリードフレーム101の側端E1～E4に隣接する辺に形成するはんだフィレット(51c、51d等)の長さを1.0mmとして例示した。しかし、各はんだフィレットの長さは一例であって、各半導体チップ11～14における、他の半導体チップ11～14に隣接する辺に形成するはんだフィレット(51a、51b、52a、53b等)の長さは、0.3mmより短くしてもよいし、0.3mmより長くしてもよい。各半導体チップ11～14における他の半導体チップ11～14に隣接する二つの辺に形成するはんだフィレット(51aと51b等)の長さを、それぞれ、異なる長さとしてもよい。同様に、各半導体チップ11～14における、第1のリードフレーム101の側端E1～E4に隣接する辺に形成するはんだフィレット(51c、51d等)の長さを1.0mmより短くしてもよいし、1.0mmより長くしてもよい。各半導体チップ11～14における、第1のリードフレーム101の側端E1～E4に隣接する二つの辺に形成するはんだフィレット(51cと51d等)の長さを異なる長さとしてもよい。

30

40

#### 【0085】

上記実施例2では、各半導体チップ11～14における、他の半導体チップ11～14に隣接する辺に形成するはんだフィレット(51a、51b、52a、53b等)の長さを1.0mmとし、各半導体チップ11～14における、第1のリードフレーム101の側端E1～E4に隣接する辺に形成するはんだフィレット(51c、51d等)の長さを0.3mmとして例示した。しかし、各はんだフィレットの長さは一例であって、各半導体チップ11～14における、他の半導体チップ11～14に隣接する辺に形成するはんだフィレット(51a、51b、52a、53b等)の長さは、1.0mmより短くしてもよいし、1.0mmより長くしてもよい。各半導体チップ11～14における、他の半

50

導体チップ11～14に隣接する二つの辺に形成するはんだフィレット(51aと51b等)の長さを、それぞれ、異なる長さとしてもよい。同様に、各半導体チップ11～14における、第1のリードフレーム101の側端E1～E4に隣接する辺に形成するはんだフィレット(51c、51d等)の長さを0.3mmより短くしてもよいし、0.3mmより長くしてもよい。各半導体チップ11～14における、第1のリードフレーム101の側端に隣接する二つの辺に形成するはんだフィレット(51cと51d等)の長さを異なる長さとしてもよい。

#### 【0086】

半導体チップ11～14、21～23それぞれの各辺に形成するはんだフィレットの長さを確実に調整可能な方法として、はんだフィレットが形成される領域の周囲に、はんだ濡れを防止するためのはんだ濡れ防止構造を形成するようにしてもよい。はんだ濡れ防止構造は、例えば、ソルダレジストを塗布したり、ディンプル加工を施したり、レーザ等による酸化処理、あるいは化学的粗化処理等を施したりすることにより形成することができる。

10

#### 【0087】

上記実施形態では、半導体チップ11～14、21～23を、第1、第2のリードフレーム101、102にはんだ50、60によりはんだ付けする構造として例示した。しかし、第2のリードフレーム102を備えていない構造に適用することができる。

#### 【0088】

上記実施形態では、半導体チップ11～14、21～23が、はんだ60によりはんだ付けされる第2のリードフレーム102に、突出部103を設けた構造として例示した。しかし、第2のリードフレーム102に突出部103を形成しない構造とすることもできる。

20

#### 【0089】

上記実施形態では、半導体チップ11～14、21～23が、はんだ50、60により第1、第2のリードフレーム101、102に、はんだ付けされる構造として例示した。しかし、第1、第2のリードフレーム101、102に代えて、アルミダイキャスト等の鋳造品や、セラミック等の焼結体を用いることもできる。

#### 【0090】

上記実施形態1～7を、選択的に組み合わせてもよい。

30

その他、本発明は、発明の趣旨の範囲内において、種々、変形して適用することが可能であり、要は、第一の半導体チップの第1の辺から第二の半導体チップにおける第一の半導体チップの第1の辺に隣接する一辺までの距離の1/2の距離と、第一の半導体チップの第2の辺から第三の半導体チップにおける第一の半導体チップの第2の辺に隣接する一辺までの距離の1/2の距離と、第一の半導体チップの第3の辺または第4の辺の少なくとも一方の辺からベース板の側端までの距離とのうち、最も短い距離となる箇所の辺に形成された第一の半導体チップのはんだフィレットの長さが最も短く形成されているものであればよい。

#### 【符号の説明】

#### 【0092】

40

11～14 半導体チップ

21～23 半導体チップ

50 第1のはんだ

51a、51b、51c、51d はんだフィレット

52a、52c はんだフィレット

53a、53b はんだフィレット

60 第2のはんだ

61 はんだフィレット

100 パワーモジュール

101 第1のリードフレーム(ベース板)

50

|             |            |

|-------------|------------|

| 102         | 第2のリードフレーム |

| 102a        | 内面         |

| 102b、102c   | 凹部         |

| 103         | 突出部        |

| 111         | リード        |

| 201         | モジュールケース   |

| 304B        | フランジ       |

| 305         | フィン        |

| 307         | 放熱ベース      |

| 350         | 一次封止材      |

| 351         | 二次封止材      |

| a ~ d       | 距離         |

| E1、E2、E3、E4 | 側端         |

10

【図1】

【図1】

【図2】

【図2】

【図3】

【図4】

【図5】

【図5】

【図6】

【図6】

実施形態2

(b)

【図7】

【図8】

【図7】

実施形態2実施形態3

【図9】

【図10】

【図9】

【図10】

実施形態4実施形態5

【図11】

【図12】

【図11】

実施形態5の変形例

【図12】

実施形態6

【図13】

【図14】

【図13】

【図14】

実施形態6の変形例1実施形態6の変形例2

【図15】

【図16】

【図17】

【図18】

【図17】

【図18】

半導体チップ間の短絡発生頻度

|                   | 実施例1                           | 比較例1     |

|-------------------|--------------------------------|----------|

| フィレットの長さ          | 半導体チップ間:0.3mm<br>フレーム側端側:1.0mm | すべて0.3mm |

| ショート発生個数          | 0個/20個                         | 7個/20個   |

| フレーム側端への<br>はんだ溢れ | 0個/20個                         | 0個/20個   |

フレーム側端へのはんだ溢れ発生頻度

|                   | 実施例2                           | 比較例2     |

|-------------------|--------------------------------|----------|

| フィレットの長さ          | 半導体チップ間:1.0mm<br>フレーム側端側:0.3mm | すべて0.3mm |

| ショート発生個数          | 0個/20個                         | 0個/20個   |

| フレーム側端への<br>はんだ溢れ | 0個/20個                         | 11個/20個  |

---

フロントページの続き

審査官 多賀 和宏

(56)参考文献 特開2013-069825(JP,A)

特開2002-176128(JP,A)

特開2014-078739(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/07

H01L 21/60

H01L 23/48

H01L 25/18