#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2013/043602 A2

(43) International Publication Date 28 March 2013 (28.03.2013)

(51) International Patent Classification: G11C 16/10 (2006.01) G11C 5/06 (2006.01) G11C 11/56 (2006.01)

(21) International Application Number:

PCT/US2012/055919

(22) International Filing Date:

18 September 2012 (18.09.2012)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/536,555 19 September 2011 (19.09.2011)

IIC

- (71) Applicant (for all designated States except US): SANDISK TECHNOLOGIES, INC. [US/US]; Two Legacy Town Center, 6900 North Dallas Parkway, Plano, TX 75024 (US).

- (72) Inventors; and

- (71) Applicants (for US only): CHEN, Jian [US/US]; 601 Mc-Carthy Boulevard, Milpitas, CA 95035 (US).

GOROBETS, Sergei [GB/GB]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). SPROUSE, Steven [US/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). KUO, Tien-chien [—/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). LI, Yan [US/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). LEE, Seungpil [KR/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). MAK, Alex [US/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). DUTTA, Deepanshu [IN/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). HIGASHITANI, Masaaki [JP/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US).

- US (74) Agent: MAGEN, Burt; Vierra Magen Marcus & Deniro, LLP, 575 Market Street, Suite 2500, San Francisco, CA 94105 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT,

[Continued on next page]

(54) Title: HIGH ENDURANCE NON-VOLATILE STORAGE

# Fig. 24

(57) Abstract: A non-volatile storage system is disclosed that includes non-volatile memory cells designed for high endurance and lower retention than other non-volatile memory cells.

#

HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

without international search report and to be republished upon receipt of that report (Rule 48.2(g))

-1-

#### HIGH ENDURANCE NON-VOLATILE STORAGE

[0001] This patent application claims priority to U.S. Provisional Application 61/536,555, "High Endurance Non-Volatile Storage," filed on September 19, 2011.

# **BACKGROUND OF THE INVENTION**

# Field of the Invention

[0002] The present invention relates to technology for non-volatile storage.

# Description of the Related Art

[0003] Semiconductor memory devices have become more popular for use in various electronic devices. For example, non-volatile semiconductor memory is used in cellular telephones, digital cameras, personal digital assistants, mobile computing devices, non-mobile computing devices and other devices. Electrical Erasable Programmable Read Only Memory (EEPROM) and flash memory are among the most popular non-volatile semiconductor memories.

[0004] Both EEPROM and flash memory utilize a floating gate that is positioned above and insulated from a channel region in a semiconductor substrate. The floating gate is positioned above a channel region and between source and drain regions. The floating gate is separated from the channel region by a layer of a dielectric. A control gate is provided over and insulated from the floating gate. The threshold voltage of the transistor is controlled by the amount of charge that is retained on the floating gate. That is, the minimum amount of voltage that must be applied to the control gate before the transistor is turned on to permit conduction between its source and drain is controlled by the level of charge on the floating gate.

-2-

[0005] When programming an EEPROM or flash memory device, typically a program voltage is applied to the control gate and the bit line is grounded. Electrons (charge) from the channel are injected into the floating gate. When electrons accumulate in the floating gate, the floating gate becomes negatively charged and the threshold voltage of the memory cell is raised so that the memory cell is in the programmed state. More information about programming can be found in U.S. Patent 6,859,397, titled "Source Side Self Boosting Technique For Non-Volatile Memory;" and U.S. Patent 6,917,542, titled "Detecting Over Programmed Memory," both patents are incorporated herein by reference in their entirety.

[0006] Some EEPROM and flash memory devices have a floating gate that is used to store two ranges of charges and, therefore, the memory cell can be programmed/erased between two states, an erased state and a programmed state that correspond to data "1" and data "0." Such a device is referred to as a binary or two-state device.

[0007] A multi-state flash memory device is implemented by identifying multiple, distinct allowed threshold voltage ranges. Each distinct threshold voltage range corresponds to a predetermined value for the set of data bits. The specific relationship between the data programmed into the memory cell and the threshold voltage ranges of the memory cell depends upon the data encoding scheme adopted for the memory cells. For example, U.S. Patent No. 6,222,762 and U.S. Patent Application Publication No. 2004/0255090, both of which are incorporated herein by reference in their entirety, describe various data encoding schemes for multi-state flash memory cells.

[0008] Some issues faced by non-volatile storage, including flash memory, include data retention and endurance. Data retention refers to how long data will remain stored accurately in the memory device. A memory device with long data retention will maintain data stored in an accurate manner

-3-

for a long time (e.g., 10 years). A memory device with shorter data retention will maintain data stored in an accurate manner for a shorter times, such as weeks or months (or other time period).

[0009] Endurance refers to the ability to continue operating accurately after many cycles of writing and erasing (or re-writing). A memory device with high endurance will continue to operate effectively after tens of thousands of cycles. A memory device with low endurance can only be written hundreds (or in some cases thousands) of times before the device starts to suffer a degradation in performance.

# BRIEF DESCRIPTION OF THE DRAWINGS

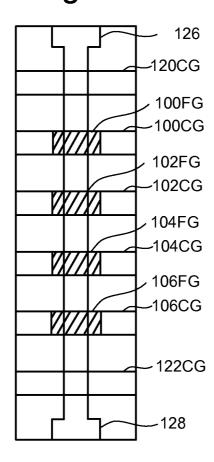

[0010] Figure 1 is a top view of a NAND string.

[0011] Figure 2 is an equivalent circuit diagram of the NAND string.

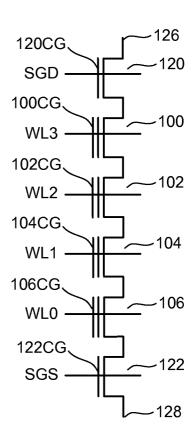

[0012] Figure 3 depicts a cross section of a memory cell.

[0013] Figure 4 depicts a cross section of a memory cell.

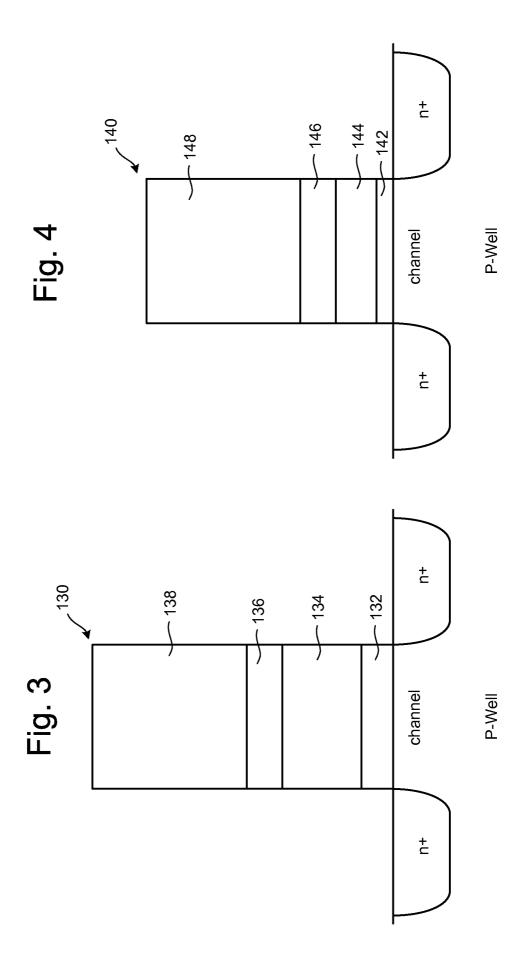

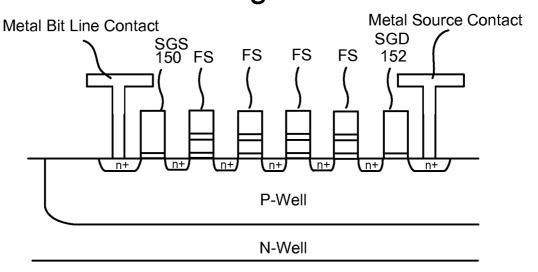

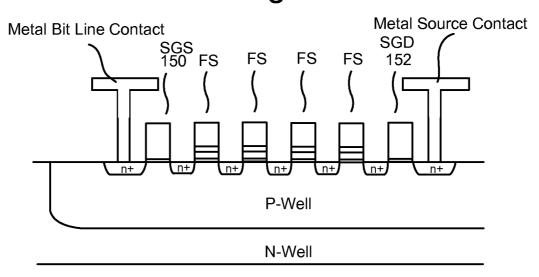

[0014] Figure 5 depicts a cross section of a NAND string.

[0015] Figure 6 depicts a cross section of a NAND string.

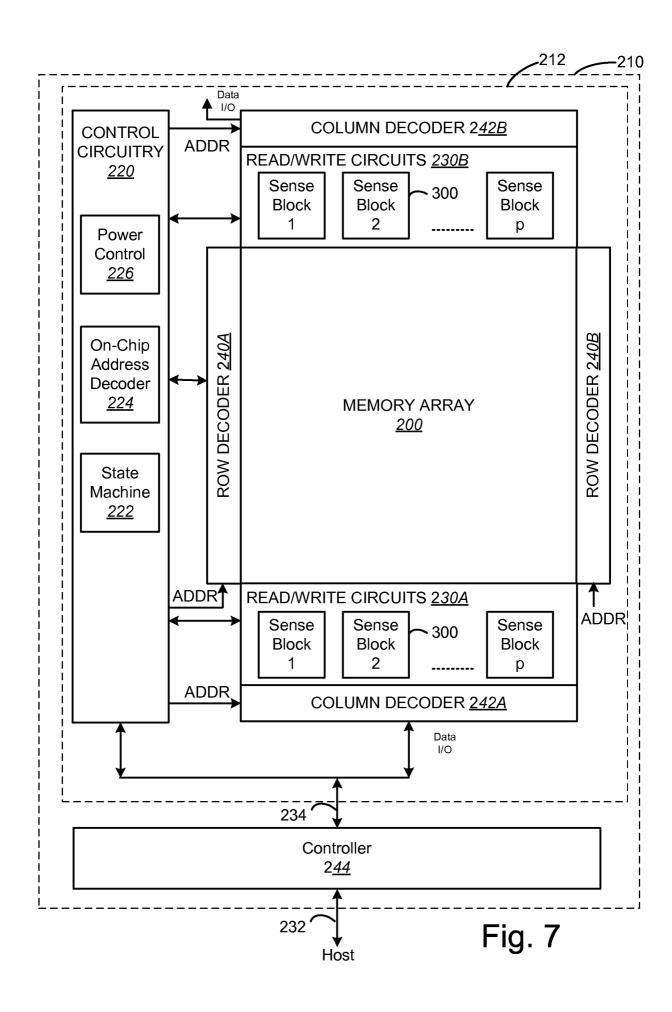

[0016] Figure 7 is a block diagram of a non-volatile memory system.

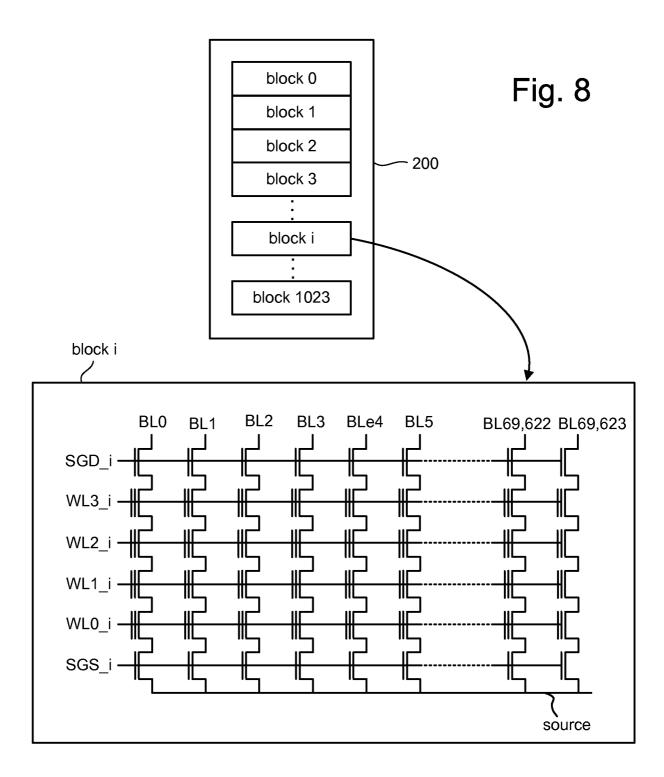

[0017] Figure 8 is a block diagram depicting one embodiment of a memory array.

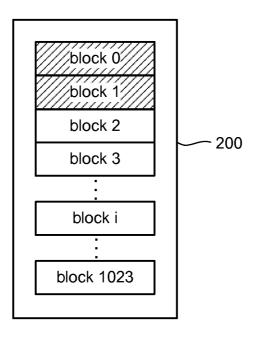

[0018] Figure 9 is a block diagram depicting one embodiment of a memory array.

[0019] Figure 10 is a block diagram depicting one embodiment of a memory array.

[0020] Figure 11 is a block diagram depicting one example organization of a memory system.

[0021] Figure 12 is a block diagram depicting one example organization of a memory system.

**[0022]** Figure 13 is a block diagram depicting one example organization of a memory system.

[0023] Figure 14 is a block diagram depicting one example organization of a memory system.

[0024] Figure 15 is a block diagram depicting one embodiment of a sense block.

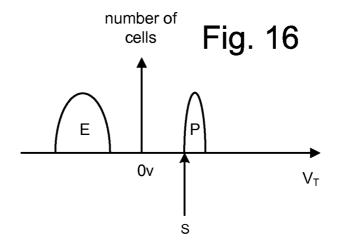

[0025] Figure 16 depicts threshold voltage distributions for binary memory.

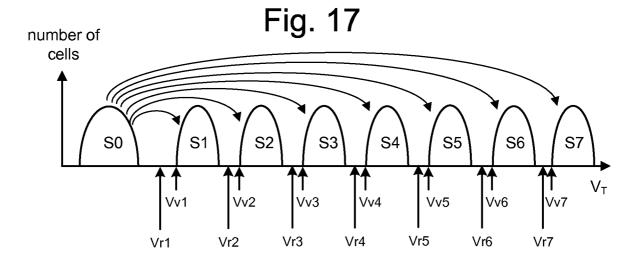

[0026] Figure 17 depicts threshold voltage distributions for multi-state memory, and depicts one example process for programming.

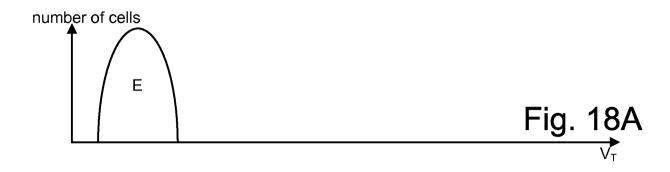

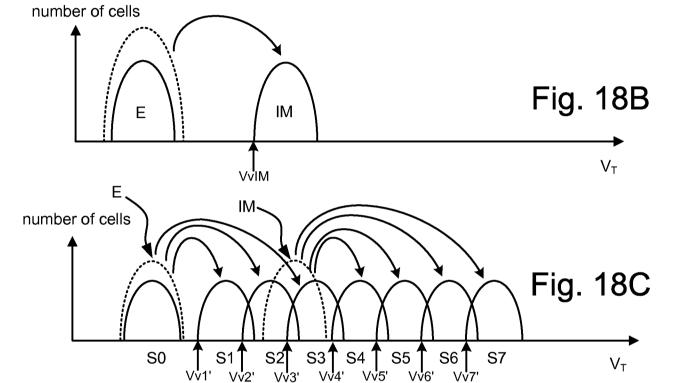

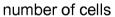

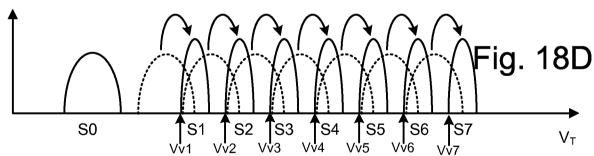

[0027] Figures 18A-E depict threshold voltage distributions for multi-state memory, and depict one example process for programming.

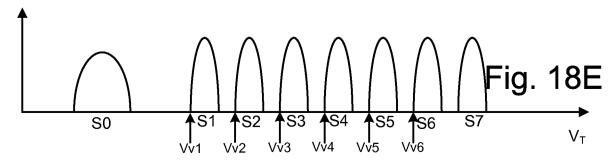

**[0028]** Figure 19 is a flow chart describing one embodiment of a process for operating non-volatile memory.

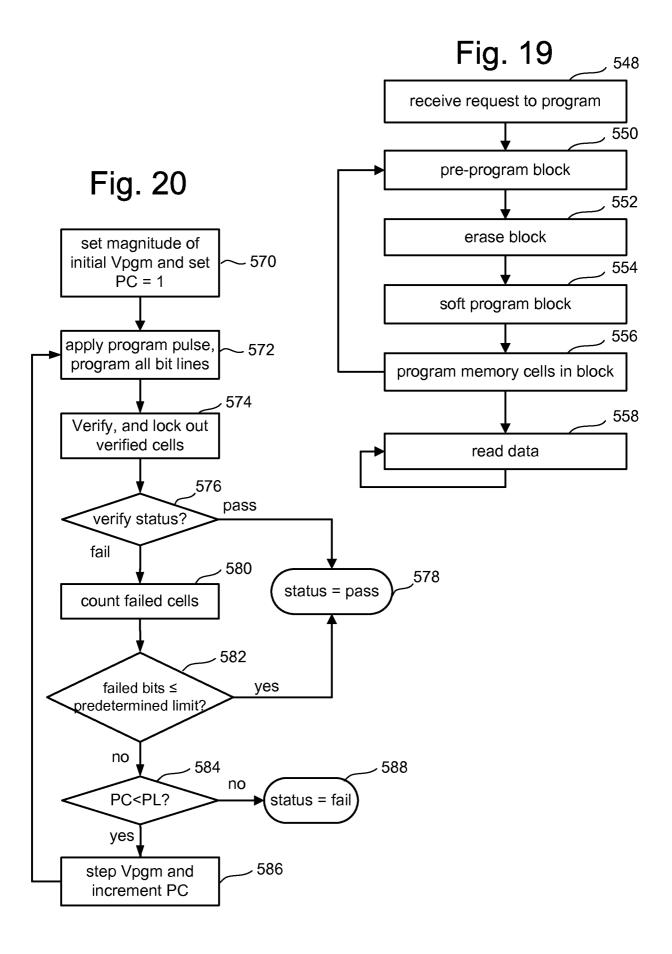

[0029] Figure 20 is a flow chart describing one embodiment of a process for programming non-volatile memory.

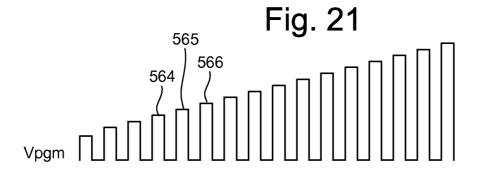

[0030] Figure 21 depicts one example of a programming signal that comprises programming pulses.

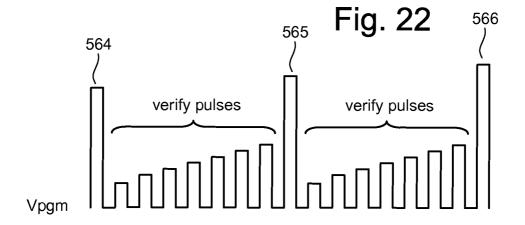

- [0031] Figure 22 depicts three programming pulses, and the verify pulses applied between the programming pulses.

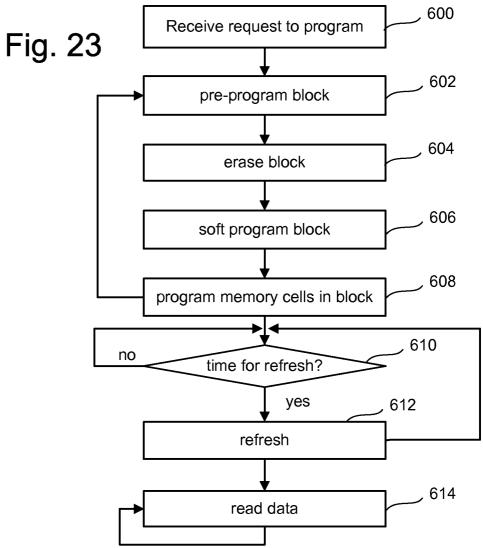

- [0032] Figure 23 is a flow chart describing one embodiment of a process for operating non-volatile memory.

- [0033] Figure 24 is a flow chart describing one embodiment of a process for programming non-volatile memory.

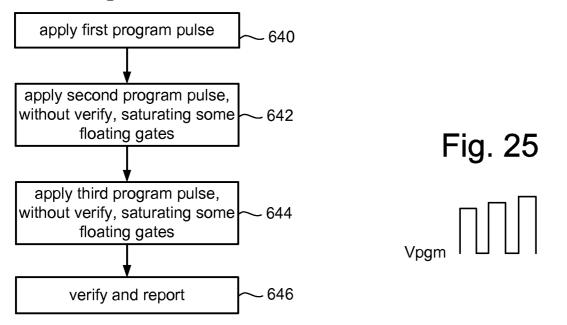

- [0034] Figure 25 depicts one example of a programming signal that comprises programming pulses.

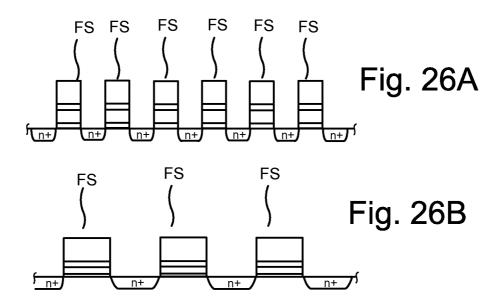

- [0035] Figure 26A shows a cross section of a portion of a NAND string.

- [0036] Figure 26B shows a cross section of a portion of a NAND string.

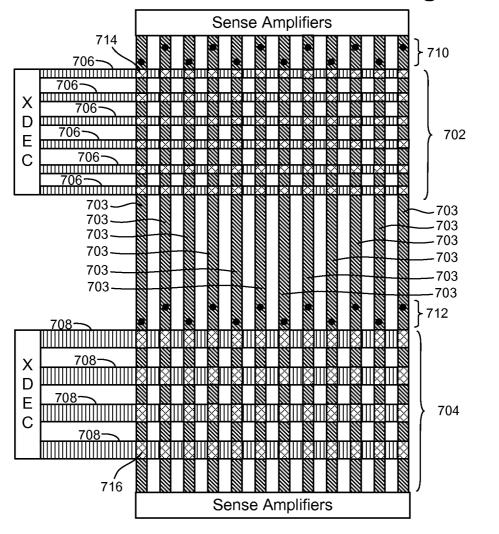

- [0037] Figure 26C shows a top view of a portion of two blocks of NAND flash memory on the same chip and in the same array, such that the two blocks have different physical characteristics.

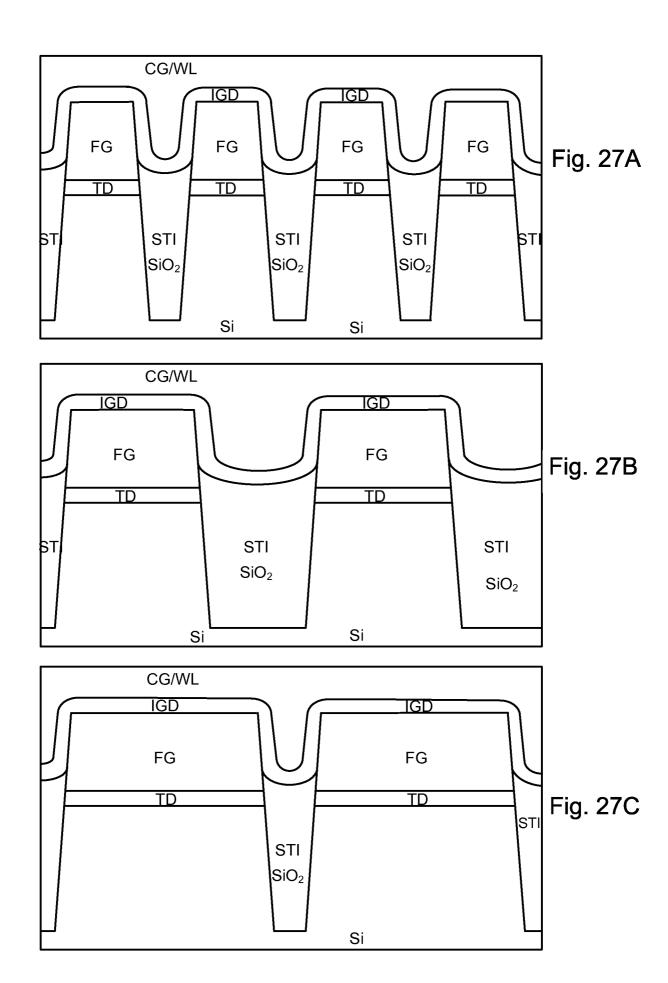

- [0038] Figure 27A shows a cross section of a memory array along the word line.

- [0039] Figure 27B shows a cross section of a memory array along the word line.

- [0040] Figure 27C shows a cross section of a memory array along the word line.

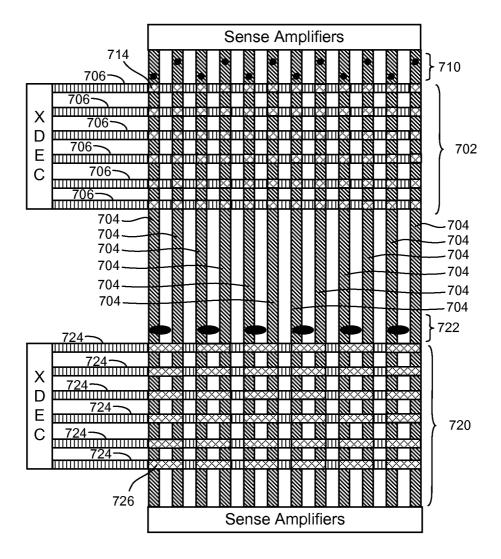

- [0041] Figure 27D shows a top view of a portion of two blocks of NAND flash memory on the same chip and in the same array, such that the two blocks have different physical characteristics.

-6-

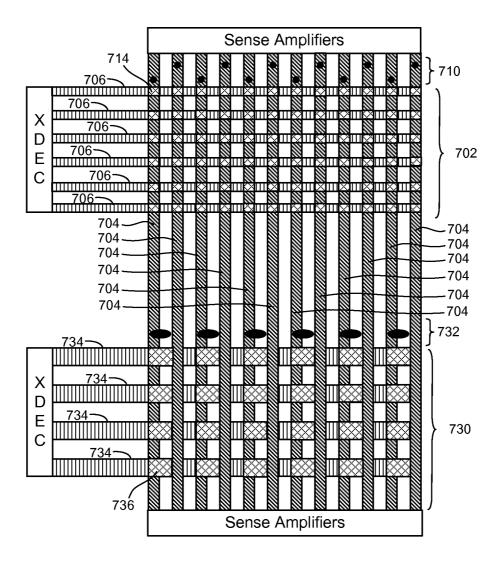

[0042] Figure 28 shows a top view of a portion of two blocks of NAND flash memory on the same chip and in the same array, such that the two blocks have different physical characteristics.

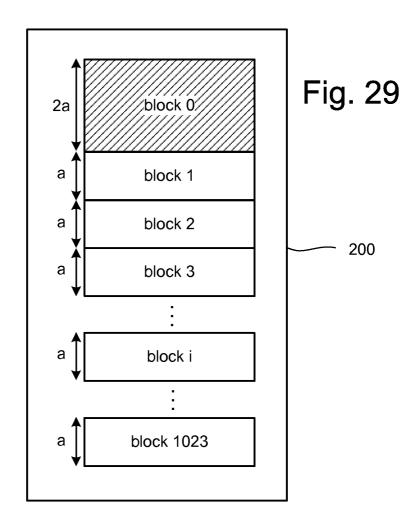

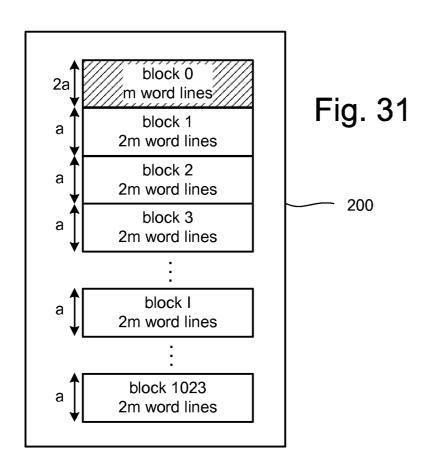

- [0043] Figure 29 shows an example organization of a memory array.

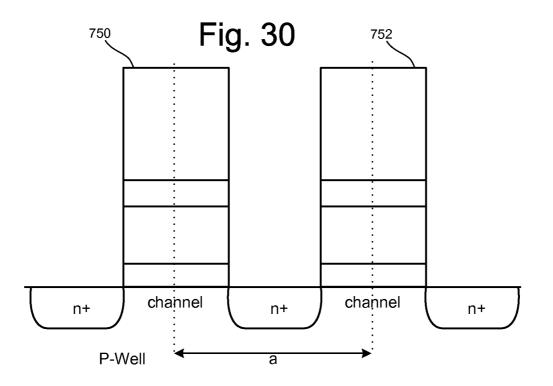

- [0044] Figure 30 shows a cross section of a portion of a NAND string.

- [0045] Figure 31 shows an example organization of a memory array.

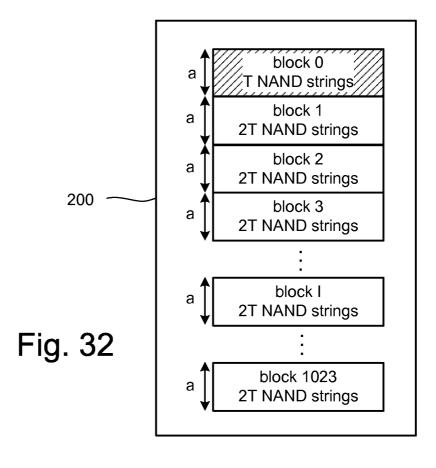

- [0046] Figure 32 shows an example organization of a memory array.

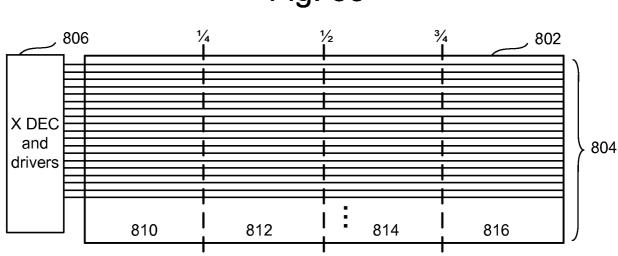

- [0047] Figure 33 shows a portion of a memory array with decoders and drivers.

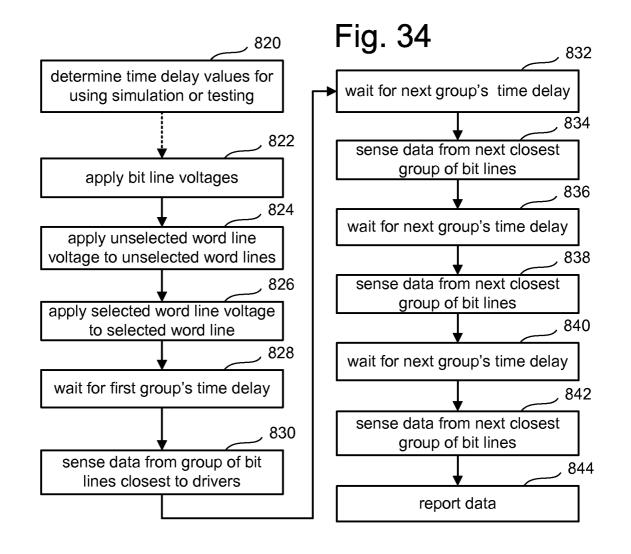

- [0048] Figure 34 is a flow chart describing one embodiment of a process for reading non-volatile storage.

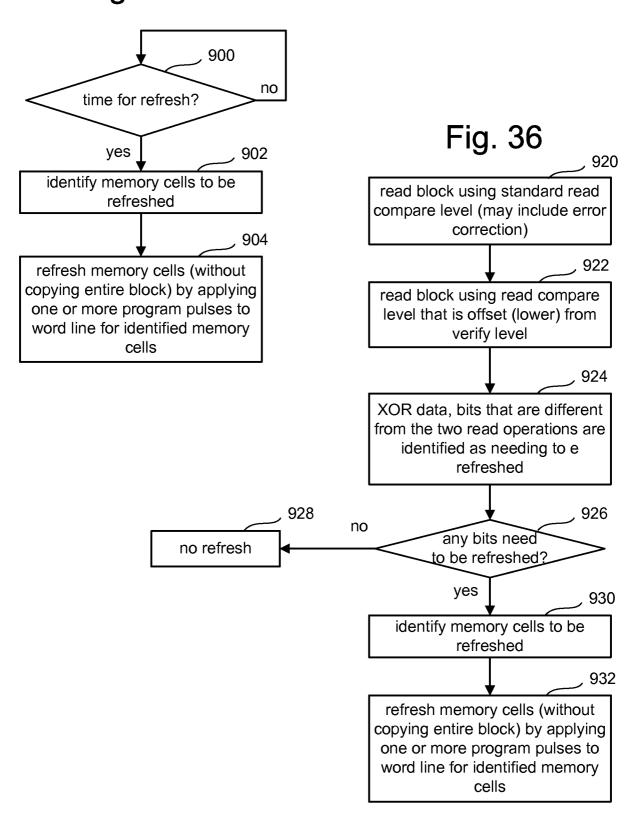

- [0049] Figure 35 is a flow chart describing one embodiment of a process for managing refresh for high endurance low retention memory cells.

- **[0050]** Figure 36 is a flow chart describing one embodiment of a process for managing refresh operations.

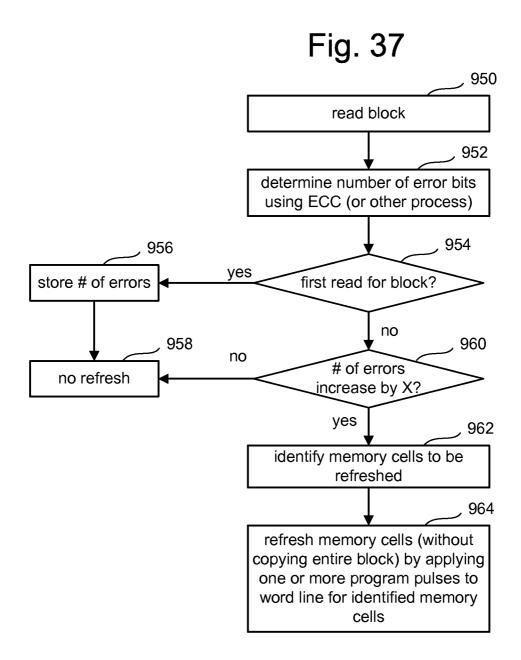

- [0051] Figure 37 is a flow chart describing one embodiment of a process for managing refresh operations.

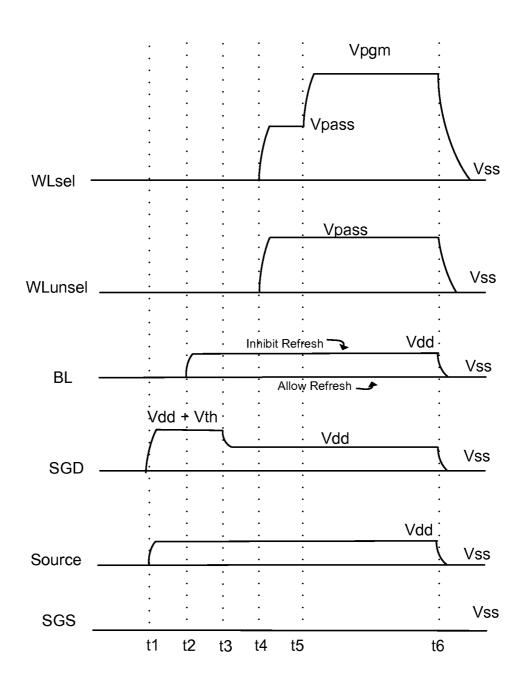

- [0052] Figure 38 is a timing diagram showing voltage plotted against time for various signals.

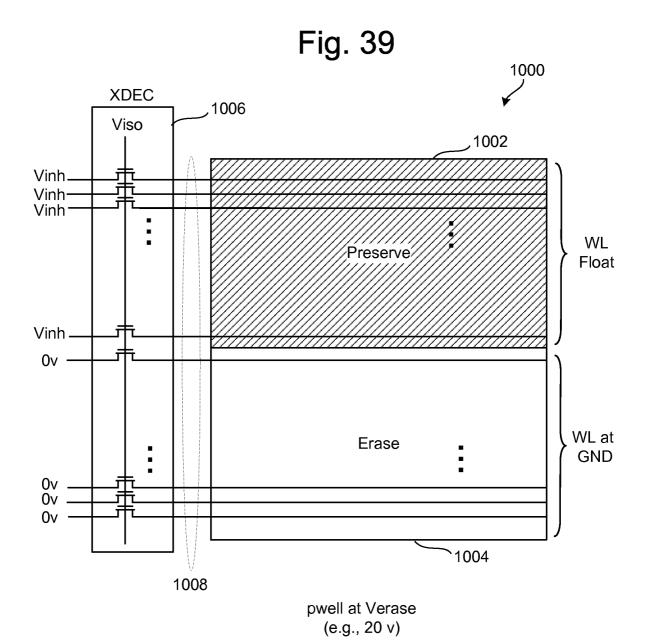

- [0053] Figure 39 is a block diagram depicting a portion of a memory array and word line decoder and drivers.

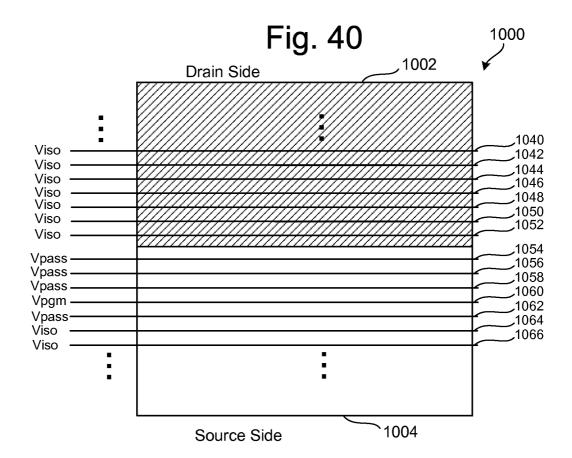

- [0054] Figure 40 is a block diagram depicting a portion of a memory array.

-7-

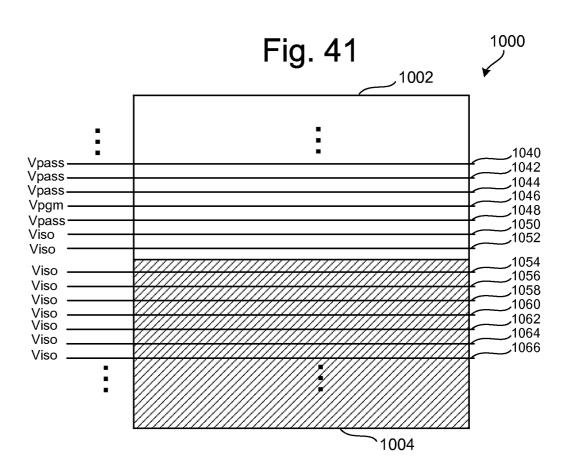

[0055] Figure 41 is a block diagram depicting a portion of a memory array.

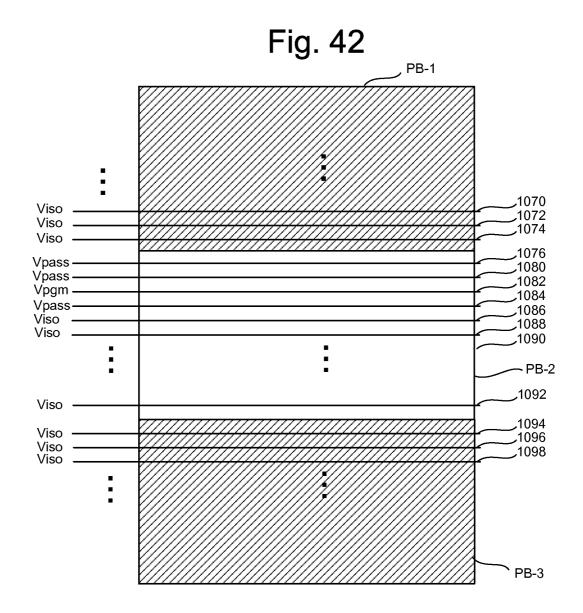

[0056] Figure 42 is a block diagram depicting a portion of a memory array.

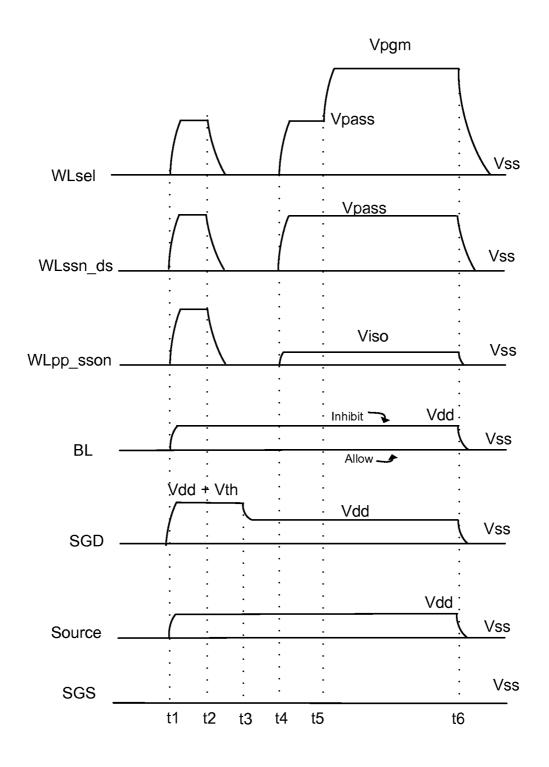

[0057] Figure 43 is a timing diagram showing voltage plotted against time for various signals.

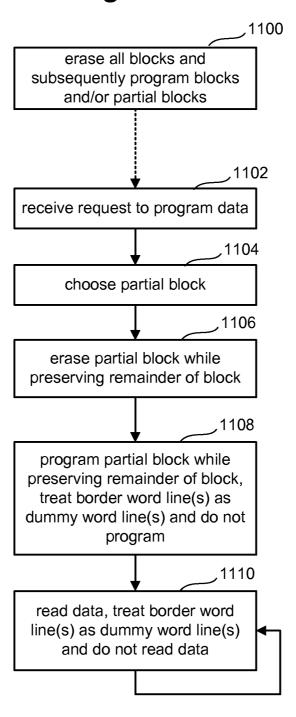

[0058] Figure 44 is a flow chart describing one embodiment of the operation of partial block erasing and programming.

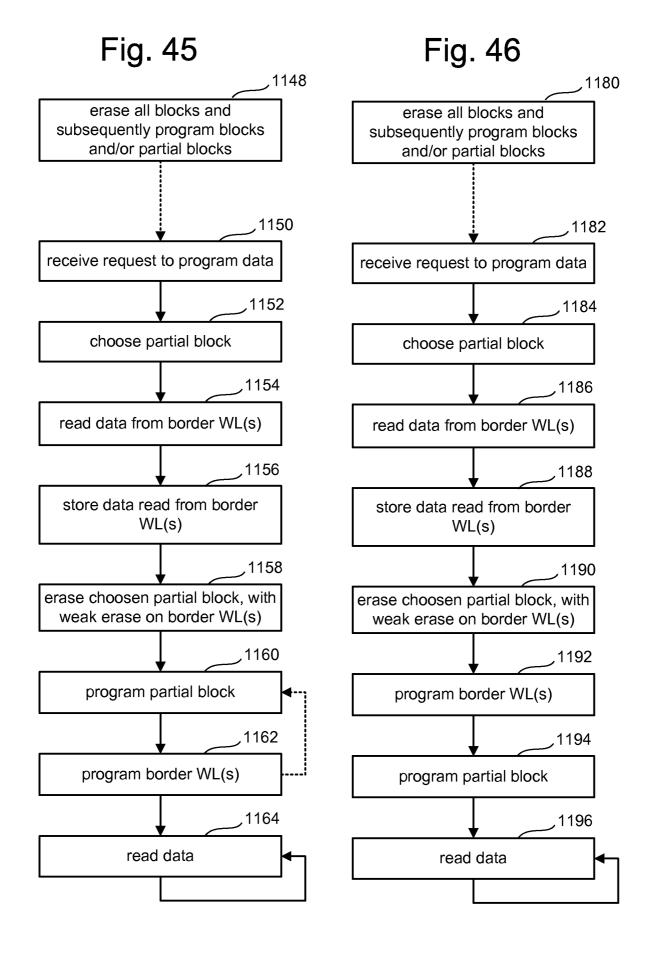

**[0059]** Figures 45 and 46 are flow charts depicting two embodiments of processes that perform partial memory erase/programming, including reading out the border word lines prior to such an operation.

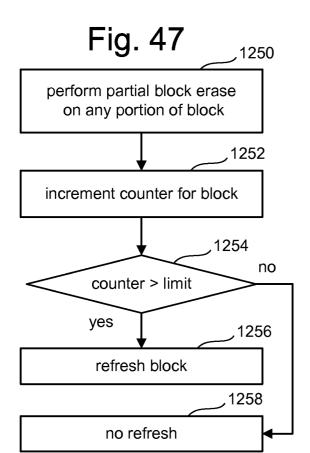

**[0060]** Figures 47 and 48 are flowcharts that describe two embodiments of processes for determining whether it is time to refresh a block for systems that use partial block erase.

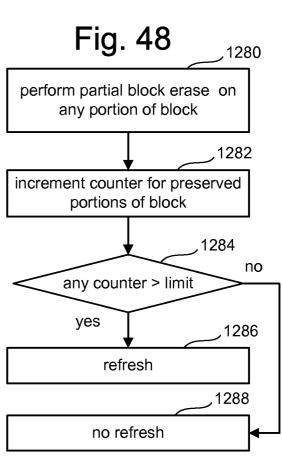

[0061] Figure 49 is a block diagram that shows one example computing system that can include High Endurance Short Retention memory cells and/or Low Endurance Long Retention memory cells.

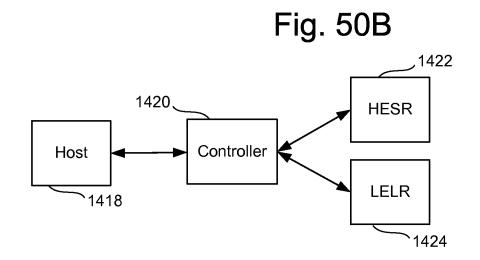

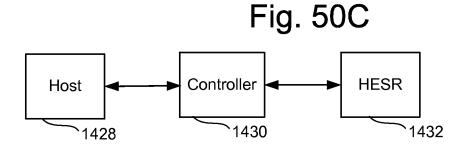

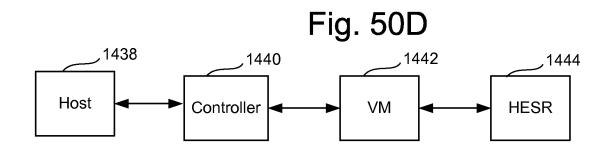

[0062] Figures 50A-D are block diagrams depicting various embodiments for configuring High Endurance Short Retention memory and Low Endurance Long Retention memory.

# **DETAILED DESCRIPTION**

[0063] In many circumstances, designing memory can require compromises. For example, some memory devices may be optimized for long

data retention at the expense of lower endurance (referred to as Low Endurance Long Retention memory) while other memory devices may be optimized for high endurance at the expense of shorter data retention (referred to as High Endurance Short Retention memory). Many non-volatile memory systems commercially available are Low Endurance Long Retention memory devices that are designed so that they will maintain the user's data for a long time. To guarantee the long data retention, certain design decisions are made for the memory devices that result in slower performance and lower data density.

[0064] There are uses and circumstances where data does not need to persist for many years, therefore, using memory devices with long data retention in those situations may not be necessary, such as when used in a Cache system. Technology is proposed herein for a High Endurance Short Retention non-volatile memory that is optimized for high performance, with the understanding that data retention will not be as long as other non-volatile memory. In traditional flash memory, the data retention is in the range of 10 years to at least 1 year, while the traditional DRAM have data retention of a few milliseconds. The proposed technology introduce a class of memory that have data retention in between of these two extremes.

# Saturated Memory Cell

[0065] One embodiment of a High Endurance Short Retention non-volatile memory includes memory cells with smaller floating gates. For example, the floating gates may be shorter or thinner. By having a smaller floating gate, the floating gate will be able to absorb a smaller amount of charge during program operations.

[0066] Traditionally, smaller floating gates are avoided because limiting the charge on the floating gate will limit the increase in threshold voltage that can be achieved during programming. To increase memory density, many

-9-

non-volatile storage systems implement multi-state memory devices. By having each memory cell store multiple bits of data, more data is stored per unit area of substrate. To store multiple bits of data, the memory cell needs to be able to implement multiple, distinct allowed threshold voltage ranges, which requires that the threshold voltage can be raised to a significantly high voltage. Therefore, in one embodiment, the proposed High Endurance Short Retention memory cell will have a smaller floating gate and store binary data (two states – erased and programmed). As the memory cells is only storing binary data (as opposed to multi-state data), there is no need for the higher threshold voltages required by multi-state data. Since programming will only raise the threshold voltage by a smaller amount than multi-state memory cells, the time needed for programming will decrease.

[0067] One property of a smaller floating gate is that it will saturate at a lower amount of charge than a larger floating gate. This is a property that has not been acceptable for multi-state memory cells as they need to implement multiple narrow threshold voltage distributions. However, the High Endurance Short Retention memory cell storing binary data can take advantage of the lower saturation level.

[0068] In many embodiments, the program voltage is applied to the word line as a series of pulses, with each successive pulse being higher in magnitude than a previous pulse by a step size. Between each pulse, a set of one or more verify operations are performed to determine whether the programming has completed by testing whether the memory cells are in the appropriate data states. However, it is proposed to further shorten the time needed for programming by applying a small number of programming pulses without all or some of the intervening verify operations. The magnitude and width of the programming pulses are designed such that after the programming pulses all, almost all, or a large percentage of the memory cells being programmed have their floating gate saturated with electrons. That is, the amount of

programming applied to the selected memory cells is more than needed to move the threshold voltage to the programmed state. Therefore, many memory cells will have the amount of charge on the floating gate reach a saturation point before programming is completed. This results in a narrow threshold voltage distribution and allows for the programming to be performed without verifying between programming pulses. In some embodiments, a verification operation can be performed after all of the programming pulses have been applied to insure that the data was written correctly. Note that because the floating gates reach saturation, over programming is not a problem.

[0069] In one embodiment, rather than using a smaller floating gate, nanodots can be used in the floating gate to limit the amount of charge that is added to the floating gate during programming. More information about nanodots can be found in U.S. Patent Application 2009/0155967, "Method of Forming Memory With Floating Gates Including Self-Aligned Metal Nanodots Using a Coupling Layer," filed on December 18, 2007 and U.S. Patent Application 2011/0020992, "Integrated Nonostructure-Based Non-Volatile Memory Fabrication," filed on July 20, 2010; and U.S. Patent Application, both of which are incorporated herein by reference in their entirety.

[0070] In one embodiment, the High Endurance Short Retention memory cell storing binary data can also utilize a thinner dielectric between the floating gate and the channel area. The thinner dielectric allows the programming operation to proceed quicker, as it is easier for charge to pass through the dielectric to the floating gate. The thinner dielectric and the thinner floating gate also allow for lower program voltages to be used, which saves power. The smaller dielectric and smaller floating gate will also result in a smaller memory cell (which reduces area per memory cell).

[0071] One example of a non-volatile storage system that can implement the technology described herein is a flash memory system that uses the NAND

structure, which includes arranging multiple transistors in series, sandwiched between two select gates. The transistors in series and the select gates are referred to as a NAND string. Figure 1 is a top view showing one NAND string. Figure 2 is an equivalent circuit thereof. The NAND string depicted in Figures 1 and 2 includes four transistors 100, 102, 104 and 106 in series and sandwiched between (drain side) select gate 120 and (source side) select gate 122. Select gate 120 connects the NAND string to a bit line via bit line contact 126. Select gate 122 connects the NAND string to source line 128. Select gate 120 is controlled by applying the appropriate voltages to select line SGD. Select gate 122 is controlled by applying the appropriate voltages to select line SGS. Each of the transistors 100, 102, 104 and 106 has a control gate and a floating gate. For example, transistor 100 has control gate 100CG and floating gate 100FG. Transistor 102 includes control gate 102CG and a floating gate 102FG. Transistor 104 includes control gate 104CG and floating gate 104FG. Transistor 106 includes a control gate 106CG and a floating gate 106FG. Control gate 100CG is connected to word line WL3, control gate 102CG is connected to word line WL2, control gate 104CG is connected to word line WL1, and control gate 106CG is connected to word line WL0.

[0072] Note that although Figures 1 and 2 show four memory cells in the NAND string, the use of four memory cells is only provided as an example. A NAND string can have less than four memory cells or more than four memory cells. For example, some NAND strings will include eight memory cells, 16 memory cells, 32 memory cells, 64 memory cells, 128 memory cells, etc. The discussion herein is not limited to any particular number of memory cells in a NAND string. One embodiment uses NAND strings with 66 memory cells, where 64 memory cells are used to store data and two of the memory cells are referred to as dummy memory cells because they do not store data.

[0073] A typical architecture for a flash memory system using a NAND structure will include several NAND strings. Each NAND string is connected

to the common source line by its source select gate controlled by select line SGS and connected to its associated bit line by its drain select gate controlled by select line SGD. Each bit line and the respective NAND string(s) that are connected to that bit line via a bit line contact comprise the columns of the array of memory cells. Bit lines are shared with multiple NAND strings. Typically, the bit line runs on top of the NAND strings in a direction perpendicular to the word lines and is connected to a sense amplifier.

[0074] Relevant examples of NAND type flash memories and their operation are provided in the following U.S. Patents/Patent Applications, all of which are incorporated herein by reference in their entirety: U.S. Pat. No. 5,570,315; U.S. Pat. No. 5,774,397; U.S. Pat. No. 6,046,935; U.S. Pat. No. 6,456,528; and U.S. Pat. Publication No. US2003/0002348.

Figure 3 is a cross section of one embodiment of a memory cell [0075] 130 on a NAND string (e.g., such as any of the memory cells depicted in Figures 1 and 2). In some embodiments, the memory system is implemented on a p type of substrate. Within the p substrate will be an n-well. Within the n-well are one or more p-wells. The NAND strings are implemented in the pwells Figure 3 shows a p-well, but does not show the n-well or underlying p substrate. N+ diffusion regions, serving as the source and drain, are located in the p-well. The area in the p-well between the N+ diffusion regions is the channel. Above the channel is a dielectric layer 132, which in one embodiment is SiO<sub>2</sub>. In one example, dielectric layer 132 is 8 nm thick. programming and erasing is performed by moving elections through dielectric layer 132 (e.g., on and off the floating gate), dielectric layer 132 is often referred to as the tunnel dielectric or tunnel oxide. Above dielectric layer 132 is the floating gate 134, which in one embodiment is polysilicon. In one example, floating gate 134 is 85 nm. Above floating gate 134 is inter-gate dielectric layer 136, which in one embodiment is SiO<sub>2</sub>. In one example, intergate dielectric layer 136 is 14 nm thick. Above inter-gate dielectric layer 136

is control gate 138, which in one embodiment is polysilicon and/or a metal (can be the same metal as the word line).

[0076] Figure 4 is a cross section of another embodiment of a memory cell 140 on a NAND string (e.g., such as any of the memory cells depicted in Figures 1 and 2). In one example implementation, the memory cell of Figure 3 a Low Endurance Long Retention memory cell that will store multi-state data and the memory cell of Figure 4 is a High Endurance Short Retention memory that will store binary data. In various embodiments, the memory cells of Figure 3 and Figure 4 can be implemented in the same memory array or in different arrays in same memory system. In other embodiments, a memory system may only have memory cells according to Figure 3 or only have memory cells according to Figure 4.

Figure 4 depicts the proposed High Endurance Short Retention [0077] memory cell that has a smaller floating gate and stores binary data (two states - erased and programmed). As in Figure 3, the memory cell is implemented in a p-well, within an n-well that is in a p type substrate. N+ diffusion regions, serving as the source and drain, are located in the p-well. The area in the pwell between the N+ diffusion regions is the channel. Above the channel is a dielectric layer 142, which in one embodiment is SiO<sub>2</sub>. In one example, dielectric layer 142 is 5 nm thick. Above dielectric layer 142 is the floating gate 144, which in one embodiment is polysilicon. In one example, the floating gate 144 is 40 nm thick (height). Above floating gate 144 is inter-gate dielectric layer 146, which in one embodiment is SiO<sub>2</sub>. In on example, intergate dielectric layer 146 is 10 nm thick. Above inter-gate dielectric layer 146 is a control gate 148, which in one embodiment is polysilicon and/or a metal (can be the same metal as the word line). As described above, the High Endurance Short Retention memory cell 140 of Figure 4 (storing binary data) has a thinner (e.g. shorter) floating gate and thinner tunnel dielectric than the Low Endurance Long Retention memory cell 130 of Figure 3 (storing multi-

-14-

state data). Because memory cell 140 has a thinner floating gate and thinner tunnel dielectric, the overall height of memory cell 140 is shorter than the overall height of memory cell 130.

[0078] With such structures that have a much thinner tunnel oxide, the program voltage Vpgm can be significantly reduced, resulting in lower voltage required in the area of the circuit, as well as the charge pumps required for such memory chips. Due to the lower voltages needed to program and erase the new memory cell, cell structure with less aspect ratio is acceptable and making manufacturing process significantly easier and cheaper. Further due to the lower programming voltage needed to program such a memory cell, the field between adjacent wordlines is also reduced, resulting in less breakdown and high reliability characteristics.

[0079] Figure 5 is a cross section of a NAND string having memory cells according to the structure of Figure 3 - Low Endurance Long Retention. Figure 6 is a cross section of a NAND string having memory cells according to the structure of Figure 4 - High Endurance Short Retention. Both Figures 4 and 5 show the NAND strings implemented in p-wells, within n-wells, within the p substrate. N+ diffusion regions, serving as the sources and drains, are located in the p-well. Figures 5 and 6 show the Bit Line Contacts, Metal Source Line Contacts, the source selection lines (SGS 150) and the drain selection lines (SGD 152). Each of the memory cells include a floating gate stack (FS), that comprises a tunnel dielectric, floating gate, inter-gate dielectric and control gate. As can be seen, the floating gates of Figure 6 are thinner than the floating gates of Figure 5. Additionally, the tunnel dielectrics of Figure 6 are thinner than tunnel dielectrics of Figure 5.

[0080] The embodiments of Figures 5 and 6 assume that within a NAND string, all of the memory cells are the Low Endurance Long Retention memory cells of Figure 3 or all of the memory cells are the High Endurance Short

Retention memory cells of Figure 4. In some implementations, a memory will have both NAND strings of the type depicted in Figure 5 and NAND strings of the type depicted in Figure 6. In some embodiments, a given NAND strings may be mixed such that it includes some memory calls that are the Low Endurance Long Retention memory cells of Figure 3 and some memory cells are the High Endurance Short Retention memory cells of Figure 4.

[0081] Other types of non-volatile storage devices, in addition to NAND flash memory, can also be used to implement a suitable memory system. For example, a TANOS structure (consisting of a stacked layer of TaN-Al<sub>2</sub>O<sub>3</sub>-SiN-SiO<sub>2</sub> on a silicon substrate), which is basically a memory cell using trapping of charge in a nitride layer (instead of a floating gate), can also be used with the technology described herein. Another type of memory cell useful in flash EEPROM systems utilizes a non-conductive dielectric material in place of a conductive floating gate to store charge in a non-volatile manner. Such a cell is described in an article by Chan et al., "A True Single-Transistor Oxide-Nitride-Oxide EEPROM Device," IEEE Electron Device Letters, Vol. EDL-8, No. 3, March 1987, pp. 93-95. A triple layer dielectric formed of silicon oxide, silicon nitride and silicon oxide ("ONO") is sandwiched between a conductive control gate and a surface of a semi-conductive substrate above the memory cell channel. The cell is programmed by injecting electrons from the cell channel into the nitride, where they are trapped and stored in a limited region. This stored charge then changes the threshold voltage of a portion of the channel of the cell in a manner that is detectable. The cell is erased by injecting hot holes into the nitride. See also Nozaki et al., "A 1-Mb EEPROM with MONOS Memory Cell for Semiconductor Disk Application," IEEE Journal of Solid-State Circuits, Vol. 26, No. 4, April 1991, pp. 497-501, which describes a similar cell in a split-gate configuration where a doped polysilicon gate extends over a portion of the memory cell channel to form a separate select transistor.

[0082] Another example is described by Eitan et al., "NROM: A Novel Localized Trapping, 2-Bit Nonvolatile Memory Cell," IEEE Electron Device Letters, vol. 21, no. 11, November 2000, pp. 543-545. An ONO dielectric layer extends across the channel between source and drain diffusions. The charge for one data bit is localized in the dielectric layer adjacent to the drain, and the charge for the other data bit is localized in the dielectric layer adjacent to the source. United States patents Nos. 5,768,192 and 6,011,725 disclose a non-volatile memory cell having a trapping dielectric sandwiched between two silicon dioxide layers. Multi-state data storage is implemented by separately reading the binary states of the spatially separated charge storage regions within the dielectric. Other types of non-volatile memory technologies can also be used.

100831 Figure 7 is a block diagram of a memory device 210 that can include the memory cells discussed above. Memory device 210 includes read/write circuits for reading and programming a page of memory cells (e.g., NAND multi-state flash memory) in parallel. Memory device 210 may include one or more memory die or chips 212. Memory die/chip 212 includes an array (two-dimensional or three dimensional) of memory cells 200, control circuitry 220, and read/write circuits 230A and 230B. In one embodiment, access to the memory array 200 by the various peripheral circuits is implemented in a symmetric fashion, on opposite sides of the array, so that the densities of access lines and circuitry on each side are reduced by half. The read/write circuits 230A and 230B include multiple sense blocks 300 which allow a page of memory cells to be read or programmed in parallel. The memory array 200 is addressable by word lines via row decoders 240A and 240B and by bit lines via column decoders 242A and 242B. In a typical embodiment, a controller 244 is included in the same memory device 210 (e.g., a removable storage card or package) as the one or more memory die 212. Commands and data are transferred between the host and controller 244 via lines 232 and between the

-17-

controller and the one or more memory die 212 via lines 234. Some memory systems may include multiple dies 212 in communication with Controller 244.

[0084] Control circuitry 220 cooperates with the read/write circuits 230A and 230B to perform memory operations on the memory array 200. The control circuitry 220 includes a state machine 222, an on-chip address decoder 224 and a power control module 226. The state machine 222 provides chip-level control of memory operations. The on-chip address decoder 224 provides an address interface between that used by the host or a memory controller to the hardware address used by the decoders 240A, 240B, 242A, and 242B. The power control module 226 controls the power and voltages supplied to the word lines and bit lines during memory operations. In one embodiment, power control module 226 includes one or more charge pumps that can create voltages larger than the supply voltage. Control circuitry 220, power control 226, decoder 224, state machine 222, decoders 240 A/B & 242A/B, the read/write circuits 230A/B and the controller 244, collectively or separately, can be referred to as one or more managing or control circuits.

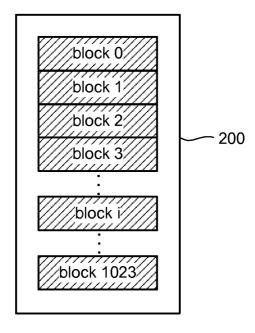

**[0085]** Figure 8 depicts an exemplary structure of memory array 200. In one embodiment, the array of memory cells is divided into a large number of blocks of memory cells. As is common for flash EEPROM systems, the block is the unit of erase. That is, each block contains the minimum number of memory cells that are erased together.

[0086] As one example, the NAND flash memory array depicted in Fig. 8 is partitioned into 1,024 blocks. However, more or less than 1024 blocks can be used. In each block, in this example, there are 69,624 columns corresponding to bit lines BL0, BL1, ... BL69,623. In one embodiment, all the bit lines of a block can be simultaneously selected during read and program operations. Memory cells along a common word line and connected to any bit line can be programmed (or read) at the same time. In another embodiment,

the bit lines are divided into even bit lines and odd bit lines. In an odd/even bit line architecture, memory cells along a common word line and connected to the odd bit lines are programmed at one time, while memory cells along a common word line and connected to even bit lines are programmed at another time.

[0087] Figure 8 shows four memory cells connected in series to form a NAND string. Although four cells are shown to be included in each NAND string, more or less than four can be used (e.g., 16, 32, 64, 128 or another number or memory cells can be on a NAND string). One terminal of the NAND string is connected to a corresponding bit line via a drain select gate (connected to select gate drain line SGD), and another terminal is connected to the source line via a source select gate (connected to select gate source line SGS).

[8800] Each block is typically divided into a number of pages. A page is a unit of programming. One or more pages of data are typically stored in one row of memory cells. A page can store one or more sectors. A sector includes user data and overhead data. Overhead data typically includes an Error Correction Code (ECC) that has been calculated from the user data of the sector. The controller calculates the ECC when data is being programmed into the array, and also checks it when data is being read from the array. In some embodiments, the state machine, controller, or other component can calculate and check the ECC. In some alternatives, the ECCs and/or other overhead data are stored in different pages, or even different blocks, than the user data to which they pertain. A sector of user data is typically 512 bytes, corresponding to the size of a sector in magnetic disk drives. A large number of pages form a block, anywhere from 8 pages, for example, up to 32, 64, 128 or more pages. In one embodiment, each word line of a block is associated with one page. In another embodiment, each word line of a block is associated with 3 pages. In

other embodiments, the word lines can be associate with other numbers of pages.

[0089] In one embodiment, each of the blocks depicted in Figure 8 include memory cells according to the structure of Figure 3. In other embodiments, a memory array may include some memory cells according to the structure of Figure 3 and some memory cells according to the structure of Figure 4. For example, Figure 9 shows another embodiment of memory array 200 for which block 0 and block 1 include High Endurance Short Retention memory cells storing binary data according to the structure of Figure 4 (as indicated by the shading) and the remaining blocks include Low Endurance Long Retention memory cells storing multi-state data according to the structure of Figure 3. In one example, blocks 0 and 1 can serve as a cache for the remaining blocks. In another example, block 0 and 1 can store data that is to be short lived (e.g., calculation, scratch pad, temporary data, applications being run, etc.), while the remaining blocks stored long term data.

[0090] Figure 10 shows another embodiment of memory array 200 in which all blocks include High Endurance Short Retention memory cells storing binary data according to the structure of Figure 4 (as indicated by the shading).

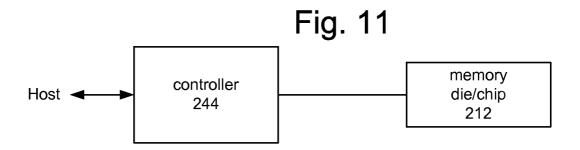

[0091] Figures 11-14 show various embodiments for using the memory arrays depicted in Figures 8-10. For example, Figure 11 shows controller 244 in communication with a host and memory die/chip 212, where memory die/chip 212 can include a memory array according to any of Figures 8-10 or any other memory that includes a combination of High Endurance Short Retention memory cells storing binary data according to the structure of Figure 4 and Low Endurance Long Retention memory cells storing multi-state data according to the structure of Figure 3. Thus, memory die/chip 212 of Figure 11 can include only High Endurance Short Retention memory cells storing binary data according to the structure of Figure 4, only Low Endurance Long

Retention memory cells storing multi-state data according to the structure of Figure 3, or any combination of both.

[0092] Figure 12 depicts controller 244 in communication with a host and memory die/chips 212a and 212b, where memory die/chip 212a includes Low Endurance Long Retention memory cells storing multi-state data according to the structure of Figure 3 and memory die/chip 212b includes High Endurance Short Retention memory cells storing binary data according to the structure of Figure 4.

[0093] Figure 13 shows memory die/chip 212c directly in communication with a host (assuming the host includes the logic to operate memory die/chip 212c), where memory die/chip 212c includes only Low Endurance Long Retention memory cells storing multi-state data according to the structure of Figure 3. Figure 14 shows memory die/chip 212d directly in communication with a host (assuming the host includes the logic to operate memory die/chip 212d), where memory die/chip 212d includes only High Endurance Short Retention memory cells storing multi-state data according to the structure of Figure 4.

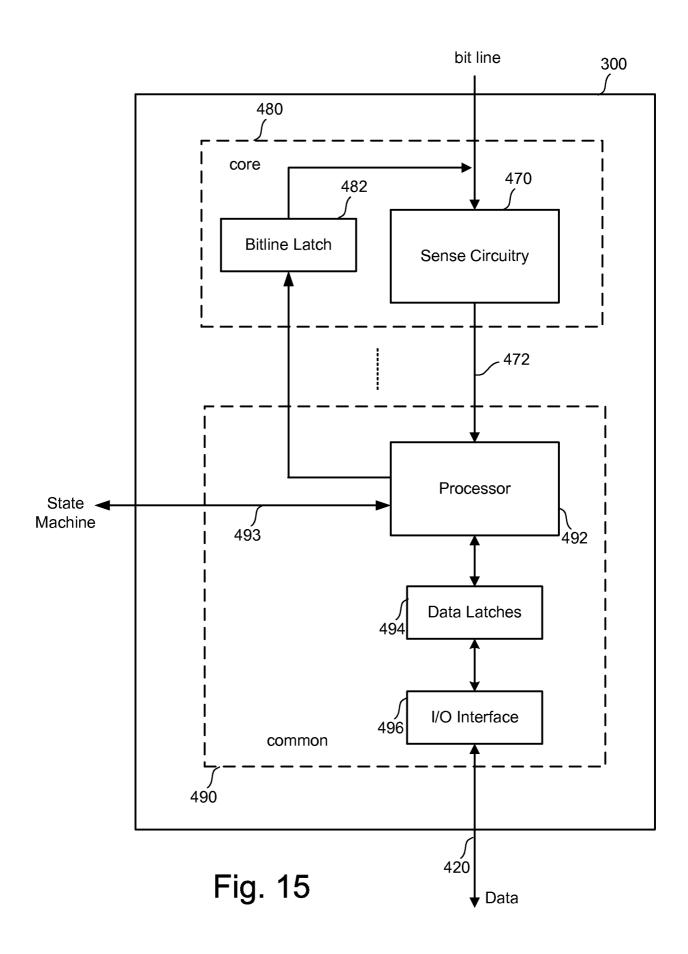

[0094] Figure 15 is a block diagram of an individual sense block 300 (see Figure 7) partitioned into a core portion, referred to as a sense module 480, and a common portion 490. In one embodiment, there will be a separate sense module 480 for each bit line and one common portion 490 for a set of multiple sense modules 480. In one example, a sense block will include one common portion 490 and eight sense modules 480. Each of the sense modules in a group will communicate with the associated common portion via a data bus 472. For further details, refer to U.S. Patent Application Publication 2006/0140007, which is incorporated herein by reference in its entirety.

[0095] Sense module 480 comprises sense circuitry 470 that determines whether a conduction current in a connected bit line is above or below a

predetermined threshold level. In some embodiments, sense module 480 includes a circuit commonly referred to as a sense amplifier. Sense module 480 also includes a bit line latch 482 that is used to set a voltage condition on the connected bit line. For example, a predetermined state latched in bit line latch 482 will result in the connected bit line being pulled to a state designating program inhibit (e.g., Vdd).

[0096] Common portion 490 comprises a processor 492, a set of data latches 494 and an I/O Interface 496 coupled between the set of data latches 494 and data bus 420. Processor 492 performs computations. For example, one of its functions is to determine the data stored in the sensed memory cell and store the determined data in the set of data latches. The set of data latches 494 is used to store data bits determined by processor 492 during a read operation. It is also used to store data bits imported from the data bus 420 during a program operation. The imported data bits represent write data meant to be programmed into the memory. I/O interface 496 provides an interface between data latches 494 and the data bus 420.

[0097] During read or sensing, the operation of the system is under the control of state machine 222 that controls the supply of different control gate voltages to the addressed cell. As it steps through the various predefined control gate voltages (the read reference voltages or the verify reference voltages) corresponding to the various memory states supported by the memory, the sense module 480 may trip at one of these voltages and an output will be provided from sense module 480 to processor 492 via bus 472. At that point, processor 492 determines the resultant memory state by consideration of the tripping event(s) of the sense module and the information about the applied control gate voltage from the state machine via input lines 493. It then computes a binary encoding for the memory state and stores the resultant data bits into data latches 494. In another embodiment of the core portion, bit line

latch 482 serves double duty, both as a latch for latching the output of the sense module 480 and also as a bit line latch as described above.

It is anticipated that some implementations will include multiple [0098] processors 492. In one embodiment, each processor 492 will include an output line (not depicted in Fig. 15) such that each of the output lines is wired-OR'd together. In some embodiments, the output lines are inverted prior to being connected to the wired-OR line. This configuration enables a quick determination during the program verification process of when the programming process has completed because the state machine receiving the wired-OR line can determine when all bits being programmed have reached the desired level. For example, when each bit has reached its desired level, a logic zero for that bit will be sent to the wired-OR line (or a data one is inverted). When all bits output a data 0 (or a data one inverted), then the state machine knows to terminate the programming process. In embodiments where each processor communicates with eight sense modules, the state machine may (in some embodiments) need to read the wired-OR line eight times, or logic is added to processor 492 to accumulate the results of the associated bit lines such that the state machine need only read the wired-OR line one time. In some embodiments that have many sense modules, the wired-OR lines of the many sense modules can be grouped in sets of N sense modules, and the groups can then be grouped to form a binary tree.

[0099] During program or verify of the Low Endurance Long Retention memory cells storing multi-state data, the data to be programmed is stored in the set of data latches 494 from the data bus 420. The program operation, under the control of the state machine, comprises a series of programming voltage pulses (with increasing magnitudes) concurrently applied to the control gates of the addressed memory cells to that the memory cells are programmed at the same time. Each programming pulse is followed by a verify process to determine if the memory cell has been programmed to the desired state.

Processor 492 monitors the verified memory state relative to the desired memory state. When the two are in agreement, processor 492 sets the bit line latch 482 so as to cause the bit line to be pulled to a state designating program inhibit. This inhibits the memory cell coupled to the bit line from further programming even if it is subjected to programming pulses on its control gate. In other embodiments the processor initially loads the bit line latch 482 and the sense circuitry sets it to an inhibit value during the verify process.

[00100] Data latch stack 494 contains a stack of data latches corresponding to the sense module. In one embodiment, there are three (or four or another number) data latches per sense module 480. In some implementations (but not required), the data latches are implemented as a shift register so that the parallel data stored therein is converted to serial data for data bus 420, and vice versa. In one preferred embodiment, all the data latches corresponding to the read/write block of memory cells can be linked together to form a block shift register so that a block of data can be input or output by serial transfer. In particular, the bank of read/write modules is adapted so that each of its set of data latches will shift data into or out of the data bus in sequence as if they are part of a shift register for the entire read/write block.

[00101] Additional information about the structure and/or operations of various embodiments of non-volatile storage devices can be found in (1) United States Patent Application Pub. No. 2004/0057287, "Non-Volatile Memory And Method With Reduced Source Line Bias Errors," published on March 25, 2004; (2) United States Patent Application Pub No. 2004/0109357, "Non-Volatile Memory And Method with Improved Sensing," published on June 10, 2004; (3) U.S. Patent Application Pub. No. 20050169082; (4) U.S. Patent Application Pub. 2006/0221692, titled "Compensating for Coupling During Read Operations of Non-Volatile Memory," Inventor Jian Chen, filed on April 5, 2005; and (5) U.S. Patent Application Pub. 2006/0158947, titled "Reference Sense Amplifier For Non-Volatile Memory, Inventors Siu Lung

-24-

Chan and Raul-Adrian Cernea, filed on December 28, 2005. All five of the immediately above-listed patent documents are incorporated herein by reference in their entirety.

[00102] At the end of a successful programming process (with verification), the threshold voltages of the memory cells should be within one or more distributions of threshold voltages for programmed memory cells or within a distribution of threshold voltages for erased memory cells, as appropriate. Figure 16 illustrates example threshold voltage distributions (threshold voltage versus number of memory cells) for memory cells storing one bit of data (aka binary data). For example, Figure 16 shows threshold voltage distributions for High Endurance Short Retention memory cells storing binary data according to the structure of Figure 4. As can be seen, there are two threshold voltage distributions E and P. Threshold voltage distribution E (also known as state E) represents threshold voltages for memory cells that are in an erased state. Threshold voltage distribution P (also known as state P) represents threshold voltages for memory cells that are in a programmed state. In one example, memory cells in the erased state E represent data 1 and memory cells in the programmed state P represent data 1. Memory cells in the erased state E can be programmed into the programmed state P by applying one or more programming pulses that saturate the floating gate of the memory cell with charge (e.g., electrons). Memory cells in the programmed state P can be erased back to the erased state E. In one embodiment, data state E is below 0 volts and data state P is above 0 volts.

[00103] Figure 17 illustrates example threshold voltage distributions for Low Endurance Long Retention memory cells storing multi-state data according to the structure of Figure 3, where each memory cell stores three bits of data. Other embodiments, however, may use more or less than three bits of data per memory cell (e.g., such as four or more bits of data per memory cell). Since each memory cell stores three bits of data, there are eight valid threshold

voltage distributions, also called data states: S0, S1, S2, S3, S4, S5, S6 and S7. In one embodiment, data state S0 is below 0 volts and data states S1-S7 are above 0 volts. In other embodiments, all eight data states are above 0 volts, or other arrangements can be implemented. In one embodiment, the threshold voltage distribution for S0 is wider than for S1-S7. In one embodiment, S0 is for erased memory cells. Data is programmed from S0 to S1-S7.

[00104] Each data state corresponds to a unique value for the three data bits stored in the memory cell. In one embodiment, S0=111, S1=110, S2=101, S3=100, S4=011, S5=010, S6=001 and S7=000. Other mapping of data to states S0-S7 can also be used. The specific relationship between the data programmed into the memory cell and the threshold voltage levels of the cell depends upon the data encoding scheme adopted for the cells. For example, U.S. Patent No. 6,222,762 and U.S. Patent Application Publication No. 2004/0255090, "Tracking Cells For A Memory System," filed on June 13, 2003, both of which are incorporated herein by reference in their entirety, describe various data encoding schemes for multi-state flash memory cells. In one embodiment, data values are assigned to the threshold voltage ranges using a Gray code assignment so that if the threshold voltage of a floating gate erroneously shifts to its neighboring threshold voltage distribution, only one bit will be affected. However, in other embodiments, Gray code is not used.

[00105] In one embodiment, all of the bits of data stored in a memory cell are stored in the same logical page. In other embodiments, each bit of data stored in a memory cell corresponds to different logical pages. Thus, a memory cell storing three bits of data would include data in a first page, data in a second page and data in a third page. In some embodiments, all of the memory cells connected to the same word line would store data in the same three pages of data. In some embodiments, the memory cells connected to a word line can be grouped into different sets of pages (e.g., by odd and even bit lines, or by other arrangements).

[00106] In some devices, the memory cells will be erased to state S0. From state S0, the memory cells can be programmed to any of states S1-S7. In one embodiment, known as full sequence programming, memory cells can be programmed from the erased state S0 directly to any of the programmed states S1-S7. For example, a population of memory cells to be programmed may first be erased so that all memory cells in the population are in erased state S0. While some memory cells are being programmed from state S0 to state S1, other memory cells are being programmed from state S0 to state S2, state S0 to state S3, state S0 to state S4, state S0 to state S5, state S0 to state S6, and state S0 to state S7. Full sequence programming is graphically depicted by the seven curved arrows of Fig. 17.

Figure 17 shows a set of verify target levels Vv1, Vv2, Vv3, Vv4, [00107] Vv5, Vv6, and Vv7. These verify levels are used as comparison levels during the programming process. For example, when programming memory cells to state S1, the system will check to see if the threshold voltages of the memory cells have reached Vv1. If the threshold voltage of a memory cell has not reached Vv1, then programming will continue for that memory cell until its threshold voltage is greater than or equal to Vv1. If the threshold voltage of a memory cell has reached Vv1, then programming will stop for that memory cell. Verify target level Vv2 is used for memory cells being programmed to state S2. Verify target level Vv3 is used for memory cells being programmed to state S3. Verify target level Vv4 is used for memory cells being programmed to state S4. Verify target level Vv5 is used for memory cells being programmed to state S5. Verify target level Vv6 is used for memory cells being programmed to state S6. Verify target level Vv7 is used for memory cells being programmed to state S7.

[00108] Figure 17 also shows a set of read compare levels Vr1, Vr2, Vr3, Vr4, Vr5, Vr6, and Vr7. These read compare levels are used as comparison levels during the read process. By testing whether the memory cells turn on or

-27-

remain off in response to the read compare levels Vr1, Vr2, Vr3, Vr4, Vr5, Vr6, and Vr7 being separately applied to the control gates of the memory cells, the system can determine which states that memory cells are storing data for.

[00109] In general, during verify operations and read operations, the selected word line is connected to a voltage, a level of which is specified for each read operation (e.g., see read compare levels Vr1, Vr2, Vr3, Vr4, Vr5, Vr6, and Vr7 of Fig. 17 and 0v of Fig. 16) or verify operation (e.g. see verify target levels Vv1, Vv2, Vv3, Vv4, Vv5, Vv6, and Vv7of Fig. 7) in order to determine whether a threshold voltage of the concerned memory cell has reached such level. After applying the word line voltage, the conduction current of the memory cell is measured to determine whether the memory cell turned on in response to the voltage applied to the word line. If the conduction current is measured to be greater than a certain value, then it is assumed that the memory cell turned on and the voltage applied to the word line is greater than the threshold voltage of the memory cell. If the conduction current is not measured to be greater than the certain value, then it is assumed that the memory cell did not turn on and the voltage applied to the word line is not greater than the threshold voltage of the memory cell. During a read process, the unselected memory cells are provided with one or more read pass voltages at their control gates so that these memory cells will operate as pass gates (e.g., conducting current regardless of whether they are programmed or erased).

[00110] There are many ways to measure the conduction current of a memory cell during a read or verify operation. In one example, the conduction current of a memory cell is measured by the rate it discharges or charges a dedicated capacitor in the sense amplifier. In another example, the conduction current of the selected memory cell allows (or fails to allow) the NAND string that includes the memory cell to discharge a corresponding bit line. The voltage on the bit line is measured after a period of time to see whether it has been discharged or not. Note that the technology described herein can be used

with different methods known in the art for verifying/reading. More information about verifying/reading can be found in the following patent documents that are incorporated herein by reference in their entirety: (1) United States Patent Application Pub. No. 2004/0057287; (2) United States Patent Application Pub No. 2004/0109357; (3) U.S. Patent Application Pub. No. 2005/0169082; and (4) U.S. Patent Application Pub. No. 2006/0221692. The read and verify operations described above are performed according to techniques known in the art. Thus, many of the details explained can be varied by one skilled in the art. Other read and verify techniques known in the art can also be used.

[00111] Figure 17 shows a programming process that includes one phase where all memory cells connected to the same word line are programmed concurrently during that one phase. Figures 18A-E illustrates a multi-phase programming approach. In this embodiment, the programming process includes three phases. Prior to programming, the memory cells are erased so that all memory cells connected to a common word line are in an erased threshold voltage distribution E, as depicted in Figure 18A. During the first phase of programming, those memory cells whose targets (due to the data to be stored in those memory cells) are data states S4, S5, S6 or S7 are programmed to an intermediate state IM. Those memory cells are targeted for data states S0, S1, S2 or S3 and remain in the erased threshold voltage distribution E. The first phase is graphically depicted by Figure 18B. Memory cells being programmed to intermediate state IM are programmed to a target threshold voltage of VvIM.

[00112] During the second phase of the programming process of Figures 18A-E, those memory cells that are in the erased threshold voltage distribution E are programmed to their target data states. For example, those memory cells to be programmed to data state S3 are programmed from erased threshold voltage distribution E to data state S3, those memory cells to be programmed

to data state S2 are programmed from erased threshold voltage distribution E to data state S2, those memory cells to be programmed to data state S1 are programmed from erase threshold voltage distribution E to data state S1, and those memory cells to be in data state S0 are not programmed during the second phase of the programming process. Thus, erased threshold voltage distribution E becomes data state S0. Also, during the second phase, memory cells are programmed from the intermediate state IM to various data states S4-S7. For example, those memory cells to be programmed to data state S7 are programmed from the intermediate state IM to data state S7, those memory cells targeted to be in data state S6 are programmed from intermediate state IM to data state S5, and those memory cells to be programmed from intermediate state IM to data state S5, and those memory cells to be programmed from intermediate state IM to data state S4 are programmed from intermediate state IM to data state S4. This second phase of programming is illustrated in Figure 18C.

[00113] As can be seen in Figure 18C, at the end of the second phase of programming data states S1-S7 overlap with neighboring data states. For example, data state S1 overlaps with data state S2, data state S2 overlaps with data states S1 and S3, data state S3 overlaps with data states S2 and S4, data state S4 overlaps with data states S3 and S5, data state S5 overlaps with data states S4 and S6, and data state S6 overlaps with data states S5 and S7. In some embodiments, all or some of the data states do not overlap.

**[00114]** In the third phase of programming, each of data states S1-S7 are tightened so that they no longer overlap with neighboring states. This is depicted graphically by Figure 18D. The final result of the three phrase programming process is depicted in Figure 18E, which shows data states S0-S7. In some embodiments, data state S0 is wider than data states S1-S7.

[00115] In some embodiments, those memory cells to be programmed to data state S4 are not programmed during the second phase and, therefore, remain in intermediate state IM. During the third programming phase, the memory cells are programmed from IM to S4. In other embodiments, memory cells destined for other states can also remain in IM or E during the second phase.

**[00116]** In some programming processes, coarse/fine programming techniques can be incorporated. For example, memory cells being programmed to a target condition (e.g., Vv2) would first be quickly programmed to coarse condition (e.g., Vv2 less a small voltage) that corresponds to a threshold voltage condition slightly lower than the target condition. Subsequently, the memory cells would be programmed to the target condition in a manner more slowly (and with more precision). The coarse/fine programming techniques can be used for programming to all or a subset of the data states.

[00117] Figure 19 is a flow chart describing a process for operating Low Endurance Long Retention memory cells storing multi-state data according to the structure of Figure 3. In step 548, a request to program data is received. In some embodiments, data is programmed without receiving a request. In step 550, all (or a subset) of the memory cells in the block to be programmed are programmed to the highest data state (or another state) to put all of the data cells into the same condition). In step 552, memory cells are erased (in blocks or other units) prior to programming. Memory cells are erased in one embodiment by raising the p-well to an erase voltage (e.g., 20 volts) for a sufficient period of time and grounding the word lines of a selected block while the source and bit lines are floating. In blocks that are not selected to be erased, word lines are floated. Due to capacitive coupling, the unselected word lines, bit lines, select lines, and the common source line are also raised to a significant fraction of the erase voltage thereby impeding erase on blocks that

are not selected to be erased. In blocks that are selected to be erased, a strong electric field is applied to the tunnel dielectric layers of selected memory cells and the selected memory cells are erased as electrons of the floating gates are emitted to the substrate side, typically by Fowler-Nordheim tunneling mechanism. As electrons are transferred from the floating gate to the p-well region, the threshold voltage of a selected cell is lowered. Erasing can be performed on the entire memory array, on individual blocks, or another unit of memory cells. In one embodiment, after erasing the memory cells, all of the erased memory cells in the block will be in state S0 or E. One implementation of an erase process includes applying several erase pulses to the p-well and verifying between erase pulses whether the NAND strings are properly erased.

In step 554, soft programming is (optionally) performed to narrow [00118] the distribution of erased threshold voltages for the erased memory cells. Some memory cells may be in a deeper erased state than necessary as a result of the erase process. Soft programming can apply programming pulses to move the threshold voltage of the deeper erased memory cells to the erase In step 556, the memory cells of the block are threshold distribution. programmed. The programming can be performed in response to a request to program from the host, or in response to an internal process. After programming, the memory cells of the block can be read (step 558). Many different read processes known in the art can be used to read data. In some embodiments, the read process includes using ECC to correct errors. The data that is read is output to the hosts that requested the read operation. The ECC process can be performed by the state machine, the controller or another device.

[00119] Figure 19 shows that the erase-program cycle (loop consisting of steps 550-556) can happen many times without or independent of reading, the read process can occur many times without or independent of programming, and the read process can happen any time after programming. The process of

Figure 19 can be performed at the direction of the state machine using the various circuits described above. In other embodiments, the process of Figure 19 can be performed at the direction of the Controller using the various circuits described above.

[00120] Figure 20 is a flow chart describing one embodiment of a process for performing programming on Low Endurance Long Retention memory cells storing multi-state data according to the structure of Figure 3 connected to a common word line. The process of Figure 20 can be performed one or multiple times during step 556 of Figure 19. For example, the process of Figure 20 can be used to program memory cells (e.g., full sequence programming) from state S0 directly to any of states S1-S7. Alternatively, the process of Figure 20 can be used to perform one or each of the phases of the process of Fig. 18A-E. For example, when performing the process of Fig. 18A, the process of Fig. 20 is used to implement the first phase that includes programming some of the memory cells from state E to state IM. The process of Fig. 20 can then be used again to implement the second phase that includes programming some of the memory cells from state E to states S1-S3 and from state IM to states S4-S7. The process of Fig. 20 can be used again to adjust states S1-S7 in the third phase (see Fig. 18D). The process of Fig. 20 can also be used with other multi-phase programming processes.

[00121] Typically, the program voltage applied to the control gate during a program operation is applied as a series of program pulses. In step 570 of Figure 20, the programming voltage (Vpgm) is initialized to the starting magnitude (e.g., ~12-16V or another suitable level) and a program counter PC maintained by state machine 222 is initialized at 1. In step 572, a program pulse of the program signal Vpgm is applied to the selected word line (the word line selected for programming). In one embodiment, the group of memory cells being programmed are all connected to the same word line (the selected word line). The unselected word lines receive one or more boosting

voltages (e.g., ~9 volts) to perform boosting schemes known in the art. If a memory cell should be programmed, then the corresponding bit line is grounded. On the other hand, if the memory cell should remain at its current threshold voltage, then the corresponding bit line is connected to Vdd to inhibit programming. In step 572, the program pulse is concurrently applied to all memory cells connected to the selected word line so that all of the memory cells connected to the selected word line are programmed concurrently. That is, they are programmed at the same time (or during overlapping times). In this manner all of the memory cells connected to the selected word line will concurrently have their threshold voltage change, unless they have been locked out from programming.

[00122] In step 574, the appropriate memory cells are verified using the appropriate set of target levels to perform one or more verify operations. In one embodiment, the verification process is performed by applying the appropriate verify compare voltage (Vv1, Vv2, Vv3, Vv4, Vv5, Vv6, and Vv7) to the selected word line and the current read pass voltage to unselected word lines.

[00123] In step 576, it is determined whether all the memory cells have reached their target threshold voltages. If so, the programming process is complete and successful because all selected memory cells were programmed and verified to their target states. A status of "PASS" is reported in step 578. If, in 576, it is determined that not all of the memory cells have reached their target threshold voltages, then the programming process continues to step 580.

[00124] In step 580, the system counts the number of memory cells that have not yet reached their respective target threshold voltage distribution. That is, the system counts the number of cells that have failed the verify process. This counting can be done by the state machine, the controller, or other logic. In one implementation, each of the sense blocks 300 will store the status

(pass/fail) of their respective cells. These values can be counted using a digital counter. As described above, many of the sense blocks have an output signal that is wire-Or'd together. Thus, checking one line can indicate that no cells of a large group of cells have failed verify. By appropriately organizing the lines being wired-Or together (e.g., a binary tree- like structure), a binary search method can be used to determine the number of cells that have failed. In such a manner, if a small number of cells failed, the counting is completed rapidly. If a large number of cells failed, the counting takes a longer time. More information can be found in United States Patent Publication 2008/0126676, incorporated herein by reference in its entirety. In another alternative, each of the sense amplifiers can output an analog voltage or current if its corresponding memory cell has failed and an analog voltage or current summing circuit can be used to count the number of memory cells that have failed. In one embodiment, there is one total count, which reflects the total number of memory cells currently being programmed that have failed the last verify step. In another embodiment, separate counts are kept for each data state.

[00125] In step 582, it is determined whether the count from step 580 is less than or equal to a predetermined limit. In one embodiment, the predetermined limit is the number of bits that can be corrected by ECC during a read process for the page of memory cells. If the number of failed cells is less than or equal to the predetermined limit, than the programming process can stop and a status of "PASS" is reported in step 578. In this situation, enough memory cells programmed correctly such that the few remaining memory cells that have not been completely programmed can be corrected using ECC during the read process. In some embodiments, step 580 will count the number of failed cells for each sector, each target data state or other unit, and those counts will individually or collectively be compared to a threshold in step 582.

[00126] In another embodiment, the predetermined limit can be less than the number of bits that can be corrected by ECC during a read process to allow for future errors. When programming less than all of the memory cells for a page, or comparing a count for only one data state (or less than all states), than the predetermined limit can be a portion (pro-rata or not pro-rata) of the number of bits that can be corrected by ECC during a read process for the page of memory cells. In some embodiments, the limit is not predetermined. Instead, it changes based on the number of errors already counted for the page, the number of program-erase cycles performed, temperature or other criteria.

[00127] If number of failed cells is not less than the predetermined limit, than the programming process continues at step 584 and the program counter PC is checked against the program limit value (PL). One example of a program limit value is 20; however, other values can be used. If the program counter PC is not less than the program limit value PL, then the program process is considered to have failed and a status of FAIL is reported in step 588. If the program counter PC is less than the program limit value PL, then the process continues at step 586 during which time the Program Counter PC is incremented by 1 and the program voltage Vpgm is stepped up to the next magnitude. For example, the next pulse will have a magnitude greater than the previous pulse by a step size (e.g., a step size of 0.1-0.4 volts). After step 586, the process loops back to step 572 and another program pulse is applied to the selected word line.

[00128] In some embodiments, the program voltage applied to the control gate includes a series of pulses that are increased in magnitude with each successive pulse by a predetermined step size (e.g. 0.2v, 0.3v, 0.4v, or others). Between pulses, some memory systems will verify whether the individual memory cells have reached their respective target threshold voltage ranges. For example, Figure 21 shows program voltage applied to the control gate as a series of pulses.

-36-

**[00129]** Figure 22 shows a portion of the signal depicted in Figure 21. More specifically, Figure 22 shows programming pulses 564, 565 and 566, with a set of verify pulses between the programming pulses. The verify pulses are not depicted in Figure 21.

[00130] When performing full sequence programming in one embodiment, the verification process between programming pulses will test for each of the threshold voltage distribution (data states) S1-S7. Therefore, Figure 22 shows seven verify pulses that have magnitudes corresponding to verify target levels Vv1, Vv2, Vv3, Vv4, Vv5, Vv6, and Vv7. In some embodiments, one or more of the verify operations can be skipped (and, therefore one or more of the verify pulses can be skipped) because the verify operation is not necessary or superfluous. For example, if none of the memory cells being programmed have reached Vv2, there is no reason to verify at Vv7. More information about intelligent verification schemes that skip verification for one or more states can be found in the following patent documents which are incorporated herein by reference in their entirety: U.S. Patent 7,073,103; U.S. Patent 7,224,614; U.S. Patent 7,310,255; U.S. Patent 7,301,817; U.S. Patent App. 2004/0109362; and U.S. Patent App. 2009/0147573.

[00131] Figure 23 is a flow chart describing a process for operating High Endurance Short Retention memory cells storing binary data according to the structure of Figure 4. In step 600, a request to program data is received. In some embodiments, data is programmed without receiving a request. In step 602, all (or a subset) of the memory cells in the selected block are programmed to the programmed data state (or another condition) to put all of the data cells into the same condition. In step 604, memory cells are erased (in blocks or other units) prior to programming. In step 606, soft programming is (optionally) performed to narrow the distribution of erased threshold voltages for the erased memory cells. In step 608, the memory cells of the block are

programmed. The programming can be performed in response to a request to program from the host, or in response to an internal process.

Since these memory cells have shorter data retention (e.g., days,... [00132] weeks, months, etc. ) they will need to be refreshed from time to time. Step 610 includes determining whether the memory cells need to be refreshed. In one embodiment, the memory system will physically test whether the memory cells need to be refreshed, while in other embodiments the memory system will automatically refresh after a predefined period has elapsed. Examples of physical tests include testing whether the threshold voltage has drifted by a particular amount, testing the behavior of sample or actual memory cells, determining whether the read process has identified more errors, etc. The test for refresh (step 610) can be performed periodically, continuously or in response to a trigger (where the trigger can be based on a condition occurring). If it is determined that a refresh is needed, then a refresh operation is performed in step 612. One example of a refresh operation is to copy the block of data to a new block of memory cells and then mark the old block of memory cells as no longer storing valid data.

[00133] Any time after programming, the memory cells of the block can be read (step 614). Many different read processes known in the art can be used to read data. In some embodiments, the read process includes using ECC to correct errors. The data that is read is output to the hosts that requested the read operation. The ECC process can be performed by the state machine, the controller or another device.

[00134] Figure 23 shows that the erase-program cycle (loop consisting of steps 602-608) can happen many times without or independent of reading, the read process can occur many times without or independent of programming, and the read process can happen any time after programming. The process of Figure 23 can be performed at the direction of the state machine using the

-38-

various circuits described above. In other embodiments, the process of Figure 23 can be performed at the direction of the Controller using the various circuits described above. The read process can also be performed in response to both the Controller and state machine.

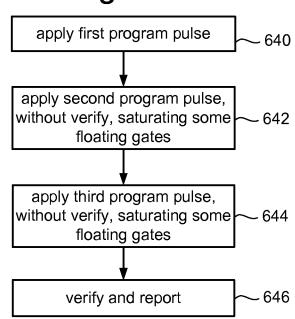

[00135] Figure 24 is a flow chart describing one embodiment of a process for performing programming on High Endurance Short Retention memory cells storing binary data according to the structure of Figure 4 connected to a common word line. The process of Figure 24 can be performed one or multiple times during step 608 of Figure 23. For example, the process of Figure 24 can be used to program memory cells from state E to state P (see Figure 16).

[00136] Typically, the program voltage applied to the control gates (via the common connected word line) during a program operation is applied as a series of program pulses. The embodiment of Figure 24 includes applying one or more program pulses without performing intervening verify operations. The intent is to saturate the floating gates with electrons so that all (or nearly all) of the programmed memory cells will have a threshold voltage near saturation level so the threshold voltage distribution will be narrow. Since the floating gates will be limited in the charge retention by saturation, there will not be a need to verify between program pulses.

[00137] Testing or simulation can be used to determine in advance the exact number of program pulses, the magnitude of the pulses, and the width of the pulses to use to cause all (or nearly all) of the floating gates to reach saturation.

**[00138]** In step 640 of Fig. 24, the first program pulse is applied to the control gates of the selected memory cells (via the common connected word line). In one embodiment, a pulse magnitude between 12-18 volts is used. Some of the memory cells will have their floating gate saturated with electrons

due to the first pulse. In step 642, a second program pulse is applied to the control gates of the selected memory cells (via the common connected word line). No verification operation is performed between the first program pulse and the second program pulse. Some of the memory cells will have their floating gate saturated with electrons due to the second pulse. In step 644, a third program pulses is applied to the control gates of the selected memory cells (via the common connected word line). No verification operation is performed between the second program pulse and the third program pulse. Some of the memory cells will have their floating gate saturated with electrons due to the third program pulse. The flow chart of Figure 24 only shows three program pulses being applied (without verification between the pulses). In other embodiments, more or less than three program pulses can be used.

[00139] In step 646, a verification operation can be performed. For example, the system can test whether all programmed memory cells have a threshold voltage greater than S volts (see Fig. 16) and record the number of bits that do not have a threshold voltage greater than S volts. If the number of bits that do not have a threshold voltage greater than S volts is a greater than the amount allowed by the system (the amount that can be corrected by ECC or a little lower than that amount), than the program operation has failed and programming will be repeated by performing the erase-program cycle (loop consisting of steps 602-608) of Figure 23.