(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6482566号

(P6482566)

(45) 発行日 平成31年3月13日(2019.3.13)

(24) 登録日 平成31年2月22日(2019.2.22)

(51) Int.Cl.

G05F 1/56 (2006.01)

H03H 11/04 (2006.01)

F 1

G05F 1/56

H03H 11/04310F

C

請求項の数 20 (全 13 頁)

(21) 出願番号 特願2016-553380 (P2016-553380)

(86) (22) 出願日 平成27年2月19日 (2015.2.19)

(65) 公表番号 特表2017-512341 (P2017-512341A)

(43) 公表日 平成29年5月18日 (2017.5.18)

(86) 國際出願番号 PCT/US2015/016520

(87) 國際公開番号 WO2015/127018

(87) 國際公開日 平成27年8月27日 (2015.8.27)

審査請求日 平成30年2月16日 (2018.2.16)

(31) 優先権主張番号 14/183,739

(32) 優先日 平成26年2月19日 (2014.2.19)

(33) 優先権主張国 米国(US)

(73) 特許権者 390020248

日本テキサス・インスツルメンツ合同会社

東京都新宿区西新宿六丁目24番1号

(73) 特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

-5474 ダラス メイル ステイショ

ン 3999 ピーオーボックス 655

474

(74) 上記1名の代理人 100098497

弁理士 片寄 恒三

最終頁に続く

(54) 【発明の名称】低ドロップアウト電圧レギュレータ回路

## (57) 【特許請求の範囲】

## 【請求項 1】

レギュレートされた出力電圧を提供するための回路であって、

第1の端子と第2の端子と第3の端子とを含むスイッチであって、前記第1の端子において入力信号を受け取り、前記第2の端子においてエラー信号を受け取るように構成され、前記入力信号と前記エラー信号とに応答して前記第3の端子において出力信号を生成するように更に構成される、前記スイッチと、

第1のトランジスタと第2のトランジスタとを含む第1のフィードバック回路であって、前記第1のトランジスタが第1のノードと第2のノードと第3のノードとを含み、前記第2のトランジスタが第4のノードと第5のノードと第6のノードとを含み、前記第1のノードと前記第2のノードとが前記出力信号を受け取るように配置されるように、前記第1のノードと前記第2のノードとが前記スイッチの前記第3の端子に結合され、前記第1のフィードバック回路が前記エラー信号を制御するように構成されるように、前記第5のノードが基準信号を受け取るように配置されて前記第4のノードが前記第2の端子に結合され、前記第3のノードと前記第6のノードとが互いに結合され、前記第1のトランジスタと前記第2のトランジスタとが、前記出力信号と前記基準信号との間の差に応答して前記スイッチの前記第2の端子において前記エラー信号を制御するように構成される、前記第1のフィードバック回路と、

前記エラー信号を感知するように構成され、それぞれ前記第1のトランジスタと前記第2のトランジスタとにおいて実質的に等しい電流を維持するために前記第2のノードと前記第1のノードとが互いに結合されるように構成される。

10

20

記第4のノードとにおいてテール電流を生成するように構成され、それにより、前記出力信号の電圧を前記基準信号の電圧に実質的に等しくする、第2のフィードバック回路と、を含む、回路。

【請求項2】

請求項1に記載の回路であって、

第7のノードと第8のノードとを含むトランジスタベースダイオードであって、前記第7のノードが前記入力信号を受け取るように配置され、前記第8のノードが前記第4のノードと前記第2の端子とに結合される、前記トランジスタベースダイオードを更に含む、回路。

【請求項3】

請求項2に記載の回路であって、

前記第2のフィードバック回路が、

前記スイッチの前記第2の端子に結合される第3のトランジスタであって、前記トランジスタベースダイオードの電流をミラーするように構成される、前記第3のトランジスタと、

第4のトランジスタと第5のトランジスタとを含む電流ミラー回路であって、前記第4のトランジスタが前記第3のトランジスタに結合され、前記第5のトランジスタが前記第3のノードと前記第6のノードとに結合され、それにより、前記第1のトランジスタと前記第2のトランジスタとからテール電流をシンクし、前記第4のトランジスタが、前記第3のトランジスタから電流をソースするように構成され、前記第5のトランジスタが、前記第4のトランジスタにおいて前記第3のトランジスタからソースされる前記電流の実質的に2倍である前記第5のトランジスタにおける前記テール電流として、前記第5のトランジスタにおいて電流をミラーするように構成される、前記電流ミラー回路と、

を含む、回路。

【請求項4】

請求項3に記載の回路であって、

前記第5のトランジスタが前記第4のトランジスタの幾何学的寸法の実質的に2倍の幾何学的寸法を有する、回路。

【請求項5】

請求項3に記載の回路であって、

前記スイッチが金属酸化物半導体(MOS)トランジスタである、回路。

【請求項6】

請求項5に記載の回路であって、

前記トランジスタベースダイオードが前記スイッチより小さな幾何学的な寸法とされる、回路。

【請求項7】

請求項3に記載の回路であって、

前記第5のトランジスタにおける前記テール電流が前記トランジスタベースダイオードを流れる電流の2倍である、回路。

【請求項8】

請求項2に記載の回路であって、

前記第3のノードと前記第6のノードとを接地に結合する第1のバイアス回路であって、前記第1のトランジスタと前記第2のトランジスタとから第1のテール電流をシンクするように構成される、前記第1のバイアス回路を更に含む、回路。

【請求項9】

請求項8に記載の回路であって、

前記第2のトランジスタにおいてバイアス電流を提供するように構成される第2のバイアス回路を更に含む、回路。

【請求項10】

請求項9に記載の回路であって、

10

20

30

40

50

前記第1のテール電流が前記バイアス電流の約2倍である、回路。

【請求項11】

レギュレートされた出力電圧を提供するための回路であって、

第1の端子と第2の端子と第3の端子とを含むスイッチであって、前記第1の端子において電力供給入力を受け取り、前記第2の端子においてエラー信号を受け取るように構成され、前記電力供給入力と前記エラー信号とに応答して前記第3の端子において出力信号を生成するように更に構成される、前記スイッチと、

第1のトランジスタと第2のトランジスタとを含み、前記エラー信号を制御する第1のフィードバック回路であって、前記第1のトランジスタが第1のノードと第2のノードと第3のノードとを含み、前記第2のトランジスタが第4のノードと第5のノードと第6のノードとを含み、前記第1のノードと前記第2のノードとが前記出力信号を受け取るように配置されるように前記第1のノードと前記第2のノードとが前記スイッチの前記第3の端子に結合され、前記第1のフィードバック回路が前記エラー信号を制御するように構成されるように前記第5のノードが基準信号を受け取るように構成されて前記第4のノードが前記第2の端子に結合され、前記第3のノードと前記第6のノードとが互いに結合され、前記第1のトランジスタと前記第2のトランジスタとが、前記出力信号と前記基準信号との間の差に応答して前記スイッチの前記第2の端子において前記エラー信号を制御するように構成される、前記第1のフィードバック回路と、

第7のノードと第8のノードとを含むトランジスタベースダイオードであって、前記第7のノードが前記入力信号を受け取るように配置され、前記第8のノードが前記第4のノードと前記第2の端子とに結合される、前記トランジスタベースダイオードと、

前記エラー信号を感知するように構成され、それぞれ前記第1のトランジスタと前記第2のトランジスタとにおいて実質的に等しい電流を維持するために前記第2のノードと前記第4のノードとにおいてテール電流を生成するように構成され、それにより、前記出力信号の電圧を前記基準信号の電圧に実質的に等しくする、第2のフィードバック回路と、

前記第2のフィードバック回路に結合される適合フィルタであって、前記第2のフィードバック回路の利得を、閾値周波数より大きい動作周波数での前記第1のフィードバック回路の利得より小さく低減するように構成される、前記適合フィルタと、

を含む、回路。

【請求項12】

請求項11に記載の回路であって、

前記第2の端子に結合されるフィルタ回路であって、前記トランジスタベースダイオードに関連付けられる極を、前記回路のユニティゲイン帯域幅の外に移すように構成される、前記フィルタ回路を更に含む、回路。

【請求項13】

請求項11に記載の回路であって、

前記適合フィルタが少なくとも1つの抵抗器とキャパシタとを含む、回路。

【請求項14】

請求項11に記載の回路であって、

前記第2のフィードバック回路が、

前記スイッチの前記第2の端子に結合される第3のトランジスタであって、前記トランジスタベースダイオードの電流をミラーするように構成される、前記第3のトランジスタと、

第4のトランジスタと第5のトランジスタとを含む電流ミラー回路であって、前記第4のトランジスタが前記第3のトランジスタに結合され、前記第5のトランジスタが前記第3のノードと前記第6のノードとに結合され、それにより、前記第1のトランジスタと前記第2のトランジスタとからテール電流をシンクし、前記第4のトランジスタが、前記第3のトランジスタから電流をソースするように構成され、前記第5のトランジスタが、前記第4のトランジスタにおいて前記第3のトランジスタからソースされる前記電流の実質的に2倍である前記第5のトランジスタにおける前記テール電流として、前記第5のトランジスタと、

10

20

30

40

50

ンジスタにおいて電流をミラーするように構成される、前記電流ミラー回路と、

を含む、回路。

【請求項 15】

請求項 14 に記載の回路であって、

前記第 5 のトランジスタが前記第 4 のトランジスタの幾何学的寸法の実質的に 2 倍の幾何学的寸法を有する、回路。

【請求項 16】

請求項 14 に記載の回路であって、

前記スイッチが金属酸化物半導体 (MOS) トランジスタである、回路。

【請求項 17】

請求項 16 に記載の回路であって、

前記トランジスタベースダイオードが前記スイッチより小さな幾何学的寸法とされる、

回路。

【請求項 18】

請求項 14 に記載の回路であって、

前記第 5 のトランジスタにおける前記テール電流が、前記トランジスタベースダイオードにおいて流れる電流の 2 倍である、回路。

【請求項 19】

請求項 14 に記載の回路であって、

前記第 3 のノードと前記第 6 のノードとを接地サプライに結合する第 1 のバイアス回路

であって、前記第 1 のトランジスタと前記第 2 のトランジスタとから第 1 のテール電流を

シンクするように構成される、前記第 1 のバイアス回路を更に含む、回路。

【請求項 20】

請求項 19 に記載の回路であって、

前記第 2 のトランジスタにおいてバイアス電流を提供するように構成される第 2 のバイ

アス回路を更に含む、回路。

【発明の詳細な説明】

【技術分野】

【0001】

本願は、概して電子回路に関し、更に特定して言えば低ドロップアウト電圧レギュレ

タに関連する。

【背景技術】

【0002】

電圧レギュレータは、入力電圧及び負荷電流の変動に関係なく、レギュレートされた出

力電圧を電子デバイスに提供するように構成される。携帯電話などの種々のポータブル電

子デバイスが、電子デバイスの電力消費を低減するために低ドロップアウト電圧を備えた

電圧レギュレータを用いる。このような電圧レギュレータは、本明細書では低ドロップア

ウト (LDO) レギュレータと称する。これらの電圧レギュレータは、低負荷電流での低

静止電流、及び負荷電流範囲にわたる正確な電圧出力を達成するという目的を備えて設計

される。幾つかの使用シナリオにおいて、電圧レギュレータからの電力を用いる電子的構

成要素により提供される負荷は継続的に変化する。例えば、スタンバイモードの間電子的

構成要素における電流消費（例えば、負荷電流）は、標準モードにおける電流消費より少

ない。このようなシナリオにおいて、システムオンチップ (SOC) がスタンバイモード

LDO に切り替える。このようなスタンバイモード LDO レギュレータは、出力電圧の不

充分なレギュレーションを提供する。例えば、スタンバイモード LDO は、負荷の変動と

共に一定ではない出力電圧を提供する。電圧レギュレータにおける低電力消費を達成する

潜在的な利点を考慮すると、負荷電流範囲にわたって正確な LDO 出力電圧を保つことが

重要である。

【発明の概要】

【0003】

10

20

30

40

50

記載される例において、回路が、レギュレートされた出力電圧を提供するように構成される。少なくとも一つの実施例において、回路が、スイッチ、第1のフィードバック回路、及び第2のフィードバック回路を含む。スイッチは、第1の端子、第2の端子、及び第3の端子を含む。スイッチは、第1の端子において入力信号を及び第2の端子においてエラー信号を受け取るように構成される。スイッチはまた、入力信号及びエラー信号に応答して第3の端子において出力信号を生成するように構成される。第1のフィードバック回路は、エラー信号を制御するために第1のトランジスタ及び第2のトランジスタを含む。第1のトランジスタは、第1のノード、第2のノード、及び第3のノードを含む。第2のトランジスタは、第4のノード、第5のノード、及び第6のノードを含む。第1のノード及び第2のノードはスイッチの第3の端子に結合され、そのため、第1及び第2のノードの各々が出力信号を受け取るように配置される。第5のノードは基準信号を受け取るように配置され、第4のノードは第2の端子に結合され、そのため、第4のノードはエラー信号を制御するように配置される。第3のノード及び第6のノードは互いに結合される。第1のトランジスタ及び第2のトランジスタは、出力信号と基準信号との間の差に応答してスイッチの第2の端子においてエラー信号を制御するように構成される。第2のフィードバック回路は、エラー信号を感知するように、及び、それぞれ、第1のトランジスタ及び第2のトランジスタにおいて実質的に等しい電流を維持するために第2のノード及び第4のノードにおいてテール電流を生成するように構成され、それにより、出力信号の電圧を、基準信号の電圧に実質的に等しくする。

## 【0004】

別の実施例において、回路が、スイッチ、第1のフィードバック回路、及び第2のフィードバック回路を含む。スイッチは、第1の端子、第2の端子、及び第3の端子を含む。スイッチは、第1の端子において入力信号を及び第2の端子においてエラー信号を受け取るように構成される。スイッチはまた、入力信号及びエラー信号に応答して第3の端子において出力信号を生成するように構成される。第1のフィードバック回路は、エラー信号を制御するために第1のトランジスタ及び第2のトランジスタを含む。第1のトランジスタは、第1のノード、第2のノード、及び第3のノードを含む。第2のトランジスタは、第4のノード、第5のノード、及び第6のノードを含む。第1のノード及び第2のノードは、スイッチの第3の端子に結合され、そのため、第1及び第2のノードの各々が出力信号を受け取るように配置される。第5のノードは基準信号を受け取るように配置され、第4のノードは第2の端子に結合され、そのため、第4のノードはエラー信号を制御するように配置される。第3のノード及び第6のノードは互いに結合される。第1のトランジスタ及び第2のトランジスタは、出力信号と基準信号との間の差に応答してスイッチの第2の端子においてエラー信号を制御するように構成される。回路はまた、第7のノード及び第8のノードを含むトランジスタベースのダイオードを含む。第7のノードは入力信号を受け取るように配置され、第8のノードは、第4のノード及び第2の端子に結合される。

## 【0005】

少なくとも一つの実施例において、第2のフィードバック回路は、エラー信号を感知するように、及び、それぞれ、第1のトランジスタ及び第2のトランジスタにおいて実質的に等しい電流を維持するために第2のノード及び第4のノードにおいてテール電流を生成するように構成され、それにより、出力信号の電圧を、基準信号の電圧に実質的に等しくする。回路はまた、第2のフィードバック回路に結合される適合フィルタを含む。適合フィルタは、第2のフィードバック回路の利得を、閾値周波数より大きい動作周波数での第1のフィードバック回路の利得より小さく低減するように構成される。

## 【図面の簡単な説明】

## 【0006】

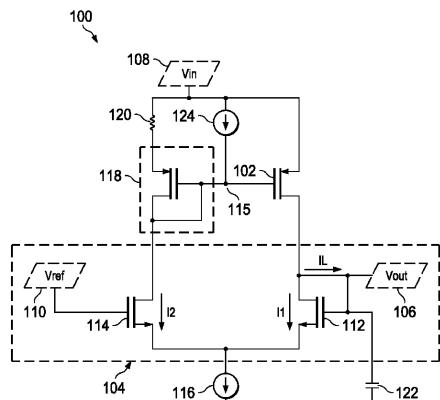

【図1】例示のシナリオに従った例示の低ドロップアウト電圧レギュレータの回路図である。

## 【0007】

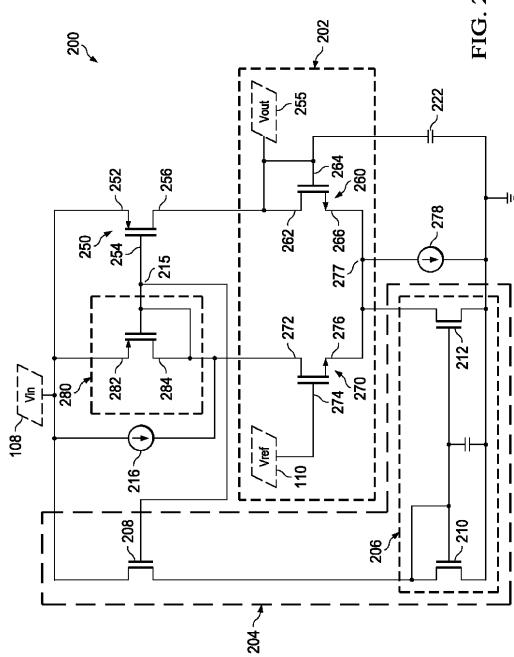

【図2】一実施例に従った電圧レギュレータの回路図である。

10

20

30

40

50

## 【0008】

【図3】別の実施例に従った電圧レギュレータの回路図である。

## 【発明を実施するための形態】

## 【0009】

低ドロップアウト電圧レギュレータ100の例示の回路表現を図1に示す。低ドロップアウト電圧レギュレータ100は、電圧レギュレータの一例である。電圧レギュレータ100はスイッチ102を含み、スイッチ102は、入力信号108(スイッチ102の第1の端子への $V_{in}$ として示される)を受信し、入力信号108に応答して出力信号106(スイッチ102の第2の端子からの $V_{out}$ として示される)を提供する。この例では、電圧レギュレータ100は、スイッチ102の出力信号106を制御するエラー信号を(スイッチ102の第3の端子において)提供するように構成されるフィードバック回路104を含む。入力信号108は、レギュレートされていない入力電圧であり、 $V_{out}$ はレギュレートされた出力電圧である。図1に示すように、フィードバック回路104は、 $V_{out}$ を受け取るように構成される第1のトランジスタ112と、基準電圧110( $V_{ref}$ として示される)を受け取るように構成される第2のトランジスタ114とを含む差動増幅器回路である。一例において、フィードバック回路104は、 $V_{out}$ 及び $V_{ref}$ 間の差に基づいてノード115における信号(以降では「エラー信号」と称する)を制御するように構成される。スイッチ102(スイッチ102のゲートなど)に提供されるノード115におけるエラー信号は、 $V_{out}$ を $V_{ref}$ に実質的に等しくなるようにレギュレートする。図1に示すように、電圧レギュレータ100はまた、スイッチ102の第3の端子と入力信号108との間に結合される衰退(degeneration)抵抗器120を備えたダイオード118を含む。ダイオード118は、スイッチ102に関連付けられる極(pole)を、電圧レギュレータ100の動作周波数以外の周波数に移すように構成される。電圧レギュレータ100は、バイアス回路116(電流シンクなど)とバイアス回路124(電流源など)とを含み、バイアス回路124は、実質的に等しいバイアス電流を第1のトランジスタ112及び第2のトランジスタ114に提供するように構成される。例えば、バイアス回路124は一定の電流 $I_{b/2}$ を提供し、バイアス回路116は一定の電流 $I_b$ を引き出す。

## 【0010】

出力信号( $V_{out}$ )106は負荷(図示せず)に提供される。幾つかの例示のシナリオにおいて、負荷の異なるモードに基づいて負荷電流が変化し得る。例えば、負荷は、アクティブモード、パワーダウンモード、及びスタンバイモードなど、異なるオペレーションモードを有するデバイスであり得る。従って、負荷の電流要件は、負荷の異なるオペレーションモード毎に変化し得る。負荷電流におけるこのような変化は、 $V_{out}$ 106の増大/低減を引き起こし、それにより粗悪なDC負荷レギュレーションにつながる。例えば、回路100における負荷電流が増大又は減少するので、第1のトランジスタ112を介して流れる電流( $I_1$ など)及び第2のトランジスタ114を介して流れる電流( $I_2$ など)に差が存在する。電流 $I_1$ 及び $I_2$ におけるこのような差は、固定電流 $I_b$ に起因する。

## 【0011】

例えば、負荷電流が増大する場合、ダイオード118における電流が、増大し、電流 $I_1$ を電流 $I_2$ より小さくする。電流 $I_1$ が電流 $I_2$ より小さくなるので、 $V_{out}$ 106が減少する。負荷電流の変動に応じた $V_{out}$ 106の減少のこのような現象は、例示の電圧レギュレータ100において粗悪なDC負荷レギュレーションを提供する。一例において、 $I_1$ 及び $I_2$ の合計は $I_b$ に等しい。良好なDC負荷レギュレーション( $V_{ref} = V_{out}$ )では、 $I_1$ は $I_2$ に等しくなるべきであり、そのため、 $I_1 = I_2 = I_b/2$ である。ここでは、 $I_1$ は第1のトランジスタ112における電流であり、 $I_2$ は第2のトランジスタ114における電流であり、 $I_b$ はバイアス回路(電流シンク)116を流れる電流であり、 $I_b/2$ はバイアス回路(電流源)124を流れる電流である。更に、電流 $I_2$ は、 $I_b/2$ (バイアス回路(電流源)124における電流)及び $I_{T3}$ (ダ

イオード 118 を流れる電流 ) の合計に等しい。従って、I1 が Ib / 2 に等しくなるには、IT3 はゼロ電流に等しくなるべきである。所与の負荷電流 Iload では、IT3 = IT4 / N であり ( N は、ダイオード 118 の抵抗器衰退、及びダイオード 118 とスイッチ 102 との間の比に因る ) 、ここで、IT3 はダイオード 118 における電流であり、IT4 はスイッチ 102 における電流である。電流 IT3 及び IT4 は下記式によつて定義され得る。

$$IT4 = ( Iload + Ib / 2 - Ierror )$$

$$IT3 = ( Iload + Ib / 2 - Ierror ) / N$$

$$Ierror = ( Iload + Ib / 2 ) / ( N + 1 )$$

ここで、Ierror はダイオード 118 を介する電流である。

10

#### 【0012】

N がおよそ 1000 など非常に大きい場合、IT3 は、Iload / N に実質的に等しい。従って、負荷電流 ( Iload ) における増大と共に、IT3 が増大する。I2 は IT3 と Ib / 2 の合計であるため、IT3 が増大するにつれて I2 も増大し、I1 は、電流 Ib を維持するため低減する。I1 の低減など、I1 及び I2 におけるこのようなミスマッチは Vout を低減させ、それにより、回路 100 における粗悪な DC 負荷レギュレーションを起こす。

#### 【0013】

種々の実施例が、現在利用可能な利点を提供することに加えて、上述の制約及び他の制約を克服するために負荷電流の変化に関係なく出力電圧をレギュレートすることが可能な解決策を提供する。種々の実施例を、図 2 及び図 3 に関連して本明細書に開示する。

20

#### 【0014】

図 2 は、一実施例に従った電圧レギュレータ回路 200 の回路図である。回路 200 は、スイッチ 250 などのスイッチを含む。スイッチ 250 の一例は、図 1 を参照して説明したスイッチ 102 である。一実施例において、スイッチ 250 は、端子 252 ( 第 1 の端子 ) において入力信号 108 ( Vin 参照 ) を、及び端子 254 ( 第 2 の端子 ) においてエラー信号を受信し、入力信号 108 及びスイッチ 250 の端子 254 に接続されるノード 215 において受信されるエラー信号に応答して、スイッチ 250 の端子 256 ( 第 3 の端子 ) において出力信号 255 ( Vout として示される ) を提供する。スイッチ 250 を流れる電流が、スイッチ 250 の端子 254 にフィードされるエラー信号により制御される。例示の一実施例において、スイッチ 250 は、NMOS トランジスタ又は PMOS トランジスタなどの、MOS トランジスタであり得る。代替の実施例において、スイッチ 250 は、他の電界効果トランジスタ ( FET ) 及びバイポーラ接合トランジスタ ( BJT ) として構成され得る。

30

#### 【0015】

例示の実施例において、電圧レギュレータ 200 は、エラー信号を制御するために第 1 のフィードバック回路 202 を含む。この例示の実施例において、第 1 のフィードバック回路 202 は、トランジスタ 260 ( 第 1 のトランジスタ ) 及びトランジスタ 270 ( 第 2 のトランジスタ ) によって形成される差動増幅器を含む。例示の一実施例において、トランジスタ 260 及び 270 は、スイッチ 250 の構成に応じて、NMOS 又は PMOS トランジスタとし得る。図 2 に示すように、トランジスタ 260 は、ノード 262、264、及び 266 を含み、トランジスタ 270 は、ノード 272、274、及び 276 を含む。

40

#### 【0016】

ノード 262 ( 第 1 のノード ) 及びノード 264 ( 第 2 のノード ) は、出力信号 255 を受け取るためスイッチ 250 の端子 256 に結合される。トランジスタ 270 のノード 274 ( 第 5 のノード ) が、基準信号 110 ( Vref として示される ) を受け取るよう構成される。ノード 272 ( 第 4 のノード ) が、エラー信号を制御するため第 2 の端子 254 ( 又はノード 215 ) に結合される。ノード 266 ( 第 3 のノード ) 及びノード 276 ( 第 6 のノード ) が、互いに結合され ( ノード 277 参照 ) 、第 1 のバイアス回路 2

50

78を介して接地と結合される。トランジスタ260及び270は、Vout及びVref間の差に応答して、スイッチ250の第2の端子254においてエラー信号を制御するように構成される。

#### 【0017】

一実施例において、回路200は、第1のバイアス回路278、第2のバイアス回路216、及びトランジスタベースのダイオード280（後述では、ダイオード280と称する）を含む。一実施例において、第1のバイアス回路278はノード277及び接地間に結合され、第1のバイアス回路278は、バイアス電流をトランジスタ260及び270に提供するように構成される。一実施例において、第1のバイアス回路278は、トランジスタ260及び270を流れる一定の総電流を維持するように、及びトランジスタ260及び270において一定のDCバイアスを維持するように構成される。ここでは、第1のバイアス回路278を、トランジスタ260及び270から一定の電流をシンクする電流シンク回路として示す。しかし、第1のバイアス回路278は、特定の回路要素（トランジスタなど）又は回路要素の組合せ（増幅器、ダイオード、抵抗器、及びトランジスタなど）を用いることによるなど、種々の方式で構成され得る。一実施例において、ダイオード280は、スイッチ250の第1のノード252と第2のノード254との間に結合される。ダイオード280は、入力信号108（Vin参照）を受け取るように配置されるノード282（第7のノード）、及びノード272（第4のノード）及び端子254に結合されるノード284（第8のノード）を含む。一実施例において、ダイオード280は、回路200の伝達関数における極を補償するように構成される。例えば、スイッチ250は、一層高い負荷条件で回路200を不安定にする回路伝達関数において極を導入する。一実施例において、ダイオード280は、スイッチ250に関連付けられる極を、高負荷電流で回路200を安定にするために回路100の動作周波数以外の周波数に移すように構成される。この実施例において、ダイオード280は、共に結び付けられた2つの端子を備えたトランジスタにより実装される。一実施例において、スイッチ250は、幾何学的にダイオード280の寸法のN倍の寸法とされ、スイッチ250を流れる電流はダイオード280を流れる電流のN倍である。

#### 【0018】

回路100は、スイッチ250の端子252とトランジスタ270のノード272との間に結合される第2のバイアス回路216を含む。一実施例において、負荷電流が低であるとき、ダイオード280が、オフにされ、第1のフィードバック回路202におけるトランジスタ260及び270に対して実質的にゼロバイアス電流を提供する。この実施例において、第2のバイアス回路216は、非負荷条件下でトランジスタ260及び270における電流をバイアスするように構成される。例えば、非常に低い負荷電流では、スイッチ250に接続されるダイオード280はオフ状態に入り、トランジスタ260及び270を流れるバイアス電流はない。従って、ダイオード280及び電流シンク（第1のバイアス回路278）に並列の電流源（第2のバイアス回路216）が、ゼロ負荷電流で良好なDC負荷レギュレーションを維持するようにトランジスタ260及び270のテールとして付加される。一実施例において、第2のバイアス回路216における電流が、固定であり、ゼロ負荷電流におけるDC負荷レギュレーションを維持するように第1のバイアス回路278により引き出されるバイアス電流の半分を提供する。回路200は、トランジスタ260のノード264と接地との間に結合されるキャパシタ222を含む。キャパシタ222は、負荷遷移（図示せず）の間、負荷にフィードされる出力信号255を保持するように構成される。

#### 【0019】

この例示の実施例において、電圧レギュレータ回路200は、トランジスタ260及び270において実質的に等しい電流（それぞれ、I1及びI2）を維持するように構成される第2のフィードバック回路204を含む。これらの電流は、別の状況では負荷電流における変動を有する回路100において等しくない。従って、電圧レギュレータ回路200は良好なDC負荷レギュレーションを提供する。第2のフィードバック回路204の例

10

20

30

40

50

示の実施例を図 2 に示す。

【0020】

一実施例において、第 2 のフィードバック回路 204 は、スイッチ 250 の第 2 のノード 254 とノード 277 との間に結合される。一実施例において、第 2 のフィードバック回路 204 は、負荷電流における増大 / 低減に起因するダイオード 280 を介する電流を補償するように構成され、そのため、トランジスタ 260 及び 270 における電流が等しくなり、それにより、出力電圧 255 がレギュレートされる。

【0021】

一実施例において、第 2 のフィードバック回路 204 は、スイッチ 250 のノード 254 にフィードされるエラー信号を感知するように構成される。このエラー信号は、負荷電流の増大 / 減少に比例する。例えば、負荷電流が増大又は減少するとき、トランジスタ 260 及び 270 における電流 ( それぞれ、  $I_1$  及び  $I_2$  ) が変化し、そのため、エラー信号も変化し、従って、第 2 のフィードバック回路 204 により感知される電流も変化する。一実施例において、( a ) 第 2 のフィードバック回路 204 は電流ミラー回路 206 を含み、及び ( b ) トランジスタ 208 ( 第 3 のトランジスタ ) が、ダイオード 280 とともに別の電流ミラー回路を形成する。

【0022】

例示の一実施例において、トランジスタ 208 及びダイオード 280 は、電流ミラー回路を形成する。電流ミラー回路 206 は、トランジスタ 210 ( 第 4 のトランジスタ ) 及びトランジスタ 212 ( 第 5 のトランジスタ ) を含み、これらは、負荷電流における変化を補償するような幾何学的寸法とされる。トランジスタ 210 はトランジスタ 208 に結合され、トランジスタ 212 は、トランジスタ 260 及び 270 からテール電流をシンクするように第 3 のノード 266 及び第 6 のノード 276 ( ノード 266 及び 276 に結合されるノード 277 など ) に結合される。トランジスタ 210 は、トランジスタ 208 から電流をソースするように構成され、トランジスタ 212 は、トランジスタ 210 を介する電流の実質的に 2 倍の ( トランジスタ 260 及び 270 の ) テール電流としてトランジスタ 210 における電流をミラーするように構成される。この実施例において、トランジスタ 212 は、トランジスタ 210 の寸法の 2 倍であり、トランジスタ 208 は、感知された電流 ( エラー信号に起因してノード 215 から感知された電流など ) を受け取るように構成される。ダイオード 280 を流れる電流の 2 倍が、トランジスタ 212 においてテール電流として引き出される。これは、ダイオード 280 における電流がトランジスタ 208 においてミラーされ、トランジスタ 208 を流れる電流の 2 倍がトランジスタ 212 においてミラーされるためである。この実施例において、テール電流 (  $2 \times I_{T3}$  など ) は、トランジスタ 260 及び 270 を流れる電流における増大 / 減少を補償し、それにより、負荷電流変動に関係なく  $V_{out}$  をレギュレートする。

【0023】

図 3 は、一実施例に従った低ドロップアウト電圧レギュレータ回路 300 の回路図である。図 3 は集積回路の一部であり得る回路 300 を表す。図 3 に示すように、回路 300 は、スイッチ 250 、差動増幅器回路 ( 第 1 のフィードバック回路 202 など ) 、第 1 のバイアス回路 278 、トランジスタベースのダイオード 280 、及び第 2 のバイアス回路 350 を含む。スイッチ 250 、第 1 のフィードバック回路 202 、第 1 のバイアス回路 278 、及びダイオード 280 は、既に図 2 を参照して説明されている。この例では、スイッチ 250 は、図 2 に示すような入力信号 (  $V_{in}$  ) 108 の代わりに電力供給入力 (  $V_{DD}$  ) 325 を受け取り、基準信号 110 に応答して出力信号 355 がレギュレートされる。

【0024】

回路 300 は第 2 のフィードバック回路 350 を含み、これは、第 2 のフィードバック回路 206 における回路要素、及び付加的な回路要素を含む。例えば、第 2 のフィードバック回路 350 は、トランジスタ ( 第 3 のトランジスタ 208 など ) 、電流ミラー回路 ( トランジスタ 210 及び 212 によって形成される電流ミラー回路 206 など ) 、及び適

10

20

30

40

50

合フィルタ302を含む。一実施例において、適合フィルタ302は、高い動作周波数での回路300の安定性を改善するためトランジスタ210と212のゲート端子間に結合される。第1のフィードバック回路202によって提供される負のフィードバックループ利得は、一層高い動作周波数で回路300を安定に維持するために第2のフィードバック回路350によって提供される正のフィードバックループ利得より大きくすべきである。一実施例において、適合フィルタ302は、(ノード215からの感知された電流の)感知された信号に関連付けられる高周波数信号を減衰させるローパスフィルタであり、高い動作周波数でトランジスタ208を介してミラーされる。高い動作周波数での感知された信号のこのような減衰は、第2のフィードバック回路350の正のフィードバックループ利得を低減し、高い動作周波数で回路300を安定にする。一実施例において、適合フィルタ302は、負荷電流における変化に適合し、適合フィルタ302のカットオフ周波数は、負荷電流とともに変化する。

#### 【0025】

この実施例において、適合フィルタ302は、トランジスタ304、第1の抵抗器306(MOSトランジスタとして構成される)、第2の抵抗器308(MOSトランジスタとして構成される)、及びキャパシタ214を含む。一実施例において、トランジスタ304は、(トランジスタ208を介してスイッチ250の第2のノード254からの)感知された電流を受け取るように、及び抵抗器306及び308の両端の感知された電流に関連付けられる電圧を提供するように構成される。抵抗器306及び308は例示の目的のために示されており、回路300は、適合フィルタ302におけるより少ない又はより多い抵抗器を含む。この実施例において、抵抗器306及び308はNMOSトランジスタとして実装される。代替として、抵抗器306及び308は、PMOSトランジスタ、又はPMOSトランジスタ及びNMOSトランジスタの組合せを用いて実装され得る。適合フィルタ302はまた、特定の回路要素、又は、抵抗器、キャパシタ、増幅器、トランジスタ、及びダイオードなどの回路要素の組み合わせを用いて、種々の方式で実装され得る。

#### 【0026】

図3に示すように、回路300は、スイッチ250のノード252と254との間に結合されるフィルタ回路310を含む。一実施例において、フィルタ回路310は、スイッチ250に結合されるダイオード280に関連付けられる極を、回路300のユニティゲイン帯域幅より高い周波数にシフトするように構成されるトランジスタ312、314、及びキャパシタ316を含む。図3に示すフィルタ回路310は単なる例であり、特定の回路要素又は回路要素の組み合わせ(抵抗器、キャパシタ、増幅器、トランジスタ、及びダイオードなど)を用いて種々の方式で構成され得る。

#### 【0027】

一実施例において、回路300の伝達関数は次のように表され得る。

$$H(s) = \frac{-gmp\{(N-2)gm1.gmt - 2.gmt.g_L\}(1+S.\omega z)}{(gmt+SCx)\{gm1+2g_L+S.2.C_L\}(gmp+SC_p)}$$

ここで、

$$\omega Z = \frac{NC_xgm1-2gmtC_L}{(N-2).gm1.gmt-2gmt.g_L}$$

である。この実施例において、gmpは、ダイオード280及びトランジスタ208のトランスクンダクタンスである。スイッチ250はダイオード280の「N」倍の寸法とされ、スイッチ250のトランスクンダクタンスはN × gmpである。トランジスタ270のトランスクンダクタンスはgm1であり、gmtは、下記により与えられる、電流ミラーアンプ回路206及び適合フィルタ回路302の総トランスクンダクタンスである。

10

20

30

40

$$gmt = \frac{gm2}{1+gm2.Rx}$$

ここで、 $gm2$  は、電流ミラー回路 206 におけるトランジスタ 210 のトランスコンダクタンスであり、 $R_x$  は、ローパスフィルタとして構成される適合フィルタ回路 302 において抵抗器 306 及び 308 により提供される抵抗であり、 $g_L$  は負荷（図示せず）により提供されるトランスコンダクタンスである。一実施例において、 $C_L$  及び  $C_x$  は、それぞれ、キャパシタ 222（負荷キャパシタ）及びキャパシタ 214（フィルタ静電容量）の静電容量である。一実施例において、第 1 のフィードバック回路 202 によって提供される負のフィードバックループ利得は、回路 300 を安定に維持するために第 2 のフィードバック回路 350 によって提供される正のフィードバックループ利得より大きい。

10

$z$  が LHP にあるようにするため又は一層良好な位相マージン（回路 300 の安定性）のための条件は下記式により与えられ、

$$\frac{N * gm1}{2C_L} \geq \frac{gmt}{C_x}$$

これは、 $gmt$  及び  $C_x$  の値、及びその他の値の選択によって達成され得る。

【0028】

一つ又は複数の例示の実施例が、負荷電流における変動と共に良好な DC 負荷レギュレーションを提供することが可能な回路を提供する。この回路は、静止電流の増大なしに一層高い負荷電流までスケーリング可能である。第 2 のフィードバック回路は、負荷電流の増大と共に静止電流を適合的に増大させる。第 2 のフィードバック回路はまた、出力電圧が、レギュレートされ、負荷電流変化にわたって正確であることを確実にする。回路の安定性は、第 1 のフィルタ回路及び適合フィルタ回路を用いることにより著しく増大される。第 1 のフィルタ回路は、スイッチに結合されたダイオードに関連付けられる極を、回路の動作周波数以外の周波数へ移すように構成される。適合フィルタ回路は、第 2 のフィードバック回路に関連付けられる回路の正のフィードバックループ利得が常に、第 1 のフィードバック回路に関連付けられる負のフィードバックループ利得より低いことを確実にし、それにより、回路を安定に維持し、一層高い動作周波数及び増大された負荷電流でリンクギングを取り除く。

20

30

【0029】

本発明の特許請求の範囲内で、説明した例示の実施例に変形が成され得、その他の実施例が可能である。

【 义 1 】

FIG. 1

【 囮 2 】

FIG. 2

【図3】

---

フロントページの続き

(72)発明者 ナイティン アガワル

インド 560075 カルナータカ, バンガロール, ジェイ ビー ナガール, シマ レ

ディ コロニー, アシュラヤ アパートメンツ 206

(72)発明者 スレシュ マララ

インド 560093 カルナータカ, バンガロール, シーブイ ラマン ナガール, カガ

ダスプラ, セブンス エイ クロス, サイ マルグ アパートメンツ 303

審査官 田中 寛人

(56)参考文献 米国特許第07843180(US, B1)

中国特許出願公開第102945059(CN, A)

米国特許出願公開第2007/0046474(US, A1)

特開2006-301787(JP, A)

特開2001-075663(JP, A)

特開2000-075941(JP, A)

(58)調査した分野(Int.Cl., DB名)

G05F 1/56

H03H 11/04