(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4505981号

(P4505981)

(45) 発行日 平成22年7月21日(2010.7.21)

(24) 登録日 平成22年5月14日(2010.5.14)

|                      |              |

|----------------------|--------------|

| (51) Int.Cl.         | F 1          |

| HO4B 1/707 (2006.01) | HO4J 13/00 D |

| HO4L 7/00 (2006.01)  | HO4L 7/00 C  |

| HO4L 27/22 (2006.01) | HO4L 27/22 Z |

請求項の数 13 外国語出願 (全 40 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2000-363847 (P2000-363847)  |

| (22) 出願日  | 平成12年10月24日 (2000.10.24)      |

| (65) 公開番号 | 特開2002-135169 (P2002-135169A) |

| (43) 公開日  | 平成14年5月10日 (2002.5.10)        |

審査請求日 平成19年3月12日 (2007.3.12)

|           |                                                                     |

|-----------|---------------------------------------------------------------------|

| (73) 特許権者 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号                              |

| (74) 代理人  | 100094053<br>弁理士 佐藤 隆久                                              |

| (72) 発明者  | エルビノ シルベイラ ソウザ<br>東京都品川区東五反田3丁目14番13号<br>株式会社ソニーコンピュータサイエンス<br>研究所内 |

| (72) 発明者  | 河野 隆二<br>東京都品川区東五反田3丁目14番13号<br>株式会社ソニーコンピュータサイエンス<br>研究所内          |

審査官 太田 龍一

最終頁に続く

(54) 【発明の名称】スペクトル拡散受信機

## (57) 【特許請求の範囲】

## 【請求項 1】

所定の拡散コードによりある帯域に拡散されたスペクトル拡散信号を受信し、逆拡散処理をアナログ形態で行うスペクトル拡散受信機であって、

所定周波数のアナログ形式の A C ローカル発振信号を出力するローカル発振器と、

A C 受信信号の拡散コードに応じてローカル拡散コードを生成するローカル拡散コード生成手段と、

上記ローカル発振器による上記 A C ローカル発振信号および上記ローカル拡散コード生成手段による上記ローカル拡散コードに基づいて A C リファレンスローカル信号をアナログ値で生成し、上記 A C 受信信号および上記 A C リファレンスローカル信号とをアナログ値のままで線形合成し、その線形合成され A C 成分を含むアナログ値を二乗してアナログ電力値を生成し、当該アナログ電力値から D C 成分を取り除くことにより、位相差を有する 2 つのアナログ値の信号を生成し、上記位相差を持つ 2 つのアナログ値の信号に基づいて逆拡散を行うダイレクトコンバージョン回路と

を具備する、

スペクトル拡散受信機。

## 【請求項 2】

上記ダイレクトコンバージョン回路は、上記受信信号の信号レベルを検波する検波器を有する、

請求項 1 に記載のスペクトル拡散受信機。

## 【請求項 3】

上記ダイレクトコンバージョン回路は、上記検波器の出力信号に対してフィルタリング処理を行うフィルタを有する、

請求項 2 に記載のスペクトル拡散受信機。

## 【請求項 4】

所定の拡散コードによりある帯域に拡散されたスペクトル拡散信号を受信し、逆拡散処理をアナログ形態で行うスペクトル拡散受信機であって、

所定周波数のアナログ形式の A C ローカル発振信号を出力するローカル発振器と、

A C 受信信号の拡散コードに応じてローカル拡散コードを生成するローカル拡散コード生成手段と、

上記ローカル発振器による上記 A C ローカル発振信号および上記ローカル拡散コード生成手段による上記ローカル拡散コードに基づいて A C リファレンスローカル信号をアナログ値で生成し、上記 A C 受信信号および上記 A C リファレンスローカル信号とをアナログ値のままで線形合成し、その線形合成され A C 成分を含むアナログ値を二乗してアナログ電力値を生成し、当該アナログ電力値から D C 成分を取り除くことにより、位相差を有する 2 つのアナログ値の信号を生成し、上記位相差を持つ 2 つのアナログ値の信号に基づいて逆拡散を行うダイレクトコンバージョン回路と

を具備する、

スペクトル拡散受信機。

## 【請求項 5】

上記ダイレクトコンバージョン回路は、上記受信信号の信号レベルを検波する検波器を有する、

請求項 4 に記載のスペクトル拡散受信機。

## 【請求項 6】

上記ダイレクトコンバージョン回路は、上記検波器の出力信号に対して所定のフィルタリング処理を行うフィルタを有する、

請求項 5 に記載のスペクトル拡散受信機。

## 【請求項 7】

上記リファレンスローカル信号に含まれる拡散コードは、上記受信信号の拡散コードに同期している、

請求項 1 に記載のスペクトル拡散受信機。

## 【請求項 8】

上記受信信号のキャリア周波数は、上記リファレンスローカル信号のキャリア周波数に略等しい、

請求項 1 に記載のスペクトル拡散受信機。

## 【請求項 9】

上記検波器は、二乗検波器を有する

請求項 5 に記載のスペクトル拡散受信機。

## 【請求項 10】

所定の拡散コードによりある帯域に拡散されたスペクトル拡散信号を受信し、逆拡散処理をアナログ形態で行うスペクトル拡散受信機であって、

所定周波数のアナログ形式の A C ローカル発振信号を出力するローカル発振器と、

A C 受信信号および上記ローカル発振器による上記 A C ローカル発振信号に基づいて同期および同期保持処理を介してローカル拡散コードを生成するローカル拡散コード同期保持手段と、

上記ローカル発振器による上記 A C ローカル発振信号および上記ローカル拡散コード同期保持手段による上記ローカル拡散コードに基づいて A C リファレンスローカル信号をアナログ値で生成し、上記 A C 受信信号および上記 A C リファレンスローカル信号とをアナログ値のままで線形合成し、その線形合成され A C 成分を含むアナログ値を二乗してアナログ電力値を生成し、当該アナログ電力値から D C 成分を取り除くことにより、位相差を

10

20

30

40

50

有する 2 つのアナログ値の信号を生成し、上記位相差を持つ 2 つのアナログ値の信号に基づいて逆拡散を行うダイレクトコンバージョン回路と

を具備する、

スペクトル拡散受信機。

【請求項 1 1】

上記ローカル拡散コード同期保持回路は、

制御信号の値に基づいて上記ローカル拡散コードを生成するローカル拡散コード生成器と、

所定の時間だけ上記生成されたローカル拡散コードを遅延させる第 1 の位相調整手段と、

所定の時間だけ上記生成されたローカル拡散コードを進行させる第 2 の位相調整手段と、

上記 A C ローカル発振信号と上記第 1 の位相調整手段の出力信号を乗算する第 1 の乗算器と、

上記 A C ローカル発振信号と上記第 2 の位相調整手段の出力信号を乗算する第 2 の乗算器と、

上記 A C 受信信号と上記第 1 の乗算器の出力信号とを加算する第 1 の加算器と、

上記第 1 の加算器の出力信号の振幅成分を検波する第 1 の検波器と、

上記第 1 の検波器の出力信号の第 1 のエンベロープを検波する第 1 のエンベロープ検波手段と、

上記 A C 受信信号と上記第 2 の乗算器の出力信号とを加算する第 2 の加算器と、

上記第 2 の加算器の出力信号の振幅成分を検波する第 1 の検波器と、

上記第 2 の検波器の出力信号の第 2 のエンベロープを検波する第 2 のエンベロープ検波手段と、

上記第 1 のエンベロープと第 2 のエンベロープ間の差がゼロに近づいて減少するように上記制御信号を生成する制御信号生成手段と

を有する、

請求項 1 0 に記載のスペクトル拡散受信機。

【請求項 1 2】

上記ローカル拡散コード同期保持回路は、

制御信号の値に基づいて上記ローカル拡散コードを生成するローカル拡散コード生成器と、

所定の時間だけ上記生成されたローカル拡散コードを遅延させる第 1 の位相調整手段と、

所定の時間だけ上記生成されたローカル拡散コードを進行させる第 2 の位相調整手段と、

上記 A C ローカル発振信号と上記第 1 の位相調整手段の出力信号を乗算する第 1 の乗算器と、

上記 A C ローカル発振信号と上記第 2 の位相調整手段の出力信号を乗算する第 2 の乗算器と、

上記 A C 受信信号の位相をシフトする第 1 の位相シフタと、

上記第 1 の乗算器の出力信号の位相をシフトする第 2 の位相シフタと、

上記第 2 の乗算器の出力信号の位相をシフトする第 3 の位相シフタと、

上記 A C 受信信号の位相をシフトする第 4 の位相シフタと、

上記第 1 の位相シフタの出力信号と上記第 1 の乗算器の出力信号とを加算する第 1 の加算器と、

上記 A C 受信信号と上記第 2 の位相シフタの出力信号とを加算する第 2 の加算器と、

上記 A C 受信信号と上記第 3 の位相シフタの出力信号とを加算する第 3 の加算器と、

上記第 2 の乗算器の出力信号と上記第 4 の位相シフタの出力信号とを加算する第 4 の加算器と、

10

20

30

40

50

上記第1の加算器の出力信号の信号レベルを検波する第1の検波器と、

上記第2の加算器の出力信号の信号レベルを検波する第2の検波器と、

上記第3の加算器の出力信号の信号レベルを検波する第3の検波器と、

上記第4の加算器の出力信号の信号レベルを検波する第4の検波器と、

上記第1の検波器の出力に対して所定のフィルタリング処理を行う第1のフィルタと、

上記第2の検波器の出力に対して所定のフィルタリング処理を行う第2のフィルタと、

上記第3の検波器の出力に対して所定のフィルタリング処理を行う第3のフィルタと、

上記第4の検波器の出力に対して所定のフィルタリング処理を行う第4のフィルタと、

上記第1および第2のフィルタの出力に基づいて第1のノルムを計算する第1のノルム回路と、

10

上記第3および第4のフィルタの出力に基づいて第2のノルムを計算する第2のノルム回路と、

上記第1のノルムと第2のノルム間の差がゼロに近づいて減少するように上記制御信号を生成する制御信号生成手段と

を有する請求項10に記載のスペクトル拡散受信機。

【請求項13】

所定の拡散コードによりある帯域に拡散されたスペクトル拡散信号を受信し、逆拡散処理をアナログ形態で行うソフトウェア無線用スペクトル拡散受信機であって、

所定周波数のアナログ形式のA Cローカル発振信号を出力するローカル発振器と、

A C受信信号および上記ローカル発振器による上記A Cローカル発振信号に基づいて同期および同期保持処理を介してローカル拡散コードを生成するローカル拡散コード同期保持手段と、

20

上記ローカル発振器による上記A Cローカル発振信号および上記ローカル拡散コード同期保持手段による上記ローカル拡散コードに基づいてA Cリファレンスローカル信号をアナログ値で生成し、上記A C受信信号および上記A Cリファレンスローカル信号とをアナログ値のままで線形合成し、その線形合成されたA C成分を含むアナログ値を二乗してアナログ電力値を生成し、当該アナログ電力値からD C成分を取り除くことにより、位相差を有する2つのアナログ値の信号を生成し、上記位相差を持つ2つのアナログ値の信号に基づいて逆拡散を行うダイレクトコンバージョン回路と

を具備する、

30

スペクトル拡散受信機。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、ソフトウェア無線用のスペクトル拡散受信機、特に、F E T広帯域ダイレクトコンバージョン回路に基づくダイレクトシーケンス（直接拡散）R Fスペクトル拡散信号のアナログ逆拡散およびダイレクトコンバージョン用回路、および異なるタイプのダイレクトシーケンススペクトル拡散のP N（疑似ランダムノイズ）符号同期および逆拡散用回路に関するものである。

【0002】

40

【従来の技術】

ソフトウェア無線の基本概念は、ソフトウェアの制御の下、異なるフォーマット、すなわち異なる変調方式の信号を受信する無線機を容易に再構成可能のように、可能な限りデジタル処理を利用するにある。シングルステージのR Fダウンコンバージョンを利用すると、無線機は、大いに簡易化される。近年、二乗検波に基づくF E T検波器の利用に基づくダイレクトコンバージョン用の新規な回路が提案されている（文献〔1〕、〔2〕を参照：〔1〕M.Abe,N.Sasho,D.Krupezevic, and V.Brankovic, "Receiver circuit", 〔2〕W099/33166('99.July.1)）。これらの回路は、以前可能であったよりも、高い帯域性および線形性をともなったダイレクトコンバージョン回路の実現を可能にする。

【0003】

50

直接拡散（ダイレクトシーケンス）スペクトル拡散受信機に関するダイレクトコンバージョン回路の使用は、上述したシングルステージコンバータの利益よりはるかに大きい利益を有する。シングルステージコンバータに加えて、ダイレクトコンバージョン回路は、アナログ相関器として効果的に動作する。このことは、結果としてスペクトル拡散受信機に要求される処理速度の大幅な低減およびこれに伴う電力消費の削減につながる。

【0004】

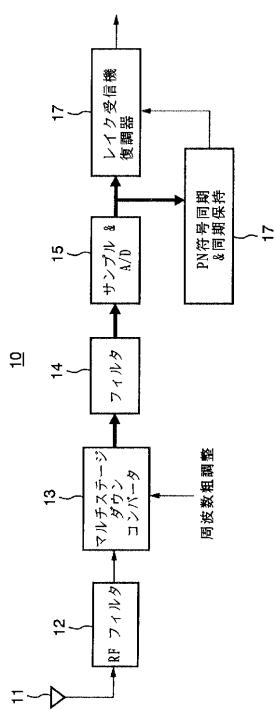

図1は、従来の直接拡散スペクトル拡散受信機のブロック図である。

図1の直接拡散スペクトル拡散受信機10は、レシーバアンテナ11、RFフィルタ12、マルチステージコンバータ13、RFフロント-エンドノイズ削減フィルタ14、サンプルおよびアナログ-デジタル（A/D）コンバータ15、PNコード同期および同期保持回路16、およびレイク（RAKE）受信機（復調器）17を有している。

10

【0005】

図1に示すように、直接拡散スペクトル拡散受信機10の代表的なインプリメンテーションは、チップレートの複数倍、たとえばチップレート8倍の周波数で動作するサンプルおよびA/Dコンバータ15が後続するRFフロント-エンドノイズ削減フィルタ14を含んでいる。3X帯域における広帯域CDMA（符号分割多元接続）では、このチップレートは、 $8 \times 3 \cdot 84 = 30 \cdot 72 \text{ MHz}$ に等しい。さらに高い帯域では、そのレートは100MHzを簡単に越えてしまう。受信機は、PNコード同期および同期保持回路16を動作させて、これらのレートでデジタルで逆拡散を行う。

【0006】

20

【発明が解決しようとする課題】

受信機がアンテナダイバーシティ、あるいはデジタルビーム形成アレイを利用していると、この回路は、各アレイ要素ごとに繰り返される。大きな拡散帯域については、回路の複雑さ、これに伴う電力消費が大きくなる。

【0007】

チップレートよりシンボルレートの倍数のクロック周波数で動作させることは、受信機の設計に有利となる。このことは、逆拡散がアナログ形態で効果的に実行されれば可能である。

【0008】

本発明の第1の目的は、回路の複雑さがチップレートと無関係で、非常に高チップレートの電力効率のよいスペクトル拡散システムの設計が可能であり、電力消費を削減可能なスペクトル拡散受信機を提供することにある。

30

【0009】

本発明の第2の目的は、チップレートの代わりにデータシンボルレートでデジタル処理を行うことが可能なソフトウェア無線用スペクトル拡散受信機を提供することにある。

【0010】

本発明によれば、所定の拡散コードによりある帯域に拡散されたスペクトル拡散信号を受信し、逆拡散処理をアナログ形態で行うスペクトル拡散受信機であって、所定周波数のアナログ形式のACローカル発振信号を出力するローカル発振器と、

AC受信信号の拡散コードに応じてローカル拡散コードを生成するローカル拡散コード生成手段と、

40

上記ローカル発振器による上記ACローカル発振信号および上記ローカル拡散コード生成手段による上記ローカル拡散コードに基づいてACリファレンスローカル信号をアナログ値で生成し、上記AC受信信号および上記ACリファレンスローカル信号とをアナログ値のままで線形合成し、その線形合成されたAC成分を含むアナログ値を二乗してアナログ電力値を生成し、当該アナログ電力値からDC成分を取り除くことにより、位相差を有する2つのアナログ値の信号を生成し、上記位相差を持つ2つのアナログ値の信号に基づいて逆拡散を行うダイレクトコンバージョン回路と

を具備する、スペクトル拡散受信機が提供される。

【0011】

50

本発明によれば、所定の拡散コードによりある帯域に拡散されたスペクトル拡散信号を受信し、逆拡散処理をアナログ形態で行うスペクトル拡散受信機であって、

所定周波数のアナログ形式の A C ローカル発振信号を出力するローカル発振器と、

A C 受信信号の拡散コードに応じてローカル拡散コードを生成するローカル拡散コード生成手段と、

上記ローカル発振器による上記 A C ローカル発振信号および上記ローカル拡散コード生成手段による上記ローカル拡散コードに基づいて A C リファレンスローカル信号をアナログ値で生成し、上記 A C 受信信号および上記 A C リファレンスローカル信号とをアナログ値のままで線形合成し、その線形合成され A C 成分を含むアナログ値を二乗してアナログ電力値を生成し、当該アナログ電力値から D C 成分を取り除くことにより、位相差を有する 10 2 つのアナログ値の信号を生成し、上記位相差を持つ 2 つのアナログ値の信号に基づいて逆拡散を行うダイレクトコンバージョン回路と

を具備する、スペクトル拡散受信機が提供される。

【 0 0 1 3 】

また、本発明では、上記第 1 の検波器の出力信号に対して所定のフィルタリング処理を行う第 1 のフィルタと、上記第 2 の検波器の出力信号に対して所定のフィルタリング処理を行う第 2 のフィルタと、上記第 3 の検波器の出力信号に対して所定のフィルタリング処理を行う第 3 のフィルタとをさらに有する。

【 0 0 1 4 】

また、上記変調器は直交変調器を有する。

【 0 0 1 5 】

好適には、上記リファレンスローカル信号に含まれる拡散コードは、受信信号の拡散コードに同期している。

【 0 0 1 6 】

また、上記受信信号のキャリア周波数は、上記リファレンスローカル信号のキャリア周波数に略等しい。

【 0 0 1 7 】

また、本発明では、少なくとも第 1 、第 2 、および第 3 の検波器の一つは、二乗検波器を有する。

【 0 0 1 8 】

本発明によれば、所定の拡散コードによりある帯域に拡散されたスペクトル拡散信号を受信し、逆拡散処理をアナログ形態で行うスペクトル拡散受信機であって、

所定周波数のアナログ形式の A C ローカル発振信号を出力するローカル発振器と、

A C 受信信号および上記ローカル発振器による上記 A C ローカル発振信号に基づいて同期および同期保持処理を介してローカル拡散コードを生成するローカル拡散コード同期保持手段と、

上記ローカル発振器による上記 A C ローカル発振信号および上記ローカル拡散コード同期保持手段による上記ローカル拡散コードに基づいて A C リファレンスローカル信号をアナログ値で生成し、上記 A C 受信信号および上記 A C リファレンスローカル信号とをアナログ値のままで線形合成し、その線形合成され A C 成分を含むアナログ値を二乗してアナログ電力値を生成し、当該アナログ電力値から D C 成分を取り除くことにより、位相差を有する 2 つのアナログ値の信号を生成し、上記位相差を持つ 2 つのアナログ値の信号に基づいて逆拡散を行うダイレクトコンバージョン回路と

を具備する、スペクトル拡散受信機が提供される。

【 0 0 1 9 】

好適には、上記ローカル拡散コード同期保持回路は、制御信号の値に基づいて上記ローカル拡散コードを生成するローカル拡散コード生成器と、所定の時間だけ上記生成されたローカル拡散コードを遅延させる第 1 の位相調整手段と、所定の時間だけ上記生成されたローカル拡散コードを進行させる第 2 の位相調整手段と、上記ローカル信号と上記第 1 の位相調整手段の出力信号を乗算する第 1 の乗算器と、上記ローカル信号と上記第 2 の位相調 40 50

整手段の出力信号を乗算する第2の乗算器と、上記受信信号と上記第1の乗算器の出力信号とを加算する第1の加算器と、上記第1の加算器の出力信号の振幅成分を検波する第1の検波器と、上記第1の検波器の出力信号の第1のエンベロープを検波する第1のエンベロープ検波手段と、上記受信信号と上記第2の乗算器の出力信号とを加算する第2の加算器と、上記第2の加算器の出力信号の振幅成分を検波する第1の検波器と、上記第2の検波器の出力信号の第2のエンベロープを検波する第2のエンベロープ検波手段と、上記第1のエンベロープと第2のエンベロープ間の差がゼロに近づいて減少するように上記制御信号を生成する制御信号生成手段とを有する。

【0020】

また、上記ローカル拡散コード同期保持回路は、制御信号の値に基づいて上記ローカル拡散コードを生成するローカル拡散コード生成器と、所定の時間だけ上記生成されたローカル拡散コードを遅延させる第1の位相調整手段と、所定の時間だけ上記生成されたローカル拡散コードを進行させる第2の位相調整手段と、上記ローカル信号と上記第1の位相調整手段の出力信号を乗算する第1の乗算器と、上記ローカル信号と上記第2の位相調整手段の出力信号を乗算する第2の乗算器と上記受信信号の位相をシフトする第1の位相シフタと、上記第1の乗算器の出力信号の位相をシフトする第2の位相シフタと、上記第2の乗算器の出力信号の位相をシフトする第3の位相シフタと、上記受信信号の位相をシフトする第4の位相シフタと、上記第1の位相シフタの出力信号と上記第1の乗算器の出力信号とを加算する第1の加算器と、上記受信信号と上記第2の位相シフタの出力信号とを加算する第2の加算器と、上記受信信号と上記第3の位相シフタの出力信号とを加算する第3の加算器と、上記第2の乗算器の出力信号と上記第4の位相シフタの出力信号とを加算する第4の加算器と、上記第1の加算器の出力信号の信号レベルを検波する第1の検波器と、上記第2の加算器の出力信号の信号レベルを検波する第2の検波器と、上記第3の加算器の出力信号の信号レベルを検波する第3の検波器と、上記第4の加算器の出力信号の信号レベルを検波する第4の検波器と、上記第1の検波器の出力に対して所定のフィルタリング処理を行う第1のフィルタと、上記第2の検波器の出力に対して所定のフィルタリング処理を行う第2のフィルタと、上記第3の検波器の出力に対して所定のフィルタリング処理を行う第3のフィルタと、上記第4の検波器の出力に対して所定のフィルタリング処理を行う第4のフィルタと、上記第1および第2のフィルタの出力に基づいて第1のノルムを計算する第1のノルム回路と、上記第3および第4のフィルタの出力に基づいて第2のノルムを計算する第2のノルム回路と、上記第1のノルムと第2のノルム間の差がゼロに近づいて減少するように上記制御信号を生成する制御信号生成手段とを有する。

【0021】

また、本発明では、少なくとも上記第1、第2、第3、および第4の検波器の一つは二乗検波器を有する。

【0022】

好適には、上記ローカル拡散コード同期保持回路は、上記第1、第2、第3、および第4のフィルタの出力からDCオフセットを除去する手段を有する。

【0023】

また、上記ローカル拡散コード同期保持回路は、制御信号の値に基づいて上記同相ローカル拡散コードを生成する第1のローカル拡散コード生成器と、制御信号の値に基づいて上記直交ローカル拡散コードを生成する第2のローカル拡散コード生成器と、所定の時間だけ上記生成された同相および直交ローカル拡散コードを遅延させる第1の位相調整手段と、所定の時間だけ上記生成された同相および直交ローカル拡散コードを進行させる第2の位相調整手段と、上記第1の位相調整手段の出力信号により上記ローカル信号を変調する第1の直交変調器と、上記第2の位相調整手段の出力信号により上記ローカル信号を変調する第2の直交変調器と、上記受信信号の位相をシフトする第1の位相シフタと、上記第1の直交変調器の出力信号の位相をシフトする第2の位相シフタと、上記第2の直交変調器の出力信号の位相をシフトする第3の位相シフタと、上記受信信号の位相をシフトする第4の位相シフタと、上記第1の位相シフタの出力信号と上記第1の直交変調器の出力信号

10

20

30

40

50

号とを加算する第1の加算器と、上記受信信号と上記第2の位相シフタの出力信号とを加算する第2の加算器と、上記受信信号と上記第3の位相シフタの出力信号とを加算する第3の加算器と、上記第2の直交変調器の出力信号と上記第4の位相シフタの出力信号とを加算する第4の加算器と、上記第1の加算器の出力信号の信号レベルを検波する第1の検波器と、上記第2の加算器の出力信号の信号レベルを検波する第2の検波器と、上記第3の加算器の出力信号の信号レベルを検波する第3の検波器と、上記第4の加算器の出力信号の信号レベルを検波する第4の検波器と、上記第1の検波器の出力に対して所定のフィルタリング処理を行う第1のフィルタと、上記第2の検波器の出力に対して所定のフィルタリング処理を行う第2のフィルタと、上記第3の検波器の出力に対して所定のフィルタリング処理を行う第3のフィルタと、上記第4の検波器の出力に対して所定のフィルタリング処理を行う第4のフィルタと、上記第1および第2のフィルタの出力に基づいて第1のノルムを計算する第1のノルム回路と、上記第3および第4のフィルタの出力に基づいて第2のノルムを計算する第2のノルム回路と、上記第1のノルムと第2のノルム間の差がゼロに近づいて減少するように上記制御信号を生成する制御信号生成手段とを有する。

#### 【0024】

また、上記ローカル拡散コード同期保持回路は、制御信号の値に基づいて上記同相ローカル拡散コードを生成する第1のローカル拡散コード生成器と、制御信号の値に基づいて上記直交ローカル拡散コードを生成する第2のローカル拡散コード生成器と、所定の時間だけ上記生成された同相ローカル拡散コードを遅延させる第1の位相調整手段と、所定の時間だけ上記生成された直交ローカル拡散コードを遅延させる第2の位相調整手段と、所定の時間だけ上記生成された同相ローカル拡散コードを進行させる第3の位相調整手段と、所定の時間だけ上記生成された直交ローカル拡散コードを進行させる第4の位相調整手段と、上記ローカル信号と上記第1の位相調整手段の出力信号を乗算する第1の乗算器と、上記ローカル信号と上記第2の位相調整手段の出力信号を乗算する第2の乗算器と、上記ローカル信号と上記第3の位相調整手段の出力信号を乗算する第3の乗算器と、上記ローカル信号と上記第4の位相調整手段の出力信号を乗算する第4の乗算器と、上記受信信号と上記第1の乗算器の出力信号とを加算する第1の加算器と、上記受信信号と上記第2の乗算器の出力信号とを加算する第2の加算器と、上記受信信号と上記第3の乗算器の出力信号とを加算する第3の加算器と、上記受信信号と上記第4の乗算器の出力信号とを加算する第4の加算器と、上記第1の加算器の出力信号の信号レベルを検波する第1の検波器と、上記第2の加算器の出力信号の信号レベルを検波する第2の検波器と、上記第3の加算器の出力信号の信号レベルを検波する第3の検波器と、上記第4の加算器の出力信号の信号レベルを検波する第4の検波器と、上記第1の検波器の出力に対して所定のフィルタリング処理を行う第1のフィルタと、上記第2の検波器の出力に対して所定のフィルタリング処理を行う第2のフィルタと、上記第3の検波器の出力に対して所定のフィルタリング処理を行う第3のフィルタと、上記第4の検波器の出力に対して所定のフィルタリング処理を行う第4のフィルタと、上記第1および第2のフィルタの出力に基づいて第1のノルムを計算する第1のノルム回路と、上記第3および第4のフィルタの出力に基づいて第2のノルムを計算する第2のノルム回路と、上記第1のノルムと第2のノルム間の差がゼロに近づいて減少するように上記制御信号を生成する制御信号生成手段とを有する。

#### 【0027】

本発明によれば、所定の拡散コードによりある帯域に拡散されたスペクトル拡散信号を受信し、逆拡散処理をアナログ形態で行うソフトウェア無線用スペクトル拡散受信機であつて、

所定周波数のアナログ形式のA Cローカル発振信号を出力するローカル発振器と、

A C受信信号および上記ローカル発振器による上記A Cローカル発振信号に基づいて同期および同期保持処理を介してローカル拡散コードを生成するローカル拡散コード同期保持手段と、

上記ローカル発振器による上記A Cローカル発振信号および上記ローカル拡散コード同期保持手段による上記ローカル拡散コードに基づいてA Cリファレンスローカル信号をア

10

20

30

40

50

ナログ値で生成し、上記 A C 受信信号および上記 A C リファレンスローカル信号とをアナログ値のままで線形合成し、その線形合成され A C 成分を含むアナログ値を二乗してアナログ電力値を生成し、当該アナログ電力値から D C 成分を取り除くことにより、位相差を有する 2 つのアナログ値の信号を生成し、上記位相差を持つ 2 つのアナログ値の信号に基づいて逆拡散を行うダイレクトコンバージョン回路と

を具備する、スペクトル拡散受信機が提供される。

【 0 0 2 8 】

好適には、上記ローカル拡散コード同期保持回路は、制御信号の値に基づいて上記同相ローカル拡散コードを生成する第 1 のローカル拡散コード生成器と、制御信号の値に基づいて上記直交ローカル拡散コードを生成する第 2 のローカル拡散コード生成器と、所定の時間だけ上記生成された同相および直交ローカル拡散コードを遅延させる第 1 の位相調整手段と、所定の時間だけ上記生成された同相および直交ローカル拡散コードを進行させる第 2 の位相調整手段と、上記第 1 の位相調整手段の出力信号により上記ローカル信号を変調する第 1 の直交変調器と、上記第 2 の位相調整手段の出力信号により上記ローカル信号を変調する第 2 の直交変調器と、上記受信信号の位相をシフトする第 1 の位相シフタと、上記第 1 の直交変調器の出力信号の位相をシフトする第 2 の位相シフタと、上記第 2 の直交変調器の出力信号の位相をシフトする第 3 の位相シフタと、上記受信信号の位相をシフトする第 4 の位相シフタと、上記第 1 の位相シフタの出力信号と上記第 1 の直交変調器の出力信号とを加算する第 1 の加算器と、上記受信信号と上記第 2 の位相シフタの出力信号とを加算する第 2 の加算器と、上記受信信号と上記第 3 の位相シフタの出力信号とを加算する第 3 の加算器と、上記第 2 の直交変調器の出力信号と上記第 4 の位相シフタの出力信号とを加算する第 4 の加算器と、上記第 1 の加算器の出力信号の信号レベルを検波する第 1 の検波器と、上記第 2 の加算器の出力信号の信号レベルを検波する第 2 の検波器と、上記第 3 の加算器の出力信号の信号レベルを検波する第 3 の検波器と、上記第 4 の加算器の出力信号の信号レベルを検波する第 4 の検波器と、上記第 1 の検波器の出力に対して所定のフィルタリング処理を行う第 1 のフィルタと、上記第 2 の検波器の出力に対して所定のフィルタリング処理を行う第 2 のフィルタと、上記第 3 の検波器の出力に対して所定のフィルタリング処理を行う第 3 のフィルタと、上記第 4 の検波器の出力に対して所定のフィルタリング処理を行う第 4 のフィルタと、上記第 1 および第 2 のフィルタの出力アナログ信号をデジタル信号に変換する第 1 のアナログ - デジタル (A / D) 変換手段と、上記第 3 および第 4 のフィルタの出力アナログ信号をデジタル信号に変換する第 2 の A / D 変換手段と、上記第 1 の A / D 変換手段と第 2 の A / D 変換手段の出力間の差がゼロに近づいて減少するように上記制御信号を生成するデジタル処理手段とを有する。

【 0 0 2 9 】

本発明によれば、n ポートダイレクト回路コンバータにおいては、公称 45 度に等しいだけ位相がシフトされ、検波機は理想的には二乗関数である。入力の一つは逆拡散 (復調) すべき受信信号である。他の入力は、直接拡散スペクトル拡散信号である。リファレンス信号は、受信信号の P N コードに同期している P N (拡散) コードを有する。受信信号のキャリア周波数は、ローカルリファレンス信号のキャリア周波数に同期する必要がない、リファレンス信号のキャリア周波数と略等しい。正確なキャリアおよび位相同期は、デジタル領域で行われる。

【 0 0 3 0 】

受信信号と位相が だけシフトされたリファレンスローカル信号の和は、電力検波器に入力される。リファレンスローカル信号と位相が だけシフトされた受信信号は、第 2 の電力検波器に入力される。第 3 の出力は受信信号の電力を生み出す。

【 0 0 3 1 】

また、本発明によれば、P N コード同期保持回路は、トラッキングループのためのエラー信号が二乗検波器の出力から決定されるダイレクトコンバージョン概念に基づく近ゼロ (near-zero) I F ダウンコンバータを伴うアーリー (early) ・ レイト (late) 構造を利用する。

10

20

30

40

50

## 【0032】

また、複素拡散を用いるスペクトル拡散信号用のダイレクトコンバージョン受信機においては、QPSK変調ブロックが、複素拡散器を構成する。受信信号は複素拡散を伴う信号である。

## 【0033】

また、たとえば、ソフトウェア無線におけるソフトウェアモジュールを利用したダイレクトコンバージョンを伴うスペクトル拡散のための同期保持回路が一般化される。ソフトウェアモジュールは、初期の荒い（粗）同期、あるいはPNコード同期捕捉が、トラッキンググループのためのロック範囲内に引き込む値の領域を通すVCOの周波数を進める処理を通して、実行するようにプログラムされる。ソフトウェアモジュールは、またエラー信号の生成を含むトラッキンググループ用、およびこの信号のフィルタリング用アルゴリズムを含む。

10

## 【0034】

## 【発明の実施の形態】

以下、ソフトウェア無線（SDR）用直接拡散スペクトル拡散受信機の最善の形態を、図面に関連付けて詳細に説明する。

## 【0035】

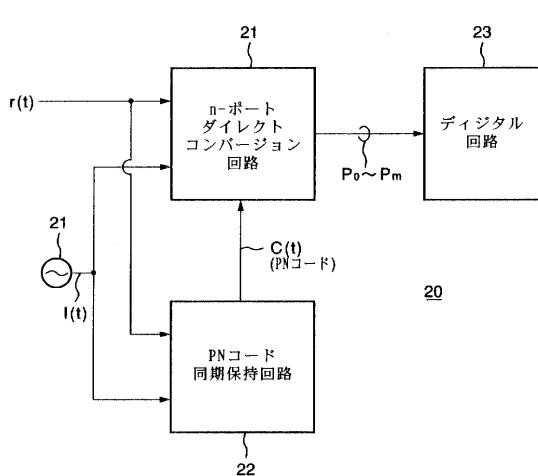

図2は、本発明に係るスペクトル拡散受信機の第1の実施形態を示すブロック図である。

## 【0036】

スペクトル拡散受信機20は、図2に示すように、n（nは3またはそれ以上の整数、本実施形態では、たとえばn=5または4）ポートダイレクトコンバージョン回路21、PNコード同期保持回路22、デジタル回路23、およびローカル発振器24を有している。

20

## 【0037】

nポートダイレクトコンバージョン回路21は、2つの信号、すなわち送信側でPNコードc(t)が乗算された受信信号r(t)と、ローカル発振器24によるローカル信号1(t)にPNコード同期保持回路22によるローカルPNコード（±1値）を乗算することにより生成されたローカル信号1(t)とを線形合成で合成し、一つの信号あるいは2つあるいはそれ以上の信号を出力する。出力信号のアナログ電力値は、たとえばFET二乗検波器により検波される。

30

## 【0038】

PNコード同期回路22は、送信側からの受信信号r(t)およびローカル発振器24によるローカル信号1(t)に基づく同期（捕捉）および同期保持処理を通してローカルPNコードを生成する。

## 【0039】

デジタル回路23は、nポートダイレクトコンバージョン回路21の出力信号を、図示しないA/Dコンバータを介して受信信号あるいはローカル信号に含まれる1または複数の信号成分に変換する。

## 【0040】

次に、nポートダイレクトコンバージョン回路21およびPNコード同期保持回路22の具体的な構成および基本的な機能について順を追って説明する。

40

## 【0041】

まず、nポートダイレクトコンバージョン回路21の具体的な構成について説明する。

## 【0042】

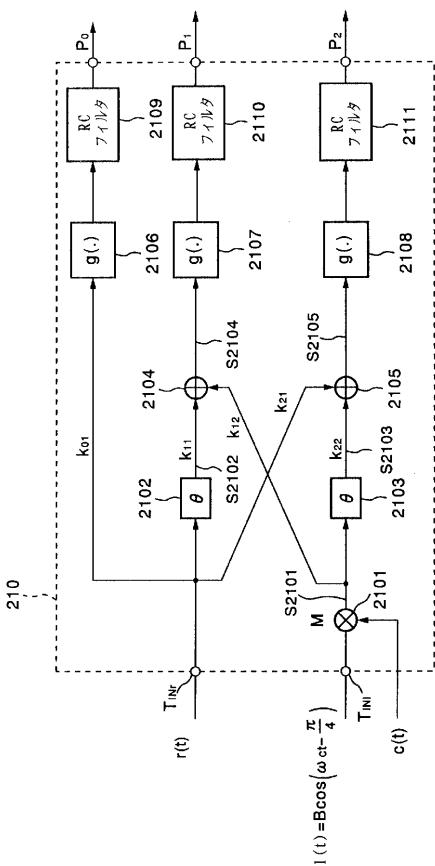

図3は、本発明に係る5（n=5）ポートダイレクトコンバージョン回路の構成例を示す図である。

## 【0043】

5ポートダイレクトコンバージョン回路210は、図3に示すように、乗算器2101、位相シフタ2102, 2103、加算器2104, 2105、検波器2106, 2107, 2108、およびRCフィルタ2109, 2110, 2111を有している。

50

## 【0044】

ここで、5ポートは、受信信号用入力端子  $T_{IN_r}$  、ローカル信号用入力端子  $T_{IN_l}$  、RCフィルタ2109の出力端子（ポート）、RCフィルタ2110の出力端子、およびRCフィルタ2111の出力端子により構成される。

## 【0045】

図3において、パラメータ  $\theta$  は、位相シフト（理論上は45°）を示している。実際に実現される5ポートデバイスは、2つの位相シフトが完全に整合する（釣り合う）ことを確実にしている。利得係数  $k_{ij}$  は回路構成要素パラメータによる。検波器2106～2108の関数  $g(\cdot)$  は、二乗関数におおよそあるいは理想的には等しい非線形関数であり、RCフィルタ2109～2111は、一次ローパスフィルタである。

10

## 【0046】

乗算器2101においては、ローカル信号1(t)が、PNコード同期保持回路22において同期および同期保持処理を通して得られたPNコード  $c(t)$  と掛け合わされ、リファレンスローカル信号  $S_{2101}$  が位相シフタ2103および加算器2104に出力される。ローカル信号  $1(t)$  が  $B_c \cos[\omega_c t - \theta/4]$  で与えられると、リファレンスローカル信号は、 $B_c(t) \cos[\omega_c t - \theta/4]$  で与えられる。

## 【0047】

位相シフタ2102においては、受信信号  $r(t)$  が（たとえば45°）だけ位相シフトされ、信号  $S_{2102}(r(t))$  が加算器2104に出力される。

20

## 【0048】

位相シフタ2103においては、リファレンスローカル  $S_{2102}$  がだけ位相シフトされ、信号  $S_{2103}$  が加算器2105に出力される。

## 【0049】

加算器2104においては、位相シフタ2102の出力信号  $S_{2104}$  とリファレンスローカル信号  $S_{2101}$  が加算され、信号  $S_{2104}$  が検波器2107に出力される。

## 【0050】

加算器2105においては、位相シフタ2103の出力信号  $S_{2103}$  と受信信号  $r(t)$  が加算され、信号  $S_{2105}$  が検波器2108に出力される。

## 【0051】

検波器2106においては、受信信号  $r(t)$  の振幅成分が検波され、検波された振幅成分がRCフィルタ2109に供給される。

30

## 【0052】

検波器2107においては、加算器2104の出力信号  $S_{2104}$  の振幅成分が検波され、検波された振幅成分がRCフィルタ2110に供給される。

## 【0053】

検波器2108においては、加算器2105の出力信号  $S_{2105}$  の振幅成分が検波され、検波された振幅成分がRCフィルタ2111に供給される。

## 【0054】

RCフィルタ2109は、たとえばローパスフィルタ（LPF）により構成され、検波器2106による振幅成分に対するフィルタリング処理を行い、パワー信号  $P_0$  をデジタル回路23に出力する。

40

## 【0055】

RCフィルタ2110は、たとえばLPFにより構成され、検波器2107による振幅成分に対するフィルタリング処理を行い、パワー信号  $P_1$  をデジタル回路23に出力する。

## 【0056】

RCフィルタ2111は、たとえばLPFにより構成され、検波器2108による振幅成分に対するフィルタリング処理を行い、パワー信号  $P_2$  をデジタル回路23に出力する。

## 【0057】

ここで、受信信号  $r(t)$  が、次のような両側波帯信号である場合を考察する。

## 【0058】

50

【数1】

$$r(t) = A m(t) \cos(\omega_0 t + \phi) \quad (1)$$

【0059】

ここで、 $r(t)$ はゆっくりと時間変動すると仮定した場合の位相であり、 $m(t)$ は変調信号である。上述したように、ローカル信号 $l(t) = B \cos(\omega_0 t - \pi/4)$ とする。

【0060】

もし、ローカル信号 $l(t)$ が完全に受信信号 $r(t)$ を同期保持すると、 $\phi = -\pi/4$ となる。

【0061】

今、 $g(\cdot)$ を二乗関数と仮定する。信号 $P_0$ はおおよそ $\omega_0^2 A^2 / 2 \cdot m^2(t)$ と等しい。信号 $P_1$ は次のように与えられる。

【0062】

【数2】

$$\begin{aligned} & (\kappa_{11}r_e(t) + \kappa_{12}c(t)l(t))^2 \\ &= L_p \left\{ \kappa_{11}^2 r_e^2(t) + 2\kappa_{11}\kappa_{12}Br_e(t)c(t)\cos\left(\omega_0 t - \frac{\pi}{4}\right) + \kappa_{12}^2 c^2(t)l^2(t) \right\} \quad (2) \\ &= \frac{\kappa_{11}^2 A^2}{2} m^2(t) + \frac{\kappa_{12}^2 B^2}{2} + \kappa_{11}\kappa_{12}ABm(t)c(t)\cos\left(\phi + \frac{\pi}{4} - \theta\right) \end{aligned}$$

【0063】

ここで、 $L_p$ はローパス成分を示し、 $r(t)$ は位相を $\phi$ だけシフトした $r(t)$ と等しい。

【0064】

今、上記において、第1項は出力 $P_0$ ( $\kappa_{11} = \omega_0$ ならば同等)、第2項は、DC(直流)成分、第3項は所望の信号である。したがって、 $P_1$ および $P_0$ を処理して、次を得ることができる。(当該式で、+を、-と読み替える)

【0065】

【数3】

$$Y_1 = \kappa_{22}\kappa_{21}ABm(t)c(t)\cos\left(\phi + \frac{\pi}{4} + \theta\right) \quad (3)$$

【0066】

同様にして、 $P_2$ での出力は、次のように得られるように処理可能に示すことが可能である。

【0067】

【数4】

$$Y_0 = \kappa_{22}\kappa_{21}ABm(t)c(t)\cos\left(\phi + \frac{\pi}{4} + \theta\right) \quad (4)$$

【0068】

パラメータ $\phi = -\pi/4$ と設定すると、次を得ることができる。

【0069】

【数5】

$$Y_1 = k m(t) c(t) \cos(\phi) \quad (5)$$

【0070】

【数6】

10

20

30

40

50

$$Y_Q = -k m(t) c(t) \sin \quad (6)$$

【0071】

ここで、 $k$  は比例定数である。5 ポートダイレクトコンバージョン回路 210 の出力  $P_1$  および  $P_2$  は、 $P_0$  の多重を減算し、DC 成分の除去する処理が行われ、これにより上記 I - Q 信号が得られる。したがって、5 ポートダイレクトコンバージョン回路 210 は、I - Q ダイレクトコンバータとして使用することが可能である。

【0072】

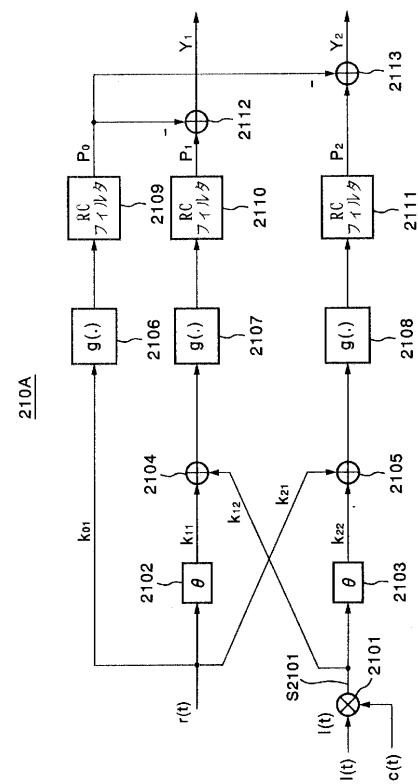

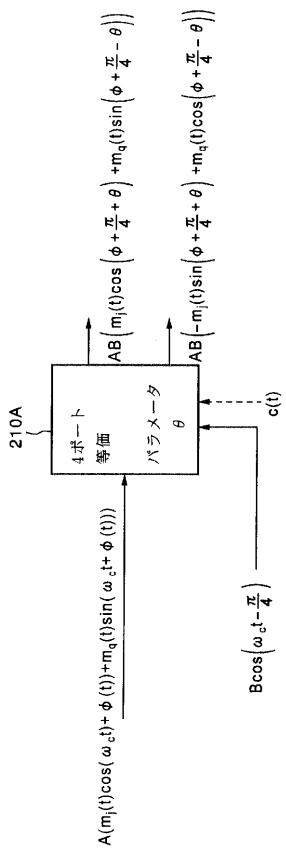

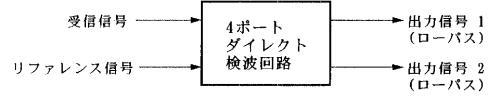

なお、回路成分が、 $m_1 = m_0$  と仮定できるように、都合よく整合されれば、5 ポートダイレクトコンバージョン回路は、図 4 に示すように、4 ポートダイレクトコンバージョン回路に適応させることができる。ここで、I - Q 成分は、 $Y_1$  および  $Y_Q$  から DC オフセットを除去することにより得ることができる。 10

【0073】

今、受信信号  $r(t)$  を次のように書くことができる直交変調信号のより一般的なケースについて考察する。

【0074】

【数 7】

$$r(t) = A(m_i(t) \cos(\omega_c t + \phi) + m_q(t) \sin(\omega_c t + \phi)) \quad (7)$$

【0075】

20

多重  $P_0$  を減算し、DC オフセットを除去する 5 ポートデバイスの出力処理の後、次の I - Q 信号を得ることができる。

【0076】

【数 8】

$$Y_I = \kappa \left( m_i(t) \cos\left(\phi + \frac{\pi}{4} - \theta\right) + m_q(t) \sin\left(\phi + \frac{\pi}{4} - \theta\right) \right) \quad (8)$$

【0077】

【数 9】

30

$$Y_Q = \kappa \left( m_i(t) \cos\left(\phi + \frac{\pi}{4} + \theta\right) + m_q(t) \sin\left(\phi + \frac{\pi}{4} + \theta\right) \right) \quad (9)$$

【0078】

転送された（あるいは情報）I - Q 信号は次のように計算することができる。

【0079】

【数 10】

$$\begin{bmatrix} m_i(t) \\ m_q(t) \end{bmatrix}$$

$$= \frac{1}{\kappa \sin(2\theta)} \begin{bmatrix} \sin\left(\phi + \frac{\pi}{4} + \theta\right) - \sin\left(\phi + \frac{\pi}{4} - \theta\right) \\ -\cos\left(\phi + \frac{\pi}{4} + \theta\right) \cos\left(\phi + \frac{\pi}{4} - \theta\right) \end{bmatrix} \begin{bmatrix} Y_I \\ Y_Q \end{bmatrix} \quad (10)$$

【0080】

50

なお、上記は、 $\phi = \pi/4$  を除く任意の位相角 $\phi$ について解くことができる。しかしながら、 $\phi = \pi/4$  の値は、荒い（骨の折れる）計算に関しては最適である。 $\phi = \pi/4$  を選択するならば、上記した式は、次のようになる。

【0081】

【数11】

$$\begin{bmatrix} m_r(t) \\ m_q(t) \end{bmatrix} = \frac{1}{\kappa} \begin{bmatrix} \cos \phi - \sin \phi \\ \cos \phi \cos \phi \end{bmatrix} \begin{bmatrix} Y_r \\ Y_q \end{bmatrix}$$

(11)

10

【0082】

オリジナル（変調）I - Q 信号は、式(11)のように、ディローーションマトリクスにより上記（検波された）I - Q 信号を処理することにより回復される。この動作を行うため、受信信号のキャリア位相 $\phi$ の情報が要求される。

【0083】

上記展開の後、5ポートデバイスを、図5に示すように、効果的に4ポートデバイスに設計することができる。

【0084】

もしも、前述の展開におけるローカル発振器24のローカル信号 $l(t)$ が、受信信号のキャリアに位相ロックしていないならば、上記位相エラー $\phi$ は、時間変動し、実際、として示す周波数オフセットに寄与する。 $\phi = 0$ を達成し、位相 $\phi$ を追跡するための2つの主なアプローチがある。一つのアプローチは位相ロックループを用いることである。エラー信号は、受信信号の位相を追跡するためにVCOを駆動するような方法で、回転されたI - Q 出力から生成される。

【0085】

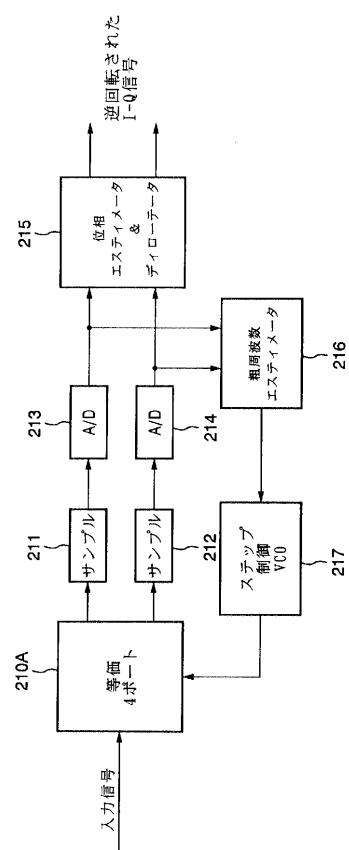

もう一つは、位相を正確に追跡する代わりに、4ポートデバイス出力の粗周波数推定を行い、図6に示すように、それをステップ入力制御を持つ発振器の周波数制御に使うことである。

【0086】

図6において、210Aは4ポートダイレクトコンバージョン回路を示し、211および212はサンプラーを示し、213および214はA/Dコンバータを示し、215は位相推定器（エスティメータ）・ディローーターを示し、216は粗周波数推定器（エスティメータ）を示し、217は電圧制御発振器（VCO）を示している。

【0087】

粗周波数推定アルゴリズムは、受信信号 $r(t)$ のキャリアに対するローカル発振器の周波数ドリフトの度合いによって決定される周期により周期的に行われる。デジタル位相推定器（エスティメータ）215の実現は、変調機構の特性による。QAM変調については、位相推定器は、デジタルトラッキングループとして実現可能である。2つの主なアプローチは、Nのべき乗法および決定有向法（decision direct method）である（文献[3]参照：H.Meyr, M.Moeneclaey, and S.Fechtel, Digital Communication Receivers: Synchronization, Channel Estimation, and Signal Processing）。

【0088】

ダウンコンバージョンのシングルステージを用いると、図1におけるスペクトル拡散（SS）受信機は、図6のダイレクトコンバータ受信機のハードウェアリファレンスモデルに適合する。PNコードチップ検出のためにダイレクトコンバージョン回路を使用することができ従来のデジタル相關技術を用いた逆拡散を行うことができる。しかしながら、他に採りうる道は、ダイレクト検波処理を用いるアナログ相關を実現することである。

【0089】

そのようなダイレクトコンバージョン回路は図3に示されている。上述したように、図3

20

30

40

50

において、 $c(t)$  は P N コード ( $\pm 1$  値) のローカルレプリカを示している。このローカル P N コードは、P N コード同期保持回路 2 2 において同期および同期保持処理を通して得られる必要がある。

【 0 0 9 0 】

スペクトル拡散受信機の設計における要点は、P N コード  $c(t)$  の同期である。拡散コードがデータにより変調されている場合、この同期を、達成するのは困難である。

【 0 0 9 1 】

実際のシステムにおいては、典型的には、無変調拡散コードが同期信号として送信される。この信号は、データフレームの始め、すなわちシンクあるいはパイロットバースト、あるいはパイロット信号として連続する場所に現出できる。

10

【 0 0 9 2 】

大きな処理利得および高 S N R の場合、データシンボルの転送内に符号同期捕捉が発生する P N コードにおけるデータ変調と仮定することができる。ここでの目的として、データ変調を伴わない拡散コードの転送と仮定することができる。最良な例は、I S - 9 5 あるいはW C D M A システムにおけるパイロット信号である。

【 0 0 9 3 】

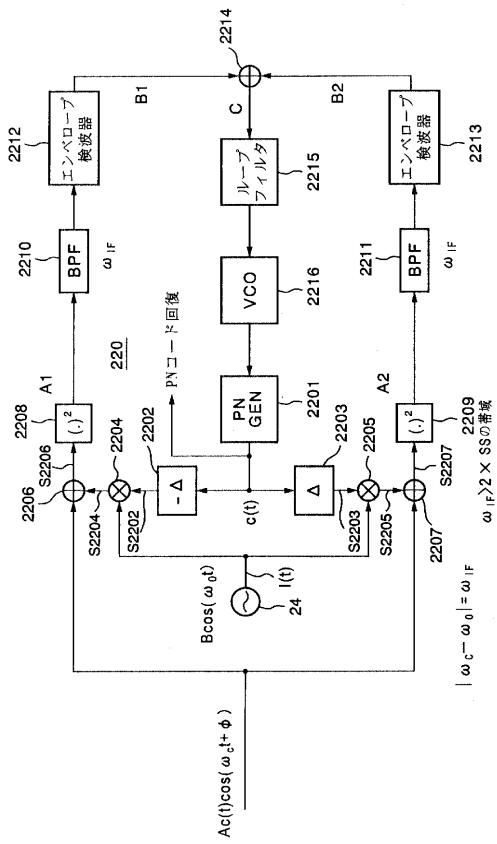

図 7 は、図 2 の P N コード同期保持回路の構成例を示す図である。

P N コード同期保持回路 2 2 0 は、図 7 に示すように、P N コード生成器 2 2 0 1 、位相調整回路 2 2 0 2 , 2 2 0 3 、乗算器 2 2 0 4 , 2 2 0 5 、加算器 2 2 0 6 , 2 2 0 7 、二乗検波器 2 1 0 8 , 2 2 0 9 、バンドパスフィルタ (B P F) 2 2 1 0 , 2 2 1 1 、エンベロープ検波器 2 2 1 2 , 2 2 1 3 、減算器 2 2 1 4 、ループフィルタ 2 2 1 5 、および V C O 2 2 1 6 を有している。

20

【 0 0 9 4 】

短から中の長さの P N コードのシステム (たとえば、I S - 9 5 、あるいはW C D M A におけるパイロット信号) では、この回路は、P N コード同期捕捉 (acquisition) および同期保持 (tracking) の 2 つの機能を実行できる。

【 0 0 9 5 】

初期 P N コードクロック周波数オフセットがさほど大きくなれば、ローカル P N コード同期捕捉処理において P N コードを引き入れることによりスライドする。このスライド処理は、結局 2 つの符号をアライメントする (時間的に同期化させる)。そのような時に、同期保持回路は、2 つの符号の同期を維持する。

30

【 0 0 9 6 】

同期保持ループの V C O の周波数のステップ制御は、P N コード長およびフィルタの帯域 (あるいは積分時間に等価) による期間内に現出する同期のための実行可能な値にスライドレートが伴うように設計可能である。

【 0 0 9 7 】

具体的には、P N コード生成器 2 2 0 1 において、P N コード  $c(t)$  は V C O 2 2 1 6 による制御信号 S 2 2 1 6 に基づいて生成され、生成された P N コード  $c(t)$  は、位相調整回路 2 2 0 2 , 2 2 0 3 、および図 3 の 5 ポートダイレクトコンバージョン回路 2 1 0 の乗算器 2 1 0 1 (あるいは図 4 の 4 ポートダイレクトコンバージョン回路 2 1 0 A の乗算器 2 1 0 1 ) に出力される。

40

【 0 0 9 8 】

位相調整回路 2 2 0 2 においては、P N コード生成器 2 2 0 1 により生成された P N コード  $c(t)$  の位相が、- (公称、 $= 1 / 2$  チップ) だけ遅延され、信号 S 2 2 0 2 ( $c(t -)$ ) が乗算器 2 2 0 4 に出力される。

【 0 0 9 9 】

位相調整回路 2 2 0 3 においては、P N コード生成器 2 2 0 1 により生成された P N コード  $c(t)$  の位相が、+ (上述したように、公称、 $= 1 / 2$  チップ) だけ遅延され、信号 S 2 2 0 3 ( $c(t +)$ ) が乗算器 2 2 0 5 に出力される。

【 0 1 0 0 】

50

乗算器 2204においては、ローカル信号  $l(t) [= B \cos(\omega_0 t)]$  が位相調整回路 2202 による出力信号 S2202 と掛け合わされ(乗算され)、信号 S2204 ( $B_c(t - \Delta) \cos(\omega_0 t)$ ) が加算器 2206 に出力される。

【0101】

乗算器 2205においては、ローカル信号  $l(t) [= B_c \cos(\omega_0 t)]$  が位相調整回路 2203 による出力信号 S2203 と掛け合わされ(乗算され)、信号 ( $B_c(t + \Delta) \cos(\omega_0 t)$ ) が加算器 2207 に出力される。

【0102】

加算器 2206においては、受信信号  $r(t) [= A_c(t) \cos(\omega_0 t + \Delta)]$  と乗算器 2204 の出力信号 S2204 を加算し、信号 S2206 ( $r(t) + B_c(t - \Delta) \cos(\omega_0 t)$ ) が二乗検波器 2208 に出力される。

10

【0103】

加算器 2207においては、受信信号  $r(t)$  と乗算器 2205 の出力信号 S2204 を加算し、信号 S2207 ( $r(t) + B_c(t + \Delta) \cos(\omega_0 t)$ ) が二乗検波器 2209 に出力される。

【0104】

二乗検波器 2208においては、信号 A1 が加算器 2207 の出力信号 S2207 に基づいて得られる。

【0105】

同様に、二乗検波器 2209においては、信号 A2 が加算器 2208 の出力信号 S2208 に基づいて得られる。

20

【0106】

ここで、信号 A1 は次により与えられる。

【0107】

【数12】

$$(r(t) + B_c(t - \Delta) \cos(\omega_0 t))^2 = \\ r^2(t) + 2Br(t)c(t-\Delta)\cos(\omega_0 t) + B^2c^2(t-\Delta)\cos^2(\omega_0 t) \quad (12)$$

30

【0108】

バンドパスフィルタ (BPF) 2210 の出力は、次の入力に対するバンドパスフィルタの応答として得られる。

【0109】

【数13】

$$ABc(t)c(t - \Delta) \cos(\omega_{IF}t + \phi) \quad (13)$$

【0110】

そして、次のように与えられる。

40

【0111】

【数14】

$$\overline{ABc(t)c(t - \Delta) \cos(\omega_{IF}t + \phi)} \quad (14)$$

【0112】

ここで、バーは図7のバンドパスフィルタの帯域の 1/2 に相当する帯域を有するローバスフィルタのフィルタリングを示している。

【0113】

B1におけるエンベロープ検波器 2212 の出力は、次のようになる。

50

【 0 1 1 4 】

【数 1 5 】

$$|ABc(t)c(t - \Delta)|$$

【 0 1 1 5 】

同様に、B 2 点における信号（エンベロープ検波器 2 2 1 3 の出力）は次のように与えられる。

【 0 1 1 6 】

【数 1 6 】

10

$$|ABc(t)c(t + \Delta)|$$

【 0 1 1 7 】

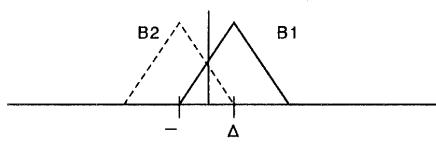

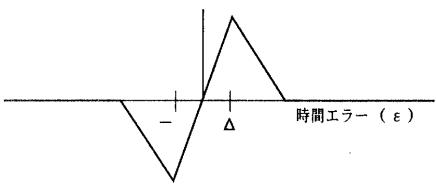

今、方形チップパルスとし、かつ P N コードの相関自己ノイズを無視すると、引き入れ P N コードとローカルに生成された P N コード間のタイミングエラーを対でプロットしたとき、B 1 および B 2 における信号は、図 8 に示すような値を持つ。

【 0 1 1 8 】

C 点における信号（減算器 2 2 1 4 の出力）は、タイミングエラーの関数として、図 9 に示すように、" S " カーブを追跡する。

20

【 0 1 1 9 】

図 7 の P N コード同期保持回路 2 2 0 は、I F 周波数  $f_{IF}$  で動作する。それ自体、より簡単なローパスフィルタの代わりに二乗検波器の出力において 2 つのバンドパスフィルタを必要とする。

【 0 1 2 0 】

ローカル発振器周波数が、受信信号  $r(t)$  のキャリア周波数と等しい適当な周波数に選択された同期保持回路のベースバンドバージョンを設計することが可能である。そのような同期保持回路を設計するため、二乗検波器 2 2 0 8 ( 2 2 0 9 ) の出力を、入力信号  $r(t)$  およびローカルリファレンス信号  $L_1(t)$  から考察する。

【 0 1 2 1 】

【数 1 7 】

30

$$r(t) = Ac(t) \cos(\omega_c t + \phi) \quad (15)$$

【 0 1 2 2 】

【数 1 8 】

$$L_1(t) = Bc(t - \tau) \cos(\omega_c t - \theta) \quad (16)$$

$$(r(t) + L_1(t))^2 =$$

40

$$r^2(t) + L_1^2(t) + ABc(t)c(t - \tau) \cos(\phi + \theta) + \text{double}$$

$$\text{frequency term} \quad (17)$$

【 0 1 2 3 】

今、この信号および可能ならば他の二乗検波器の出力から、図 9 のようなトラッキングカーブ（" S " カーブ）を生成する必要がある。受信信号とリファレンスローカル信号の周波数がロックしていない場合を考察する。この場合において、位相  $\phi$  は実際には時間変動であり、 $\phi(t) = \omega_c t$  と書くことができる。  $\theta$  は小さい周波数オフセットである。

【 0 1 2 4 】

50

” S ” カーブを生成するためには、” アーリー(early) ” リファレンス信号  $L_E(t) = B_c(t + \tau) \cos(\phi_c - \theta)$  との相関は必ずしも必要でないことは明らかである。簡単化のため、図 3 における電圧伝達係数  $k_{ij}$  は、1 (unity) に等しいもの仮定する。二乗検波器の一つの出力は次のようになる。

【0125】

【数19】

$$(r(t) + L_e(t))^2 =$$

$$r^2(t) + L_e^2(t) + ABc(t)c(t + \tau)\cos(\Phi + \theta) + \text{double}$$

10

frequency term (18)

【0126】

上記において、要求される成分は第 3 項である。しかしながら、この項は、発振し、小さい  $\tau$  はトラッキンググループに十分に長い時間にゼロになる。その結果、入力信号をだけシフトし、ローカルリファレンス  $\cos(\phi_c t)$  を用いることにより効果的に直交成分を生成する。ここで、 $\tau = \pi / 4$  は位相の公称値である。今、式(17)および(18)における信号は、積分時間の逆(inverse)に等しい帯域のローパスフィルタでフィルタリングされる。次の 4 つの信号が得られる。

【0127】

【数20】

$$\overline{r^2(t) + L_1^2(t) + ABc(t)c(t - \tau)\cos(\phi + \theta)} \quad (19)$$

$$\overline{r^2(t) + L_1^2(t) + ABc(t)c(t - \tau)\cos(\phi - \theta)} \quad (20)$$

$$\overline{r^2(t) + L_e^2(t) + ABc(t)c(t + \tau)\cos(\phi + \theta)} \quad (21)$$

$$\overline{r^2(t) + L_e^2(t) + ABc(t)c(t + \tau)\cos(\phi - \theta)} \quad (22)$$

30

【0128】

上記 4 つの信号の第 1 項は、SS チップ時間が積分時間、あるいはローパスフィルタ (LPF) 帯域の逆(inverse)より十分に小さいと仮定する定数によって近似できる。この定数は、DC オフセットとして扱うことができ、除去できる。 $\tau = \pi / 4$  を用いて、第 1 の 2 つの項は、アーリー相関のための値を得るために処理(二乗の和の平方根)が可能である。同様に、第 2 の 2 つの項は、遅延相関を得るために処理が可能である。しかしながら、より簡単なアプローチは、絶対値を使うこと、および 2 つの ” S ” カーブの和である ” S ” カーブを形成することである。ベクトルの成分としてこれら 2 つの項を考える、2 つのアプローチは、ベクトルの  $L_1$  および  $L_2$  ノルムを計算することに対応する。 $L_1$  ノルムを使用する場合では、引き込み信号のタイミングエラーを  $\tau$  と仮定すると、トラッキンググループの ” S ” カーブを次のように生成することができる。

【0129】

【数21】

10

20

30

40

$S(\varepsilon)$

$$= \left| ABc(t - \varepsilon) c(t - \tau) \cos(\phi + \theta) \right| - \left| ABc(t - \varepsilon) c(t + \tau) \cos(\phi + \theta) \right| \\ + \left| ABc(t - \varepsilon) c(t - \tau) \cos(\phi - \theta) \right| - \left| ABc(t - \varepsilon) c(t + \tau) \cos(\phi - \theta) \right|$$

(23)

【0130】

10

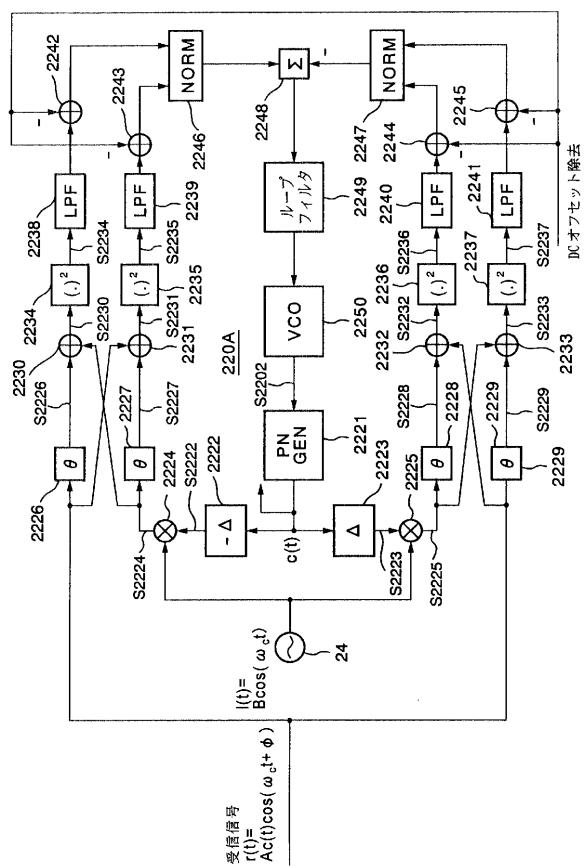

図10は、上記理論に基づいた図2のPNコード同期保持回路の他の構成例を示す図である。

【0131】

PNコード同期保持回路220Aは、図10に示すように、PNコード生成器2221、位相調整回路2222, 2223、乗算器2224, 2225、位相シフタ2226, 2227, 2228, 2229、加算器2230, 2231, 2232, 2233、二乗検波器2234, 2235、LPF2238, 2239, 2240, 2241、減算器2242, 2243, 2244, 2245、ノルム回路2246, 2247、総和回路2248、ループフィルタ2249、およびVCO2250を有している。

【0132】

20

PNコード生成器2231においては、PNコード $c(t)$ がVCOによる制御信号S2250に基づいて生成され、生成されたPNコード $c(t)$ は、位相調整回路2222, 2223、および図3の5ポートダイレクトコンバージョン回路210の乗算器2101（あるいは図4の4ポートダイレクトコンバージョン回路210Aの乗算器2101）に出力される。

【0133】

位相調整回路2222においては、PNコード生成器2221により生成されたPNコード $c(t)$ の位相が、-（公称、 $= 1/2$ チップ）だけ遅延され、信号S2222（ $c(t -)$ ）が乗算器2224に出力される。

【0134】

30

位相調整回路2223においては、PNコード生成器2221により生成されたPNコード $c(t)$ の位相が、+だけ遅延され、信号S2223（ $c(t +)$ ）が乗算器2225に出力される。

【0135】

乗算器2224においては、ローカル信号 $l(t)$  [ $= B \cos(\phi_0 t)$ ] が位相調整回路2222の出力信号S2222と掛け合わされ（乗算され）、信号S2224（ $B_c(t -) \cos(\phi_0 t)$ ）が位相シフタ2227および加算器2230に出力される。

【0136】

一方、乗算器2225においては、ローカル信号 $l(t)$ が位相調整回路2223による出力信号S2223と掛け合わされ（乗算され）、信号S2225（ $B_c(t +) \cos(\phi_0 t)$ ）が位相シフタ2228および加算器2233に出力される。

40

【0137】

位相シフタ2226においては、受信信号 $r(t)$ が（たとえば45°）だけ位相シフトされ、信号S2226が加算器2230に出力される。

【0138】

位相シフタ2227においては、乗算器2224の出力信号S2224がだけ位相シフトされ、信号S2227が加算器2231に出力される。

【0139】

加算器2230においては、位相シフタ2226の出力信号S2226と乗算器2224

50

の出力信号 S 2 2 2 4 とが加算され、信号 S 2 2 3 0 が二乗検波器 2 2 3 4 に出力される。

。

【 0 1 4 0 】

加算器 2 2 3 1 においては、受信信号  $r(t)$  と位相シフタ 2 2 2 7 の出力信号 S 2 2 2 7 とが加算され、信号 S 2 2 3 1 が二乗検波器 2 2 3 5 に出力される。

【 0 1 4 1 】

二乗検波器 2 2 3 4 においては、加算器 2 2 3 0 の出力信号 S 2 2 3 0 が二乗され、 L P F 2 2 3 8 に出力され、そして減算器 2 2 4 2 に入力される。

【 0 1 4 2 】

減算器 2 2 4 2 においては、 L P F 2 2 3 8 の出力から D C オフセット等が除去され、ノルム回路 2 2 4 6 に出力される。 10

【 0 1 4 3 】

同様に、二乗検波器 2 2 3 5 においては、加算器 2 2 3 1 の出力信号 S 2 2 3 1 が二乗され、 L P F 2 2 3 9 に出力され、そして減算器 2 2 4 3 に入力される。

【 0 1 4 4 】

減算器 2 2 4 3 においては、 L P F 2 2 3 9 の出力から D C オフセット等が除去され、ノルム回路 2 2 4 6 に出力される。

【 0 1 4 5 】

ノルム回路 2 2 4 6 においては、ベクトルのノルムが計算され、総和回路 2 2 4 8 に出力される。 20

【 0 1 4 6 】

位相シフタ 2 2 2 8 においては、乗算器 2 2 2 5 の出力信号 S 2 2 2 5 が だけ位相シフトされ、信号 S 2 2 2 8 が加算器 2 2 3 2 に出力される。

【 0 1 4 7 】

位相シフタ 2 2 2 9 においては、受信信号  $r(t)$  が (たとえば 45°) だけ位相シフトされ、信号 S 2 2 2 9 が加算器 2 2 3 3 に出力される。

【 0 1 4 8 】

加算器 2 2 3 2 においては、受信信号  $r(t)$  と位相シフタ 2 2 2 8 の出力信号 S 2 2 2 8 とが加算され、信号 S 2 2 3 2 が二乗検波器 2 2 3 6 に出力される。

【 0 1 4 9 】

加算器 2 2 3 3 においては、位相シフタ 2 2 2 9 の出力信号 S 2 2 2 9 と乗算器 2 2 2 5 の出力信号 S 2 2 2 5 とが加算され、信号 S 2 2 3 3 が二乗検波器 2 2 3 7 に出力される。

。

【 0 1 5 0 】

二乗検波器 2 2 3 6 においては、加算器 2 2 3 2 の出力信号 S 2 2 3 2 が二乗され、 L P F 2 2 4 0 に出力され、そして減算器 2 2 4 4 に入力される。

【 0 1 5 1 】

減算器 2 2 4 4 においては、 L P F 2 2 4 0 の出力から D C オフセット等が除去され、ノルム回路 2 2 4 7 に出力される。

【 0 1 5 2 】

同様に、二乗検波器 2 2 3 7 においては、加算器 2 2 3 3 の出力信号 S 2 2 3 3 が二乗され、 L P F 2 2 4 1 に出力され、そして減算器 2 2 4 5 に入力される。 40

【 0 1 5 3 】

減算器 2 2 4 5 においては、 L P F 2 2 4 1 の出力から D C オフセット等が除去され、ノルム回路 2 2 4 7 に出力される。

【 0 1 5 4 】

ノルム回路 2 2 4 7 においては、ベクトルのノルムが計算され、総和回路 2 2 4 8 に出力される。

【 0 1 5 5 】

総和回路 2 2 4 8 においては、ノルム回路 2 2 4 6 および 2 2 4 7 の出力の総和がとられ 50

、ループフィルタ2249を介してVCO2250に出力される。

【0156】

VCO2250においては、発振周波数がループフィルタ2249の出力により変化し、制御信号S2250の値が発振周波数の変化に応じて変化する。

【0157】

PNコード同期保持回路220Aにおいては、LPFの帯域はSNRによる。引き込み信号が無変調信号、たとえばIS-95あるいはWCDMAにおけるパイロット信号を有するとすると、帯域はPNコード相関のための積分時間の逆とほぼ等しい。この帯域は、SNRおよび誤ったロックの確率要求によって選択される。

【0158】

一方、引き込み信号がデータによって変調されると、LPFの帯域は、データレートより小さくすべきではない、すなわち(等価)積分時間がデータ期間以下であるべきである。

【0159】

図7および図10のIFおよびベースバンド同期保持回路に比較においては、ダイレクトコンバージョン受信器は、典型的には影像阻止フィルタ(image rejection filter)を必要としないことに留意すべきである。パワー検出回路において干渉の強さが制限されるので、RFフロントエンドフィルタは、なお望ましく、非線形領域でこれら回路を駆動できる。しかしながら、通過(pass-band)域から停止域(stop-band)のロールオフの点からみると、フィルタの設計はクリティカルではない。

10

20

【0160】

一方、IF基調の受信機を用いると、RFフロントエンドフィルタは、影像周波数の除去の機能を有する。狭帯域システムでは、影像周波数が除去されることとはクリティカルであり、フィルタの複雑さは、使用されるIF周波数による。小さいIF周波数はローカル発振器周波数と近く、フィルタ仕様(ロールオフ)はより厳格である。

【0161】

一方、スペクトル拡散信号を用いると、利得処理の結果、影像阻止能力を備えたRFフィルタを使用することは、本質ではない。影像周波数の信号は、干渉として働き、受信機の効果は、SNRで約3dBの損失となる。

【0162】

30

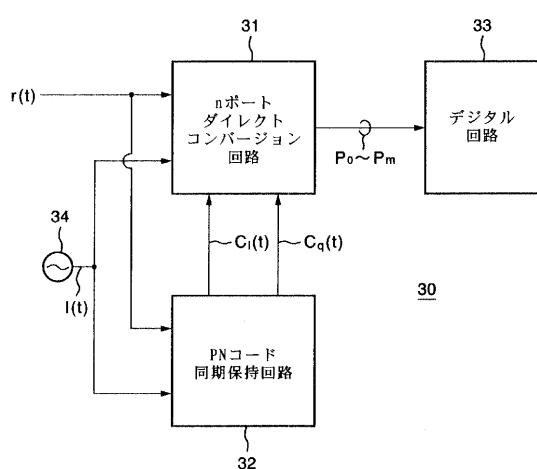

図11は、本発明に係るスペクトル拡散受信機の第2の実施形態を示すブロック図である。

【0163】

スペクトル拡散受信機30は、直交拡散および逆拡散処理に対応して構成されている。

【0164】

スペクトル拡散受信機30は、図11に示すように、n(nは3またはそれ以上の整数、本実施形態では、たとえばn=5または4)ポートダイレクトコンバージョン回路31、PNコード同期保持回路32、デジタル回路33、およびローカル発振器34を有している。

【0165】

40

nポートダイレクトコンバージョン回路31は、送信側でPNコードc(t)が乗算された受信信号r(t)と、PNコード同期保持回路32からのローカルPNコード(C<sub>i</sub>(t)とC<sub>q</sub>(t))を用いたローカル発振器24によるローカル信号l(t)を変調することにより生成されたリファレンスローカル信号l(t)c\*(t)(ここでc\*(t)は後述するように複素拡散コードである)とを線形合成で合成し、一つの信号あるいは2つあるいはそれ以上の信号を出力する。出力信号のアナログ電力値は、たとえばFET二乗検波器により検波される。

【0166】

PNコード同期回路32は、送信側からの受信信号r(t)およびローカル発振器34によるローカル信号l(t)に基づく同期(捕捉)および同期保持処理を通してローカルP

50

Nコード  $c_i(t)$  と  $c_q(t)$  を生成する。

【0167】

デジタル回路33は、図示しないA/Dコンバータを介したnポートダイレクトコンバージョン回路31の出力信号を、受信信号あるいはローカル信号に含まれる1または複数の信号成分に変換する。

【0168】

チップレベルでQPSK変調の幾つかのフォーマットを利用する3つの主なダイレクトコンバージョンスキームがある。ここでは、QPSK1、QPSK2、およびQPSK3が参照される。QPSK1においては、データシンボルを使用することにより正規のQPSK信号を形成し、2つ異なるPNコードを用いてデータシンボル（同相および直交キャリアにおける）の各々を拡散する。

【0169】

QPSK2においては、個々のデータシンボルを取り出すことができ、2つの異なるPNコードを用いてそれらを拡散することができる。一方の拡散信号は同キャリアで送信され、他方は直交キャリアで送信される。スペクトル拡散のこの形式は、IS-95のフォワードリンクにおいて用いられる。

【0170】

QPSK3は、典型的には複素拡散として言及され、3G CDMAシステムにおいて用いられる。

【0171】

まず、受信機において同期したローカルPNコードが存在すると仮定した信号のダイレクト検出のための5ポートデバイスの使用について考察し、PNコード同期のための回路について検討する。

【0172】

QPSK1の場合では、まず、同期したローカルPNコードおよびキャリア信号が存在する場合を考察する。この場合、受信信号は、実際上、同相および直交キャリア成分における2つの独自のSS信号から構成されることから、2つの5ポート回路を利用することができ、以上説明したように、BPSKの場合では、同相および直交信号を独立に復調できる。完全なキャリア同期が実現されれば、2つのブランチ（同相および直交）間は無干渉となる。

【0173】

次に、受信機において、同期したキャリアな無いが同期したPNコードがある場合を考察する。この場合、同相および直交データを復調するために2つの独立したタイプの回路を用いることができるが、2つのQPSKブランチにおける拡散コードの非ゼロ相互相關のために2つのブランチ間に干渉がある。この干渉の程度は、積分時間、フィルタの帯域、あるいは等価な処理利得により、3つのパラメータの大きい値により控えめに小さくすべきである。

【0174】

次に、nポートダイレクトコンバージョン回路31およびPNコード同期保持回路32の具体的な構成および基本的な機能について順を追って説明する。

【0175】

まず、nポートダイレクトコンバージョン回路31の具体的な構成について説明する。

【0176】

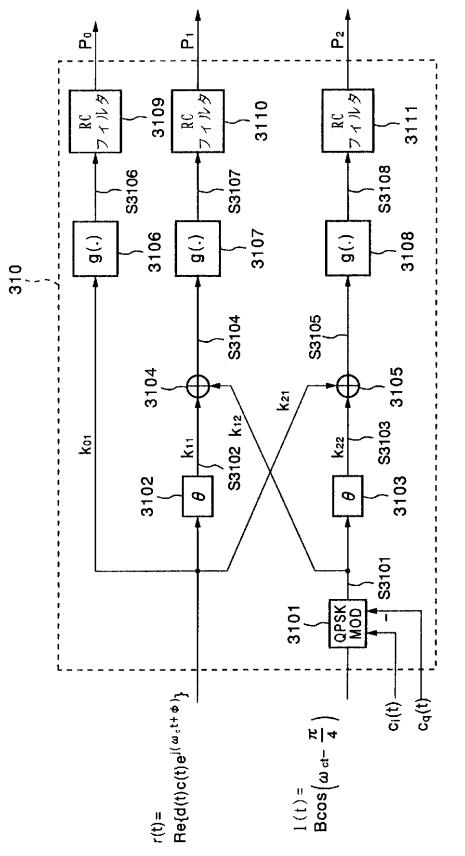

図12は、本発明に係る5(n=5)ポートダイレクトコンバージョン回路の構成例を示す図である。

【0177】

5ポートダイレクトコンバージョン回路310は、図12に示すように、QPSK変調器3101、位相シフタ3102, 3103、加算器3104, 3105、検波器3106, 3107, 3108、およびRCフィルタ3109, 3110, 3111を有している。

10

20

30

40

50

## 【0178】

ここで、5ポートは、受信信号用入力端子  $T_{INR}$  、ローカル信号用入力端子  $T_{NI}$  、RCフィルタ3109の出力端子(ポート)、RCフィルタ3110の出力端子、およびRCフィルタ3111の出力端子により構成される。

## 【0179】

QPSK変調器3101においては、受信信号  $r(t)$  が、PNコード同期保持回路22において同期および同期保持処理を通して得られたPNコード  $C_i(t)$  および  $C_q(t)$  を用いて変調され、リファレンスローカル信号S3101が位相シフタ3103および加算器3104に出力される。

## 【0180】

位相シフタ3102においては、受信信号  $r(t)$  が(たとえば  $45^\circ$ )だけ位相シフトされ、信号S3102が加算器3104に出力される。

## 【0181】

位相シフタ3103においては、リファレンスローカルS2102がだけ位相シフトされ、信号S3103が加算器3105に出力される。

## 【0182】

加算器3104においては、位相シフタ3102の出力信号S3102とリファレンスローカル信号S3101が加算され、信号S3104が検波器3107に出力される。

## 【0183】

加算器3105においては、位相シフタ3103の出力信号S3103と受信信号  $r(t)$  が加算され、信号S3105が検波器3108に出力される。

## 【0184】

検波器3106においては、受信信号  $r(t)$  の振幅成分が検波され、検波された振幅成分がRCフィルタ3109に供給される。

## 【0185】

検波器3107においては、加算器3104の出力信号S3104の振幅成分が検波され、検波された振幅成分がRCフィルタ3110に供給される。

## 【0186】

検波器3108においては、加算器3105の出力信号S3105の振幅成分が検波され、検波された振幅成分がRCフィルタ3111に供給される。

## 【0187】

RCフィルタ3109は、たとえばローパスフィルタ(LPF)により構成され、検波器3106による振幅成分に対するフィルタリング処理を行い、パワー信号  $P_0$  をデジタル回路33に出力する。

## 【0188】

RCフィルタ3110は、たとえばLPFにより構成され、検波器3107による振幅成分に対するフィルタリング処理を行い、パワー信号  $P_1$  をデジタル回路33に出力する。

## 【0189】

RCフィルタ3111は、たとえばLPFにより構成され、検波器3108による振幅成分に対するフィルタリング処理を行い、パワー信号  $P_2$  をデジタル回路33に出力する。

## 【0190】

ここで、図12のダイレクトコンバージョン回路310におけるQPSK2およびQPSK3を考察する。以下のように2つのケースを一緒に扱うことができる。次の受信SS信号を考察する。

## 【0191】

## 【数22】

$$r(t) = Re \left\{ d(t) c(t) e^{j(\omega_t t + \phi)} \right\} \quad (24)$$

## 【0192】

10

20

30

40

50

ここで、 $c(t) = c_i(t) + j c_q(t)$  は複素拡散コード（2つの実拡散コード）であり、 $d(t)$  はデータ信号である。上述したように、 $d(t)$  が実成分であれば、QPSK2 であり、 $d(t)$  が複素成分であれば、QPSK3 である。

【0193】

ここで、式(24)の信号を検波するためのダイレクトコンバージョン回路310について考察する。たとえば下記のローカル信号 $l_i(t)$ の総和に基づき、受信信号は二乗検波器に入力する。

【0194】

【数23】

$$l_i(t) = \operatorname{Re} \left\{ c^*(t) e^{-j(\omega_c t - \frac{\pi}{4} + \theta)} \right\}$$

10

【0195】

そして、次式(25)が得られる。

【0196】

【数24】

$$\begin{aligned} & \left( \operatorname{Re} \left\{ d(t) c(t) e^{j(\omega_c t + \phi)} \right\} + \operatorname{Re} \left\{ c^*(t) e^{-j(\omega_c t - \frac{\pi}{4} + \theta)} \right\} \right)^2 - \frac{1}{4} \times \\ & \left( d(t) c(t) e^{j(\omega_c t + \phi)} + d^*(t) c^*(t) e^{-j(\omega_c t + \phi)} + c^*(t) e^{-j(\omega_c t - \frac{\pi}{4} + \theta)} + c(t) e^{j(\omega_c t - \frac{\pi}{4} + \theta)} \right) \\ & = \gamma^2(t) + l_i^2(t) + |c(t)|^2 d(t) e^{j(\phi + \frac{\pi}{4} - \theta)} + |c(t)|^2 d^*(t) e^{-j(\phi + \frac{\pi}{4} - \theta)} \end{aligned}$$

20

+ double freq. terms

(25)

30

【0197】

受信およびローカル信号の二乗と二乗周波数項を減算し、 $|c(t)|^2 = 2$  と仮定すると（たとえば方形のローカルチップパルス）、次式が得られる。

【0198】

【数25】

$$I = \frac{1}{2} \left( d(t) e^{j(\phi + \frac{\pi}{4} - \theta)} + d^*(t) e^{-j(\phi + \frac{\pi}{4} - \theta)} \right)$$

40

【0199】

次のようなローカル信号を用いて上記と同様の処理により、結果 $Q$ を得る。

【0200】

【数26】

$$I_r(t) = \operatorname{Re} \left\{ c^*(t) e^{-j(\omega_c t - \frac{\pi}{4} - \theta)} \right\}$$

(27)

【0201】

【数27】

50

$$Q = \frac{1}{2} \left( d(t) e^{j(\phi + \frac{\pi}{4} + \theta)} + d^*(t) e^{-j(\phi + \frac{\pi}{4} + \theta)} \right) \quad (28)$$

【 0 2 0 2 】

今、  $\phi = \pi/4$  では、以下の 2 つの出力が得られる。

【 0 2 0 3 】

【 数 2 8 】

$$I(t) = \frac{1}{2} (d(t) e^{j\phi} + d^*(t) e^{-j\phi}) = Re(d(t) e^{j\phi}) \quad (29)$$

$$Q(t) = \frac{j}{2} (d(t) e^{j\phi} - d^*(t) e^{-j\phi}) = -Im(d(t) e^{j\phi}) \quad (30)$$

【 0 2 0 4 】

したがって、データ信号は次のように確定できる。

【 0 2 0 5 】

【 数 2 9 】

$$d(t) = (I(t) - jQ(t)) e^{-j\phi} \quad (31)$$

【 0 2 0 6 】

上記処理は、図 12 の 5 ポートダイレクトコンバージョン回路 310 において実行される。

【 0 2 0 7 】

次に、種々の QPSK スキームのための図 11 の PN コード同期回路について説明する。そのアプローチは、ダイレクト検波対応回路を用いて PN コード同期を達成することであり、キャリア周波数および位相同期をベースバンド処理においてデジタル領域に任せることである。データ変調を伴わない受信信号の場合を仮定する。したがって、全ての QPSK スキームでは、同期問題は、次の形式の信号にロックすることに帰することになる。

【 0 2 0 8 】

【 数 3 0 】

$$r(t) = A \left( c_I(t) \cos(\omega_o t + \phi) + c_Q(t) \sin(\omega_o t + \phi) \right) \quad (32)$$

【 0 2 0 9 】

ここで、 $c_I(t)$  および  $c_Q(t)$  は 2 つの拡散コード、QPSK2 (IS-95) の場合いわゆる直交拡散である。

【 0 2 1 0 】

この場合、拡散コード同期を達成するため、送信機で互いにロックしているので、2つの PN コードのいずれかに同期すれば十分である。よって、主として、2つの直交拡散のいずれかにセットされた  $c(t)$  を用いる図 7 あるいは図 10 のタイプの回路を用いることができる。

【 0 2 1 1 】

また、トラッキンググループにおいてより高い SNR を達成するために、図 13 に示すような、ローカル QPSK タイプの信号と効果的に相互関係を示す回路を実現できる。

【 0 2 1 2 】

図 13 は、ローカル QPSK タイプの信号と効果的に相互関係を示す図 11 の PN コード同期回路である。

10

20

30

40

50

ド同期保持回路の構成例を示す図である。

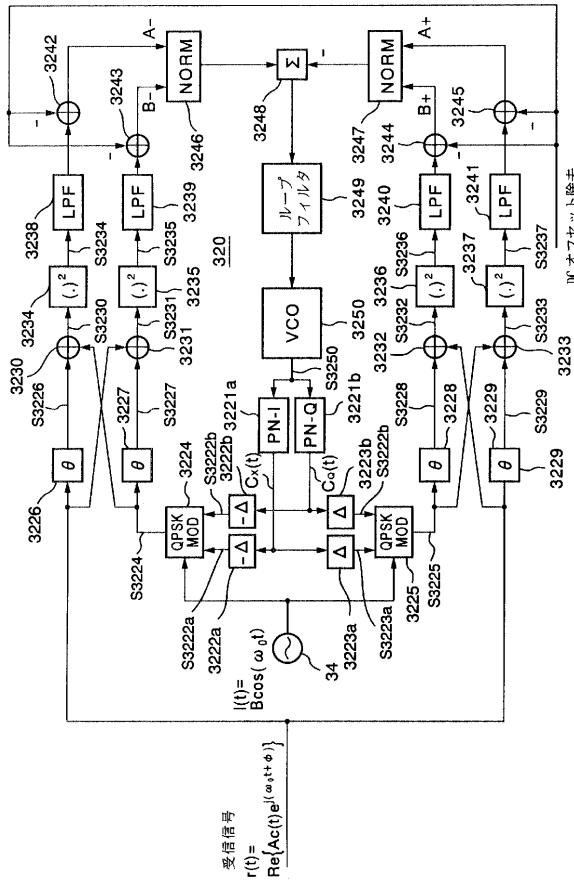

【0213】

P N コード同期保持回路 330 は、図 13 に示すように、P N コード生成器 3221a, 3221b、位相調整回路 3222a, 3222b, 3223a, 3223b、Q P S K 復調器 3224, 3225、位相シフタ 3226, 3227, 3228, 3229、加算器 3230, 3231, 3232, 3233、二乗検波器 3234, 3235, 3236, 3237、L P F 3238, 3239, 3240, 3241、減算器 3242, 3243, 3244, 3245、ノルム回路 3246, 3247、総和回路 3248、ループフィルタ 3249、および V C O 3250 を有している。

【0214】

P N コード生成器 3231a においては、P N コード  $c_1(t)$  が V C O 3250 による制御信号 S3250 に基づいて生成され、生成された P N コード  $c_1(t)$  は、位相調整回路 3222a, 3223b、および図 12 の 5 ポートダイレクトコンバージョン回路 310 の Q P S K 変調器 3101 に出力される。

【0215】

P N コード生成器 3231b においては、P N コード  $c_Q(t)$  が V C O 3250 による制御信号 S3250 に基づいて生成され、生成された P N コード  $c_Q(t)$  は、位相調整回路 3222b, 3223b、および図 12 の 5 ポートダイレクトコンバージョン回路 310 の Q P S K 変調器 3101 に出力される。

【0216】

位相調整回路 3222a においては、P N コード生成器 3221 により生成された P N コード  $c_1(t)$  の位相が、- (公称、 $= 1/2$  チップ) だけ遅延され、信号 S3222a ( $c_1(t -)$ ) が Q P S K 変調器 3224 に出力される。

【0217】

位相調整回路 3222b においては、P N コード生成器 3221 により生成された P N コード  $c_Q(t)$  の位相が、- (公称、 $= 1/2$  チップ) だけ遅延され、信号 S3222b ( $c_Q(t -)$ ) が Q P S K 変調器 3224 に出力される。

【0218】

位相調整回路 3223a においては、P N コード生成器 3221 により生成された P N コード  $c_1(t)$  の位相が、+ だけ遅延され、信号 S3223a ( $c_1(t +)$ ) が Q P S K 変調器 3225 に出力される。

【0219】

位相調整回路 3223b においては、P N コード生成器 3221 により生成された P N コード  $c_Q(t)$  の位相が、+ だけ遅延され、信号 S3223b ( $c_Q(t +)$ ) が Q P S K 変調器 3224 に出力される。

【0220】

Q P S K 変調器 3224 においては、ローカル信号  $1(t) [= B \cos(\omega_0 t)]$  が位相調整回路 3222a, 3222b の出力信号 S3222a, 3222b によって変調され、信号 S3224 が位相シフタ 3227 および加算器 3230 に出力される。

【0221】

一方、Q P S K 変調器 3225 においては、ローカル信号  $1(t)$  が位相調整回路 3223a, 3223b の出力信号 S3223a, 3223b によって変調され、信号 S3225 が位相シフタ 3228 および加算器 3233 に出力される。

【0222】

位相シフタ 3226 においては、受信信号  $r(t)$  が (たとえば  $45^\circ$ ) だけ位相シフトされ、信号 S3226 が加算器 3230 に出力される。

【0223】

位相シフタ 3227 においては、Q P S K 変調器 3224 の出力信号 S3224 が だけ位相シフトされ、信号 S3227 が加算器 3231 に出力される。

【0224】

10

20

30

40

50

加算器 3230においては、位相シフタ3226の出力信号S3226とQPSK変調器3224の出力信号S3224とが加算され、信号S3230が二乗検波器3234に出力される。

【0225】

加算器2231においては、受信信号 $r(t)$ と位相シフタ3227の出力信号S3227とが加算され、信号S3231が二乗検波器3235に出力される。

【0226】

二乗検波器3234においては、加算器3230の出力信号S3230が二乗され、LPF3238に出力され、そして減算器3242に入力される。

【0227】

減算器3242においては、LPF3238の出力からDCオフセット等が除去され、ノルム回路3246に出力される。

【0228】

同様に、二乗検波器3235においては、加算器3231の出力信号S3231が二乗され、LPF3239に出力され、そして減算器3243に入力される。

【0229】

減算器3243においては、LPF3239の出力からDCオフセット等が除去され、ノルム回路3246に出力される。

【0230】

ノルム回路3246においては、ベクトルのノルムが計算され、総和回路3248に出力される。

【0231】

位相シフタ3228においては、QPSK変調器3225の出力信号S3225がだけ位相シフトされ、信号S3228が加算器3232に出力される。

【0232】

位相シフタ3229においては、受信信号 $r(t)$ が(たとえば45°)だけ位相シフトされ、信号S3229が加算器3233に出力される。

【0233】

加算器3232においては、受信信号 $r(t)$ と位相シフタ3228の出力信号S3228とが加算され、信号S3232が二乗検波器3236に出力される。

【0234】

加算器3233においては、位相シフタ3229の出力信号S3229とQPSK変調器3225の出力信号S3225とが加算され、信号S3233が二乗検波器3237に出力される。

【0235】

二乗検波器3236においては、加算器3232の出力信号S3232が二乗され、LPF3240に出力され、そして減算器3244に入力される。

【0236】

減算器3244においては、LPF3240の出力からDCオフセット等が除去され、ノルム回路3247に出力される。

【0237】

同様に、二乗検波器3237においては、加算器3233の出力信号S3233が二乗され、LPF3241に出力され、そして減算器3245に入力される。

【0238】

減算器3245においては、LPF3241の出力からDCオフセット等が除去され、ノルム回路3247に出力される。

【0239】

ノルム回路3247においては、ベクトルのノルムが計算され、総和回路3248に出力される。

【0240】

10

20

30

40

50

総和回路 3248においては、ノルム回路 3246および3247の出力の総和がとられ、ループフィルタ 3249を介して VCO 3250に出力される。

【0241】

VCO 3250においては、発振周波数がループフィルタ 3249の出力により変化し、制御信号 S3250の値が発振周波数の変化に応じて変化する。

【0242】

図13の構成によれば、A(減算器 3242の出力)における信号は次のように与えられる。

【0243】

【数31】

10

$$\begin{aligned} & \left( \frac{B}{2} \left( c(t-\Delta) e^{j(\omega_b t - \theta)} + c^*(t-\Delta) e^{-j(\omega_b t - \theta)} \right) + \frac{A}{2} \left( c(t) e^{j(\omega_b t + \phi)} + c^*(t) e^{-j(\omega_b t + \phi)} \right) \right)^2 \\ & = \left( B \operatorname{Re} \left\{ c(t-\Delta) e^{j(\omega_b t - \theta)} \right\} \right)^2 + \left( A \operatorname{Re} \left\{ c(t) e^{j(\omega_b t + \phi)} \right\} \right)^2 + AB \operatorname{Re} \left\{ c(t-\Delta) c(t) e^{j(2\omega_b t + \phi - \theta)} \right\} \\ & + AB \operatorname{Re} \left\{ c^*(t-\Delta) c(t) e^{j(\phi + \theta)} \right\} \end{aligned}$$

【0244】

今、上記において第1の3つの項は、DCあるいは二重周波数項である。よって、信号がローパスフィルタを通過すると、DCオフセットが除去され、次のようなAにおける信号が得られる。

20

【0245】

【数32】

$$AB \operatorname{Re} \left\{ \overline{c^*(t-\Delta) c(t)} e^{j(\phi + \theta)} \right\} \quad (33)$$

【0246】

ここで、バーはローパスフィルタリングを示している。同様の方法で、B-, A+, B+における信号はそれぞれ次のように得られる。

30

【0247】

【数33】

(34)

$$AB \operatorname{Re} \left\{ \overline{c^*(t-\Delta) c(t)} e^{j(\phi - \theta)} \right\} \quad (34)$$

(35)

$$AB \operatorname{Re} \left\{ \overline{c^*(t+\Delta) c(t)} e^{j(\phi + \theta)} \right\} \quad (35)$$

(36)

$$AB \operatorname{Re} \left\{ \overline{c^*(t+\Delta) c(t)} e^{j(\phi - \theta)} \right\} \quad (36)$$

40

【0248】

式(33)および式(34)における2つの値をベクトルおよび得られる  $L_2$  ノルムの2つの成分として扱うと、トラッキングループのためのエラー信号の計算における任意の位相依存性を除去できる。

【0249】

また、簡単化の実現および  $L_1$  ノルムを伴う計算に役立つ。ここでノルムの計算は、2つの複素数の絶対値の和に帰着することになる。

【0250】

次に、キャリア位相シフタを必要としない略最適な同期保持回路について考察する。

【0251】

50

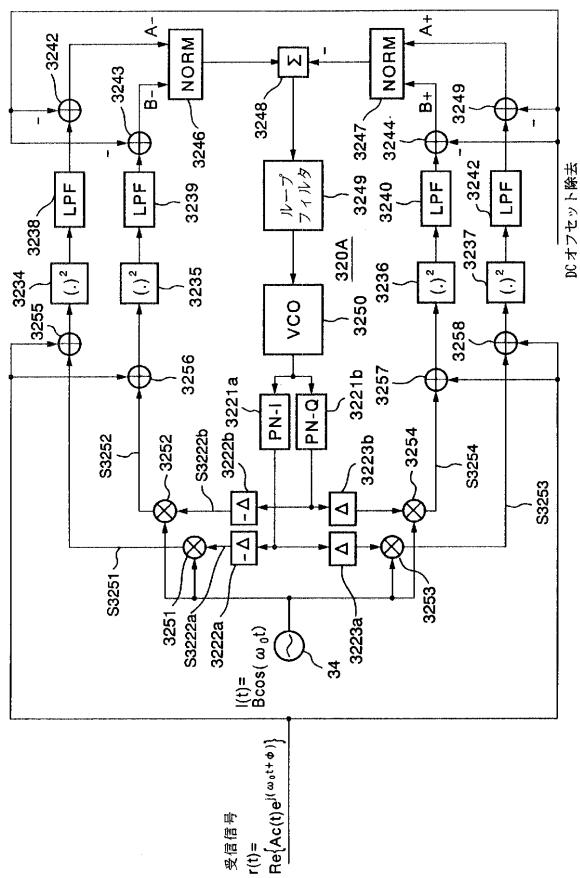

図14は、キャリア位相シフタを備えない図11のPNコード同期保持回路の他の構成例を示す図である。

【0252】

図14においては、乗算器3251および3252が図13のQPSK変調器3224の代わりに設けられている。乗算器3251は、ローカル信号1(t)と位相調回路3222aの出力信号S3222aを乗算する。乗算器3252は、ローカル信号1(t)と位相調回路3222bの出力信号S3222bを乗算する。

【0253】

同様に、図14においては、乗算器3253および3254が図13のQPSK変調器3225の代わりに設けられている。乗算器3253は、ローカル信号1(t)と位相調回路3223aの出力信号S3223aを乗算する。乗算器3254は、ローカル信号1(t)と位相調回路3223bの出力信号S3223bを乗算する。

10

【0254】

また、図14においては、加算器3255および3256が、図13の位相シフタ3226および3227、並びに加算器3230および3231の代わりに設けられている。加算器3255は、受信信号r(t)と乗算器3251の出力信号S3251を加算する。加算器3256は、受信信号r(t)と乗算器3252の出力信号S3252を加算する。

【0255】

また、図14においては、加算器3257および3258が、図13の位相シフタ3228および3229、並びに加算器3232および3233の代わりに設けられている。加算器3257は、受信信号r(t)と乗算器3254の出力信号S3254を加算する。加算器3258は、受信信号r(t)と乗算器3254の出力信号S3254を加算する。

20

【0256】

図14の構成によれば、A(減算器3242の出力)における信号は次のように与えられる。

【0257】

【数34】

$$\begin{aligned}

& AB \operatorname{Re} \left\{ \overline{c_i(t - \Delta)} c_i(t) e^{j\phi} \right\} \\

& = AB \left( \overline{c_i(t - \Delta)} \overline{c_i(t)} \cos \phi - \overline{c_i(t - \Delta)} c_i(t) \sin \phi \right) \\

& = AB \overline{c_i(t - \Delta)} \overline{c_i(t)} \cos \phi

\end{aligned} \tag{37}$$

30

【0258】

ここで、近似は、低相互相関を有する同相および直交コード $c_i(t)$ および $c_Q(t)$ に基づく。同様に、B(減算器3243の出力)における信号は次のように計算できる。

【0259】

【数35】

$$\begin{aligned}

& AB \operatorname{Re} \left\{ \overline{c_Q(t - \Delta)} c_i(t) e^{j\phi} \right\} \\

& = AB \left( \overline{c_Q(t - \Delta)} \overline{c_i(t)} \cos \phi - \overline{c_Q(t - \Delta)} c_i(t) \sin \phi \right) \\

& = -AB \overline{c_Q(t - \Delta)} \overline{c_i(t)} \sin \phi

\end{aligned} \tag{38}$$

40

【0260】

今、A-およびB-における信号を考察すると、両者をゼロにさせる位相の値がない。

50

$|\cos|$  がゼロになると、 $|\sin|$  が最大となり、逆もまた同様である。上記と同様の方法において、回路のより低いブランチに対応する信号は次のように計算可能である。

【0261】

【数36】

$$\begin{aligned}

& AB \operatorname{Re} \left\{ \overline{c_l(t + \Delta)} c_l(t) e^{j\phi} \right\} \\

& = AB \left( \overline{c_l(t + \Delta)} \overline{c_l(t)} \cos \phi - \overline{c_l(t + \Delta)} \overline{c_\varrho(t)} \sin \phi \right) \\

& \blacksquare AB \overline{c_l(t + \Delta)} \overline{c_l(t)} \cos \phi

\end{aligned} \tag{39}$$

10

【0262】

【数37】

$$\begin{aligned}

& AB \operatorname{Re} \left\{ \overline{c_\varrho(t + \Delta)} c_l(t) e^{j\phi} \right\} \\

& = AB \left( \overline{c_\varrho(t + \Delta)} \overline{c_l(t)} \cos \phi - \overline{c_\varrho(t + \Delta)} \overline{c_\varrho(t)} \sin \phi \right) \\

& \blacksquare -AB \overline{c_\varrho(t + \Delta)} \overline{c_\varrho(t)} \sin \phi

\end{aligned} \tag{40}$$

20

【0263】

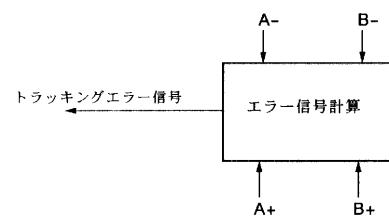

図14に示すように、A-，B-，A+，およびB+における信号は処理できる。しかしながら、2つのノルムブロック（ノルム回路3246，3247）と加算器（あるいは減算器）を、存在するループにおけるノイズ、DCオフセット、および他の欠陥によりよい性能を持つさらに一般化されたブロックと置き換えることが望ましい。

【0264】

図15に示す一般化されたブロックが利用できる。この場合、エラー信号を計算するためのアルゴリズムは、いずれの欠陥にも活用でき、アナログ回路の成分の特性の変化にさえ適応できる。

30

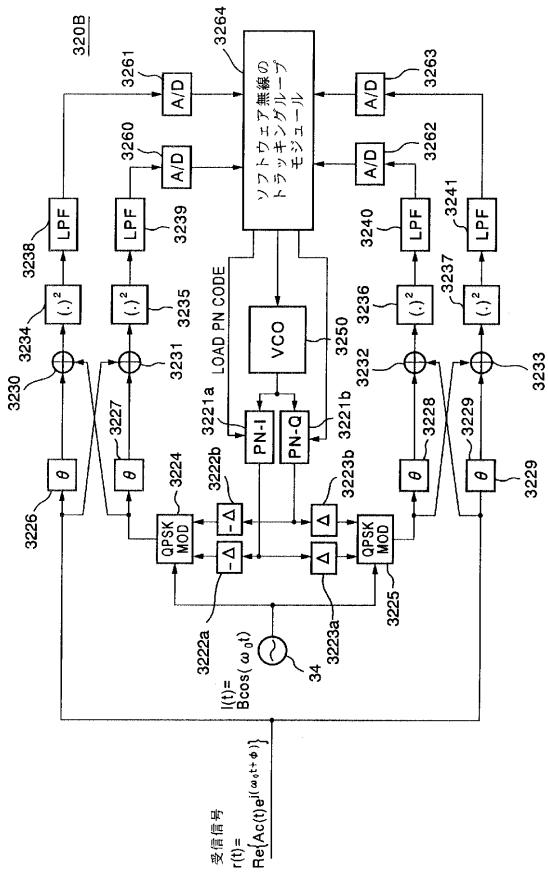

【0265】

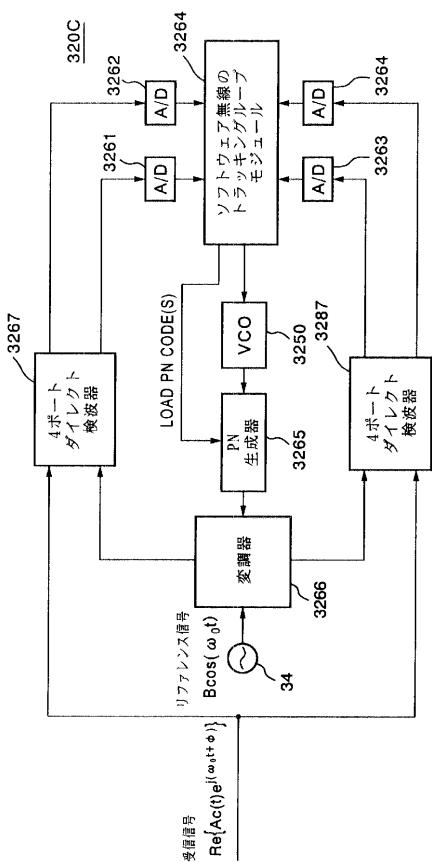

図16は、ソフトウェア無線用の図11のPNコード同期保持回路の他の構成例を示す図である。

【0266】

図16の回路320bが図13の回路と異なる点は、図13のDC除去用減算器3242～3245、ノルム回路3246および3247、総和回路3248、およびループフィルタ3249の代わりに、LPF3238，3239，3240、および3241の出力にADコンバータ3260，3261，3262、および3263を設け、かつ、ソフトウェア無線アーキテクチャを生成する部分であるデジタルプロセッサ3264を設けたことがある。

40

【0267】

ここまで検討した種々のDS/SS同期保持器回路のためのアーキテクチャは、RF周波数で動作する部分、およびより低い周波数で動作する部分を含む。低周波数部は、異なる干渉環境、および回路によって導入される周波数オフセットおよびDCオフセットの異なるケースにおける同期保持回路の柔軟な動作を達成するために、デジタル式に実現できる。

【0268】

そのような変更は、より高速なロック処理も生じさせることができる。したがって、最適化された同期捕捉回路および同期保持回路の設計では、一つのユニットに含めることができる。

50

## 【0269】

したがって、P Nコード同期保持回路320Bにおいては、A / Dコンバータ3260～3263がL P F (ローパスフィルタ)3238～3241の後段に設けられている。また、上述したように、図13のD C除去用減算器3242～3245、ノルム回路3246および3247、総和回路3248、およびループフィルタ3249が、全てデジタルプロセッサ3264、すなわち全てのソフトウェア無線アーキテクチャの部分に組み入れられている。それはそのようなアーキテクチャにおけるソフトウェアモジュールとなり得る。

## 【0270】

また、図3および図4のダイレクトコンバージョン回路210および210Aは、パワー検波用F E Tデバイス(上述した文献〔1〕参照)の基本原理を含む代替えの形態を採用できる。これらの形態の全ては、少なくとも2つの入力(受信信号およびローカルリファレンス信号)と少なくとも2つの出力信号を持つ。各出力は、一方の入力信号が、他方に對して角度だけ位相シフトされている入力信号の和のパワー信号(ローパスでフィルタリングされた信号)から構成される。出力信号は、受信信号の同相および直交成分を抽出可能にするに十分な情報を含む。4ポート回路は、基本的には、F E T出力における信号パワー(電力)をローパス(たとえばR Cフィルタ)でフィルタリングする、図17に示すような形態を持つ。

## 【0271】

一般化された図17の4ポートダイレクトコンバージョン回路に基づいて、図18に示すような一般化されたP Nコード同期保持回路を設計できる。

## 【0272】

図18において、3256はP N生成器を示し、3266は変調器を示し、3267および3268は4ポートダイレクトコンバージョン回路を示している。

## 【0273】

たとえば、変調器3266は、図13の位相調整回路3222a, 3222b, 3223a, および3223b、並びにQ P S K変調器3224および3225を含み、一方、4ポートダイレクトコンバージョン回路3267は、図13の位相シフタ3226, 3227、加算器3230, 3231、二乗検波器3234, 3235、およびL P F 3238, 3239を含んでいる。

## 【0274】

同様に、4ポートダイレクトコンバージョン回路3268は、図13の位相シフタ3228, 3229、加算器3232, 3233、二乗検波器3236, 3237、およびL P F 3240, 3241を含んでいる。

## 【0275】

図16および図18の回路は、ソフトウェアモジュール(デジタルプロセッサ)におけるアルゴリズムを適切に設計することにより、P Nコード同期捕捉と同期保持の両方に使用することができる。P Nコード同期捕捉では、モジュールは、究極的に、ローカルP Nコードを受信したP Nコードを用いるアルゴリズムに取り入れる周波数系列(sequence)を通じたV C O 3250の効果的に周波数を進める(ステップする)エラー信号系列を出力できる。いずれの同期捕捉および同期保持回路において、重要なパラメータは、二乗検波器3234～3237の出力、あるいはA / Dコンバータ3260～3263の入力におけるフィルタの帯域である。

## 【0276】

この帯域は、同等の積分時間を効果的に決定する。最適な同期捕捉回路は、受信信号r(t)のS N Rによる積分時間を持たなければならない。固定帯域(F E T出力における固定R Cフィルタ)の4ポートダイレクトコンバージョン回路を設計でき、さらにソフトウェアモジュールにおけるデジタル式のフィルタリングを実現できる。ソフトウェアモジュールの実際のアルゴリズムは、P Nコード長、受信信号のS N R、および同期捕捉処理の開始時のクロック周波数不確定による。

10

20

30

40

50

## 【0277】

この実施形態において、直接拡散スペクトル拡散信号のためのダイレクト検波およびP Nコード同期用回路について説明した。これら回路は、最近開発された高い線形性の程度を示す広帯域ダイレクト検波F E T回路の使用に基づいている。本実施形態において説明した回路は、スペクトル拡散における逆拡散機能をアナログにより効果的に実現している。そのような実現は、結果としてP Nコード拡散クロック周波数と無関係に受信機の複雑さをもたらす。その結果である回路は、3 G W C D M Aあるいはその他の将来のシステム用広帯域受信機の設計に重要である。

## 【0278】

すなわち、本実施形態によれば、F E T広帯域ダイレクトコンバータ回路に基づく直接拡散R Fスペクトル拡散信号のアナログの逆拡散およびダイレクトコンバージョンのための回路が述べられている。この回路は、回路の複雑さがチップレートに無関係な、非常に高チップレートの電力効率スペクトル拡散システムの設計を可能としている。この回路の使用は、背景技術の現状における問題、すなわち、チップレートに伴って電力消費が増大するスペクトル拡散の現実を解決する。

10

## 【0279】

また、この実施形態においては、直接拡散スペクトル拡散の異なるタイプのP Nコード同期および逆拡散のための回路が述べられている。これらの回路は、現代の直接拡散スペクトル拡散受信機の背景技術において習慣的に現実化されるチップレートに代わり、データシンボルレート（あるいは、シンボルレートの小さい倍数）でデジタル処理が実行されるソフトウェア無線受信機の設計を可能としている。

20

## 【0280】

これらの回路では、チップレートは、帯域およびF E Tダイレクト検波回路の線形性によってのみ制限される。最近の非常に広帯域で広ダイナミックレンジを持つF E Tダイレクト検波器の開発は、ここで提案した直接拡散スペクトル拡散受信機の設計のための提案されたアプローチの実現を可能としている。

## 【0281】

したがって、本発明は、インターネットに接続する低コスト情報処理デバイスを含む、スペクトル拡散およびC D M Aシステムのための極めて簡単化された受信機の設計を許容する。スペクトル拡散システムは、受信機の複雑さによる拡散帯域において典型的に制限を受ける。本発明は、これらシステムの帯域制限を、非常に拡げている。

30

## 【0282】

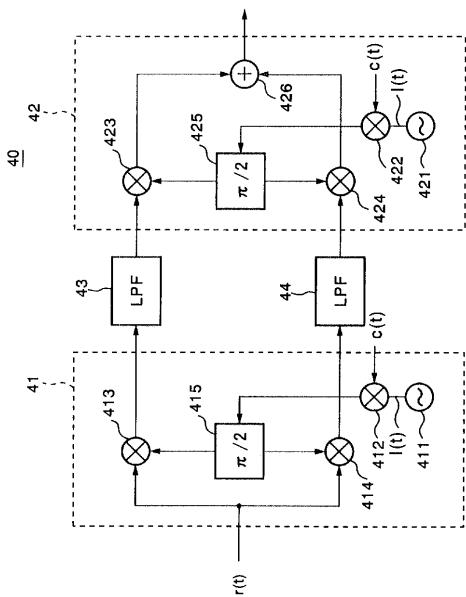

なお、本実施形態においては、nポートデバイスとして、逆拡散用ダイレクトコンバージョン回路を例に説明したが、本発明は、他のタイプのダイレクトコンバージョン回路、たとえば図19に示すような（たとえば、特開平11-317777号公報 参照）回路を適用できる。

## 【0283】

図19のダイレクトコンバージョン回路40は、直交変調器41、直交変調器42、およびL P F 43および44を有している。

40

## 【0284】

直交変調器41は、ローカル発振器411、乗算器412, 413, および414、並びに位相シフタ（/2シフタ）415により構成されている。

## 【0285】

直交変調器41においては、乗算器412がローカル信号1(t)とP Nコードc(t)を掛け合わせる（乗算する）。

## 【0286】

また、直交変調器42は、ローカル発振器421、乗算器422, 423, および424、位相シフタ425、および加算器426により構成されている。

## 【0287】

直交変調器42においては、乗算器432がローカル信号1(t)とP Nコードc(t)

50

を掛け合わせる（乗算する）。

【0288】

本発明は図解の目的のために選択された特定の実施形態に関連付けて説明したが、本発明の基本概念および範囲を逸脱しない範囲で、当業者によって変更しえる種々の変更が可能であることは明らかである。

【0289】

以上説明したように、本スペクトル拡散受信機によれば、スペクトル拡散受信機はダイレクトコンバージョン技術に基づく回路21, 22を採用している。これらの回路は、大幅に複雑が低減し、標準アプローチの完全なデジタル受信機で実現可能なレートより非常に高速のチップレートのスペクトル拡散受信機を許容する、これらの回路を用いることによって、受信機でのデジタル処理は、背景技術のおけるスペクトル拡散およびCDMA受信機の設計に習慣的に用いられるチップレートの倍数でなく、データシンボルレートで実行される。

10

【図面の簡単な説明】

【図1】従来の直接拡散スペクトル拡散受信機のブロック図である。

【図2】本発明に係るスペクトル拡散受信機の第1の実施形態を示すブロック図である。

【図3】本発明に係る5ポートダイレクトコンバージョン回路の構成例を示す図である。

【図4】本発明に係る4ポートダイレクトコンバージョン回路の構成例を示す図である。

【図5】直交変調信号の一般的な場合における4ポートダイレクトコンバージョン回路の等価回路を示す図である。

20

【図6】周波数見積およびデジタル見積の場合に基づく受信機を示す図である。

【図7】図2のPF符号同期保持回路の構成例を示す図である。

【図8】PNコード相關の説明図である。

【図9】同期保持 "S" カーブの説明図である。

【図10】図2のPNコード同期保持回路の他の構成例を示す図である。

【図11】本発明に係るスペクトル拡散受信機の第2の実施形態を示すブロック図である。

【図12】本発明に係るDS/BPSK用5ポートダイレクトコンバージョン回路の構成例を示す図である。

【図13】ローカルQPSKタイプの信号と効果的に相互関係を示す図11のPNコード同期保持回路の構成例を示す図である。

30

【図14】キャリア位相シフタを有していない図11のPNコード同期保持回路5の他の構成例を示す図である。

【図15】一般化されたエラー信号計算の説明図である。

【図16】ソフトウェア無線用の図11のPNコード同期保持回路の他の構成例を示す図である。

【図17】一般化された4ポートダイレクトコンバージョン回路を示す図である。

【図18】一般化されたソフトウェア無線用PNコード同期保持回路を示す図である。

【図19】本発明に係るダイレクトコンバージョン回路の他のタイプを示す図である。

【符号の説明】

40

20 スペクトル拡散受信機

21 nポートダイレクトコンバージョン回路

22 PNコード同期保持回路

23 デジタル回路

24 ローカル発振器

210 5ポートダイレクトコンバージョン回路

2101 乗算器

2102, 2103 位相シフタ

2104, 2105 加算器

2106 ~ 2108 二乗検波器

50

|                                               |                     |    |

|-----------------------------------------------|---------------------|----|

| 2 1 0 9 ~ 2 1 1 1                             | R C フィルタ            |    |

| 2 1 0 A                                       | 4 ポートダイレクトコンバージョン回路 |    |

| 2 2 0                                         | P N コード同期保持回路       |    |

| 2 2 0 1                                       | P N コード生成器          |    |

| 2 2 0 2 , 2 2 0 3                             | 位相調整回路              |    |

| 2 2 0 4 , 2 2 0 5                             | 乗算器                 |    |

| 2 2 0 6 , 2 2 0 7                             | 加算器                 |    |

| 2 1 0 8 , 2 2 0 9                             | 二乗検波器               |    |

| 2 2 1 0 , 2 2 1 1                             | バンドパスフィルタ ( B P F ) |    |

| 2 2 1 2 , 2 2 1 3                             | エンベロープ検波器           | 10 |

| 2 2 1 4                                       | 減算器                 |    |

| 2 2 1 5                                       | ループフィルタ             |    |

| 2 2 1 6                                       | V C O               |    |

| 2 2 0 A                                       | P N コード同期保持回路       |    |

| 2 2 2 1                                       | P N コード生成器          |    |

| 2 2 2 2 , 2 2 2 3                             | 位相調整回路              |    |

| 2 2 2 4 , 2 2 2 5                             | 乗算器                 |    |

| 2 2 2 6 ~ 2 2 2 9                             | 位相シフタ               |    |

| 2 2 3 0 ~ 2 2 3 3                             | 加算器                 |    |

| 2 2 3 4 ~ 2 2 3 7                             | 二乗検波器               | 20 |

| 2 2 3 8 ~ 2 2 4 1                             | ローパスフィルタ ( L P F )  |    |

| 2 2 4 2 ~ 2 2 4 3                             | 減算器                 |    |

| 2 2 4 6 , 2 2 4 7                             | ノルム回路               |    |

| 2 2 4 8                                       | 総和回路                |    |

| 2 2 4 9                                       | ループフィルタ             |    |

| 2 2 5 0                                       | V C O               |    |

| 3 0                                           | スペクトル拡散受信機          |    |

| 3 1                                           | n ポートダイレクトコンバージョン回路 |    |

| 3 2                                           | P N コード同期保持回路       |    |

| 3 3                                           | デジタル回路              | 30 |

| 3 4                                           | ローカル発振器             |    |

| 3 1 0                                         | 5 ポートダイレクトコンバージョン回路 |    |

| 3 1 0 1                                       | Q P S K 変調器         |    |

| 3 1 0 2 , 3 1 0 3                             | 位相シフタ               |    |

| 3 1 0 4 , 3 1 0 5                             | 加算器                 |    |

| 3 1 0 6 ~ 3 1 0 8                             | 二乗検波器               |    |

| 3 1 0 9 ~ 3 1 1 1                             | R C フィルタ            |    |

| 3 2 0                                         | P N コード同期保持回路       |    |

| 3 2 2 1 a , 3 2 2 1 b                         | P N コード生成器          |    |

| 3 2 2 2 a , 3 2 2 2 b , 3 2 2 3 a , 3 2 2 3 b | 位相調整回路              | 40 |

| 3 2 2 4 , 3 2 2 5                             | Q P S K 変調器         |    |

| 3 2 2 6 ~ 3 2 2 9                             | 位相シフタ               |    |

| 3 2 3 0 ~ 3 2 3 3                             | 加算器                 |    |

| 3 2 3 4 ~ 3 2 3 7                             | 二乗検波器               |    |

| 3 2 3 8 ~ 3 2 4 1                             | L P F               |    |

| 3 2 4 2 ~ 3 2 4 5                             | 減算器                 |    |

| 3 2 4 8                                       | 総和回路                |    |

| 3 2 4 9                                       | ループフィルタ             |    |

| 3 2 5 0                                       | V C O               |    |

| 3 2 0 A                                       | P N コード同期保持回路       | 50 |

3 2 5 1 ~ 3 2 5 4 乗算器

3 2 5 5 ~ 3 2 5 8 加算器

3 2 0 B PNコード同期保持回路

3 2 6 0 ~ 3 2 6 3 A / D コンバータ

3 2 6 4 デジタルプロセッサ

3 2 0 C PNコード同期保持回路

3 2 6 6 変調器

3 2 6 7 , 3 2 6 8 4 ポートダイレクトコンバージョン回路

4 0 ダイレクトコンバージョン回路

4 1 直交変調器 10

4 2 直交変調器

4 3 , 4 4 L P F

4 1 1 , 4 2 1 ローカル発振器

4 1 2 ~ 4 1 4 , 4 2 2 ~ 4 2 4 乗算器

4 1 5 , 4 2 5 位相シフタ

4 2 6 加算器

【図1】

【図2】

【 义 3 】

【 図 4 】

【図5】

【図6】

【圖 7】

【 8 】

【図9】

【 四 1 0 】

### 【図 1 1】

【 図 1 2 】

【図13】

### 【図14】

【図15】

【図16】

【図17】

【図18】

【 図 1 9 】

---

フロントページの続き

(56)参考文献 特開昭62-076942(JP,A)

特開平08-056176(JP,A)

特開平09-261114(JP,A)

特開平01-188130(JP,A)

特開平09-219728(JP,A)

特開平10-303776(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04B 1/707

H04L 7/00

H04L 27/22