(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6234008号

(P6234008)

(45) 発行日 平成29年11月22日(2017.11.22)

(24) 登録日 平成29年11月2日(2017.11.2)

(51) Int.Cl.

F 1

H03K 19/00 (2006.01)

H03K 19/00

108

H03B 5/32 (2006.01)

H03B 5/32

A

H03K 19/003 (2006.01)

H03B 5/32

C

HO3K 19/003

169

請求項の数 5 (全 24 頁)

(21) 出願番号

特願2012-74294 (P2012-74294)

(22) 出願日

平成24年3月28日(2012.3.28)

(65) 公開番号

特開2013-207537 (P2013-207537A)

(43) 公開日

平成25年10月7日(2013.10.7)

審査請求日

平成27年3月19日(2015.3.19)

審判番号

不服2016-16774 (P2016-16774/J1)

審判請求日

平成28年11月9日(2016.11.9)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区新宿四丁目1番6号

(74) 代理人 100116665

弁理士 渡辺 和昭

(74) 代理人 100164633

弁理士 西田 圭介

(74) 代理人 100179475

弁理士 仲井 智至

(72) 発明者 伊藤 久浩

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(72) 発明者 二村 良彦

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

最終頁に続く

(54) 【発明の名称】発振回路及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

共振子を駆動して交流信号を出力する共振子駆動回路と、

第1の電源電圧が供給され、容量を介して入力される前記交流信号から第1の増幅器を介して第1の振幅レベルを有する第1のパルス信号を生成するパルス化部と、

前記第1の電源電圧より高い第2の電源電圧が供給され、前記第1のパルス信号が入力されて第2の振幅レベルを有する第2のパルス信号を出力するレベルシフト部と、

ソースから前記第1の電源電圧を出力するN型トランジスターを有するソースフォロワー回路と、

前記共振子駆動回路にPTAT (Proportional To Absolute Temperature) 電流を出力するとともに、前記N型トランジスターのゲートに電圧を出力するバンドギャップリファレンス回路と、を含み、

前記第1の増幅器の増幅率が前記レベルシフト部の増幅率よりも大きいことを特徴とする発振回路。

## 【請求項 2】

前記パルス化部は、

前記交流信号の入力ノードに接続される一方の電極と、他方の電極とを有する前記容量と、

前記容量の前記他方の電極に接続される入力端子と、前記第1のパルス信号を出力する出力端子と、を有するインバーター回路と、

前記インバーター回路の前記入力端子と前記出力端子との間に接続される帰還抵抗と、

を含むことを特徴とする請求項1に記載の発振回路。

【請求項3】

前記レベルシフト部は、

ソースに第3の電源電圧が供給され、ゲートに前記第1のパルス信号が供給されるN型の第1のトランジスターと、

ソースに前記第2の電源電圧が供給され、ドレインに前記第1のトランジスターのドレインが接続されるP型の第2のトランジスターと、

ソースに前記第3の電源電圧が供給され、ゲートに前記第1のパルス信号の反転信号が供給され、ドレインに前記第2のトランジスターのゲートが接続されるN型の第3のトランジスターと、

ソースに前記第2の電源電圧が供給され、ドレインに前記第3のトランジスターのドレインが接続され、ゲートに前記第2のトランジスターのドレインが接続されるP型の第4のトランジスターと、を含み、

前記第4のトランジスターのドレインから前記第2のパルス信号を出力することを特徴とする請求項1又は2に記載の発振回路。

【請求項4】

前記N型トランジスターのドレインに前記第2の電源電圧が供給され、前記N型トランジスターのゲートに前記第2の電源電圧に基づく電圧が供給されることを特徴とする請求項1乃至3のいずれか一項に記載の発振回路。

【請求項5】

請求項1乃至4のいずれか一項に記載の発振回路を含む電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、パルス信号生成回路、発振回路、電子機器、及びパルス信号生成方法等に関する。

【背景技術】

【0002】

従来、S P X O (Simple Packaged X'tal Oscillator) は、ユーザーにより電源が与えられると、温度補償や温度制御を行うことなく共振子の周波数安定度をそのままに発振信号を出力する発振回路として広く用いられている。このような発振回路には、低消費電力化とともに、ユーザーが要求する振幅レベルを有する発振出力を行うことが要求されている。そのため、発振回路は、発振信号の振幅レベルを変換するレベルシフト回路を備える場合がある。

【0003】

このようなレベルシフト回路については、種々提案されている。例えば特許文献1には、ゲートとドレインが交差接続された第1導電型の第1トランジスター及び第2トランジスターと、相補的にスイッチ制御される第2導電型の第3トランジスター及び第4トランジスターとを含むレベルシフト回路が開示されている。第1トランジスター及び第2トランジスターの各々には、第3トランジスター及び第4トランジスターのドレインの各々が接続される。そして、第1トランジスター又は第2トランジスターをオン状態にするとときに閾値電圧が低くなるような電圧を、抵抗素子を介して基板に供給することで、低電圧で動作マージンの改善と低消費電力化を図る。

【0004】

ところが、この種のたすきがけ接続したインバーター回路により構成されるレベルシフト回路は、その閾値電圧と、入力信号の中心電圧とが一致しないとき、ディーティー比が50パーセントの出力信号を出力することができない。従って、発振信号をそのままレベルシフト回路に入力すると、デューティー比が50パーセントの信号を得ることが困難となる。

10

20

30

40

50

**【0005】**

これに対して、例えば特許文献2又は特許文献3には、容量を介して入力された発振信号の振幅レベルを変換するようにした発振回路が開示されている。

**【0006】**

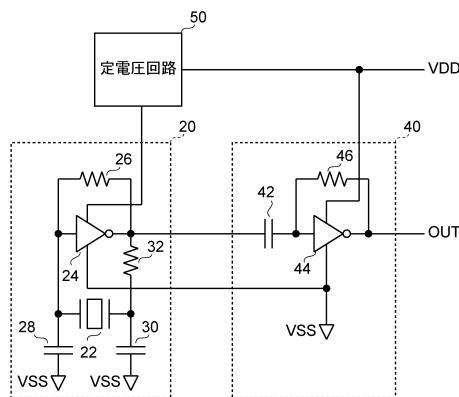

図11に、容量を介して入力された発振信号の振幅レベルを変換する従来の発振回路の構成を示す。発振回路10は、発振部20と、増幅部40と、定電圧回路50とを備えている。

**【0007】**

発振部20は、水晶振動子22と、インバーター回路24と、帰還抵抗26と、容量28,30と、ドレイン抵抗32とを備えている。容量28,30の一方の電極には、それぞれ接地電圧VSSが供給される。容量28の他方の電極と容量30の他方の電極との間には、水晶振動子22が接続される。インバーター回路24の入力には、容量28の他方の電極と帰還抵抗26の一端とが接続される。インバーター回路24の出力には、ドレイン抵抗32の一端及び帰還抵抗26の他端が接続される。ドレイン抵抗32の他端には、容量30の他方の電極が接続される。インバーター回路24の電源端子には、定電圧回路50が接続され、接地電源端子には接地電圧VSSが供給される。

10

**【0008】**

増幅部40は、容量42と、インバーター回路44と、帰還抵抗46とを備えている。容量42は、インバーター回路24の出力とインバーター回路44の入力との間に接続される。インバーター回路44の入力には、帰還抵抗46の一端が接続され、出力には、帰還抵抗46の他端が接続される。このインバーター回路44の出力が、発振回路10の出力となる。また、インバーター回路44の電源端子には、定電圧回路50が接続され、接地電源端子には接地電圧VSSが供給される。

20

**【0009】**

定電圧回路50は、発振部20のインバーター回路24、増幅部40のインバーター回路44に定電圧の電源電圧を供給する。このとき、定電圧回路50は、インバーター回路24に供給する電圧を、インバーター回路44に供給する電圧よりも低くする。

**【0010】**

発振回路10では、定電圧回路50により供給される電源電圧により発振部20を発振させることにより、発振部20の低消費電流化を図ることができる。また、振幅の小さい発振部20の出力を増幅部40に伝達するため、容量42を介してインバーター回路44に入力させることで、発振信号の交流成分がインバーター回路44に伝達される。増幅部40は、定電圧回路50により供給される電源電圧VDDまで振幅レベルを変換して、出力信号を出力する。このとき、増幅部40では、帰還抵抗46によってバイアス電圧が動作点のほぼ中間で安定するようにされるため、発振回路10の出力のデューティー比が50パーセントになりやすい。

30

**【0011】**

この点、例えば特許文献2には、レベルシフト回路をなくすため、図11の構成を有する容量結合インバーター回路を採用し、増幅部40にレベルシフト回路と出力バッファーの機能を兼用させるようにした技術が開示されている。

40

**【先行技術文献】****【特許文献】****【0012】**

【特許文献1】特開2006-237760号公報

【特許文献2】特開平1-300605号公報

【特許文献3】特開2011-244064号公報

**【発明の概要】****【発明が解決しようとする課題】****【0013】**

ところで、発振回路には、低消費電力で、ユーザーが要求する振幅レベルでデューティ

50

一比が 50 パーセントの出力信号を出力することに加えて、パルス整形の安定性や低い位相雑音が求められている。

【0014】

しかしながら、特許文献 1 に開示されたレベルシフト回路は、上記のように、入力 DC レベルが定まらないため、発振出力のような正弦波が入力されると、ディーティー比が 50 パーセントの出力を得にくいという問題がある。

【0015】

これに対して、特許文献 2 又は特許文献 3 に開示された技術によれば、ディーティー比が 50 パーセントの出力を得やすい。しかしながら、特許文献 2 又は特許文献 3 では、次のように、低消費電力化とパルス整形の安定性や低い位相雑音とを両立することができないと問題がある。 10

【0016】

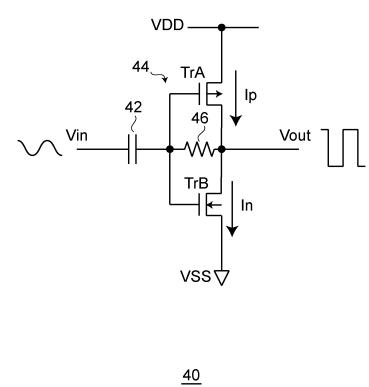

図 12 に、図 11 の増幅部 40 に流れる電流の説明図を示す。図 12 において、図 11 と同様の部分には同一符号を付し、適宜説明を省略する。

【0017】

インバーター回路 44 は、P 型の MOS (Metal-Oxide Semiconductor) トランジスター Tr A と、N 型の MOS トランジスター Tr B とにより構成される。MOS トランジスター Tr A のソースには、定電圧回路 50 によって生成された電源電圧 VDD が供給され、ゲートには、容量 42 を介して発振部 20 からの発振信号 Vin が入力され、ドレインは、増幅部 40 の出力となる。MOS トランジスター Tr B のソースには、接地電圧 VS が供給され、ゲートには、容量 42 を介して発振部 20 からの発振信号 Vin が入力され、ドレインは、増幅部 40 の出力となる。 20

【0018】

帰還抵抗 46 は、MOS トランジスター Tr A (又は MOS トランジスター Tr B) のドレインと MOS トランジスター Tr A (又は MOS トランジスター Tr B) のゲートとの間に接続される。

【0019】

ここで、MOS トランジスター Tr A のソース・ドレイン間に流れる電流を Ip 、 MOS トランジスター Tr B のソース・ドレイン間に流れる電流を In とする。

【0020】

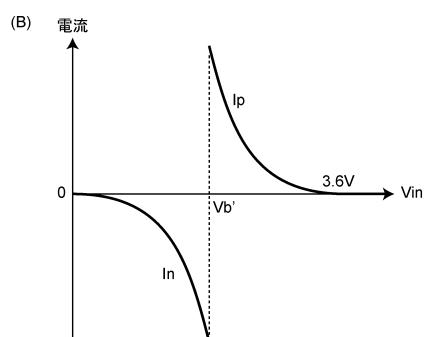

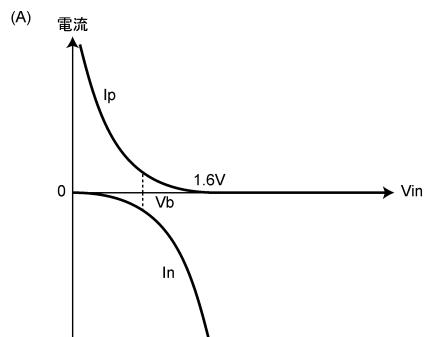

図 13 (A) 、図 13 (B) に、電流 Ip 、 In の説明図を示す。図 13 (A) 及び図 13 (B) は、横軸に発振信号 Vin 、縦軸に電流値を表す。図 13 (A) は、電源電圧 VDD が 1.6 V のときの電流 Ip 、 In の変化を模式的に表し、図 13 (B) は、電源電圧 VDD が 3.6 V のときの電流 Ip 、 In の変化を模式的に表す。 30

【0021】

発振信号 Vin の電圧が 0 V のとき、MOS トランジスター Tr A がオンとなり電流 Ip が流れ、MOS トランジスター Tr B がオフとなり電流 In が流れない。発振信号 Vin の電圧が高くなると、電流 Ip の電流値が小さくなり、電流 In の電流値が大きくなる。図 12 に示すように、増幅部 40 では、帰還抵抗 46 によりインバーター回路 44 の入力及び出力が接続されているため、自己バイアスがかかり、例えば電源電圧 VDD の中間電圧においてバイアス電圧が安定することになる。図 13 (A) では、電源電圧 VDD が 1.6 V のため、ほぼ 0.8 V (Vb) 付近にバイアス電圧が安定し、図 13 (B) では、電源電圧 VDD が 3.6 V のため、ほぼ 1.8 V (Vb') 付近にバイアス電圧が安定する。 40

【0022】

ここで、電源電圧 VDD が 1.6 V のときに MOS トランジスター Tr A 、 Tr B のサイズを最適化して図 13 (A) のように調整すると、電源電圧 VDD を 3.6 V に上げたときに、図 13 (B) のように大きな貫通電流が流れてしまい、消費電流が大きくなる。一方、電源電圧 VDD が 3.6 V のときに大きな貫通電流が流れないように MOS トランジスター Tr A 、 Tr B のサイズが小さくなるように調整すると、電源電圧 VDD を 1. 50

6 V に下げたときインバーター回路 4 4 には十分なゲインが得られない。そのため、出力波形が歪み、位相雑音が悪化するという問題がある。

【0023】

以上のように、電源電圧 VDD として広い電圧範囲での動作が要求される場合、図 1 1 の構成では、低消費電力化とパルス整形の安定性や低い位相雑音とを両立することができない。

【0024】

本発明は、上記の課題の少なくとも一部を解決するためになされたものであり、以下の形態又は態様として実現することができる。

【課題を解決するための手段】

10

【0025】

本発明の第 1 の形態は、パルス信号生成回路が、第 1 の電源電圧が供給され、容量を介して入力される交流信号から第 1 の振幅レベルを有する第 1 のパルス信号を生成するパルス化部と、前記第 1 の電源電圧より高い第 2 の電源電圧が供給され、前記第 1 のパルス信号が入力されて第 2 の振幅レベルを有する第 2 のパルス信号を出力するレベルシフト部と、を含む。

本形態においては、交流信号から所望の振幅レベルを有するパルス信号を生成する場合に、パルス化の機能とレベルシフト機能とに分け、パルス化は、第 1 の電源電圧の下で行い、レベルシフトは、パルス化の際の電源電圧より高い電源電圧の下で行う。従って、本形態によれば、パルス化をレベルシフト部の電圧よりも低い電圧で行うため、ユーザーが要求する電源電圧が高い場合でも、より低い電源電圧の下で消費電流が小さくなるようにパルス化を実現した後、レベルシフト機能により、ユーザーが要求する電源電圧まで振幅レベルを上げたパルス信号を生成することができる。従って、広い電圧範囲での動作が要求される場合、低消費電力化とパルス整形の安定性や低い位相雑音とを両立することができるようになる。

20

本発明の第 2 の形態に係るパルス信号生成回路では、第 1 の形態において、前記パルス化部は、前記交流信号の入力ノードに接続される一方の電極と、他方の電極とを有する前記容量と、前記要領の前記他方の電極に接続される入力端子と、前記第 1 のパルス信号を出力する出力端子と、を有するインバーター回路と、前記インバーター回路の前記入力端子と前記出力端子との間に接続される帰還抵抗とを含む。

30

本形態によれば、パルス化部を容量結合インバーター回路により構成するようにしたので、第 1 の電源電圧の中間電圧にバイアスされた直流レベルに交流信号が重畠するため、ディーティー比が 50 パーセントのパルス信号を生成しやすくなる。そのため、低消費電力で、ユーザーが要求する振幅レベルでデューティー比が 50 パーセントの出力信号を出力することに加えて、パルス整形の安定性や低い位相雑音を実現することができるようになる。

本発明の第 3 の形態に係るパルス信号生成回路では、第 1 の形態又は第 2 の形態において、前記レベルシフト部は、ソースに第 3 の電源電圧が供給され、ゲートに前記第 1 のパルス信号が供給される N 型の第 1 のトランジスターと、ソースに前記第 2 の電源電圧が供給され、ドレインに前記第 1 のトランジスターのドレインが接続される P 型の第 2 のトランジスターと、ソースに前記第 3 の電源電圧が供給され、ゲートに前記第 1 のパルス信号の反転信号が供給され、ドレインに前記第 2 のトランジスターのゲートが接続される N 型の第 3 のトランジスターと、ソースに前記第 2 の電源電圧が供給され、ドレインに前記第 3 のトランジスターのドレインが接続され、ゲートに前記第 2 のトランジスターのドレインが接続される P 型の第 4 のトランジスターと、を含み、前記第 4 のトランジスターのドレインから前記第 2 のパルス信号を出力する。

40

本形態によれば、レベルシフト部を、たすきがけ接続したインバーター回路により構成したので、電源電圧によらず貫通電流が大きく変化しない。このため、パルス化部におけるデューティー良好性を生かしながら、低消費電流化とパルス整形の安定性と低位相雑音特性を満足することができるようになる。

50

本発明の第4の形態に係るパルス信号生成回路は、第1の形態乃至第3の形態のいずれかにおいて、ソースから前記第1の電源電圧を出力するN型トランジスターを有するソースフォロワー回路を含む。

本形態によれば、ソースフォロワー回路により第1の電源電圧を供給するようにしたので、上記の効果に加えて、複数の電源電圧を供給するための不要な回路を省略することができるようになる。

本発明の第5の形態に係るパルス信号生成回路は、第4の形態において、前記N型トランジスターのドレインに前記第2の電源電圧が供給され、前記N型トランジスターのゲートに前記第2の電源電圧に基づく電圧が供給される。

本形態によれば、ソースフォロワー回路により、第2の電源電圧に基づいて第1の電源電圧を生成するようにしたので、上記の効果に加えて、複数の電源電圧を供給するための演算増幅器等の不要な回路を省略することができ、構成を簡素化することができる。

10

本発明の第6の形態は、発振回路が、第1の形態乃至第5の形態のいずれかのパルス信号生成回路と、共振子を駆動して前記第1のパルス信号を出力する共振子駆動回路と、を含む。

本形態によれば、パルス化部におけるデューティー良好性を生かしながら、低消費電流化とパルス整形の安定性と低位相雑音特性を満足する発振回路を提供することができるようになる。

本発明の第7の形態は、発振回路が、第4の形態のパルス信号生成回路と、共振子を駆動して前記第1のパルス信号を出力する共振子駆動回路と、前記共振子駆動回路にP T A T (Proportional To Absolute Temperature) 電流を出力するとともに、前記N型トランジスターのゲートに電圧を出力するバンドギャップリファレンス回路と、を含む。

20

本形態によれば、パルス化部におけるデューティー良好性を生かしながら、低消費電流化とパルス整形の安定性と低位相雑音特性を満足する発振回路を提供することができるようになる。更に、本形態によれば、電流駆動を行う素子の温度特性を補償することができるようになる。

本発明の第8の形態は、電子機器が、第6の形態又は第7の形態に記載の発振回路を含む。

本形態によれば、パルス化部におけるデューティー良好性を生かしながら、低消費電流化とパルス整形の安定性と低位相雑音特性を満足する発振回路が適用された電子機器を提供することができる。

30

本発明の第9の形態は、パルス信号生成方法が、共振子を駆動して発振信号を生成する発振信号生成ステップと、第1の電源電圧の下で、容量を介して入力される前記発振信号から第1の振幅レベルを有する第1のパルス信号を生成するパルス化ステップと、前記第1の電源電圧より高い第2の電源電圧の下で、前記第1のパルス信号を第2の振幅レベルを有する第2のパルス信号に変換するレベルシフトステップとを含む。

本形態においては、交流信号から所望の振幅レベルを有するパルス信号を生成する場合に、パルス化の機能とレベルシフト機能とに分け、パルス化は、第1の電源電圧の下で行い、レベルシフトは、パルス化の際の電源電圧より高い電源電圧の下で行う。従って、本形態によれば、パルス化をレベルシフト部の電圧よりも低い電圧で行うため、ユーザーが要求する電源電圧が高い場合でも、より低い電源電圧の下で消費電流が小さくなるようパルス化を実現した後、レベルシフト機能により、ユーザーが要求する電源電圧まで振幅レベルを上げたパルス信号を生成することができる。従って、広い電圧範囲での動作が要求される場合、低消費電力化とパルス整形の安定性や低い位相雑音とを両立することができるようになる。

40

本発明の第10の形態に係るパルス信号生成方法では、第9の形態において、前記発振信号生成ステップは、バンドギャップリファレンス回路から出力されるP T A T 電流を用いた電流駆動により前記発振信号を生成し、前記パルス化ステップは、前記バンドギャップリファレンス回路により生成された電圧がゲートに供給されるN型トランジスターのソース電圧を前記第1の電源電圧として、前記第1のパルス信号を生成する。

50

本形態によれば、上記の効果に加えて、構成を簡素化し、電流駆動を行う素子の温度特性を補償することができるようになる。

(1) 本発明の第1の態様は、パルス信号生成回路が、定電圧である第1の電源電圧が供給され、容量を介して入力される交流信号から第1の振幅レベルを有する第1のパルス信号を生成するパルス化部と、前記第1の電源電圧より高い第2の電源電圧が供給され、前記第1のパルス信号を第2の振幅レベルを有する第2のパルス信号に変換するレベルシフト部とを含む。

#### 【0026】

本態様においては、交流信号から所望の振幅レベルを有するパルス信号を生成する場合に、パルス化の機能とレベルシフト機能とに分け、パルス化は、一定の電源電圧の下で行い、レベルシフトは、パルス化の際の電源電圧より低い電源電圧の下で行う。従って、本態様によれば、パルス化を定電圧の下で行うため、消費電流を一定にすることができます。そのため、ユーザーが要求する電源電圧が高い場合でも、より低い電源電圧の下で消費電流が小さくなるようにパルス化を実現した後、レベルシフト機能により、ユーザーが要求する電源電圧まで振幅レベルを上げたパルス信号を生成することができる。従って、広い電圧範囲での動作が要求される場合、低消費電力化とパルス整形の安定性や低い位相雑音とを両立することができるようになる。

#### 【0027】

(2) 本発明の第2の態様に係るパルス信号生成回路では、第1の態様において、前記パルス化部は、一方の電極が前記交流信号の入力ノードに接続される前記容量と、入力端子が前記容量の他方の電極に接続され、出力端子から前記第1のパルス信号を出力するインバーター回路と、前記インバーター回路の前記入力端子と前記出力端子との間に接続される帰還抵抗とを含む。

#### 【0028】

本態様によれば、パルス化部を容量結合インバーター回路により構成するようにしたので、第1の電源電圧の中間電圧にバイアスされた直流レベルに交流信号が重畳するため、ディーティー比が50パーセントのパルス信号を生成しやすくなる。そのため、低消費電力で、ユーザーが要求する振幅レベルでデューティー比が50パーセントの出力信号を出力することに加えて、パルス整形の安定性や低い位相雑音を実現することができるようになる。

#### 【0029】

(3) 本発明の第3の態様に係るパルス信号生成回路では、第1の態様又は第2の態様において、前記レベルシフト部は、ソースに第3の電源電圧が供給され、ゲートに前記第1のパルス信号が供給されるN型の第1のトランジスターと、ソースに前記第2の電源電圧が供給され、ドレインに前記第1のトランジスターのドレインが接続されるP型の第2のトランジスターと、ソースに前記第3の電源電圧が供給され、ゲートに前記第1のパルス信号の反転信号が供給され、ドレインに前記第2のトランジスターのゲートが接続されるN型の第3のトランジスターと、ソースに前記第2の電源電圧が供給され、ドレインに前記第3のトランジスターのドレインが接続され、ゲートに前記第2のトランジスターのドレインが接続されるP型の第4のトランジスターとを含み、前記第4のトランジスターのドレインから前記第2のパルス信号を出力する。

#### 【0030】

本態様によれば、レベルシフト部を、たすきがけ接続したインバーター回路により構成したので、電源電圧によらず貫通電流が大きく変化しない。このため、パルス化部におけるデューティー良好性を生かしながら、低消費電流化とパルス整形の安定性と低位相雑音特性を満足することができるようになる。

#### 【0031】

(4) 本発明の第4の態様に係るパルス信号生成回路は、第1の態様乃至第3の態様のいずれかにおいて、ソースに前記パルス化部の電源端子が接続されるN型トランジスターを有するソースフォロワー回路を含む。

10

20

30

40

50

## 【0032】

本態様によれば、ソースフォロワー回路により第1の電源電圧を供給するようにしたので、上記の効果に加えて、複数の電源電圧を供給するための不要な回路を省略することができるようになる。

## 【0033】

(5) 本発明の第5の態様に係るパルス信号生成回路は、第4の態様において、前記N型トランジスターのドレインに前記第2の電源電圧が供給され、前記N型トランジスターのゲートに定電圧が供給される。

## 【0034】

本態様によれば、ソースフォロワー回路により、第2の電源電圧に基づいて第1の電源電圧を生成するようにしたので、上記の効果に加えて、複数の電源電圧を供給するための演算増幅器等の不要な回路を省略することができ、構成を簡素化することができる。 10

## 【0035】

(6) 本発明の第6の態様は、発振回路が、共振子を駆動して発振信号を出力する共振子駆動回路と、前記発振信号が入力される第1の態様乃至第5の態様のいずれか記載のパルス信号生成回路とを含む。

## 【0036】

本態様によれば、パルス化部におけるデューティー良好性を生かしながら、低消費電流化とパルス整形の安定性と低位相雑音特性を満足する発振回路を提供することができるようになる。 20

## 【0037】

(7) 本発明の第7の態様は、発振回路が、前記定電圧を生成するバンドギャップリファレンス回路と、共振子を駆動して発振信号を出力する共振子駆動回路と、前記発振信号が入力される第4の態様記載のパルス信号生成回路とを含み、前記共振子駆動回路は、前記バンドギャップリファレンス回路から出力されるP T A T (Proportional To Absolute Temperature) 電流を用いた電流駆動により前記共振子を駆動する。

## 【0038】

本態様によれば、パルス化部におけるデューティー良好性を生かしながら、低消費電流化とパルス整形の安定性と低位相雑音特性を満足する発振回路を提供することができるようになる。更に、本態様によれば、電流駆動を行う素子の温度特性を補償することができるようになる。 30

## 【0039】

(8) 本発明の第8の態様は、電子機器が、第6の態様又は第7の態様記載の発振回路を含む。

## 【0040】

本態様によれば、パルス化部におけるデューティー良好性を生かしながら、低消費電流化とパルス整形の安定性と低位相雑音特性を満足する発振回路が適用された電子機器を提供することができる。

## 【0041】

(9) 本発明の第9の態様は、パルス信号生成方法が、共振子を駆動して発振信号を生成する発振信号生成ステップと、一定の第1の電源電圧の下で、容量を介して入力される前記発振信号から第1の振幅レベルを有する第1のパルス信号を生成するパルス化ステップと、前記第1の電源電圧より高い第2の電源電圧の下で、前記第1のパルス信号を第2の振幅レベルを有する第2のパルス信号に変換するレベルシフトステップとを含む。 40

## 【0042】

本態様においては、交流信号から所望の振幅レベルを有するパルス信号を生成する場合に、パルス化の機能とレベルシフト機能とに分け、パルス化は、一定の電源電圧の下で行い、レベルシフトは、パルス化の際の電源電圧より低い電源電圧の下で行う。従って、本態様によれば、パルス化を定電圧の下で行うため、消費電流を一定にすることができます。そのため、ユーザーが要求する電源電圧が高い場合でも、より低い電源電圧の下で消費電 50

流が小さくなるようにパルス化を実現した後、レベルシフト機能により、ユーザーが要求する電源電圧まで振幅レベルを上げたパルス信号を生成することができる。従って、広い電圧範囲での動作が要求される場合、低消費電力化とパルス整形の安定性や低い位相雑音とを両立することができるようになる。

【0043】

(10) 本発明の第10の態様に係るパルス信号生成方法では、第9の態様において、前記発振信号生成ステップは、バンドギャップリファレンス回路から出力されるP T A T電流を用いた電流駆動により前記発振信号を生成し、前記パルス化ステップは、前記バンドギャップリファレンス回路により生成された定電圧がゲートに供給されるN型トランジスターのソース電圧を前記第1の電源電圧として、前記第1のパルス信号を生成する。 10

【0044】

本態様によれば、上記の効果に加えて、構成を簡素化し、電流駆動を行う素子の温度特性を補償することができるようになる。

【図面の簡単な説明】

【0045】

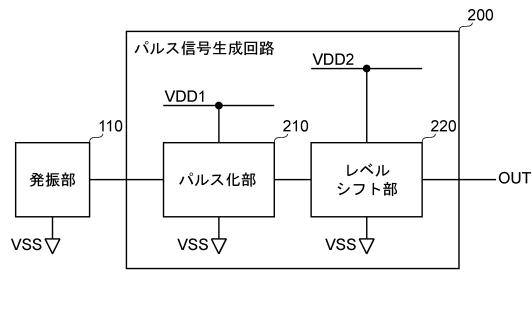

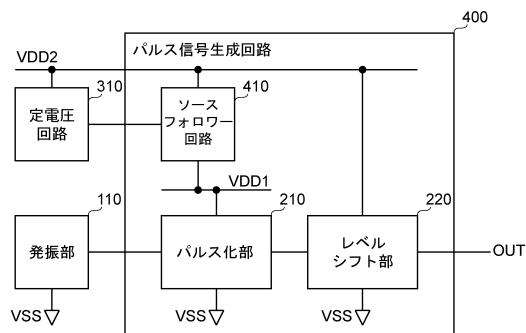

【図1】第1の実施形態における発振回路の構成例のブロック図。

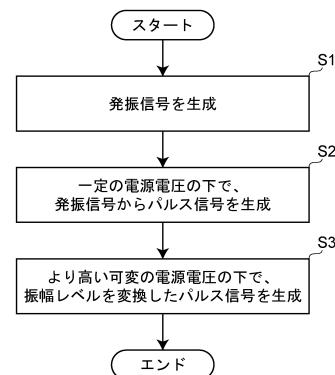

【図2】第1の実施形態におけるパルス信号生成方法のフローの一例を示す図。

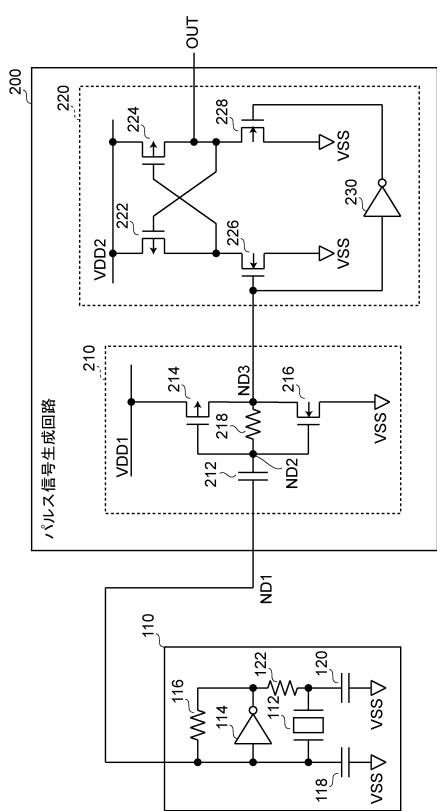

【図3】第1の実施形態における発振回路の具体的な構成例の回路図。

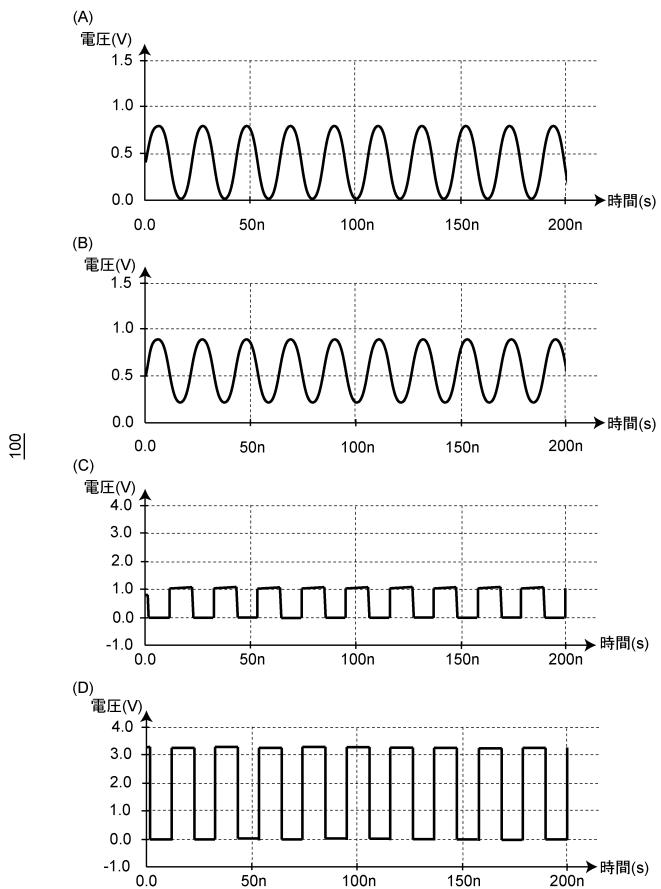

【図4】図4(A)、図4(B)、図4(C)、図4(D)は、発振回路のシミュレーション結果の一例を示す図。 20

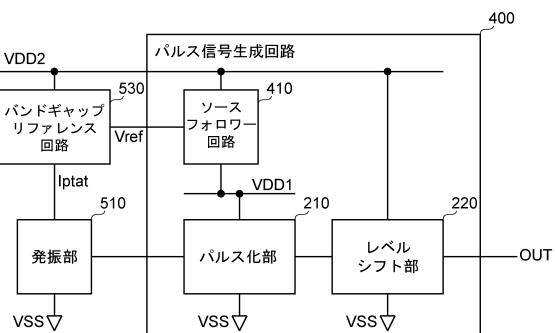

【図5】第2の実施形態における発振回路の構成例のブロック図。

【図6】第3の実施形態における発振回路の構成例のブロック図。

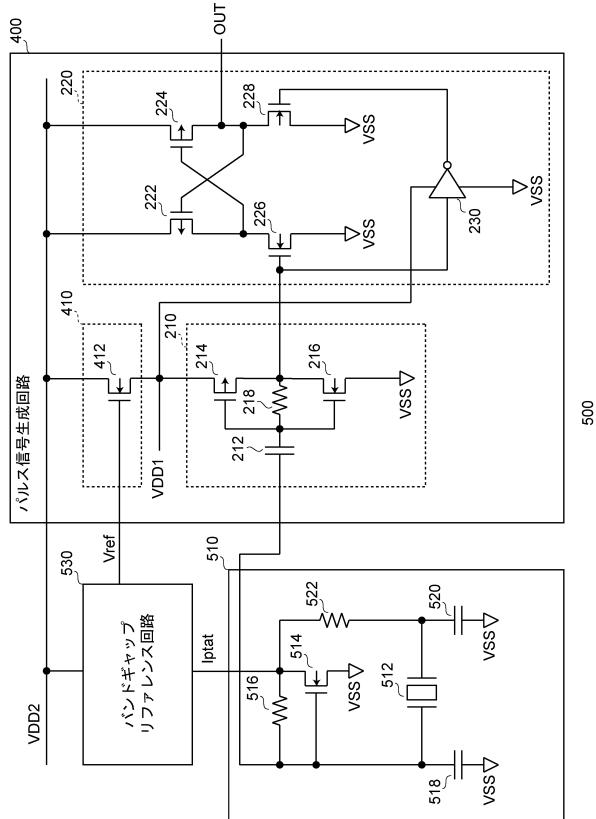

【図7】第3の実施形態における発振回路の具体的な構成例の回路図。

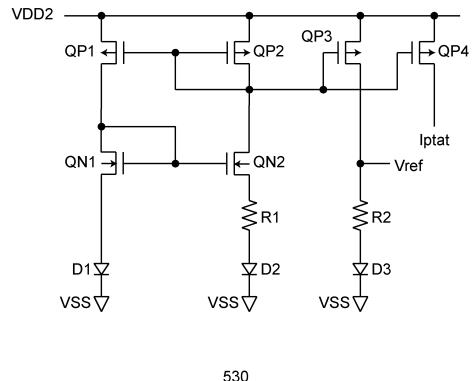

【図8】図7のバンドギャップリファレンス回路の構成例の回路図。

【図9】第3の実施形態の変形例におけるバンドギャップリファレンス回路の構成例の回路図。

【図10】本発明に係る実施形態又はその変形例における発振回路が適用された電子機器として携帯型情報端末の構成例のブロック図。

【図11】従来の発振回路の構成を示す図。

【図12】図11の増幅部に流れる電流の説明図。 30

【図13】図13(A)は、電源電圧が1.6Vのときの電流の変化を模式的に示す図。

図13(B)は、電源電圧が3.6Vのときの電流の変化を模式的に示す図。

【発明を実施するための形態】

【0046】

以下、本発明の実施の形態について図面を用いて詳細に説明する。なお、以下に説明する実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではない。また以下で説明される構成のすべてが本発明の課題を解決するために必須の構成要件であるとは限らない。

【0047】

【第1の実施形態】

図1に、本発明の第1の実施形態における発振回路の構成例のブロック図を示す。 40

【0048】

第1の実施形態における発振回路100は、発振部110と、パルス信号生成回路200とを備えている。パルス信号生成回路200は、パルス化部210と、レベルシフト部220とを備えている。発振部110は、共振子と、共振子駆動回路とを備え、共振子駆動回路が共振子を駆動することで発振信号をパルス信号生成回路200に出力する。

【0049】

パルス信号生成回路200において、パルス化部210には、定電圧である第1の電源電圧VDD1と接地電源からの接地電圧VSSとが供給される。また、レベルシフト部220には、第1の電源電圧VDD1より高い可変の第2の電源電圧VDD2と接地電源か 50

らの接地電圧 VSS とが供給される。以下では、接地電圧 VSS が 0 V であるものとし、各部は、高電位側の電源電圧を動作電圧として動作するものとする。

#### 【0050】

パルス化部 210 には、容量を介して発振部 110 からの発振信号が入力される。パルス化部 210 は、第 1 の電源電圧 VDD1 を動作電圧として動作し、発振信号の交流成分（交流信号）から、第 1 の電源電圧 VDD1 の電圧レベルに対応する第 1 の振幅レベルを有する第 1 のパルス信号を生成する。

#### 【0051】

レベルシフト部 220 は、第 1 のパルス信号を、第 2 の電源電圧 VDD2 の電圧レベルに対応する第 2 の振幅レベルを有する第 2 のパルス信号に変換する。発振回路 100 は、レベルシフト部 220 によって変換された第 2 のパルス信号を、出力端子 OUT から出力信号として出力する。

10

#### 【0052】

図 2 に、第 1 の実施形態におけるパルス信号生成方法のフローの一例を示す。

#### 【0053】

まず、第 1 の実施形態では、発振回路 100 は、発振部 110 において、共振子を駆動して発振信号を生成する（ステップ S1、発振信号生成ステップ）。

#### 【0054】

次に、発振回路 100 は、パルス化部 210 において、一定の電源電圧の下で、容量を介して入力される発振信号から第 1 の振幅レベルのパルス信号（第 1 のパルス信号）を生成する（ステップ S2、パルス化ステップ）。

20

#### 【0055】

そして、発振回路 100 は、レベルシフト部 220 において、ステップ S2 における電源電圧より高い電源電圧の下で、第 1 のパルス信号を、第 2 の振幅レベルを有する第 2 のパルス信号に変換する（ステップ S3、レベルシフトステップ）。その後、発振回路 100 は、一連の処理を終了する（エンド）。

#### 【0056】

以上のように、第 1 の実施形態では、図 11 の增幅部 40 のように 1 つのインバーター回路で、レベルシフト回路の機能と出力バッファー回路の機能とを兼用させるのではなく、パルス化の機能とレベルシフト機能とを分ける。このとき、パルス化は、一定の電源電圧の下で行い、レベルシフトは、パルス化の際の電源電圧より低い電源電圧の下で行う。また、レベルシフトは、ユーザーが要求する電源電圧の下で行う。

30

#### 【0057】

従って、第 1 の実施形態によれば、パルス化を定電圧の下で行うため、消費電流を一定にすることができる。そのため、ユーザーが要求する電源電圧が高い場合でも、より低い電源電圧の下で消費電流が小さくなるようにパルス化を実現した後、レベルシフト機能により、ユーザーが要求する電源電圧まで振幅レベルを上げたパルス信号を生成することができる。このとき、レベルシフト機能を実現する回路として、低消費電流で動作する回路を採用することによって、発振回路 100 のより一層の低消費電力化を図ることができる。

40

#### 【0058】

図 3 に、第 1 の実施形態における発振回路 100 の具体的な構成例の回路図を示す。図 3 において、図 1 と同様の部分には同一符号を付し、適宜説明を省略する。以下では、1.2 V の定電圧の電源電圧の下でパルス化部 210 を動作させ、1.6 V ~ 3.6 V の可変の電源電圧の下でレベルシフト部 220 を動作させるものとする。

#### 【0059】

発振部 110 は、共振子（振動子）としての水晶振動子 112 と、共振子駆動回路としてのインバーター回路 114 と、帰還抵抗 116 と、容量 118, 120 と、ドレイン抵抗 122 とを備えている。容量 118, 120 の一方の電極には、それぞれ接地電圧 VSS が供給される。容量 118 の他方の電極と容量 120 の他方の電極との間には、水晶振

50

動子 112 が接続される。インバーター回路 114 の入力には、容量 118 の他方の電極と帰還抵抗 116 の一端とが接続される。インバーター回路 114 の出力には、ドレイン抵抗 122 の一端及び帰還抵抗 116 の他端が接続される。ドレイン抵抗 122 の他端には、容量 120 の他方の電極が接続される。インバーター回路 114 の電源端子（図示せず）には、所与の電源電圧が供給され、接地電源端子（図示せず）には接地電圧 VSS が供給される。

#### 【0060】

パルス化部 210 は、容量 212 と、P 型の MOS トランジスター 214 と、N 型の MOS トランジスター 216 と、帰還抵抗 218 を備えた容量結合インバーター回路である。MOS トランジスター 214, 216 によりインバーター回路が構成される。容量 212 の一方の電極には、パルス化部 210 の入力ノード（例えば、インバーター回路 114 の入力）が接続される。容量 212 の他方の電極には、MOS トランジスター 214, 216 のゲート（インバーター回路 44 の入力）及び帰還抵抗 218 の一端が接続される。帰還抵抗 218 の他端には、MOS トランジスター 214, 216 のドレイン（インバーター回路 44 の出力）が接続される。MOS トランジスター 214 のソースには、第 1 の電源電圧 VDD1 が供給される。MOS トランジスター 216 のソースには、接地電圧 VSS が供給される。MOS トランジスター 214, 216 のドレイン（インバーター回路 44 の出力）から、第 1 の電源電圧 VDD1 に対応する第 1 の振幅レベルを有するパルス信号が出力される。

#### 【0061】

レベルシフト部 220 は、P 型の MOS トランジスター 222, 224 と、N 型の MOS トランジスター 226, 228 と、インバーター回路 230 を備えた、たすきがけ接続したインバーター回路である。MOS トランジスター 222, 224 のソースには、第 2 の電源電圧 VDD2 が供給される。MOS トランジスター 222 のゲートには、MOS トランジスター 224 のドレインと MOS トランジスター 228 のドレインとが接続される。MOS トランジスター 222 のドレインには、MOS トランジスター 224 のゲートと MOS トランジスター 226 のドレインとが接続される。MOS トランジスター 226 のソースには、接地電圧 VSS（第 3 の電源電圧）が供給され、ゲートには、MOS トランジスター 214, 216 のドレインとインバーター回路 230 の入力とが接続される。MOS トランジスター 228 のソースには、接地電圧 VSS が供給され、ゲートには、インバーター回路 230 の出力が接続される。MOS トランジスター 224, 228 のドレインからパルス信号生成回路 200 の出力が取り出される。

#### 【0062】

なお、できるだけ歪みのない波形を有する発振出力を得るために、パルス化部 210 のゲインは、レベルシフト部 220 のゲインより大きいことが望ましい。

#### 【0063】

なお、MOS トランジスター 226 は、第 1 のトランジスターとして機能し、MOS トランジスター 222 は、第 2 のトランジスターとして機能する。MOS トランジスター 228 は、第 3 のトランジスターとして機能し、MOS トランジスター 224 は、第 4 のトランジスターとして機能する。

#### 【0064】

以上のような構成を有する発振回路 100 は、発振部 110 において、インバーター回路 114 に所与の電源電圧が与えられると、インバーター回路 114 が増幅した発振信号により水晶振動子 112 が駆動される。このとき、増幅された発振信号を帰還抵抗 116 によりインバーター回路 114 の入力に帰還させながら、発振ノードに接続される容量 118, 120 の充電と放電を行って、所望の発振周波数で発振を継続するようになっている。発振部 110 における発振による発振信号は、インバーター回路 114 の入力側（ゲート側）から取り出される。

#### 【0065】

パルス化部 210 を構成する MOS トランジスター 214, 216 のゲートには、容量

10

20

30

40

50

212を介して発振部110からの発振信号が入力される。そのため、発振信号の交流成分のみが、MOSトランジスター214, 216により構成されるインバーター回路に伝達される。このとき、MOSトランジスター214, 216により構成されるインバーター回路では、VDD1/2にバイアスされた直流レベルに交流信号が重畠するため、帰還抵抗218によってバイアス電圧が動作点のほぼ中間で安定する。そのため、パルス化部210のデューティー比が50パーセントになりやすい。

#### 【0066】

なお、容量結合インバーター回路は、1.6V～3.6Vのような広い電源電圧範囲で動作させると、消費電流と、パルス整形の安定性及び位相雑音特性との間でトレードオフがある。そこで、第1の実施形態では、容量結合インバーター回路では低い定電圧の下で動作させ、レベルシフト部220により振幅レベルを高くする。こうすることで、容量結合インバーター回路において消費電流を優先にしたときに劣化するパルス整形の安定性及び位相雑音特性の悪化を抑える。

#### 【0067】

レベルシフト部220では、MOSトランジスター226がオンになると、MOSトランジスター224がオンとなり、出力端子OUTは第2の電源電圧VDD2の電圧レベルとなる。このとき、MOSトランジスター222, 228がオフとなるため、レベルシフト部220では、貫通電流がほとんど流れない。

#### 【0068】

また、MOSトランジスター228がオンになると、出力端子OUTは接地電圧VSSの電圧レベルとなる。このとき、MOSトランジスター222がオンとなるが、MOSトランジスター224, 226がオフとなるため、レベルシフト部220では、貫通電流がほとんど流れない。

#### 【0069】

なお、たすきがけ接続したインバーター回路は、その閾値電圧と、入力信号の中心電圧とが一致しないとき、ディーティー比が50パーセントの出力信号を出力することができない。この点、第1の実施形態では、パルス化部210によって一定の中心電圧を基準としたパルス信号が入力されるため、たすきがけ接続したインバーター回路の閾値電圧をこれに揃えることができる。

#### 【0070】

図4(A)、図4(B)、図4(C)、図4(D)に、発振回路100のシミュレーション結果の一例を示す。図4(A)～図4(D)は、パルス化部210に1.2Vの電源電圧(第1の電源電圧VDD1)を供給し、レベルシフト部220に3.3Vの電源電圧(第2の電源電圧VDD2)を供給した場合のシミュレーション結果を表す。図4(A)はパルス化部210の入力ノードND1のシミュレーション波形、図4(B)はMOSトランジスター214, 216のゲートノードND2のシミュレーション波形を表す。図4(C)はMOSトランジスター214, 216のドレインノードND3のシミュレーション波形、図4(D)は出力端子OUTから出力される出力信号のシミュレーション波形を表す。図4(A)～図4(D)において、横軸は時間軸とし、縦軸は電圧を表している。

#### 【0071】

図4(A)に示すような約0.8Vの振幅レベルを有する発振信号が入力ノードND1に入力されると、容量212を介してこの発振信号が入力されるゲートノードND2は、図4(B)に示すように、図4(A)の交流成分のみが伝搬される。このとき、帰還抵抗218によって自己バイアスされるため、ゲートノードND2は、0.6V(=VDD1/2)を中心レベルとした交流信号となる。この結果、ドレインノードND3には、図4(C)に示すように、1.2Vの振幅レベルのパルス信号が出力される。

#### 【0072】

レベルシフト部220は、上記のように振幅レベルの変換を行い、図4(D)に示すように、3.3V(=VDD2)の振幅レベルを有するパルス信号を、出力端子OUTから出力信号として出力する。

10

20

30

40

50

## 【0073】

以上説明したように、第1の実施形態において、パルス化部210を容量結合インバータ回路により構成したので、VDD1/2にバイアスされた直流レベルに交流信号が重畳するため、ディーティー比が50パーセントのパルス信号を生成しやすくなる。また、第1の実施形態では、発振部110から取り出される発振信号の振幅をそれほど高くする必要がないため、インバータ回路114の入力側から発振信号を取り出してパルス信号を生成することができる。これにより、ノイズ成分のより一層少ない発振信号からパルス信号を生成することができ、ディーティー比が50パーセントのパルス信号をより一層得やすくなる。

## 【0074】

更に、レベルシフト部220を、たすきがけ接続したインバータ回路により構成したので、電源電圧によらず貫通電流が大きく変化しない。このため、パルス化部210におけるデューティー良好性を生かしながら、低消費電流化とパルス整形の安定性と低位相雑音特性のすべてを満足する発振回路を提供することができるようになる。

## 【0075】

## 〔第2の実施形態〕

第1の実施形態では、第1の電源電圧VDD1及び第2の電源電圧VDD2を図示しない電圧発生回路から供給することができるが、第1の電源電圧VDD1を、第2の電源電圧VDD2に基づいて生成するようにしてもよい。

## 【0076】

図5に、本発明の第2の実施形態における発振回路の構成例のブロック図を示す。図5において、図1と同様の部分には同一符号を付し、適宜説明を省略する。

## 【0077】

第2の実施形態における発振回路300は、発振部110と、パルス信号生成回路400と、定電圧回路310とを備えている。パルス信号生成回路400は、パルス化部210と、レベルシフト部220と、ソースフォロワー回路410とを備えている。

## 【0078】

定電圧回路310は、第2の電源電圧VDD2から一定電圧である基準電圧を生成する。定電圧回路310によって生成された基準電圧は、ソースフォロワー回路410に出力される。

## 【0079】

ソースフォロワー回路410は、N型MOSトランジスター（N型トランジスター）を備えている。このN型MOSトランジスターのドレインには、第2の電源電圧VDD2が供給され、ゲートには定電圧回路310からの基準電圧が供給され、ソースには第1の電源電圧VDD1が出力される。このN型MOSトランジスターの閾値電圧をV<sub>thn</sub>とすると、次式が成り立つ。

## 【数1】

$$VDD1 = VDD2 - V_{thn} \quad \dots \quad (1)$$

## 【0080】

N型MOSトランジスターのソースには、パルス化部210の電源端子が接続され、パルス化部210には、定電圧である第1の電源電圧VDD1が供給される。

## 【0081】

パルス化部210には、第1の電源電圧VDD1と接地電源からの接地電圧VSSとが供給され、レベルシフト部220には、第1の電源電圧VDD1より高い可変の第2の電源電圧VDD2と接地電源からの接地電圧VSSとが供給される。

## 【0082】

以上のような構成を有する第2の実施形態においても、図2で説明したように、第1の実施形態と同様に、パルス信号を生成して、ユーザーが要求する電源電圧レベルの発振出力を得ることができる。

## 【0083】

10

20

30

40

50

即ち、第2の実施形態においても、第1の実施形態と同様に、図11の増幅部40のように1つのインバーター回路で、レベルシフト回路の機能と出力バッファー回路の機能とを兼用させるのではなく、パルス化の機能とレベルシフト機能とを分けることができる。このとき、パルス化は、一定の電源電圧の下で行い、レベルシフトは、パルス化の際の電源電圧より低い電源電圧の下で行う。また、レベルシフトは、ユーザーが要求する電源電圧の下で行う。

#### 【0084】

しかも、第2の実施形態では、第1の電源電圧VDD1を第2の電源電圧VDD2に基づいて生成するようにしたので、複数の電源電圧を供給するための不要な回路を省略し、簡素な構成で、第1の実施形態と同様の効果を得ることができる。

10

#### 【0085】

##### 〔第3の実施形態〕

第1の実施形態又は第2の実施形態では、発振部において電圧駆動によって発振信号を生成する発振回路を例に説明したが、本発明に係る実施形態は、これに限定されるものではない。

#### 【0086】

図6に、本発明の第3の実施形態における発振回路の構成例のブロック図を示す。図6において、図1又は図5と同様の部分には同一符号を付し、適宜説明を省略する。

#### 【0087】

第3の実施形態における発振回路500は、発振部510と、パルス信号生成回路400と、バンドギャップリファレンス回路530とを備えている。パルス信号生成回路400は、パルス化部210と、レベルシフト部220と、ソースフォロワー回路410とを備えている。

20

#### 【0088】

発振部510は、共振子と、共振子駆動回路とを備え、電流駆動により共振子駆動回路が共振子を駆動することで発振信号をパルス信号生成回路400に出力する。このような発振部510の機能は、ピアース型の発振回路の発振部によって実現される。

#### 【0089】

バンドギャップリファレンス回路530には、第2の電源電圧VDD2が供給される。バンドギャップリファレンス回路530は、1.25Vの定電圧Vrefを生成してソースフォロワー回路410に供給するとともに、PTAT(Proportional To Absolute Temperature)電流を発振部510に出力する。発振部510は、バンドギャップリファレンス回路530からのPTAT電流Iptatを用いて発振信号を生成する。

30

#### 【0090】

ソースフォロワー回路410が備えるN型のMOSトランジスターのドレインには、第2の電源電圧VDD2が供給され、ゲートにはバンドギャップリファレンス回路530からの定電圧Vrefが供給され、ソースには第1の電源電圧VDD1が出力される。このとき、第1の電源電圧VDD1は、式(1)のようになる。

#### 【0091】

以上のような構成を有する第3の実施形態でも、図2で説明したように、第1の実施形態と同様に、パルス信号を生成して、ユーザーが要求する電源電圧レベルの発振出力を得ることができる。

40

#### 【0092】

即ち、第3の実施形態においても、第1の実施形態と同様に、図11の増幅部40のように1つのインバーター回路で、レベルシフト回路の機能と出力バッファー回路の機能とを兼用させるのではなく、パルス化の機能とレベルシフト機能とを分けることができる。このとき、パルス化は、一定の電源電圧の下で行い、レベルシフトは、パルス化の際の電源電圧より低い電源電圧の下で行う。また、レベルシフトは、ユーザーが要求する電源電圧の下で行う。

#### 【0093】

50

しかも、第3の実施形態では、バンドギャップリファレンス回路530により発振部510にP T A T電流I<sub>ptat</sub>を供給し、ソースフォロワー回路410を介してパルス化部210に第1の電源電圧V<sub>DD1</sub>を供給する。そのため、複数の電源電圧を供給するための演算増幅器等の不要な回路を省略することができ、簡素な構成で、第1の実施形態と同様の効果を得ることができる。

【0094】

図7に、第3の実施形態における発振回路500の具体的な構成例の回路図を示す。図7において、図3又は図6と同様の部分には同一符号を付し、適宜説明を省略する。

【0095】

発振部510は、共振子としての水晶振動子512と、共振子駆動回路としてのN型のMOSトランジスター514と、帰還抵抗516と、容量518, 520と、ドレイン抵抗522とを備えている。容量518, 520の一方の電極には、それぞれ接地電圧V<sub>SS</sub>が供給される。容量518の他方の電極と容量520の他方の電極との間には、水晶振動子512が接続される。

【0096】

MOSトランジスター514のソースには、接地電圧V<sub>SS</sub>が供給され、ゲートには、容量518の他方の電極が接続され、ドレインにはドレイン抵抗522の一端が接続される。ドレイン抵抗522の他端には、容量520の他方の電極が接続される。MOSトランジスター514のゲートとドレインとの間には、帰還抵抗516が接続される。また、MOSトランジスター514のドレインには、バンドギャップリファレンス回路530が接続され、バンドギャップリファレンス回路530からのP T A T電流I<sub>ptat</sub>が供給される。

【0097】

パルス化部210における容量212は、MOSトランジスター514のゲートと、MOSトランジスター214, 216のゲートとの間に接続される。

【0098】

ソースフォロワー回路410は、N型のMOSトランジスター（N型トランジスター）412を備えている。MOSトランジスター412のドレインには、第2の電源電圧V<sub>DD2</sub>が供給され、ゲートにはバンドギャップリファレンス回路530からの定電圧V<sub>ref</sub>が供給され、ソースには第1の電源電圧V<sub>DD1</sub>が出力される。

【0099】

図8に、図7のバンドギャップリファレンス回路530の構成例の回路図を示す。

【0100】

バンドギャップリファレンス回路530は、P N接合を有するダイオードD1, D2, D3と、P型のMOSトランジスターQ P1, Q P2, Q P3, Q P4と、N型のMOSトランジスターQ N1, Q N2と、抵抗R1, R2とを備えている。MOSトランジスターQ P1, Q P2のゲート同士が接続され、ソースには、第2の電源電圧V<sub>DD2</sub>が供給される。MOSトランジスターQ P2のゲート及びドレインが接続される。MOSトランジスターQ N1, Q N2のゲート同士が接続され、MOSトランジスターQ N1のゲート及びドレインが接続される。MOSトランジスターQ N1のドレインには、MOSトランジスターQ P1のドレインが接続され、ソースには、ダイオードD1のアノードが接続される。ダイオードD1のカソードには、接地電圧V<sub>SS</sub>を供給する接地電源が接続される。MOSトランジスターQ N2のドレインには、MOSトランジスターQ P2のドレインが接続され、ソースには、抵抗R1の一端が接続される。抵抗R1の他端には、ダイオードD2のアノードが接続される。ダイオードD2のカソードには、接地電圧V<sub>SS</sub>を供給する接地電源が接続される。

【0101】

MOSトランジスターQ P3のソースには、第2の電源電圧V<sub>DD2</sub>が供給され、ゲートには、MOSトランジスターQ P1, Q P2のゲートが接続される。MOSトランジスターQ P3のドレインには、抵抗R2の一端が接続される。抵抗R2の他端には、ダイオ

10

20

30

40

50

ードD3のアノードが接続される。ダイオードD3のカソードには、接地電圧VSSを供給する接地電源が接続される。MOSトランジスターQ P3のドレインの電圧が定電圧Vrefとして出力される。

【0102】

MOSトランジスターQ P4のソースには、第2の電源電圧VDD2が供給され、ゲートには、MOSトランジスターQ P1, Q P2のゲートが接続される。MOSトランジスターQ P4のドレインの電流が、PTAT電流Ipatとして出力される。

【0103】

図8の構成において、MOSトランジスターQ P1, Q P2, Q P3, Q P4, Q N1, Q N2の各々は、チャネル長及びチャネル幅が同サイズのトランジスター素子として形成される。そのため、MOSトランジスターQ P1～Q P4はカレントミラー回路を構成し、MOSトランジスターQ N1, Q N2もカレントミラー回路を構成するため、各MOSトランジスターに流れる電流は、ほぼ等しくなる。また、MOSトランジスターQ N1, Q N2のソースの電圧も、ほぼ等しくなる。

【0104】

一方、ダイオードD2におけるPN接合の並列接続数（又は面積）は、ダイオードD1におけるPN接合の並列接続数（又は面積）のM倍となるように形成される。そのため、ダイオードD1の飽和電流をIsとすると、ダイオードD2の飽和電流はM×Isとなる。

【0105】

ここで、MOSトランジスターQ P1～Q P4の各々に流れる電流をI、ダイオードD1～D3の各々の両端電圧をVd1～Vd3、抵抗R1, R2の各々の抵抗値をR1, R2とすると、以下の式が成立する。なお、以下の式において、kはボルツマン定数、Tは絶対温度であり、qは電子の電荷とする。

【数2】

$$Vd1 = \frac{kT}{q} \ln\left(\frac{I}{Is}\right) \quad \dots \quad (2)$$

$$Vd2 = \frac{kT}{q} \ln\left(\frac{I}{M \cdot Is}\right) \quad \dots \quad (3)$$

$$Vd1 = I \cdot R1 + Vd2 \quad \dots \quad (4)$$

【0106】

式(2)～式(4)より、MOSトランジスターQ P3のドレインの電圧である定電圧Vrefは、次式によって表される。

【数3】

$$Vref = I \cdot R2 + Vd3 = \frac{R2}{R1} \cdot \frac{kT}{q} \ln(M) + Vd3 \quad \dots \quad (5)$$

【0107】

ここで、式(5)を絶対温度Tで微分すると、次式のようになる。

【数4】

$$\frac{dVref}{dT} = \frac{R2}{R1} \cdot \frac{k}{q} \ln(M) + \frac{dVd3}{dT} \quad \dots \quad (6)$$

【0108】

式(6)において、dVd3/dTの項は負の温度特性を有し、これに対応して、(R2/R1)(k/q)ln(M)の値を正の値に調整することにより、式(6)はゼロとすることができる、定電圧Vrefの温度依存性をキャンセルすることができる。

10

20

30

40

50

## 【0109】

また、MOSトランジスターQ P 4のドレインの電流  $I_{p t a t}$  は、次式のように表すことができる。

## 【数5】

$$I_{p t a t} = \frac{kT}{qR_1} \ln(M) \quad \dots \quad (7)$$

## 【0110】

以上のような構成を有する発振回路500は、発振部510において、バンドギャップリファレンス回路530からPTAT電流  $I_{p t a t}$  が供給されると、MOSトランジスター514が増幅した発振信号により水晶振動子512が駆動される。このとき、増幅された発振信号を帰還抵抗516によりMOSトランジスター514のゲートに帰還させながら、発振ノードに接続される容量518, 520の充電と放電を行って、所望の発振周波数で発振を継続するようになっている。

10

## 【0111】

一方、バンドギャップリファレンス回路530が生成する定電圧  $V_{r e f}$  は、MOSトランジスター412のゲートに供給され、一定電圧である第1の電源電圧  $V_{D D 1}$  が第2の電源電圧  $V_{D D 2}$  から生成される。

## 【0112】

パルス化部210を構成するMOSトランジスター214, 216のゲートには、容量212を介して発振部510からの発振信号が入力される。そのため、発振信号の交流成分のみが、MOSトランジスター214, 216により構成されるインバーター回路に伝達される。このとき、MOSトランジスター214, 216により構成されるインバーター回路では、上記のように帰還抵抗218によってバイアス電圧が動作点のほぼ中間で安定し、パルス化部210のデューティー比が50パーセントになりやすい。

20

## 【0113】

レベルシフト部220は、上記のように、パルス化部210からのパルス信号の振幅レベルを、第2の電源電圧  $V_{D D 2}$  の振幅レベルに変換する。

## 【0114】

なお、第3の実施形態では、図2のステップS2では、バンドギャップリファレンス回路530から出力されるPTAT電流  $I_{p t a t}$  を用いた電流駆動により発振信号を生成する。また、図2のステップS3では、バンドギャップリファレンス回路530により生成された定電圧  $V_{r e f}$  がゲートに供給されるMOSトランジスター412のソース電圧を第1の電源電圧  $V_{D D 1}$  として、第1のパルス信号を生成する。

30

## 【0115】

以上説明したように、第3の実施形態において、パルス化部210を容量結合インバーター回路により構成したので、 $V_{D D 1/2}$  にバイアスされた直流レベルに交流信号が重畳するため、ディーティー比が50パーセントのパルス信号を生成しやすくなる。また、第3の実施形態では、発振部510から取り出される発振信号の振幅をそれほど高くする必要がないため、MOSトランジスター514のゲート側から発振信号を取り出してパルス信号を生成することができる。これにより、ノイズ成分のより一層少ない発振信号からパルス信号を生成することができ、ディーティー比が50パーセントのパルス信号をより一層得やすくなる。

40

## 【0116】

更に、レベルシフト部220を、たすきがけ接続したインバーター回路により構成したので、電源電圧によらず貫通電流が大きく変化しない。このため、パルス化部210におけるデューティー良好性を生かしながら、低消費電流化とパルス整形の安定性と低位相雑音特性のすべてを満足する発振回路を提供することができるようになる。

## 【0117】

更に、第3の実施形態では、バンドギャップリファレンス回路530により発振部51

50

0 に P T A T 電流  $I_{p t a t}$  を供給し、ソースフォロワー回路 410 を介してパルス化部 210 に第 1 の電源電圧  $V_{D D 1}$  を供給する。そのため、複数の電源電圧を供給するための演算増幅器等の不要な回路を省略することができ、簡素な構成で、第 1 の実施形態と同様の効果を得ることができる。

【0118】

また、P T A T 電流  $I_{p t a t}$  により M O S トランジスター 514 を駆動するようにしたので、低温で抵抗が大きくなる分だけ電流値が小さくなり、高温で抵抗が大きくなる分だけ電流値が大きくなる。このため、M O S トランジスター 514 の温度特性を補償することができるようになる。

【0119】

〔変形例〕

第 3 の実施形態では、バンドギャップリファレンス回路 530 として図 8 に示す構成を例に説明したが、本発明に係る実施形態は、これに限定されるものではない。

【0120】

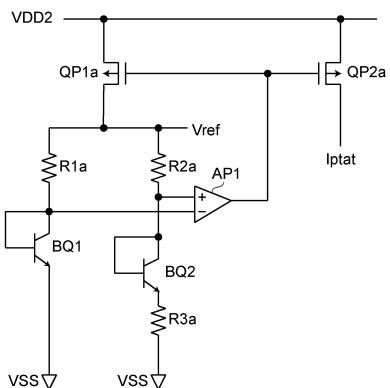

図 9 に、第 3 の実施形態の変形例におけるバンドギャップリファレンス回路の構成例の回路図を示す。

【0121】

本変形例におけるバンドギャップリファレンス回路 530a は、N P N 型のバイポーラトランジスター B Q 1, B Q 2 と、P 型のM O S トランジスター Q P 1a, Q P 2a と、抵抗 R 1a, R 2a, R 3a と、差動増幅器 A P 1 とを備えている。M O S トランジスター Q P 1a, Q P 2a のゲート同士が接続され、ソースには、第 2 の電源電圧  $V_{D D 2}$  が供給される。

【0122】

M O S トランジスター Q P 1a のドレインには、抵抗 R 1a, R 2a の一端が接続される。M O S トランジスター Q P 1a のドレインの電圧が、定電圧  $V_{r e f}$  として出力される。M O S トランジスター Q P 2a のドレインの電流が、P T A T 電流  $I_{p t a t}$  として出力される。抵抗 R 1a の他端には、バイポーラトランジスター B Q 1 のコレクター及びベースが接続される。バイポーラトランジスター B Q 1 のエミッターには、接地電圧  $V_{S S}$  が供給される。抵抗 R 2a の他端には、バイポーラトランジスター B Q 2 のコレクター及びベースが接続される。バイポーラトランジスター B Q 2 のエミッターには、抵抗 R 3a の一端が接続される。抵抗 R 3a の他端には、接地電圧  $V_{S S}$  が供給される。

【0123】

差動増幅器 A P 1 の非反転入力端子には、バイポーラトランジスター B Q 2 のコレクターが接続される。差動増幅器 A P 1 の反転入力端子には、バイポーラトランジスター B Q 1 のコレクターが接続される。差動増幅器 A P 1 の出力端子には、M O S トランジスター Q P 1a, Q P 2a のゲートが接続される。

【0124】

このような構成を有するバンドギャップリファレンス回路 530a は、バンドギャップリファレンス回路 530 に代えて図 7 の構成に設けられる。

【0125】

図 9 の構成において、M O S トランジスター Q P 1a, Q P 2a の各々は、チャネル長及びチャネル幅が同サイズのトランジスター素子として形成される。そのため、M O S トランジスター Q P 1a, Q P 2a はカレントミラー回路を構成するため、各 M O S トランジスターに流れる電流は、ほぼ等しくなる。バイポーラトランジスター B Q 2 における P N 接合の並列接続数（又は面積）は、バイポーラトランジスター B Q 1 における P N 接合の並列接続数（又は面積）の M 倍となるように形成される。また、抵抗 R 1a, R 2a は、同じ抵抗値となるように形成される。

【0126】

差動増幅器 A P 1 は、バイポーラトランジスター B Q 1 のコレクターの電圧と、バイポーラトランジスター B Q 2 のコレクターの電圧とが等しくなるように、M O S トランジス

10

20

30

40

50

ター Q P 1 , Q P 2 のゲートを制御する。その結果、M や R 2 a / R 3 a を調整することによって、定電圧  $V_{ref}$  の温度依存性をキャンセルすることができる。例えば、抵抗 R 1 a , R 2 a の抵抗値を図 8 の抵抗 R 1 と同じ抵抗値  $R_1$  、抵抗 R 3 a の抵抗値を図 8 の抵抗 R 2 と同じ抵抗値  $R_2$  とすると、定電圧  $V_{ref}$  は式 (5) 、 P T A T 電流  $I_{ptat}$  は式 (7) のように表すことができる。

#### 【 0 1 2 7 】

##### 〔 電子機器 〕

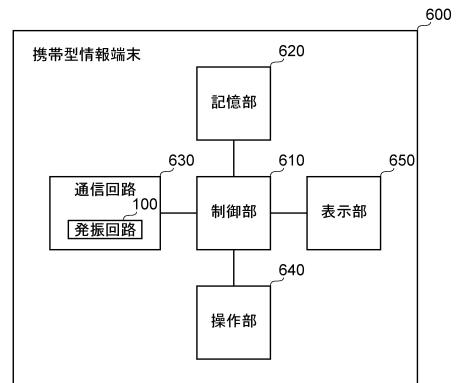

図 10 に、上記のいずれかの実施形態又はその変形例における発振回路が適用された電子機器として携帯型情報端末の構成例のブロック図を示す。なお、図 10 において、図 1 と同様の部分には同一符号を付し、適宜説明を省略する。また、図 10 では、第 1 の実施形態における発振回路 100 が携帯型情報端末に適用される例を示したが、第 2 の実施形態、第 3 の実施形態、又はその変形例における発振回路を適用してもよい。

10

#### 【 0 1 2 8 】

携帯型情報端末 600 は、制御部 610 と、記憶部 620 と、通信回路 630 と、操作部 640 と、表示部 650 とを備えている。制御部 610 は、中央演算処理装置を備え、記憶部 620 に記憶されたプログラムを読み込んで、携帯型情報端末 600 を構成する各部の制御を行う。記憶部 620 は、制御部 610 によって実行されるプログラムやデータなどを記憶し、制御部 610 により各種ワークエリアとして機能する。

#### 【 0 1 2 9 】

通信回路 630 は、外部機器からの受信信号を受信して復調処理を行ったり、変調処理後のデータを送信信号として外部機器に送信したりする。通信回路 630 は、発振回路 100 を備えている。通信回路 630 は、発振回路 100 により生成された発振信号に基づいて、例えば送信及び受信用の基準クロックを生成し、上記の送信又は受信を行う。

20

#### 【 0 1 3 0 】

操作部 640 は、ユーザーからの操作情報を受け付け、該操作情報を制御部 610 に供給する。例えば制御部 610 は、操作部 640 からの操作情報に基づいて、通信回路 630 及び記憶部 620 とデータをやりとりし、必要なデータ処理を行う。表示部 650 は、制御部 610 により行われた所定の処理後のデータに対応した画像を表示する。

#### 【 0 1 3 1 】

以上、本発明に係るパルス信号生成回路、発振回路、電子機器、及びパルス信号生成方法等を上記のいずれかの実施形態又はその変形例に基づいて説明したが、本発明は上記のいずれかの実施形態又はその変形例に限定されるものではない。例えば、その要旨を逸脱しない範囲において種々の態様において実施することが可能であり、次のような変形も可能である。

30

#### 【 0 1 3 2 】

(1) 上記のいずれかの実施形態又はその変形例において、発振回路として S P X O を例に説明したが、本発明は、これに限定されるものではない。

#### 【 0 1 3 3 】

(2) 上記のいずれかの実施形態又はその変形例において、発振回路の外部に、水晶振動子等の共振子が設けられていてもよい。

40

#### 【 0 1 3 4 】

(3) 上記のいずれかの実施形態又はその変形例において、パルス化部の後段にレベルシフト部を設けているが、本発明は、これに限定されるものではない。パルス化部とレベルシフト部との間に、インバーター回路やバッファ回路を設けて、パルス化部からのパルス信号の振幅レベルを上げてから、更にレベルシフト部にパルス信号を入力するようにしてもよい。

#### 【 0 1 3 5 】

(4) 上記のいずれかの実施形態又はその変形例において、バンドギャップリファレンス回路として、図 8 又は図 9 の構成を例に説明したが、本発明は、これに限定されるものではない。

50

## 【0136】

(5) 本発明に係る発振回路が適用される電子機器として、携帯型情報端末を例に説明したが、本発明はこれに限定されるものではない。例えば、デジタルスチルカメラ、テレビ、ビデオカメラ、カーナビゲーション装置、ページャー、電子手帳、電子ペーパー、電卓、ワードプロセッサー、ワークステーション、テレビ電話、POS (Point of sale system) 端末、プリンター、スキャナー、複写機、ビデオプレーヤー、タッチパネルを備えた機器などが挙げられる。

## 【符号の説明】

## 【0137】

100, 300, 500...発振回路、110, 510...発振部、

112, 512...水晶振動子（共振子）、114, 230...インバーター回路、

116, 218, 516...帰還抵抗、

118, 120, 212, 518, 520...容量、122, 522...ドレイン抵抗、

200, 400...パルス信号生成回路、210...パルス化部、

214, 222, 224...P型のMOSトランジスター、

216, 226, 228, 412...N型のMOSトランジスター、

220...レベルシフト部、310...定電圧回路、410...ソースフォロワー回路、

530...バンドギャップリファレンス回路、600...携帯型情報端末（電子機器）、

610...制御部、620...記憶部、630...通信回路、640...操作部、

650...表示部、Iptat...PTAT電流、OUT...出力端子、

VDD1...第1の電源電圧、VDD2...第2の電源電圧、Vref...定電圧、

VSS...接地電圧（第3の電源電圧）

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

300

400

500

【図7】

【図8】

【図10】

530a

【図1-1】

【図1-2】

10

【図1-3】

---

フロントページの続き

合議体

審判長 大塚 良平

審判官 吉田 隆之

審判官 中野 浩昌

(56)参考文献 特開2005-45695 (JP, A)

特開2008-160510 (JP, A)

特開2006-211514 (JP, A)

特開2006-270902 (JP, A)

特開平6-83468 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H03K