(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4230219号

(P4230219)

(45) 発行日 平成21年2月25日(2009.2.25)

(24) 登録日 平成20年12月12日(2008.12.12)

(51) Int.Cl.

H01L 33/00 (2006.01)

F 1

H01L 33/00

B

請求項の数 27 (全 21 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2002-518539 (P2002-518539)  |

| (86) (22) 出願日 | 平成13年8月8日(2001.8.8)           |

| (65) 公表番号     | 特表2004-506331 (P2004-506331A) |

| (43) 公表日      | 平成16年2月26日(2004.2.26)         |

| (86) 國際出願番号   | PCT/DE2001/003033             |

| (87) 國際公開番号   | W02002/013281                 |

| (87) 國際公開日    | 平成14年2月14日(2002.2.14)         |

| 審査請求日         | 平成15年2月25日(2003.2.25)         |

| 審判番号          | 不服2007-3761 (P2007-3761/J1)   |

| 審判請求日         | 平成19年2月8日(2007.2.8)           |

| (31) 優先権主張番号  | 100 38 671.7                  |

| (32) 優先日      | 平成12年8月8日(2000.8.8)           |

| (33) 優先権主張国   | ドイツ(DE)                       |

| (31) 優先権主張番号  | 100 59 532.4                  |

| (32) 優先日      | 平成12年11月30日(2000.11.30)       |

| (33) 優先権主張国   | ドイツ(DE)                       |

|           |                                                                                                                                                                                                           |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 599133716<br>オスラム オプト セミコンダクターズ<br>ゲゼルシャフト ミット ベシュレンクテ<br>ル ハフツング<br>Osram Opto Semiconductors GmbH<br>ドイツ連邦共和国、93055 レーゲン<br>スブルグ、ライプニッツシュトラーゼ 4<br>Leibnizstrasse 4, D<br>-93055 Regensburg,<br>Germany |

| (74) 代理人  | 100061815<br>弁理士 矢野 敏雄                                                                                                                                                                                    |

| (74) 代理人  | 100094798<br>弁理士 山崎 利臣                                                                                                                                                                                    |

最終頁に続く

(54) 【発明の名称】発光半導体チップおよびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

p n 接合領域の含まれる、光子を形成する活性ゾーンを備えた薄膜活性層は、成長基板としては用いられない支持体基板に接合されて配置されており、チップのうち放射の出射方向とは反対側に少なくとも 1 つのキャビティを有し、該キャビティにより複数のメサが形成され、

前記薄膜活性層は前記複数のメサおよび該メサに接するカバー層を有しており、前記キャビティは、薄膜活性層の p n 接合領域が分断されずにカバー層の内部に位置する深さに設けられており、メサ(4)は反射層(9、10)によってカバーされており、さらに支持体基板へ向かって先細になっている

ことを特徴とする発光半導体チップ。

## 【請求項 2】

キャビティ(8)の横断面は支持体基板(1)から離れるにつれて小さくなる、請求項 1 記載の半導体チップ。

## 【請求項 3】

薄膜活性層は In<sub>1-x-y</sub> Al<sub>x</sub> Ga<sub>y</sub> P (ここで 0 < x < 1, 0 < y < 1, x + y = 1 である) ベースの層列を有している、請求項 1 または 2 記載の半導体チップ。

## 【請求項 4】

薄膜活性層(2)の放射形成領域にのみ、複数のキャビティ(8)によりメサ(4)が構成されている、請求項 1 から 3 までのいずれか 1 項記載の半導体チップ。

10

20

**【請求項 5】**

活性ゾーン（3）から放出される光子の少なくとも1つのトラジェクトリ（18）が各メサ（4）から隣接する1つのメサ（4）へ通じている、請求項1から4までのいずれか1項記載の半導体チップ。

**【請求項 6】**

メサ（4）は凹形の側面（13）を有する、請求項1記載の半導体チップ。

**【請求項 7】**

メサ（4）は角錐台状に構成されている、請求項4から6までのいずれか1項記載の半導体チップ。

**【請求項 8】**

カバー層（5）は活性ゾーン（3）から放出される光子に対して一貫して透過性を有する、請求項1から7までのいずれか1項記載の半導体チップ。

**【請求項 9】**

カバー層（5）は高濃度にドープされている、請求項1から8までのいずれか1項記載の半導体チップ。

**【請求項 10】**

反射層は絶縁層（9）の下方に配置されるメタライゼーション層（10）を有する、請求項9記載の半導体チップ。

**【請求項 11】**

薄膜活性層（2）は5μm～50μmの厚さである、請求項1から10までのいずれか1項記載の半導体チップ。

**【請求項 12】**

薄膜活性層（2）は5μm～25μmの厚さである、請求項11記載の半導体チップ。

**【請求項 13】**

少なくとも1つのキャビティ（8）の深さは薄膜活性層（2）の厚さの1/2よりも大きい、請求項1から12までのいずれか1項記載の半導体チップ。

**【請求項 14】**

支持体基板（1）は導電性であり、薄膜活性層（2）とは反対側に電気コンタクト面（44）を有する、請求項1から13までのいずれか1項記載の半導体チップ。

**【請求項 15】**

支持体基板（1）は電気的に絶縁性または導電性であり、薄膜活性層（2）へ向かう側に薄膜活性層（2）のほか電気コンタクト面（46）を有する、請求項1から14までのいずれか1項記載の半導体チップ。

**【請求項 16】**

薄膜活性層（2）の実装側（11）とは反対側の表面（6）に光出力を改善するための光学的なコーティング層（42）が設けられている、請求項1から15までのいずれか1項記載の半導体チップ。

**【請求項 17】**

光学的なコーティング層（42）はケイ素窒化物から形成されている、請求項16記載の半導体チップ。

**【請求項 18】**

光学的なコーティング層（42）は導電性のインジウム錫酸化物から形成されている、請求項16記載の半導体チップ。

**【請求項 19】**

薄膜活性層（2）は1つまたは複数のコンタクト位置（7、43）の領域内にはキャビティ（8）を有さない、請求項1から18までのいずれか1項記載の半導体チップ。

**【請求項 20】**

メサ（4）は支持体基板（1）へ向かって先細になっている、請求項1から19までのいずれか1項記載の半導体チップ。

**【請求項 21】**

10

20

30

40

50

メサ(4)は角錐台状または円錐台状の形状を有しており、その斜めの側面は薄膜活性層(2)のラテラルな延在方向に対して5°～60°の立ち上がり角<sub>1</sub>、例えば10°～40°の立ち上がり角<sub>2</sub>を有している、請求項2\_0記載の半導体チップ。

**【請求項2\_2】**

立ち上がり角<sub>1</sub>は15°～30°である、請求項2\_1記載の半導体チップ。

**【請求項2\_3】**

光子を形成する活性ゾーン(3)を備えた薄膜活性層(2)を有する発光半導体チップを同時に複数個製造する

発光半導体チップの製造方法において、

光子を形成する活性ゾーン(3)を含む層列を成長基板(2\_0)上にエピタキシャル成長させるステップと、

小さな深さの少なくとも1つのキャビティ(8)を層列内に形成して複数のメサ(4)を層列内に生じさせ、層列が複数のメサに接するカバー層(5)を有し、該カバー層の内部に光子を形成する活性ゾーン(3)が位置するようにし、ここで前記キャビティは薄膜活性層のp-n接合領域が分断されずにカバー層の内部に位置する深さに設けられ、メサ(4)は支持体基板へ向かって先細となり、さらに反射層(9、10)によってカバーされるステップと、

成長基板(2\_0)および層列から成るプレート接合体を、メサ(4)が支持体基板(2\_1)の方向へ向くように支持体基板(2\_1)上へ被着し、プレート接合体と支持体基板(2\_1)とを例えればはんだまたは接着剤により接合するステップと、

電気コンタクト(7、43、49)をメサ(4)とは反対側の層列上に被着するステップと、

支持体基板(2\_1)およびパターニングされた層列から成る接合体を半導体チップ(2\_3)の分離トラック(2\_2)に沿ってダイシングするステップと

を有する

ことを特徴とする発光半導体チップの製造方法。

**【請求項2\_4】**

成長基板(2\_0)を少なくとも部分的に除去する、請求項2\_3記載の方法。

**【請求項2\_5】**

少なくとも1つの絶縁層(9)をキャビティ(8)の設けられた層列の表面上に被着し、メサ(4)上に少なくとも1つのスルーコンタクト(12)を形成する、請求項2\_3または2\_4記載の方法。

**【請求項2\_6】**

層列と支持体基板(2\_1)とを接合する前に層列を分離トラック(2\_2)に沿って分離する、請求項2\_3から2\_5までのいずれか1項記載の方法。

**【請求項2\_7】**

接合前に成長基板(2\_0)を少なくとも部分的に除去し、続いて支持体基板(2\_1)の分離前に層列を分離トラック(2\_2)に沿って別個のステップで分離する、請求項2\_6記載の方法。

**【発明の詳細な説明】**

**【0001】**

本発明は、光子を形成するゾーンを備えた薄膜活性層、例えばIn<sub>1-x-y</sub>A<sub>1-x</sub>Ga<sub>y</sub>P(ここで0<x<1、0<y<1、x+y=1である)ベースの層列を有する活性層と、チップの放射方向とは反対側に薄膜活性層を備え、これに接続されている支持体基板とを有する発光半導体チップに関する。本発明はさらに、この種の発光半導体チップを複数個同時に作成する方法に関する。

**【0002】**

支持体基板はそれ自体で半導体チップの一部であり、薄膜層の機械的な支承部、すなわち主として薄膜層を支承する部材となっている。ここでは支持体基板の反対側には独立の層は設けられていない。

10

20

30

40

50

## 【0003】

$In_{1-x-y}Al_xGa_yP$  (ここで $0 < x < 1$ 、 $0 < y < 1$ 、 $x+y < 1$ である) ベースの薄膜活性層とは、複数の層を有する薄膜活性層を意味しており、これはドープまたは非ドープの材料系 $In_{1-x-y}Al_xGa_yP$  (ここで $0 < x < 1$ 、 $0 < y < 1$ 、 $x+y < 1$ である) から製造されている。

## 【0004】

冒頭に言及した形式の半導体チップは米国特許第5008718号明細書、米国特許第5367580号明細書から公知である。こうした公知のタイプのチップを製造するためには、有利には半導体の活性層の列を基板上にエピタキシャルプロセスにより堆積させる。半導体の活性層の列の上表面にはさらに支持体基板が固定される。この半導体の層列の上表面に設けられた基板は少なくとも部分的に除去される。10

## 【0005】

有利には支持体基板と半導体の活性層の列とのあいだには金属の反射層が存在しており、このため光は支持体基板には吸収されない。

## 【0006】

周知の半導体チップの欠点は支持体基板と半導体の活性層の列とのあいだに配置された金属の反射層が短い波長では一般に充分な反射率を有さないことである。特に600nm以下の波長では金は反射率が大幅に低下するため、金属の反射層としては全く適していない。600nm以下の波長では反射率が比較的一定である例えばAl、Agなどの元素が使用される。20

## 【0007】

さらに大面積の接合により金属の反射層と同様の問題が生じる。接合剤と金属のコンタクト層の合金とによりさらに金属の反射層の品質を損なう重大な危険まで生じる。

## 【0008】

さらに独国特許出願公開第19807758号明細書から、角錐台上の半導体チップが公知であり、ここでは活性の光形成層が上方のウインドウ層と下方のウインドウ層とのあいだに設けられている。上方のウインドウ層および下方のウインドウ層はともに角錐台のベースボディを有する。ウインドウ層の側壁が斜めに配向されることにより、活性ゾーンから出る光が側面で全反射し、ほぼ垂直に発光面として用いられる角錐台状のベースボディのベース面へ出射される。これにより活性ゾーンから放出される光の一部しか半導体エレメントの出射円錐の内部で表面へは出射されない。30

## 【0009】

出射円錐とは、ここでは次のような円錐であると解されたい。すなわち、出射面への入射角が全反射の限界角よりも小さいために全反射は生じず、直接に半導体材料から出力される光ビームから成る円錐である。したがって出射円錐の開放角は全反射の限界角の2倍である。出射円錐から外れて存在する光ビーム、つまり全反射の限界角よりも大きな角度で出射面へ到來した光ビームは全反射してしまう。

## 【0010】

光効率を大幅に上昇させるために、本発明のコンセプトでは上方のウインドウ層および下方のウインドウ層の最小厚さが前提となっている。公知の角錐台状の半導体エレメントでは、上方のウインドウ層および下方のウインドウ層の厚さは少なくとも50.8μm(2minch)である。このような層厚さは一応製造可能な範囲には入っている。しかし公知の半導体チップの出力を高めようすると、全寸法をスケーリングしなければならない。その際には層の厚さは迅速に得られるものの、高いコストのかかるエピタキシャルな手法を用いてしか製造できない。したがってこうした公知の半導体チップはそもそも大きな技術コストをかけなければスケーリングすることができない。40

## 【0011】

こうした従来技術に基づいて、本発明は、薄膜技術によって製造可能な、光出力の改善された半導体チップとその製造方法とを提供することを課題とする。

## 【0012】

10

20

30

40

50

この課題は本発明の請求項1の特徴部分記載の構成を有する半導体チップを構成して解決される。課題はまた、請求項2 3の特徴部分記載の構成を有する方法を構成して解決される。

### 【0013】

有利な実施形態および半導体チップの製造方法は従属請求項の対象となっている。

### 【0014】

半導体チップの特に有利な実施形態では、キャビティの横断面積は外側から内側へ向かって、つまり支持体基板の境界部から薄膜層の内部へ向かって小さくなっている。キャビティの深さは薄膜層の厚さの1/2よりも大きい。

### 【0015】

キャビティまたはこれにより形成される複数のメサから、一方では有利に薄膜層の接続側が支持体基板に対する圧着面を有することになり、この圧着面はチップの全横断面に比べて小さい。これにより小さな圧着面の領域で比較的大きな局所圧力が形成されるという利点が得られる。このことは支持体基板と薄膜層との確実な接合を促進し、同時に薄膜層にかかる圧力が充分を小さく保持する。これにより薄膜層を支持体基板に接合する際の層損壊の危険がほぼ排除される。

### 【0016】

他方では使用される接合面がキャビティのために拡大され、このことにより同様に支持体基板と薄膜層との接合が改善される。さらにキャビティは余った接着剤またははんだ材料も収容することができ、これらの材料の用法をクリティカルに監視しなくて済む。

### 【0017】

キャビティによればさらに有利な側面が得られ、ここでは活性ゾーンから放出されたビームの一部が偏向され、出射円錐の内部で支持体基板とは反対側の薄膜層の出射面へ出射する。従来技術と比べて、本発明の半導体チップでは、メサの側面での反射の少なくとも一部は透過性の平坦な反射層上の反射の位置で生じる。

### 【0018】

本発明によらない提案では、側面ができる限り薄膜層内へ深く入りこむ。というのは、ビームの最大成分、すなわち活性ゾーンから放出されても直接に出射面に到来せず、場合によっては何度も反射してしまう成分が出射円錐内部にある所定の角度で出射面に達するからである。

### 【0019】

実験したところでは、キャビティの深さが薄膜層の厚さの1/2よりも大きいとき、出力効率が上昇すると判明している。

### 【0020】

本発明によらない提案では、キャビティは薄膜活性層の活性ゾーンが分断される深さを有する。

### 【0021】

活性ゾーンが固定面側から薄膜活性層内へ埋め込まれているキャビティによって分断されている半導体チップは特に高い光効率を有することが判明している。なぜならこの場合には固定面へ向かって放出される光子のみでなく、薄膜活性層の出射面へ向かって放出される光子の少なくとも一部も出射円錐内に入ってくるからである。これは反射により光がメサの側面で出射面に対する所定の角度へ偏向されることによって生じる。

### 【0022】

メサの界面での反射により活性ゾーンから放出される光子の大部分は出射円錐の内部で出射面へ到来し、半導体チップから出力される。

### 【0023】

本発明の有利な実施形態では、活性ゾーンから放出される光子の少なくとも1つのトラジェクトリが各メサから隣接するメサへと通じている。

### 【0024】

メサの光学的な結合状態により、もともとのメサの側面で反射しなかった光子は隣接す

10

20

30

40

50

るメサに達し、その側面で反射され、出射円錐の内部で出射面へ到来する。

**【0025】**

さらに本発明の有利な実施形態では、凹型の側面を有するメサが設けられる。

**【0026】**

こうした手段により、出射面で最初に反射され、以後反射のたびにメサの側面で出射面に対して鋭角をなすようになっていくビームが生じ、これにより最終的にはこれらのビームも出射円錐の内部で出射面から出射される。

**【0027】**

本発明の別の実施形態によれば、メサは反射層によってカバーされる。

**【0028】**

こうした手段により、全体ではメサの側面で生じる光ビームは半導体チップの出射方向へ偏向される。

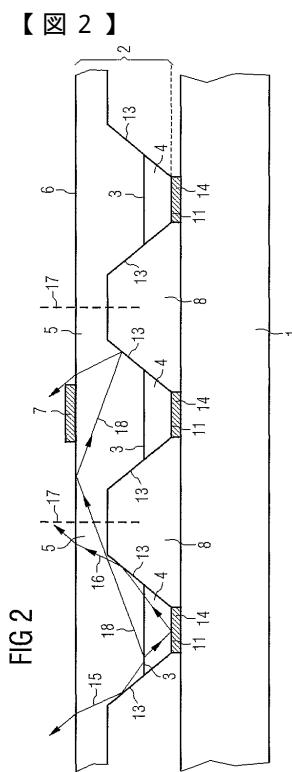

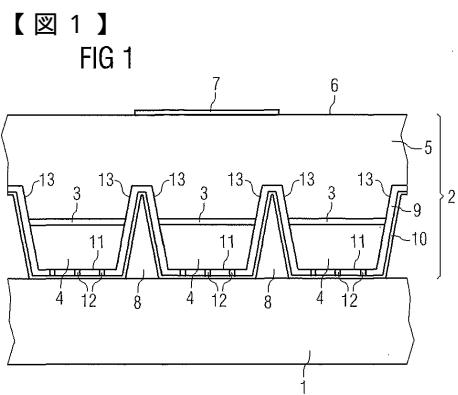

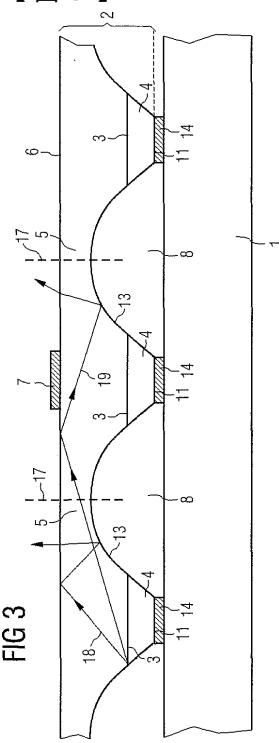

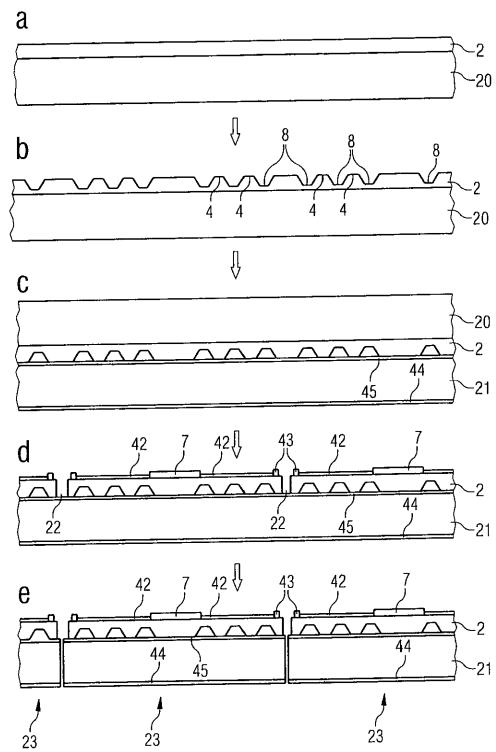

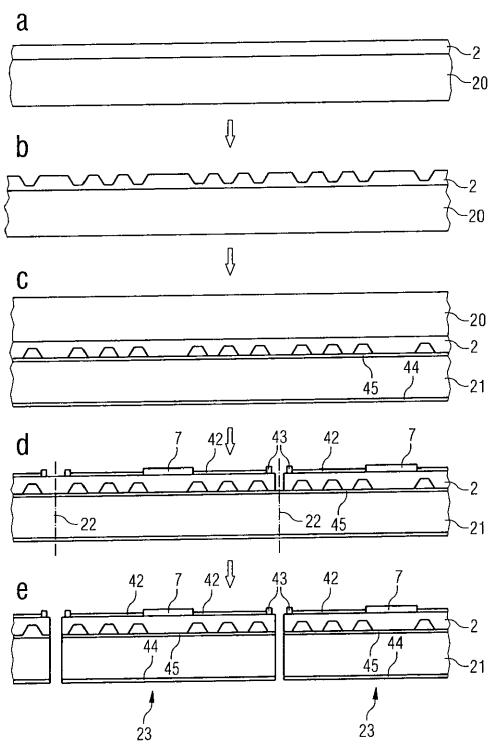

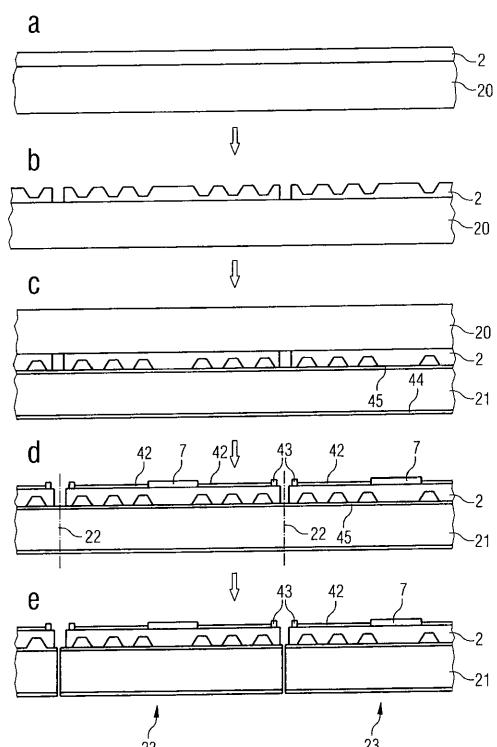

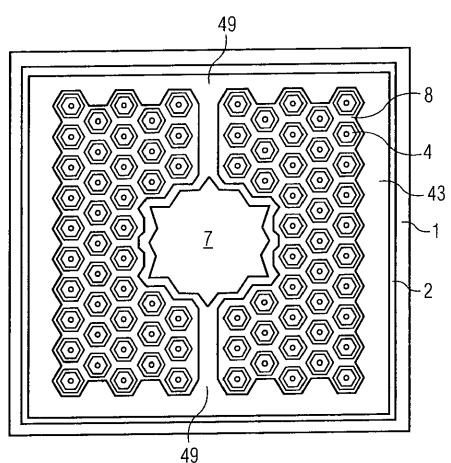

**【0029】**

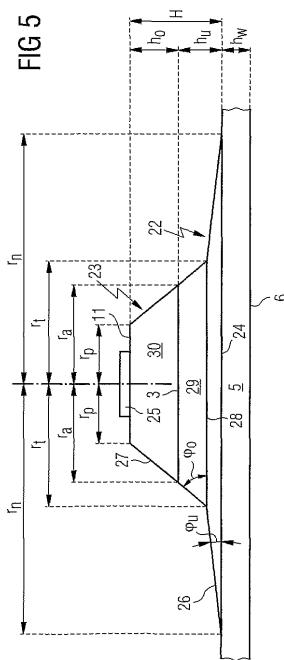

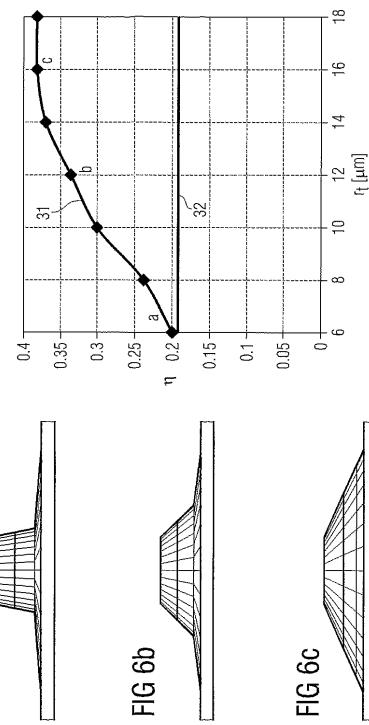

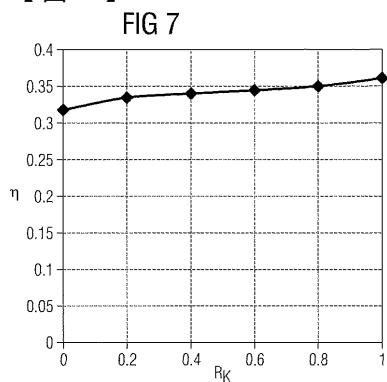

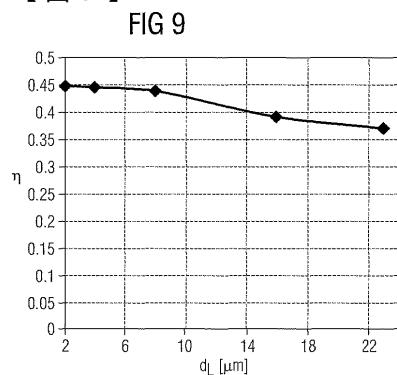

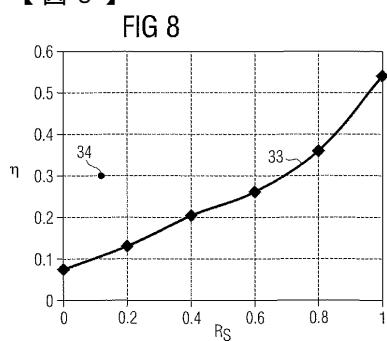

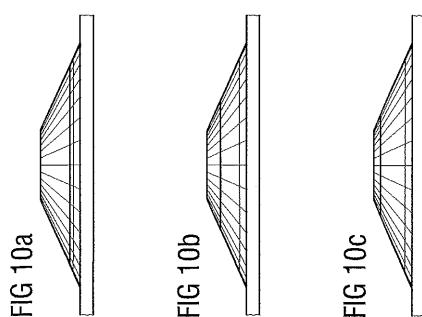

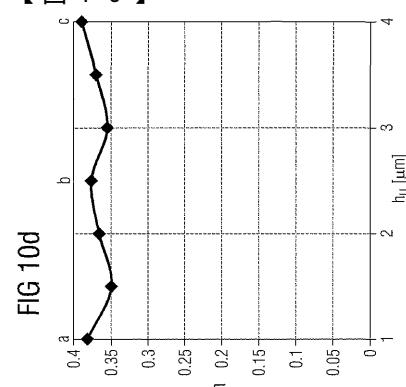

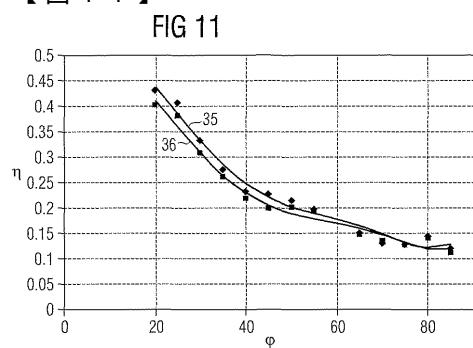

本発明の半導体チップおよび本発明の方法の別の有利な構成を以下に図示の実施例に則して説明する。図1には半導体チップの概略的な断面図が示されている。図2には活性ゾーンが角錐台状のメサ内に配置されている半導体チップの第2の例の概略的な断面図が示されている。図3には凹形の側面を有するメサの設けられた半導体チップの第3の例の概略的な断面図が示されている。図4には図3の半導体チップと従来の半導体チップとを比較して光効率が上昇していることが示されている。図5には、下方がなだらかな円錐台となっており、上方が急峻な円錐台となっているメサの断面プロファイルの概略図が示されている。図6のa～dにはメサの下方の角錐台および上方の角錐台の界面の種々の半径を表す各断面プロファイルおよびこれと出力効率との関係を表す図が示されている。図7にはメサのピークに配置された図5のコンタクト層の反射性と出力効率との関係を表す図が示されている。図8には図5のメサの側面の反射性と出力効率との関係を表す図が示されている。図9には出力効率と活性ゾーン内の発光点の大きさとの関係を表す図が示されている。図10のa～dには活性ゾーンの高さの変化した種々のメサの各断面プロファイル、および出力効率と下方の境界層の厚さとの関係を表す図が示されている。図11には図10のbに示された断面プロファイルを有するメサのエッジ角度と出力効率との関係を表す図が示されている。図12には図10のbに示された断面プロファイルを有するメサのエッジ角度との出力効率との関係図が示されている。図13には同じ高さで薄膜活性層の幅を種々に変えた場合の出力効率を表す図が示されている。図14にはメサに接合されているカバー層の厚さと出力効率との関係がメサの種々のプロファイルごとに示されている。図15には本発明の半導体チップの第3の実施例の概略的な断面図が示されている。図16には本発明の半導体チップの第4の実施例の概略的な断面図が示されている。図17のa～eには本発明による複数の半導体チップの製造方法の第1の実施例が概略的に示されている。図18のa～eには本発明による複数の半導体チップの製造方法の第2の実施例が概略的に示されている。図19のa～eには本発明による複数の半導体チップの製造方法の第3の実施例が概略的に示されている。図20には本発明による半導体チップを上方から見た図が示されている。図21にはキャビティを形成したあとの薄膜活性層の表面の斜視図が示されている。図22には図21の表面の拡大部分図が示されている。

**【0030】**

実施例の同じ構成素子または相応する構成素子には図中でも同じ参照番号を付してある。

**【0031】**

図1に示されているルミネセンスダイオード用の半導体チップは支持体基板1を有しており、この基板上に薄膜活性層2が被着されている。わかりやすくするために図1では薄膜活性層2の厚さを支持体基板1の厚さに比べて大きく示してある。薄膜活性層2は光子を形成する活性ゾーン3を有しており、このゾーンはそれぞれメサ4の中程の高さに配置されている。メサ4は角錐台状または円錐台状に構成することができる。半導体チップはルミネセンスダイオードである。

10

20

30

40

50

## 【0032】

メサ4はカバー層5に設けられている。メサの平坦な前面6の中央フロントにコンタクト面7が設けられており、このコンタクト面は有利にはメタライゼーション層によって形成されている。その反対側にキャビティ8によって形成されているメサは反射層によってカバーされており、このカバー層は誘電体のアイソレーション層9とその上に被着されたメタライゼーション層10とから成る。アイソレーション層9はメサ4のベース面11に沿って、メタライゼーション部から成るスルーコンタクト12により分断されている。

## 【0033】

アイソレーション層9は有利にはこれに接している薄膜層2の半導体層よりも小さい屈折率を有する。これはメタライゼーション層10の拡散バリアとして構成されている。10

アイソレーション層9に代えて導電体層を使用することもできる。重要なのは当該の層の光学的特性である。

## 【0034】

図1に示されている半導体チップを製造するために、最初に成長基板上に薄膜活性層2をエピタキシャル成長させる。薄膜活性層2は例えばInGaAlPベースで製造される。このとき、まずカバー層5を成長基板上に被着し、続いて $10^{18} \text{ cm}^{-3}$ 以上の濃度でドープし、カバー層5の良好な導電性を保証する。なぜならカバー層5の良好な導電性はルミネセンスダイオードの前面6において、中央のコンタクト位置7が複数のメサ4の活性ゾーン3へ電流を給電するために充分に機能することの前提となるからである。さらにカバー層5の組成は活性ゾーン内で形成される光子が透過されるように選定されている。20

これは通常の場合カバー層5の材料組成を変更してバンドギャップを調整することにより行われる。

## 【0035】

続いて別の層がカバー層5上に被着される。ここではメサ4が適切なウェットケミカルエッティングまたはドライケミカルエッティングにより構成される。この種のエッティングプロセスは周知であり、本発明の直接の対象ではない。メサ4は有利には半導体チップに対して設けられている領域（有利には光出力が行われる領域）のみに構成され、薄膜活性層2の表面のコンタクト層7、43、49の下方には設けられない。半導体チップのために設けられている領域は典型的には例えば $400 \times 400 \text{ nm}$ のラテラル方向の外半径を有する。このメサ4はこの薄膜活性層2の層厚さの範囲内に存在する外半径を有する。したがってメサ4の外半径は $10 \mu\text{m}$ の範囲にある。30

## 【0036】

さらなる方法ステップではアイソレーション層9のメサ4上の堆積とスルーコンタクト12の形成とが行われる。その後メタライゼーション層がカバーされる。

## 【0037】

続いて薄膜活性層2は設けられている半導体チップの数に相応に分離される。これは例えばウェットエッティングにより行われる。

## 【0038】

次に個別化された薄膜活性層2を支持体基板1に例えば共晶作用を用いた接合により固定され、成長基板をウェットエッティングにより除去する。続いてコンタクト位置7を露出された薄膜活性層2の前面に構成し、半導体チップを支持体基板1から分離してダイシングする。40

## 【0039】

図1に示されている半導体チップは活性ゾーン3から形成された光子が吸収性の半導体チップの素子には入射しないという利点を有している。なぜならメタライゼーション層10により光子は支持体基板1から隔絶されるからである。したがって支持体基板は有利には導電性および/または熱伝導性および/または熱拡散性の点できわめて良好に最適化されている。

## 【0040】

さらなる利点は、図1の半導体チップでは活性ゾーン3から放出される光子の大部分が

10

20

30

40

50

メサ 4 の側面で全反射するということである。側面 1 3 で全反射した光子は前面 6 へ大きな角度で当たる。特に光子のうちの一部、すなわち側面 1 3 での反射なしに全面で全反射した成分は出射円錐内部の前面 6 へ当たって半導体チップを出る。これにより図 1 の半導体チップでは従来技術から周知の透過性の底面での反射が少なくとも部分的に側面 1 3 での全反射に置き換えられる。したがって図 1 の半導体チップはキャビティ 8 のない従来の半導体チップに比べてほぼ係数 2 ほども改善された光効率を有する。

#### 【 0 0 4 1 】

前述の効果を以下に図 2 、図 3 に示されている別の実施例に則して詳細に説明する。

#### 【 0 0 4 2 】

ここで考察する光ビームとは所定の波長に制限されるものではなく、幾何光学の手法に 10 関連して、波長とは独立に理解すべきものである。

#### 【 0 0 4 3 】

図 2 に示されている実施例では、メサ 4 は角錐台状に構成されており、これはコンタクト層 1 4 を介してベース面 1 1 でのみ支持体基板 1 に固定されている。コンタクト層 1 4 を通して活性ゾーン 3 に電流が給電される。

#### 【 0 0 4 4 】

半導体と樹脂とでは屈折率が値にして 1 . 5 ~ 3 . 5 と大きく異なっていることから、半導体と樹脂との界面では半導体から出射円錐の内部、開放角約 1 6 ° で界面へ到来した光ビームのみが出力される。所定の角度にわたって均等に分散した光ビームの入射は平坦なユニットに入射する光ビームの約 2 % に相応する。 20

#### 【 0 0 4 5 】

メサ 4 により活性ゾーン 3 から出る光ビームは前面 6 の方向へ偏向される。メサ 4 は側面 1 3 へ入る光ビームが前面 6 の方向へ偏向され、そこから出射円錐内部で半導体チップから出射されるように作用する。このとき光効率はベース面 1 1 、側面 1 3 の傾斜角、メサ 4 の高さおよび活性ゾーン 3 の位置を適切に選定することにより最適化される。

#### 【 0 0 4 6 】

図 2 には、まず側面 1 3 で全反射され、そこから前面 6 へ偏向される光ビーム 1 5 が示されている。前面 6 では光ビーム 1 5 が界面へ当たって出射円錐の内部で半導体チップから出射される。側面 1 3 での全反射がない場合には、光ビーム 1 5 は前面 6 で全反射し、従来技術から周知の反射層へ戻る方向で偏向されてしまい、そこで新たに反射するはずである。このように、図 2 に示されている例では従来行われている反射層での反射が側面 1 3 での反射に置き換えられる。 30

#### 【 0 0 4 7 】

これはまずベース面 1 1 で反射し、次に側面 1 3 で反射する光ビーム 1 6 についても当てはまる。光ビーム 1 6 も第 2 の反射の後には前面 6 へ偏向され、そこから出射円錐内部で出射される。側面 1 3 での全反射がない場合には、光ビーム 1 6 も同様に前面 6 で全反射し、反射層へ戻る方向で偏向されてしまう。

#### 【 0 0 4 8 】

さらに有利には、メサ 4 はカバー層 5 の上方で光学的に結合されている。本発明における光学的な結合とは、薄膜活性層 2 から出る光ビームのうち少なくとも 1 つが中心線 1 7 を超えて 1 つのメサの領域から隣接するメサの領域へ達するということである。なぜならカバー層 5 を介した光学的な結合により、それぞれのメサの側面へ到来しない光ビーム 1 8 が隣接するメサの側面へ達し、そこで前面へ偏向されて出射円錐として出射されるからである。カバー層 5 を介した光学的結合により光効率は著しく上昇する。 40

#### 【 0 0 4 9 】

図 3 には半導体チップの変形例の断面図が示されている。ここではメサ 4 は凹形の側面 1 3 を有する円錐台状に構成されている。側面 1 3 の構成から、前面 6 と側面 1 3 とのあいだを往復して反射する光ビーム 1 8 が中心線 1 7 へ近づくにつれて前面へ向かう方向へ偏向され、出射円錐として前面 6 へ出射される。同じことが、まずカバー層 5 を介して各メサから隣接するメサへ達し、そこから大きな角度で前面 6 へ出ていく光ビーム 1 9 にも 50

当てはまる。

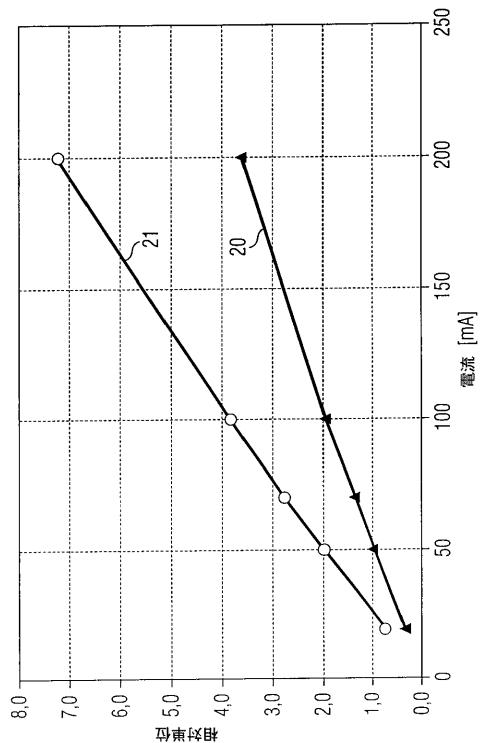

#### 【0050】

図4には、従来の薄膜技術で製造される発光ダイオードをパルス駆動した場合の相対単位で表される光効率と駆動電流との関係を表す測定曲線20と、図3に示されている例において相対単位で表される光効率と駆動電流との関係を表す測定曲線21とのダイアグラムが示されている。図4からわかるように、図3に示されている例の光効率は従来のキャビティ8のない半導体チップのほぼ2倍となっている。

#### 【0051】

メサ4の有利な形状を求めるために、一連の考察を行った。これらの考察の結果を以下に図5～図14に則して詳細に説明する。

10

#### 【0052】

まず考察に用いた種々のパラメータを図5に則して説明する。図5にはメサ4の断面プロファイルが示されている。図示の実施例では、メサ4は下方の円錐台22と上方の円錐台23とから成っている。下方の円錐台22は底面24を介してカバー層5に接している。上方の円錐台23には活性ゾーン3が構成されている。さらに図5にはメサ3のベース面11に配置されたコンタクト位置25が設けられている。

#### 【0053】

メサ4の側面13は下方の円錐台22のエッジ26と上方の円錐台23のエッジ27とから成る。下方の円錐台22のジオメトリ寸法は共通の界面28に沿って、エッジ26が直接にエッジ27に移行するように選定されている。

20

#### 【0054】

以下にメサ4の種々の寸法を考察する。下方の円錐台22の底面24の半径を $r_n$ 、界面28の半径を $r_t$ 、ベース面11の半径を $r_p$ とする。さらにメサ4は底面24と活性ゾーン3とのあいだの下方の限界層29と、活性ゾーン3とベース面11とのあいだの上方の限界層30とに分けられる。下方の限界層29はここでは高さ $h_u$ を有しており、上方の限界層30は高さ $h_v$ を有する。メサ4の全高をHとする。この全高Hは以下の考察において一貫して $6 \mu m$ とする。カバー層5の厚さ $h_w$ は、これを変更しない実施例においては、 $2 \mu m$ の値に選定されている。

#### 【0055】

図6のa～dにはベース面11の半径 $r_p$ が $5 \mu m$ 、底面24の半径 $r_n$ が $20 \mu m$ に設定されている場合の計算結果が示されている。界面28の半径 $r_t$ が $6 \mu m \sim 18 \mu m$ のあいだで変更され、これは図6のa～cの断面プロファイルに相応する。

30

#### 【0056】

ここでの考察では活性ゾーン3の屈折率3.2を使用している。下方の限界層29の屈折率、上方の限界層30の屈折率およびカバー層5の屈折率はそれぞれ等しく、3.3である。変更のないかぎりコンタクト位置25の反射率には0.3を使用する。コンタクト位置25でカバーされていないベース面11およびエッジ26、28の反射率は0.8の値に設定する。反射率とはエネルギーに対する反射係数を意味するものである。

#### 【0057】

さらに活性ゾーン3の自己吸収は $10000/cm$ の吸収係数で考慮される。全ての考察において光子のリサイクルを前提としている。これについては内部量子効率0.8を仮定した。電荷担体の再結合により光子が形成される際の量子効率は考慮に入れていない。したがってダイアグラムに示されている出力効率は半導体チップから出力される光子数と実際に形成された光子数との比に等しい。つまり、ここに示されている出力効率の値から外部効率を得るには係数0.8を乗算しなければならない。

40

#### 【0058】

さらにコンタクト位置25およびエッジ26、27での反射は角度に依存していると仮定する。この考察では、まず誘電体アイソレーション層9がメサ4上に被着され、鏡面化されたメタライゼーション層10によって補完される。この場合の作用は見過ごされがちである。なぜならこの考察ではこのようなケースで発生する全反射を考慮しないからであ

50

る。

#### 【0059】

図6のdには出力効率 $\eta$ と半径 $r_t$ との関係が曲線31で示されている。比較のために通常の薄膜半導体チップの出力効率を光子のリサイクルの過程にわたって散乱を平均したかたちで示してある。エッジ長さ300μmを有する薄膜半導体チップは、メサ4と同じエピタキシ構造体を下方の円錐台22および上方の円錐台23内に有している。半導体チップのp側にミラーが設けられていると仮定すると、反射率は0.72となる。この値は占有率で重みづけされた反射層およびコンタクト層の反射率の平均値である。ここで反射層の反射率は値0.8、反射層の占有率は値0.85、コンタクト層の反射率は値0.3、占有率は0.15である。

10

#### 【0060】

図6からわかるように、図6のaに示されている断面プロファイルでは上方の円錐台23のきわめて大きな立ち上がり角 $\theta$ のために、従来の薄膜ルミネセンスダイオードに比べても出力効率 $\eta$ はあまり改善されていない。この出力効率とは図6のdに直線32で示されているものである。ここで図6のaに示されている平坦な面積断面プロファイルを有するメサ4では、活性ゾーン3から出る光ビームが発光面6に対する急峻な角度ではほとんど生じないことが理解される。また図6のcに示されている断面プロファイルを有するメサ4はこの場合、従来の薄膜ルミネセンスダイオードの出力効率 $\eta$ のほぼ2倍の出力効率を有する。

20

#### 【0061】

さらに出力効率 $\eta$ とコンタクト位置25の反射率との関係を考察する。このために出力効率 $\eta$ がコンタクト位置25の反射率に依存して計算される。ここでメサ4の断面プロファイルは図6のbに示されている断面プロファイルに等しい。さらにコンタクト位置25がベース面11全体をカバーしていると仮定する。図7からわかるように、出力効率 $\eta$ はコンタクト位置25の反射率にはほとんど依存していない。ここに示されている固定面上にメサ4を設けられた半導体チップは、コンタクト位置25の低い反射率に対してはほとんど不感であり、従来の薄膜ルミネセンスダイオードよりも格段に有利である。なぜなら出力にいたるまでの多重の反射がベース面11と発光面6とのあいだの僅かな部分でのみ開放されるのではなく、メサ4内で3次元的に開放されるかである。

30

#### 【0062】

コンタクト位置25の反射率が相対的な依存関係を有することは特に有利である。なぜなら実際にはコンタクト位置25と上方の限界層30とのあいだの低いオーム抵抗は一般に低い反射率に結びついているからである。というのは、良好なオーム抵抗はコンタクト位置25を形成する層からその下方に存在する材料への原子の拡散を必要とするからである。

#### 【0063】

コンタクト位置25の反射率の依存性とは異なり、出力効率 $\eta$ とベース面11およびエッジ26、27のミラー面の反射率 $R_s$ との関係は強い特徴を有する。これはモデルを用いてメサ4の半径 $r_p = 5 \mu m$ 、 $r_d = 16 \mu m$ 、 $r_n = 20 \mu m$ の半導体チップに対して行われた計算の結果である。

40

#### 【0064】

したがってメサ4は図6のbに示されている断面プロファイルを有することが望ましい。

#### 【0065】

この計算の結果が図8に示されている曲線33であり、これは反射率 $R_s$ が増大とともに比例して上昇する。図8のダイアグラムに記入されている点34は、ミラー層は被着されていないものの周囲の媒体として樹脂中に埋め込まれた半導体チップに対する計算の結果である。ここでは全反射が生じてあり、これによりミラー層を有する半導体チップに比べて大きな出力効率が得られている。これは図1に示されている実施例、すなわちメタライゼーション層10のあいだに電気的なアイソレーション層が配置され、ここで同様に全反射が起こるケースと同様である。

50

## 【0066】

図9にはメサ4の半径  $r_p = 5 \mu m$ 、 $r_t = 16 \mu m$ 、 $r_n = 20 \mu m$ の半導体チップに対して行われた計算の結果が示されている。つまりこのメサ4は図6のbに示されている断面プロファイルを有する。活性ゾーン3のはここでは底面24とベース面11との中間の高さに存在する。計算では活性ゾーン3内で光子が発生して発光点へ集束される領域の直径  $d_L$  が横軸に示されている。図9のダイアグラムに基づいて見てとれるように、小さな発光点での出力効率のほうが高い。このことは光子が活性ゾーン3の中央で特に良好に出力されることを意味する。ここでは小さなWeierstrass効果が生じている。

## 【0067】

さらに活性ゾーン3の位置の影響を考察する。図10のa～cには種々の断面プロファイルが示されている。ここでは一定の全高Hのもとで下方の限界層29の高さ  $h_u$  と上方の限界層30の高さ  $h_v$  とが種々に変更されている。計算の結果は図10のdに示されており、ここでは出力効率  $\eta$  が下方の限界層29の厚さ  $h_u$  に依存して示されている。出力効率  $\eta$  は活性ゾーン3の位置にはほとんど依存していないことがわかる。活性ゾーン3をメサ4の下方の半部に設けると特に有利である。なぜならその場合には活性ゾーン3を通る電流密度が小さく、したがって活性ゾーン3の電流負荷を小さく保つことができるからである。これにより経年劣化または線形性の問題が回避される。

10

## 【0068】

さらにエッジ27の立ち上がり角  $\alpha$  およびエッジ26の立ち上がり角  $\beta$  の影響を考察する。この場合、下方の円錐台22および上方の円錐台23がそれぞれ等しい値の立ち上がり角  $\alpha$ 、 $\beta$  を有する断面プロファイルに基づいている。ここでは活性ゾーン3の半径  $r_a$  は一定の  $10 \mu m$  に保持されており、立ち上がり角  $\alpha = \beta = \gamma$  が変化している。ここでは2つのケースを考える。一方は出力効率  $\eta$  に対して周期的な限界条件が存在するケースである。ここでは脚部点の間隔は  $10 \mu m$  の値である。この結果は図11のダイアグラムに曲線35として示されている。もう一方は非周期的なケースである。このために半導体チップの出力効率  $\eta$  は個々のメサ4ごとに計算される。ここではカバー層5へ入射する全ての光子がカバー層5によって吸収される。非周期的なケースは図11では曲線36により再現されている。図11からはカバー層5が出力効率  $\eta$  にはっきり寄与していることが見て取れる。

20

## 【0069】

30

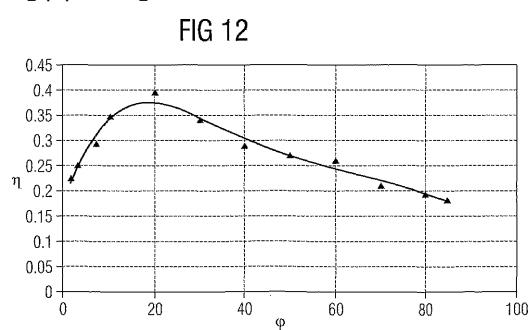

エッジ角  $\alpha$  について最適な領域が存在する。このことを図12に則して説明する。基礎とする計算では半径  $r_p$  を  $10 \mu m$  に設定した。活性ゾーン3の半径  $r_a$  と底面24の半径  $r_n$  とを変化させ、エッジ27、26の立ち上がり角  $\alpha$  を  $1.5^\circ \sim 85^\circ$  の間の値領域がカバーされるようにした。図12から見て取れるように、立ち上がり角  $\alpha$  の最適な角度領域が存在する。エッジ角  $\alpha$  は  $5^\circ \sim 60^\circ$  のあいだであり、有利には  $10^\circ \sim 40^\circ$  のあいだである。特に有利な出力効率  $\eta$  の値は立ち上がり角  $\alpha$  が  $15^\circ \sim 30^\circ$  のときに得られる。

## 【0070】

40

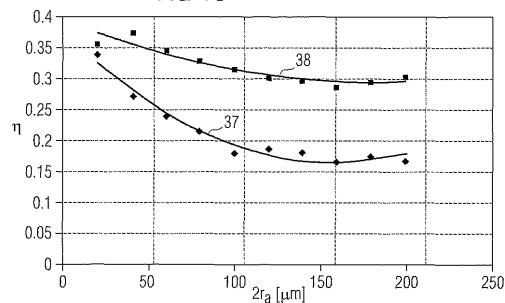

続いてメサ4の幅の変更が出力効率  $\eta$  に与える影響を考察する。この場合にはメサ4の高さは一定であり、半径  $r_p$ 、 $r_a$ 、 $r_n$  も等しい。図13の第1の曲線37はコンタクト位置25の反射率  $R_K$  が  $0.3$  であるケースを示している。第2の曲線38はコンタクト位置25の反射率  $R_K$  が  $0.8$  であるケースを示している。第1の曲線37でも第2の曲線38でも出力効率  $\eta$  は活性ゾーン3の直径  $2r_a$  に依存していることがわかる。コンタクト位置25の反射率が良好である場合、出力効率  $\eta$  は活性ゾーン3の直径が増大しても僅かしか低下しない。コンタクト位置25の反射率  $R_K$  の低い現実的なケースを表した第1の曲線37では、出力効率  $\eta$  は活性ゾーン3の直径が増大するにつれて大きく低下する。したがって出力効率はメサ4の側方の広がりを小さくすることによって改善されることになる。

## 【0071】

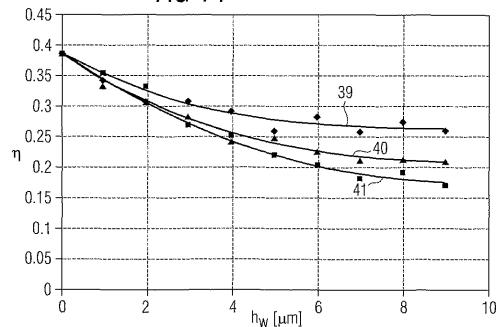

カバー層5の厚さも出力効率  $\eta$  にとって重要である。図14にはカバー層5の種々の厚

50

さ  $h_w$  に依存する出力効率 の結果が示されている。第 1 の曲線 3 9 は前述の周期的なケースを表し、第 2 の曲線 4 0 は非周期的なケースを表し、第 3 の曲線 4 1 はエッジ長さ 3 0 0  $\mu m$  の矩形の半導体チップが接合層を介して相互に接合されているケースを表している。図 1 4 からわかるのはカバー層 5 の層厚さが増大するにつれて有利になるということである。特に有利には、層厚さ  $h_w$  はメサ 4 の高さよりも小さく、例えば（このケースでは）6  $\mu m$  である。ここからキャビティ 8 の深さを薄膜活性層 2 の厚さの 1 / 2 よりも大きくすべきであることがわかる。

#### 【 0 0 7 2 】

しかも図 1 4 から見て取れるように、個々の半導体チップがそれぞれ 1 つずつメサ 4 を有している構成は最良のケースである。なぜならこのとき出力効率が厚さ  $h_w = 0$  で最高となるからである。ただし個々のチップはその出力を任意に増大することができないという欠点を有している。なぜなら出力とともに半導体チップの寸法もスケーリングしなければならないからである。実際にはエピタキシャル層の厚さは制限されている。このため個々の半導体チップを任意の大きさの出力に構成することはできない。これに対して図 1 ~ 図 4 に提示されている半導体チップはほぼ任意にスケーリングすることができる。これはカバー層 5 の面積の増大に相応して半導体チップの光出力を増大するためにメサ 4 の数のみを増大すれば良いからである。

#### 【 0 0 7 3 】

次の考察は活性ゾーン 3 がカバー層 5 の内部に位置しているか否かという問題に関連する。これについては従来の薄膜ルミネセンスダイオードの出力効率を考慮してこれを 1 とする。活性ゾーン 3 がカバー層 5 内に設けられている半導体チップは従来の薄膜ルミネセンスダイオードに比べて出力効率 1 . 2 5 を有する。これは活性ゾーン 3 がカバー層 5 の内部に設けられるとき、出力効率 の増大が達成されたことを示している。

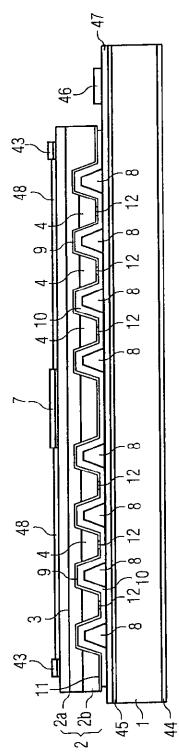

#### 【 0 0 7 4 】

図 1 5 には本発明の薄膜ルミネセンスダイオードの有利な構成の概略図が示されている。薄膜活性層 2 はここでは Te を高濃度（濃度 > 1 0<sup>17</sup> cm<sup>-3</sup>、有利には > 1 0<sup>18</sup> cm<sup>-3</sup>）にドープされた厚さ約 4  $\mu m$  の n 型 InGaAlP 層 2 a と、Mg をドープされた厚さ約 3 . 5  $\mu m$  の p 型 GaP 層 2 b とから成っている。

#### 【 0 0 7 5 】

支持体基板 1 に向かう側の薄膜活性層 2 の固定面 1 1 上には、図 1 に関連して説明したように、アイソレーション層 9、例えば Si<sub>3</sub>N<sub>4</sub> から成る層と金属の反射コンタクト層 1 0 とが被着されている。Si<sub>3</sub>N<sub>4</sub> は活性ゾーン 3 から放出される光の波長に関連して形成される放射の 3 つの波長による厚さを有しており、電気的な絶縁作用のほか、金属の反射層のミラー機能を改善する作用も有している。またこの層は適切な材料が使用されれば同時に薄膜活性層 2 と金属の反射層 1 0 とのあいだの拡散バリアとなる。

#### 【 0 0 7 6 】

これに代えてアイソレーション層 9 を例えばケイ素窒化物層およびケイ素酸化物層とが交互に配置された積層スタックから構成することもできる。

#### 【 0 0 7 7 】

活性ゾーン 3 への p 側の給電部は埋め込まれた AuZn コンタクト 1 2 により保証される。このコンタクトは支持体基板 1 に向かうメサ 4 の面に配置され、アイソレーション層 9 により貫通される。

#### 【 0 0 7 8 】

反射コンタクト層 1 0 は有利には AuZn / TiW (N) / Au 層である。ただしこの層を Au、Al、Ag、またはこれらの金属の合金から形成することもできる。

#### 【 0 0 7 9 】

充分な機械的安定性を達成するために、薄膜活性層 2 を接合により導電性の支持体基板 1（この実施例では n 型の GaAs 基板）上に被着する。この場合支持体基板 1 の上面および下面に Auge コンタクト層 4 4、4 5 が設けられる。薄膜活性層 2 に向かう側の面では Auge コンタクト層 4 5 上に例えば付加的な TiPtAu / AuSn 層 4 7 が配置

10

20

30

40

50

される。

**【0080】**

チップの前面または出力面には中央コンタクト7および金属のフレーム43または他の導電性のフレームが設けられており、これらは図示されていない導電性の2つのスタブを介して中央コンタクト7に接続されている。中央コンタクト7および金属のフレーム43は例えばTiPtAu層やこれと薄膜活性層2とのあいだに配置されたTiAuGe層から成る。

**【0081】**

n型のInGaAlP層の高い導電率により、必要な電流伝搬が保証される。活性ゾーン3のp側への給電はコンタクト層44を介して支持体基板1の下面で行われ、この基板を通って電流が流れる。

10

**【0082】**

光出力をさらに改善するために、薄膜活性層2の前面に光学的なコーティング層42が配置される。これはこの実施例ではSi<sub>3</sub>N<sub>4</sub>から成る/4の層である。

**【0083】**

既に図2に関連して説明したように、薄膜活性層2には支持体基板1と薄膜活性層2とのあいだの接合面から複数の角錐台状のキャビティ8が設けられている。これらのキャビティはルミネセンスダイオードの光出力を著しく高める。本発明によらない提案ではキャビティ8はpn接合領域3を分断する幅で薄膜活性層2内に延在している。本発明ではキャビティ8はpn接合領域を分断しない深さに構成する。

20

**【0084】**

光出力を上昇させるほか、キャビティ8は付加的に薄膜活性層2と支持体基板1との共晶作用による接合の際に、それぞれの材料ひいては熱拡散係数が異なることにより、発生する電圧を大幅に低減することができる利点を有する。このためプロセスの確実性および製造の歩留まりが改善される。

**【0085】**

同様のことが半導体チップの駆動中に熱損失による温度上昇時に異なる熱拡散係数のために発生する機械的な応力の保証についても当てはまる。

**【0086】**

図16には本発明の半導体チップの別の実施例が概略図で示されている。この実施例では薄膜活性層2は電気的に絶縁性の支持体基板1上に被着されており、pn接合領域3のp側への給電はAuGeコンタクト層45上に薄膜活性層2に隣接して配置されたp型コンタクト46を介して行われる。

30

**【0087】**

p型のInGaAlP層2bは6μmの厚さを有しており、 $1 \times 10^{18} \text{ cm}^{-3}$ の濃度でドープされたn型のInGaAlP:T<sub>e</sub>層2aは3μmの厚さを有している。キャビティ8はこの実施例では5.5μmの深さで延在している。これらのキャビティはこの実施例ではpn接合領域3を分断していない。

**【0088】**

支持体基板1とは反対側の薄膜活性層2の前面に、この実施例では例えば導電性のインジウム錫酸化物から成る光学的なコーティング層48が配置される。これは光出力を改善するほか、電流伝搬路としても用いられる。n型の層2aはここでは電気的に絶縁性のコーティング層を使用する場合よりも薄く構成することができる。なぜならこの場合には電流の伝搬は薄膜活性層2のみで行わなくてよいからである。

40

**【0089】**

このような導電性のコーティング層48は半導体チップの他の全ての実施例においても使用することができる。同様に図16の実施例ではインジウム錫酸化物層48に代えてアイソレーション用のコーティング層42を使用することができる。

**【0090】**

図16に示されている構造は導電性の支持体基板1を使用する場合にも適しており、電

50

気的に絶縁性の支持体基板1の使用には制限されない。

【0091】

図16の実施例の構造は、支持体基板1が有利には特に熱拡散および／または熱伝導性の点で最適化され、その際にも導電性に注意を払わなくてよいという利点を有する。

【0092】

必要に応じて薄膜活性層2の処理時にはキャビティ8を適切な材料で充填することができる。

【0093】

図17のa～eには複数の半導体チップを同時に製造する本発明の方法のシーケンスが概略図で示されている。ここではウェハを結んだ縦のセクションで製造プロセスの各時点が示されている。ただし薄膜活性層2および支持体基板1と薄膜活性層2とのあいだの前述の層の詳細図は図18a～図19eのプロセスを説明する際にも簡単化のために省略してある。

10

【0094】

薄膜活性層2、アイソレーション層9、コンタクト層7、43～47、49、およびコーティング層42、48は例えば従来の半導体技術から周知の堆積プロセスにより製造される。

【0095】

第1の部分プロセスでは、成長基板20上に薄膜活性層2が成長される（図17のaを参照）。前述のようにこのような薄膜活性層2は一般に種々の組成の複数の半導体層を有している。

20

【0096】

次にメサ4を形成するための薄膜活性層2内の後に半導体チップでの光形成を行うべき領域にキャビティ8が形成される。これは例えば適切なマスク技術と異方性ウェットケミカルエッティングにより行われる（図17のbを参照）。

【0097】

さらに薄膜活性層2のキャビティ8の設けられる側には反射層9、10が被着され、メサ4にスルーコンタクト12が形成される。これらは図示されていないが、例えば図15、図16を参照されたい。その後これらの側は続いて支持体基板1に接合される。基板上の主表面には有利なコンタクト層44、45が存在している（図17のcを参照）。

30

【0098】

成長基板20が少なくとも部分的に、有利には完全に除去された後、薄膜活性層2の露出面では半導体チップの存在する領域にボンディングパッド7が被着される。このボンディングパッドにより端子スタブ49（図20を参照）を介して給電フレーム43が接続されている。このフレームは後にチップとなる薄膜活性層2の外縁部に延在する。例えばこの種のコンタクト層の材料は上述した通りである。後のチップの放射出力面はボンディングパッド7とコンタクトフレーム70とのあいだに存在しており、これには光学的なコーティング層42が設けられている（図17のdを参照）。

【0099】

このようにして処理されたウェハをダイシングする前に、薄膜活性層2を分離トラック22に沿って有利にはエッティングにより分離し、これによって生じる薄膜活性層2のエッジにダメージエッティングが行われる。薄膜活性層2のエッジには必要な場合にコーティング層および／またはパッシベーション層を設けることができる。

40

【0100】

このステップの後、支持体基板21は例えばソーや旋盤、カッタなどにより分離トラック22に沿って切断され、分離される。これにより個々の半導体チップ23が得られる。

【0101】

半導体チップは有利にはプレート接合体として完成される。すなわちウェハを個々のチップへダイシングするステップがプロセスの最終ステップであり、これは後の時点でチップを例えればケーシング内へマウントする前に行われる。

50

**【0102】**

図18のa～eに示されている方法は、図17のa～eに示されている方法に比べて、主として薄膜活性層2の個別化を支持体基板のウェハ21の分離前に行い、薄膜活性層2の分離と支持体基板のウェハ21の分離トラック22に沿った分離とを同時に1つのステップで行う点が異なっている。

**【0103】**

図19のa～eに示されている方法は、図17のa～eに示されている方法に比べて、主として薄膜活性層2の個別の分離を薄膜活性層2と支持体基板のウェハ21との接合前に行う点が異なっている。

**【0104】**

成長基板の除去は研削および／またはウェットケミカルエッティングを用いる手法に代えて、分解法により行ってもよい。このために有利には薄膜活性層と成長基板とのあいだに成長基板よりも小さなバンドギャップを有する吸収層を挿入する。成長基板を通して吸収層は適切な波長のレーザーにより分解される。GaAsから成る成長基板では吸収層は例えばInGaAsから成っており、レーザーは例えばIRレーザーである。

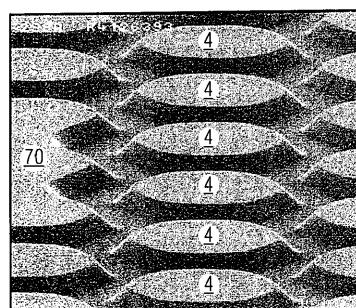

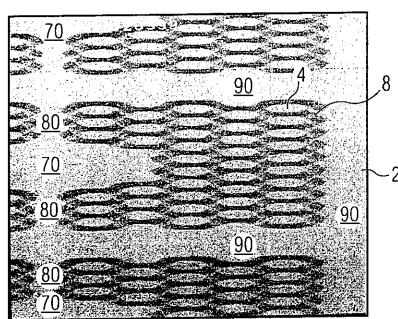

**【0105】**

図20に示されている本発明のチップの平面図はキャビティ8により形成されたメサ4を上方から見た図である。ここからわかるように、特にコンタクト7の領域70、端子スタブ49の領域80、給電フレーム43の領域90、および分離トラックにはキャビティ8は設けられていない。これらは全て放射が全く出力されないか、わずかしか出力されない領域である。これらの領域からキャビティを排除することにより、有利には薄膜活性層2の機械的な安定性が著しく上昇する。これにより特にコンタクト7の領域にポジティブな効果が得られる。なぜならそこでは半導体チップをケーシングに実装する際に一般にボンディングワイヤが載せられ、プリントされるからである。

**【0106】**

図21にはキャビティ8を形成した後の薄膜活性層2の表面の斜視図が示されている。ここでもコンタクト7の領域70、端子スタブ49の領域80、および給電フレーム43の領域90にメサ4が設けられていないことが見て取れる。

**【0107】**

図22は図21の拡大部分図である。

10

20

30

**【図面の簡単な説明】**

**【図1】** 半導体チップの概略的な断面図である。

**【図2】** 半導体チップの第2の例の概略的な断面図である。

**【図3】** 半導体チップの第3の例の概略的な断面図である。

**【図4】** 図3の半導体チップと従来の半導体チップとの光効率の比較図である。

**【図5】** メサの断面プロファイルの概略図である。

**【図6】** メサの各断面プロファイルおよびこれと出力効率との関係を表す図である。

**【図7】** メサのピークに配置された図5のコンタクト層の反射性と出力効率との関係を表す図である。

**【図8】** 図5のメサの側面の反射性と出力効率との関係を表す図である。

40

**【図9】** 活性ゾーン内の発光点の大きさと出力効率との関係を表す図である。

**【図10】** 活性ゾーンの種々の高さのメサの各断面プロファイル、および出力効率と下方の境界層の厚さとの関係を表す図である。

**【図11】** 図10のbに示された断面プロファイルを有するメサのエッジ角度と出力効率との関係を表す図である。

**【図12】** 図10のbに示された断面プロファイルを有するメサのエッジ角度と出力効率との別の関係を表す図である。

**【図13】** 同じ高さで薄膜活性層の幅を種々に変えた場合の出力効率の関係を表す図である。

**【図14】** メサに接合されているカバー層の厚さと出力効率との関係を表す図である。

50

- 【図 15】 本発明の半導体チップの第3の実施例の概略的な断面図である。

- 【図 16】 本発明の半導体チップの第4の実施例の概略的な断面図である。

- 【図 17】 本発明による複数の半導体チップの製造方法の第1の実施例を示す図である。

- 【図 18】 本発明による複数の半導体チップの製造方法の第2の実施例を示す図である。

- 【図 19】 本発明による複数の半導体チップの製造方法の第3の実施例を示す図である。

- 【図 20】 本発明による半導体チップを上方から見た図である。

- 【図 21】 キャビティを形成した後の薄膜活性層の表面の斜視図である。 10

- 【図 22】 図21の活性層の表面の拡大部分図である。

【 図 3 】

【 図 4 】

【図5】

【図6】

【図7】

【図9】

【図8】

【図10】

【図11】

【図12】

【図13】

FIG 13

【図14】

FIG 14

【図16】

【図17】

【図18】

【図19】

【図20】

【図22】

【図21】

---

フロントページの続き

(74)代理人 100099483

弁理士 久野 琢也

(72)発明者 シュテファン イレク

ドイツ連邦共和国 フェルトキルヒエン ロートヴァントシュトラーセ 41

(72)発明者 アンドレアス プレスル

ドイツ連邦共和国 レーゲンスブルク ランツフーター シュトラーセ 41

(72)発明者 クラウス シュトロイベル

ドイツ連邦共和国 ラーバー エアレンシュトラーセ 7

(72)発明者 ヴァルター ヴェークライター

ドイツ連邦共和国 ニッティンドルフ マリーエンシュトラーセ 15

(72)発明者 ラルフ ヴィルト

ドイツ連邦共和国 レーゲンスブルク アウグステンシュトラーセ 13

合議体

審判長 稲積 義登

審判官 吉野 公夫

審判官 三橋 健二

(56)参考文献 特開平07-193275(JP,A)

特開平06-318731(JP,A)

特開平04-063478(JP,A)

特開平11-274568(JP,A)

特開昭52-124885(JP,A)

特開平01-151275(JP,A)

特開昭61-183986(JP,A)

特開平07-142815(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 33/00