(19) (KR)

(12) (B1)

(51) . Int. Cl.<sup>6</sup> (45) 2004 11 26

H03K 19/177 (11) 10-0458371

(24) 2004 11 15

|      |                   |      |                 |

|------|-------------------|------|-----------------|

| (21) | 10-1999-7001391   | (65) | 10-2000-0068256 |

| (22) | 1999 02 20        | (43) | 2000 11 25      |

|      | 1999 02 20        |      |                 |

| (86) | PCT/IB1997/000987 | (87) | WO 1998/08306   |

| (86) | 1997 08 12        | (87) | 1998 02 26      |

|      |          |    |    |         |            |            |      |

|------|----------|----|----|---------|------------|------------|------|

| (81) | AP ARIPO | EA | EP | OA OAPI | 08/700,966 | 1996 08 21 | (US) |

| (30) |          |    |    |         |            |            |      |

| (73) |          |    |    |         | 01930      |            | 3    |

| (72) |          |    |    |         | 01748      | 6          |      |

| (74) |          |    |    |         |            |            |      |

(54) 가

4

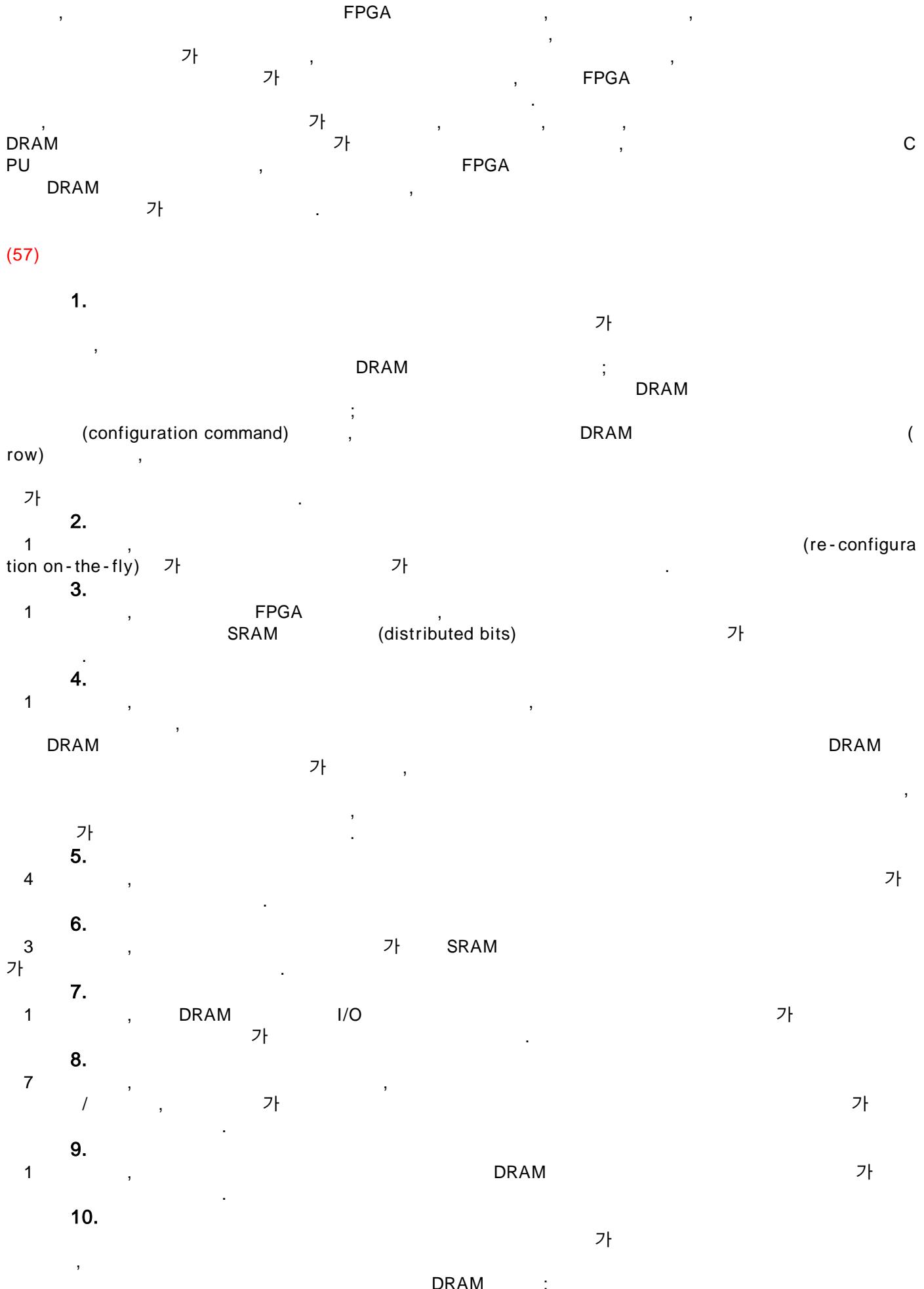

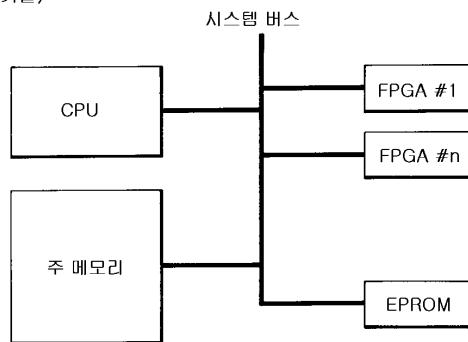

가 , FPGA(field programmable gata array; ) .

The diagram illustrates a hybrid architecture with the following components and connections:

- Central Processing Unit (CPU):** Represented by a large rectangle labeled "CPU". It has two 32-bit data buses (labeled 2 and 32) connected to a **Floating Point Unit (FPU)** (labeled "floating point unit").

- Field-Programmable Gate Array (FPGA):** Represented by a large rectangle labeled "FPGA". It has two 64-bit data buses (labeled 64 and 64) connected to the CPU. It also has a 32-bit data bus (labeled 32) connected to a **Design Emulation Unit (DEU)** (labeled "(design emulation)'").

- Random Access Memory (RAM):** Represented by a large rectangle labeled "RAM". It has a 64-bit data bus (labeled 64) connected to the CPU. It also has a 32-bit data bus (labeled 32) connected to the DRAM.

- Dynamic Random Access Memory (DRAM):** Represented by a large rectangle labeled "DRAM". It has a 64-bit data bus (labeled 64) connected to the RAM. It also has a 32-bit data bus (labeled 32) connected to the CPU.

- Design Emulation Unit (DEU):** Represented by a rectangle labeled "DEU". It has a 32-bit data bus (labeled 32) connected to the FPGA. It also has a 64-bit data bus (labeled 64) connected to the RAM.

- Non-configuration (non-reconfiguration) Unit:** Represented by a rectangle labeled "non-reconfiguration". It has a 10,000-bit data bus (labeled 10,000) connected to the FPGA. It also has a 10,000-bit data bus (labeled 10,000) connected to the DRAM.

- AM (Address Memory):** Represented by a rectangle labeled "AM". It has a 1-bit data bus (labeled 1) connected to the DRAM. It also has a 3-bit data bus (labeled 3) connected to the DRAM.

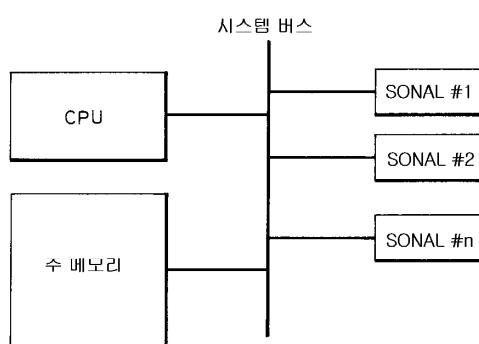

- SONAL (Self-modifying, On-the-fly Alterable Logic):** Represented by a rectangle labeled "SONAL". It has a 1-bit data bus (labeled 1) connected to the DRAM. It also has a 3-bit data bus (labeled 3) connected to the DRAM.

5

6 , 'SONAL' FPGA

7

8 1994 10 7 (pinout) 08/320,058 'PARA

S'

AL' FPGA 7 'SON

, FPGA

'SONAL'

가

가

**22.**

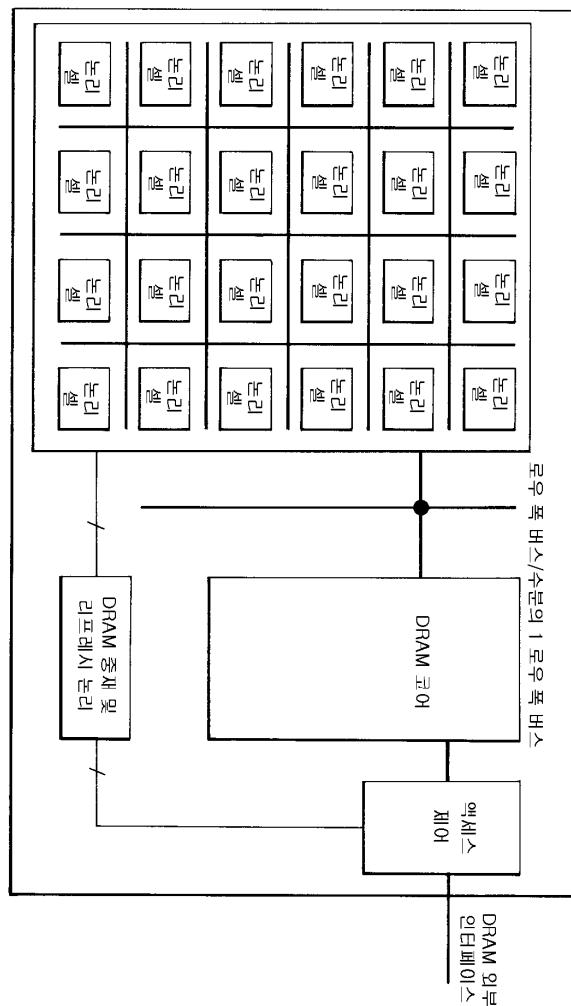

10 , 가 DRAM ,

**23.**

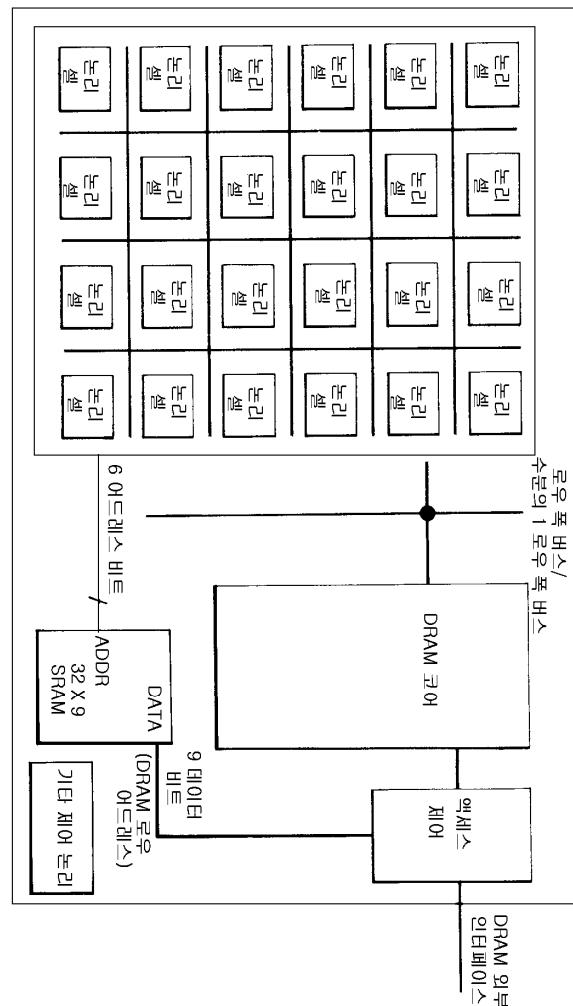

22 , FPGA ,

**24.**

11 , 가 , 가

**25.**

11 , 2 DRAM , 가

**26.**

24 , 가 DRAM ( ) ,

가

1

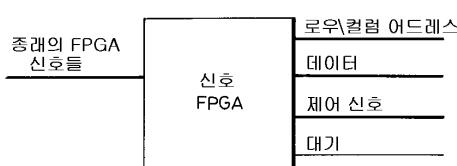

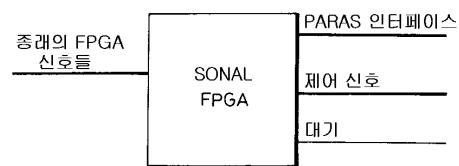

(종래 기술)

2

(종래 기술)

3

(종래 기술)

5

6

7