(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7537377号**

**(P7537377)**

(45)発行日 令和6年8月21日(2024.8.21)

(24)登録日 令和6年8月13日(2024.8.13)

(51)国際特許分類

|        |                  |     |        |       |         |

|--------|------------------|-----|--------|-------|---------|

| H 01 L | 29/78 (2006.01)  | F I | H 01 L | 29/78 | 6 5 2 H |

| H 01 L | 29/12 (2006.01)  |     | H 01 L | 29/78 | 6 5 2 T |

| H 01 L | 29/06 (2006.01)  |     | H 01 L | 29/78 | 6 5 3 A |

| H 01 L | 21/336 (2006.01) |     | H 01 L | 29/78 | 6 5 2 J |

|        |                  |     | H 01 L | 29/78 | 6 5 2 F |

請求項の数 24 (全25頁) 最終頁に続く

(21)出願番号 特願2021-103917(P2021-103917)

(22)出願日 令和3年6月23日(2021.6.23)

(65)公開番号 特開2022-140217(P2022-140217)

A)

(43)公開日 令和4年9月26日(2022.9.26)

審査請求日 令和5年2月1日(2023.2.1)

(31)優先権主張番号 特願2021-39221(P2021-39221)

(32)優先日 令和3年3月11日(2021.3.11)

(33)優先権主張国・地域又は機関

日本国(JP)

(31)優先権主張番号 特願2021-69123(P2021-69123)

(32)優先日 令和3年4月15日(2021.4.15)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74)代理人 110000110

弁理士法人 快友国際特許事務所

高谷 秀史

愛知県刈谷市昭和町1丁目1番地 株式

会社デンソー内

審査官 恩田 和彦

最終頁に続く

(54)【発明の名称】 電界効果トランジスタとその製造方法

**(57)【特許請求の範囲】****【請求項1】**

電界効果トランジスタ(10)であって、

上面にトレンチ(14)が設けられた半導体基板(12)と、

前記トレンチの内面を覆うゲート絶縁膜(16)と、

前記トレンチ内に配置されており、前記ゲート絶縁膜によって前記半導体基板から絶縁

されているゲート電極(18)、

を有し、

前記半導体基板が、

前記トレンチの側面で前記ゲート絶縁膜に接するn型のソース層(30)と、

前記ソース層の下側に位置する前記トレンチの前記側面で前記ゲート絶縁膜に接する

p型のボディ層(34)と、

前記トレンチの下側に配置されており、上側から前記半導体基板を見たときに前記ト

レンチの長手方向に沿って伸びているp型トレンチ下層(35)と、

複数のp型ディープ層(36)と、

複数のn型ディープ層(37)と、

前記各n型ディープ層の下側に配置されており、前記各n型ディープ層に対して下側から接してあり、前記各n型ディープ層よりも濃度が薄いn型のドリフト層(38)、

を有し、

前記各p型ディープ層が、前記ボディ層から下側に突出しており、前記ボディ層から前

記トレンチの底面よりも下側まで伸びており、上側から前記半導体基板を見たときに前記トレンチに対して交差する第1方向に沿って伸びており、上側から前記半導体基板を見たときに前記第1方向に対して直交する第2方向に間隔部を開けて配置されており、前記トレンチの下側に配置されている前記p型トレンチ下層に接しており、

前記各n型ディープ層が、対応する前記間隔部内に配置されており、前記ボディ層の下側に位置する前記トレンチの前記側面で前記ゲート絶縁膜に接しており、

前記各n型ディープ層は、

n型ディープ下層(137A)と、

前記n型ディープ下層の上側に配置されており、前記n型ディープ下層よりも高いn型不純物濃度を有するn型ディープ上層(137B)、

10

を有し、

前記n型ディープ上層は、前記トレンチの底面よりも上側に配置されている、電界効果トランジスタ。

#### 【請求項2】

前記ソース層は、上側から前記半導体基板を見たときに前記トレンチの長手方向に対して平行に伸びている、請求項1に記載の電界効果トランジスタ。

#### 【請求項3】

前記半導体基板が、

前記ボディ層上に設けられており、前記ボディ層よりも高いp型不純物濃度を有するコンタクト層(32)、を有しております、

20

前記コンタクト層は、上側から前記半導体基板を見たときに前記トレンチの長手方向に対して平行に伸びている、請求項1又は2に記載の電界効果トランジスタ。

#### 【請求項4】

前記各p型ディープ層は、

p型ディープ下層(136A)と、

前記p型ディープ下層の上側に配置されており、前記p型ディープ下層よりも高いp型不純物濃度を有するp型ディープ上層(136B)、

を有し、

前記p型ディープ上層は、前記トレンチの底面よりも上側に配置されている、請求項1～3のいずれか一項に記載の電界効果トランジスタ。

30

#### 【請求項5】

対応する前記トレンチの底面から前記各p型トレンチ下層の下面までの深さは、前記半導体基板の上面から前記ボディ層の下面までの深さと一致する、請求項1～4のいずれか一項に記載の電界効果トランジスタ。

#### 【請求項6】

前記p型トレンチ下層は、前記トレンチの底面から離れている、請求項5に記載の電界効果トランジスタ。

#### 【請求項7】

前記p型トレンチ下層は、深さ方向に濃度が異なる複数の部分を有している、請求項5に記載の電界効果トランジスタ。

40

#### 【請求項8】

前記p型トレンチ下層は、

第1p型トレンチ下層(135A)と、

前記第1p型トレンチ下層の上側に配置されている第2p型トレンチ下層(135B)、

を有し、

前記第2p型トレンチ下層は、前記第1p型トレンチ下層よりも濃度が濃い、請求項7に記載の電界効果トランジスタ。

#### 【請求項9】

前記p型トレンチ下層は、

50

第 1 p 型トレンチ下層 ( 1 3 5 A ) と、

前記第 1 p 型トレンチ下層の上側に配置されている第 2 p 型トレンチ下層 ( 1 3 5 B ) 、

を有し、

前記第 2 p 型トレンチ下層は、前記第 1 p 型トレンチ下層よりも濃度が薄い、請求項 7 に記載の電界効果トランジスタ。

**【請求項 1 0】**

前記第 2 p 型トレンチ下層の深さ方向の厚みは、前記ソース層の深さ方向の厚みよりも小さい、請求項 8 又は 9 に記載の電界効果トランジスタ。

**【請求項 1 1】**

前記 p 型トレンチ下層は、前記トレンチの長手方向に沿って分断されており、

前記各 p 型ディープ層は、前記 p 型トレンチ下層の分断された部分を通過する、請求項 1 ~ 1 0 のいずれか一項に記載の電界効果トランジスタ。

**【請求項 1 2】**

前記各 p 型ディープ層の p 型不純物濃度は、前記 n 型ディープ下層に対応する深さ範囲で相対的に濃く、前記 n 型ディープ上層に対応する深さ範囲で相対的に薄い、請求項 1 に記載の電界効果トランジスタ。

**【請求項 1 3】**

電界効果トランジスタ ( 1 0 ) の製造方法であって、

n 型のエピタキシャル層 ( 5 0 ) に複数の p 型ディープ層 ( 3 6 ) と複数の n 型ディープ層 ( 3 7 , 1 3 7 ) を形成するディープ層形成工程であって、前記各 p 型ディープ層が、上側から前記エピタキシャル層を見たときに第 1 方向に沿って伸びており、上側から前記エピタキシャル層を見たときに前記第 1 方向に対して直交する第 2 方向に間隔部を開けて配置されており、前記各 n 型ディープ層が、対応する前記間隔部内に配置されている、ディープ層形成工程と、

前記エピタキシャル層の表面から前記複数の p 型ディープ層と前記複数の n 型ディープ層を超えない深さのトレンチ ( 1 4 ) を形成するトレンチ形成工程であって、前記トレンチは、上側から前記エピタキシャル層を見たときに前記複数の p 型ディープ層と前記複数の n 型ディープ層に交差している、トレンチ形成工程と、

イオン注入技術を利用して、前記エピタキシャル層の表面に向けて p 型不純物を導入し、前記複数の p 型ディープ層と前記複数の n 型ディープ層の上側にボディ層 ( 3 4 ) を形成する、ボディ層形成工程と、

イオン注入技術を利用して、前記トレンチの底面の下側に p 型トレンチ下層 ( 3 5 ) を形成する、 p 型トレンチ下層形成工程、

を有する、電界効果トランジスタの製造方法。

**【請求項 1 4】**

前記ディープ層形成工程では、イオン注入技術を利用して、前記複数の p 型ディープ層と前記複数の n 型ディープ層が、前記エピタキシャル層の表面から離れた所定深さ範囲に n 型不純物と p 型不純物を導入することによって形成される、請求項 1 3 に記載の電界効果トランジスタの製造方法。

**【請求項 1 5】**

前記ボディ層形成工程と前記 p 型トレンチ下層形成工程は、前記トレンチ形成工程の後に同時に実施される、請求項 1 3 又は 1 4 に記載の電界効果トランジスタの製造方法。

**【請求項 1 6】**

イオン注入技術を利用して、前記エピタキシャル層の上層部に n 型不純物を導入し、ソース層 ( 3 0 ) を形成する、ソース層形成工程、をさらに有し、

前記 p 型トレンチ下層は、

第 1 p 型トレンチ下層 ( 1 3 5 A ) と、

前記第 1 p 型トレンチ下層の上側に配置されている第 2 p 型トレンチ下層 ( 1 3 5 B ) 、

10

20

30

40

50

を有し、

前記第2 p型トレンチ下層は、前記第1 p型トレンチ下層よりも濃度が濃く、

前記第2 p型トレンチ下層の深さ方向の厚みは、前記ソース層の深さ方向の厚みよりも小さい、請求項1\_5に記載の電界効果トランジスタの製造方法。

【請求項17】

イオン注入技術を利用して、前記エピタキシャル層の上層部にn型不純物を導入し、ソース層を形成する、ソース層形成工程、をさらに有し、

前記p型トレンチ下層は、

第1 p型トレンチ下層(135A)と、

前記第1 p型トレンチ下層の上側に配置されている第2 p型トレンチ下層(135B)

）、

を有し、

前記第2 p型トレンチ下層は、前記第1 p型トレンチ下層よりも濃度が薄く、

前記第2 p型トレンチ下層の深さ方向の厚みは、前記ソース層の深さ方向の厚みよりも小さい、請求項1\_5に記載の電界効果トランジスタの製造方法。

【請求項18】

前記p型トレンチ下層形成工程は、前記トレンチ形成工程の前に実施され、

前記p型トレンチ下層の幅は、前記トレンチの幅よりも狭い、請求項1\_3又は1\_4に記載の電界効果トランジスタの製造方法。

【請求項19】

前記p型トレンチ下層形成工程は、前記ディープ層形成工程のうちの前記複数のp型ディープ層を形成する工程と同時に実施される、請求項1\_8に記載の電界効果トランジスタの製造方法。

【請求項20】

前記ボディ層形成工程と前記p型トレンチ下層形成工程は、別々に実施される、請求項1\_3又は1\_4に記載の電界効果トランジスタの製造方法。

【請求項21】

電界効果トランジスタ(10)であって、

上面にトレンチ(14)が設けられた半導体基板(12)と、

前記トレンチの内面を覆うゲート絶縁膜(16)と、

前記トレンチ内に配置されており、前記ゲート絶縁膜によって前記半導体基板から絶縁されているゲート電極(18)、

）、

を有し、

前記半導体基板が、

前記トレンチの側面で前記ゲート絶縁膜に接するn型のソース層(30)と、

前記ソース層の下側に位置する前記トレンチの前記側面で前記ゲート絶縁膜に接するp型のボディ層(34)と、

前記トレンチの下側に配置されており、上側から前記半導体基板を見たときに前記トレンチの長手方向に沿って伸びているp型トレンチ下層(35)と、

複数のp型ディープ層(36)と、

複数のn型ディープ層(37)、

を有し、

前記各p型ディープ層が、前記ボディ層から下側に突出しており、前記ボディ層から前記トレンチの底面よりも下側まで伸びており、上側から前記半導体基板を見たときに前記トレンチに対して交差する第1方向に沿って伸びており、上側から前記半導体基板を見たときに前記第1方向に対して直交する第2方向に間隔部を開けて配置されており、前記トレンチの下側に配置されている前記p型トレンチ下層に接しており、

前記各n型ディープ層が、対応する前記間隔部内に配置されており、前記ボディ層の下側に位置する前記トレンチの前記側面で前記ゲート絶縁膜に接しており、

前記各p型ディープ層は、

10

20

30

40

50

p型ディープ下層(136A)と、

前記p型ディープ下層の上側に配置されており、前記p型ディープ下層よりも高いp型不純物濃度を有するp型ディープ上層(136B)、

を有し、

前記p型ディープ上層は、前記トレンチの底面よりも上側に配置されている、電界効果トランジスタ。

【請求項22】

電界効果トランジスタ(10)であって、

上面にトレンチ(14)が設けられた半導体基板(12)と、

前記トレンチの内面を覆うゲート絶縁膜(16)と、

前記トレンチ内に配置されており、前記ゲート絶縁膜によって前記半導体基板から絶縁されているゲート電極(18)、

を有し、

前記半導体基板が、

前記トレンチの側面で前記ゲート絶縁膜に接するn型のソース層(30)と、

前記ソース層の下側に位置する前記トレンチの前記側面で前記ゲート絶縁膜に接するp型のボディ層(34)と、

前記トレンチの下側に配置されており、上側から前記半導体基板を見たときに前記トレンチの長手方向に沿って伸びているp型トレンチ下層(35)と、

複数のp型ディープ層(36)と、

複数のn型ディープ層(37)、

を有し、

前記各p型ディープ層が、前記ボディ層から下側に突出しており、前記ボディ層から前記トレンチの底面よりも下側まで伸びており、上側から前記半導体基板を見たときに前記トレンチに対して交差する第1方向に沿って伸びており、上側から前記半導体基板を見たときに前記第1方向に対して直交する第2方向に間隔部を開けて配置されており、前記トレンチの下側に配置されている前記p型トレンチ下層に接しており、

前記各n型ディープ層が、対応する前記間隔部内に配置されており、前記ボディ層の下側に位置する前記トレンチの前記側面で前記ゲート絶縁膜に接しており、

対応する前記トレンチの底面から前記各p型トレンチ下層の下面までの深さは、前記半導体基板の上面から前記ボディ層の下面までの深さと一致する、電界効果トランジスタ。

【請求項23】

電界効果トランジスタ(10)であって、

上面にトレンチ(14)が設けられた半導体基板(12)と、

前記トレンチの内面を覆うゲート絶縁膜(16)と、

前記トレンチ内に配置されており、前記ゲート絶縁膜によって前記半導体基板から絶縁されているゲート電極(18)、

を有し、

前記半導体基板が、

前記トレンチの側面で前記ゲート絶縁膜に接するn型のソース層(30)と、

前記ソース層の下側に位置する前記トレンチの前記側面で前記ゲート絶縁膜に接するp型のボディ層(34)と、

前記トレンチの下側に配置されており、上側から前記半導体基板を見たときに前記トレンチの長手方向に沿って伸びているp型トレンチ下層(35)と、

複数のp型ディープ層(36)と、

複数のn型ディープ層(37)、

を有し、

前記各p型ディープ層が、前記ボディ層から下側に突出しており、前記ボディ層から前記トレンチの底面よりも下側まで伸びており、上側から前記半導体基板を見たときに前記トレンチに対して交差する第1方向に沿って伸びており、上側から前記半導体基板を見た

10

20

30

40

50

ときに前記第1方向に対して直交する第2方向に間隔部を開けて配置されており、前記トレンチの下側に配置されている前記p型トレンチ下層に接しており、

前記各n型ディープ層が、対応する前記間隔部内に配置されており、前記ボディ層の下側に位置する前記トレンチの前記側面で前記ゲート絶縁膜に接しており、

前記p型トレンチ下層は、前記トレンチの長手方向に沿って分断されており、

前記各p型ディープ層は、前記p型トレンチ下層の分断された部分を通過する、電界効果トランジスタ。

#### 【請求項24】

電界効果トランジスタ(10)であって、

上面にトレンチ(14)が設けられた半導体基板(12)と、

10

前記トレンチの内面を覆うゲート絶縁膜(16)と、

前記トレンチ内に配置されており、前記ゲート絶縁膜によって前記半導体基板から絶縁されているゲート電極(18)、

を有し、

前記半導体基板が、

前記トレンチの側面で前記ゲート絶縁膜に接するn型のソース層(30)と、

前記ソース層の下側に位置する前記トレンチの前記側面で前記ゲート絶縁膜に接するp型のボディ層(34)と、

前記トレンチの下側に配置されており、上側から前記半導体基板を見たときに前記トレンチの長手方向に沿って伸びているp型トレンチ下層(35)と、

20

複数のp型ディープ層(36)と、

複数のn型ディープ層(37)、

を有し、

前記各p型ディープ層が、前記ボディ層から下側に突出しており、前記ボディ層から前記トレンチの底面よりも下側まで伸びており、上側から前記半導体基板を見たときに前記トレンチに対して交差する第1方向に沿って伸びており、上側から前記半導体基板を見たときに前記第1方向に対して直交する第2方向に間隔部を開けて配置されており、前記トレンチの下側に配置されている前記p型トレンチ下層に接しており、

前記各n型ディープ層が、対応する前記間隔部内に配置されており、前記ボディ層の下側に位置する前記トレンチの前記側面で前記ゲート絶縁膜に接しており、

前記各n型ディープ層は、

n型ディープ下層(137A)と、

30

前記n型ディープ下層の上側に配置されており、前記n型ディープ下層よりも高いn型不純物濃度を有するn型ディープ上層(137B)、

を有し、

前記n型ディープ上層は、前記トレンチの底面よりも上側に配置されており、

前記各p型ディープ層のp型不純物濃度は、前記n型ディープ下層に対応する深さ範囲で相対的に濃く、前記n型ディープ上層に対応する深さ範囲で相対的に薄い、電界効果トランジスタ。

#### 【発明の詳細な説明】

40

#### 【技術分野】

#### 【0001】

本明細書に開示の技術は、電界効果トランジスタとその製造方法に関する。

#### 【0002】

特許文献1には、トレンチゲート型の電界効果トランジスタが開示されている。この電界効果トランジスタは、ボディ層から下側に突出する複数のp型ディープ層を有している。各p型ディープ層は、上側から半導体基板を見たときにトレンチに対して交差するよう伸びている。複数のp型ディープ層は、その幅方向に間隔部を開けて配置されている。各p型ディープ層は、ボディ層からトレンチの底面よりも下側まで伸びている。特許文献1に開示の電界効果トランジスタの一例では、各p型ディープ層は、ボディ層の下側に位

50

置するトレンチの側面及びトレンチの底面でゲート絶縁膜に接している。また、電界効果トランジスタは、ボディ層及び各 p 型ディープ層に接する n 型のドリフト層を有している。この電界効果トランジスタがオフすると、ボディ層からドリフト層内に空乏層が広がる。ドリフト層内に広がる空乏層によって、ソース - ドレイン間の電圧が保持される。また、この電界効果トランジスタがオフすると、各ディープ p 層からもドリフト層内に空乏層が広がる。各ディープ p 層がトレンチの底面でゲート絶縁膜に接しているので、各ディープ p 層から広がる空乏層によってトレンチの底面の周辺のドリフト層が空乏化される。このように、各ディープ p 層からトレンチの底面の周辺に広がる空乏層によって、トレンチの底面の周辺のゲート絶縁膜及びドリフト層で電界集中が生じることが抑制される。したがって、この電界効果トランジスタは、高い耐圧を有する。

10

**【先行技術文献】**

**【特許文献】**

**【0003】**

**【文献】特開2009-194065号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

このような複数の p 型ディープ層を有する電界効果トランジスタでは、トレンチの底面の周辺のゲート絶縁膜における電界集中をさらに緩和し、高耐圧化するための技術が必要である。本明細書では、複数の p 型ディープ層を有する電界効果トランジスタにおいて、

高耐圧化を実現する技術を提案する。

20

**【課題を解決するための手段】**

**【0005】**

本明細書が開示する電界効果トランジスタ(10)は、上面にトレンチ(14)が設けられた半導体基板(12)と、前記トレンチの内面を覆うゲート絶縁膜(16)と、前記トレンチ内に配置されており、前記ゲート絶縁膜によって前記半導体基板から絶縁されているゲート電極(18)、を有することができる。前記半導体基板が、前記トレンチの側面で前記ゲート絶縁膜に接する n 型のソース層(30)と、前記ソース層の下側に位置する前記トレンチの前記側面で前記ゲート絶縁膜に接する p 型のボディ層(34)と、前記トレンチの下側に配置されており、上側から前記半導体基板を見たときに前記トレンチの長手方向に沿って伸びている p 型トレンチ下層(35)と、複数の p 型ディープ層(36)と、複数の n 型ディープ層(37)を有することができる。前記各 p 型ディープ層が、前記ボディ層から下側に突出しており、前記ボディ層から前記トレンチの底面よりも下側まで伸びており、上側から前記半導体基板を見たときに前記トレンチに対して交差する第 1 方向に沿って伸びてあり、上側から前記半導体基板を見たときに前記第 1 方向に対して直交する第 2 方向に間隔部を開けて配置されており、前記トレンチの下側に配置されている前記 p 型トレンチ下層に接している。前記各 n 型ディープ層が、対応する前記間隔部内に配置されており、前記ボディ層の下側に位置する前記トレンチの前記側面で前記ゲート絶縁膜に接している。

30

**【0006】**

この電界効果トランジスタは、トレンチの下側に配置されている p 型トレンチ下層を有している。このため、電界効果トランジスタがオフするときにトレンチの底面の周辺の電界集中が緩和される。この結果、この電界効果トランジスタは、高い耐圧を有することができる。さらに、この電界効果トランジスタでは、 p 型トレンチ下層が複数の p 型ディープ層を介してボディ層に電気的に接続されている。このため、 p 型トレンチ下層の電位が安定し、この電界効果トランジスタのスイッチング特性が悪化することが抑えられている。このように、この電界効果トランジスタでは、 p 型トレンチ下層と複数の p 型ディープ層を組合せたことにより、スイッチング特性の悪化を抑えながら、耐圧を改善することができる。

40

**【0007】**

50

本明細書が開示する電界効果トランジスタ(10)の製造方法は、n型のエピタキシャル層(50)に複数のp型ディープ層(36)と複数のn型ディープ層(37)を形成するディープ層形成工程であって、前記各p型ディープ層が、上側から前記エピタキシャル層を見たときに第1方向に沿って伸びており、上側から前記エピタキシャル層を見たときに前記第1方向に対して直交する第2方向に間隔部を開けて配置されており、前記各n型ディープ層が、対応する前記間隔部内に配置されている、ディープ層形成工程と、前記エピタキシャル層の表面から前記複数のp型ディープ層と前記複数のn型ディープ層に交差している、トレンチ形成工程と、イオン注入技術を利用して、前記エピタキシャル層の表面に向けてp型不純物を導入し、前記複数のp型ディープ層と前記複数のn型ディープ層の上側にボディ層(34)を形成するボディ層形成工程と、イオン注入技術を利用して、前記トレンチの底面の下側にp型トレンチ下層(35)を形成する、p型トレンチ下層形成工程、を有することができる。

#### 【0008】

この電界効果トランジスタの製造方法によると、p型トレンチ下層と複数のp型ディープ層を有する電界効果トランジスタを製造することができる。

#### 【図面の簡単な説明】

#### 【0009】

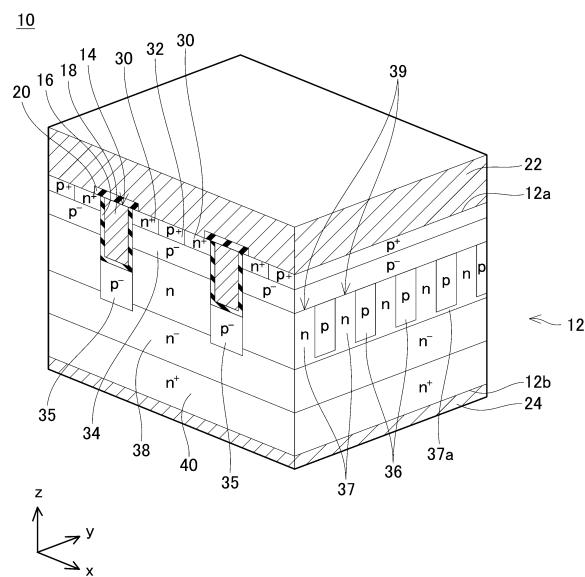

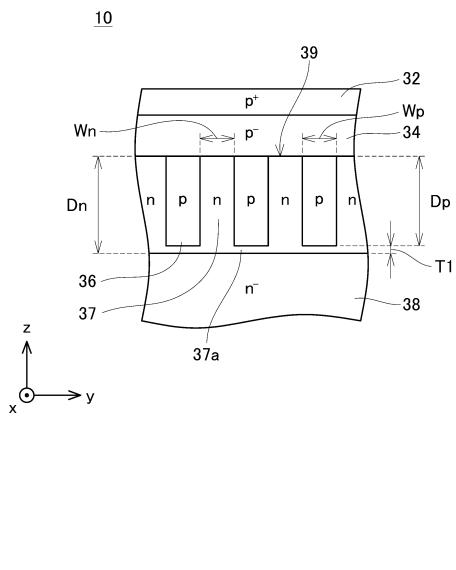

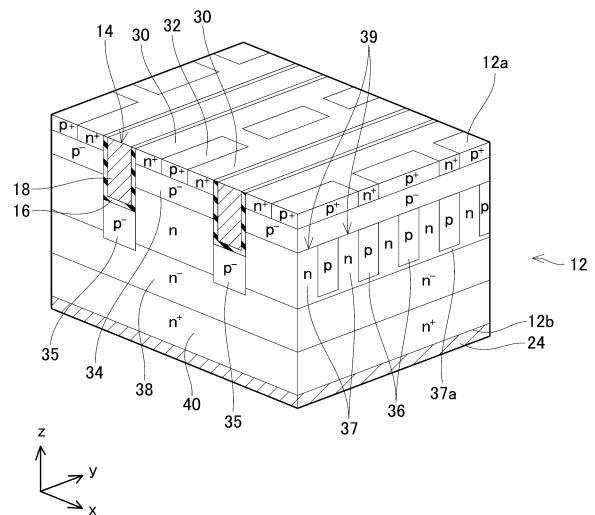

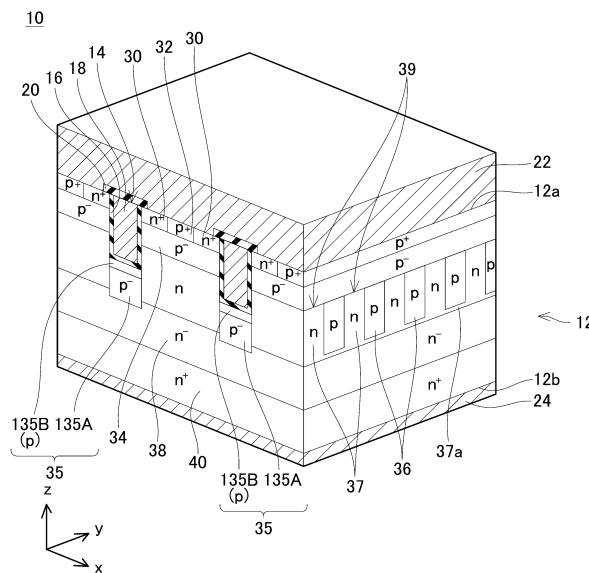

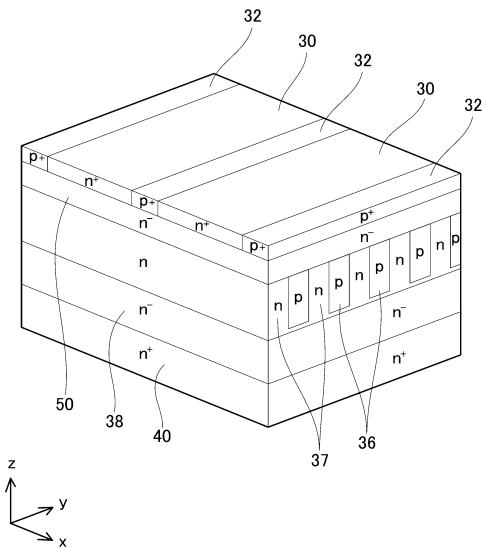

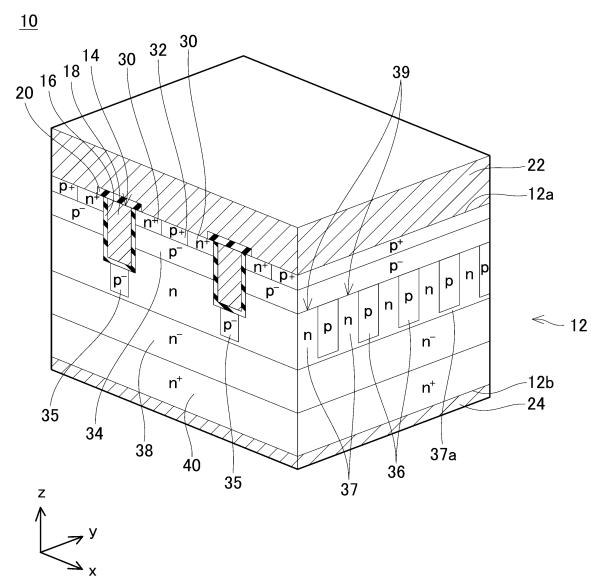

【図1】MOSFET10の断面斜視図(p型ディープ層36を含まないxz断面を示す図)。

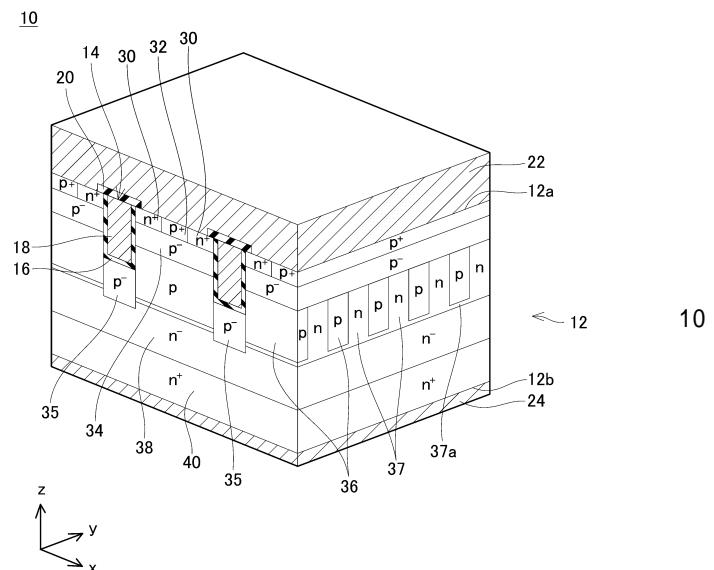

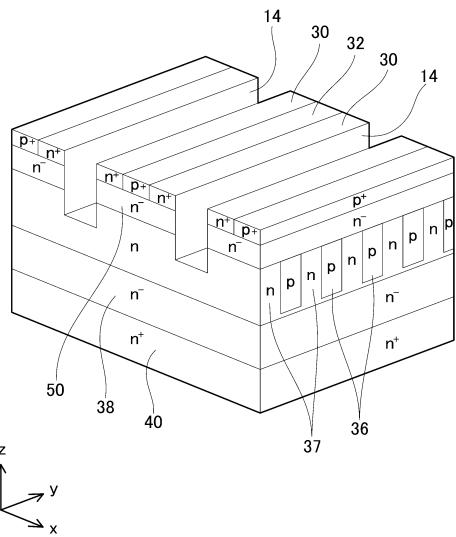

【図2】ソース電極22と層間絶縁膜20を省略したMOSFET10の断面斜視図(p型ディープ層36を含まないxz断面を示す図)。

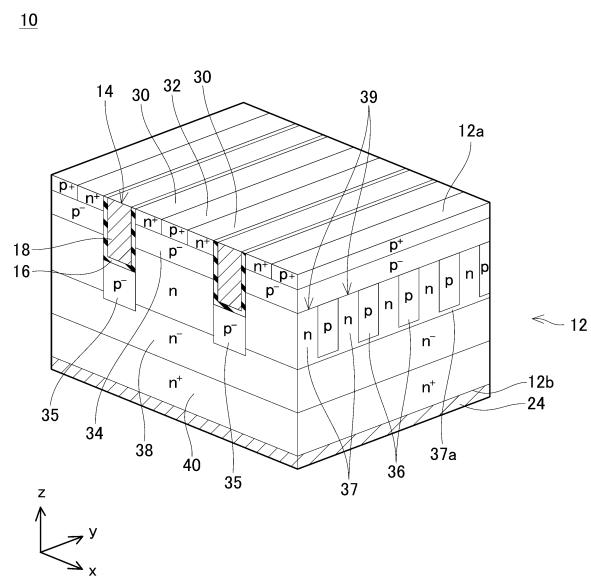

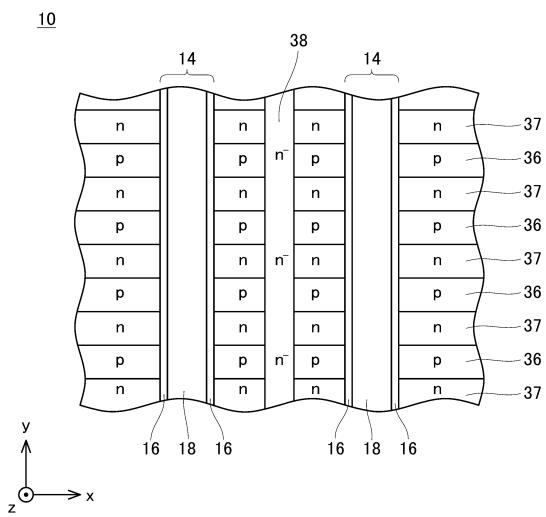

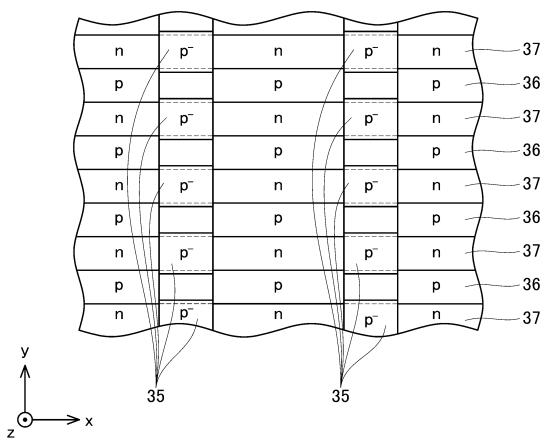

【図3】p型トレンチ下層35、p型ディープ層36及びn型ディープ層37を含む拡大xy断面であって、半導体基板12を上から見たときのp型トレンチ下層35、p型ディープ層36及びn型ディープ層37の配置を示すMOSFET10の拡大断面図。

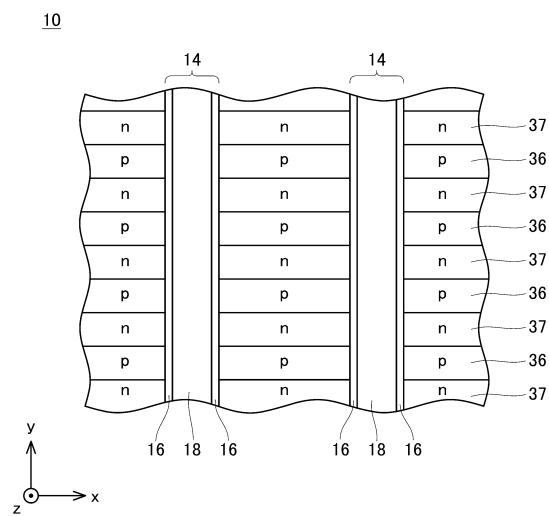

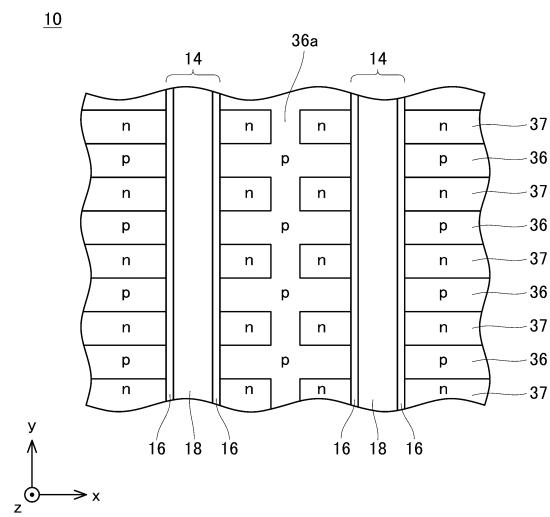

【図4】トレンチ14、p型ディープ層36及びn型ディープ層37を含む拡大xy断面であって、半導体基板12を上から見たときのトレンチ14、p型ディープ層36及びn型ディープ層37の配置を示すMOSFET10の拡大断面図。

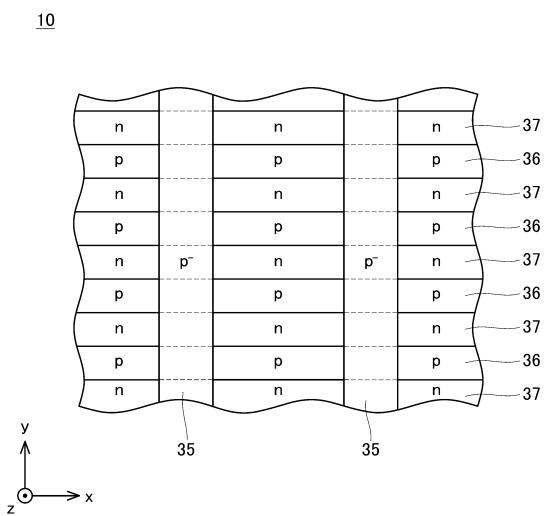

【図5】p型ディープ層36及びn型ディープ層37を含むMOSFET10の拡大yz断面図。

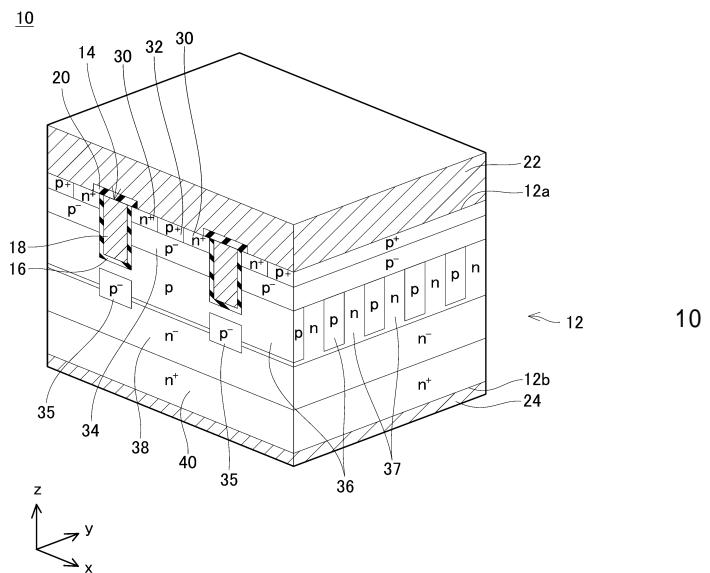

【図6】MOSFET10の断面斜視図(p型ディープ層36を含むxz断面を示す図)。

【図7】トレンチ14、p型ディープ層36及びn型ディープ層37を含む拡大xy断面であって、半導体基板12を上から見たときのトレンチ14とp型ディープ層36及びn型ディープ層37の配置を示すMOSFET10の変形例の拡大断面図。

【図8】トレンチ14、p型ディープ層36及びn型ディープ層37を含む拡大xy断面であって、半導体基板12を上から見たときのトレンチ14とp型ディープ層36及びn型ディープ層37の配置を示すMOSFET10の変形例の拡大断面図。

【図9】p型トレンチ下層35、p型ディープ層36及びn型ディープ層37を含む拡大xy断面であって、半導体基板12を上から見たときのp型トレンチ下層35、p型ディープ層36及びn型ディープ層37の配置を示すMOSFET10の変形例の拡大断面図。

【図10】ソース電極22と層間絶縁膜20を省略したMOSFET10の変形例の断面斜視図(p型ディープ層36を含まないxz断面を示す図)。

【図11】MOSFET10の変形例の断面斜視図(p型ディープ層36を含まないxz断面を示す図)。

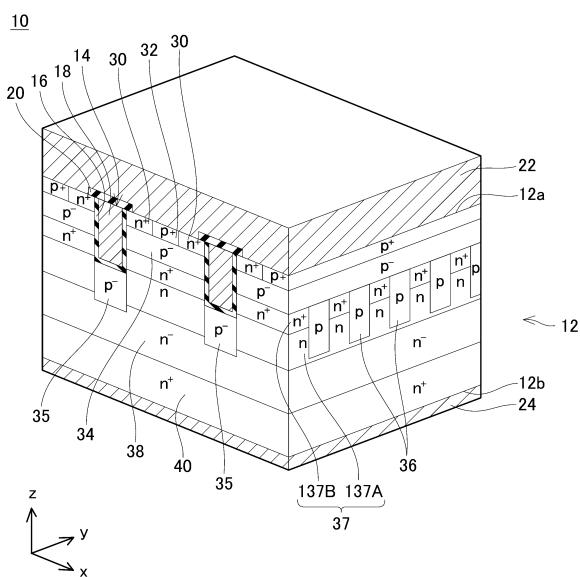

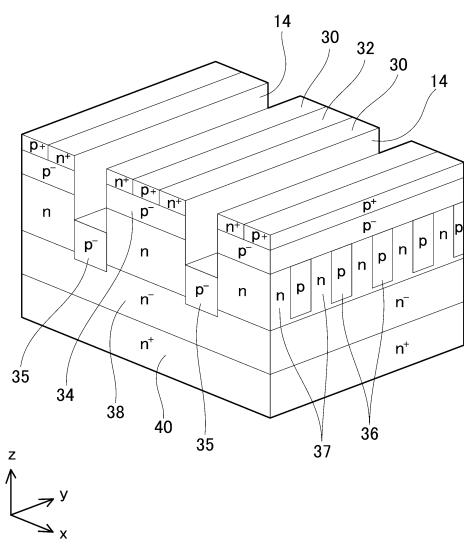

【図12】MOSFET10の変形例の断面斜視図(p型ディープ層36を含むxz断面を示す図)。

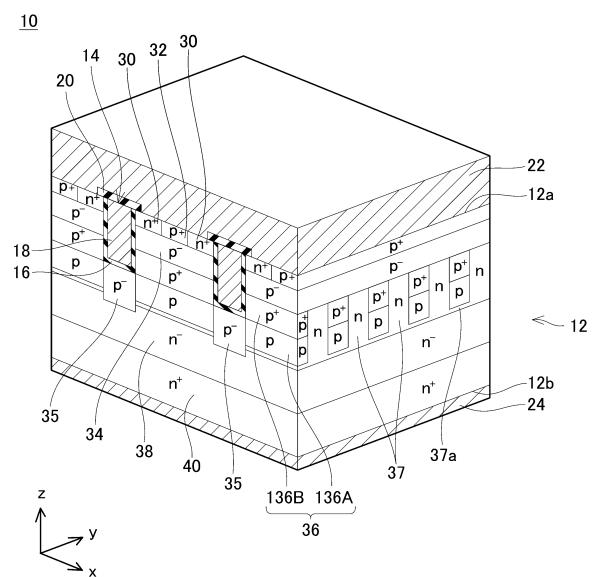

【図13】MOSFET10の変形例の断面斜視図(p型ディープ層36を含まないxz断面を示す図)。

【図14】MOSFET10の変形例の断面斜視図(p型ディープ層36を含むxz断面

を示す図)。

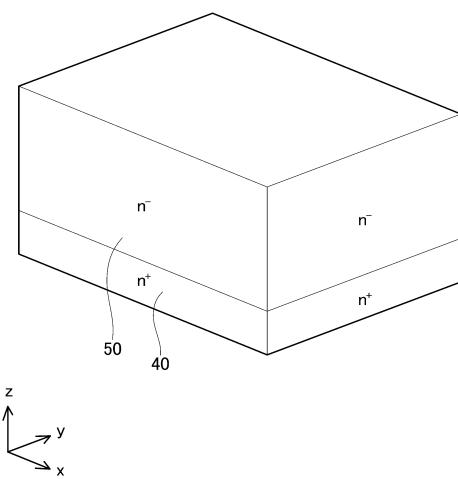

【図15】MOSFET10の製造方法の説明図。

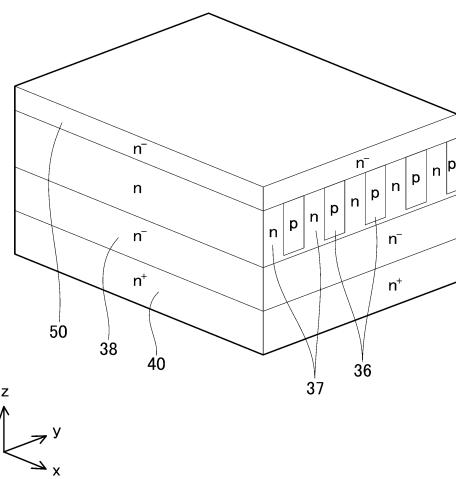

【図16】MOSFET10の製造方法の説明図。

【図17】MOSFET10の製造方法の説明図。

【図18】MOSFET10の製造方法の説明図。

【図19】MOSFET10の製造方法の説明図。

【図20】MOSFET10の変形例の断面斜視図(p型ディープ層36を含まないxz断面を示す図)。

【発明を実施するための形態】

【0010】

図1、2に示す実施形態のMOSFET10(metal-oxide-semiconductor field effect transistor)は、半導体基板12を有している。以下では、半導体基板12の厚み方向をz方向といい、半導体基板12の上面12aに平行な一方( z方向に直交する一方)をx方向といい、x方向及びz方向に直交する方向をy方向という。半導体基板12は、炭化シリコン(すなわち、SiC)により構成されている。なお、半導体基板12がシリコン、窒化ガリウム等の他の半導体材料により構成されていてもよい。半導体基板12の上面12aには、複数のトレンチ14が設けられている。図2に示すように、複数のトレンチ14は、上面12aにおいて、y方向に沿って長く伸びている。複数のトレンチ14は、x方向に間隔を開けて配置されている。

【0011】

図1、2に示すように、各トレンチ14の内面(すなわち、側面と底面)は、ゲート絶縁膜16によって覆われている。各トレンチ14内に、ゲート電極18が配置されている。各ゲート電極18は、ゲート絶縁膜16によって半導体基板12から絶縁されている。図1に示すように、各ゲート電極18の上面は、層間絶縁膜20によって覆われている。半導体基板12の上部に、ソース電極22が設けられている。ソース電極22は、各層間絶縁膜20を覆っている。ソース電極22は、層間絶縁膜20によってゲート電極18から絶縁されている。ソース電極22は、層間絶縁膜20が存在しない位置で、半導体基板12の上面12aに接している。半導体基板12の下部には、ドレイン電極24が配置されている。ドレイン電極24は、半導体基板12の下面12bの全域に接している。

【0012】

図1、2に示すように、半導体基板12は、複数のソース層30、複数のコンタクト層32、ボディ層34、複数のp型トレンチ下層35、複数のp型ディープ層36、複数のn型ディープ層37、ドリフト層38、及び、ドレイン層40を有している。

【0013】

各ソース層30は、高いn型不純物濃度を有するn型層である。各ソース層30は、半導体基板12の上面12aを部分的に含む範囲に配置されている。各ソース層30は、ソース電極22にオーミック接触している。各ソース層30は、トレンチ14の側面の最上部において、ゲート絶縁膜16に接している。各ソース層30は、ゲート絶縁膜16を介してゲート電極18に対向している。各ソース層30はトレンチ14の側面に沿ってy方向に長く伸びている。即ち、各ソース層30は、上側から半導体基板12を見たときに、トレンチ14の長手方向に対して平行に伸びており、トレンチ14の長手方向の一方の端部から他方の端部まで伸びている。

【0014】

各コンタクト層32は、高いp型不純物濃度を有するp型層である。各コンタクト層32は、半導体基板12の上面12aを部分的に含む範囲に配置されている。各コンタクト層32は、対応する2つのソース層30の間に配置されている。各コンタクト層32は、ソース電極22にオーミック接触している。各コンタクト層32は、y方向に長く伸びている。即ち、各コンタクト層32は、上側から半導体基板12を見たときに、トレンチ14の長手方向に対して平行に伸びており、トレンチ14の長手方向の一方の端部から他方の端部まで伸びている。

10

20

30

40

50

**【 0 0 1 5 】**

ボディ層 3 4 は、コンタクト層 3 2 よりも低い p 型不純物濃度を有する p 型層である。ボディ層 3 4 は、複数のソース層 3 0 及び複数のコンタクト層 3 2 の下側に配置されている。ボディ層 3 4 は、複数のソース層 3 0 及び複数のコンタクト層 3 2 に対して下側から接している。ボディ層 3 4 は、ソース層 3 0 の下側に位置するトレンチ 1 4 の側面で、ゲート絶縁膜 1 6 に接している。ボディ層 3 4 は、ゲート絶縁膜 1 6 を介してゲート電極 1 8 に対向している。

**【 0 0 1 6 】**

各 p 型トレンチ下層 3 5 は、対応するトレンチ 1 4 の下側に配置されている p 型層である。後述するように、各 p 型トレンチ下層 3 5 は、ボディ層 3 4 と共にイオン注入工程で形成されてもよい。この場合、各 p 型トレンチ下層 3 5 とボディ層 3 4 の p 型不純物の深さ方向の濃度プロファイルは一致しており、対応するトレンチ 1 4 の底面から各 p 型トレンチ下層 3 5 の下面までの深さは、半導体基板 1 2 の上面 1 2 a からボディ層 3 4 の下面までの深さと一致する。この例では、各 p 型トレンチ下層 3 5 は、対応するトレンチ 1 4 の底面を被覆するゲート絶縁膜 1 6 に接している。図 3 に示すように、半導体基板 1 2 を上側から見たときに、各 p 型トレンチ下層 3 5 は、対応するトレンチ 1 4 の長手方向（この例では y 方向）に沿って長く伸びており、トレンチ 1 4 の長手方向の一方端から他方端まで連続して伸びてもよい。後述するように、各 p 型トレンチ下層 3 5 は、対応するトレンチ 1 4 の長手方向（この例では y 方向）に沿って長く伸びており、トレンチ 1 4 の長手方向の一方端から他方端の間で分断してもよい。

10

**【 0 0 1 7 】**

各 p 型ディープ層 3 6 は、ボディ層 3 4 の下面から下側に突出している p 型層である。各 p 型ディープ層 3 6 の p 型不純物濃度は、ボディ層 3 4 の p 型不純物濃度よりも高く、コンタクト層 3 2 の p 型不純物濃度よりも低い。図 4 に示すように半導体基板 1 2 を上側から見たときに、各 p 型ディープ層 3 6 は、x 方向に長く伸びており、トレンチ 1 4 の長手方向（この例では、y 方向）に対して直交している。複数の p 型ディープ層 3 6 は、y 方向に間隔を開けて配置されている。以下では、複数の p 型ディープ層 3 6 の間の部分を、間隔部 3 9（図 1 及び図 2 参照）という。図 5 に示すように、p 型ディープ層 3 6 は、y z 断面において、z 方向に長い形状を有している。すなわち、p 型ディープ層 3 6 の z 方向における寸法（以下、深さ D p という）は、p 型ディープ層 3 6 の y 方向における寸法（以下、幅 W p という）よりも大きい。例えば、深さ D p を、幅 W p の 1 ~ 4 倍とすることができる。図 6 に示すように、各 p 型ディープ層 3 6 は、ボディ層 3 4 の下面から各トレンチ 1 4 の底面よりも下側の深さまで伸びている。各 p 型ディープ層 3 6 は、ボディ層 3 4 の下側に位置するトレンチ 1 4 の側面でゲート絶縁膜 1 6 に接している。また、図 3 に示すように、各 p 型ディープ層 3 6 は、トレンチ 1 4 の下側に配置されている p 型トレンチ下層 3 5 に交差するように接している。

20

30

**【 0 0 1 8 】**

各 n 型ディープ層 3 7 は、ドリフト層 3 8 よりも n 型不純物濃度が高い n 型層である。各 n 型ディープ層 3 7 の n 型不純物濃度は、各 p 型ディープ層 3 6 の p 型不純物濃度よりも低い。なお、この例に代えて、各 n 型ディープ層 3 7 は、ドリフト層 3 8 の n 型不純物濃度と同一濃度であってもよい。図 1、2 に示すように、各 n 型ディープ層 3 7 は、対応する間隔部 3 9 内に配置されている。各 n 型ディープ層 3 7 は、ボディ層 3 4 の下面に接している。各 n 型ディープ層 3 7 は、その両側の p 型ディープ層 3 6 の側面に接している。各 n 型ディープ層 3 7 は、ボディ層 3 4 の下面から各トレンチ 1 4 の底面及び各 p 型ディープ層 3 6 の下面よりも下側まで伸びている。図 5 に示すように、間隔部 3 9 内の n 型ディープ層 3 7 は、y z 断面において、z 方向に長い形状を有している。すなわち、n 型ディープ層 3 7 の z 方向における寸法（以下、深さ D n という）は、間隔部 3 9 内の n 型ディープ層 3 7 の y 方向における寸法（以下、幅 W n という）よりも大きい。例えば、深さ D n を、幅 W n の 1 ~ 4 倍とすることができる。本実施形態では、n 型ディープ層 3 7 の幅 W n は、p 型ディープ層 3 6 の幅 W p と略等しい。各 n 型ディープ層 3 7 は、隣接す

40

50

る p 型ディープ層 3 6 の下面の直下まで伸びる接続領域 3 7 a を有している。各接続領域 3 7 a は、対応する p 型ディープ層 3 6 の下面に接している。各 n 型ディープ層 3 7 は、各接続領域 3 7 a を介して互いに繋がっている。n 型ディープ層 3 7 が p 型ディープ層 3 6 の下面よりも下側に突出する部分の厚み T 1 ( すなわち、p 型ディープ層 3 6 の下面から n 型ディープ層 3 7 下面までの z 方向における距離 ) は、約 0 . 1  $\mu\text{m}$  であり、極めて薄い。図 1、2 に示すように、各 n 型ディープ層 3 7 は、各間隔部 3 9 内において、ボディ層 3 4 の下側に位置するトレンチ 1 4 の側面でゲート絶縁膜 1 6 に接している。また、図 3 に示すように、各 n 型ディープ層 3 7 は、トレンチ 1 4 の下側に配置されている p 型トレンチ下層 3 5 に交差するように接している。

## 【 0 0 1 9 】

10

ドリフト層 3 8 は、各 n 型ディープ層 3 7 よりも低い n 型不純物濃度を有する n 型層である。ドリフト層 3 8 は、n 型ディープ層 3 7 の下側に配置されている。ドリフト層 3 8 は、n 型ディープ層 3 7 に対して下側から接している。

## 【 0 0 2 0 】

ドレイン層 4 0 は、ドリフト層 3 8 及び n 型ディープ層 3 7 よりも高い n 型不純物濃度を有する n 型層である。ドレイン層 4 0 は、ドリフト層 3 8 に対して下側から接している。ドレイン層 4 0 は、半導体基板 1 2 の下面 1 2 b を含む範囲に配置されている。ドレイン層 4 0 は、ドレイン電極 2 4 にオーミック接触している。

## 【 0 0 2 1 】

20

次に、MOSFET 1 0 の動作について説明する。MOSFET 1 0 は、ドレイン電極 2 4 にソース電極 2 2 よりも高い電位が印加された状態で使用される。各ゲート電極 1 8 にゲート閾値以上の電位が印加されると、ゲート絶縁膜 1 6 の近傍のボディ層 3 4 にチャネルが形成される。チャネルによって、ソース層 3 0 と n 型ディープ層 3 7 が接続される。このため、ソース層 3 0 からチャネル、n 型ディープ層 3 7 、及び、ドリフト層 3 8 を経由してドレイン層 4 0 へ電子が流れる。すなわち、MOSFET 1 0 がオンする。各ゲート電極 1 8 の電位をゲート閾値以上の値からゲート閾値未満の値へ引き下げると、チャネルが消失し、電子の流れが停止する。すなわち、MOSFET 1 0 がオフする。

## 【 0 0 2 2 】

次に、MOSFET 1 0 をオフするときの動作について、より詳細に説明する。チャネルが消失すると、ボディ層 3 4 と各 n 型ディープ層 3 7 の界面の p-n 接合に逆電圧が印加される。したがって、ボディ層 3 4 から各 n 型ディープ層 3 7 へ空乏層が広がる。また、各 p 型ディープ層 3 6 は、ボディ層 3 4 と電気的に接続されており、ボディ層 3 4 と略同じ電位を有する。したがって、チャネルが消失すると、各 p 型ディープ層 3 6 と各 n 型ディープ層 3 7 の界面の p-n 接合にも逆電圧が印加される。したがって、各 p 型ディープ層 3 6 から各 n 型ディープ層 3 7 へも空乏層が広がる。さらに、各 p 型トレンチ下層 3 5 は、各 p 型ディープ層 3 6 を介してボディ層 3 4 と電気的に接続されており、ボディ層 3 4 と略同じ電位を有する。したがって、チャネルが消失すると、各 p 型トレンチ下層 3 5 と各 n 型ディープ層 3 7 の界面の p-n 接合にも逆電圧が印加される。このように、各 n 型ディープ層 3 7 は、ボディ層 3 4 と各 p 型トレンチ下層 3 5 と各 p 型ディープ層 3 6 から広がる空乏層によって素早く空乏化される。特に、各 p 型トレンチ下層 3 5 が対応するトレンチ 1 4 の下側に設けられているので、トレンチ 1 4 の底面の周辺が良好に空乏化される。これによって、トレンチ 1 4 の底面近傍における電界集中が大幅に緩和される。また、ボディ層 3 4 と各 p 型トレンチ下層 3 5 と各 p 型ディープ層 3 6 から広がる空乏層によって、各 n 型ディープ層 3 7 の全体が空乏化される。なお、各 n 型ディープ層 3 7 はドリフト層 3 8 よりも n 型不純物濃度が高いため、各 n 型ディープ層 3 7 内にはドリフト層 3 8 内よりも空乏層が広がり難い。しかしながら、各 n 型ディープ層 3 7 は p 型ディープ層 3 6 によって挟まれてあり、かつ、各 n 型ディープ層 3 7 の幅 Wn が狭いので、各 n 型ディープ層 3 7 の全体が空乏化する。また、空乏層は、各 n 型ディープ層 3 7 を介してドリフト層 3 8 へ広がる。ドリフト層 3 8 の n 型不純物濃度が低いので、ドリフト層 3 8 のほぼ全体が空乏化される。空乏化されたドリフト層 3 8 及び各 n 型ディープ層 3 7 によって、

30

40

50

ドレイン電極 24 とソース電極 22 の間に印加される高電圧が保持される。したがって、MOSFET 10 は高い耐圧を有する。

#### 【0023】

また、MOSFET 10 では、p 型トレンチ下層 35 が p 型ディープ層 36 を介してボディ層 34 に電気的に接続されている。このため、p 型トレンチ下層 35 の電位が安定し、この MOSFET 10 のスイッチング特性が悪化することが抑えられる。このように、この MOSFET 10 では、p 型トレンチ下層 35 と p 型ディープ層の組合せによりスイッチング特性の悪化を抑えながら、耐圧を改善することができる。

#### 【0024】

また、MOSFET 10 では、p 型トレンチ下層 35 がトレンチ 14 の底面を被覆するゲート絶縁膜 16 に接している。このため、ゲート電極 18 とドレイン電極 24 の間の静電容量（すなわち、帰還容量）が小さくなる。さらに、MOSFET 10 では、各 n 型ディープ層 37 と各 p 型ディープ層 36 が縦に長い形状を有している。このように各 n 型ディープ層 37 と各 p 型ディープ層 36 が構成されると、帰還容量が小さくなる。これらによって、MOSFET 10 のスイッチング速度を向上させることができる。

10

#### 【0025】

また、MOSFET 10 では、p 型トレンチ下層 35 の深さが p 型ディープ層 36 及び n 型ディープ層 37 の深さよりも深い。このような深い p 型トレンチ下層 35 が設けられると、n 型ディープ層 37 及びドリフト層 38 の空乏化を促進することができるので、MOSFET 10 の耐圧が改善される。また、このような深い p 型トレンチ下層 35 が設けられると、過電圧が印加されたときに下方に突出する p 型トレンチ下層 35 でブレークダウンが生じるので、セル領域で確実にブレークダウンを生じさせることができ。この結果、MOSFET 10 もアバランシェ耐量が安定することができる。なお、p 型トレンチ下層 35 の深さが p 型ディープ層 36 及び n 型ディープ層 37 の深さよりも浅くてもよい。この場合、p 型トレンチ下層 35 から伸びる空乏層が抑えられるので、MOSFET 10 のオン抵抗が改善される。

20

#### 【0026】

なお、MOSFET 10 では、図 4 に示されるように、上側から半導体基板 12 を見たときに、各 p 型ディープ層 36 及び各 n 型ディープ層 37 が x 方向に連続して長く伸びていた。この例に代えて、図 7 に示すように、各 p 型ディープ層 36 及び各 n 型ディープ層 37 が x 方向に分断していてもよい。この例では、各 p 型ディープ層 36 が分断されているので、電流経路が広く確保され、オン抵抗が低下する。ただし、この例であっても、各 p 型ディープ層 36 及び各 n 型ディープ層 37 は、トレンチ 14 を跨ぐように配置されている。これにより、上記した作用効果を発揮することができる。なお、各 p 型ディープ層 36 及び各 n 型ディープ層 37 のいずれか一方のみが x 方向に分断していてもよい。また、図 8 に示すように、隣り合う p 型ディープ層 36 を接続する接続 p 層 36a が設けられていてもよい。このような接続 p 層 36a は、ゲート絶縁膜 16 に加わる電界の緩和及び耐圧向上に有効である。

30

#### 【0027】

なお、MOSFET 10 では、図 3 に示されるように、上側から半導体基板 12 を見たときに、各 p 型トレンチ下層 35 がトレンチ 14 の長手方向の一方端から他方端まで連続して伸びていた。この例に代えて、図 9 に示すように、半導体基板 12 を上側から見たときに、各 p 型トレンチ下層 35 は、対応するトレンチ 14 の長手方向（この例では y 方向）に沿って長く伸びており、トレンチ 14 の長手方向の一方端から他方端の間で分断していてもよい。この場合、各 p 型ディープ層 36 は、p 型トレンチ下層 35 の分断された部分を通過する。例えば、図 3 に示す例では、p 型トレンチ下層 35 と p 型ディープ層 36 が重複する部分でイオン注入時のダメージが大きくなり、リーク電流の増加が懸念される。一方、図 9 に示す例では、p 型トレンチ下層 35 と p 型ディープ層 36 の重複部分が少ないので、リーク電流の増加が抑えられる。

40

#### 【0028】

50

なお、MOSFET 10では、図2に示されるように、上側から半導体基板12を見たときに、各ソース層30及び各コンタクト層32がトレンチ14の長手方向に対して平行に伸びている。特に、各ソース層30がトレンチ14の長手方向に対して平行に伸びるとともにトレンチ14の側面に接していることにより、トレンチ14の側面全体を高濃度なチャネルとして利用することができるので、MOSFET 10のオン抵抗は低い。さらに、トレンチ14の側面全体をチャネルとして利用することができるので、チャネルと各n型ディープ層37が良好に接続される。例えば、各ソース層30がトレンチ14の長手方向に対して交差するように、特に、トレンチ14の長手方向に対して直交するように伸びていると、トレンチ14の側面に接するソース層30の位置が限定されるので、トレンチ14の側面に形成される高濃度なチャネルの位置も限定される。このため、このような例では、製造時のソース層30とn型ディープ層37の相対的な位置関係のズレによって、トレンチ14の側面に形成される高濃度なチャネルとn型ディープ層37の相対的な位置関係にもズレが生じるので、オン抵抗が大きく変動し易いという問題がある。一方、MOSFET 10では、トレンチ14の側面全体を高濃度なチャネルとして利用することができるので、このようなオン抵抗の変動が生じない。なお、図2の例に代えて、図10に示されるように、各コンタクト層32がトレンチ14の長手方向に沿って分散して配置されていてもよい。なお、この例でも、各コンタクト層32は、上側から半導体基板12を見たときにトレンチ14の長手方向に対して平行に伸びている、ということができる。また、この例では、コンタクト層32間にソース層30が設けられていてもよい。

#### 【0029】

また、MOSFET 10では、図11に示すように、n型ディープ層37が、n型ディープ下層137Aとn型ディープ上層137Bを有していてもよい。n型ディープ下層137Aは、n型ディープ上層137Bの下側に設けられており、ドリフト層38よりもn型不純物濃度が高く、n型ディープ上層137Bよりもn型不純物濃度が低いn型層である。n型ディープ下層137Aのn型不純物濃度は、上記したような実質的に単一濃度で構成されるときと同一の濃度であってもよい。n型ディープ上層137Bは、n型ディープ下層137Aとボディ層34の間に設けられており、トレンチ14の底面よりも上側に配置されており、ボディ層34の下側に位置するトレンチ14の側面でゲート絶縁膜16に接している。このようなn型ディープ上層137Bが設けられていると、p型トレンチ下層35とボディ層34の双方から伸びる空乏層によってp型トレンチ下層35とボディ層34の間の領域の電流経路が狭くなる現象（JFET効果）を抑え、オン抵抗の増大を抑えることができる。なお、n型ディープ層37の全体がn型ディープ上層137Bと同等の高濃度に構成されていると、上述した耐圧の改善効果が低下する。n型ディープ層37がn型ディープ下層137Aとn型ディープ上層137Bを有し、さらに、n型ディープ上層137Bがトレンチ14の底面よりも上側に配置されていることにより、オン抵抗の増大抑制と高耐圧化を良好に両立させることができる。

#### 【0030】

また、MOSFET 10では、図12に示すように、p型ディープ層36が、p型ディープ下層136Aとp型ディープ上層136Bを有していてもよい。p型ディープ下層136Aは、p型ディープ上層136Bの下側に設けられており、ボディ層34のp型不純物濃度よりも高く、p型ディープ上層136Bのp型不純物濃度よりも低いp型層である。p型ディープ上層136Bは、p型ディープ下層136Aとボディ層34の間に設けられており、トレンチ14の底面よりも上側に配置されており、ボディ層34の下側に位置するトレンチ14の側面でゲート絶縁膜16に接している。MOSFET 10の耐圧向上させるためには、p型ディープ層36の全体の濃度が高いのが望ましいが、その場合、p型ディープ層36とp型トレンチ下層35が重複する部分でイオン注入時のダメージが大きくなり、リーク電流の増加が懸念される。図12に示すMOSFET 10では、p型トレンチ下層35と重複しない部分のp型ディープ上層136Bの濃度を高くすることで、リーク電流の増加を抑えながら、耐圧向上させることができる。

#### 【0031】

10

20

30

40

50

また、MOSFET 10では、図13に示すように、p型トレンチ下層35が、第1p型トレンチ下層135Aと第2p型トレンチ下層135Bを有していてもよい。第1p型トレンチ下層135Aは、第2p型トレンチ下層135Bの下側に設けられており、第2p型トレンチ下層135Bのp型不純物濃度よりも低いp型層である。第2p型トレンチ下層135Bは、第1p型トレンチ下層135Aとトレンチ14の間に設けられており、トレンチ14の底面でゲート絶縁膜16に接している。第2p型トレンチ下層135Bの深さ方向(z方向)の厚みは、ソース層30の厚み方向の厚みよりも小さくてもよい。特に限定されるものではないが、第2p型トレンチ下層135Bのp型不純物濃度と厚みの積は、n型ディープ層37のn型不純物濃度と厚みの積よりも大きくてよい。p型不純物濃度の高い第2p型トレンチ下層135Bが設けられていると、MOSFET 10がオフしたときに第2p型トレンチ下層135Bが空乏化しない。このため、ゲート電極18とドレイン電極24の間の静電容量(すなわち、帰還容量)が小さくなり、MOSFET 10のスイッチング速度を向上させることができる。

#### 【0032】

なお、帰還容量が大きいデバイスが必要とされる場合がある。このような場合、図13の第1p型トレンチ下層135Aと第2p型トレンチ下層135Bのp型不純物濃度の関係を逆にしてもよい。すなわち、第2p型トレンチ下層135Bのp型不純物濃度が、第1p型トレンチ下層135Aのp型不純物濃度よりも低くてもよい。この場合も、第2p型トレンチ下層135Bの深さ方向(z方向)の厚みは、ソース層30の厚み方向の厚みよりも小さくてもよい。

#### 【0033】

また、MOSFET 10では、図14に示すように、p型トレンチ下層35がトレンチ14の底面から離れていてもよい。なお、p型トレンチ下層35とトレンチ14の底面の間の距離は、ソース層30の厚み方向の厚みよりも小さくてもよい。このような位置関係にp型トレンチ下層35が設けられていっても、上述した耐圧の改善効果が得られる。一方、後述の製造方法で説明するように、このようなp型トレンチ下層35は、同時形成されるボディ層34のイオン注入回数を減らした結果が反映された形態である。即ち、図14に示すMOSFET 10は、低コストで製造可能な構造を有している。

#### 【0034】

また、上記で説明したMOSFET 10はいずれも、n型ディープ層37の深さがp型ディープ層36の深さよりも深かった。この例に代えて、n型ディープ層37の深さがp型ディープ層36の深さと等しくてもよい。また、n型ディープ層37の深さがp型ディープ層36の深さより浅くてもよい。

#### 【0035】

また、上記で説明したMOSFET 10はいずれも、各n型ディープ層37がp型ディープ層36の直下まで伸びる接続領域37aを有していた。この例に代えて、n型ディープ層37が接続領域37aを有していなくてもよい。

#### 【0036】

また、上記で説明したMOSFET 10はいずれも、上側から半導体基板12を見たときに、各p型ディープ層36及び各n型ディープ層37が各トレンチ14に対して直交していた。この例に代えて、各p型ディープ層36及び各n型ディープ層37が各トレンチ14に対して斜めに交差していてもよい。

#### 【0037】

次に、MOSFET 10の製造方法について説明する。MOSFET 10は、全体がドレイン層40によって構成された半導体基板から製造される。まず、図15に示すように、エピタキシャル成長技術を利用して、ドレイン層40上にn型のエピタキシャル層50を形成する。

#### 【0038】

次に、図16に示すように、イオン注入技術を利用して、エピタキシャル層50の表面から離れた所定深さ範囲にn型不純物とp型不純物を導入することによってn型ディープ

層 3 7 と p 型ディープ層 3 6 を形成する（ディープ層形成工程の一例）。具体的には、エピタキシャル層 5 0 の所定深さに向けて面的に n 型不純物導入した後に、n 型不純物が導入された範囲の一部に向けて p 型不純物をマスク越しにカウンタードーピングすることにより、n 型ディープ層 3 7 と p 型ディープ層 3 6 を形成することができる。なお、この例に代えて、n 型ディープ層 3 7 と p 型ディープ層 3 6 のそれぞれに対応したマスクを越しに n 型不純物と p 型不純物を順に導入することによって n 型ディープ層 3 7 と p 型ディープ層 3 6 を形成してもよい。また、エピタキシャル層 5 0 をエピタキシャル成長するときに n 型ディープ層 3 7 の形成範囲に対応した深さの n 型不純物を予め濃く調整することで、n 型ディープ層 3 7 を形成するためのイオン注入を省略することができる。なお、イオン注入技術又はエピタキシャル成長技術を利用して n 型ディープ層 3 7 又は p 型ディープ層 3 6 を形成するときに、深さ方向の濃度を変更することで、図 1 1 に示すような n 型ディープ下層 1 3 7 A と n 型ディープ上層 1 3 7 B 又は図 1 2 に示すような p 型ディープ下層 1 3 6 A と p 型ディープ上層 1 3 6 B を形成することができる。

10

#### 【 0 0 3 9 】

次に、図 1 7 に示すように、イオン注入技術を利用して、エピタキシャル層 5 0 の表層部に n 型不純物及び p 型不純物を導入することによってソース層 3 0 とコンタクト層 3 2 を形成する。

#### 【 0 0 4 0 】

次に、図 1 8 に示すように、エッチング技術を利用して、エピタキシャル層 5 0 の表面から n 型ディープ層 3 7 及び p 型ディープ層 3 6 に達するトレンチ 1 4 を形成する（トレンチ形成工程の一例）。トレンチ 1 4 の深さは、n 型ディープ層 3 7 及び p 型ディープ層 3 6 を超えないように調整される。トレンチ 1 4 は、上側からエピタキシャル層 5 0 を見たときに、複数の p 型ディープ層 3 6 と複数の n 型ディープ層 3 7 に交差している。

20

#### 【 0 0 4 1 】

次に、図 1 9 に示すように、イオン注入技術を利用して、エピタキシャル層 5 0 の表面に向けて p 型不純物を多段で導入することによってボディ層 3 4 と p 型トレンチ下層 3 5 を形成する（ボディ層形成工程と p 型トレンチ下層形成工程の一例）。ボディ層 3 4 は、n 型ディープ層 3 7 及び p 型ディープ層 3 6 よりも上側であって、ソース層 3 0 とコンタクト層 3 2 よりも下側に形成される。p 型トレンチ下層 3 5 は、トレンチ 1 4 の底面の下側に形成される。ここで、イオン注入技術を利用してボディ層 3 4 と p 型トレンチ下層 3 5 を形成するときに、深さ方向の濃度を変更することで、図 1 3 に示すような第 1 p 型トレンチ下層 1 3 5 A と第 2 p 型トレンチ下層 1 3 5 B を形成することができる。さらに、第 2 p 型トレンチ下層 1 3 5 B を形成するために p 型不純物を導入する深さは、ソース層 3 0 よりも浅い範囲に限定する。これにより、ボディ層 3 4 の p 型不純物の濃度を所望の値としながら、第 2 p 型トレンチ下層 1 3 5 B の p 型不純物の濃度を自由に設定することができる。なお、第 2 p 型トレンチ下層 1 3 5 B を形成するための p 型不純物はソース層 3 0 にも導入されるが、ソース層 3 0 に含まれる n 型不純物の濃度は導入される p 型不純物の濃度よりも高いので、MOSFET 1 0 の電気的特性を大きく変動させることがない。

30

また、n 型ディープ層 3 7 及び p 型ディープ層 3 6 よりも上側であって、ソース層 3 0 とコンタクト層 3 2 よりも下側の範囲に p 型不純物が選択的に導入されるように、イオン注入の段数を調整すると、p 型トレンチ下層 3 5 は、トレンチ 1 4 の底面から離れた位置に形成される。図 1 4 に示される MOSFET 1 0 は、このような方法で製造された例である。なお、p 型不純物をイオン注入する前に、トレンチ 1 4 の側面にソーク防止遮蔽膜を成膜してもよい。

40

#### 【 0 0 4 2 】

その後、トレンチ 1 4 、ゲート絶縁膜 1 6 、ゲート電極 1 8 、層間絶縁膜 2 0 、ソース電極 2 2 、及び、ドレイン電極 2 4 を形成することで、MOSFET 1 0 が完成する。

#### 【 0 0 4 3 】

上記製造方法では、エピタキシャル層 5 0 を形成した後は、再エピ工程を実施することなく、イオン注入技術を利用して各種半導体領域を形成することができる。帰還容量を低

50

くするためには、n型ディープ層37及びp型ディープ層36を深く形成するのが望ましい。しかしながら、このような深いn型ディープ層37及びp型ディープ層36を、上記製造方法のように、エピタキシャル層50の所定深さにイオン注入技術で形成するのは難しい。このため、背景技術で説明した従来例では、エピタキシャル層の表面に深いn型ディープ層及びp型ディープ層をイオン注入で形成した後に、再エピ工程を実施してボディ層を形成する。しかしながら、再エピ工程を含む製造方法は、コストが増加するという問題がある。一方、本実施形態のMOSFET10は、p型トレンチ下層35を有しているので、帰還容量が低い。このため、本実施形態のMOSFET10では、n型ディープ層37及びp型ディープ層36を深く形成しなくても、低い帰還容量が得られる。このため、上記製造方法のように、再エピ工程を実施しなくても、帰還容量の低いMOSFET10を製造することができる。なお、必要に応じて、再エピ工程を実施して本実施形態のMOSFET10を製造してもよいことは言うまでもない。

#### 【0044】

上記で説明したMOSFET10は、トレンチ14を形成した後に、イオン注入技術を利用してボディ層34とp型トレンチ下層35を同時形成する例であった。この例に代えて、トレンチ14を形成する前に、p型トレンチ下層35とp型ディープ層36を同時形成してもよい。この場合、ボディ層34は、別のイオン注入工程によって形成される。図20に、p型トレンチ下層35とp型ディープ層36を同時形成したMOSFET10を示す。

#### 【0045】

このMOSFET10では、トレンチ14の短手方向(×方向)に沿って測定したときに、p型トレンチ下層35の幅がトレンチ14の幅よりも狭い。これにより、p型トレンチ下層35とトレンチ14の若干の位置合わせのズレを許容することができるので、トレンチ14を形成したときに、p型トレンチ下層35をトレンチ14の底面のみに接するように配置することができる。

#### 【0046】

以下、本明細書で開示される技術の特徴を整理する。なお、以下に記載する技術要素は、それぞれ独立した技術要素であって、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。

#### 【0047】

本明細書が開示する電界効果トランジスタは上面にトレンチが設けられた半導体基板と、前記トレンチの内面を覆うゲート絶縁膜と、前記トレンチ内に配置されており、前記ゲート絶縁膜によって前記半導体基板から絶縁されているゲート電極、を有することができる。前記半導体基板の材料は、特に限定されるものではないが、例えば炭化珪素であってもよい。前記半導体基板が、前記トレンチの側面で前記ゲート絶縁膜に接するn型のソース層と、前記ソース層の下側に位置する前記トレンチの前記側面で前記ゲート絶縁膜に接するp型のボディ層と、前記トレンチの下側に配置されており、上側から前記半導体基板を見たときに前記トレンチの長手方向に沿って伸びているp型トレンチ下層と、複数のp型ディープ層と、複数のn型ディープ層を有することができる。前記各p型ディープ層が、前記ボディ層から下側に突出しており、前記ボディ層から前記トレンチの底面よりも下側まで伸びており、上側から前記半導体基板を見たときに前記トレンチに対して交差する第1方向に沿って伸びており、上側から前記半導体基板を見たときに前記第1方向に対して直交する第2方向に間隔部を開けて配置されており、前記トレンチの下側に配置されている前記p型トレンチ下層に接している。前記各n型ディープ層が、対応する前記間隔部内に配置されており、前記ボディ層の下側に位置する前記トレンチの前記側面で前記ゲート絶縁膜に接している。

#### 【0048】

上記電界効果トランジスタでは、前記ソース層が、上側から前記半導体基板を見たときに前記トレンチの長手方向に対して平行に伸びていてよい。この電界効果トランジスタでは、オン抵抗の変動が抑えられる。

10

20

30

40

50

**【 0 0 4 9 】**

上記電界効果トランジスタでは、前記半導体基板が、前記ボディ層上に設けられており、前記ボディ層よりも高いp型不純物濃度を有するコンタクト層、を有していてもよい。この場合、前記コンタクト層は、上側から前記半導体基板を見たときに前記トレンチの長手方向に対して平行に伸びていてもよい。

**【 0 0 5 0 】**

上記電界効果トランジスタでは、前記p型トレンチ下層は、前記各p型ディープ層よりも下側に突出していてもよい。この電界効果トランジスタは、高い耐圧を有することができる。

**【 0 0 5 1 】**

上記電界効果トランジスタでは、前記p型トレンチ下層は、前記各p型ディープ層よりも浅くてもよい。この電界効果トランジスタは、低いオン抵抗を有することができる。

**【 0 0 5 2 】**

上記電界効果トランジスタでは、前記半導体基板が、前記各n型ディープ層の下側に配置されており、各n型ディープ層よりも低いn型不純物濃度を有するドリフト層、をさらに有していてもよい。換言すると、前記各n型ディープ層は、前記ドリフト層よりも高いn型不純物濃度を有してもよい。この電界効果トランジスタは、低いオン抵抗を有することができる。

**【 0 0 5 3 】**

上記電界効果トランジスタでは、前記各n型ディープ層が、n型ディープ下層と、前記n型ディープ下層の上側に配置されており、前記n型ディープ下層よりも高いn型不純物濃度を有するn型ディープ上層、を有していてもよい。この場合、前記n型ディープ上層は、前記トレンチの底面よりも上側に配置されている。この電界効果トランジスタは、高い耐圧と低いオン抵抗を両立することができる。

**【 0 0 5 4 】**

上記電界効果トランジスタでは、前記各p型ディープ層が、p型ディープ下層と、前記p型ディープ下層の上側に配置されており、前記p型ディープ下層よりも高いp型不純物濃度を有するp型ディープ上層、を有していてもよい。この場合、前記p型ディープ上層は、前記トレンチの底面よりも上側に配置されている。この電界効果トランジスタは、リーケ電流の増加を抑えながら、高い耐圧を有することができる。

**【 0 0 5 5 】**

上記電界効果トランジスタでは、対応するトレンチの底面から前記各p型トレンチ下層の下面までの深さは、前記半導体基板の上面から前記ボディ層の下面までの深さと一致してもよい。この電界効果トランジスタは、前記p型トレンチ下層と前記ボディ層が同時形成された結果が反映された形態である。この電界効果トランジスタは、低コストで製造可能な構造を有している。

**【 0 0 5 6 】**

上記電界効果トランジスタでは、前記p型トレンチ下層が、前記トレンチの底面から離れていてもよい。この電界効果トランジスタは、同時形成されるボディ層のイオン注入回数を減らした結果が反映された形態である。この電界効果トランジスタは、低コストで製造可能な構造を有している。

**【 0 0 5 7 】**

上記電界効果トランジスタでは、前記p型トレンチ下層が、深さ方向に濃度が異なる複数の部分を有していてもよい。前記p型トレンチ下層は、第1p型トレンチ下層と、前記第1p型トレンチ下層の上側に配置されている第2p型トレンチ下層、を有していてもよい。前記第2p型トレンチ下層は、前記第1p型トレンチ下層よりも濃度が濃くてもよく、前記第1p型トレンチ下層よりも濃度が薄くてもよい。また、前記第2p型トレンチ下層の深さ方向の厚みは、前記ソース層の深さ方向の厚みよりも小さくてもよい。前記p型トレンチ下層の不純物濃度を調整することにより、帰還容量を調整することができる。

**【 0 0 5 8 】**

10

20

30

40

50

上記電界効果トランジスタでは、前記 p 型トレンチ下層が、前記トレンチの長手方向に沿って分断されていてもよい。前記各 p 型ディープ層は、前記 p 型トレンチ下層の分断された部分を通過してもよい。この電界効果トランジスタでは、リーク電流の増加が抑えられる。

#### 【 0 0 5 9 】

上記電界効果トランジスタでは、前記複数の n 型ディープ層が、前記ボディ層の下面から前記複数の p 型ディープ層の下面よりも下側まで伸びていてもよい。

#### 【 0 0 6 0 】

上記電界効果トランジスタでは、前記第 1 方向が、上側から前記半導体基板を見たときに、前記トレンチに対して直交しててもよい。

10

#### 【 0 0 6 1 】

本明細書が開示する電界効果トランジスタの製造方法は、n 型のエピタキシャル層に複数の p 型ディープ層と複数の n 型ディープ層を形成するディープ層形成工程であって、前記各 p 型ディープ層が、上側から前記エピタキシャル層を見たときに第 1 方向に沿って伸びてあり、上側から前記エピタキシャル層を見たときに前記第 1 方向に対して直交する第 2 方向に間隔部を開けて配置されており、前記各 n 型ディープ層が、対応する前記間隔部内に配置されている、ディープ層形成工程と、前記エピタキシャル層の表面から前記複数の p 型ディープ層と前記複数の n 型ディープ層を超えない深さのトレンチを形成するトレンチ形成工程であって、前記トレンチは、上側から前記エピタキシャル層を見たときに前記複数の p 型ディープ層と前記複数の n 型ディープ層に交差している、トレンチ形成工程と、イオン注入技術を利用して、前記エピタキシャル層の表面に向けて p 型不純物を導入し、前記複数の p 型ディープ層と前記複数の n 型ディープ層の上側にボディ層を形成する、ボディ層形成工程と、イオン注入技術を利用して、前記トレンチの底面の下側に p 型トレンチ下層を形成する、p 型トレンチ下層形成工程、を有することができる。

20

#### 【 0 0 6 2 】

前記ディープ層形成工程では、イオン注入技術を利用して、前記複数の p 型ディープ層と前記複数の n 型ディープ層が、前記エピタキシャル層の表面から離れた所定深さ範囲に n 型不純物と p 型不純物を導入することによって形成されてもよい。この製造方法によると、再エピ工程を実施することなく、電界効果トランジスタを製造することができる。

30

#### 【 0 0 6 3 】

前記ボディ層形成工程と前記 p 型トレンチ下層形成工程は、前記トレンチ形成工程の後に同時に実施されてもよい。この製造方法によると、低コストで電界効果トランジスタを製造することができる。

#### 【 0 0 6 4 】

上記製造方法は、イオン注入技術を利用して、前記エピタキシャル層の上層部に n 型不純物を導入し、ソース層を形成する、ソース層形成工程、をさらに有しててもよい。この場合、前記 p 型トレンチ下層は、第 1 p 型トレンチ下層と、前記第 1 p 型トレンチ下層の上側に配置されている第 2 p 型トレンチ下層、を有してもよい。前記第 2 p 型トレンチ下層は、前記第 1 p 型トレンチ下層よりも濃度が濃くてもよい、前記第 1 p 型トレンチ下層よりも濃度が薄くてもよい。前記第 2 p 型トレンチ下層の深さ方向の厚みは、前記ソース層の深さ方向の厚みよりも小さくてもよい。この製造方法によると、前記 p 型トレンチ下層の不純物濃度を調整することにより、帰還容量が調整された電界効果トランジスタを製造することができる。

40

#### 【 0 0 6 5 】

前記 p 型トレンチ下層形成工程は、前記トレンチ形成工程の前に実施されてもよい。この場合、前記 p 型トレンチ下層の幅は、前記トレンチの幅よりも狭くてもよい。この製造方法によると、前記 p 型トレンチ下層と前記トレンチの若干の位置合わせのズレを許容することができる。

#### 【 0 0 6 6 】

前記 p 型トレンチ下層形成工程は、前記ディープ層形成工程のうちの前記複数の p 型デ

50

イープ層を形成する工程と同時に実施されてもよい。この製造方法によると、低成本で電界効果トランジスタを製造することができる。

#### 【0067】

以上、実施形態について詳細に説明したが、これらは例示にすぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例をさまざまに変形、変更したものが含まれる。本明細書または図面に説明した技術要素は、単独あるいは各種の組み合わせによって技術有用性を発揮するものであり、出願時請求項記載の組み合わせに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成するものであり、そのうちの1つの目的を達成すること自体で技術有用性を持つものである。

10

#### 【符号の説明】

#### 【0068】

10 : MOSFET、12 : 半導体基板、14 : トレンチ、16 : ゲート絶縁膜、18 : ゲート電極、20 : 層間絶縁膜、22 : ソース電極、24 : ドレイン電極、30 : ソース層、32 : コンタクト層、34 : ボディ層、35 : p型トレンチ下層、36 : p型ディープ層、37 : n型ディープ層、38 : ドリフト層、40 : ドレイン層

20

30

40

50

## 【図面】

## 【図 1】

## 【図 2】

10

20

## 【図 3】

## 【図 4】

30

40

50

【 四 5 】

【図6】

【図7】

【 図 8 】

20

30

40

50

【図9】

10

【図10】

10

10

【図11】

【図12】

20

30

40

50

【図13】

【図14】

【図15】

【図16】

20

30

40

50

【図 1 7】

【図 1 8】

【図 1 9】

【図 2 0】

10

20

30

40

50

---

**フロントページの続き****(51)国際特許分類**

| F I    |       |         |

|--------|-------|---------|

| H 01 L | 29/06 | 3 0 1 D |

| H 01 L | 29/06 | 3 0 1 V |

| H 01 L | 29/78 | 6 5 2 D |

| H 01 L | 29/78 | 6 5 8 A |

**(56)参考文献**

特開2010-225615(JP, A)

国際公開第2016/157606(WO, A1)

特開2015-046628(JP, A)

特開2012-169384(JP, A)

特開2012-169386(JP, A)

特開2020-109809(JP, A)

特開2018-113421(JP, A)

特開2019-212836(JP, A)

特開2018-082058(JP, A)

特開2011-253867(JP, A)

**(58)調査した分野 (Int.Cl., DB名)**

H 01 L 29 / 7 8

H 01 L 29 / 1 2

H 01 L 29 / 0 6

H 01 L 21 / 3 3 6