(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4209588号

(P4209588)

(45) 発行日 平成21年1月14日(2009.1.14)

(24) 登録日 平成20年10月31日(2008.10.31)

(51) Int.Cl.

F 1

G 11 C 11/417 (2006.01)

G 11 C 11/41 (2006.01)G 11 C 11/34 305

G 11 C 11/34 345

請求項の数 16 (全 14 頁)

(21) 出願番号 特願2000-518387 (P2000-518387)

(86) (22) 出願日 平成10年10月20日 (1998.10.20)

(65) 公表番号 特表2001-521262 (P2001-521262A)

(43) 公表日 平成13年11月6日 (2001.11.6)

(86) 國際出願番号 PCT/US1998/021939

(87) 國際公開番号 WO1999/022376

(87) 國際公開日 平成11年5月6日 (1999.5.6)

審査請求日 平成17年9月7日 (2005.9.7)

(31) 優先権主張番号 08/956,981

(32) 優先日 平成9年10月24日 (1997.10.24)

(33) 優先権主張国 米国(US)

(73) 特許権者 507293332

エーアールエム・インコーポレーテッド

ARM INCORPORATED

アメリカ合衆国 カリフォルニア州940

89-1013 サニーベイル, カスピア

ン・コート, 141

(74) 代理人 110000028

特許業務法人明成国際特許事務所

(74) 代理人 100096817

弁理士 五十嵐 孝雄

(74) 代理人 100097146

弁理士 下出 隆史

(74) 代理人 100102750

弁理士 市川 浩

最終頁に続く

(54) 【発明の名称】高速メモリ用自己タイミング回路及びその実現方法

## (57) 【特許請求の範囲】

## 【請求項1】

メモリ回路であって、

複数のワード線と複数のビット線対と複数のセンスアンプとに接続されているコアセルのアレイを有するメモリコアと、

モデルワード線ドライバにより駆動されるモデルワード線に直列に接続された複数のダミーコアセル及びモデルコアセルと、モデルビット線対を通じて前記モデルコアセルに接続されたモデルセンスアンプとを有する自己タイミング経路と、

を備え、

前記モデルワード線に接続された前記ダミーコアセルの数は、前記複数のワードラインの一つに接続された前記コアセルの数に等しく、

前記モデルワード線は、前記モデルワード線が前記モデルワード線ドライバに近接した位置において終端を有するように折り返されているとともに、前記モデルワード線に接続された最後のダミーコアセルが前記モデルワード線ドライバに近接した位置に配置されており、

前記メモリ回路は、さらに、前記自己タイミング経路を駆動するように構成された制御回路であって、モデルビット線対を通じて前記モデルコアセルに接続された前記モデルセンスアンプに接続されている制御回路を備え、

前記制御回路は、前記モデルワード線ドライバにワード線イネーブル信号を伝達して前記自己タイミング経路を駆動し、前記折り返されたワード線を通じて前記モデルワード線

10

20

ドライバが前記モデルコアセルへアクセスするように構成されるとともに、前記モデルワード線の自己タイミング経路 R C 遅延を受け取ったときに、前記メモリコアのセンスアンプに伝達される読み出しレディ信号を生成する、

メモリ回路。

【請求項 2】

メモリ回路であって、

複数のワード線と複数のビット線対と複数のセンスアンプとに接続されているコアセルのアレイを有するメモリコアと、

モデルワード線ドライバにより駆動されるモデルワード線に直列に接続された複数のダミーコアセル及びモデルコアセルと、モデルビット線対を通じて前記モデルコアセルに接続されたモデルセンスアンプとを有する自己タイミング経路と、

を備え、

前記モデルワード線に接続された前記ダミーコアセルの数は、前記複数のワードラインの一つに接続された前記コアセルの数に等しく、

前記モデルワード線は、前記モデルワード線が前記モデルワード線ドライバに近接した位置において終端を有するように折り返されているとともに、前記ダミーコアセルの半数が前記モデルワード線の前半に配置され、残りの半数が前記モデルワード線の後半に配置されているワード線であり、

前記モデルコアセルは、前記モデルワード線ドライバに近接した位置において前記モデルワード線の前記終端に接続されており、

前記メモリ回路は、さらに、前記自己タイミング経路を駆動するように構成された制御回路であって、モデルビット線対を通じて前記モデルコアセルに接続された前記モデルセンスアンプに接続されている制御回路を備え、

前記制御回路は、前記モデルワード線ドライバにワード線イネーブル信号を伝達して前記自己タイミング経路を駆動し、前記折り返されたワード線を通じて前記モデルワード線ドライバが前記モデルコアセルへアクセスするように構成されるとともに、前記モデルワード線の自己タイミング経路 R C 遅延を受け取ったときに、前記メモリコアのセンスアンプに伝達される読み出しレディ信号を生成する、

メモリ回路。

【請求項 3】

請求項 1 又は 2 記載のメモリ回路であって、

前記自己タイミング経路 R C 遅延は、前記最悪ケースコアセルの R C 遅延とほぼ等しい、メモリ回路。

【請求項 4】

請求項 3 記載のメモリ回路であって、

前記最悪ケースコアセルは、前記コアセルのアレイの中で、前記メモリコアのワード線ドライバと前記センスアンプから最も遠いものである、メモリ回路。

【請求項 5】

請求項 1 又は 2 記載のメモリ回路であって、さらに、

前記複数のワード線に接続されている複数のワード線ドライバを備える、メモリ回路。

【請求項 6】

請求項 5 記載のメモリ回路であって、

前記制御回路が、前記コアセルのアレイに接続されている各々の前記複数のセンスアンプと各々の前記複数のワード線ドライバに接続されている、メモリ回路。

【請求項 7】

請求項 1 又は 2 記載のメモリ回路であって、

前記メモリ回路は、ROM回路と、RAM回路と、SRAM回路と、DRAM回路と、

EPROM回路と、EEPROM回路とで構成されるグループから選択されたものである、

メモリ回路。

【請求項 8】

10

20

30

40

50

自己タイミング経路を有するメモリ回路の製造方法であって、複数のワード線と複数のビット線対と複数のセンスアンプとに接続されているコアセルのアレイを有するメモリコアを提供する工程と、

モデルワード線とモデルビット線対とに沿ってコアセルの自己タイミング経路を集積化する工程と、

前記モデルワード線に沿った R C 遅延と前記モデルビット線対に沿った R C 遅延とが完了したことを示す R C 遅延信号の後に、読み出しレディ信号を前記メモリコアのセンスアンプに伝達する工程と、

を備え、

前記自己タイミング経路は、モデルワード線ドライバにより駆動されるモデルワード線に直列に接続された複数のダミーコアセル及びモデルコアセルと、モデルビット線対を通じて前記モデルコアセルに接続されたモデルセンスアンプとを有し、

前記モデルワード線に接続された前記ダミーコアセルの数は、前記複数のワードラインの一つに接続された前記コアセルの数に等しく、

前記モデルワード線は、前記モデルワード線が前記モデルワード線ドライバに近接した位置において終端を有するように折り返されているとともに、前記モデルワード線に接続された最後のダミーコアセルが前記モデルワード線ドライバに近接した位置に配置されている、

メモリ回路の製造方法。

【請求項 9】

自己タイミング経路を有するメモリ回路の製造方法であって、複数のワード線と複数のビット線対と複数のセンスアンプとに接続されているコアセルのアレイを有するメモリコアを提供する工程と、

モデルワード線とモデルビット線対とに沿ってコアセルの自己タイミング経路を集積化する工程と、

前記モデルワード線に沿った R C 遅延と前記モデルビット線対に沿った R C 遅延とが完了したことを示す R C 遅延信号の後に、読み出しレディ信号を前記メモリコアのセンスアンプに伝達する工程と、

を備え、

前記自己タイミング経路は、モデルワード線ドライバにより駆動されるモデルワード線に直列に接続された複数のダミーコアセル及びモデルコアセルと、モデルビット線対を通じて前記モデルコアセルに接続されたモデルセンスアンプとを有し、

前記モデルワード線に接続された前記ダミーコアセルの数は、前記複数のワードラインの一つに接続された前記コアセルの数に等しく、

前記モデルワード線は、前記モデルワード線が前記モデルワード線ドライバに近接した位置において終端を有するように折り返されているとともに、前記ダミーコアセルの半数が前記モデルワード線の前半に配置され、残りの半数が前記モデルワード線の後半に配置されているワード線であり、

前記モデルコアセルは、前記モデルワード線ドライバに近接した位置において前記モデルワード線の前記終端に接続されている、

メモリ回路の製造方法。

【請求項 10】

請求項 8 又は 9 記載の自己タイミング経路を有するメモリ回路の製造方法であって、前記読み出しレディ信号の立ち下がりエッジが前記メモリコアの前記センスアンプのトリガーとなる、メモリ回路の製造方法。

【請求項 11】

請求項 10 記載の自己タイミング経路を有するメモリ回路の製造方法であって、前記読み出しレディ信号の立ち上がりエッジが、前記モデルワード線の前記始端で前記モデルワード線に接続されたモデルワード線ドライバのトリガーとなる、メモリ回路の製造方法。

10

20

30

40

50

## 【請求項 1 2】

請求項 1 1 記載の自己タイミング経路を有するメモリ回路の製造方法であって、

前記メモリ回路は、ROM回路と、RAM回路と、SRAM回路と、DRAM回路と、

EPROM回路と、EEPROM回路とで構成されるグループから選択されたものである

、メモリ回路の製造方法。

## 【請求項 1 3】

複数のワード線と複数のビット線対と複数のセンスアンプとに接続されているコアセル

のアレイを有するメモリコアを含み、かつ、自己タイミング経路を有するメモリ回路を生成

するためのメモリジェネレータであって、

モデルワード線とモデルビット線対とに沿ってコアセルの自己タイミング経路を生成し

ており、

前記自己タイミング経路は、モデルワード線ドライバにより駆動されるモデルワード線

に直列に接続された複数のダミーコアセル及びモデルコアセルと、モデルビット線対を通

じて前記モデルコアセルに接続されたモデルセンスアンプとを有し、

前記モデルワード線に接続された前記ダミーコアセルの数は、前記複数のワードライン

の一つに接続された前記コアセルの数に等しく、

前記モデルワード線は、前記モデルワード線が前記モデルワード線ドライバに近接した

位置において終端を有するように折り返されているとともに、前記モデルワード線に接続

された最後のダミーコアセルが前記モデルワード線ドライバに近接した位置に配置され

おり、

制御回路が、復帰経路のRC遅延なしで、前記モデルワード線と前記モデルビット線対

との合成RC遅延を受信するように構成されている、

メモリジェネレータ。

## 【請求項 1 4】

複数のワード線と複数のビット線対と複数のセンスアンプとに接続されているコアセル

のアレイを有するメモリコアを含み、かつ、自己タイミング経路を有するメモリ回路を生成

するためのメモリジェネレータであって、

モデルワード線とモデルビット線対とに沿ってコアセルの自己タイミング経路を生成し

ており、

前記自己タイミング経路は、モデルワード線ドライバにより駆動されるモデルワード線

に直列に接続された複数のダミーコアセル及びモデルコアセルと、モデルビット線対を通

じて前記モデルコアセルに接続されたモデルセンスアンプとを有し、

前記モデルワード線に接続された前記ダミーコアセルの数は、前記複数のワードライン

の一つに接続された前記コアセルの数に等しく、

前記モデルワード線は、前記モデルワード線が前記モデルワード線ドライバに近接した

位置において終端を有するように折り返されているとともに前記ダミーコアセルの半数が

前記モデルワード線の前半に配置され、残りの半数が前記モデルワード線の後半に配置さ

れていますワード線であり、

前記モデルコアセルは、前記モデルワード線ドライバに近接した位置において前記モ

デルワード線の前記終端に接続されており、

制御回路が、復帰経路のRC遅延なしで、前記モデルワード線と前記モデルビット線対

との合成RC遅延を受信するように構成されている、

メモリジェネレータ。

## 【請求項 1 5】

請求項 1 3 又は 1 4 記載のメモリ回路を生成するメモリジェネレータであって、

前記モデルビット線対は、複数のワード線ドライバと隣接した前記メモリコアの側部に

沿って配置される、メモリジェネレータ。

## 【請求項 1 6】

請求項 1 5 記載のメモリ回路を生成するメモリジェネレータであって、

モデルワード線ドライバが、前記複数のワード線ドライバの隣に整列されるとともに、

10

20

30

40

50

前記モデルコアセルの隣に配置される、メモリジェネレータ。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

この発明は一般に集積回路に関し、特に、改善されたメモリ用自己タイミング回路のための方法と装置に関する。

【0002】

【従来の技術】

半導体メモリコアは、通常、各々の独立したコアセルがワード線と一対の差動ビット線に接続されるようにアレイ形式で配置される。選択されたコアセルに格納されたデータにアクセスするため、メモリコアの周りに、付随するメモリーアクセス回路が共通に設計される。例えば、キーメモリーアクセス回路は、通常は、コアセルを選択するためのアドレス指定回路と、選択されたワード線を駆動するためのワード線ドライバと、選択されたコアセルからの読み出し信号を増幅するセンスアンプとを含む。

10

【0003】

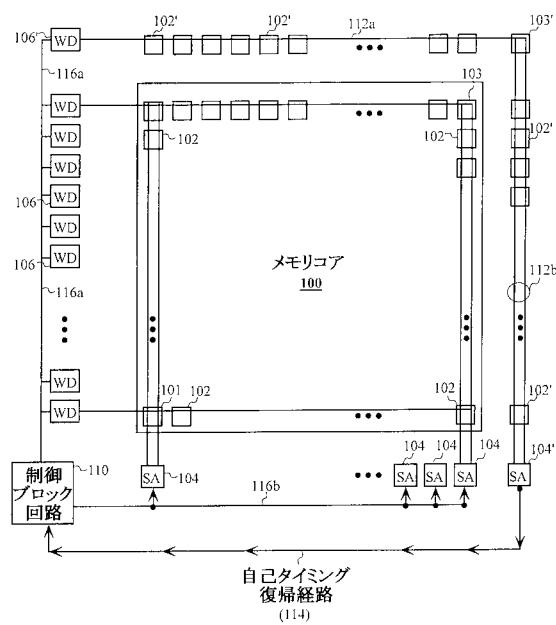

理解の容易のため、図1に、メモリコア100及び付随するアクセス回路を有するメモリ回路のブロック図を示す。従来のメモリコア設計においては、複数のコアセル102はメモリコア100の全体にアレイ形式で配置されている。この例では、選択されたメモリコアセル102へのアクセスを制御するために、制御ブロック回路110が使用され、このアクセスには、ワード線ドライバ106とセンスアンプ(SA)104が使用される。

20

【0004】

この例では、制御ブロック回路110は、その立ち上がりエッジによって一つの選択されたワード線ドライバ106をトリガーする信号116を生成するように構成されている。信号116が、立ち下がりエッジ(すなわち、以下に説明する従来の自己タイミングアーキテクチャにより決定されるタイミング)を生ずる時に、この信号116は選ばれたセンスアンプ104のうちの一つにデータの感知を開始させる。図示されるように、ワード線ドライバ106は、各コアセル102を相互接続するワード線を使用して、コアセル102それぞれと水平方向に接続される。同様に、センスアンプ104は、差動ビット線を使用してコアセル102の各々と垂直方向に接続される。

30

【0005】

従来のメモリ回路において、設計者は、自己タイミングアーキテクチャを使用しており、この自己タイミングアーキテクチャは、メモリコア100においてコアセル102からデータを感知することをセンスアンプ104がいつ開始すべきであるかを、メモリ回路が決定することを可能にするものである。自己タイミングアーキテクチャは、一般に、いずれかのコアセル102へのアクセスを試みるときに使用する標準の遅延時間(すなわち、一般に、与えられたコアのための最悪ケースの遅延タイミングである)を概算するために使用される。一般に、あるコアセル102の現実の遅延時間は、そのコアセル102のロケーションにより異なるので、一般に自己タイミングアーキテクチャが必要である。例として、コアセル103は、ワード線ドライバ106とセンスアンプ104から最も遠くに位置している。

40

【0006】

その結果、ワード線ドライバ106をコアセル103に接続するワード線に伴うRC遅延と、センスアンプ104をコアセル103に接続するビット線に伴うRC遅延による合成RC遅延は、メモリコア100内の他のどのコアセル102よりも大きい。例えば、コアセル101に接続されたワード線とビット線による合成RC遅延は、メモリコア100内に配置された他のどのコアセルよりも小さい。従って、モデルワード線ドライバ106'、と、コアセル102'、と、モデルコアセル103'、と、モデルワード線112aと、モデルビット線112bと、センスアンプ104'、と、自己タイミング復帰経路114とを含む自己タイミングアーキテクチャは、かかる標準の遅延時間を設定する役割を有している。

50

## 【0007】

従って、自己タイミングアーキテクチャは、メモリコア100において、あるコアセル102のデータを読むために、センス増幅を正しく実行するのに十分なビット線差がいつ達成されたかを推定するのに適している（最悪ケースのモデルコアセル103'によるもの）。作動時には、制御ブロック回路は、モデルコアセル103'にアクセスするために、モデルワード線ドライバ106'に選択信号116を出力する。モデルコアセル103'がアクセスされると、信号がモデルビット線112bと、センスアンプ104'とを通り、自己タイミング復帰経路114に沿って制御ブロック回路110に伝達される。

## 【0008】

従来の自己タイミングアーキテクチャについての特有の問題は、センスアンプ104'がモデルコアセル103'から信号を一度受け取ると、メモリ回路はデータの読み出しが可能になるという点にある。しかしながら、自己タイミング復帰経路114を付加すると、モデルワード線112aとモデルビット線112bのRC遅延に付加的なRC遅延が必然的に追加される。自己タイミング復帰経路114により導入されるこの付加的なRC遅延は、メモリのアクセス動作を遅らせることになる。このため、制御ブロック回路110は、信号を自己タイミング復帰経路114から受け取るまで、読み出しレディ信号116を、センスアンプ104'に出力しない。その結果、高速メモリアクセスが必要な用途において、全体のメモリ回路の性能は、自己タイミング復帰経路114により生ずる付加的なRC遅延のため低下することになる。

## 【0009】

以上のことから、最悪ケースのモデルコアセルへのアクセスが実行される時に、不要なRC遅延の導入を排除する自己タイミングメモリ回路の必要性が存在する。

## 【0010】

## 【発明の概要】

要するに、この発明は、不要なRC遅延を取り除き、メモリアクセス動作を大幅に加速する自己タイミングメモリ回路のための方法と装置を提供することによって、上記の要請を満たすものである。この発明は、プロセス、装置、システム、デバイス、または方法を含む多くの態様で実施できることが認識されるべきである。この発明のいくつかの実施例を以下に説明する。

## 【0011】

一実施例としてメモリ回路が開示される。このメモリ回路はコアセルのアレイを含むメモリコアを有するものである。コアセルのアレイは複数のワード線と複数のビット線対とに接続される。このメモリ回路はさらに、モデルワード線に接続されたモデルコアセルを有する自己タイミング経路を有しており、このモデルワード線はモデルワード線ドライバにより駆動される。自己タイミング経路には、モデルビット線対を通じてモデルコアセルに接続されたモデルセンスアンプも含まれている。コアセルのアレイの最悪ケースコアセルのRC遅延を近似するため、モデルワード線とモデルビット線対のそれぞれは複数のダミーのコアセルに接続される。さらに、モデルワード線は、モデルワード線ドライバに近接した位置において終端を有するように折り返されたワード線である。

## 【0012】

別の実施例において、自己タイミング経路を有するメモリ回路の作成方法が開示されている。この方法は、コアセルのアレイを有するメモリコアを提供することを含む。この方法は、さらに、モデルワード線とモデルビット線対に沿ってコアセルの自己タイミング経路を集積化することを含むものである。モデルワード線は、モデルコアセルがモデルワード線のほぼ始端に配置され、そしてモデルワード線の終端がモデルコアセルに接続されるように折り返されている。

## 【0013】

また、別の実施例では、自己タイミング経路を有するメモリ回路を生成するためのメモリジェネレータが開示されている。このメモリ回路はコアセルのアレイを含むメモリコアを有している。この実施例において、メモリジェネレータは、モデルワード線とモデルビッ

10

20

30

40

50

ト線対に沿って、コアセルの自己タイミング経路を生成するように構成される。モデルワード線は、モデルコアセルがモデルワード線のほぼ始端に置かれ、モデルワード線の終端がモデルコアセルに接続されるように折り返されている。

【0014】

発明の他の特徴と優位点は、以下の添付図面とともに実施例に基づいて発明の原理を説明する発明の詳細な説明により明らかにする。

【0015】

この発明は、添付図面を参照した以下の詳細な記述により理解できるようにされている。ここで、同種の各構成要素は同種の参照番号により明示する。

【0016】

10

【好適な実施例の詳細な記述】

不要なRC遅延を排除し、メモリアクセス動作を大幅に加速する自己タイミングメモリ回路の発明を開示する。以下の記述において、多くの具体的な内容は、この発明の完全な理解を提供するために述べられるものである。この発明は、しかしながら、当業者にとっては、一部または全部の具体的な内容なしで実施することもできるものと了解されている。他の例では、周知のプロセス操作は詳細に説明していない。この発明を必要に不明瞭にしないようにするためである。

【0017】

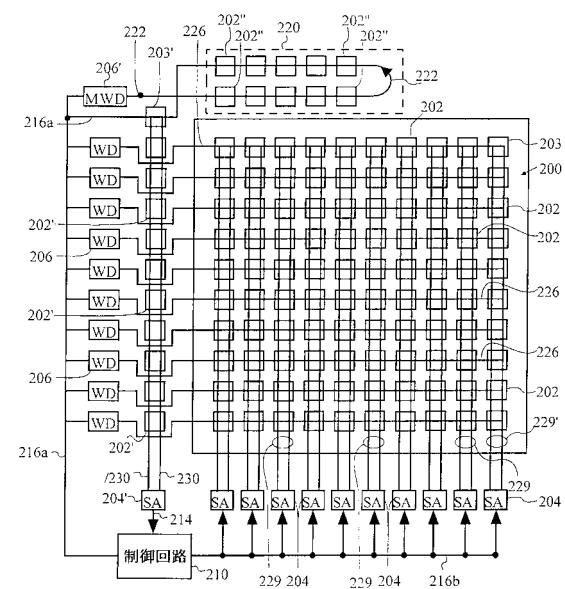

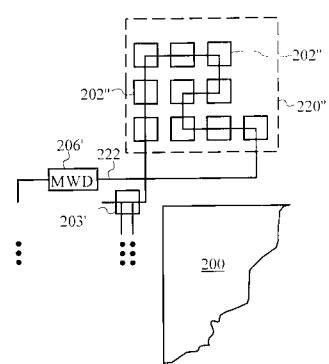

図2Aは、この発明の一実施例に従ったコアセル202のアレイを含むメモリコア200を有するメモリ回路を示す図である。図示されるように、コアセル202は、ワード線226を通してワード線ドライバ206に水平方向に接続されるとともに、ビット線229を通してセンスアンプ204に垂直方向に接続されている。また、ワード線ドライバ206とセンスアンプ204のそれぞれに接続された制御回路210も示されている。この例において、センスアンプ204は個別の複数のブロックとして示されるが、一般には、センスアンプは、周知のYデコーダ回路(図示せず)を通してビット線229のそれぞれに接続された一つの回路であることが理解されているべきである。

20

【0018】

良く知られているように、Yデコーダは、メモリコア200内の選ばれた列(すなわち、差動ビット線)をアドレス指定するために使われる。例えば、Yデコーダは、一般に、長いアドレス指定可能メモリ列をいくつかのより短いメモリ列に折り返して(例えば分割して)、メモリアレイの縦横比を減らすために使用される。いくつかの列に折り返されると、Yデコーダは、適切なマルチプレクス機能を適切に実行して、アドレス指定されたデータにアクセスすることができる。

30

【0019】

この実施例において、改善された自己タイミングアーキテクチャは、図1に示す従来の設計において使用される自己タイミング復帰経路114に起因する遅延を取り除くものとして開示されている。例えば、図2Aに示すように、ワード線222と差動ビット線(すなわち、230、/230)のRC遅延が、信号214により(モデルセンスアンプ204'から)制御回路210に速やかに伝達されると、読み出しレディ信号216が直ちに送信される。従来の設計の自己タイミング復帰経路に起因するRC遅延の除去は、主として、折り返されたワード線220により容易に実施されている。

40

【0020】

折り返されたワード線220は、半分のコアセル202'が残り半分のその上に積み重ねられたものを含むことが好ましい。この配置は、それゆえに、ワード線222の終端を、この例ではメモリコア200の上端の一番左側に配置されたモデルコアセル203'と接続するための効率的な経路を提供する。図示されるように、モデルビット線230、/230は、モデルコアセル203'に至るまで複数のコアセル202'を相互に接続する。作動時において、制御回路210が、信号216の立ち上がりエッジによってワード線イネーブル信号を、モデルワード線ドライバ206'に出力する時は、ワード線222と差動的なビット線230、/230を通じてモデルセンスアンプ204'に至る経路の分だ

50

けの R C 遅延が計算されることになる。

【 0 0 2 1 】

その時、モデルセンス信号 214 が制御回路 210 に提供される。制御回路 210 がこの信号 214 を受け取ると、制御回路 210 は、読み出しレディ信号 216 の立ち下がりエッジを選択された複数のセンスアンプ 204 に伝達する。この発明の自己タイミングアーキテクチャは、メモリコア 200 内のすべてのコアセル 202 とコアセル 203 に使用する標準遅延を提供するものである点に留意することが重要である。さらに、この標準遅延は、コアセル 203 を読むという最悪ケースのシナリオのための R C 遅延よりも大きくなっていることが好ましい。

【 0 0 2 2 】

10

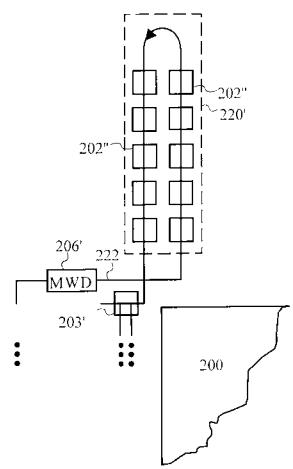

図 2B は、この発明の他の実施例に従った折り返されたワード線 220' の別の配置を示す図である。図示されるように、折り返されたワード線 220' は、図 2A の折り返されたワード線 220 に比べて、90 度ずれた角度で配置されている。この実施例は、折り返されたワード線 220' は、特定の設計に適するような方法によっても配置でき、水平に配置する必要はないことを示すものである。例えば、図 2C は、折り返されたワード線 220" の他の配置を示す。この配置は、特定の集積回路設計において、他の種々のロジックに適したものとなる可能性があるものである。

【 0 0 2 3 】

従って、モデルワード線ドライバ 206' の出力点の十分近くに折り返しのワード線 222 の終了経路を提供するものである限り、折り返しのワード線がどのように配置されているかは重要ではないことが理解されるべきである。適切に配置される時には、余分な R C 遅延が自己タイミング経路に含まれることはない。従って、モデルワード線 222 とモデルビット線 230、/230 を代表する R C 遅延だけが制御回路 210 によって使用され、読み出しレディ信号 216 をセンスアンプ 204 に提供されるべきことが決定される。

20

【 0 0 2 4 】

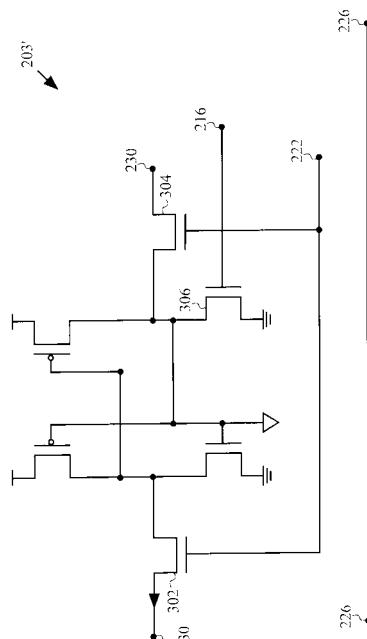

図 3 は、この発明の一実施例に従ったモデルコアセル 203' の例を示す図である。この実施例において、ワード線 226 は、モデルコアセル 203' とは相互接続されず、メモリコア 200 内のコアセル 202 に直接接続されている線として示されている。しかし、モデルワード線 222 は、トランジスタ 302 と 304 のゲートに接続されている。また、トランジスタ 304 の端子と接続されたモデルビット線 230、およびトランジスタ 302 の端子と接続される相補的なモデルビット線 /230 が示されている。さらに、信号 216 が、制御回路 210 からトランジスタ 306 のゲートに入力される。一般に、モデルコアセル 203' は、プルダウン動作を実行するように構成されており、このプルダウン動作は、メモリコア 200 内にあるコアセル 202 のプルダウンの強さを近似するように構成されている。

30

【 0 0 2 5 】

別の実施例において、モデルコアセル 203' は、特定のメモリコア 200 の深さに応じてプルダウンドライブを増大させるために適切に調整しても良い。例えば、モデルコアセル 203' は、プルダウン強度を高めるために、一つ以上のモデルコアセルと置き換えても良く、より大きいメモリコアの駆動に伴う遅延や制御回路 210 に起因する遅延などを取り除くために使用できる可能性がある。

40

【 0 0 2 6 】

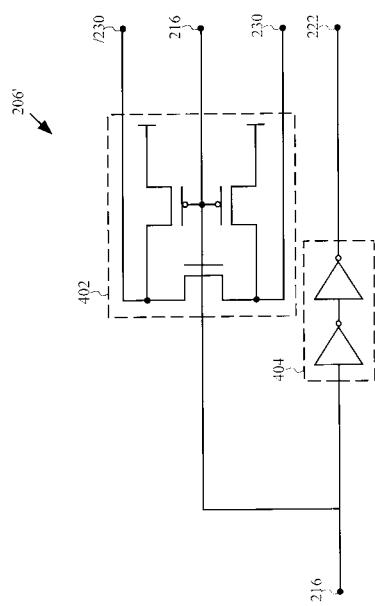

図 4 は、この発明の一実施例に従った図 2A に示されたモデルワード線ドライバ 206' の例を示す図である。このモデルワード線ドライバ 206' は、モデルビット線 230、/230 と信号 216 とに接続されたプレチャージ回路 402 を有するものとして示されている。また、信号 216 を受け取って、バッファされた信号をモデルワード線 222 上に出力するバッファ 404 が示されている。一般に、信号 216 がハイになる（すなわち、立ち上がりエッジを発生する）時に、モデルワード線ドライバ 206' がアクセス動作を開始するために起動される。さらに、バッファ 404 には、上の図 2A に示されるように、メモリコア 200 にアクセスするワード線ドライバ 206 が生ずる遅延を近似するた

50

めに、十分な遅延が設定されている。

【0027】

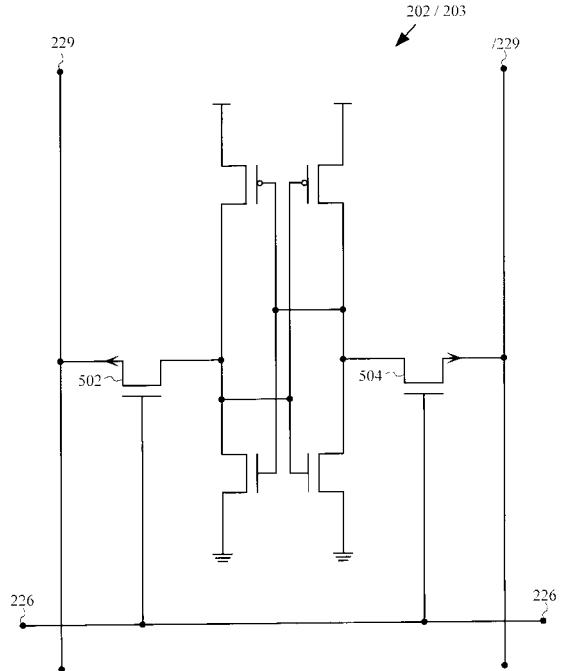

図5Aは、この発明の一実施例に従ったメモリコア200内のコアセル202、203の例を示す図である。図示されるように、相補的なビット線229、/229は、1対のパスゲートトランジスタ502、504のドレイン端子にそれぞれ接続されている。ワード線226は、パスゲートトランジスタ502、504のゲートに接続されている。ひとつの典型的なコアセル202/203が示されているが、この発明の実施例が他のコアセルと他のメモリ回路に適用可能であることは了解されるべきである。

【0028】

従って、この発明の実施例はのどのようなメモリ回路にでも適用できる。例えば、ROMメモリ回路、RAMメモリ回路、SRAMメモリ回路、DRAMメモリ回路、EPROMメモリ回路、EEPROMメモリ回路等である。メモリ回路とコアセルの詳細については、「The Art of Electronics第2版」(Paul Horowitz、Winfield Hill著)の812~820ページ(1996)を参照することができる。従って、この本は引用により明細書中に含まれる。

【0029】

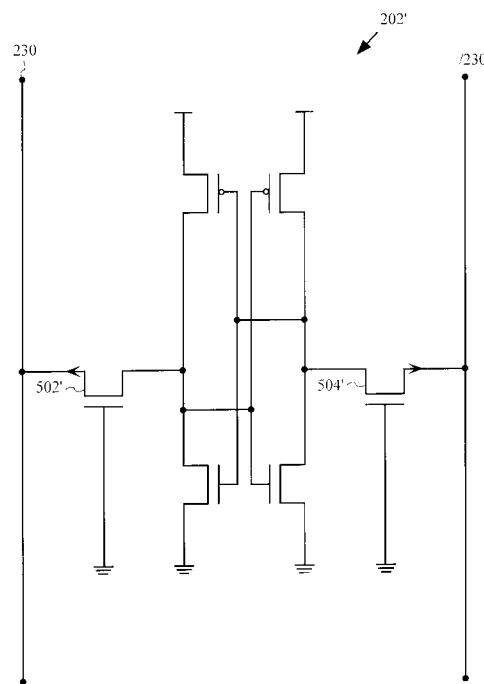

図5Bは、この発明の一実施例に従ったモデルビット線に沿って配置されたコアセル202'の例を示す図である。図示されるように、ビット線230は、パスゲートトランジスタ502'のドレイン端子に接続されており、ビット線/230はパスゲートトランジスタ504'のドレイン端子に接続されている。この実施例においてパスゲートトランジスタ502'、504'のそれぞれのゲートは接地されている。各々のコアセル202'は、一般に、メモリコア200のビット線229'において生ずるRC遅延を近似するために使用されるダミーのコアセルである。

【0030】

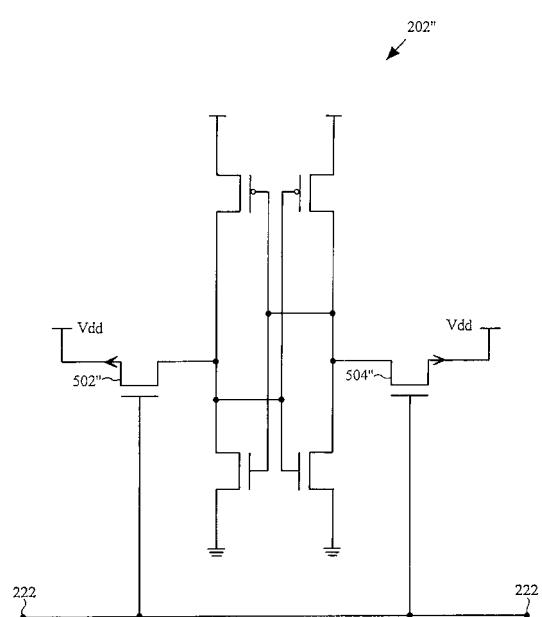

図5Cは、この発明の一つの実施例に従ったモデルワード線222に沿って配置されたコアセル202"の例を示す図である。図示されるように、パスゲートトランジスタ502"のドレイン端子はVddに接続されており、パスゲートトランジスタ504"のドレイン端子もVddに接続されている。この実施例においては、パスゲートトランジスタ502"、504"のそれぞれのゲートが、モデルワード線222に接続されている。コアセル202"のそれとも、一般に、メモリコア200のワード線226において生ずるRC遅延を近似するために使用されるダミーのコアセルである。

【0031】

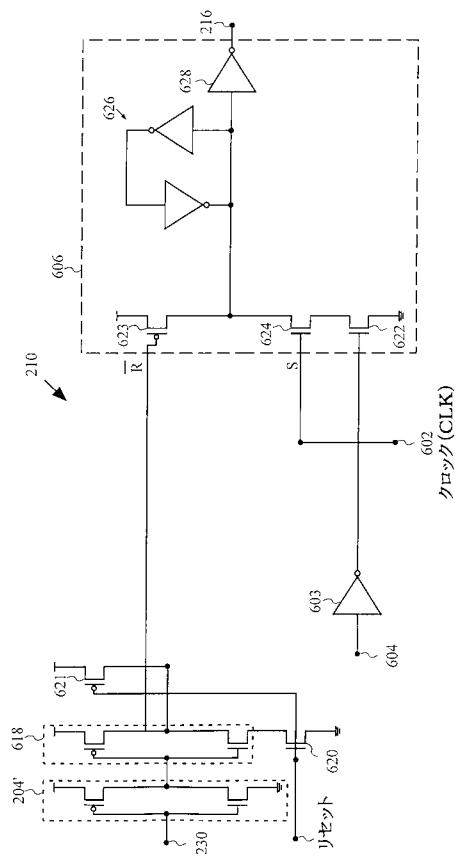

図6は、この発明の一実施例に従った図2Aの制御回路の回路図の例を示す図である。制御回路210は、一般に、モデルセンスアンプ204'、セッタリセットラッチ回路606とを有する。セッタリセットラッチ回路606は、一般に、リセット(/R)信号を受けるために使用するトランジスタ623と、クロック(CLK)602からSET(S)信号を受けるために使用するトランジスタ624とを有する。セッタリセットラッチ回路606は、また、インバータ603の出力にゲートが接続されたトランジスタ622を含んでおり、このインバータ603は入力604(これはCLK602の遅延である)を有している。

【0032】

セッタリセットラッチ回路606は、さらに、ラッチ626と、信号216を生成するインバータ628とを含んでいる。また、トランジスタ620のゲートとトランジスタ621のゲートとに伝達されるリセット信号が示されている。この例において、ビット線230はモデルセンスアンプ204'に接続されており、このモデルセンスアンプ204'はインバータ回路であることが示されている。このモデルセンスアンプ204'の出力はインバータ回路618に接続されている。一般に、リセット信号は、信号216の立ち下がりエッジが受け取られた後に伝達される。上述のように、信号216がロウになる時に(すなわち立ち下がりエッジで)、センスアンプには読み出しレディ信号が供給される。一方、信号216がハイになる時には、ワード線ドライバは、特定のセルにアクセスす

10

20

30

40

50

るよう信号で伝えられる。

【0033】

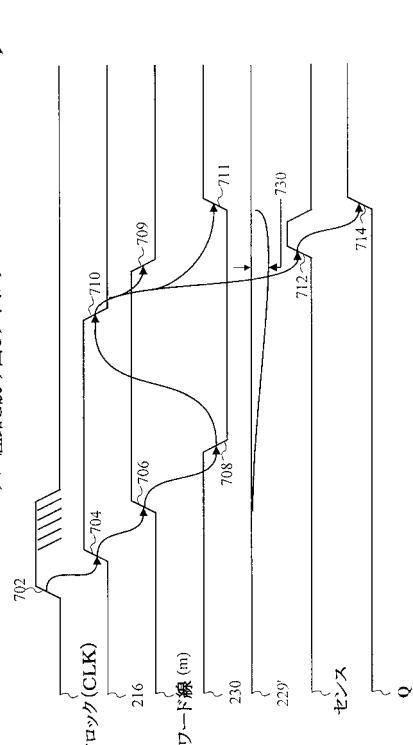

図7は、この発明の一実施例に従ったモデル経路と読み出しタイミング図700を示す図である。最初に、メモリクロック(CLK)信号に立ち上がりエッジ702が発生すると、これにより、信号216は立ち上がりエッジ704を生ずる。そして、信号216の立ち上がりエッジ704は、すべてのアドレス指定されたワード線(モデルワード線を含む)に立ち上がりエッジ706を生じさせる。この立ち上がりエッジ706は、モデルビット線230に立ち下がりエッジ708を生じさせる。立ち下がりエッジ708は、信号216の立ち下がりエッジ710を生じさせる。立ち下がりエッジ710は、ワード線とモデルワード線を立ち下げ、入力ラッチを開き、そしてビット線とデータバスをプレチャージするように作動する。

【0034】

上述に加えてさらに、信号216に立ち下がりエッジ710が発生する時に、センスアンプ204は読み出し開始を命じられ、センスライン上において立ち上がりエッジ712を発生させる。具体的には、立ち下がりエッジ710は、すべてのアドレスワード線(モデルワード線を含む)の立ち下がりエッジ709、およびビット線230の立ち上がりエッジ711を生じさせる。さらに、センス信号の立ち上がりエッジ712は、感知されたデータの値(このケースでは論理「1」)を反映した出力「Q」におけるエッジ714を生じさせる。ここで、立ち上がりエッジ712は、最悪ケースコアセル203に対してちょうど十分なビット線差730が達成された時とほとんど同時に発生することに留意することが重要である。

【0035】

現実に、従来技術における自己タイミング復帰経路114のRC遅延が取り除かれているので、モデルコアセル203'が十分なビット線差に達したときと、ほぼ同時に最悪ケースコアセル203が十分なビット線差に達する。不要な遅延が取り除かれているので、メモリ回路は非常に高いスピードでアクセス動作を有利に実行することができる。

【0036】

前述の発明は、明確に理解できるように詳細に説明されているが、変更や修正は、請求項の範囲内で行われうることは明らかである。従って、様々な回路図は以下に示すどのような形にも具体的に示されうることが了解されるべきである。例えば、半導体基板、プリント板、パッケージされた集積回路、またはソフトウェア等である。

【0037】

例えば、ニューヨーク州ニューヨーク市のIEEEから入手可能なVHDL(登録商標)ハードウェア記述言語のようなハードウェア記述言語設計や合成プログラムによりシリコンレベルの配置を設計することも可能である。従って、現実の実施例は制限的であることではなく、説明のためのものであると考える必要がある、そして、発明は、ここに記載された詳細に制限されるものではなく、請求項とその等価物の範囲で修正できる。

【図面の簡単な説明】

【図1】 図1は、メモリコアとそれに付随するアクセス回路を有するメモリ回路のプロック図である。

【図2A】 図2Aは、この発明の一実施例に従ったコアセルのアレイを含むメモリコアを有するメモリ回路を示す図である。

【図2B】 図2Bは、この発明の他の実施例に従った折り返しワード線の配置を示す図である。

【図2C】 図2Cは、この発明の他の実施例に従った折り返しワード線の配置を示す図である。

【図3】 図3は、この発明の一実施例に従ったモデルコアセルの例を示す図である。

【図4】 図4は、この発明の一実施例に従った図2Aに示されるモデルワード線ドライバの例を示す図である。

【図5A】 図5Aは、この発明の一実施例に従ったメモリコア内のコアセルの例を示す

10

20

30

40

50

図である。

【図 5 B】 図 5 B は、この発明の一実施例に従ったモデルピット線に沿って配置されたコアセルの例を示す図である。

【図5C】 図5Cは、この発明の一実施例に従ったモデルワード線に沿って配置されたコアセルの例を示す図である。

【図6】 図6は、この発明の一実施例に従った図2Aの制御回路の回路図の例を示す図である。

【図7】 図7は、この発明の一実施例に従ったモデル経路と読み出しタイミング図700を示す図である。

【 义 1 】

## 【 図 2 A 】

FIG. 1

(従来技術)

FIG. 2A

【図 2 B】

【図 3】

FIG. 3

【図 2 C】

FIG. 2C

【図 4】

FIG. 4

【図 5 A】

FIG. 5A

【図 5 B】

FIG. 5B

【図 5 C】

FIG. 5C

【図 6】

FIG. 6

【図 7】

FIG. 7

---

フロントページの続き

(74)代理人 100109759

弁理士 加藤 光宏

(72)発明者 コーナチャク・スティーブ・ピー・

アメリカ合衆国 カリフォルニア州 95131 サン・ホセ, ウッドメドウ・コート, 1573

(72)発明者 ベッカー・スコット・ティー・

アメリカ合衆国 カリフォルニア州 95132 サン・ホセ, クイーンズ・クロッシング・ドライブ, 1661

審査官 須原 宏光

(56)参考文献 特表平05-504648 (JP, A)

特開昭63-205891 (JP, A)

特開平07-211073 (JP, A)

特開平03-156795 (JP, A)

国際公開第97/024726 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

G11C 11/40-11/41