**(19) 대한민국특허청(KR)**

**(12) 특허공보(B1)**

(51) Int. Cl.<sup>4</sup>

B66B 1/24

(45) 공고일자 1987년03월19일

(11) 공고번호 특 1987-0000559

|            |                                                          |           |                |

|------------|----------------------------------------------------------|-----------|----------------|

| (21) 출원번호  | 특 1984-0002960                                           | (65) 공개번호 | 특 1985-0001117 |

| (22) 출원일자  | 1984년05월29일                                              | (43) 공개일자 | 1985년03월16일    |

| (30) 우선권주장 | 130711 1983년07월18일 일본(JP)                                |           |                |

| (71) 출원인   | 미쓰비시전기 주식회사<br>카다야마 히도하치로<br>일본국 토쿄도 지요다구 마루노우치 2 츠메 2-3 |           |                |

(72) 발명자

다나하시 도오루

일본국 아이찌켄 이나자와시 히시마찌 1 반지 미쓰비시전기주식회사 이

나자와세이사꾸쇼내

다데누마 이사오

일본국 아이찌켄 이나자와시 히시마찌 1 반지 미쓰비시전기주식회사 이

나자와세이사꾸쇼내

(74) 대리인

정우훈, 박태경

**심사관 : 고금영 (책자공보 제1273호)**

**(54) 엘리베이터의 속도제어장치**

### 요약

내용 없음.

### 대표도

### 도1

### 명세서

[발명의 명칭]

엘리베이터의 속도제어장치

[도면의 간단한 설명]

제1도, 제2도는 종래의 엘리베이터 속도제어장치의 한 예를 나타낸 요부회로도.

제3도는 본 발명에 의한 엘리베이터의 한 실시예를 나타낸 요부회로도.

제4도는 본 발명의 다른 실시예를 보인 회로도이다.

\* 도면의 주요부분에 대한 부호의 설명

2 : 주회로 개폐기            3 : 변환기

5 : 역변환기            6, 7 : 검출기

9 : 속도검출기

[발명의 상세한 설명]

본 발명은 엘리베이터의 속도제어장치의 개량에 관한 것이다.

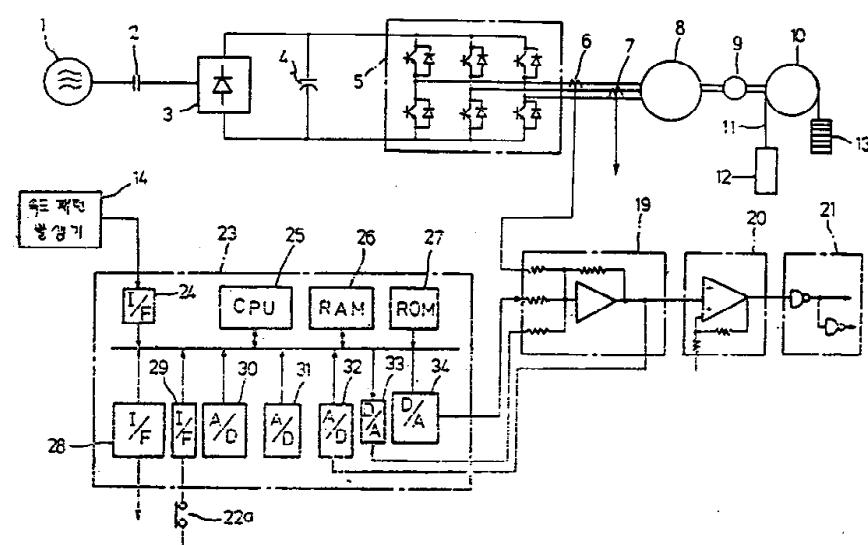

제1도는 인버터를 사용한 엘리베이터의 속도제어장치의 한 예를 나타낸 회로도이다.

여기서 1은 전원, 2는 주회로 개폐기(코일은 안그리고 접점만 나타났다), 3은 교류를 직류로 변환하는 변환기, 4는 변환기(3)의 출력전압을 평활화하는 콘덴서, 5는 직류를 교류로 변환하는 역변환기, 6,7은 역변환기(5)의 출력전류를 검출하는 전류 검출기, 8은 권상용 전동기, 9는 권상용 전동기(8)에 붙은 속도검출기, 10은 권상기, 11은 엘리베이터카(이하 카라 부른다)(12)와 균형추(13)를 접속하는 로우프, 14는 속도패턴 발생기, 15는 속도패턴 발생기(14)의 출력검출기(9)의 출력과를 비교하여 전류제어회로(16)-(18)에 전류지령을 내리는 속도연산회로, 16,17,18은 각각 U상, V상, W상의 전류제어회로다.

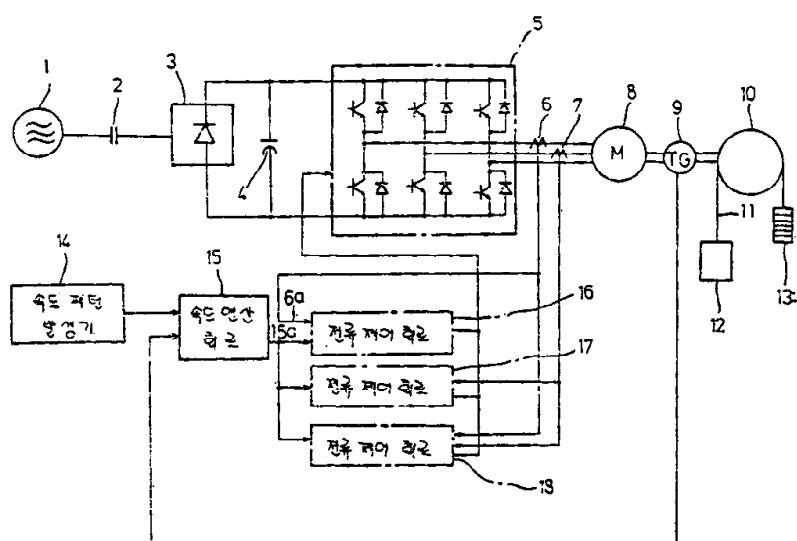

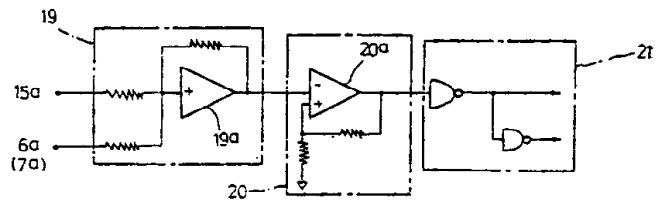

제2도는 제1도에서 보인 전류제어회로(16),(17),(18)의 상세부분을 나타낸 것이다.

어느 것이나 같은 구성을 지닌 것이므로 한 개만 나타내 있다.

그림 중의 19도는 속도연산회로(15)의 출력(15a)와, 전류검출기(6)의 출력(6a)를 비교하여 증폭하는 연산회로이며, 이 연산회로(19)는 복수개의 저항과 연산증폭기(19a)로 구성되어 있다.

이 연산회로(19)의 연산증폭기(19a)의 출력은 비교회로(20)의 비교기(20a)로 펄스폭이 변조되어 PWM 출력을 내어서 베이스 드라이브 회로(21)를 거쳐서 제1도에 나타낸 역변환기의 각 트랜지스터를 구동시킨다.

이같은 구성에 있어서, 전류검출기(6),(7)에는 일반적으로 호울소자를 사용한 전류검출기가 사용되고 있다.

그러나, 전류검출기(6),(7)는 온도의 변동, 혹은 경년변화에 따라 옵셋(off set)전압이 변동된다는 문제가 있었다.

즉, 역변환기(5)의 트랜지스터의 베이스가 차단되어 있는 때에도 전류검출기(6) 또는 (7)이 출력을 내고 있으며 이 출력이 옵셋전압인데, 옵셋전압은 늘 일정하지는 않고 변화한다.

이 때문에 전류검출기(6),(7)의 출력을 받아서 작동하는 각 전류제어회로(16),(17),(18)의 동작은 그 옵셋전압의 변동을 따라서 변동하게 되며, 그 결과 역변환기(5)의 출력전류에 직류분(分)이 나타나서 권상용 전동기(8)가 직류분에 의한 토오크립풀을 발생시킨다.

이 토오크립풀이 권상기(10), 로우프(11)를 거쳐서 카(12)에 전해지고, 카(12)안의 승객에게 불쾌감을 주는 결점이 있었다.

따라서 본 발명은 상기한 종래의 결점을 해소하기 위하여 행해진 것이며, 그 목적하는 바는 전류검출기의 옵셋전압에 의한 전동기로부터의 토오크립풀을 저감시켜서 카 안의 승객에게 주는 불쾌감을 제거한 엘리베이터의 속도제어장치를 제공하는데 있다.

본 발명의 다른 목적은 옵셋전압의 영향을 없애기 위하여 전류검출기의 옵셋전압을 검출하고, 그 검출치를 기준으로 역변환기에의 제어신호를 적당하게 변화시키도록 하는데 있다.

본 발명의 또 다른 하나의 목적은 전류검출기의 옵셋전압의 검출치가 역변환기의 제어 때문에 적정한 상태로 사용될 수 있게 하는데 있다.

이상과 같은 목적을 달성하기 위한 본 발명에 있어서는 교류를 직류로 변환하는 순변환기와 그것의 출력에 접속된 콘덴서와, 상기 콘덴서의 출력전압을 입력으로 하여 직류전력을 교류전원으로 변환하여 권상용 유도전동기를 구동하는 역변환기와, 상기 역변환기의 출력전류를 검출하는 전류검출기와 상기 전류검출기의 출력을 펄스폭 변조를 하여 상기 역변환기를 제어하는 전류제어회로와, 상기 전류검출기의 옵셋전압을 검출하여 상기 전류제어회로의 펄스폭 변조회로에 보상입력을 주는 기억수단과를 갖춘 것을 특징으로 하고 있다.

아래 도면을 사용하여 본 발명의 실시예를 상세히 설명한다.

제3도는 본 발명에 의한 엘리베이터의 속도제어장치의 한 실시예에 있어서의 전류제어회로를 나타낸 도면이다.

그 도면 중의 제2도와 동일 기호는 동일 또는 상당부분을 나타낸다.

22는 기억회로, 22a는 엘리베이터가 정지하여 제1도에 보이는 역변환기 (5)에 베이스차단이 걸린 때에 닫아지는 접점, 22b는 접점(22a)가 닫힌 때 연산회로(19)의 출력을 기억하는 콘덴서, 22c는 완충증폭기이며, 이 완충증폭기(22c)의 출력은 연산회로(19)의 연산증폭기(19a)에 입력되어 있다.

22d는 접점(22a)의 브레이크접점이다.

이같은 구성에 있어서, 엘리베이터가 정지하고 역변환기(5)의 트랜지스터의 베이스가 차단되어 있을 때 접점(22a)은 닫히고 접점(22d)은 개방되고, 또 이때의 전류검출기(6) 또는 (7)의 출력(6a) 또는 (7a)가 옵셋전압이다.

이제, 연산증폭기(19a)의 이득(Gain)을  $-Ki$ , 완충증폭기 22c의 이득을  $1/Ki$ , 전류검출기(6) 또는 (7)의 옵셋전압을  $Veo$ 로 하면, 연산증폭기(19a)의 출력전압  $Ve$ 는,  $Ve = -Ki \cdot Veo$ 가 되고, 콘덴서(22b)의 충전전압으로 기억된다. 다음에 역변환기(5)의 베이스 전류차단기가 해제되면 접점(22a)가 열리고 접점(22d)가 닫힌다. 이때 연산회로(19)에는 완충증폭기(22c)의 출력이 인가되고 전류검출기(6) 또는 (7)의 출력을 상쇄할 수가 있다.

이같이 하여 전류검출기(6) 또는 (7)의 옵셋전압에 의하여 권상용 전동기 (8)에서 발생하는 토오크립풀을 누를 수가 있어 쾌적한 느낌을 느낄 수가 있다.

엘리베이터는 항상 그 기동 및 정지가 자주 거듭되고 엘리베이터가 주행하는 상태를 장시간 유지하는 일은 없다.

따라서 상기 실시예처럼 앰프(19a)의 출력을 콘덴서(22b)에 의하여 엘리베이터 정지시 기억하도록 하더라도 콘덴서(22b)의 누설전류에 의하여 기억된 전압의 저하는 실용상 문제가 되지는 않는다. 더구나 이 실시예의 구성은 비교적 간단한 것이기 때문에 값싸게 만들 수가 있어서 제조상 극히 우리한 것이다.

한편 엘리베이터 중에는 정밀한 전동기제어가 요구되는 고급 엘리베이터가 있는데, 이같은 엘리베이터에 있어서는 옵셋전압의 기억이 정확히 행해지지 않으면 안된다.

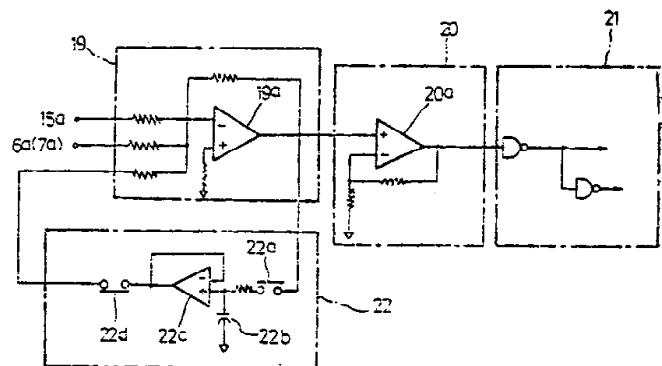

제4도는 이같은 목적을 바탕삼아서 그려진 다른 실시예를 나타낸 것이다.

도면의 제1-3도와 같은 부호로 표시된 부분은 그것들과 동일, 혹은 그에 상당하는 부분을 나타내고 있다.

여기에서 23은 마이크로컴퓨터에 의한 기억장치이며, 24는 속도패턴발생기(14)에서의 신호를 위한 인터페이스(Interface), 25는 연산처리를 하는 센트럴·프로세싱·유니트(CPU), 26은 갖가지 데이터를 써 넣든지 읽기 위한 랜덤·액세스·메모리(RAM), 27은 CPU(25)를 동작시키기 위한 프로그램등이 기억되어 있는 리이드 온리 메모리(ROM), 28은 인터페이스, 29는 엘리베이터의 주행 및 정지에 응동하여 개폐하는 접점(22a)의 동작상태를 입력하기 위한 인터페이스, 30-32는 아날로그신호를 디지털신호로 변환하는 AD변환기, 33 및 34는 디지털신호를 아날로그신호로 변환하는 DA변환기이다.

이같은 구성에 있어서 엘리베이터가 정지중에 역변환기(5)에 트랜지스터의 베이스차단이 걸려 있으면, 접점(22a)이 닫히고 CPU(25)가 A/D 콘버터(32)를 거쳐서 연산회로(19)의 출력(이것은 전류검출기의 6 또는 7 옵셋전압을 증폭한 값이 되어 있다)을 RAM(26)에 기억시킨다.

다음에 엘리베이터가 주행 역변환기(5)의 베이스차단이 해방되면 접점(22a)이 개방되고 CPU(25)는 이제껏 RAM(26)에 기억하고 있던 연산회로(19)의 출력을 D/A 콘버터(34)를 거쳐서 연산회로(19)에 출력한다.

그 결과 전류검출기 6의 출력은 상쇄되게 된다.

제3도의 실시예에 있어서는 콘덴서에서 옵셋전압을 기억하기 위하여 그 누설 전류에 의하여 주행중에 그 기억된 전압이 저하하는 문제가 있었는데, CPU를 써서 제4도의 방식에서는 그같은 불편은 없고 옵셋전압이 보정치를 일정하게 유지할 수가 있는 이점이 있다.

이상 설명대로 본 발명에 의하면 권상용 전동기에서 발생하는 토오크립틀을 확실히 억제할 수 있으므로쾌적한 탑승감을 느낄 수 있는 매우 뛰어난 효과를 얻을 수가 있다.

### (57) 청구의 범위

#### 청구항 1

엘리베이터카를 주행시키기 위한 전동기를 제어함으로 인하여 속도제어를 하는 엘리베이터의 속도제어장치로서,

- a) 전원(1)에서 공급되는 교류를 직류로 변환하는 제1의 변환기(3) ;

- b) 상기 제1의 변환기의 직류 출력단자에 걸쳐서 접속되며 상기 직류출력을 평활케하는 콘덴서(4) ;

- c) 상기 평활된 직류출력을 입력으로 삼고 직류를 교류로 변환하고 상기 전동기(8)에 공급하는 제2의 변환기(5) ;

- d) 상기 제2의 변환기의 교류출력을 검출하는 검출기(6, 7) ;

- e) 상기 검출기(6, 7)가 검출한 출력에 바탕을 두고 상기 제2의 변환기(5)를 제어하기 위한 신호를 변화시켜서 출력하는 제어장치를 갖춘 속도제어장치에 있어서,

상기 제2의 변환기(5)가 상기 교류출력을 내지 않는 상태에 있어서의 상기 검출기(6)의 출력을 검출하고 이것을 상기 제어장치(19)에 보내는 기억장치(22)를 갖춘 것을 특징으로 하는 엘리베이터의 속도제어장치.

#### 청구항 2

청구범위 제1항에 있어서,

상기 제어장치(19)는 그 입력으로서 상기 검출기(6)의 출력(6a)과 더불어 상기 기억장치(22)의 출력이 공급되어, 상기 제2변환기의 비출력상태에 있어서의 상기 검출기(6)의 출력이 상쇄되는 엘리베이터의 속도제어장치.

#### 청구항 3

청구범위 제2항에 있어서,

상기 제어장치는 상기 검출기의 출력을 입력으로 하여 동작하고 상기 제2변환기에 대한 제어신호 생성을 위한 출력을 내는 연산장치를 지니고 있으며, 상기 기억수단은 상기 연산장치의 출력을 검출하고 기억하는 엘리베이터의 속도제어장치.

#### 청구항 4

청구범위 제3항에 있어서,

상기 제어장치는 상기 기억장치의 기억내용은 상기 연산장치의 입력으로서 상기 연산장치의 입력부에 동시에 입력되는 엘리베이터의 속도제어장치.

#### 청구항 5

청구범위 제1항에 있어서,

상기 기억수단은 엘리베이터의 주행 및 정지에 연동하여 출력동작 및 기억동작을 하는 엘리베이터의 속도제어장치.

**청구항 6**

청구범위 제5항에 있어서,

상기 기억수단은 엘리베이터의 정지중, 상기 제어장치에 설치된 연산장치의 출력을 기억하여 엘리베이터의 주행중 그 기억한 내용을 상기 연산장치의 입력의 일부로서 공급하기 위하여 출력하는 엘리베이터의 속도제어장치.

**청구항 7**

청구범위 제6항에 있어서,

상기 기억수단의 입력부와 상기 연산장치의 출력부와의 사이에 엘리베이터 정지중은 문이 닫히며, 주행중은 문이 열리는 접점이 마련되고 상기 기억수단은 엘리베이터 정지 중 기억동작하는 엘리베이터의 속도제어장치.

**청구항 8**

청구범위 제7항에 있어서,

상기 기억장치의 출력부와 상기 연산장치의 입력부와의 사이에 엘리베이터 주행중은 닫히며 주행중은 개방 절점이 설치되고 상기 기억수단은 엘리베이터 주행중 출력작동하는 엘리베이터의 속도제어장치.

**청구항 9**

청구범위 제6항에 있어서,

상기 기억장치는 상기 연산장치의 출력부에 한끝이 접속된 콘덴서를 지니고 있는 엘리베이터 속도제어장치.

**청구항 10**

청구범위 제5항에 있어서,

상기 기억장치는 랜덤·액세스·메모리를 지니고 있는 엘리베이터의 속도제어장치.

**청구항 11**

청구범위 제10항에 있어서,

상기 기억장치에는 엘리베이터의 정지, 주행에 응동하여 개폐하는 접점의 동작상태가 입력되고 이 접점의 동작상태에 응하여 상기 랜덤·액세스·메모리가 기억 동작 혹은 출력동작하는 엘리베이터의 속도제어장치.

**도면****도면1**

도면2

도면3

도면4