(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2010-0057784

(43) 공개일자 2010년06월01일

(51) Int. Cl.

G11C 16/34 (2006.01) G11C 16/24 (2006.01)

(21) 출원번호 10-2010-7002519

(22) 출원일자(국제출원일자) 2008년07월02일

심사청구일자 없음

(85) 번역문제출일자 2010년02월03일

(86) 국제출원번호 PCT/US2008/068988

(87) 국제공개번호 WO 2009/006513

국제공개일자 2009년01월08일

(30) 우선권주장

11/773,032 2007년07월03일 미국(US)

11/773,035 2007년07월03일 미국(US)

(71) 출원인

샌디스크 코포레이션

미국 캘리포니아 95035 밀피타스 맥카시 블러바드

601

(72) 별명자

리 시-정

미국 캘리포니아 95035 밀피타스 맥카시 블러바드

601

(74) 대리인

박장원

전체 청구항 수 : 총 20 항

(54) 개선된 감지를 위해 상이한 기준 레벨들을 이용하는 비휘발성 메모리에서의 비정밀/정밀 프로그램 검증

### (57) 요 약

비휘발성 메모리의 비정밀/정밀 프로그래밍(coarse/fine programming)이 제공되는 바, 여기에서 메모리 셀들은 자신들의 의도된 상태에 대한 비정밀 검증 레벨에 도달하기 전에는 제 1 프로그래밍 속도(rate of programming)로 프로그램되고, 상기 비정밀 검증 레벨에는 도달하였지만 자신들의 의도된 상태에 대한 최종 검증 레벨에 도달하기 전에는 제 2 프로그래밍 속도로 프로그램된다. 보다 작은 메모리 셀들과 관련된 큰 서브 임계 스윙 팩터들(sub-threshold swing factors)은, 특히 상이한 감지 사이에서 비트라인을 프리챠지(pre-charge)시키지 않으면서 비정밀 검증 레벨에서 감지한 후 정밀 검증 레벨에서 감지할 때, 감지 동작들의 정확성에 영향을 미칠 수 있다. 비정밀 검증 레벨 및 최종 검증 레벨에서 감지할 때, 상이한 기준 전위(reference potential)들이 이용된다. 상기 기준 전위들 간의 차이는 비정밀 레벨 감지 동안 상기 비트라인의 어떠한 방전도 보상할 수 있다.

대 표 도 - 도19

## 특허청구의 범위

### 청구항 1

비휘발성 메모리를 프로그램하는 방법으로서,

비휘발성 저장 요소들의 세트의 하나 이상의 저장 요소들을 특정 상태로 프로그램하기 위해, 상기 비휘발성 저장 요소들의 세트에 하나 이상의 프로그래밍 펄스들을 인가하는 단계와;

각 프로그래밍 펄스를 인가한 이후, 상기 저장 요소들의 세트에 제 1 전압을 인가하고 상기 하나 이상의 저장 요소들 각각의 비트라인 전압을 제 1 기준 전위와 비교함으로써, 상기 특정 상태에 대응하는 중간 검증 레벨로의 상기 하나 이상의 저장 요소들의 프로그래밍을 검증하는 단계와;

각 프로그래밍 펄스를 인가한 후, 상기 저장 요소들의 세트에 제 2 전압을 인가하고 상기 하나 이상의 저장 요소들 각각의 비트라인 전압을 제 2 기준 전위와 비교함으로써, 상기 특정 상태에 대응하는 최종 검증 레벨로의 상기 하나 이상의 저장 요소들의 프로그래밍을 검증하는 단계를 포함하고,

여기서, 상기 제 2 기준 전위는, 상기 중간 검증 레벨로의 프로그래밍의 검증으로부터 야기되는 상기 하나 이상의 저장 요소들 각각의 비트라인 전압의 감소를 보상하는 것을 특징으로 하는 비휘발성 메모리를 프로그램하는 방법.

### 청구항 2

제 1 항에 있어서,

상기 제 2 기준 전위는, 상기 하나 이상의 저장 요소들이 상기 중간 검증 레벨 이상일 때, 상기 중간 검증 레벨로의 프로그래밍의 검증으로부터 야기되는 상기 하나 이상의 저장 요소들 각각의 비트라인 전압의 감소를 보상하기 위한 레벨로 제공되는 것을 특징으로 하는 비휘발성 메모리를 프로그램하는 방법.

### 청구항 3

제 1 항에 있어서,

상기 제 2 기준 전위는, 상기 제 1 전압이 인가되고 상기 하나 이상의 저장 요소들이 상기 중간 검증 레벨 이상일 때, 상기 하나 이상의 비휘발성 저장 요소들의 비트라인이 방전될 양과 실질적으로 동일한 양 만큼 상기 제 1 기준 전위 보다 작은 것을 특징으로 하는 비휘발성 메모리를 프로그램하는 방법.

### 청구항 4

제 1 항에 있어서,

상기 제 2 기준 전위는, 상기 제 1 전압이 인가될 때, 상기 중간 검증 레벨 이상에서의 저장 요소에 대한 비트라인 방전량과 실질적으로 동일한 양 만큼 상기 제 1 기준 전위 보다 작은 것을 특징으로 하는 비휘발성 메모리를 프로그램하는 방법.

### 청구항 5

제 1 항에 있어서,

상기 각 프로그래밍 펄스를 인가한 이후 그리고 상기 중간 검증 레벨로의 프로그래밍의 검증 이전에, 상기 하나 이상의 저장 요소들과 통신하는 비트라인들의 세트를 프리차지(pre-charge)시키는 단계를 더 포함하며,

상기 중간 검증 레벨로의 프로그래밍을 검증하는 단계는,

상기 비트라인들의 세트 및 상기 하나 이상의 저장 요소들과 통신하는 선택 게이트들의 세트를 개방(open)하는 단계와; 그리고

상기 선택 게이트들의 세트를 개방하는 단계에 후속하여 미리 결정된 시간량 이후 상기 하나 이상의 저장 요소들 각각의 비트라인 전압을 감지하는 단계를 포함하며,

상기 최종 검증 레벨로의 프로그래밍을 검증하는 단계는, 상기 선택 게이트들의 세트를 개방하는 단계에 후속하여 미리 결정된 다른 시간량 이후 상기 하나 이상의 저장 요소들 각각의 비트라인 전압을 감지하는 단계를 포함하는 것을 특징으로 하는 비휘발성 메모리를 프로그램하는 방법.

#### 청구항 6

제 5 항에 있어서,

상기 비휘발성 저장 요소들의 세트는 제 1 워드라인과 통신하며; 그리고

상기 비트라인들의 세트는 비트라인들의 그룹 내에 하나 걸러마다(every other) 비트라인을 포함하는 것을 특징으로 하는 비휘발성 메모리를 프로그램하는 방법.

#### 청구항 7

제 1 항에 있어서,

각 프로그래밍 펠스를 인가한 이후 그리고 상기 중간 검증 레벨로의 프로그래밍을 검증하는 단계 이전에, 상기 하나 이상의 저장 요소들과 통신하는 비트라인들의 세트를 프리챠지시키는 단계를 더 포함하며,

상기 최종 검증 레벨로의 프로그래밍을 검증하는 단계는, 상기 중간 검증 레벨로의 프로그래밍을 검증하는 단계 이후 상기 비트라인들의 세트를 프리챠지시키는 것을 포함하지 않는 것을 특징으로 하는 비휘발성 메모리를 프로그램하는 방법.

#### 청구항 8

제 7 항에 있어서,

상기 비트라인들의 세트는 비트라인들의 그룹 내에 하나 걸러마다 비트라인을 포함하는 것을 특징으로 하는 비휘발성 메모리를 프로그램하는 방법.

#### 청구항 9

제 1 항에 있어서,

상기 세트의 하나 이상의 다른 저장 요소들을 상이한 상태로 프로그램하기 위해, 하나 이상의 추가적인 프로그래밍 펠스들을 상기 세트에 인가하는 단계와; 그리고

각 추가적인 프로그래밍 펠스를 인가한 후, 상기 상이한 상태에 대응하는 다른 최종 검증 레벨로의 상기 하나 이상의 저장 요소들의 프로그래밍을 검증하는 단계를 더 포함하며,

여기서, 상기 다른 최종 검증 레벨은 상기 특정 상태에 대한 상기 중간 검증 레벨 및 상기 최종 검증 레벨 보다 높은 것을 특징으로 하는 비휘발성 메모리를 프로그램하는 방법.

#### 청구항 10

제 1 항에 있어서,

상기 중간 검증 레벨은 비정밀 검증 전압(coarse verify voltage)인 것을 특징으로 하는 비휘발성 메모리를 프로그램하는 방법.

#### 청구항 11

비휘발성 저장 요소들의 세트와; 그리고

상기 저장 요소들의 세트와 통신하는 관리 회로를 포함하며,

여기서, 상기 관리 회로는,

상기 세트의 하나 이상의 저장 요소들을 특정 상태로 프로그램하기 위해, 상기 세트에 하나 이상의 프로그래밍 펠스들을 인가하고;

각 프로그래밍 펠스를 인가한 이후, 상기 관리 회로는 상기 저장 요소들의 세트에 제 1 전압을 인가하고 상기

하나 이상의 저장 요소들 각각의 비트라인 전압을 제 1 기준 전위와 비교함으로써, 상기 특정 상태에 대응하는 중간 검증 레벨로의 상기 하나 이상의 저장 요소들의 프로그래밍을 검증하고;

각 프로그래밍 펄스를 인가한 후, 상기 관리 회로는 상기 저장 요소들의 세트에 제 2 전압을 인가하고 상기 하나 이상의 저장 요소들 각각의 비트라인 전압을 제 2 기준 전위와 비교함으로써, 상기 특정 상태에 대응하는 최종 검증 레벨로의 상기 하나 이상의 저장 요소들의 프로그래밍을 검증하며;

여기서, 상기 제 2 기준 전위는, 상기 중간 검증 레벨로의 프로그래밍의 검증으로부터 야기되는 상기 하나 이상의 저장 요소들 각각의 비트라인 전압의 감소를 보상하는 것을 특징으로 하는 비휘발성 메모리 시스템.

## 청구항 12

제 11 항에 있어서,

상기 관리 회로는, 상기 하나 이상의 저장 요소들이 상기 중간 검증 레벨 이상일 때, 상기 중간 검증 레벨로의 프로그래밍의 검증으로부터 야기되는 상기 하나 이상의 저장 요소들 각각의 비트라인 전압의 감소를 보상하기 위한 레벨로 상기 제 2 기준 전위를 제공하는 것을 특징으로 하는 비휘발성 메모리 시스템.

## 청구항 13

제 11 항에 있어서,

상기 제 2 기준 전위는, 상기 제 1 전압이 인가되고 상기 하나 이상의 저장 요소들이 상기 중간 검증 레벨 이상일 때, 상기 하나 이상의 비휘발성 저장 요소들의 비트라인이 방전될 양과 실질적으로 동일한 양 만큼 상기 제 1 기준 전위 보다 작은 것을 특징으로 하는 비휘발성 메모리 시스템.

## 청구항 14

제 11 항에 있어서,

상기 제 2 기준 전위는, 상기 제 1 전압이 인가될 때, 상기 중간 검증 레벨 이상에서의 저장 요소에 대한 비트라인 방전량과 실질적으로 동일한 양 만큼 상기 제 1 기준 전위 보다 작은 것을 특징으로 하는 비휘발성 메모리 시스템.

## 청구항 15

제 11 항에 있어서,

상기 하나 이상의 저장 요소들 및 상기 관리 회로와 통신하는 비트라인들의 세트와; 그리고

상기 비트라인들의 세트 및 상기 하나 이상의 저장 요소들과 통신하는 선택 게이트들의 세트를 더 포함하며,

상기 관리 회로는, 상기 각 프로그래밍 펄스를 인가한 이후 그리고 상기 중간 검증 레벨로의 프로그래밍의 검증 이전에, 상기 비트 라인들의 세트를 프리챠지시키고;

상기 관리 회로는, 상기 선택 게이트들의 세트를 개방시킴으로써 상기 중간 검증 레벨로의 프로그래밍을 검증하고, 상기 선택 게이트들의 세트를 개방하는 것에 후속하여 미리 결정된 시간량 이후 상기 하나 이상의 저장 요소들 각각의 비트라인 전압을 감지하며; 그리고

상기 관리 회로는, 상기 선택 게이트들의 세트를 개방하는 것에 후속하여 미리 결정된 다른 시간량 이후 상기 하나 이상의 저장 요소들 각각의 비트라인 전압을 감지함으로써 상기 최종 검증 레벨로의 프로그래밍을 검증하는 것을 특징으로 하는 비휘발성 메모리 시스템.

## 청구항 16

제 15 항에 있어서,

상기 비휘발성 저장 요소들의 세트와 통신하는 제 1 워드라인을 더 포함하며,

상기 비트라인들의 세트는 비트라인들의 그룹 내에 하나 걸러 마다 비트라인을 포함하는 것을 특징으로 하는 비휘발성 메모리 시스템.

**청구항 17**

제 11 항에 있어서,

상기 하나 이상의 저장 요소들과 통신하는 비트라인들의 세트를 더 포함하며,

상기 관리 회로는, 각 프로그래밍 펄스를 인가한 이후 그리고 상기 중간 검증 레벨로의 프로그래밍을 검증하기 전에, 상기 비트라인들의 세트를 프리챠지시키고,

상기 관리 회로는, 상기 최종 검증 레벨로의 프로그래밍을 검증하기 위해, 상기 중간 검증 레벨로의 프로그래밍을 검증한 이후 상기 비트라인들의 세트를 프리챠지시키지 않는 것을 특징으로 하는 비휘발성 메모리 시스템.

**청구항 18**

제 17 항에 있어서,

상기 비트라인들의 세트는 비트라인들의 그룹 내에 하나 걸러 마다 비트라인을 포함하는 것을 특징으로 하는 비휘발성 메모리 시스템.

**청구항 19**

제 11 항에 있어서,

상기 비휘발성 저장 요소들의 세트는 NAND 플래시 메모리 셀들의 세트인 것을 특징으로 하는 비휘발성 메모리 시스템.

**청구항 20**

제 11 항에 있어서,

상기 중간 검증 레벨은 비정밀 검증 전압인 것을 특징으로 하는 비휘발성 메모리 시스템.

**명세서****기술분야**

[0001]

본 발명은 비휘발성 메모리의 프로그래밍에 관한 것이다.

**배경기술**

[0002]

반도체 메모리 디바이스들을 다양한 전자 디바이스들에 사용하는 것이 점점 보편화되고 있다. 예를 들어 비휘발성 반도체 메모리는 휴대 전화기, 디지털 카메라, 개인 휴대 정보 단말기, 휴대용 연산 장치, 비-휴대용 연산 장치 및 기타 장치에서 사용된다. 전기적으로 소거 가능하고 프로그램 가능한 읽기 전용 메모리(EEPROM, Electrical Erasable Programmable Read Only Memory) 및 전자적으로 프로그램 가능한 읽기 전용 메모리(EPROM, Electronically Programmable Read Only Memory)가 가장 보편적인 비휘발성 반도체 메모리이다.

[0003]

EEPROM과 EPROM 메모리는, 반도체 기판의 채널 영역 위에 위치되어 채널 영역으로부터 절연되는 플로팅 게이트(floating gate)를 이용한다. 상기 플로팅 게이트는 소스와 드레인 영역 사이에 위치한다. 제어 게이트(control gate)는 상기 플로팅 게이트 위에 플로팅 게이트와 절연된 상태로 제공된다. 상기 트랜지스터의 임계 전압(threshold voltage)은 상기 플로팅 게이트 상에 유지되는 전하량에 의해 제어된다. 트랜지스터의 소스와 드레인 사이가 도통(conduction)이 되도록 트랜지스터가 터온되기 전에 상기 제어 게이트에 인가되어야만 하는 최소 전압의 크기는 상기 플로팅 게이트 상의 전하 레벨에 의해 제어된다.

[0004]

플래시 메모리 디바이스를 프로그램할 때, 보통 프로그램 전압은 상기 제어 게이트에 인가되고 비트라인은 접지된다. 상기 채널로부터의 전자들은 상기 플로팅 게이트 내로 주입된다. 전자들이 상기 플로팅 게이트 내에 축적되면, 상기 플로팅 게이트는 음(negative)으로 대전(charge)되고, 상기 메모리 셀의 임계 전압은 증가되며, 결과적으로 상기 메모리 셀이 프로그램된 상태가 된다.

[0005]

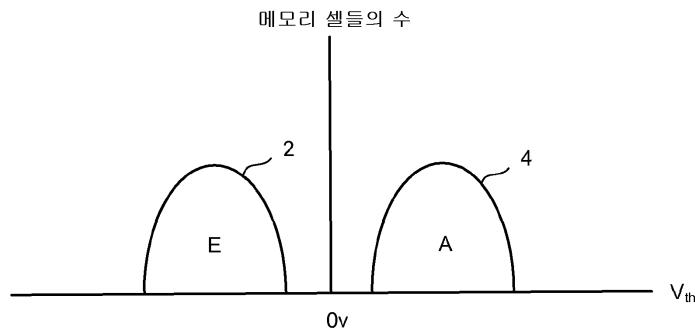

몇몇 EEPROM과 플래시 메모리 디바이스들은 두 범위의 전하들을 저장하는 데 사용되는 플로팅 게이트를 가지고 있으며, 이에 따라 상기 메모리 셀은 두 개의 상태(소거된 상태 및 프로그램된 상태) 사이에서 프로그램/소거될 수 있다. 예를 들어, 도 1은 두 개의 임계 전압의 분포를 나타낸 그래프이다. x축은 임계 전압을 나타내며, y축

은 메모리 셀의 개수를 나타낸다. 분포(2)의 임계 전압은 0V 보다 작다. 일 실시예에 있어서, 임계 전압 분포(2)는 데이터 "1"을 저장하는 소거된 메모리 셀들에 해당한다. 분포(4)의 임계 전압은 0 볼트보다 크다. 일 실시예에서, 임계 전압 분포(4)는 데이터 "0"을 저장하는 프로그램된 메모리 셀들에 해당한다.

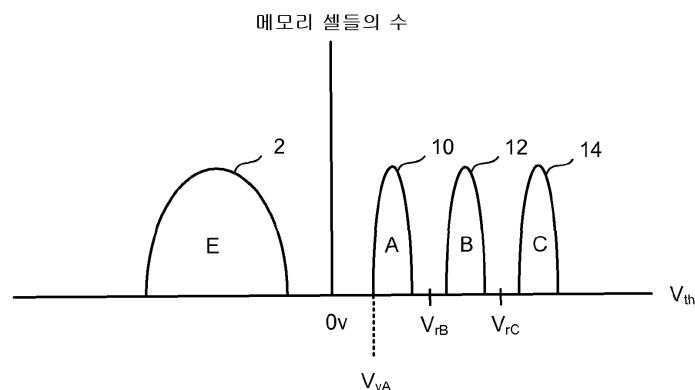

[0006] 다중-상태(multi-state) 플래시 메모리 셀은, 금지된(forbidden) 전압 범위들에 의해 분리되는 복수 개의 별개로 허용된 임계 전압 범위들을 식별함으로써 실시된다. 각각의 별개의 임계 전압 범위는 데이터 비트들의 세트(set)에 관한 미리 결정된 값에 해당한다. 도 2는 네 개의 데이터 상태들을 이용하여 데이터의 두 개의 비트들의 데이터를 저장하는 메모리 셀의 임계 전압 분포를 나타낸 것이다. 일 실시예에 있어서, 임계 전압 분포(2)는 음(negative)의 임계 전압 레벨들을 가지며, 소거된 상태(예를 들어, "11"을 저장한 상태)의 메모리 셀을 표시한다. 임계 전압 분포(10)는 양(positive)의 임계 전압 레벨들을 가지며, 데이터 "10"을 저장한 메모리 셀을 나타낸다. 임계 전압 분포(12)는 데이터 "00"을 저장한 메모리 셀을 나타낸다. 임계 전압 분포(14)는 "01"을 저장하고 있는 메모리 셀을 나타낸다. (상기 예시한 바와 같은) 몇몇 실시예에서, 이러한 데이터 값들(예를 들어, 논리 상태(logical state))은 그레이 코드 할당(gray code assignment)을 이용하여 상기 임계 범위로 지정되는 데, 이는 플로팅 게이트의 임계 전압이 플로팅 게이트의 임계 전압에 인접한 물리적 상태로 잘못 천이하였을 때라도 단지 하나의 논리 비트만 영향을 받도록 하기 위함이다. 다른 실시예에서, 각각의 분포들은 상술한 것과 다른 데이터 상태에 해당할 수 있다. 메모리 셀 내에 프로그램되는 데이터와 상기 셀의 임계 전압 범위들과의 소정의 관계는 상기 메모리 셀에 대해 채택되는 데이터 인코딩 체계(encoding scheme)에 따라 좌우된다. 예를 들어, 2003년 6월 13일 출원되었으며 그 명칭이 "Tracking Cells For A Memory System"인 미국 특허 출원 번호 제10/461,244호 및 미국 특허 제 6,222,762호는 다중-상태의 플래시 메모리 셀을 위한 다양한 인코딩 체계를 개시하는 바, 상기 두 출원은 본원의 참조로서 그 전체가 인용된다. 또한, 본 발명에 따른 실시예는 2 비트 이상의 데이터를 저장하는 메모리 셀에 적용될 수 있다.

[0007] 임계 전압 분포들(2 및 4)은 어떠한 검증 동작도 수행되지 않았을 때의 소거 및 프로그램된 전압-분포를 보여준다. 이러한 분포들은 하나의 단일 프로그래밍이나 소거 펄스로 상기 메모리 셀을 프로그램하거나 소거함으로써 획득될 수 있다. 상기 메모리 어레이의 크기와 제조 프로세스의 변동에 따라, 상기 임계 전압 분포(4)는 자연적인  $V_{th}$  폭(natural  $V_{th}$  width)이라고 알려진 소정의 폭을 가질 수 있다.

[0008] 도 2로부터 알 수 있는 바와 같이, (다중 상태 디바이스의 프로그래밍에 해당하는) 임계 전압 분포들(10, 12 및 14)은 임계 전압 분포(4)의 자연적인  $V_{th}$  폭 보다 훨씬 좁을 것이 요구된다. 이렇게 좁은 임계 전압 분포들을 획득하기 위해서는, 도 3A, 3B 및 도 3C에 도시된 바와 같이, 다중 프로그래밍 펄스들과 검증 동작들을 이용하는 프로세스가 이용될 수 있다.

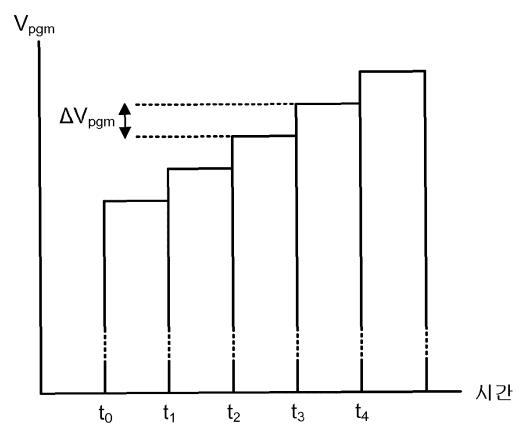

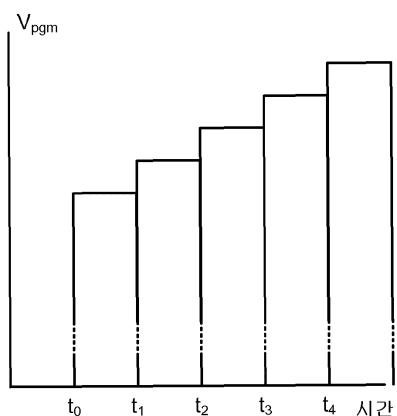

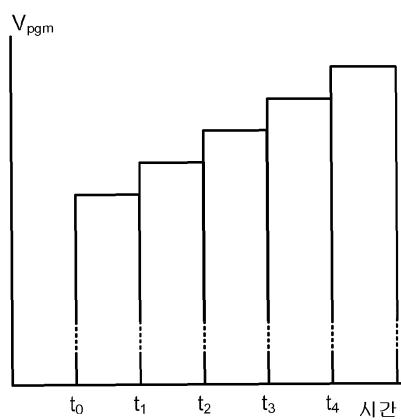

[0009] 도 3A는 제어 게이트에 인가되는 프로그래밍 전압 신호( $V_{pgm}$ )를 일련의 펄스들로서 나타낸 것이다. 펄스의 크기는, 도 3A에  $\Delta V_{pgm}$ 으로 나타낸 바와 같이, 각 연속적인 펄스 마다 미리 결정된 스텝(step) 크기(예를 들어, 0.2V - 0.4V) 만큼 증가된다. 상기 펄스들 사이의 주기에서, 검증 동작이 수행된다. 프로그램 가능한 상태들의 개수가 증가할수록, 검증 동작의 개수가 증가하며, 시간 또한 더 필요하다. 상기 시간에 대한 부담을 줄이기 위한 하나의 수단은, 2002년 12월 5일 출원되었으며 그 명칭이 "Smart Verify For Multi-State Memories"인 미국 특허 출원 제10/314,055호에 개시된 것과 같은 보다 효율적인 검증 프로세스를 이용하는 것이며, 상기 특허 출원은 본원의 참조로서 그 전체가 인용된다. 실제로, 도 3A의 펄스들은 검증하는 동안의 시간 간격에 의해 각각 분리된다. 그러나, 도 3을 읽기 쉽게 하기 위해, 검증의 시간 간격은 도면에서 생략되었다.

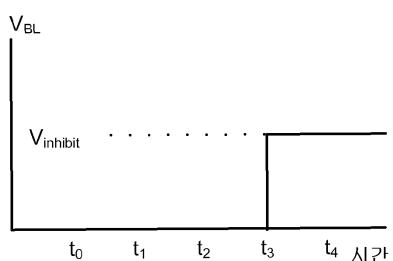

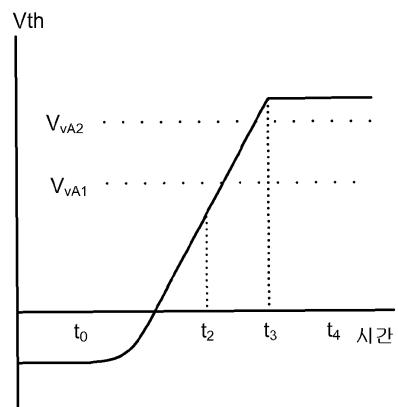

[0010] 도 3B는 상기 프로그램된 관련 메모리 셀의 비트라인에 인가되는 전압 신호를 나타낸다. 도 3C는 상기 프로그램된 메모리 셀의 임계 전압을 나타낸다. 도 3C에서의 그래프는 읽기 쉽도록 완만(smooth)하게 도시하였다. 각 프로그래밍 펄스 이후, 검증 동작(미도시)이 수행된다. 검증 동작 동안, 상기 프로그램된 메모리 셀의 임계 전압이 점검된다. 만약 메모리 셀의 임계 전압이 목표 값(예를 들어,  $V_{verify}$ )보다 크다면, 비트라인 전압을 0V에서  $V_{inhibit}$ (예를 들어,  $t_4$ 에서의)까지 증가시킴으로써 그 메모리 셀에 대한 프로그래밍은 다음 사이클에서 금지된다.

[0011] 다른 전자 디바이스들과 마찬가지로, 소비자는 가능한 한 빨리 프로그램할 수 있는 메모리 디바이스를 요구한다. 예를 들어, 플래시 메모리 카드에 이미지들을 저장하는 디지털 카메라의 사용자는 사진과 사진 사이에 필요없이 오랜 시간 동안 기다리는 것을 원치 않는다. 합리적인 속도로 프로그램하는 것에 외에, 다중-상태 메모리 셀에서 적절한 데이터 스토리지(storage)를 확보하기 위해서는, 상기 다중-상태 메모리 셀의 임계 전압들의 복수개의 범위가 충분한 여유를 가지고 서로 분리되어 있어야만 하는 바, 그래야만 메모리 셀의 레벨들이 명백한(unambiguous) 방식으로 프로그램되고 판독될 수 있기 때문이다. 조밀한 임계 전압 분포가 권장된다. 조

밀한 임계 전압 분포를 얻기 위해, 일반적으로 작은(small) 프로그램 단계들을 이용하는데, 이에 의해 메모리 셀의 임계 전압에 대한 프로그래밍을 더욱 느리게 한다. 원하는 임계 전압 분포가 조밀하면 조밀할수록, 프로그래밍 단계들은 작아지고, 상기 프로그래밍 프로세스의 속도 역시 더 느려진다.

[0012] 조밀한 임계 전압 분포들을 얻기 위한 방법 중의 하나의 해결책은, 이유없이 프로그래밍 프로세스가 늦어지는 일이 없도록, 두 개의 페이즈(two-phase) 프로그래밍 프로세스를 이용하는 것을 포함한다. 첫번째 페이즈는 비정밀(coarse) 프로그래밍 페이즈로, 이 페이즈에서는 좀 더 빠른 방식으로 임계 전압을 증가시키는 것이 주요 관심사이며, 조밀한 임계 전압 분포에는 상대적으로 관심이 적다. 두 번째 페이즈는 정밀(fine) 프로그래밍 페이즈로, 이 페이즈는 목표 임계 전압에 도달하기 위해서 좀 더 느린 방식으로 임계 전압을 증가시키는 반면에, 조밀한 임계 전압 분포를 획득하고자 하는 페이즈이다. 비정밀/정밀 프로그래밍에 대한 실시예는 미국 특허 제 6,643,188호에 개시되어 있으며, 이는 본원의 참조로서 그 전체가 인용된다.

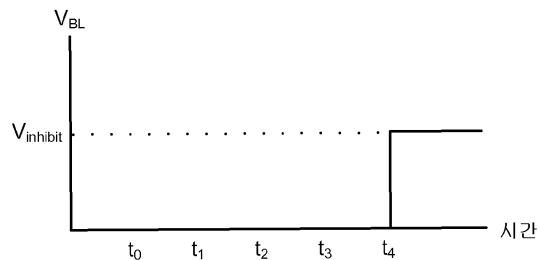

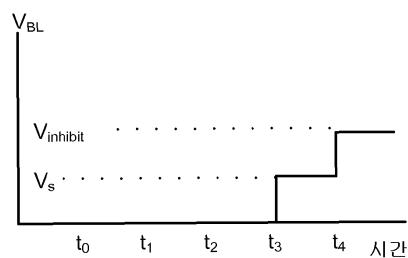

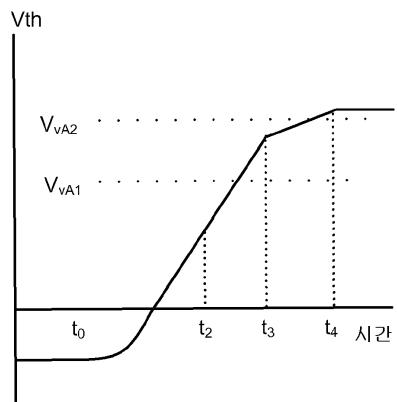

[0013] 도 4 및 5는 비정밀/정밀 프로그래밍 방법에 대한 하나의 실시예를 더욱 상세하게 나타낸 것이다. 도 4a 및 도 5a는 제어 게이트에 인가된 프로그래밍 펄스( $V_{pgm}$ )를 나타낸 것이다. 도 4b 및 도 5b는 프로그램된 메모리 셀들의 비트라인 전압들을 나타낸 것이다. 도 4c 및 도 5c는 프로그램된 메모리 셀들의 임계 전압을 나타낸 것이다. 도 4 및 도 5의 실시예에서는 두 개의 검증 레벨들을 사용하였으며, 도면 상에  $V_{vA1}$ 과  $V_{vA2}$ 로 표시하였다. 최종 목표 레벨은  $V_{vA2}$ 로 나타내었다. 메모리 셀의 임계 전압이  $V_{vA2}$ 에 도달하면, 상기 메모리 셀은 그 메모리 셀에 대응하는 비트라인에 금지 전압을 인가함으로써 더 이상의 프로그래밍이 금지된다. 예를 들면, 상기 비트라인 전압은  $V_{inhibit}$ 까지 증가될 수 있다(도 4b 및 도 5b 참조). 그러나, 메모리 셀이 목표 값인  $V_{vA2}$ 에 가까운(또는 그 보다 낮은) 임계 전압에 도달하면, 상기 임계 전압은 상기 비트라인에 보통 약 0.3v 내지 0.8v 정도의 소정의 바이어스 전압을 인가함에 따라, 이어지는 프로그래밍 펄스들이 느려지는 동안에 메모리 셀로 천이한다. 그 다음의 몇몇 펄스 동안 임계 전압 천이의 비율이 감소하기 때문에, 최종 임계 전압 분포는 도 3에 도시된 방법에 의할 때 보다 더 좁아질 수 있다. 본 방법을 실시하기 위해,  $V_{vA2}$ 의 검증 레벨 보다 작은 두 번째 검증 레벨이 사용된다. 이러한 두 번째 검증 레벨은 도 4 및 도 5에  $V_{vA1}$ 으로 도시되어 있다. 상기 메모리 셀의 임계 전압이  $V_{vA1}$  보다 크나 여전히  $V_{vA2}$  보다 작으면, 비트라인 바이어스( $V_s$ )를 인가함으로써 그 다음의 프로그래밍 펄스들에 대해 상기 메모리 셀로 천이하는 임계 전압이 감소할 것이다(도 5b). 이 경우, 각각의 상태에 대해 두 개의 검증 동작이 요구된다는 것에 주목해야 한다. 하나의 검증 동작은 비정밀/정밀 프로그래밍 방법이 적용되는 각 상태에 대해 최종 검증 레벨(예를 들어,  $V_{vA2}$ )에 해당되는 동작을 검증하며, 다른 하나는 각 상태에 대해 두 번째 검증 레벨(예를 들어,  $V_{vA1}$ )에 해당되는 동작을 검증한다. 이것은 상기 메모리 셀을 프로그램하는 데 총 소요되는 시간을 증가시킬 수 있다. 반면에, 보다 큰  $\Delta V_{pgm}$  스텝 사이즈(step size)를 이용하여 상기 프로세스들을 빠르게 할 수 있다.

[0014] 도 4a, 4b 및 4c는 하나의 프로그래밍 펄스에서 메모리 셀의 임계 전압이  $V_{vA1}$  및  $V_{vA2}$ 를 통과한 메모리 셀의 동작을 나타낸다. 예를 들어, 도 4c에는  $t_2$ 와  $t_3$  사이에서  $V_{vA1}$  및  $V_{vA2}$ 를 통과하는(pass) 임계 전압이 도시되어 있다. 따라서,  $t_3$  이전에는 상기 메모리 셀은 비정밀 모드에 해당한다.  $t_3$  이후에는 상기 메모리 셀은 금지 모드에 해당한다.

[0015] 도 5a, 5b 및 5c는 비정밀 및 정밀 프로그래밍 모드 양쪽에 들어가는 메모리 셀을 도시한 것이다. 메모리 셀의 임계 전압은  $t_2$ 와  $t_3$ 의 시간 사이에서  $V_{vA1}$ 과 교차한다.  $t_3$ 이 되기 이전에, 상기 메모리 셀은 비정밀 모드에 해당한다.  $t_3$  이후에는 상기 비트라인 전압은  $V_s$ 까지 증가되며, 이에 따라 상기 메모리 셀은 정밀 모드에 해당하게 된다.  $t_3$ 과  $t_4$ 의 사이에서, 상기 메모리 셀의 임계 전압은  $V_{vA2}$ 와 교차한다. 따라서, 상기 메모리 셀은 상기 비트라인 전압이  $V_{inhibit}$ 까지 증가됨으로써 더 이상의 프로그래밍이 금지된다.

[0016] 일반적으로, 합리적인 프로그래밍 시간을 유지하기 위해서, 비정밀/정밀 알고리즘이 가장 높은 메모리 상태(가장 큰 임계 전압 범위에 해당하는 상태)로는 인가되지 않는다. 도 2에서 분포(14)로 나타낸 상태(C)와 같은 가장 높은 상태는, 더 높은 상태와 차별화될 필요가 있다. 일반적으로, 다음의 가장 낮은 상태(예를 들어, 분포(12)에 의해 나타나는 상태(B))와 상이하게 하기 위하여 셀들을 이 상태에서 최소 임계 레벨 이상으로 프로그램 하기만 하면 된다. 따라서, 이러한 셀들의 분포는 디바이스의 성능에 악영향을 미치지 않으면서 보다 넓은 임계 전압 범위를 차지할 수 있다. 하지만, 몇몇 실시예들은 가장 높은 레벨 상태를 프로그램할 때에도 비정밀/정밀

프로그래밍 기술들을 이용할 것이다.

## 발명의 내용

### 해결하려는 과제

[0017] 여기에서 개시되는 기술은 비정밀/정밀 프로그래밍이 이용될 때 프로그래밍 검증 동안 비휘발성 저장 요소들의 임계 전압을 더욱 정확하게 감지하고자 한 것이다.

### 과제의 해결 수단

[0018] 비휘발성 메모리의 비정밀/정밀 프로그래밍(coarse/fine programming)이 제공되는 바, 여기에서 메모리 셀들은 자신들의 의도된 상태에 대한 비정밀 검증 레벨에 도달하기 전에는 제 1 프로그래밍 속도(rate of programming)로 프로그램되고, 상기 비정밀 검증 레벨에는 도달하였지만 자신들의 의도된 상태에 대한 최종 검증 레벨에 도달하기 전에는 제 2 프로그래밍 속도로 프로그램된다. 보다 작은 메모리 셀들과 관련된 큰 서브 임계 스윙 팩터들(sub-threshold swing factors)은, 특히 상이한 감지들 사이에서 비트라인을 브리챠지(pre-charge)시키지 않으면서 비정밀 검증 레벨에서 감지한 후 정밀 검증 레벨에서 감지할 때, 감지 동작들의 정확성에 영향을 미칠 수 있다. 비정밀 검증 레벨 및 최종 검증 레벨에서 감지할 때, 상이한 기준 전위(reference potential)들이 이용된다. 상기 기준 전위들 간의 차이는 비정밀 레벨 감지 동안 상기 비트라인의 어떠한 방전도 보상할 수 있다.

[0019] 일 실시예는 비휘발성 메모리의 프로그래밍 방법을 포함한다. 이 방법은 비휘발성 저장 요소들의 세트의 하나 이상의 저장 요소들을 특정 상태로 프로그램하기 위해, 하나 이상의 프로그래밍 펠스들을 상기 비휘발성 저장 요소들의 세트에 인가하는 단계를 포함한다. 각 프로그래밍 펠스를 인가한 이후, 저장 요소들의 세트에 제 1 전압을 인가하고 상기 하나 이상의 저장 요소들 각각의 비트라인 전압을 제 1 기준 전위와 비교함으로써, 상기 하나 이상의 저장 요소들의 상기 특정 상태에 대응하는 중간 검증 레벨(intermediate verify level)로의 프로그래밍이 검증된다. 각 프로그래밍 펠스를 인가한 이후, 상기 저장 요소들의 세트에 제 2 전압을 인가하고 상기 하나 이상의 저장 요소들 각각의 비트라인 전압을 제 2 기준 전위와 비교함으로써, 상기 하나 이상의 저장 요소들의 상기 특정 상태에 대응하는 최종 검증 레벨로의 프로그래밍의 검증이 수행된다. 여기서, 상기 제 2 기준 전위는, 상기 중간 검증 레벨로의 프로그래밍의 검증으로부터 야기되는 상기 하나 이상의 저장 요소들 각각의 비트라인 전압의 감소를 보상한다.

[0020] 다른 실시예에서는, 비휘발성 저장소(storage)의 프로그래밍을 검증하는 방법이 개시되는 바, 이 방법은 비휘발성 저장 요소에 대응하는 비트라인을 대전(charge)시키는 단계와, 상기 비휘발성 저장 요소에 상기 비휘발성 저장 요소에 대한 목표 상태에 대응하는 중간 검증 전압을 인가하는 단계와; 상기 중간 검증 전압이 인가되는 동안, 상기 비트라인의 전압을 감지하는 단계와; 상기 비트라인의 전압을 제 1 기준 전위와 비교하는 단계와; 상기 비휘발성 저장 요소에 상기 비휘발성 저장 요소에 대한 상기 목표 상태에 대응하는 최종 검증 전압을 인가하는 단계와; 상기 최종 검증 전압이 인가되는 동안 그리고 상기 비트라인이 상기 대전된 상태로부터 완전히 방전되기 때문에, 상기 비트라인의 전압을 감지하는 단계와; 그리고 상기 최종 검증 전압이 인가되는 동안, 상기 비트라인의 전압을 제 2 기준 전위와 비교하는 단계를 포함한다.

[0021] 하나의 예시적인 실시예는 비휘발성 저장 요소들의 세트 및 상기 비휘발성 저장 요소들의 세트와 통신하는 관리 회로를 포함한다. 상기 하나 이상의 관리 회로는 상술한 프로세스들을 수행할 수 있다.

## 발명의 효과

[0022] 본 발명은 비정밀/정밀 프로그래밍이 이용될 때, 프로그래밍 검증 동안 비휘발성 저장 요소들의 임계 전압을 더욱 정확하게 감지할 수 있다.

## 도면의 간단한 설명

[0023] 도 1은 두 개의 임계 전압 분포를 나타내는 그래프이다.

도 2는 네 개의 임계 전압 분포를 나타내는 그래프이다.

도 3a, 3b 및 3c는 프로그래밍 프로세스를 나타낸다. 도 3a는 비휘발성 저장 요소의 제어 게이트에 인가되는 프로그래밍 전압 신호를 나타낸다. 도 3b는 NAND 스트링에 대한 비트라인에 인가되는 전압 신호를 나타낸다. 도 3c는 프로그램될 비휘발성 저장 요소의 임계 전압을 나타낸다.

도 4a, 4b 및 4c는 비정밀/정밀 프로그래밍의 일부로서 수행되는 프로그래밍 프로세스의 일 실시예를 나타낸다.

도 5a, 5b 및 5c는 비정밀/정밀 프로그래밍의 일부로서 수행되는 프로그래밍 프로세스의 일 실시예를 나타낸다.

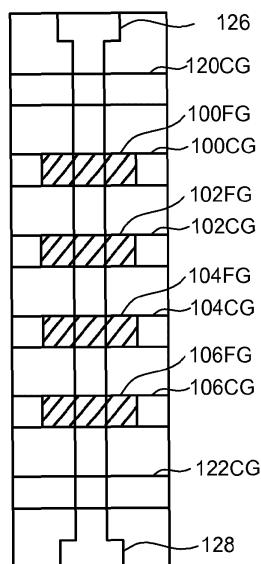

도 6은 NAND 스트링의 평면도이다.

도 7은 도 6의 NAND 스트링의 등가 회로도이다.

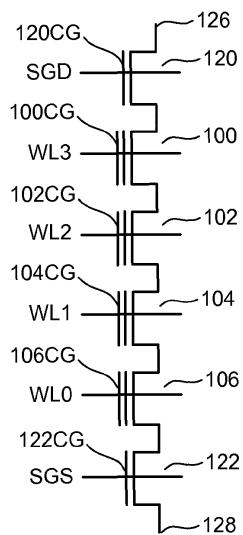

도 8은 비휘발성 메모리 시스템의 일 실시예의 블록도이다.

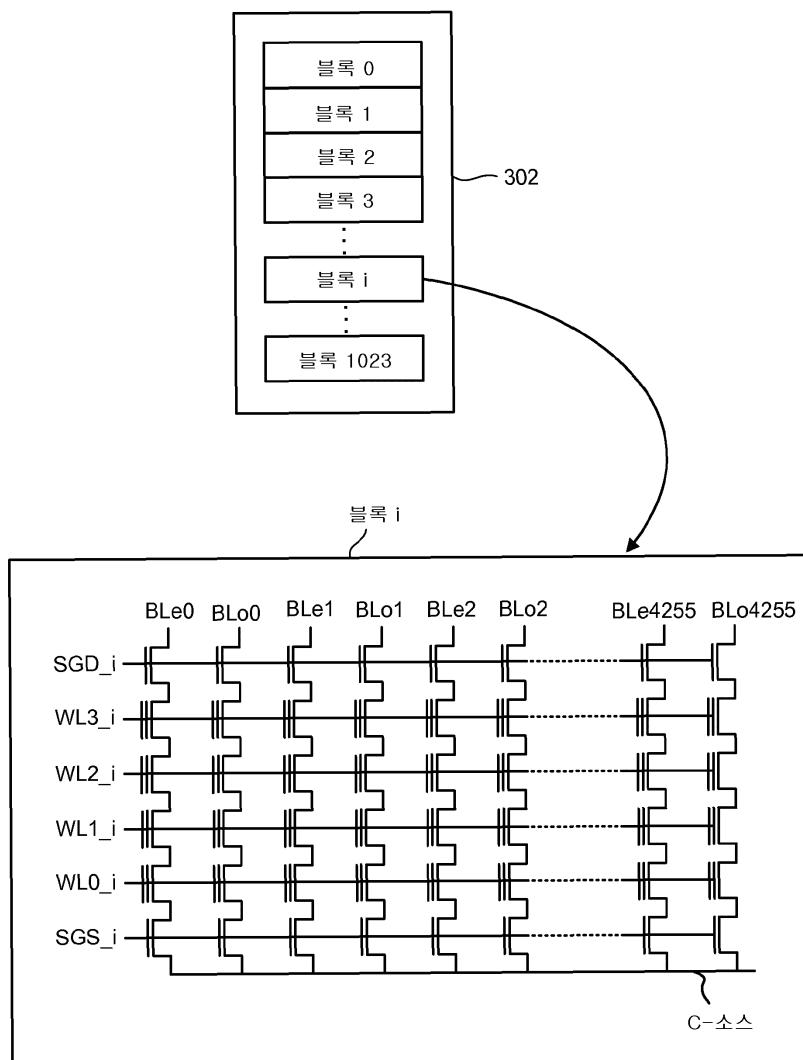

도 9는 메모리 어레이의 구성의 일 예를 나타낸다.

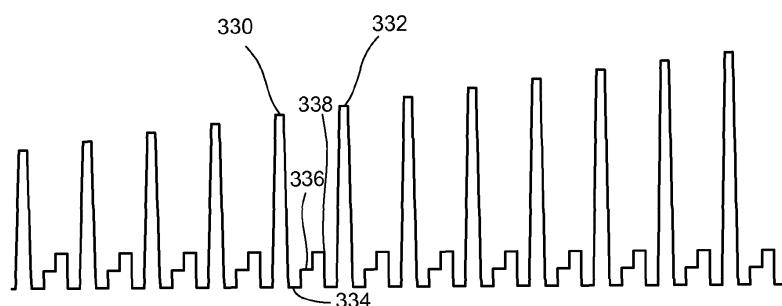

도 10은 일 실시예에 따라 사용될 수 있는, 검증 펄스들을 포함하는 프로그램 전압 신호를 나타낸다.

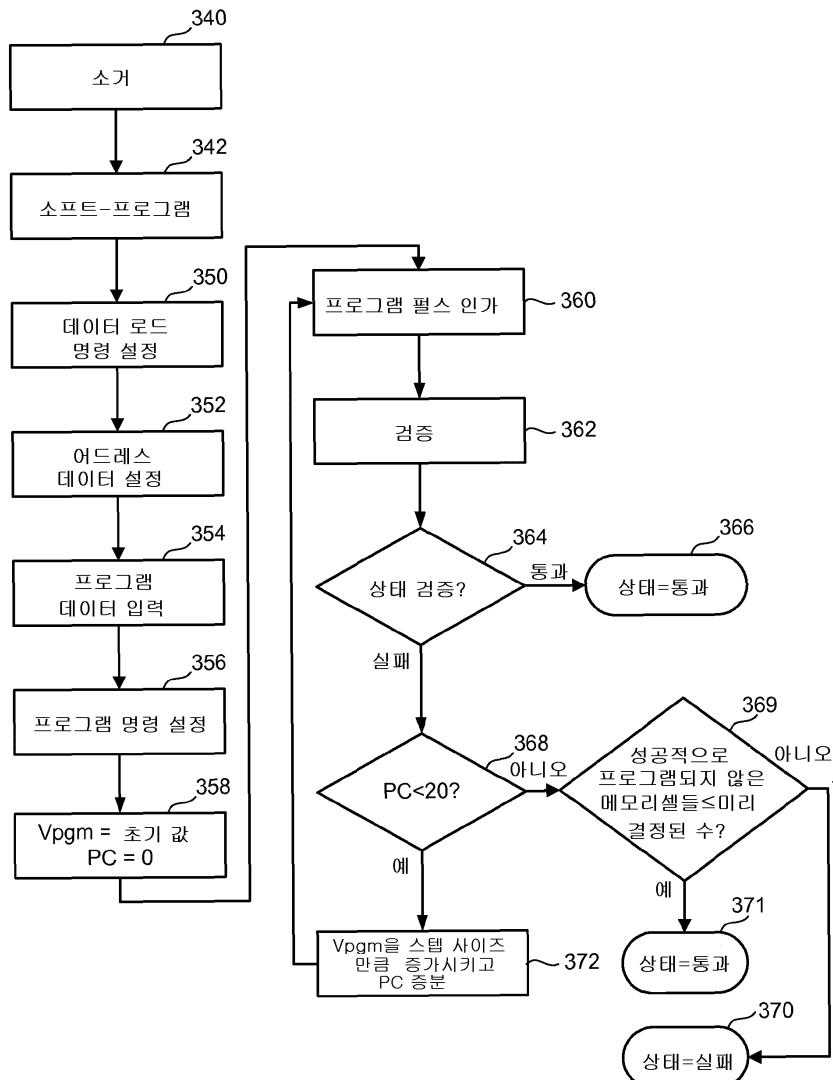

도 11은 일 실시예에 따른 비휘발성 메모리의 프로그래밍 방법을 도시하는 흐름도이다.

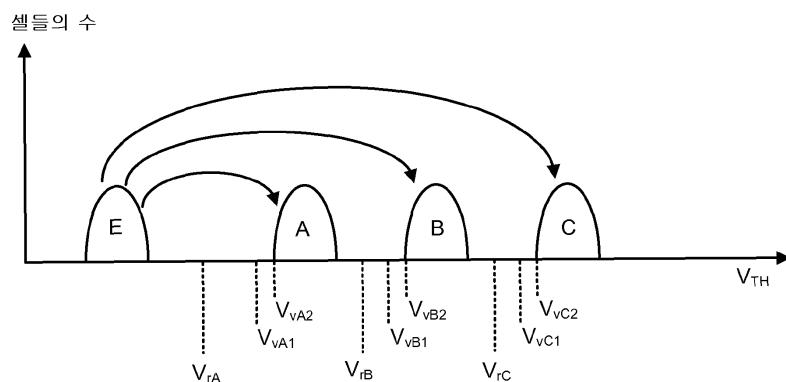

도 12는 임계 전압 분포들의 세트 및 풀 시퀀스 프로그래밍 프로세스(full sequence programming process)의 일 예를 나타낸다.

도 13은 임계 전압 분포들의 세트 및 2-패스 프로그래밍 프로세스의 일 예를 나타낸다.

도 14a 내지 14c는 임계 전압 분포들의 세트 및 또 다른 2-패스 프로그래밍 프로세스의 일 예를 나타낸다.

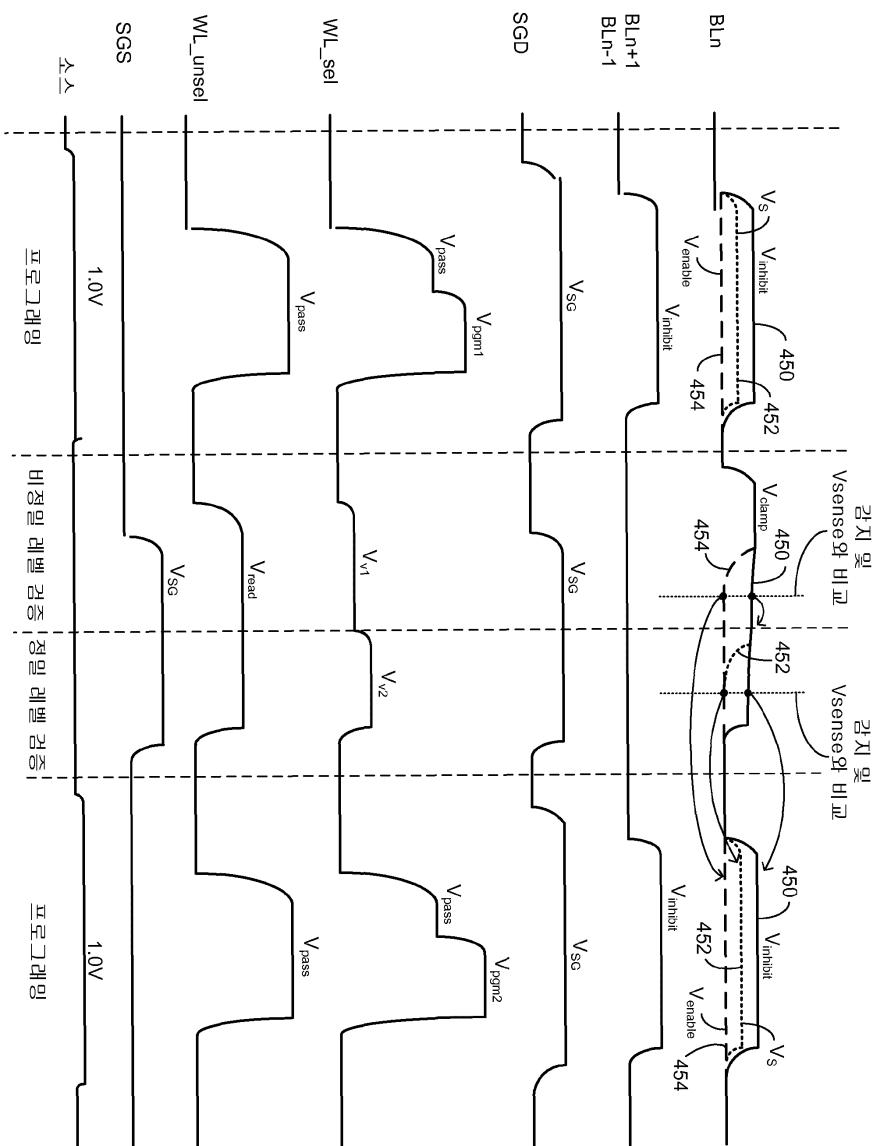

도 15는 프로그램 및 프로그램 검증 동작 동안 메모리 디바이스에 인가될 수 있는 다양한 신호들을 나타내는 타이밍도이다.

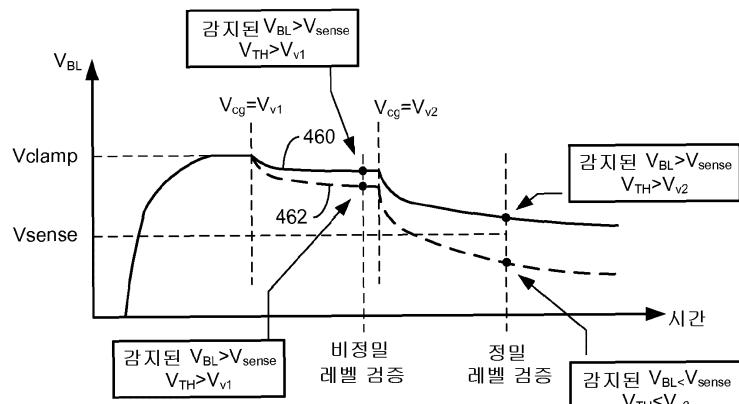

도 16은 메모리 셀들이 작은 서브-임계 스윙 팩터들을 갖는 검증 동작 동안 상이한 메모리 셀들의 비트라인 전위를 나타내는 그래프이다.

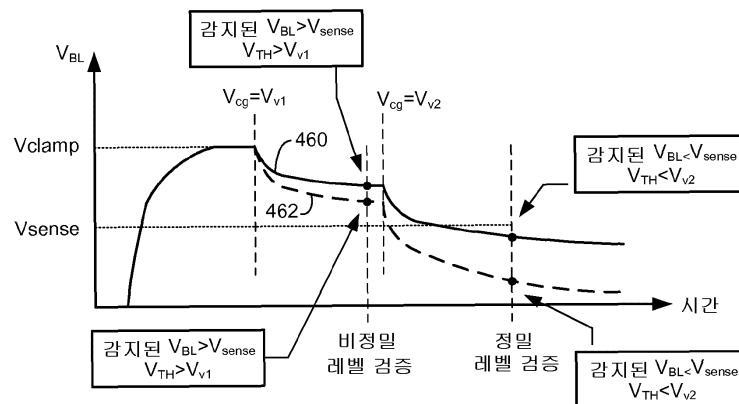

도 17은 메모리 셀들이 큰 서브-임계 스윙 팩터들을 갖는 검증 동작 동안 상이한 메모리 셀들의 비트라인 전위를 나타내는 그래프이다.

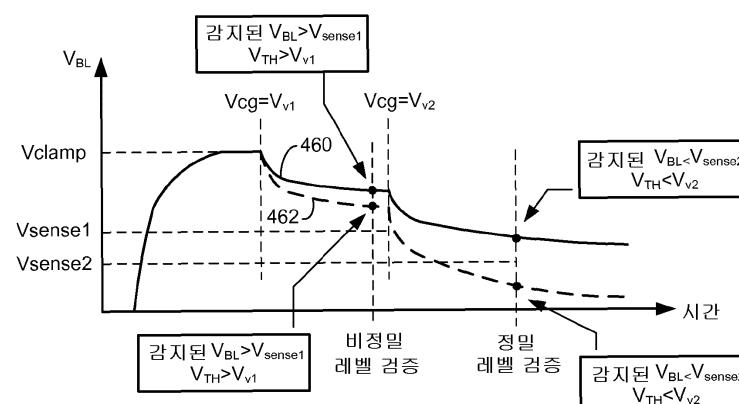

도 18은 일 실시예에 따른 검증 프로세스 동안 상이한 메모리 셀들의 비트라인 전위를 나타내는 그래프이다.

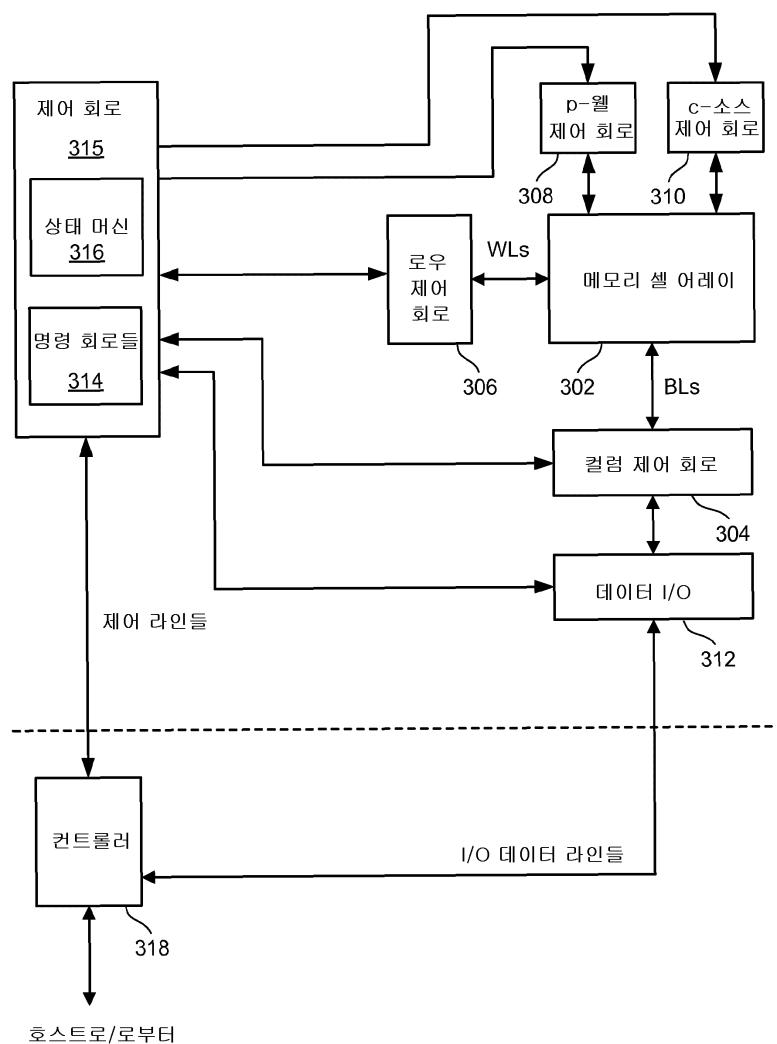

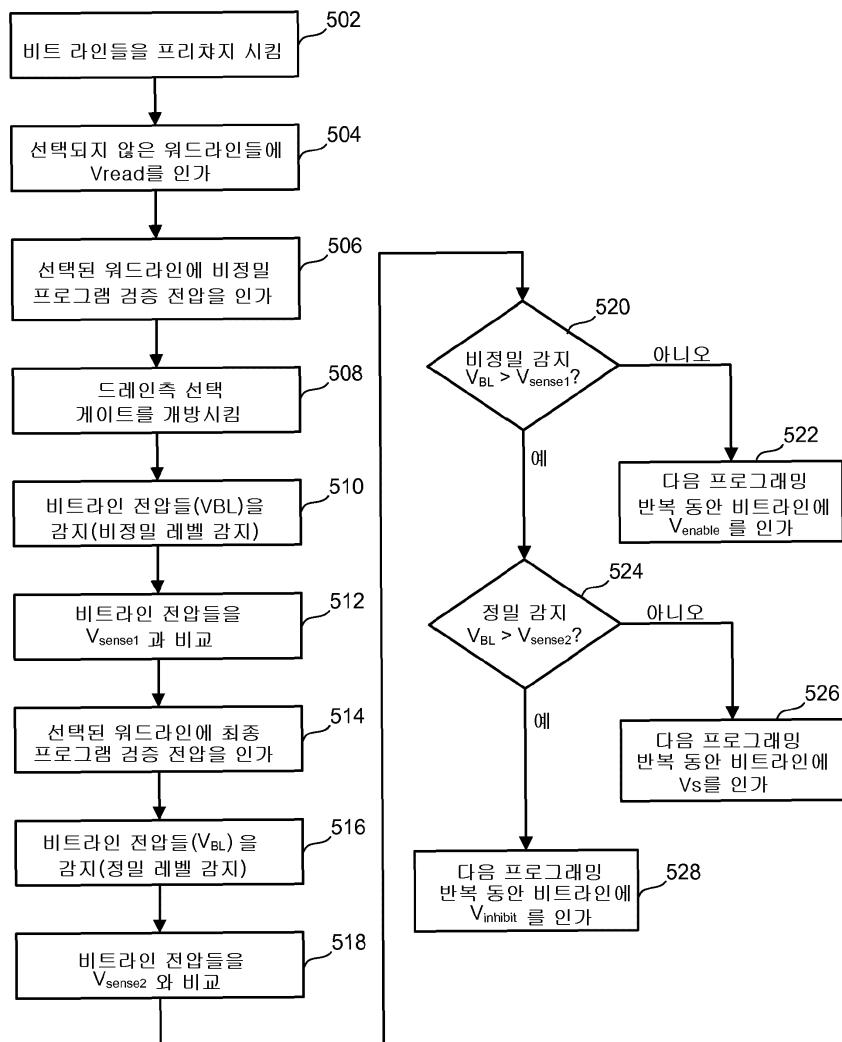

도 19는 일 실시예에 따른 비정밀/정밀 프로그래밍 동안 메모리 셀들의 검증을 나타내는 흐름도이다.

도 20은 일 실시예에 따라 사용될 수 있는 메모리 디바이스의 컬럼 제어 회로의 일부이다.

### 발명을 실시하기 위한 구체적인 내용

[0024]

본 발명의 실시예를 구현하는 데에 적절한 플래시 메모리 시스템의 일 실시예는 NAND 구조를 이용하여, 이러한 NAND 구조는 두 개의 선택 게이트들 사이에 배열된 직렬의 다수의 트랜지스터들을 포함하여 이루어진다. 상기 직렬의 트랜지스터들과 선택 게이트들은 NAND 스트링(string)으로 일컬어진다. 도 6은 하나의 NAND 스트링을 도시한 평면도이며, 도 7은 그에 대한 등가 회로도이다. 도 6 및 7에 도시된 NAND 스트링은 직렬의 네 개의 트랜지스터들(100, 102, 104 및 106)을 포함하는 바, 이들은 선택 게이트(120)와 제 2 선택 게이트(122) 사이에 있다. 선택 게이트(120)는 상기 NAND 스트링을 비트라인 컨택(126)에 연결시킨다. 선택 게이트(122)는 상기 NAND 스트링을 소스 라인 컨택(128)에 연결시킨다. 선택 게이트(120)는 제어 게이트(120CG)에 적절한 전압들을 인가함으로써 제어된다. 선택 게이트(122)는 제어 게이트(122CG)에 적절한 전압들을 인가함으로써 제어된다. 각각의 트랜지스터들(100, 102, 104, 및 106)은 하나의 제어 게이트와 하나의 플로팅 게이트를 갖는다. 트랜지스터(100)는 제어 게이트(100CG)와 플로팅 게이트(100FG)를 갖는다. 트랜지스터(102)는 제어 게이트(102CG)와 플로팅 게이트(102FG)를 포함한다. 트랜지스터(104)는 제어 게이트(104CG)와 플로팅 게이트(104FG)를 포함한다. 트랜지스터(106)는 제어 게이트(106CG)와 플로팅 게이트(106FG)를 포함한다. 제어 게이트(100CG)는 워드라인(WL 3)에 연결되며, 제어 게이트(102CG)는 워드라인(WL2)에 연결되고, 제어 게이트(104CG)는 워드라인(WL1)에 연결되고, 제어 게이트(106CG)는 워드라인(WL0)에 연결된다. 일 실시예에 따르면, 트랜지스터들(100, 102, 104 및 106)은 각각 메모리 셀들이다. 다른 실시예에 따르면, 상기 메모리 셀들은 다수의 트랜지스터들을 포함할 수 있으며, 도 6 및 도 7에 도시된 것과 다를 수 있다. 선택 게이트(120)는 선택 라인(SGD)에 연결되며, 선택 게이트(122)는 선택 라인(SGS)에 연결된다.

[0025]

비록 도 6 및 도 7이 NAND 스트링에서의 네 개의 메모리 셀들을 도시하고 있지만, 이러한 네 개의 트랜지스터를 사용하는 것은 단지 예로서 제시된 것이다. NAND 스트링은 네 개 이하의 메모리 셀들을 가지거나 네 개 이상의 메모리 셀들을 가질 수 있다. 예를 들어, 어떤 NAND 스트링들은 8개, 16개, 32개 등의 메모리 셀들을 포함할 수

있다. 본 설명에서의 NAND 스트링의 메모리 셀들의 개수는 특정한 개수로 한정되지 않는다.

[0026] NAND 타입의 플래시 메모리들과 그 동작에 관련한 적절한 실시예들은 미국 특허 제5,570,315호; 미국 특허 제5,774,397호; 미국 특허 제6,046,935호; 미국 특허 제5,386,422호; 미국 특허 제6,456,528호 및 미국 특허 출원 제09/893,277호(공개 번호 US2003/0002348호)에서 개시되어 있으며, 이들 모두는 본원의 참조로서 그 전체가 통합된다. 셀프 부스팅 기술(self boosting technique)을 포함하는, NAND 플래시 메모리를 프로그래밍하는 것에 관한 정보는, 2003년 3월 5일에 출원되었으며 그 명칭이 "Self Boosting Technique"인 미국 특허 출원 제10/379,608호 및 2003년 7월 29일에 출원되었으며 그 명칭이 "Detecting Over Programmed Memory"인 미국 특허 출원 제10/629,068호에서 확인할 수 있으며, 이들 출원들은 본원의 참조로서 그 전체가 통합된다. 다른 타입의 플래시 메모리 소자들도 본 발명과 함께 사용될 수 있음을 물론이다. 예를 들면, 미국 특허 제5,095,344호, 제5,172,338호; 제5,890,192호 및 제6,151,248호는 NOR 타입의 플래시 메모리들을 개시하며, 본원의 참조로서 그 전체가 통합된다. 플래시 메모리 타입의 다른 실시예는 미국 특허 제6,151,248호에서 확인할 수 있으며, 이는 그 전체가 본원의 참조로서 통합된다.

[0027] 본 명세서에서 설명된 기술은 플로팅 게이트 타입의 메모리들에 한정되는 것은 아니다. 예를 들어, 본 명세서에 설명된 기술은 제어 게이트(또는 워드라인)와 기판 사이에 있는 다양한 타입의 전하 저장 영역들/층(들), 예를 들어 나노결정(nano-crystal)으로 알려진 비전도성 유전체 전하 저장 영역 또는 작은 실리콘 섬들(islands)을 사용하는 메모리 디바이스들과 함께 사용될 수 있다.

[0028] 도 8은 본 발명의 하나 이상의 실시예들을 실시하기 위해 사용될 수 있는 플래시 메모리 시스템의 일 실시예를 나타낸 블록도이다. 도 8은 다른 시스템들 및 실시예들이 사용될 수 있기 때문에 예시적인 것이다. 메모리 셀 어레이(302)는 컬럼(column) 제어 회로(304), 로우(row) 제어 회로(306), c-소스 제어 회로(310) 및 p-웰 제어 회로(308)에 의해 제어된다. 컬럼 제어 회로(304)는 메모리 셀 어레이(302)의 비트라인들에 연결되는데, 이는 메모리 셀들에 저장된 데이터를 판독하고, 프로그램이 동작하는 동안 메모리 셀들의 상태를 결정하며, 그리고 프로그래밍 및 소거를 진행하거나 금지하기 위한 비트라인들의 전위 레벨들을 제어하기 위해서이다. 로우 제어 회로(306)는 상기 워드라인들에 연결되는데, 이는 워드라인들 중 하나를 선택하고, 판독 전압들을 인가하고, 컬럼 제어 회로(304)에 의해 제어되는 비트라인 전위 레벨들과 결합된 프로그램 전압들을 인가하며, 그리고 소거 전압을 인가하기 위해서이다. C-소스 제어 회로(301)는 상기 메모리 셀들에 연결된 (도 9에서 "C-소스"라고 표시된) 공통 소스 라인을 제어한다. P-웰 제어 회로(308)는 P-웰 전압을 제어한다.

[0029] 상기 메모리 셀들에 저장된 데이터는 상기 컬럼 제어 회로(304)에 의해 판독되고, 데이터 입/출력 버퍼(312)를 통해 외부의 I/O 라인들로 출력된다. 상기 메모리 셀들에 저장될 프로그램 데이터는 상기 외부 I/O 라인들을 통해 상기 데이터 입/출력 버퍼(312)에 입력되고, 상기 컬럼 제어 회로(304)로 전송된다. 상기 외부 I/O 라인들은 컨트롤러(318)에 연결된다.

[0030] 상기 플래시 메모리 디바이스를 제어하기 위한 명령 데이터는 컨트롤러(218)로 입력된다. 상기 명령 데이터는 상기 플래시 메모리에 어떤 동작이 필요한지 통지한다. 입력 명령은 제어 회로(315)의 부분인 상태 머신(state machine)(316)에 전송된다. 상태 머신(316)은 컬럼 제어 회로(304), 로우 제어 회로(306), c-소스 제어 회로(310), p-웰 제어 회로(308) 및 데이터 입/출력 버퍼(312)를 제어한다. 상태 머신(316)은 또한 READY/BUSY 또는 PASS/FAIL과 같은 플래시 메모리의 상태 데이터를 출력할 수 있다.

[0031] 컨트롤러(318)는 퍼스널 컴퓨터, 디지털 카메라, 개인 휴대 정보 단말기 등의 호스트 시스템과 연결되거나 연결될 수 있다. 컨트롤러(318)는 메모리 어레이(302)로의 데이터 저장 또는 메모리 어레이(302)로부터의 데이터 판독 및 이와 같은 데이터를 제공 또는 송신하기 위한 명령들을 초기화하는 호스트와 통신한다. 컨트롤러(318)는 호스트로부터의 명령을 제어 회로(315)의 부분인 명령 회로(314)에 의해 해석되고 실행될 수 있는 명령 신호(command signals)로 변환한다. 명령 회로(314)는 상태 머신(316)과 통신한다. 컨트롤러(318)는 보통 메모리 어레이에 기입되거나 메모리 어레이로부터 판독되는 사용자 데이터를 위한 버퍼 메모리를 포함한다.

[0032] 하나의 예시적인 메모리 시스템은 컨트롤러(318)를 포함하는 하나의 집적 회로 및 각각이 메모리 어레이 및 연관된 제어, 입력/출력 및 상태 머신 회로들을 포함하는 하나 이상의 집적 회로 칩을 포함한다. 시스템의 메모리 어레이들과 컨트롤러들을 하나의 집적 회로 칩 상에 함께 집적하는 것이 추세이다. 상기 메모리 시스템은 상기 호스트 시스템의 일부로서 내장(embed)될 수 있으며, 상기 호스트 시스템에 탈착 가능하게 삽입된 메모리 카드(또는 다른 패키지)에 포함될 수 있다. 이와 같은 카드는 전체 메모리 시스템(예를 들어, 컨트롤러를 포함하여)을 포함하여 이루어지거나, 단지 메모리 어레이(들) 및 이에 연관된 주변 회로들(peripheral circuits) 만을 포함하여 이루어질 수 있다(여기서, 상기 컨트롤러 또는 제어 기능은 상기 호스트에 내장된다). 이에 따라, 상

기 컨트롤러는 상기 호스트에 내장될 수 있으며, 또는 탈착 가능한 메모리 시스템에 포함될 수 있다.

[0033] 몇몇 실시예에서는, 도 8의 몇몇 구성요소들이 결합될 수 있다. 다양한 설계에 있어서, 메모리 셀 어레이(302) 이외의 도 8의 하나 이상의 구성요소들이 메모리 시스템의 관리 회로로서 고려될 수 있다. 예를 들어, 하나 이상의 관리 회로들은 명령 회로, 상태 머신, 로우 제어 회로, 컬럼 제어 회로, 웰 제어 회로, 소스 제어 회로, 데이터 I/O 회로 또는 컨트롤러들중 어느 하나를 포함하여 이루어지거나 또는 조합을 포함하여 이루어질 수 있다.

[0034] 도 9를 참조하면, 메모리 셀(302) 구조의 일 실시예가 도시되어 있다. 본 실시예에서, 1,024 블록으로 분할된 NAND 플래시 EEPROM이 도시되어 있다. 각 블록에 저장된 데이터는 동시에 소거된다. 일 실시예에 따르면, 상기 블록은 동시에 소거되는 최소 단위이다. 각 블록은 일반적으로 프로그래밍의 단위가 될 수 있는 다수의 페이지들로 분할된다. 프로그래밍을 위한 데이터의 다른 단위들도 또한 가능하고 고려될 수 있다. 일 실시예에서, 개별적인 페이지들은 세그먼트들로 분할될 수 있고, 세그먼트들은 기본 프로그래밍 동작으로서 한번에 기록되는 가장 적은 수의 셀들을 포함할 수 있다. 데이터의 하나 이상의 페이지들은 일반적으로 메모리 셀들의 하나의 로우에 저장된다.

[0035] 도 9의 실시예에서 각 블록에는 짹수 컬럼들과 홀수 컬럼들로 나누어진 8,512개의 컬럼이 있다. 비트라인들 또한 짹수 비트라인들(BLe)과 홀수 비트라인들(BLo)로 나누어진다. 홀수/짜수 비트라인 아키텍처에서, 공통 워드라인을 따르고 홀수 비트라인에 연결된 메모리 셀들은 하나의 시간(one time)에 프로그램되고, 반면에 공통 워드라인을 따르고 짹수 비트라인에 연결된 메모리 셀들은 다른 시간(another time)에 프로그램된다. 도 9의 각 NAND 스트링에 도시된 네 개의 셀들이 포함되어 있지만, 네 개 이상 또는 네 개 이하의 메모리 셀들이 사용될 수 있다. 상기 NAND 스트링의 한 말단은 드레인 선택 게이트 제어 라인(SGD)에 연결된 제 1 선택 트랜지스터를 통해 대응하는 비트라인에 연결되며, 나머지 말단은 소스 선택 게이트 제어 라인(SGS)에 연결된 제 2 선택 트랜지스터를 통해 C-소스에 연결된다.

[0036] 다른 실시예에 있어서, 비트라인들은 홀수 및 짹수 비트라인들로 분할되지 않는다. 이와 같은 아키텍처들은 일반적으로 모든 비트라인 아키텍처(all bit line architecture)로 불린다. 모든 비트라인 아키텍처에서, 블록의 모든 비트라인들은 읽기 및 프로그램 동작 동안에 동시에 선택된다. 공통 워드라인을 따르고 임의의 비트라인에 연결된 메모리 셀들은 동시에 프로그램된다.

[0037] 홀수/짜수 비트라인 아키텍처에서 판독 및 프로그램 동작들의 일 실시예 동안에, 4,256개의 메모리 셀들이 동시에 선택된다. 선택된 메모리 셀들은 동일 워드라인과 동일 종류의 비트라인(예를 들어, 짹수 비트라인들 또는 홀수 비트라인들)을 갖는다. 따라서, 532 바이트의 데이터가 동시에 판독되거나 프로그램될 수 있다. 상기 동시에 판독되거나 프로그램되는 532 바이트의 데이터는 논리 페이지(logical page)를 형성한다. 따라서, 하나의 블록은 적어도 8개의 논리 페이지들(각각 홀수 및 짹수의 페이지를 갖는, 4개의 워드라인들)을 저장할 수 있다. 각 메모리 셀이 2비트의 데이터(예를 들어, 다중-상태 메모리 셀들)를 저장하면, 상기 2비트 각각은 다른 페이지에 저장되며, 하나의 블록은 16개의 논리 페이지를 저장한다. 본 발명에 따르면 다른 크기의 블록이나 페이지들도 사용될 수 있다. 또한, 도 8 및 도 9에 도시된 아키텍처 이외의 아키텍처들이 또한 본 발명의 실시를 위해 사용될 수 있다.

[0038] 메모리 셀들은 p-웰의 소거 전압을 증가시키고(예를 들어, 20볼트) 선택된 블록의 워드라인들을 접지시킴으로써 소거될 수 있다. 상기 소스와 비트라인들은 플로팅 상태이다. 소거는 전체 메모리 어레이, 분리 블록, 또는 셀들의 또 다른 유닛에서 수행될 수 있다. 전자들은 상기 플로팅 게이트에서 p-웰 영역으로 전송되고 임계 전압은(일 실시예에서) 음의 값이 된다.

[0039] 일 실시예에서, 메모리 셀을 프로그램할 때, 제어 게이트는 증가하는 크기를 갖는 일련의 프로그래밍 펄스를 수신하는 반면, 드레인 및 p-웰은 0볼트를 수신한다. 일 실시예에서, 일련의 펄스들의 크기는 12볼트에서 24볼트의 범위를 갖는다. 다른 실시예에서, 일련의 펄스들의 범위는 다를 수 있고, 예를 들어 12볼트 보다 높은 시작 레벨을 가질 수 있다. 메모리 셀들을 프로그램하는 동안, 프로그래밍 펄스들 사이의 주기에서 검증 동작이 수행된다. 즉, 별도로 프로그램되는 셀들의 그룹 중 각 셀의 프로그래밍 레벨은 프로그램될 검증 레벨에 도달했거나 프로그램될 검증 레벨을 초과했는지 여부를 결정하기 위하여 각 프로그래밍 펄스 사이에서 판독된다. 프로그래밍을 검증하는 한가지 방법은 특정의 비교 포인트에서 도통을 점검하는 것이다. 충분히 프로그램된 것으로 검증된 셀들은, 예를 들어 NAND 셀들에서, 그 셀들에 대한 프로그래밍 프로세스를 종료시키기 위해 모든 후속 프로그래밍 펄스들에 대해 비트라인 전압을 0에서 V<sub>DD</sub>(예를 들어, 2.5V)로 증가시킴으로써 록 아웃된다(locked out). 몇몇 경우에, 펄스들의 수는 제한될 것이고(예를 들어, 20 펄스들), 소정의 메모리 셀이 마지막 펄스에

의해 충분히 프로그램되지 않는다면, 오류인 것으로 추정된다. 몇몇 실시예에서, 메모리 셀들은 프로그래밍 이전에 (블록들 또는 다른 유닛들에서) 소거된다.

[0040] 도 10은 일 실시예에 따른 프로그램 전압 신호를 나타낸다. 이 신호는 크기가 증가하는 펄스들의 세트를 갖는다. 크기는 각 펄스에 대해 미리 결정된 스텝 사이즈 만큼씩 증가된다. 다중 비트 데이터를 저장하는 메모리 셀들을 포함하는 일 실시예에서, 예시적인 스텝 사이즈는 0.2볼트(또는 0.4볼트)이다. 각 프로그램 펄스들의 사이에는 검증 펄스들이 있다. 도 10의 신호는 4개의 상태 메모리 셀을 가정하므로, 3개의 검증 펄스들을 포함한다. 예를 들면, 프로그래밍 펄스들(330 및 332)의 사이에는 3개의 순차(sequential) 검증 펄스들이 있다. 제 1 검증 펄스(334)는 0 볼트 검증 전압 레벨에서 도시된다. 제 2 검증 펄스(336)는 제 2 검증 전압 레벨에서 제 1 검증 펄스에 후속한다. 제 3 검증 펄스(338)는 제 3 검증 전압 레벨에서 제 2 검증 펄스(336)에 후속한다. 8 개의 상태에서 데이터를 저장할 수 있는 다중-상태 메모리 셀은 7개의 비교 포인트들에서 검증 동작을 수행할 필요가 있을 수 있다. 그러므로, 두 개의 연속하는 프로그래밍 펄스들 사이의 7개의 검증 레벨에서 7개의 검증 동작을 수행하기 위하여 순차적으로 7개의 검증 펄스들이 인가된다. 7개의 검증 동작에 근거하여, 시스템은 메모리 셀들의 상태를 결정할 수 있다. 검증의 시간 부담을 줄이는 한가지 방법은 더욱 효율적인 검증 프로세스를 이용하는 것인데, 이는 예를 들어 2002년 12월 5일 출원되었으며 그 명칭이 "Smart Verify for Multi-State Memories"인 미국 특허 출원 제10/314,055호; 2005년 10월 27일 출원되었으며 그 명칭이 "Method for Programming of Multi-State Non-Volatile Memory Using Smart Verify"인 미국 특허 출원 제11/259,799호; 및 2005년 10월 27일 출원되었으며 그 명칭이 "Apparatus for Programming of Multi-State Non-Volatile Memory using Smart Verify"인 미국 특허 출원 제11/260,658호에 개시되어 있으며, 이들은 본원의 참조로서 그 전체가 인용된다.

[0041] 도 11은 비휘발성 메모리의 프로그래밍 방법의 일 실시예를 나타내는 흐름도이다. 프로그램될 메모리 셀들은 단계(340)에서 소거된다. 단계(340)는 프로그램될 메모리 셀들 보다 더 많은 메모리 셀들(예를 들어, 블록들 또는 유닛들에서)을 소거하는 단계를 포함할 수 있다. 단계(342)에서, 소거된 메모리 셀들에 대한 소거된 임계 전압 분포를 좁히기 위해 소프트 프로그래밍(soft programming)이 수행된다. 몇몇 메모리 셀들은 소거 프로세스의 결과로 필요보다 더 깊게 소거된 상태가 될 수 있다. 소프트 프로그래밍은 소거된 메모리 셀들의 임계 전압을 소거 검증 레벨에 더 가깝게 이동시키기 위하여 작은 프로그래밍 펄스를 인가할 수 있다. 도 11의 단계(350)에서, "데이터 로드(data load)" 명령이 컨트롤러(318)에 의해 발행되어, 명령 회로(314)에 입력된다. 입력 데이터는 명령으로 인식되고 도시되지 않은 명령 회로(314)에 입력된 명령 래치 신호를 통해 상태 머신(316)에 의해 래치된다. 단계(352)에서, 페이지 어드레스를 지정하는 어드레스 데이터가 컨트롤러 또는 호스트로부터 로우 컨트롤러 또는 디코더(306)에 입력된다. 입력 데이터는 페이지 어드레스로 인식되며, 명령 회로(314)에 입력된 어드레스 래치 신호에 의해 영향받는 상태 머신(316)을 통해 래칭된다. 단계(354)에서, 어드레스된 페이지에 대한 프로그램 데이터의 페이지는 프로그래밍을 위한 데이터 입력/출력 버퍼(312)에 입력된다. 예를 들면, 일 실시예에서 532 바이트의 데이터가 입력될 수 있다. 상기 데이터는 선택된 비트라인의 적절한 레지스터에 래칭된다. 몇몇 실시예에서, 데이터는 검증 동작들에 사용되기 위해 선택된 비트라인들의 제 2 레지스터에 래칭될 수도 있다. 단계(356)에서, "프로그램" 명령은 컨트롤러에 의해 발행되어, 데이터 입력/출력 버퍼(312)에 입력된다. 이 명령은 명령 회로(314)에 입력된 명령 래치 신호를 통해 상태 머신(316)에 의해 래칭된다.

[0042] "프로그램" 명령에 의해 트리거(trigger)되면, 단계(354)에서 래칭된 데이터는 적절한 워드라인에 인가된 도 6의 단계화된 펄스들(stepped pulses)을 이용하는 상태 머신(316)에 의해 제어되는 선택된 메모리 셀들로 프로그램될 것이다. 단계(358)에서, 선택된 워드라인에 인가된 프로그래밍 펄스 전압 레벨( $V_{pgm}$ )이 시작 펄스(예를 들어, 12볼트)로 초기화되고, 상태 머신(316)에 의해 유지되는 프로그램 카운터(PC)가 0으로 초기화된다. 단계(360)에서, 제 1  $V_{pgm}$  펄스는 선택된 워드라인에 인가된다. 논리 "0"이 특정 데이터 래치에 저장되어, 대응하는 메모리 셀이 프로그램되어야 함을 나타내면, 대응하는 비트라인이 접지된다. 한편, 논리 "1"이 특정 래치에 저장되어, 대응하는 메모리 셀이 대응하는 메모리 셀의 현재 데이터 상태에 유지되어야 함을 나타내면, 프로그래밍을 금지하기 위하여 대응하는 비트라인이  $V_{DD}$ 에 연결된다.

[0043] 단계(362)에서, 선택된 메모리 셀들의 상태들이 검증된다. 선택된 셀의 목표 임계 전압이 적절한 레벨에 도달했다는 것이 감지되면, 대응하는 데이터 래치에 저장된 데이터가 논리 "1"로 변경된다. 임계 전압이 적절한 레벨에 도달하지 않았다는 것이 감지되면, 대응하는 데이터 래치에 저장된 데이터는 변경되지 않는다. 이러한 방식으로, 비트라인의 대응하는 데이터 래치에 저장된 논리 "1"을 갖는 비트라인이 프로그램될 필요가 없다. 모든 데이터 래치들이 논리 "1"을 저장하고 있으면, 상태 머신은 모든 선택된 셀들이 프로그램되었다는 것을 인지한

다. 단계(364)에서, 모든 데이터 레치들이 논리 "1"을 저장하는지 여부가 검사된다. 모든 데이터 레치들이 논리 "1"을 저장하고 있으면, 모든 선택된 메모리 셀들이 프로그램되었고 모든 선택된 메모리 셀들의 목표 상태들로 검증되었기 때문에, 프로그래밍 프로세스는 완벽하고 성공적이다. 단계(366)에서 "통과(PASS)"의 상태가 통지된다.

[0044] 단계(364)에서, 모든 데이터 레치들이 논리 "1"을 저장하고 있지 않는 것으로 결정되면, 프로그래밍 프로세스가 계속된다. 단계(368)에서는, 프로그램 카운터(PC)가 프로그램 한계 값과 비교하여 검사된다. 프로그램 한계 값의 일 예는 20이지만, 다양한 실시예들에서 다른 값들이 사용될 수 있다. 프로그램 카운터(PC)가 20 보다 작지 않으면, 단계(369)에서 성공적으로 프로그램되지 않은 비트들의 수가 미리 결정된 수보다 같거나 작은지가 결정된다. 성공적으로 프로그램되지 않은 비트들의 수가 미리 결정된 수보다 같거나 작다면, 프로그래밍 프로세스가 통과된 것으로 플래그(flag)되고, 단계(371)에서 통과의 상태가 통지된다. 성공적으로 프로그램되지 않은 비트들은 판독 프로세스 동안에 오류 수정(correction)을 이용하여 수정될 수 있다. 그러나 만약, 성공적으로 프로그램되지 않은 비트들의 수가 미리 결정된 수보다 크면, 프로그램 프로세스는 실패로 표시되고, 실패의 상태가 단계(370)에서 통지된다. 프로그램 카운터(PC)가 20 보다 작으면, 단계(372)에서,  $V_{pgm}$  레벨이 스텝 사이즈 만큼 증가되고 프로그램 카운터(PC)가 증분된다. 단계(372) 이후, 프로세스는 다음  $V_{pgm}$  펄스를 인가하기 위하여 단계(360)로 되돌아간다.

[0045] 성공적인 프로그램 프로세스의 종료시, 바람직하게는 메모리 셀들의 임계 전압들은 프로그램된 메모리 셀들에 대한 하나 이상의 임계 전압 분포들 내에 또는 소거된 메모리 셀들에 대한 임계 전압 분포 내에 있어야 한다. 도 12는 각 메모리 셀이 2 비트의 데이터를 저장할 때 메모리 셀에 대한 임계 전압 분포를 나타낸다. 도 12는 소거된 메모리 셀들에 대한 제 1 임계 전압 분포(E)를 나타낸다. 프로그램된 메모리 셀들에 대한 3개의 임계 전압 분포들(A, B 및 C) 또한 도시되어 있다. 일 실시예에서, E 분포에서의 임계 전압들은 음의 값을 갖고, A, B 및 C 분포들에서의 임계 전압들은 양의 값을 갖는다.

[0046] 도 12의 각각의 별개의 임계 전압 범위는 데이터 비트 세트에 대한 미리 결정된 값들에 대응한다. 메모리 셀에 프로그램된 데이터와 셀의 임계 전압 레벨들 간의 특정의 관계는 셀들에 대해 채택된 데이터 인코딩 체계에 의존한다. 일 실시예에서, 데이터 값들은 그레이 코드 할당을 이용하여 임계 전압 범위로 지정되는데, 이는 플로팅 게이트의 임계 전압이 임계 전압에 인접한 물리적 상태로 잘못 천이하였을 지라도 단지 하나의 논리 비트만 영향을 받도록 하기 위함이다. 그러나, 다른 실시예들에서는 그레이 코딩이 사용되지 않는다. 일 예는 임계 전압 범위(E)(상태 E)에 "11"을, 임계 전압 범위(A)(상태 A)에 "10"을, 임계 전압 범위(B)(상태 B)에 "00"을 및 임계 전압 범위(C)(상태 C)에 "01"을 할당한다. 도 12가 4개의 상태를 나타내지만, 본 발명에 따른 실시예들은 4개보다 많거나 적은 상태들을 포함하는 다른 다중 상태 구조들이 포함될 수 있다.

[0047] 도 12는 또한 풀 시퀀스 프로그래밍(full sequence programming)을 이용하는 일 실시예를 나타낸다. 풀 시퀀스 프로그래밍에서, 메모리 셀들은 소거 상태(E)로부터 프로그램 상태(A, B 또는 C) 중 어느 하나의 상태로 바로 프로그램될 수 있다. 예를 들면, 프로그램되어야 하는 메모리 셀들의 집단(population)이 먼저 소거됨으로써, 그 집단 내의 모든 메모리 셀들이 소거 상태(E)가 된다. 선택된 메모리 셀들의 제어 게이트에 인가된 일련의 프로그램 전압 펄스들을 이용하는 도 11에 도시된 프로세스는 메모리 셀들을 상태들(A, B 또는 C)로 직접 프로그램하는 데에 이용될 것이다. 몇몇 메모리 셀들이 상태(E)에서 상태(A)로 프로그램되는 동안, 다른 메모리 셀들은 상태(E)에서 상태(B) 및/또는 상태(E)에서 상태(C)로 프로그램된다.

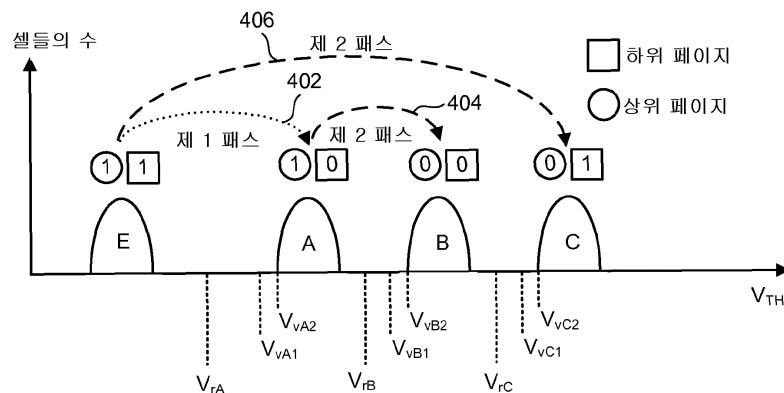

[0048] 도 13은 2개의 다른 페이지들(하위 페이지 및 상위 페이지)에 데이터를 저장하는 다중-상태 메모리 셀들을 프로그램하는 2-패스 기술의 일 예를 보여준다. 4개의 상태들(상태(E(11)), 상태(A(10)), 상태(B(00)) 및 상태(C(01)))이 도시된다. 상태(E)에서, 양 페이지들은 "1"을 저장한다. 상태(A)에서, 하위 페이지는 "0"을 저장하고 상위 페이지는 "1"을 저장한다. 상태(B)에서, 양 페이지들은 "0"을 저장한다. 상태(C)에서, 하위 페이지는 "1"을 저장하고 상위 페이지는 "0"을 저장한다. 비록 특정 비트 패턴들이 각 상태들에 할당되었지만, 다른 비트 패턴들도 할당될 수 있다는 점이 주목된다. 제 1 프로그래밍 패스에서, 셀의 임계 전압 레벨은 하위 논리 페이지 내에 프로그램될 비트에 따라 설정된다. 만약 그 비트가 "1"이면, 이전에 소거된 결과로서 임계 전압이 적절한 상태에 있기 때문에, 임계 전압은 변하지 않는다. 그러나, 프로그램될 비트가 "0"이면, 화살표(402)에 의해 도시된 바와 같이 셀의 임계 레벨은 상태(A)로 증가된다. 이에 의해, 제 1 프로그래밍 패스가 끝난다.

[0049] 제 2 프로그래밍 패스에서, 셀의 임계 전압 레벨은 상위 논리 페이지 내에 프로그램되고 있는 비트에 따라 설정된다. 만약 상위 논리 페이지 비트가 "1"을 저장하는 경우에는, 하위 페이지 비트의 프로그래밍에 따라, 셀들이 모두 상위 페이지 비트 "1"을 수행하는 상태들(E 또는 A) 중 하나에 있기 때문에, 어떠한 프로그래밍도 발생하

지 않는다. 만약 상위 페이지 비트가 논리 "0"으로 될 예정이라면, 임계 전압은 천이된다. 만약 제 1 패스가 소거 상태(E)에 존재하는 셀에서 발생했다면, 화살표(406)로 도시된 바와 같이, 제 2 모드에서 셀이 프로그램되는 바, 임계 전압이 증가되어 상태(C) 내에 있기 위함이다. 만약 셀이 제 1 프로그래밍 패스의 결과로 상태(A)로 프로그램되었다면, 화살표(404)로 도시된 바와 같이, 메모리 셀은 제 2 패스에서 더 프로그램되는바, 임계 전압이 상태(B) 내가 되게 증가되기 위함이다. 제 2 패스의 결과는 하위 페이지에서 데이터를 변경하지 않으면서, 상위 페이지에서 논리 "0"을 저장하도록 지정된 상태로 셀을 프로그램하는 것이다. 2-패스 프로그래밍 방법에서는, 다수의 프로그래밍 또는 검증 단계들이 도 11에 도시된 방법의 단일 반복(iteration)에 사용될 수 있다. 단계들(358 내지 372)은 프로그래밍 동작의 각 패스에 대해서 수행될 수 있다. 제 1 패스에서, 하나 이상의 프로그램 펄스들이 인가될 수 있고, 셀이 적절한 중간 상태에 있는지를 결정하기 위하여 그 결과들이 검증된다. 제 2 패스에서, 하나 이상의 프로그램 펄스들이 인가될 수 있고 셀이 적절한 최종 상태에 있는지를 결정하기 위하여 그 결과들이 검증된다. 몇몇 실시예에서, 이 기술은 단계들(350 내지 356)에 도시된 바와 같이 어드레스 및 프로그램 데이터의 개별적인 입력들뿐만 아니라 개별적인 데이터 로드 및 프로그램 명령들을 포함할 수 있다.

[0050]

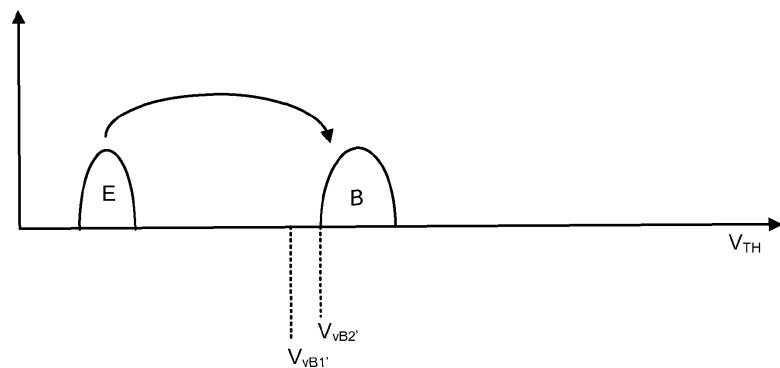

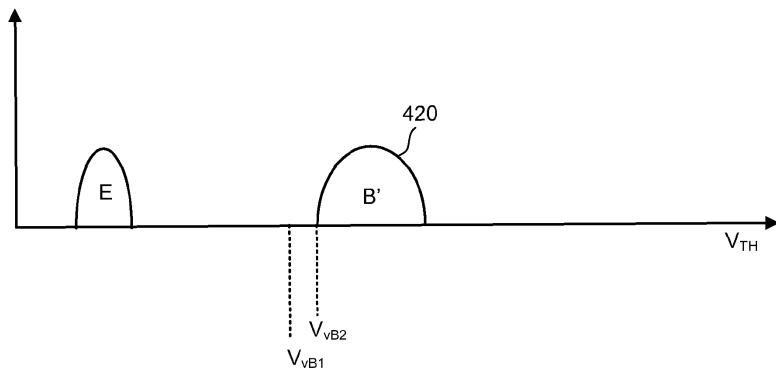

도 14A 내지 14C는 비휘발성 메모리를 프로그램하는 다른 프로세스를 개시하는 바, 이는 임의의 특정 메모리 셀에 대하여, 이전의 페이지들에 대해 인접하는 메모리 셀들을 기록한 이후에 특정 페이지에 관하여 상기 특정 메모리 셀을 기록함으로써, 플로팅 게이트 간의 결합(floating gate to floating gate coupling)을 감소시킨다. 도 14A 내지 14C에 의해 교시된 프로세스의 일 실시예에서, 비휘발성 메모리 셀들은 4개의 데이터 상태들을 이용하여 메모리 셀마다 2비트 데이터를 저장한다. 예를 들면, 상태(E)가 소거 상태이고, 상태들(A, B 및 C)이 프로그램 상태들이라 가정한다. 상태(E)는 데이터 11을 저장한다. 상태(A)는 데이터 01을 저장한다. 상태(B)는 데이터 10을 저장한다. 상태(C)는 데이터 00을 저장한다. 또한, 물리적 데이터 상태들에 대한 다른 데이터 인코딩이 이용될 수도 있다. 각 메모리 셀은 데이터의 2페이지들을 저장한다. 참조를 위해, 데이터의 이 페이지들은 상위 페이지 및 하위 페이지로 불려지지만, 이 페이지들에는 다른 라벨들이 붙여질 수 있다. 도 14A 내지 14C의 프로세스에 대한 상태(A)와 관련하여, 상위 페이지는 비트 0을 저장하고 하위 페이지는 비트 1을 저장한다. 상태(B)와 관련하여, 상위 페이지는 비트 1을 저장하고 하위 페이지는 비트 0을 저장한다. 상태(C)와 관련하여, 양 페이지들은 비트 데이터 0을 저장한다. 도 14A 내지 14C의 프로그래밍 프로세스는 2-단계 프로세스이다. 제 1 단계에서, 하위 페이지가 프로그램된다. 만약 하위 페이지가 데이터 1을 유지하면, 메모리 셀 상태는 상태(E)로 유지된다. 만약 데이터가 0으로 프로그램되면, 메모리 셀의 임계 전압이 증가되는 바, 메모리 셀이 중간(interim) 상태(B')로 프로그램되기 위함이다. 도 14B는 메모리 셀들의 상태(E)에서 상태(B')로의 프로그래밍을 나타낸다. 도 14A에 도시된 상태(B')는 중간 상태(B')이다. 그러므로,  $V_{VB}$  보다 낮은 검증 포인트는  $V_{VB}'$ 로 도시된다.

[0051]

일 실시예에서, 메모리 셀이 상태(E)에서 상태(B)로 프로그램된 후, NAND 스트링의 메모리 셀의 인접 메모리 셀이 메모리 셀의 하위 페이지에 대하여 프로그램될 것이다. 예를 들면, 다시 도 7을 참조하면, 메모리 셀(106)의 하위 페이지가 프로그램된 후, 메모리 셀(104)의 하위 페이지가 프로그램될 것이다. 메모리 셀(104)을 프로그램한 후, 만약 메모리 셀(104)이 상태(E)로부터 상태(B)로 증가된 임계 전압을 갖는다면, 플로팅 게이트 간 결합 효과는 메모리 셀(106)의 피상(apparent) 임계 전압을 증가시킬 것이다. 이는 상태(B)에 대한 임계 전압 분포를 도 14B의 임계 전압 분포(320)로 도시된 것으로 확장시키는 효과를 가질 것이다. 임계 전압 분포의 이 피상적인 확장은 상위 페이지를 프로그램할 때 고정될 것이다.

[0052]

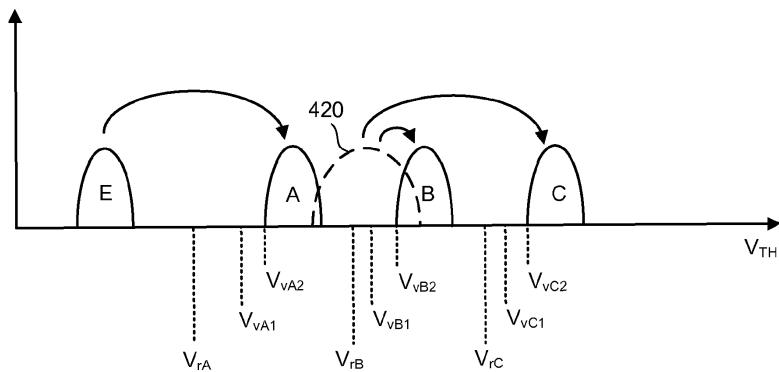

도 14C는 상위 페이지를 프로그램하는 프로세스를 나타낸다. 메모리 셀이 소거 상태(E)에 있고 상위 페이지가 1로 유지되면, 메모리 셀은 상태(E)로 유지될 것이다. 메모리 셀이 상태(E)에 있고 그 상위 페이지 데이터가 0으로 프로그램되면, 메모리 셀의 임계 전압은 메모리 셀이 상태(A)에 있기 위하여 증가될 것이다. 메모리 셀이 중간 임계 전압 분포(320)에 있었고 상위 페이지 데이터가 1로 유지되면, 메모리 셀은 최종 상태(B)로 프로그램될 것이다. 메모리 셀이 중간 임계 전압 분포(320)에 있고 상위 페이지 데이터가 데이터 0이 되면, 메모리 셀의 임계 전압은 메모리 셀이 상태(C)에 있기 위하여 증가될 것이다. 인접하는 메모리 셀들의 상위 페이지 프로그래밍 만이 주어진 메모리 셀의 피상 임계 전압에 영향을 미칠 것이기 때문에, 도 14A내지 14C에 도시된 프로세스는 플로팅 게이트 간 결합 효과를 감소시킨다.

[0053]

비록 도 14A 내지 14C가 4개의 데이터 상태들 및 데이터의 2개의 페이지들에 대한 일 예를 제공하지만, 도 14A 내지 14C에 의해 교시된 사상은 4개의 상태들 보다 많거나 적고 다른 수의 페이지들을 갖는 다른 실시예들에도 적용될 수 있다.

[0054]

도 12, 13 및 14A 내지 14C는 메모리 셀들로부터 데이터를 판독하기 위한 판독 참조 전압들,  $V_{rA}$ ,  $V_{rB}$  및  $V_{rC}$ 를

보여준다. 소정의 메모리 셀의 임계 전압이  $V_{rA}$ ,  $V_{rB}$  및  $V_{rC}$  보다 높거나 낮은지 점검함으로써, 시스템은 메모리 셀이 어떤 상태에 있는지를 결정할 수 있다.  $V_{rA}$ 의 인가된 제어 게이트 전압( $V_{cg}$ )을 도통하는 셀은 상태(E)에 있고,  $V_{rA}$ 가 아닌  $V_{rB}$ 에서 도통하는 셀은 상태(A)에 있고,  $V_{rB}$ 가 아닌  $V_{rC}$ 에서 도통하는 셀은 상태(B)에 있으며,  $V_{rA}$ ,  $V_{rB}$  또는  $V_{rC}$ 에서 도통하지 않는 셀은 상태(C)에 있다.

[0055] 판독 및 검증 동작들에서, 선택된 블록의 선택 게이트들은 하나 이상의 선택 전압들로 증가되고, 선택되지 않은 웨드라인들(예를 들어, WL0, WL2 및 WL3)은 트랜지스터를 패스 게이트들로 동작하게 하기 위하여 판독 패스 전압( $V_{read}$ )(예를 들어, 4.5볼트)으로 증가된다. 소스 및 p-웰은 0볼트에 있다. 선택된 웨드라인(BLe)은, 예를 들어 0.7V의 레벨로 프리차지된다. 선택된 웨드라인(예를 들어, WL1)은 판독 또는 검증 전압에 연결되는 바, 판독 또는 검증 전압의 레벨은 관련 메모리 셀의 임계 전압이 이와 같은 레벨 이상인지 이하인지를 결정하기 위하여 각 판독 및 검증 동작에서 지정된다. 만약 임계 전압이 웨드라인 상의 판독 또는 검증 레벨보다 높으면, 관심대상의 셀과 관련된 비트라인(BLe)의 전위 레벨은 비전도성의 메모리 셀 때문에 상위 레벨을 유지한다. 반면에, 상기 임계 전압이 상기 판독 또는 검증 레벨보다 낮을 경우, 비트라인을 방전하는 전도성 메모리 때문에, 관련된 비트라인(BLe)의 전위 레벨은, 예를 들어 0.5V 보다 작은 하위 레벨로 감소한다. 따라서, 메모리 셀의 상태는, 결과적인 비트라인 전압을 감지하기 위해 비트라인에 연결된 전압 비교기 감지 증폭기에 의해 검출된다.

[0056] 상술된 상기 소거, 판독 및 검증 동작들은 종래 기술에 따라 수행된다. 따라서, 설명된 많은 세부사항들이 당업자에 의해 변형될 수 있다. 종래의 다른 소거, 판독 및 검증 동작들이 또한 사용될 수 있다.

[0057] 도 12, 13 및 14A 내지 14C는 또한  $V_{vA2}$ ,  $V_{vB2}$  및  $V_{vC2}$ 를 포함하는 검증 전압들을 나타낸다. 메모리 셀들을 상태(A)로 프로그램할 때, 시스템은 메모리 셀들이 메모리 셀들의 최종 목표 레벨에 도달했는지를 검증하기 위하여 그 메모리 셀들이  $V_{vA2}$  보다 크거나 같은 임계 전압들을 갖는지를 검사할 것이다. 메모리 셀들을 상태(B)로 프로그램할 때, 시스템은 메모리 셀들이 메모리 셀들의 최종 목표 레벨에 도달했는지를 검증하기 위하여  $V_{vB2}$ 보다 크거나 같은 임계 전압들을 갖는지를 검사할 것이다. 메모리 셀들을 상태(C)로 프로그램할 때, 시스템은 메모리 셀들이 메모리 셀들의 최종 목표 레벨에 도달했는지를 검증하기 위하여  $V_{vC2}$  보다 크거나 같은 임계 전압들을 갖는지를 검사할 것이다.

[0058] 이상에서 설명된 바와 같이, 비정밀/정밀 프로그래밍은 프로그램 가능한 상태들 중 하나 이상에 대한 검증 전압들의 두 세트들을 이용한다. 이는, 메모리 셀에 대한 프로그래밍의 최종 레벨을 검증하고, 추가적으로 셀이 그 의도된 상태에 대한 최종 검증 레벨에 가까워지지만 아직 도달하지 않았을 때 셀들을 비정밀 프로그래밍 모드에서 정밀 프로그래밍 모드로 전환하기 위함이다. 도 12, 13 및 14A 내지 14C에서 검증 레벨들의 두 세트들은 각 프로그램된 상태에 대하여 나타낸다. 메모리 셀이 그 의도된 상태에 대한 최종 검증 레벨에 도달했는지를 검증하기 위하여 검증 레벨들( $V_{vA2}$ ,  $V_{vB2}$  및  $V_{vC2}$ )이 이용되는 반면, 메모리 셀이 비정밀 검증 레벨에 도달했는지를 검증하기 위하여 검증 레벨들( $V_{vA1}$ ,  $V_{vB1}$  및  $V_{vC1}$ )이 이용된다. 그 의도된 상태에 대한 검증 레벨들 어디에도 도달하지 않은 셀들은 프로그래밍 프로세스의 다음 반복 동안에 풀(full) 또는 비정밀 프로그래밍을 겪는다. 그 의도된 상태에 대한 최종 검증 레벨이 아닌 비정밀 검증 레벨에 도달한 셀들은 다음 프로그래밍 반복 동안에 감소(reduced) 또는 정밀 레벨 프로그래밍을 겪는다. 그 의도된 상태가 최종 검증 레벨에 도달한 셀들은 다음 프로그래밍 반복 동안에 프로그래밍으로부터 금지된다. 비록 검증 레벨들의 두 개의 세트들이 도 12, 13 및 14A 내지 14C에서 각 프로그램 가능한 상태들을 나타내더라도, 몇몇 실시예들은 하나 이상의 상태들에 대한 비정밀 검증 레벨을 사용하지 않을 수 있다. 예를 들면, 몇몇 실시예들은 판독 중에 상이해야만 하는 더 높은 상태가 없기 때문에, 최상의 프로그램 가능한 상태에 대한 비정밀 검증 레벨들을 사용하지 않을 것이다. 이와 같은 실시예들이 고려된다.

[0059] 도 15는 비정밀/정밀 프로그래밍을 포함하는 예시적인 프로그래밍 프로세스의 일부 동안에 비휘발성 메모리 디바이스에 인가되는 다양한 신호들을 나타내는 타이밍도(timing diagram)이다. "프로그래밍"으로 표시된 제 1 시간 주기는 선택된 웨드라인(WL\_sel)의 하나 이상의 메모리 셀들을 프로그램하기 위해 인가된 신호들을 포함한다. 이 프로그래밍 주기는 일반화된 것으로서, 웨드라인에 인가된 제 1 프로그래밍 펄스 또는 제 2 또는 그 이후의 프로그래밍 펄스에 대응할 수 있다. 이 주기는 도 11의 단계(360)에 대응한다. 이 프로그래밍 주기는 소스라인을 낮은 양(low positive) 전압, 약 1V로 증가시킴으로써 시작한다. 이어서,  $V_{SG}$ (예를 들어, 3.5V)를 드레인 선택 게이트 라인(SGD)에 인가함으로써 드레인 선택 게이트가 개방된다(또는 턴온된다). 드레인 선택 게

이트를 개방시킨 후, 금지 전압( $V_{inhibit}$ )이 임의의 선택되지 않은 워드라인들에 인가된다. 도 15에서는, 홀수/짝수 프로그램 기법 또는 아키텍처를 추정한다. 비트라인(BLn)은 선택된 비트라인을 나타낸다. 그러므로, 블록의 인접하는 비트라인들(BLn+1, BLn+3 등 및 BLn-1, BLn-3 등)은 프로그래밍 동작 내내 선택되지 않을 것이다. 일반적으로, 모든 비트라인들(예를 들어, 홀수 또는 짝수)은 모든 비트라인들(BLn, BLn+2 등)이 BLn에 인가된 동일한 신호들을 수신하도록 동시에 판독되고 프로그램된다.

[0060] 선택되지 않은 비트라인들은 금지 전압( $V_{inhibit}$ )까지 증가되는바, 선택되지 않은 비트라인들은 제 1 프로그래밍 주기 동안 내내 금지 전압( $V_{inhibit}$ )으로 유지된다. 선택된 비트라인(BLn)은 그 특정 비트라인에서 선택된 워드라인의 메모리 셀 내에 프로그램될 데이터에 따라 설정되거나 바이어스된다. 만약 비트라인(BLn)의 메모리 셀이 프로그래밍으로부터 금지되어야 한다면, BLn은 전압 레벨( $V_{inhibit}$ )로 증가된다. 일 실시예에서,  $V_{inhibit}$ 는  $V_{DD}$ (예를 들어, 1.8V-3.3V)와 동일하다. 만약 비트라인(BLn)의 메모리 셀이 풀 또는 비정밀 프로그래밍이 가능하게 된다면, BLn은 인에이블 전압( $V_{enable}$ )으로 증가된다. 일 실시예에서,  $V_{enable}$ 는 접지 또는 0V와 동일하다. 만약 비트라인(BLn)의 메모리 셀이 프로그램되어야 하는 상태에 대한 비정밀 검증 레벨에 도달했으나 그 상태에 대한 최종 검증 레벨에 도달하지 않았으면, 그 비트라인은 중간 레벨( $V_S$ )까지 증가된다. 일 실시예에서,  $V_S$ 는 대략 2.0V와 동일하다.  $V_S$ 의 값은 실시예마다 다를 수 있고,  $V_{inhibit}$ 의 레벨 및 다른 장치 특성들에 의존한다. 도 15의 실선(450)은 선택된 워드라인에서 메모리 셀의 프로그래밍을 금지하기 위해 비트라인(BLn)이  $V_{inhibit}$ 으로 증가되는 상황을 나타낸다. 점선(452)은 선택된 워드라인에서 메모리 셀의 부분 또는 정밀 레벨 프로그래밍을 허용하기 위해 비트라인(BLn)이  $V_S$ 까지 증가되는 상황을 나타낸다. 점선(454)은 선택된 워드라인에서 메모리 셀의 풀 또는 비정밀 레벨 프로그래밍을 허용하기 위해 비트라인(BLn)이  $V_{enable}$  전압을 수신하는 상황을 나타낸다.

[0061] 각 선택된 비트라인들의 메모리 셀에 인가될 프로그래밍의 양에 따라 각 선택된 비트라인들을 바이어스한 후, 워드라인들이 바이어스된다. WL\_unsel로 표시된 선택되지 않은 워드라인들은 패스 전압( $V_{pass}$ )까지 증가된다. 이 전압( $V_{pass}$ )은 이 프로그래밍 주기 동안에 프로그래밍으로부터 금지되는 메모리 셀을 갖는 NAND 스트링들에 대한 NAND 스트링 채널의 부스팅(boosting)을 가능하게 한다. 선택된 워드라인(WL\_sel)은 또한 프로그래밍을 겪지 않을 WLn에서 메모리 셀을 포함하는 NAND 스트링들에 대한 채널들의 부스팅을 가능하게 하기 위하여 전압( $V_{pass}$ )까지 증가된다. 각 워드라인을  $V_{pass}$  레벨로 증가시킨 후, 선택된 워드라인이 프로그램 전압 펄스 레벨( $V_{pgm1}$ )로 증가된다. 선택된 워드라인에 프로그래밍 펄스를 인가한 후, 워드라인들은 0V로 감소된다. 워드라인들을 0V로 감소시킨 후, 선택되지 않은 그리고 선택된 비트라인들은 각각 0V로 감소된다. 그런 다음, 드레인측 선택 게이트는 드레인 선택 게이트 라인(SGD)에 0V를 인가함으로써 턴오프된다. 프로그래밍 주기는 소스 라인 전압을 1V에서 0V로 감소시킴으로써 완료된다.

[0062] 도 15의 전압 펄스( $V_{pgm1}$ )를 인가한 후에 제 1 프로그래밍 주기에 후속하는 검증 동작이 시작된다. 도 15에서 표시된 바와 같이 검증 동작은 비정밀 레벨 검증과 정밀 레벨 검증으로 분리된다. 비정밀 레벨 검증은 비트라인(BLn)(각각의 다른 선택된 비트라인을 따라)을 미리 결정된 전압 레벨( $V_{clamp}$ )로 프리챠지시킴으로써 시작된다.  $V_{clamp}$ 는 일 실시예에서 약 0.7V와 동일하다. 일단 비트라인이 프리챠지되면, 워드라인들은 비정밀 레벨 감지에 대하여 바이어스된다. 선택되지 않은 워드라인들에는 판독 패스 전압( $V_{read}$ )이 공급된다. 이러한  $V_{read}$ 는 선택되지 않은 메모리 셀들이 선택되지 않은 메모리 셀들이 프로그램되는 상태에 관계없이 검증 프로세스 동안에 턴온되거나 전도성을 가지게 될 것을 보장하는 패스 전압이다. 이것은 워드라인(WL\_sel)에서 바로(just) 메모리 셀들에 대한 검증을 허용한다.  $V_{read}$ 가 선택되지 않은 워드라인들에 인가됨과 동시에, 선택된 워드라인에는 비정밀 레벨 검증 전압( $V_{v1}$ )이 공급된다. 각 워드라인에 적절한 바이어스 상태들을 인가한 후,  $V_{SG}$ 를 드레인 선택 게이트 라인(SGD) 및 소스 선택 게이트 라인(SGS)에 인가함으로써 드레인측 선택 게이트 및 소스측 선택 게이트가 모두 턴온된다. 도 15에서 일반화된 설명이 임의의 특정 상태에 관계없이 제공된다는 점에 주목해야 한다. 그러므로,  $V_{v1}$ 은 상태(A), 상태(B), 상태(C) 또는 다른 상태에 대한 비정밀 검증 레벨에 대응할 수 있다.

[0063] 선택된 비트라인들을 프리챠지시키고, 워드라인들을 바이어스하고, 선택 게이트들을 턴온시킨 후, 선택된 비트라인들은 선택된 워드라인(WL\_sel)에도 연결된 그 비트라인의 메모리 셀의 상태에 따라 자유롭게 방전할 수 있다. 점선(454)은 임계 전압( $V_{th}$ )이 비정밀 검증 레벨,  $V_{v1}$  이하인 메모리 셀을 나타낸다. 메모리 셀은 비정밀 검

증 레벨 이하의 임계 전압을 갖기 때문에, 메모리 셀은 NAND 스트링을 통해 비트라인 및 소스 라인 사이의 도통을 허용하기 위하여 검증 레벨의 인가하에 턴온될 것이다. 따라서, 이와 같은 메모리 셀의 비트라인은 구현에 따라 프리차지된 레벨( $V_{\text{clamp}}$ )에서 약 0.5V 또는 그 이하로 방전될 것이다. 도 15에는, 0V까지의 방전이 도시된다. 실선(450)은 비정밀 검증 레벨( $V_{\text{v1}}$ ) 이상의 임계 전압을 갖는 BLn에서의 메모리 셀을 나타낸다. 비정밀 검증 레벨( $V_{\text{v1}}$ ) 이상의 임계 전압을 갖는 메모리 셀은 턴온되지 않을 것이고, 비트라인 전압은 실질적으로  $V_{\text{clamp}}$ 로 유지될 것이다. 드레인측 선택 게이트의 개방에 후속하는 미리 결정된 시간 주기 후, 선택된 비트라인 상에서 감지가 수행된다. 감지 동작은 비트라인 상에서 전압을 감지하고 감지된 전압을 기준 전위( $V_{\text{sense}}$ )와 비교한다. 각 선택된 비트라인에 대한 감지 증폭기는 이 비교에 근거하여 WL\_se1에서 메모리 셀의 임계 전압이 검증 레벨( $V_{\text{v1}}$ ) 이상인지 결정한다. 만약 비트라인 전압이  $V_{\text{sense}}$  이하로 방전하면,  $V_{\text{v1}}$  이하의 임계 전압을 갖는 메모리 셀을 나타낸다. 만약 비트라인 전압이  $V_{\text{sense}}$  이하로 방전하면,  $V_{\text{v1}}$  이상의 임계 전압을 갖는 메모리 셀을 나타낸다. 비트라인 전압을 감지하고 감지된 비트라인을  $V_{\text{sense}}$ 과 비교함으로써 비정밀 레벨 검증 프로세스가 완료된다.

[0064]

도 15의 실시예에서, 비정밀 레벨 검증 후에 비트라인은 다시 프리차지되지 않는다. 선택된 워드라인은 비정밀 검증 레벨에서 최종 또는 정밀 검증 레벨( $V_{\text{v2}}$ )로 바로 증가된다. 비정밀 검증 레벨과 마찬가지로,  $V_{\text{v2}}$ 는 일반적인 설명을 나타내고 상태(A), 상태(B) 등에 대한 최종 검증 레벨을 포함할 수 있다. 이 기술은 선택된 비트라인들을 프리차지시키는 데에 필요한 시간을 제거함으로써 효율적인 검증을 가능하게 한다. 이는 또한 비트라인들을 다시 대전시키기 위한 에너지를 생산할 필요성을 제거한다. 최종 검증 레벨( $V_{\text{v2}}$ )을 선택된 워드라인에 인가한 후, 선택된 비트라인들은 워드라인(WL\_se1)에서 메모리 셀의 상태에 따라 방전될 것이다. 도 15에서 점선(452)은 최종 검증 레벨( $V_{\text{v2}}$ ) 이하인, 그러나 비정밀 검증 레벨( $V_{\text{v1}}$ ) 이상인 임계 전압을 갖는 메모리 셀을 나타낸다. 이와 같은 메모리 셀은 인가된 비정밀 검증 레벨로 방전하지 않고, 최종 검증 레벨이 인가될 때 비트라인을 방전하게 할 것이다. 이 메모리 셀들의 비트라인 전압은 정밀 레벨 검증 동안에 프리차지된 레벨에서 약 0.5V 또는 그 이하로 방전할 것이다. 실선(450)은 최종 검증 레벨( $V_{\text{v2}}$ ) 뿐만 아니라 비정밀 검증 레벨 이하의 임계 전압을 갖는 메모리 셀을 나타내기 위하여 계속된다.

[0065]

비트라인 전압은  $V_{\text{v2}}$ 의 인가에 후속하는 미리 결정된 양의 시간 이후에 다시 감지된다. 이 미리 결정된 양의 시간은 비정밀 레벨 감지 동안에 선택 게이트의 개방에 후속하는 시간 주기 또는 최종 검증 레벨의 인가에 후속하는 시간 주기로 표현되거나 설정될 수 있다. 감지된 전압은 기준 전위( $V_{\text{sense}}$ )와 비교된다. 만약 비트라인 전압이  $V_{\text{sense}}$  이하로 방전하지 않으면, 메모리 셀은 최종 검증 레벨( $V_{\text{v2}}$ ) 이상의 임계 전압을 갖도록 결정된다. 만약 비트라인은  $V_{\text{sense}}$  이하로 방전하면, 메모리 셀은 최종 검증 레벨( $V_{\text{v2}}$ ) 이하의 임계 전압을 갖는 것으로 결정된다. 감지한 후, 선택된 비트라인들이 0V로 감소된 다음, 워드라인들이 0V로 감소된다. 그런 다음, 드레인 및 소스 선택 게이트 라인들은 정밀 검증 프로세스를 완료하기 위하여 0V로 감소된다.

[0066]

다중-상태 메모리 디바이스가 이용되면, 비정밀 레벨 검증 및 정밀 레벨 검증 프로세스들은 대응하는 상태들에 대하여 필요한 만큼 많이 반복될 것이다. 예를 들어, 네 개의 상태 디바이스는 비정밀 및 정밀 레벨 검증들의 성능을 세번- A 상태 검증 레벨들에서 한번, B 상태 검증 레벨들에서 한번, 및 C 상태 검증 레벨들에서 한번-필요할 수 있다. A 상태에 대한 정밀 레벨 검증을 완료한 후에, 비트라인은 다시 프리차지되고 프로세스는 반복된다. B 상태에 대한 정밀 레벨 검증을 완료한 후에, 비트라인은 상태 C에 대한 비정밀 레벨 검증을 시작하기 위하여 다시 프리차지될 것이다. 몇몇 실시예들은 각 프로세스 동안에 각 상태 검증 레벨에서 감지하지 않을 수 있다. 예를 들어, 도 13에 도시된 바와 같이 메모리 셀들의 바로 상위 페이지 데이터를 관리하는 것은 상태 B 검증 레벨들에서 감지하는 것 만을 필요로 한다.

[0067]

도 15는 소스 전위를 1V로 증가시킨 후에 최종 검증 레벨들에 아직 도달하지 않은 메모리 셀들을 더 프로그램하기 위해 사용될 수 있는 프로그래밍 프로세스의 추가적인 반복을 나타낸다. 드레인측 선택 게이트는  $V_{\text{SG}}$ 를 드레인 소스 선택 게이트 라인(SGD)에 인가함으로써 턴온된다. 선택되지 않은 비트라인들(BLn+1/BLn-1)은  $V_{\text{inhibit}}$ 으로 증가된다. 그런 다음, 선택된 비트라인(BLn)은 이전의 검증 동작의 결과들 및 선택된 비트라인에 프로그램된 데이터에 따라 바이어스된다. 도 15에 도시된 화살표들은 다음의 프로그래밍 반복 동안에 인가되는 대응하는 비트라인 전압 레벨들을 나타낸다. 비정밀 검증 레벨(점선(454))의 인가 하에 비트라인을 방전한 메모리 셀에는 메모리 셀이 다음 반복 동안에 풀 프로그래밍을 겪을 수 있도록 인에이블 전압( $V_{\text{enable}}$ )이 공급된다. 비정밀 검증

레벨이나 최종 검증 레벨(실선(450)) 하에 비트라인을 방전하지 않은 메모리 셀은 그 최종 검증 레벨에 도달한 메모리 셀을 나타낸다. 따라서, 메모리 셀의 비트라인은  $V_{inhibit}$ 으로 바이어스된다. 비정밀 검증 레벨 하에 대응하는 비트라인을 방전하지 않았지만 최종 검증 레벨 하에 비트라인을 방전한 메모리 셀들은 그들이 다음 프로그래밍 반복 동안에 정밀 프로그래밍을 겪을 수 있도록 중간 전압 레벨( $V_s$ )로 증가된다.

[0068]

각 선택된 비트라인을 바이어스한 후, 선택되지 않은 그리고 선택된 워드라인들은 그들의 패스 전압 레벨들 ( $V_{pass}$ )로 증가된다. 그런 다음, 선택된 워드라인은 제 2 프로그래밍 전압 펄스 레벨( $V_{pgm2}$ )로 램프(ramp)된다. 제 2 펄스는 일반적으로 선행하는 펄스보다 스텝 사이즈( $V_{pgm}$ ) 만큼 증가된다.  $V_{pgm2}$ 를 인가한 후, 워드라인들은 0V까지 하향 복구된다. 선택된 그리고 선택되지 않은 비트라인들은 또한 0V까지 하향 복구되고, 드레인 선택 게이트들은 턴오프된다. 그리고 소스 라인 전위는 0V까지 낮아진다. 도 15에 도시된 실시예는 일반적인 구현에서 프로그래밍 및 검증 프로세스의 일부만을 나타낸다는 점이 다시 주목된다. 각 펄스의 인가를 사이에 수행된 적절한 레벨들에서 비정밀 및 정밀 레벨 검증으로 각 선택된 메모리 셀을 목표 레벨로 프로그램하기 위하여 하나 이상의 프로그램 전압 펄스들이 인가될 수 있다.

[0069]

도 16은 도 15에서 및 도 11의 단계(362) 동안에 수행될 수 있는 것과 같은 특정 상태에 대한 비정밀 레벨 및 정밀 레벨 감지 동작들을 더욱 상세하게 보여주는 그래프이다. 도 16의 그래프는 비트라인 전압( $V_{BL}$ )을 시간의 함수로 그린다. 도 16의 타이밍도에 두 개의 상이한 메모리 셀들이 표시된다. 실선(460)은 감지 동작 이전에 프로그램될 상태에 대한 최종 검증 레벨 바로 위의 임계 전압을 갖는 메모리 셀을 나타낸다. 예를 들면, 도 12를 참조하여 실선은 최종 검증 레벨( $V_{vB2}$ )을 바로 초과하는 임계 전압을 갖는 상태 B에 대한 목표된(targeted) 메모리 셀을 나타낼 수 있다. 점선(462)은 프로그램될 상태에 대한 최종 검증 레벨 바로 아래의 임계 전압을 갖는 메모리 셀을 나타낸다. 예를 들어, 점선은 최종 검증 레벨( $V_{vB2}$ ) 바로 아래의 임계 전압을 갖는 메모리 셀을 나타낼 수 있다. 도시된 메모리 셀들은 모두 프로그램되는 상태에 대한 비정밀 검증 레벨 이상의 임계 전압을 갖는다.

[0070]

메모리 셀들에 대한 비트라인들은 미리 결정된 레벨( $V_{clamp}$ )로 프리챠지된다. 그리고 선택된 워드라인에 비정밀 검증 레벨( $V_{v1}$ )(예를 들어,  $V_{cg}=V_{vB1}$ )이 인가된다. 그리고 드레인 선택 게이트들은 각 NAND 스트링을 NAND 스트링의 비트라인으로 연결하기 위하여 턴온된다. 도 16이 나타내는 바와 같이, 각 메모리 셀이 비정밀 검증 레벨 이상의 임계 전압을 갖더라도 비트라인들은 몇몇 방전을 경험할 것이다. 비트라인들의 임계 전압보다 낮은 제어 게이트 전압( $V_{cg}$ )의 인가에도 불구하고, 트랜지스터-기반의 메모리 셀들은 비트라인들의 소스 및 드레인 사이의 전류의 일부의 양을 여전히 도통할 것이다. 특히 작은 크기의 현대의 장치들에서 제조된 메모리 셀들은 양의(positive) 게이트 바이어스의 인가 하에 절대적 오프 상태(absolute off condition)로 배치되지 않는다. 트랜지스터가 그 임계 전압 이하의 인가된 게이트 전압으로 전류를 도통하게 되는 정도는 디바이스의 서브-임계 스윙 팩터(S-factor)로 표시된다.

[0071]

일반적으로, 상업적으로 제조된 메모리 셀들은 낮은 서브-임계 스윙 팩터들을 보인다. 도 16은 메모리 셀이 메모리 셀의 임계 전압보다 적은, 인가된 제어 게이트 전압 하에 전류의 상당한 양을 도통하지 않기 위하여 낮은 서브-임계 스윙 팩터를 갖는 메모리 디바이스를 나타낸다. 게이트 전압이 임계 전압 이하가 될 때에도, 메모리 셀의 임계 전압은 당연히 도통의 레벨에 영향을 미칠 것이다. 따라서, 최종 검증 레벨 바로 위의 임계 전압을 갖는 도 16의 메모리 셀(실선(460))은 최종 검증 레벨 바로 아래의 임계 전압을 갖는 메모리 셀(점선(462))보다 더 작은 양으로 방전한다.

[0072]

개방되는 드레인 선택 게이트에 후속하는 미리 결정된 양의 시간 후, 감지 동작이 비정밀 검증 레벨에서 수행된다. 비트라인 전압이 감지되고 기준 전위 ( $V_{sense}$ )와 비교된다. 도 16에서 도시된 셀들 모두에 대하여, 비정밀 레벨 감지 동안에 비트라인 전압( $V_{BL}$ )이 감지 전압( $V_{sense}$ )보다 크다는 것이 결정된다. 따라서, 감지 증폭기는 각 메모리 셀이 비정밀 검증 레벨( $V_{v1}$ ) 이상의 임계 전압을 갖는다는 것을 결정한다.

[0073]

비정밀 검증 레벨에서 감지한 후, 최종 검증 레벨이 선택된 워드라인에 인가된다. 각 메모리 셀의 제어 게이트에는 최종 검증 전압( $V_{v2}$ (예를 들어,  $V_{cg}=V_{vB2}$ ))이 공급된다. 최종 검증 레벨 이상의 임계 전압을 갖는 메모리 셀은 턴온되지 않으며, 이에 따라 셀의 비트라인 전압은 최종 검증 레벨의 인가 하에 상당한 양으로 방전하지 않는다. 다시, 비트라인 전압은 서브-임계 스윙 팩터 때문에 어느 정도 방전할 것이나, 방전은 감지의 정확도가

영향받을 정도로 상당하지는 않는다. 최종 검증 레벨( $V_{v2}$ ) 이하의 임계 전압을 갖는 메모리 셀은 최종 검증 레벨의 인가하에 턴온되고 전도성을 갖는다. 따라서, 이 메모리 셀의 비트라인은 인가된 최종 검증 레벨의 상당한 양으로 방전한다.

[0074] 최종 검증 레벨의 인가에 후속하는 미리 결정된 양의 시간 후, 각 메모리 셀의 비트라인 전압이 감지된다. 다시, 이 미리 결정된 시간은 비정밀 레벨 감지에 대한 드레인 선택 게이트의 개방에 관하여 또는 최종 검증 전압의 인가에 관하여 정립될 수 있다. 실선(460)에 의해 표시된 메모리 셀은  $V_{sense}$  보다 크도록 결정된 비트라인 전압을 갖는다. 따라서, 감지 증폭기는 셀의 임계 전압이 최종 검증 레벨( $V_{v2}$ ) 보다 크다는 것을 결정한다. 이와 같은 셀은 다른 셀들에 대하여 필요한 임의의 후속하는 프로그래밍 반복들 동안, 다른 프로그래밍으로부터 금지될 수 있다. 점선(462)에 의해 표시된 메모리 셀은 미리 결정된 양의 시간 후에 기준 전위( $V_{sense}$ ) 이하의 대응하는 비트라인 전압을 갖는다. 이 셀에 대한 감지 증폭기는 비트라인 전압이 기준 전위( $V_{sense}$ ) 보다 낮으며, 이에 따라 메모리 셀의 임계 전압이 최종 검증 레벨( $V_{v2}$ ) 이하라는 것을 결정할 것이다.

[0075] 도 17은 큰 서브-임계 스윙 팩터를 갖는 메모리 디바이스를 나타내는 그래프이다. 다시, 최종 검증 레벨 바로 위의 임계 전압을 갖는 메모리 셀이 실선(460)에 의해 표시된다. 반면에 최종 검증 레벨 바로 아래의 임계 전압을 갖는 메모리 셀이 점선(462)에 의해 표시된다. 각 메모리 셀의 비트라인 전압은 프리챠지되고, 선택된 워드라인에 비정밀 검증 레벨이 인가된다. 비정밀 검증 레벨을 인가한 후, 비트라인을 셀의 NAND 스트링에 연결하기 위하여 드레인측 선택 게이트가 턴온된다. 도 17의 디바이스에 대한 큰 S-팩터 때문에 메모리 셀들의 임계 전압이 비정밀 검증 레벨( $V_{v1}$ ) 이상이 되더라도, 메모리 셀들은 메모리 셀들의 비트라인의 전압에 상당한 감소를 초래한다. 미리 결정된 양의 시간 이후, 비트라인 전압이 감지되고 기준 전위( $V_{sense}$ )와 비교된다. 각 셀에 대한 감지 증폭기는 비트라인들이  $V_{sense}$  이하로 방전하지 않았기 때문에, 이 메모리 셀들이 비정밀 검증 레벨( $V_{v1}$ ) 이상의 임계 전압을 갖는다는 것을 결정한다.

[0076] 비정밀 레벨 감지 후, 선택된 워드라인에는 최종 검증 레벨( $V_{v2}$ )이 공급된다. 최종 검증 레벨 바로 위의 임계 전압을 갖는 메모리 셀(실선(460))은 최종 검증 레벨 바로 아래의 임계 전압을 갖는 메모리 셀(점선(462)) 만큼 전도성을 갖지 않는다. 그러나, 도 17에 도시된 바와 같이, 메모리와 관련된 큰 S-팩터는 최종 검증 레벨 이상의 임계 전압을 갖는 메모리 셀의 비트라인 전압이  $V_{sense}$  이하로 방전하게 한다. 최종 검증 레벨 이하의 임계 전압을 갖는 메모리 셀은 또한 예상된 바와 같이 그것의 비트라인을  $V_{sense}$  이하로 방전한다. 정밀 레벨 감지 동안에, 최종 검증 레벨 이상의 임계 전압을 갖는 메모리 셀에 대한 감지 증폭기는 셀의 비트라인이  $V_{sense}$  이하로 방전했는지 결정한다. 따라서, 감지 증폭기는 메모리 셀이 최종 검증 레벨 이하의 임계 전압을 갖는지 결정한다. 이것은 감지 동작에서 오류를 나타낸다. 감지 회로는 메모리 셀이 아직 그 최종 목표 레벨로 프로그램되지 않는다는 것을 잘못 결정하고 셀이 다른 프로그래밍을 겪게 할 것이다. 또한 점선에 의해 표시된 메모리 셀은  $V_{sense}$  이하의 감지된 비트라인 전압을 갖는다. 이 셀에 대한 감지 증폭기는 셀의 임계 전압이 최종 검증 레벨( $V_{v2}$ ) 이하라는 것을 정확하게 결정한다.

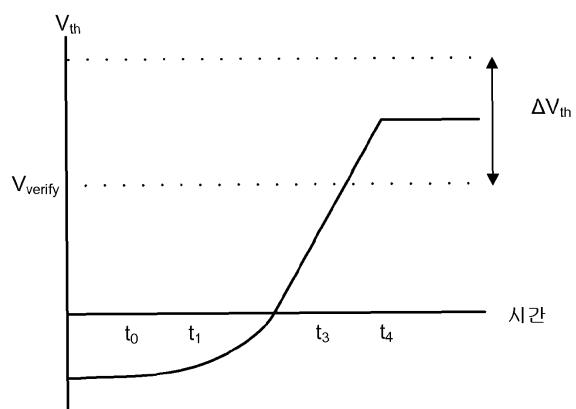

[0077] 도 18은 큰 S-팩터 장치들로부터 발생하는 비트라인 방전을 다룰 수 있는 본 발명의 일 실시예에 따른 비정밀 및 정밀 검증 및 감지 방법의 그래프이다. 실선(460)은 다시 최종 검증 레벨(예를 들어,  $V_{vA2}$ ) 바로 위의 임계 전압을 갖는 메모리 셀을 나타낸다. 점선(462)은 최종 검증 레벨 바로 아래의 임계 전압을 갖는 메모리 셀을 나타낸다. 각 메모리 셀의 비트라인은 미리 결정된 레벨( $V_{clamp}$ )로 프리챠지된다. 비트라인들을 프리챠지시킨 후, 선택된 워드라인에는 비정밀 검증 레벨( $V_{v1}$ (예를 들어,  $V_{cg}=V_{vA1}$ ))이 공급된다. 그리고 드레인측 선택 게이트는 비트라인이 방전하게 하기 위하여 턴온된다. 최종 검증 레벨 이상의 임계 전압을 갖는 메모리 셀은 큰 S-팩터 때문에 비트라인 전압에서 어느 정도 상당한 감소를 다시 겪을 것이다. 이와 유사하게, 최종 검증 레벨 이하의 임계 전압을 갖는 메모리 셀도 비트라인 전압에서 어느 정도 상당한 감소를 겪을 것이다. 미리 결정된 양의 시간 후, 각 메모리 셀의 비트라인 전압이 감지되고 기준 전위와 비교된다. 비정밀 레벨 감지 동안에, 감지된 비트라인 전압은 중간 기준 전위( $V_{sense1}$ )와 비교된다. 메모리 셀들에 대한 감지 증폭기는 비트라인 전압이 비정밀 검증 레벨( $V_{sense1}$ ) 보다 크다는 것을 결정할 것이다. 결과적으로, 감지 증폭기들은 각 메모리 셀의 임계 전압이 비정밀 검증 레벨( $V_{v1}$ ) 보다 크다는 것을 정확하게 결정한다.

[0078] 비정밀 검증 레벨에서 감지한 후, 선택된 워드라인에는 최종 검증 레벨( $V_{v2}$ )이 공급된다. 다시, 최종 검증 레벨 이상의 임계 전압을 갖는 메모리 셀은 디바이스의 큰 S-팩터 때문에 상당한 양의 전류를 도통할 것이다. 최종 검증 레벨 이하의 임계 전압을 갖는 메모리 셀은 예상된 바와 같이 더욱 전도성을 갖고 메모리 셀의 비트라인을 상당한 양으로 방전한다.

[0079] 미리 결정된 양의 시간 후에 각 메모리 셀의 비트라인 전압이 감지되고 기준 전위와 비교된다. 정밀 레벨 감지 동안에, 상이한 기준 전위가 이용된다. 감지된 비트라인 전압은 최종 기준 전위( $V_{sense2}$ )와 비교된다.  $V_{sense2}$ 는  $V_{sense1}$  보다 낮다. 더 낮은 기준 전위는 비정밀 검증 레벨의 인가 하에 발생하는 비트라인 방전을 보상한다. 이 보상은 메모리 셀이 검증 레벨 이상의 임계 전압을 갖는 경우에도, 메모리 셀들이 메모리 셀들의 비트라인을 어느 정도 상당한 양으로 방전하게 하는 메모리 디바이스와 관련된 큰 S-팩터를 고려한다. 도 18에서, 최종 검증 레벨 바로 위의 임계 전압을 갖는 메모리 셀은  $V_{sense2}$ 와 비교되는 메모리 셀의 감지된 비트라인 전압을 갖는다. 이 경우, 감지 증폭기는 비트라인 전압이 최종 기준 전위( $V_{sense2}$ ) 보다 크다는 것을 결정할 것이다. 따라서, 감지 증폭기는 메모리 셀의 임계 전압이 최종 검증 레벨( $V_{v2}$ ) 보다 크다는 것을 정확하게 결정할 것이다. 최종 검증 레벨 바로 아래의 임계 전압을 갖는 메모리 셀에 있어서, 감지 증폭기는 감지된 비트라인 전압을 최종 기준 전위( $V_{sense2}$ )와 비교한다. 이 셀의 비트라인에 대한 감지 증폭기는 비트라인 전압이 최종 기준 전위( $V_{sense2}$ )보다 작다는 것을 결정할 것이다. 감지 증폭기는 다시 메모리 셀이 최종 검증 레벨( $V_{v2}$ ) 이하의 임계 전압을 갖는다는 것을 정확하게 결정할 것이다. 따라서, 비트라인이 각 감지 동작 사이에서 다시 프리챠지되지 않을 때 비정밀 레벨 검증과 정밀 레벨 검증 사이의 기준 전위의 레벨을 조정함으로써, 메모리 셀의 상태의 더욱 정확한 감지가 달성된다. 기준 전위들의 차이는 비정밀 레벨 검증 동안의 방전량의 보상을 제공한다.

[0080] 일 실시예에서, 최종 기준 전위( $V_{sense2}$ )는 중간 기준 전위( $V_{sense1}$ ) 보다 비정밀 레벨 감지 동안에 메모리 셀의 워드라인에  $V_{v1}$ 이 인가될 때 비정밀 검증 레벨( $V_{v1}$ ) 이상의 임계 전압을 갖는 메모리 셀에 대한 비트라인 전압의 예상된 방전과 대략 동일한 양만큼 적다. 인가된 검증 레벨 하에 이론적으로 비전도성을 갖는 메모리 셀은 장치의 큰 S-팩터로부터 발생하는 관련된 비트라인 전압 방전을 가질 것이다. 중간 및 최종  $V_{sense}$  레벨들 사이의 차이는 대략 비정밀 검증 레벨이 워드라인에 인가될 때 발생하는 비트라인 프리챠지 레벨 및 비트라인 전압 간의 차이로 설정될 수 있다. 이러한 방식으로, 최종 기준 전위( $V_{sense2}$ )는 큰 S-팩터 디바이스로부터 비롯되는 비트라인 방전을 보상한다. 소정의 구현의 요건들에 따라, 중간 기준 전위( $V_{sense1}$ ) 및 최종 기준 전위( $V_{sense2}$ )의 다른 값들이 이용될 수 있다. 예를 들어,  $V_{sense2}$ 는, 비정밀 검증 레벨이 워드라인에 인가될 때, 메모리 셀에 대한 비트라인의 예상된 방전 보다 작은 양 만큼  $V_{sense1}$  보다 작게 설정될 수 있다.  $V_{sense1}$ 에 대한  $V_{sense2}$ 의 더 작은 오프셋 (offset)은 비정밀 레벨 감지 동안에 비트라인 방전의 레벨을 여전히 수용할 수 있다. 일 실시예에서, 중간 기준 전위( $V_{sense1}$ )는 장치들이 평균 또는 더 낮은 S-팩터를 가질 때 사용될 수 있는 일반적인  $V_{sense}$  레벨과 대략 동일하다. 이와 같은 경우, 최종 기준 전위( $V_{sense2}$ )는 비정밀 레벨 감지 동안에 비트라인에서 감소를 보상할 수 있는 양만큼  $V_{sense1}$ 을 참조하여 조정된다.

[0081] 일 실시예에서, 메모리 어레이는 제조 프로세스 동안에 테스트를 겪는다. 이러한 테스트는 메모리 어레이 성능의 특성화를 포함할 수 있다. 예를 들어, 비정밀 검증 레벨이 워드라인에 인가되고 메모리 셀의 임계 전압이 이 비정밀 검증 레벨 이상일 때, 비트라인들이 방전할 양을 결정하기 위해 메모리 어레이가 측정될 수 있다. 일 실시예에서, 디바이스의 다중 비트라인들과 관련된 방전량은 적절한 양에 이르기 위하여 평균화될 수 있다. 제조 프로세스 동안, 비정밀 검증 레벨들의 인가 하에 비트라인 전압에서 측정된 감소를 수용하기 위해  $V_{sense1}$ 에 대해  $V_{sense2}$ 의 값이 설정될 수 있다. 추가적으로, 중간 기준 전위( $V_{sense1}$ )가 메모리 디바이스의 특성화에 근거할 수 있다. 몇몇 실시예들에서, 메모리 디바이스들의 선택된 서브셋이 점검되고 특성화될 수 있으며, 서브셋의 특성화된 결과들을 포함하는 디바이스들의 더 큰 세트에 대한  $V_{sense1}$  및  $V_{sense2}$ 를 설정하기 위해 특성화의 결과들이 이용된다. 다른 실시예들에서, 제조 프로세스는 그 특정 메모리 디바이스에 대한 테스트 및 특성화에 근거하여 각 메모리 디바이스에 대한  $V_{sense1}$  및  $V_{sense2}$ 의 레벨들을 설정할 수 있다. 또한, 비정밀 레벨 감지에서 정확도를 최적화하기 위하여 선택 게이트를 턴온시키는 것과 비정밀 레벨 감지를 수행하는 것 사이의 시간 주기를 설정하는 것도 가능하다. 유사하게, 최종 검증 레벨을 선택된 워드라인에 인가하는 것과 그 레벨에서 감지하는 것 사이의

시간 주기는 양 레벨들에서 정확한 감지를 더 제공하기 위한 테스트 및 특성화에 근거하여 선택될 수 있다. 이 상에서 언급된 바와 같이, 비정밀 레벨 감지 동안에 감지 전의 시간은 선택 게이트들이 비정밀 레벨 감지 동안에 턴 온되는 시간에 대해 또는 정밀 검증 레벨이 선택된 워드라인에 인가되는 시간에 대해 설정될 수 있다. 다양한 기술들이 특성화 후의 이 값들을 설정하기 위해 사용될 수 있다. 예를 들어, 디바이스의 동작에 대하여 데이터를 저장하기 위하여 안티-퓨즈들(anti-fuses)의 세트, 전기적으로 프로그램 가능한 퓨즈들 등이 메모리 디바이스 내에 제공될 수 있다. 이 퓨즈들은  $V_{sense}$ 의 값들 및/또는 감지에 대한 시간 주기들을 나타내는 데이터를 저장하도록 설정될 수 있다.

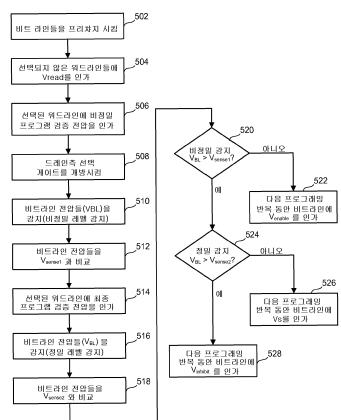

[0082] 도 19는 하나 이상의 셀들의 프로그래밍을 검증하기 위한 프로세스를 나타내는 흐름도이다. 일 실시예에서 도 19의 프로세스는 단계(360)에서 각 프로그램 펄스를 인가한 후에 도 11의 단계(362)에서 수행된다. 단계(502)에서 시작하여, 선택된 비트라인들은 프리챠지된다. 검증 및 프로그래밍이 각각의 시간에서 홀수 비트라인들 및 짹수 비트라인들에 대하여 수행되는 홀수-짜수 아키텍처에서, 단계(502)의 프리챠지시키는 단계는 홀수 비트라인들 또는 짹수 비트라인들을 프리챠지시키는 단계를 포함할 수 있다. 대안적으로, 몇몇 아키텍처들은 단계(502)가 메모리 셀들의 선택된 블록의 각 비트라인의 도전을 포함하도록 모든 비트라인 시스템을 이용할 것이다. 비트라인들을 미리 결정된 레벨로 프리챠지시킨 후, 단계(504)에서 판독 패스 전압( $V_{read}$ )이 각 선택되지 않은 워드라인에 인가된다. 단계(504)는 선택된 워드라인에 연결된 메모리 셀들만이 검증되도록 검증 프로세스 동안에 각 선택되지 않은 메모리 셀의 도통을 보장한다. 단계(506)에서, 비정밀 프로그램 검증 전압이 선택된 워드라인에 인가된다. 단계(506)는 프로그램될 메모리 디바이스의 상태들의 수에 따라  $V_{vA1}$ ,  $V_{vB1}$  또는  $V_{vC1}$ 과 같은 비정밀 검증 레벨을 인가하는 단계를 포함할 수 있다. 단계(510)에서, 드레인측 선택 게이트는 SGD 상에 양 전압을 인가함으로써 개방(즉, 턴온)된다. 드레인측 선택 게이트가 개방되면, 선택된 비트라인들은 선택된 워드라인에 연결된 그 비트라인 상에 메모리 셀의 프로그램된 상태에 따라 방전을 허용하기 위하여 선택된 비트라인들의 NAND 스트링들에 연결된다. 미리 결정된 양의 시간 이후, 단계(510)에서, 선택된 비트라인들의 전압이 감지된다. 단계(510)는 메모리 디바이스에 대한 비정밀 레벨 감지를 나타낸다. 각 선택된 비트라인에 대한 비트라인 전압들을 감지한 후에, 단계(512)에서 비트라인 전압들이 중간 기준 전위( $V_{sense1}$ )와 비교된다. 단계(514)에서, 선택된 워드라인에는 검증되는 상태 또는 상태들에 따라  $V_{vA2}$ ,  $V_{vB2}$  또는  $V_{vC2}$ 와 같은 최종 검증 전압이 제공된다. 단계(516)에서, 각 선택된 비트라인의 전압이 감지된다. 단계(516)의 감지는 최종 또는 정밀 레벨 감지를 나타낸다. 단계(518)에서, 감지된 비트라인 전압들은 최종 기준 전위( $V_{sense2}$ )와 비교된다.

[0083] 단계(520)에서, 각 선택된 비트라인에 대한 감지 증폭기는 단계(518)의 비교 결과들을 이용하여 감지된 비트라인 전압( $V_{BL}$ )이 중간 기준 전위( $V_{sense1}$ ) 보다 큰지를 결정한다. 만약 감지된 비트라인 전압이, 메모리 셀의 임계 전압이 비정밀 검증 레벨에 도달하지 않았다는 것을 나타내는 중간 참조 레벨보다 작으면, 메모리 셀은 프로그래밍 프로세스의 다음 반복을 위한 단계(522)에서 풀 프로그래밍이 가능해진다. 단계(522)는 다음 프로그래밍 펄스 동안에  $V_{enable}$  전압(예를 들어, 접지)을 이와 같은 메모리 셀의 비트라인에 인가하는 단계를 포함한다. 만약 단계(520)에서 비트라인 전압이  $V_{sense1}$  보다 크다고 결정되었다면, 프로세스는 단계(524)에서 계속된다. 단계(516)에서 정밀 레벨 감지로부터 감지된 비트라인 전압이 최종 기준 전위( $V_{sense2}$ )와 비교된다. 만약 비트라인에 대한 감지 증폭기가 비트라인 전압이 최종 기준 전위( $V_{sense2}$ ) 보다 작다고 결정하면, 다음 프로그래밍 반복을 위하여 단계(526)에서 중간 전압( $V_s$ )이 메모리 셀에 대한 비트라인에 인가된다. 만약 감지 증폭기가 정밀 레벨 감지 동안의 비트라인 전압이 최종 기준 전위( $V_{sense2}$ ) 보다 크다고 결정하면, 감지 증폭기는 다음 프로그램 반복을 위하여 단계(528)에서  $V_{inhibit}$ 가 비트라인에 인가되게 한다.

[0084] 도 19의 단계들(502 내지 528)은 메모리 디바이스의 전위 상태들의 수에 따라 수행될 필요가 있는 검증 동작들의 수에 대해 반복될 수 있다. 2비트의 데이터를 저장하는 네 개의 상태 메모리 디바이스에서 단계(362)의 검증은 도 19의 방법의 세 번의 반복을 포함할 수 있다. 비정밀 및 정밀 검증 동작들은 상태(A) 검증 레벨들에서 한번, 상태(B) 검증 레벨들에서 한번 및 상태(C) 검증 레벨들에서 한번 수행될 수 있다. 특정 상태의 검증 레벨들에서 감지의 결과들은 현재 검증되는 상태와는 다른 상태로 프로그램되는 선택된 비트라인들에 대해서는 무시될 수 있다는 점이 주목된다.

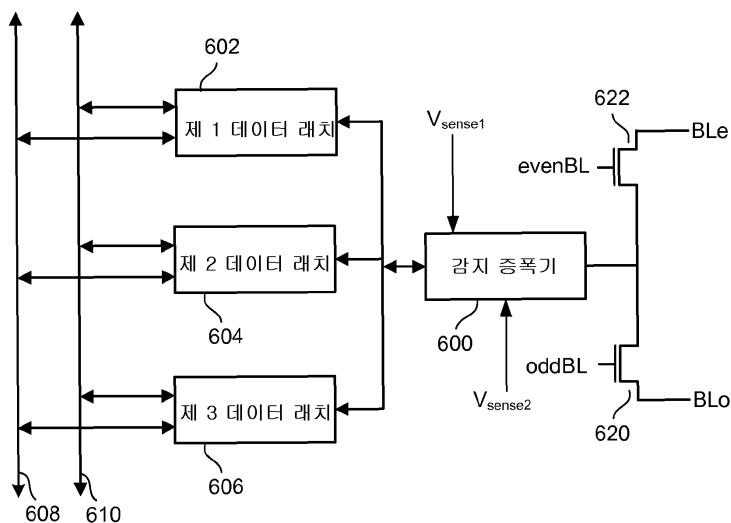

[0085] 도 20은 감지 증폭기를 포함하는 도 8의 컬럼 제어 회로(304)의 일부를 나타낸다. 비트라인들(예를 들어, BLo 및 BLo)의 각 쌍은 감지 증폭기(600)에 연결된다. 감지 증폭기는 3개의 데이터 래치들(제 1 데이터 래치(602),

제 2 데이터 래치(604) 및 제 3 데이터 래치(606))에 연결된다. 세 개의 데이터 래치들 각각은 1 비트 데이터를 저장할 수 있다. 감지 증폭기는 판독 또는 검증 동작들 동안에 선택된 비트라인의 전위 레벨을 감지하고, 감지된 데이터를 바이너리 방식으로 저장하고, 프로그램 동작 동안에 비트라인 전압을 제어한다. 감지 증폭기는 "evenBL" 및 "oddBL"의 신호들 중 하나를 선택함으로써, 선택된 비트라인에 선택적으로 연결된다. 데이터 래치들(602, 604 및 606)은 판독 데이터를 출력하고 프로그램 데이터를 저장하기 위해 I/O 라인들(608)에 연결된다. I/O 라인들(608)은 도 8의 데이터 입력/출력 버퍼(312)에 연결된다. 데이터 래치들(602, 604 및 606)은 또한 상태 정보를 수신 및 송신하기 위하여 상태 라인(들)(610)에 연결된다. 일 실시예에서, 비트라인들의 각 쌍(짝수 및 홀수)에 대한 제 1 데이터 래치(602), 제 2 데이터 래치(604) 및 제 3 데이터 래치(606)가 있다. 판독 데이터 및 프로그램 데이터를 저장하는 것에 외에, 데이터 래치들은 비정밀 검증 레벨들 및 최종 검증 레벨들을 포함하는 그 목표 상태에 관하여 저장 요소의 감지된 상태에 따라 비트라인에 인에이블 전압, 금지 전압 또는 중간 전압을 제공하기 위하여 감지의 결과들을 저장할 수 있다. 2 비트의 데이터를 저장하는 일 실시예에서, 두 개의 데이터 래치들이 메모리 셀에 프로그램될 데이터 및 셀이 현재 정밀 프로그래밍 모드 또는 비정밀 프로그래밍 모드에 있는지의 표시를 저장하는데 사용되는 나머지 데이터 래치를 저장하는데 사용될 수 있다. 감지 증폭기(600)는 비정밀 레벨 검증 동작( $V_{sense1}$ ) 및 정밀 레벨 검증 동작( $V_{sense2}$ )에 대한 비교를 동안에 사용될 기준 전위의 상이한 값들을 수신할 수 있다. 적절한 비교 레벨이 남은 데이터 래치에 저장된 데이터에 근거하여 선택될 수 있다.

[0086]

본 발명에 대한 전술한 상세한 설명은 본 발명을 묘사하고 자세히 설명하기 위해 제공된 것이다. 이것은 본 발명을 속속들이 규명하거나 본 발명을 정확하게 개시된 형태로 한정하는 것은 아니다. 상기 교시에 비추어 많은 수정과 변용이 가능할 것이다. 여기서 설명된 실시예는 본 발명의 원리와 본 발명의 실용적인 적용을 가장 잘 설명하기 위해서 선택된 것들이며, 이는 당업자에 의해 본 발명을 생각할 수 있는 특정한 사용예에 적합한 다양한 실시예와 다양한 수정예로서 최상으로 활용할 수 있도록 설명하기 위해서 선택된 것들이다. 본 발명의 범위는 본 명세서에 첨부된 청구항에 의해 정의될 것이다.

### 부호의 설명

[0087]

302: 메모리 셀 어레이

304: 컬럼 제어 회로

306: 로우 제어 회로

308: p-웰 제어 회로

310: c-소스 제어 회로

312: 데이터 I/O 버퍼

314: 명령 회로

315: 제어 회로

316: 상태 머신

318: 컨트롤러

## 도면

## 도면1

## 도면2

## 도면3a

## 도면3b

## 도면3c

## 도면4a

## 도면4b

## 도면4c

## 도면5a

## 도면5b

## 도면5c

## 도면6

## 도면7

도면8

도면9

도면10

## 도면11

## 도면12

도면13

도면14a

도면14b

### 도면 14c

### 도면15

## 도면16

작은 S-팩터를 갖는 메모리 디바이스

## 도면17

S-팩터를 갖는 메모리 디바이스

## 도면18

## 도면19

## 도면20