(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7134100号

(P7134100)

(45)発行日 令和4年9月9日(2022.9.9)

(24)登録日 令和4年9月1日(2022.9.1)

(51)国際特許分類

|         |                 |         |       |         |

|---------|-----------------|---------|-------|---------|

| G 0 6 F | 9/312 (2006.01) | G 0 6 F | 9/312 | L       |

| G 0 6 F | 9/38 (2006.01)  | G 0 6 F | 9/38  | 3 7 0 A |

| G 0 6 F | 9/34 (2006.01)  | G 0 6 F | 9/34  | 3 5 0 A |

| G 0 6 F | 12/00 (2006.01) | G 0 6 F | 12/00 | 5 6 0 B |

請求項の数 5 (全12頁)

(21)出願番号 特願2018-566347(P2018-566347)

(86)(22)出願日 平成29年6月6日(2017.6.6)

(65)公表番号 特表2019-525294(P2019-525294)

A)

(43)公表日 令和1年9月5日(2019.9.5)

(86)国際出願番号 PCT/US2017/036041

(87)国際公開番号 WO2017/222798

(87)国際公開日 平成29年12月28日(2017.12.28)

審査請求日 令和2年5月18日(2020.5.18)

(31)優先権主張番号 15/192,992

(32)優先日 平成28年6月24日(2016.6.24)

(33)優先権主張国・地域又は機関

米国(US)

前置審査

(73)特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 9 2 1

2 1 サン デイエゴ モアハウス ドライ

ブ 5 7 7 5

(74)代理人 100108453

弁理士 村山 靖彦

100163522

弁理士 黒田 晋平

(72)発明者 エリック・ウェイン・マハリン

アメリカ合衆国・カリフォルニア・9 2

1 2 1 - 1 7 1 4 ・サン・ディエゴ・モ

アハウス・ドライヴ・5 7 7 5 ・クアル

コム・インコーポレイテッド

ジャクブ・パワル・ゴラブ

最終頁に続く

(54)【発明の名称】 SIMDの集中およびコピー動作を実行するための方法および装置

## (57)【特許請求の範囲】

## 【請求項1】

メモリ動作を行う方法であって、

プロセッサによって、メモリの2つ以上のソースアドレスおよび対応する2つ以上の宛先アドレスをトランザクション入力バッファに与えるステップであって、

前記2つ以上のソースアドレスが、前記メモリにおいて独立し、不連続であり、

前記2つ以上の宛先アドレスが、前記メモリにおいて独立し、不連続である、ステップと、

前記トランザクション入力バッファによって、前記2つ以上のソースアドレスおよび前記対応する2つ以上の宛先アドレスをトランザクションシーケンサに供給するステップと、

前記プロセッサ内のレジスタへの中間コピーなしで、前記メモリ内で前記2つ以上のソースアドレスから前記対応する2つ以上の宛先アドレスに2つ以上のデータ要素をコピーするための、前記トランザクションシーケンサによって供給された2つ以上の命令を、集中動作および分散動作の組合せを使用して実行するステップと

を含む、方法。

## 【請求項2】

前記メモリ内で前記2つ以上のソースアドレスから前記対応する2つ以上の宛先アドレスに各データ要素を前記コピーすることが、单一命令複数データ(SIMD)コピー命令を実行することを含む、請求項1に記載の方法。

## 【請求項3】

前記プロセッサによる指示なしで前記SIMDコピー命令を実行するステップを含む、請求項2に記載の方法。

【請求項4】

装置であって、

メモリの2つ以上のソースアドレスおよび対応する2つ以上の宛先アドレスをトランザクション入力バッファに与えるように構成されたプロセッサであって、

前記2つ以上のソースアドレスが、前記メモリにおいて独立し、不連続であり、

前記2つ以上の宛先アドレスが、前記メモリにおいて独立し、不連続であり、

前記トランザクション入力バッファが、前記2つ以上のソースアドレスおよび前記対応する2つ以上の宛先アドレスをトランザクションシーケンサに供給するように構成される、プロセッサと、

前記プロセッサ内のレジスタへの中間コピーなしで、前記メモリ内で前記2つ以上のソースアドレスから前記対応する2つ以上の宛先アドレスに2つ以上のデータ要素を、集中動作および分散動作の組合せを使用してコピーするように構成された論理手段とを含む、装置。

【請求項5】

前記プロセッサによる指示なしで、前記2つ以上のソースアドレスから前記対応する2つ以上の宛先アドレスに前記2つ以上のデータ要素をコピーするように構成された論理手段を含む、請求項4に記載の装置。

【発明の詳細な説明】

【技術分野】

【0001】

開示する態様は、プロセッサ命令およびその効率的な実施を対象とする。より詳細には、例示的な態様は、メモリコピー、分散(scatter)、集中(gather)、およびそれらの組合せに関係する命令などの、複数のデータ要素を伴う効率的なメモリ命令に関する。

【背景技術】

【0002】

単一命令複数データ(SIMD)命令が、データ並列処理を利用するための処理システムにおいて使用される場合がある。データ並列処理は、たとえば、同じまたは共通のタスクが、データベクトルの2つ以上のデータ要素に対して実行されなければならないとき存在する。複数の命令を使用するのではなく、対応する複数のSIMDレーン内の複数のデータ要素上で実行されるべき同じ命令を規定する単一のSIMD命令を使用することによって、2つ以上のデータ要素に対して、共通のタスクを並列に実行することができる。SIMD命令は、算術演算、データ移動動作、メモリ動作などの様々な動作に使用される場合がある。メモリ動作に関しては、「分散」および「集中」が、ある場所から別の場所にデータ要素をコピーするためのよく知られている動作である。データ要素は、メモリ(たとえば、メインメモリまたはハードドライブ)にあってもよく、動作において指定されるレジスタは、プロセッサまたはシステムオンチップ(SoC)上にあってもよい。

【0003】

従来のロード命令は、データ要素をメモリ位置から、たとえばプロセッサにあるスカラ-宛先レジスタに読み出すために使用される場合があるが、「集中」命令は、複数のデータ要素を、たとえばプロセッサにあるベクトル宛先レジスタにロードするために使用される。複数のデータ要素の各々が、独立した、または直交するソースアドレス(メモリにおいて不連続である場合がある)を有し、これは、集中命令のSIMD実装を困難にする。いくつかの実装形態は、ベクトル宛先レジスタが完了するまで、各データ要素をベクトル宛先レジスタ内のそのそれぞれの位置に連続的にロードするために、複数のロード命令にわたって集中命令を実行する場合がある。しかしながら、このようなシリアル化は、パフォーマンスの劣化につながり、各コンポーネントロード命令は、各データ要素がどこから供給されるかに応じて変動するレイテンシを有する場合がある(たとえば、ソースアドレスは、キャッシュでヒットするものもあれば、しないものもある、ソースアドレスが異なればデー

10

20

30

40

50

タ依存性が異なる場合があるなど)。コンポーネントロード命令が、ベクトル宛先レジスタを順次に(in-order)更新するように実施される場合、ソフトウェアにおいて更新をパイプライン化すること、またはアウトオブオーダー処理機構を使用して、この変動するレイテンシの大部分を隠すことが可能ではない場合がある。ベクトル宛先レジスタのアウトオブオーダー更新が可能である実装のためには、追加のレジスタ(たとえば、一時的記憶用)、個々の更新のためのデータ要素ごとのキャッシング機構、ならびに他の関係するソフトウェアおよび/またはハードウェアサポートを招く場合がある。このように、集中動作の従来の実装形態は非効率的であり、大きなレイテンシおよび追加のハードウェアを伴う場合がある。

#### 【0004】

10

分散動作は、上述の集中動作の相対物と見なされてもよく、たとえばプロセッサにあるソースベクトルレジスタからのデータ要素が、不連続である場合がある複数の宛先メモリ位置に記憶される場合がある。いくつかのコードシーケンスまたはプログラムは、複数のデータ要素が、独立したまたは直交するソース位置(メモリにおいて不連続である場合がある)から読み取られ、独立したまたは直交する宛先位置(メモリにおいて不連続である場合がある)にコピーされるまたは書き込まれる動作を伴う場合がある。そのような動作は、複数のデータ要素に対する複数のコピー動作と見なされてもよい。したがって、メモリ内で直交するソース位置から直交する宛先位置への複数のデータ要素のSIMDコピー挙動を実装するために、そのような動作に対してSIMD処理を使用することが望ましい。

#### 【0005】

20

理論上、そのような機能は、メモリ内の複数のソース位置から、プロセッサにある集中宛先ベクトルレジスタへの、複数のデータ要素のSIMD集中、次いで集中宛先ベクトルレジスタからメモリ内の複数の宛先位置へのデータ要素のSIMD分散を実行することにより実現され得るが、そのような機能の実装は、実践的または実行可能ではない場合がある。これは、集中宛先ベクトルレジスタが完了するのを待つことが、上記で説明した、SIMD集中動作の従来の実装の非効率性を発生させるからである。SIMD分散が進行可能になる前に、集中宛先ベクトルレジスタがまず完了されるのを待たずに、SIMDコピーが実施された場合、SIMD集中のコンポーネントロードと、SIMD分散動作のコンポーネントストアとの間の同期もまた困難である。さらに、SIMDコピーを実行するためにSIMD分散に続いてSIMD集中を実施することは、メモリ内のソース位置から、プロセッサ内の集中宛先ベクトルレジスタを中間着地点として使用して、再びメモリ内の宛先位置へと、多数のデータ要素を転送することを伴う場合がある。諒解され得るように、メモリとプロセッサとの間で往復するそのような大きなデータ転送は、電力消費量およびSIMDコピーのレイテンシを増加させる。

30

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0006】

したがって、従来の実装形態の上述の欠点を回避しながら、SIMD処理の利点を活用するため、上記で説明したメモリ動作の改善された実装形態の必要がある。

40

#### 【課題を解決するための手段】

#### 【0007】

本発明の例示的な実装形態は、効率的なメモリ動作のためのシステムおよび方法を対象とする。単一命令複数データ(SIMD)集中動作が、メモリ内の複数の直交する位置から複数のデータ要素を受け取るまたは集中させるために、メモリ内またはメモリの極近傍にある集中結果バッファとともに実装され、集中結果バッファが完了すると、集中されたデータがプロセッサレジスタに転送される。SIMDコピー動作が、プロセッサレジスタへの中間コピーなしで、メモリ内で複数の直交するソースアドレスから対応する複数の宛先アドレスに複数のデータ要素をコピーするための2つ以上の命令を実行することによって行われる。このように、メモリ動作は、プロセッサによる指示なしで、バックグラウンドモードで行われる。

50

## 【0008】

たとえば、例示的な態様は、メモリ動作を行う方法を対象とし、この方法は、プロセッサによってメモリの2つ以上のソースアドレスを与えるステップと、メモリ内の2つ以上のソースアドレスから集中結果バッファに2つ以上のデータ要素をコピーするステップと、单一命令複数データ(SIMD)ロード動作を使用して、集中結果バッファからプロセッサ内のベクトルレジスタに2つ以上のデータ要素をロードするステップとを含む。

## 【0009】

別の例示的な態様は、メモリ動作を行う方法を対象とし、この方法は、プロセッサによってメモリの2つ以上のソースアドレスおよび対応する2つ以上の宛先アドレスを与えるステップと、プロセッサ内のレジスタへの中間コピーなしで、メモリ内で2つ以上のソースアドレスから対応する2つ以上の宛先アドレスに2つ以上のデータ要素をコピーするための2つ以上の命令を実行するステップとを含む。

10

## 【0010】

別の例示的な態様は、メモリの2つ以上のソースアドレスを与えるように構成されたプロセッサと、メモリ内の2つ以上のソースアドレスからコピーされた2つ以上のデータ要素を受け取るように構成された集中結果バッファと、プロセッサによって実行される单一命令複数データ(SIMD)ロード動作に基づいて、集中結果バッファからプロセッサ内のベクトルレジスタに2つ以上のデータ要素をロードするように構成された論理とを備える装置を対象とする。

## 【0011】

また別の例示的な態様は、メモリの2つ以上のソースアドレスおよび対応する2つ以上の宛先アドレスを与えるように構成されたプロセッサと、プロセッサ内のレジスタへの中間コピーなしで、メモリ内で2つ以上のソースアドレスから対応する2つ以上の宛先アドレスに2つ以上のデータ要素をコピーするように構成された論理とを備える装置を対象とする。

20

## 【図面の簡単な説明】

## 【0012】

添付の図面は、本発明の実施形態の説明を補助するために提供されたものであり、単に実施形態を図解するために提供されたものにすぎず、本発明を制限することは意図されていない。

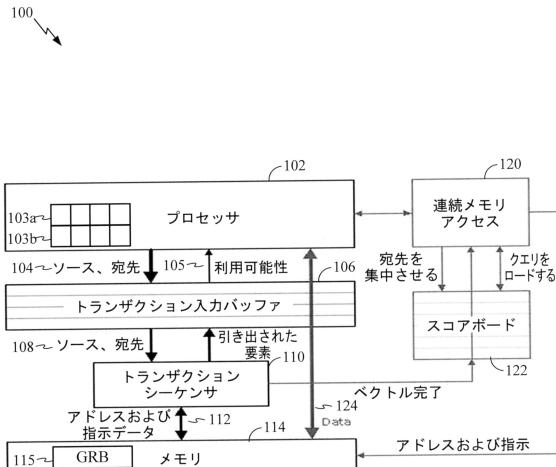

## 【図1】本開示の例示的な態様により構成された処理システムを示す図である。

30

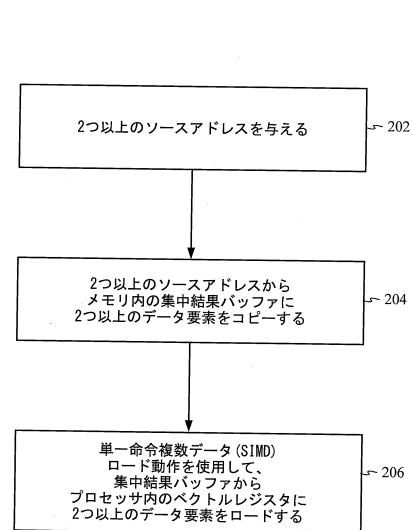

【図2】本開示の例示的な態様による、例示的なメモリ動作に関するプロセスを示す図である。

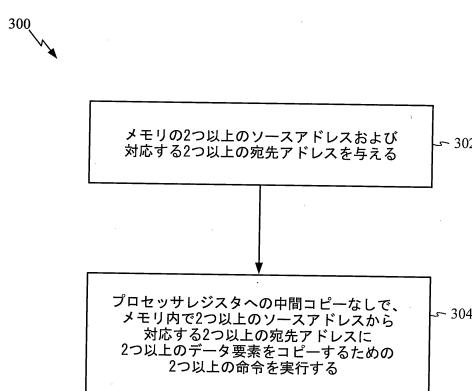

【図3】本開示の例示的な態様による、例示的なメモリ動作に関するプロセスを示す図である。

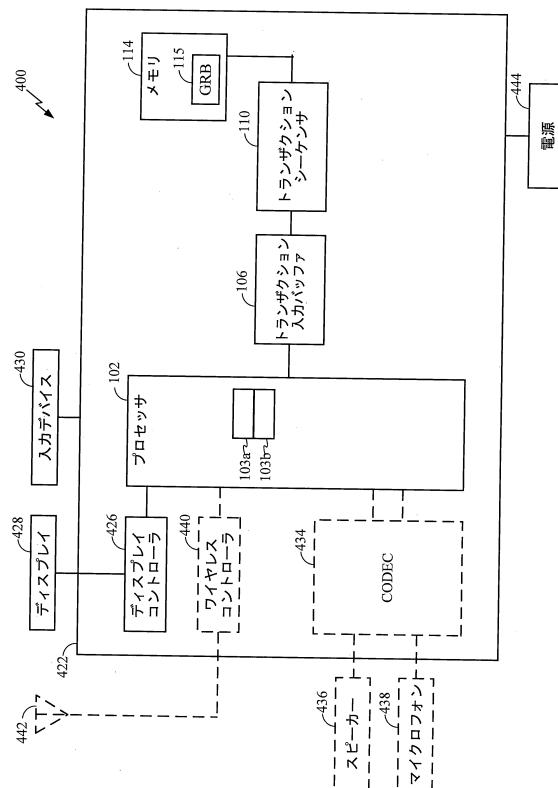

【図4】本開示の態様が有利に使用される場合がある例示的なコンピューティングデバイス400を示す図である。

## 【発明を実施するための形態】

## 【0013】

本発明の具体的な実施形態を対象とする後続の記述および関係する図面において、本発明の態様が開示される。本発明の範囲を逸脱することなく、代替実施形態が考案されてもよい。加えて、本発明のよく知られている要素については、本発明の関連する詳細を不明瞭にしないように、詳細には説明せず、または省略される。

40

## 【0014】

「例示的」という語は、本明細書では「例、事例、または例示として機能すること」を意味するために使用される。「例示的」として本明細書で説明するいかなる実施形態も、他の実施形態よりも好ましい、または有利であると必ずしも解釈されるべきでない。同様に、「本発明の実施形態」という用語は、本発明のすべての実施形態が、説明する特徴、利点、または動作モードを含むことを必要としない。

## 【0015】

本明細書において使用される用語は、特定の実施形態を説明するためのものにすぎず、

50

本発明の実施形態を限定することを意図しない。本明細書で使用される単数形「a」、「a n」、および「the」は、文脈が別段に明確に示さない限り、複数形も含むものとする。本明細書で使用される場合、「含む/備える(comprises)」、「含む/備える(comprising)」、「含む/includes)」、および/または「含む(including)」という用語は、述べられた特徴、整数、ステップ、動作、要素、および/または構成要素の存在を指定するが、1つまたは複数の他の特徴、整数、ステップ、動作、要素、構成要素、および/またはそれらのグループの存在もしくは追加を排除するものではないことをさらに理解されたい。

#### 【 0 0 1 6 】

さらに、多くの実施形態については、たとえば、コンピューティングデバイスの要素によって実行されるアクションのシーケンスの観点から説明する。本明細書に記載する様々なアクションは、特定の回路(たとえば、特定用途向け集積回路(ASIC))によって、1つまたは複数のプロセッサによって実行されているプログラム命令によって、または両方の組合せによって行われることが可能であることは認識されよう。さらに、本明細書に記載するこれらの一連のアクションは、実行されると関連するプロセッサに本明細書に記載する機能を行わせる、対応するコンピュータ命令のセットを記憶した任意の形態のコンピュータ可読記憶媒体内で完全に具体化されると見なすことができる。このように、本発明の様々な態様は、いくつかの異なる形態で具体化されることが可能であり、そのすべてが請求される主題の範囲内であると考えられている。加えて、本明細書で説明する実施形態ごとに、任意のそのような実施形態の対応する形式については、本明細書では、たとえば、説明した動作を実行する「ように構成された論理」として説明することができる。

#### 【 0 0 1 7 】

本開示の例示的な態様では、SIMD集中動作が、動作を2つのサブ動作、すなわち、(たとえば、不連続である場合もある、メモリ内の独立したまたは直交する位置から)複数のデータ要素を集中させる第1のサブ動作と、集中結果バッファから、たとえばプロセッサにあるSIMDレジスタにロードする第2のサブ動作とに分割することによって、実装されてもよい。例示的なSIMD集中動作は、ソフトウェア実装(たとえば、コンパイラ)によって2つのサブ動作に分けられてもよく、2つのサブ動作は、レイテンシを最小限に抑えるために(たとえば、複数のデータ要素をアウトオブオーダー(out-of-order)に集中結果バッファに集中させるために、第1のサブ動作に対してソフトウェアパイプライン化機構を使用して)パイプライン化されてもよい。集中結果バッファは、メモリ内またはメモリの近傍にあってもよく、プロセッサにある従来の集中宛先ベクトルレジスタと区別される。したがって、集中結果バッファには要素ごとのトラッキング機構が必要ではない。さらに、第2のサブ動作は、集中結果バッファから、複数のデータ要素を収容することができる(たとえば、プロセッサにある)宛先レジスタに、複数のデータ要素をロードしてもよい。データ要素は、個々に宛先レジスタからアクセス可能であってもよく、集中結果バッファでの順序に基づいて順序付けられてもよく、これは、集中結果バッファから宛先レジスタへの複数のデータ要素のロード動作を簡単にする(たとえば、ロード動作は、複数のデータ要素の各々の位置を指定するベクトルロードではなく、複数のデータ要素のスカラーロードに似ている場合がある)。したがって、例示的な態様では、直交するソース位置からの複数のデータ要素は、メモリにある集中結果バッファの使用によって、プロセッサ内の宛先レジスタに効率的に集中させることができる。

#### 【 0 0 1 8 】

本開示の別の例示的な態様では、メモリ内の直交するソース位置からのデータ要素を、メモリ内の直交する宛先位置に効率的にコピーすることができる。たとえば、SIMDコピー動作は、集中動作および分散動作の組合せを使用して実装されてもよく、組合せは、メモリ内で効率的に実行されてもよい。この点について、メモリ内でSIMDコピーを実行することは、中間記憶のためにプロセッサにあるレジスタ(プロセッサにある従来の集中宛先ベクトルレジスタなど)を使用せずに動作が行われることを伝えることになっている。たとえば、メモリ内で集中および分散動作の組合せを実行することは、メモリとプロセッサとの間のデータ要素の転送を回避しながら、メモリの極近傍にあるネットワークまたはシ-

10

20

30

40

50

ケンサの使用を伴うことができる。複数のデータ要素に対する要素ごとのアドレッシングを有する例示的なSIMDコピー命令は、複数のデータ要素のコピー元の集中またはソースアドレスのリスト、および複数のデータ要素が書き込まれることになる分散または宛先アドレスの対応するリストを指定してもよい。これらのリストから、複数のコピー動作が、独立したまたは直交する方法で行われて、複数のデータ要素の各々を、そのそれぞれのソースアドレスからそれのそれぞれの宛先アドレスにコピーしてもよい。例示的な態様では、複数のコピー動作の各々が、完了されるために中間ベクトル(たとえば、集中ベクトル)を必要とせずに完了可能にされ、したがって、リラックスメモリオーダリング(relaxed memory ordering)および複数のコピー動作のアウトオブオーダーの完了が可能となり得る。

10

#### 【 0 0 1 9 】

次に図1を参照しながら、上述の例示的な態様に従って構成された例示的な処理システム100について説明する。図示のように、処理システム100は、実行パイプラインを実装するように構成されてもよいプロセッサ102を含んでもよい。いくつかの態様では、プロセッサ102の実行パイプラインは、ベクトル命令、より詳細には、SIMD処理をサポートしてもよい。例示的な態様の説明を容易にするために、プロセッサ102には2つのレジスタ103aおよび103bが示されている。これらのレジスタ103a～bは、レジスタファイル(図示せず)に属してもよく、いくつかの態様では、ベクトルレジスタであってもよい。したがって、レジスタ103aは、ソースレジスタであってもよく、レジスタ103bは、以下で説明する例示的な事例ではベクトルレジスタであってもよい。たとえば、ソースベクトルレジスタ103aのデータ要素が、従来の分散動作において指定される場合がある。宛先ベクトルレジスタ103bが、以下で説明するように例示的なSIMD集中動作において使用される場合がある。

20

#### 【 0 0 2 0 】

例示的なSIMD動作では、トランザクション入力バッファ106が、バス104でソースおよび宛先オペランドのためのアドレスとともに、プロセッサ102から命令を受け取ってもよい。バス104上のソースおよび宛先アドレスは、(たとえば、宛先ベクトルレジスタ103bへの)例示的なSIMD集中動作、または前述し、さらに以下で図2および図3を参照して説明する例示的なSIMDコピー動作に対応してもよい。トランザクション入力バッファ106は、より多くの命令(または関係するオペランド)がプロセッサ102から受け取り可能であるかどうかを伝えるために、利用可能性105として示される信号をアサートすることによって、またはキューが一杯である場合、利用可能性105をアサート解除することによって、フィードバックをキューイングし、伝えるためのキューイング機構を実装してもよい。

30

#### 【 0 0 2 1 】

トランザクション入力バッファ106にキューイングされる命令は、バス108でトランザクションシーケンサ110に転送されてもよい。例示的な態様では、トランザクションシーケンサ110は、動作および調整可能な設定に基づいて、バス108からの命令をシリアル化または並列化するように構成されてもよい。メモリ動作の場合、ソースおよび/または宛先アドレスは、(それぞれの制御とともに)バス112でメモリ114に与えられてもよい。バス112は、データをメモリ114から戻すことができる2方向バスとして示される(データの方向の制御が、データ転送がメモリ114からのものであるか、それともメモリ114へのものであるかを示してもよい)。様々な代替実装形態では、まとめてバス112として示すアドレスバス、制御バス、およびデータバスに対して、別個のワイヤが使用されてもよい。

40

#### 【 0 0 2 2 】

処理システム100はまた、連続メモリアクセス120およびスコアボード122として示されるブロックなどの処理要素を含むことができる。一例では、SIMD命令が、連続するメモリ位置からデータ要素を集中させることに関係する場合、SIMD命令は、連続するメモリ位置からプロセッサ102内のベクトルレジスタ(たとえば、レジスタ103b)にデータをロードするために従来のベクトル演算として実行することができ、このために、例示のトランザクションシーケンサ110は回避されてもよい。スコアボード122は、トランザクショ

50

ン入力バッファ106と同様に機能してもよく、したがって、キューイング機構を実装してもよい。スコアボード122が、連続するメモリ位置からのSIMDロードまたはSIMD集中などの従来のベクトル演算のためにメモリ114からデータを受け取る一様では、複数のデータ要素は、トランザクションシーケンサ110を介してスコアボード122に供給されてもよく、宛先ベクトルが完了すると、宛先ベクトルは、たとえばプロセッサ102のベクトルレジスタ103bにおいて更新されるようにプロセッサ102に供給されてもよい。連続メモリアクセス120およびスコアボード122などの従来の要素の動作は、それらがメモリ動作のために例示的なブロック、トランザクション入力バッファ106、およびトランザクションシーケンサ110と相互動作することができることを伝えるために示されている。

## 【0023】

10

図1～図2を合わせて参照しながら、次に、例示的なSIMD集中動作に関係するプロセス200について説明する。ブロック202に示すように、プロセッサ102が、たとえば集中命令または2つ以上のロード命令に基づいて、2つ以上のソースアドレスを与えることができる。コンパイラまたは他のソフトウェアが、SIMD集中動作を認識し、いくつかの態様では、例示的なSIMD集中動作のためにそれを分解してコンポーネントロード命令にしてもよい。2つ以上のソースアドレスは、直交し、または独立していてもよく、メモリ114内の不連続位置に関係してもよい。コンポーネントロード命令は、2つ以上のソースアドレスからの2つ以上のデータ要素がそこに集中されることになるプロセッサ102の連続するレジスタまたは宛先ベクトルレジスタ(たとえば、レジスタ103b)を指定してもよい。

## 【0024】

20

ブロック204において、プロセッサ102が、バス104および108で、2つ以上のソースアドレスをトランザクション入力バッファ106に、そこからトランザクションシーケンサ110に送ることによって、プロセッサ102が例示的なSIMD集中動作を実施することができる。トランザクションシーケンサ110は、並行して、または連続して、2つ以上のソースアドレスからメモリ114内に例示的に示す集中結果バッファ(たとえば、GRB115)に2つ以上のデータ要素をコピーするための2つ以上の命令を与えてよい。集中結果バッファ115は、メモリ114内に実装された循環バッファであってもよい。いくつかの態様では、集中結果バッファ115は、メモリ114の外に(たとえば、プロセッサ102よりもメモリ114の近傍に)あって、メモリ114と通信してもよい。いくつかの態様では、集中結果バッファ115は、任意の他の適切なストレージ構造であって、必ずしも循環バッファでなくてもよい。2つ以上のデータ要素の2つ以上のコピー動作は、2つ以上の異なるレイテンシを伴う場合がある。さらに、2つ以上のデータ要素の集中結果バッファ115への2つ以上のコピー動作は、バックグラウンドで、たとえば、プロセッサ102による指示なしでトランザクションシーケンサ110の指示の下で行われてもよい。したがって、プロセッサ102は、複数のコピー動作がバックグラウンドで実行されている間に、(たとえば、明示的に図示していないまたは複数の実行ユニットを利用して)他の動作を行ってもよい。

## 【0025】

30

ブロック206に示すように、集中結果バッファ115が完了すると、集中結果バッファ115からプロセッサ102内の、レジスタ103bなどのベクトルレジスタにデータ要素をロードするために、ロード命令が発行されてもよい。ロードは、2つ以上のデータ要素を集中結果バッファ115内の連続するメモリ位置からベクトルレジスタ103bにロードするためのSIMDロードに対応してもよい。ロード命令が発行される前に、集中結果バッファ115が完了しているかどうかを決定するために、いくつのコピー動作が行われたかを追跡するように、スコアボード122が利用される場合もある。いくつかの手法では、集中結果バッファ115からプロセッサ102内のベクトルレジスタ103bにデータ要素をロードする前に、集中結果バッファ115が完了していることを確実にするために、1つまたは複数の同期命令が、(たとえば、ソフトウェア制御によって)実行されてもよい。このようにして、集中結果バッファ115へのコピー動作のレイテンシをプロセッサ102から隠すことができ、ロード命令は、遅延を避ける厳密なタイミングで実行され得る。

## 【0026】

50

図1および図3を合わせて参照しながら、例示的なSIMDコピー動作に関するプロセス300について説明する。プロセス300のSIMDコピー動作は、従来のSIMD集中動作、それに続く従来のSIMD分散動作と同等の結果を得ることができる。しかしながら、例示的なSIMDコピー動作は、従来の方法でSIMD集中動作、それに続くSIMD分散動作を実施するよりも複雑性およびレイテンシの少ない例示的な態様で実施することができる。

#### 【0027】

たとえば、ブロック302を参照すると、プロセッサ102が、メモリ114の2つ以上のソースアドレスおよび対応する2つ以上の宛先アドレスを与えてよい。2つ以上のソースアドレスおよび/または2つ以上の宛先アドレスは、直交しまたは独立し、不連続であってもよい。たとえば、コンパイラが、プロセッサ102にソースおよび宛先アドレスを供給するために、従来の集中から分散への命令またはコードのシーケンスをコンポーネント命令に分解してもよい。再度、プロセッサ102は、2つ以上のソースアドレスおよび対応する2つ以上の宛先アドレスをトランザクション入力バッファ106に与えてよい。トランザクション入力バッファ106が、(上記の図2のプロセス200を参照して説明したように)2つ以上のソースアドレスおよび対応する2つ以上の宛先アドレスをトランザクションシーケンサ110に供給してもよい。トランザクションシーケンサ110は、ブロック304において以下の動作を行うためにメモリ114に命令を供給してもよい。

10

#### 【0028】

ブロック304において、2つ以上の命令は、プロセッサ102内のプロセッサレジスタヘの中間コピーなしで、メモリ内で2つ以上のソースアドレスから対応する2つ以上の宛先アドレスに2つ以上のデータ要素をコピーするために実行されてもよい。たとえば、トランザクションシーケンサ110などのネットワーク要素は、コピーするための2つ以上の命令の実行中にプロセッサ102にデータを転送することなく利用されてもよい。したがって、メモリ内で2つ以上のソースアドレスから対応する2つ以上の宛先アドレスに2つ以上のデータ要素をコピーすること(たとえば、メモリからメモリへのコピー動作)は、プロセッサ102による指示なしでバックグラウンドモードで、SIMDコピー命令を実行することを含んでもよい。このようにして、中間集中ベクトル結果を形成することが回避されてもよく、場合によっては、コピーするための2つ以上の命令の実行において、完全な集中ベクトルが十分に形成されなくてもよい。コピーするための2つ以上の命令の実行が完了すると、トランザクションシーケンサ110は、スコアボード122、および/またはプロセッサ102に、2つ以上のメモリからメモリへのコピー動作のステータスを完了として知らせてよい。

20

#### 【0029】

図4を参照すると、例示的な態様によるコンピューティングデバイス400の特定の例証的な態様のブロック図である。コンピューティングデバイス400は、図2～図3のそれぞれプロセス200および300による例示的なメモリ動作の実行をサポートし、実施するように構成可能であるプロセッサ102を含む。図4では、図1のプロセッサ102(レジスタ103a～bを含む)、トランザクション入力バッファ106、トランザクションシーケンサ110、およびメモリ114(集中結果バッファ115を含む)が明確に特定されているが、図1の残りの細部は、明快のためにこの図では省略されている。図示されていないが、1つまたは複数のキヤッシュまたは他のメモリ構造が、コンピューティングデバイス400に含まれる場合もある。

30

#### 【0030】

図4は、プロセッサ102およびディスプレイ428に結合されたディスプレイコントローラ426を示す。図4はまた、コンピューティングデバイス400の特定の実装形態に基づく、たとえばワイヤレス通信のための、オプションのブロックであってもよい、いくつかの構成要素を示す。したがって、コーダ/デコーダ(CODEC)434(たとえば、オーディオおよび/またはボイスCODEC)はオプションとすることができます、ある場合、プロセッサ102に結合され、オプションブロックのスピーカー436およびマイクロフォン438は、CODEC434に結合することができる。ワイヤレスコントローラ440(モデムを含んでもよい)もまた、オプションであって、ワイヤレスアンテナ442に結合されてもよい。特定の態様では、ブ

40

50

ロセッサ402、ディスプレイコントローラ426、メモリ432、CODEC434、およびワイヤレスコントローラ440は、システムインパッケージデバイスまたはシステムオンチップデバイス422に含まれる。

#### 【0031】

特定の態様では、入力デバイス430および電源444が、システムオンチップデバイス422に結合される。さらに、特定の態様では、図4に示すように、ディスプレイ428、入力デバイス430、スピーカー436、マイクロフォン438、ワイヤレスアンテナ442、および電源444は、システムオンチップデバイス422に対して外部にある。ただし、ディスプレイ428、入力デバイス430、スピーカー436、マイクロフォン438、ワイヤレスアンテナ442、および電源444の各々は、インターフェースまたはコントローラのような、システムオンチップデバイス422の構成要素に結合することができる。

10

#### 【0032】

図4は、ワイヤレス通信デバイスを示しているが、プロセッサ102およびメモリ114が、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、携帯情報端末(PDA)、固定位置データユニット、通信デバイス、サーバー、またはコンピュータに組み込まれる場合もあることに留意されたい。さらに、ワイヤレスデバイス400の少なくとも1つまたは複数の例示的な態様は、少なくとも1つの半導体ダイに組み込まれる場合がある。

#### 【0033】

情報および信号が、様々な異なる技術および技法のいずれかを使用して表される場合があることは、当業者には諒解されよう。たとえば、上記の説明全体にわたって言及されることがあるデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場もしくは磁性粒子、光場もしくは光学粒子、またはそれらの任意の組合せによって表される場合がある。

20

#### 【0034】

さらに、本明細書で開示する実施形態に関して説明する様々な例証的な論理ブロック、モジュール、回路、およびアルゴリズムステップが、電子ハードウェア、コンピュータソフトウェア、または両方の組合せとして実装されてもよいことは、当業者には諒解されよう。ハードウェアとソフトウェアのこの互換性を明確に示すために、上記では、様々な例証的な構成要素、ブロック、モジュール、回路、およびステップについて、全般的にこれらの機能の観点から説明した。そのような機能が、ハードウェアとして実現されるか、ソフトウェアとして実現されるかは、特定の適用例と、システム全体に課される設計制約によって決まる。当業者は、説明した機能を特定の適用例ごとに様々な方法で実装してもよいが、そのような実装形態の決定は、本発明の範囲からの逸脱を引き起こすものと解釈されるべきではない。

30

#### 【0035】

本明細書において開示される実施形態に関して説明した方法、シーケンス、および/またはアルゴリズムは、ハードウェアにおいて直接具現化される場合も、プロセッサによって実行されるソフトウェアモジュールにおいて具現化される場合も、あるいは2つの組合せにおいて具現化される場合もある。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ、EPROMメモリ、EEPROMメモリ、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野において知られている任意の他の形の記憶媒体内に存在してもよい。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り、記憶媒体に情報を書き込むことができるようプロセッサに結合される。代替として、記憶媒体は、プロセッサと一体化してもよい。

40

#### 【0036】

したがって、本発明の一実施形態は、分散および集中などの効率的なメモリコピー動作のための方法を具現化するコンピュータ可読媒体を含むことができる。したがって、本発明は、示された例に限定されず、本明細書で説明する機能を実施するためのあらゆる手段が本発明の実施形態に含まれる。

50

## 【0037】

前述の開示は本発明の例証的な実施形態を示すが、添付の特許請求の範囲によって定義される本発明の範囲を逸脱することなく、本明細書では様々な変更および修正を行うことが可能であることに留意されたい。本明細書で説明した本発明の実施形態による方法請求項の機能、ステップ、および/またはアクションは、いずれかの特定の順序で実施される必要はない。さらに、本発明の要素が単数形で説明される、または特許請求される場合があるが、単数形への限定が明示的に記載されていない限り、複数形が企図される。

## 【符号の説明】

## 【0038】

|     |                |    |

|-----|----------------|----|

| 100 | 処理システム         | 10 |

| 102 | プロセッサ          |    |

| 103 | レジスタ           |    |

| 104 | バス             |    |

| 106 | トランザクション入力バッファ |    |

| 108 | バス             |    |

| 110 | トランザクションシーケンサ  |    |

| 112 | バス             |    |

| 114 | メモリ            |    |

| 115 | 集中結果バッファ       |    |

| 120 | 連続メモリアクセス      | 20 |

| 122 | スコアボード         |    |

| 400 | コンピューティングデバイス  |    |

| 402 | プロセッサ          |    |

| 422 | システムオンチップデバイス  |    |

| 426 | ディスプレイコントローラ   |    |

| 428 | ディスプレイ         |    |

| 430 | 入力デバイス         |    |

| 432 | メモリ            |    |

| 434 | コーデック          |    |

| 436 | スピーカー          | 30 |

| 438 | マイクロフォン        |    |

| 440 | ワイヤレスコントローラ    |    |

| 442 | ワイヤレスアンテナ      |    |

| 444 | 電源             |    |

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

30

40

50

---

フロントページの続き

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775・クアルコム・インコーポレイテッド

(72)発明者 ルシアン・コドレスク

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775・クアルコム・インコーポレイテッド

審査官 漆原 孝治

(56)参考文献 特開2007-172609 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

G 06 F 9 / 312

G 06 F 9 / 38

G 06 F 9 / 34

G 06 F 12 / 00