(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4850602号

(P4850602)

(45) 発行日 平成24年1月11日(2012.1.11)

(24) 登録日 平成23年10月28日(2011.10.28)

(51) Int.Cl.

F 1

H04N 5/353 (2011.01)

H04N 5/374 (2011.01)H04N 5/335 530

H04N 5/335 740

請求項の数 8 (全 14 頁)

(21) 出願番号 特願2006-183848 (P2006-183848)

(22) 出願日 平成18年7月3日 (2006.7.3)

(65) 公開番号 特開2008-16977 (P2008-16977A)

(43) 公開日 平成20年1月24日 (2008.1.24)

審査請求日 平成21年7月3日 (2009.7.3)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(72) 発明者 大輪 寧司

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

最終頁に続く

(54) 【発明の名称】撮像装置及びその制御方法並びに撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

撮像面に複数の光電変換素子が配置された撮像部と、

前記撮像部を制御する制御部と、

を備え、

前記制御部は、

前記撮像面の第1の領域に配置された第1の光電変換素子群から、M(2以上の整数)ラインずつ画像信号を1ライン分の画像信号として前記撮像部から読み出す第1のモードと、前記撮像面の前記第1の領域よりも小さい第2の領域に配置された第2の光電変換素子群から、N(1以上M未満の整数)ラインずつ画像信号を1ライン分の画像信号として前記撮像部から読み出す第2のモードとを有し、

前記第2のモードにおける水平期間が、前記第1のモードにおける水平期間のN/Mとなるように制御することで、前記第1及び第2のモードにおいて各ラインのリセットタイミング及び読み出しタイミングが一定となるように制御し、

前記第1のモードにおける水平期間は、ある前記Mライン分の画像信号の読み出し開始から、次の前記Mライン分の画像信号の読み出し開始までの期間であり、

前記第2のモードにおける水平期間は、ある前記Nライン分の画像信号の読み出し開始から、次の前記Nライン分の画像信号の読み出し開始までの期間であることを特徴とする撮像装置。

## 【請求項 2】

10

20

前記制御部は、前記第2のモードにおける水平期間が前記第1のモードにおける水平期間のN/Mとなるように、前記第1モード及び前記第2モードのいずれか一方における前記水平期間に空期間を設けることを特徴とする請求項1に記載の撮像装置。

#### 【請求項3】

前記制御部は、前記第1のモードにより読み出して得られるライン数と前記第2のモードにより読み出して得られるライン数とが等しくなるように制御を行うことを特徴とする請求項1に記載の撮像装置。

#### 【請求項4】

前記第1のモードと前記第2のモードとの切り替えがなされる場合、切り替え前の読み出し期間中のリセット動作を切り替え後の読み出し領域に対して行うことを特徴とする請求項3に記載の撮像装置。 10

#### 【請求項5】

前記第1のモードにおいて、前記Mライン分の画像信号を加算することにより1ライン分の画像信号として撮像部から読み出すことを特徴とする請求項1乃至3のいずれか1項に記載の撮像装置。

#### 【請求項6】

前記第1のモードにおいて、前記Mライン分の画像信号のうちM-1ラインの画像信号を間引いて1ライン分の画像信号として撮像部から読み出すことを特徴とする請求項1乃至3のいずれか1項に記載の撮像装置。 20

#### 【請求項7】

光学系と、

請求項1乃至請求項6のいずれか1項に記載の撮像装置と、

を備えることを特徴とする撮像システム。

#### 【請求項8】

撮像面に複数の光電変換素子が配置された撮像部と、前記撮像部を制御する制御部とを備える撮像装置の制御方法であって、

前記撮像面の第1の領域に配置された第1の光電変換素子群から、M(2以上の整数)ラインずつ画像信号を1ライン分の画像信号として前記撮像部から読み出す第1のモードと、前記撮像面の前記第1の領域よりも小さい第2の領域に配置された第2の光電変換素子群から、N(1以上M未満の整数)ラインずつ画像信号を1ライン分の画像信号として前記撮像部から読み出す第2のモードとを有し、 30

前記第2のモードにおける水平期間が、前記第1のモードにおける水平期間のN/Mとなるように制御することで、前記第1及び第2のモードにおいて各ラインのリセットタイミング及び読み出しタイミングが一定となるように制御し、

前記第1のモードにおける水平期間は、ある前記Mライン分の画像信号の読み出し開始から、次の前記Mライン分の画像信号の読み出し開始までの期間であり、

前記第2のモードにおける水平期間は、ある前記Nライン分の画像信号の読み出し開始から、次の前記Nライン分の画像信号の読み出し開始までの期間であることを特徴とする撮像装置の制御方法。

#### 【発明の詳細な説明】

40

#### 【技術分野】

#### 【0001】

本発明は、光電変換素子を有する撮像装置に関し、特に、CMOSイメージセンサを用いる場合における電子ズームの高画質化に関する。

#### 【背景技術】

#### 【0002】

従来、固体撮像素子として、CCDイメージセンサ及びCMOSイメージセンサが広く用いられている。CCDイメージセンサでは、撮像面の画素内に配置された光電変換素子で光を信号電荷に変換し、その信号電荷を全画素から同時にCCDに読み出して転送し、転送された信号電荷を電気信号に変えて出力する。一方、CMOSイメージセンサでは、 50

撮像面の画素内に配置された光電変換素子で光を信号電荷に変換し、その信号電荷を画素ごとに増幅して出力する。CMOSイメージセンサは、任意の画素領域における光電変換素子の画像信号を選択的に読み出すこと（以下「部分読み出し」という。）ができる点で、全画素領域における光電変換素子の画像信号を同時に読み出すCCDイメージセンサにはない特徴を有する。

#### 【0003】

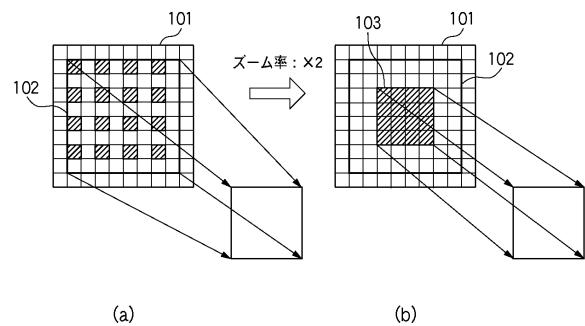

図1は、CMOSイメージセンサの上記の特徴を利用した電子ズーム動作の概念図である。図1(a)は通常モードにおける読み出しを示す図であり、図1(b)は2倍のズーム率のズームモードにおける読み出しを示す図である。図1(a)及び図1(b)において、撮像部101は、格子状に配置された複数の画素を有する。図1(a)及び図1(b)では、 $10 \times 10$ の画素が配置された撮像部を例示的に示したが、これに限定されず、任意の数の画素が配置された撮像部を用いることができる。

#### 【0004】

図1(a)に示すように、通常モードでは、 $8 \times 8$ 画素を表す太枠102の範囲内では、1画素置きに $4 \times 4$ 画素の信号を読み出す間引き率2の読みしが行われる。これに対し、ズームモードでは、 $8 \times 8$ 画素を表す太枠102内の中央部103に連続して配置された $4 \times 4$ 画素の信号を読み出す。この場合、間引き率1の読み出しを行い、中央部103を拡大して表示させることができる。ズームモードで読み出す画素数は、通常モードと同じであるため、信号処理により画素数を増加させる必要がない。このため、電子ズームにおける画質を高画質にすることができる。

【特許文献1】特開2005-94142号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0005】

しかしながら、CMOSイメージセンサで信号電荷を蓄積する場合、撮像面のライン毎に信号電荷の蓄積時間にずれが生じる。このライン毎の蓄積時間のずれによって、1ラインの読み出し時間がずれる。1ラインの読み出し時間、すなわち、ある1ラインの信号の読み出し開始から、次に読み出される1ラインの信号の読み出し開始までの期間は、以下の式1で表される。

#### 【0006】

$$1\text{ ラインの読み出し時間} = HBLK \times \dots + SKIP \times \dots + \text{水平画素数} \times \text{基準クロック時間} \quad \dots \quad (\text{式1})$$

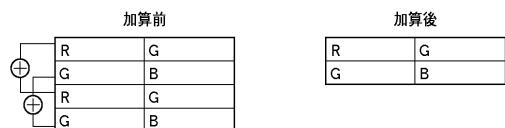

ここで、 $HBLK$ 、 $SKIP$ は垂直方向の加算方法に応じて決定される。 $HBLK$ は、水平プランキング期間を表す。 $SKIP$ は、間引きにより1ラインをスキップするのに必要な時間（スキップ時間）を表す。水平画素数×基準クロック時間は、図9及び図11に示す水平画素読み出し時間に対応する。式1に示すように、1ラインの読み出し時間は、水平プランキング期間、スキップ期間及び水平画素読み出し時間の3つの時間の合計で表される。一例として、垂直方向の2画素の加算平均を行う場合について、図2を参照して説明する。

#### 【0007】

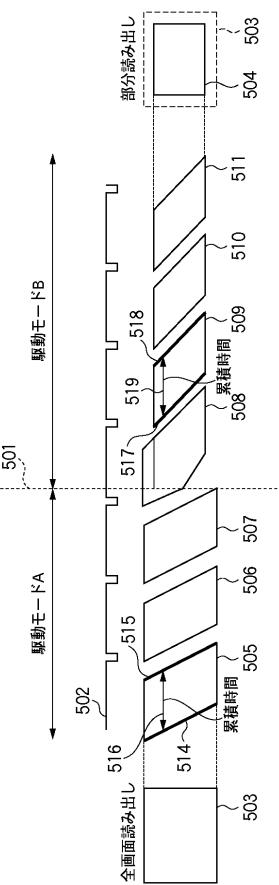

図2に示す場合では、 $HBLK$ は2であり、 $SKIP$ は1である。水平画素数だけ転送するのに必要な時間は、基準クロック時間に依存する。1ライン読み出し時間は、垂直方向の加算方法や駆動周波数などの駆動モードの変更により変化しうる。撮像面の上下の蓄積開始時間は、これらの駆動モードの変更により変動しうる。図3は、駆動モードが変更されたときのオーリングシャッタの動作を示す図である。図3では、1ラインの読み出し時間が駆動モードの変更前よりも長くなった場合を例示的に示す。図3に示す場合では、画面上下の蓄積時間差は、駆動モードの変更前よりも大きくなる。

#### 【0008】

次に、EVF（電子ビューファインダー）表示や動画録画などの動画処理において駆動モードが変更された場合の様子を図4に示す。なお、駆動モードを変更するタイミングは、読み出し終了後のVBLK（垂直プランク）期間中であるとする。

10

20

30

40

50

## 【0009】

図4の横軸は時間を表し、縦軸はCMOSイメージセンサにおける読み出し位置を示す。フレーム505～511は、各駆動におけるライン位置あたりの蓄積タイミングと蓄積時間を表している。図4では、時刻t1(501)までは駆動モードAで駆動し、時刻t1(501)で駆動モードBに切り替えた場合におけるフレーム505～511の蓄積時間を示す。502は垂直同期信号VDである。駆動モードAでは全画面読み出し503を行い、駆動モードBでは部分読み出し504を行う。駆動モードAのフレーム505では、リセットタイミング514から読み出しタイミング515までが蓄積時間516に対応する。同様に、駆動モードBのフレーム509では、リセットタイミング517から読み出しタイミング518までが蓄積時間519に対応する。駆動モードAにおけるフレーム506及び507並びに駆動モードBにおけるフレーム510及び511においても同様である。

10

## 【0010】

フレーム508におけるリセット開始時刻は、時刻t1より早いため、時刻t1以前の期間におけるリセットタイミングは駆動モードAと同じである。しかしながら、時刻t1以降は駆動モードBに切り替わるため、読み出しタイミングが駆動モードAとは異なる。その結果、駆動切り替え時のフレーム508では、切り替えの時刻t1を境に画面上下の蓄積時間に差が生じてしまう。

## 【0011】

本発明は、上記の課題に鑑みてなされたものであり、駆動モードにかかわらず撮像部における蓄積時間をほぼ一定に保つことを目的とする。

20

## 【課題を解決するための手段】

## 【0012】

本発明の第1の側面は、撮像装置に係り、撮像面に複数の光電変換素子が配置された撮像部と、前記撮像部を制御する制御部と、を備え、前記制御部は、前記撮像面の第1の領域に配置された第1の光電変換素子群から、M(2以上の整数)ラインずつ画像信号を1ライン分の画像信号として前記撮像部から読み出す第1のモードと、前記撮像面の前記第1の領域よりも小さい第2の領域に配置された第2の光電変換素子群から、N(1以上M未満の整数)ラインずつ画像信号を1ライン分の画像信号として前記撮像部から読み出す第2のモードとを有し、前記第2のモードにおける水平期間が、前記第1のモードにおける水平期間のN/Mとなるように制御することで、前記第1及び第2のモードにおいて各ラインのリセットタイミング及び読み出しタイミングが一定となるように制御し、前記第1のモードにおける水平期間は、ある前記Mライン分の画像信号の読み出し開始から、次の前記Mライン分の画像信号の読み出し開始までの期間であり、前記第2のモードにおける水平期間は、ある前記Nライン分の画像信号の読み出し開始から、次の前記Nライン分の画像信号の読み出し開始までの期間であることを特徴とする。

30

## 【0013】

本発明の第2の側面は、撮像システムに係り、光学系と、上記の撮像装置と、を備えることを特徴とする。

## 【0014】

本発明の第3の側面は、撮像面に複数の光電変換素子が配置された撮像部と、前記撮像部を制御する制御部とを備える撮像装置の制御方法に係り、前記撮像面の第1の領域に配置された第1の光電変換素子群から、M(2以上の整数)ラインずつ画像信号を1ライン分の画像信号として前記撮像部から読み出す第1のモードと、前記撮像面の前記第1の領域よりも小さい第2の領域に配置された第2の光電変換素子群から、N(1以上M未満の整数)ラインずつ画像信号を1ライン分の画像信号として前記撮像部から読み出す第2のモードとを有し、前記第2のモードにおける水平期間が、前記第1のモードにおける水平期間のN/Mとなるように制御することで、前記第1及び第2のモードにおいて各ラインのリセットタイミング及び読み出しタイミングが一定となるように制御し、前記第1のモードにおける水平期間は、ある前記Mライン分の画像信号の読み出し開始から、次の前記

40

50

M ライン分の画像信号の読み出し開始までの期間であり、前記第2のモードにおける水平期間は、ある前記N ライン分の画像信号の読み出し開始から、次の前記N ライン分の画像信号の読み出し開始までの期間であることを特徴とする。

**【発明の効果】**

**【0015】**

本発明によれば、駆動モードにかかわらず撮像部における蓄積時間をほぼ一定に保つことができる。

**【発明を実施するための最良の形態】**

**【0016】**

以下、本発明の好適な実施の形態について、添付図面を参照して詳細に説明する。 10

**(第1の実施形態)**

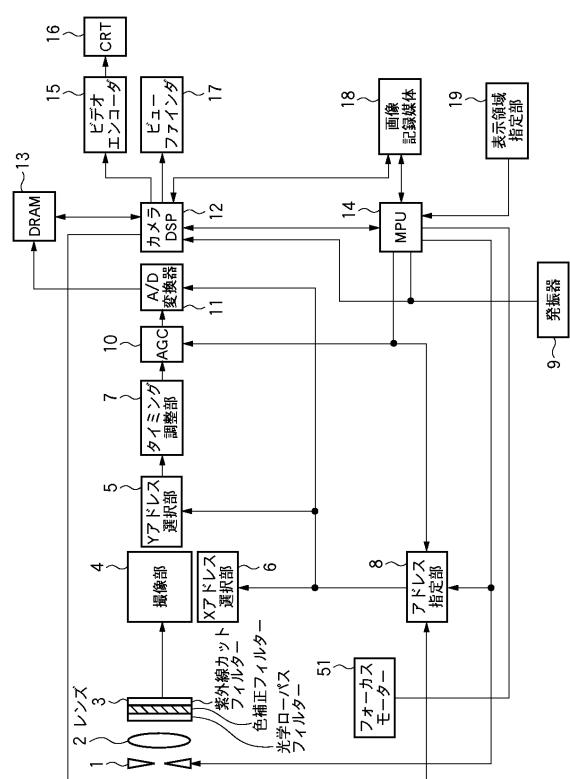

図5は、本発明の好適な実施の形態に係る撮像システムの構成を示す図である。ここで光電変換は、被写体からの光が絞り羽根1を通り、レンズ2により撮像部4へ結像されることで行われる。フィルター群3は、モアレ等を防ぐために光の高域をカットする光学ローパス・フィルター、色補正フィルター及び赤外線カットフィルター等が組み合わされたものである。撮像部4では、アドレス指定部8からの信号により、Xアドレス選択部6及びYアドレス選択部5により2次元で画素の選択が行われ、出力信号がタイミング調整部7に読み出される。タイミング調整部7では、撮像部4からの1つ又は複数の出力信号のタイミング調整が行われる。そして、タイミング調整部7から出力された信号は、A G C(オートゲインコントロール)10により電圧が制御され、A / D変換器11でデジタル信号に変換される。カメラDSP12は、動画又は静止画の画像処理を行う。また、制御部としてのMPU14は、この画像処理の際に用いられるパラメータをカメラDSP12に設定したり、AF/AE動作を行ったりする。なお、AF動作は、フォーカス・モーター51によりフォーカス・レンズ(図示せず)を前後に動かして行う。画像処理する際の一時的な記憶領域としてDRAM13が用いられ、不揮発性の記憶領域として記録媒体18が用いられる。記録媒体18としては、例えば、スマート・メディア、磁気テープ又は光ディスク等が挙げられる。ビデオエンコーダ15及びCRT16は、画像処理後の画像を表示する。ビューファインダー17は、例えば、LCDなどを用いることができ、記録媒体18に記憶する前に被写体を確認したりするために用いられる。これらの出力装置は、CRT16及びビューファインダー17に限られず、プリンタ等を用いてもよい。発振器9は、カメラDSP12及びMPU14に供給するクロック信号を発生する。表示領域指定部19は、撮像部4から読み出した画像をビューファインダー17などに表示するときの表示領域を指定する。 20

**【0017】**

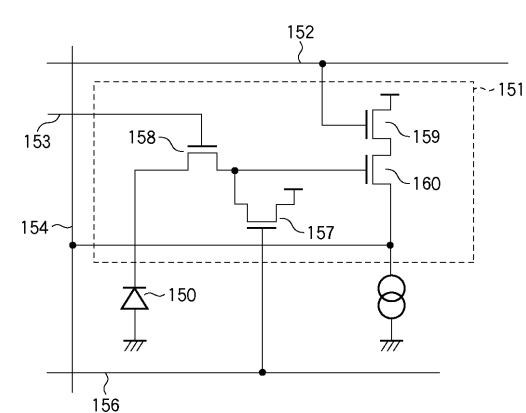

次に、本実施形態に係る光電変換装置の動作について図6を用いて説明する。電位障壁操作用転送ゲートのMOSトランジスタ158は、フォトダイオード(以下「PD」という。)150で蓄積された電荷を増幅MOSトランジスタ160のゲートを浮遊構造としたフローティング・デフュージョン(以下「FD」という。)に転送する。リセットトランジスタ157は、PD150の電荷をリセットするMOSトランジスタである。増幅MOSトランジスタ160には、ライン選択用のMOSトランジスタ159が直列接続されている。これらのMOSトランジスタのゲートは、それぞれ、PD150の電荷を転送する転送信号ライン153、FDをリセットするリセット信号ライン156及び選択信号ライン152に接続されている。ここで、PD150に蓄積された電荷は、リセット信号ライン156によりリセットトランジスタ157がオンしリセットされたFDへ、転送信号ライン153により選択されたMOSトランジスタ158を通して転送される。そして、選択信号ライン152により選択された選択MOSトランジスタ159を介してソースフォロワMOSトランジスタ160で増幅され、読み出しライン154へ読み出される。画素151は、PD150、MOSトランジスタ158、リセットトランジスタ157、増幅MOSトランジスタ160及びMOSトランジスタ159を含み、撮像部4の画素領域に複数配列されている。 30 40 50

**【0018】**

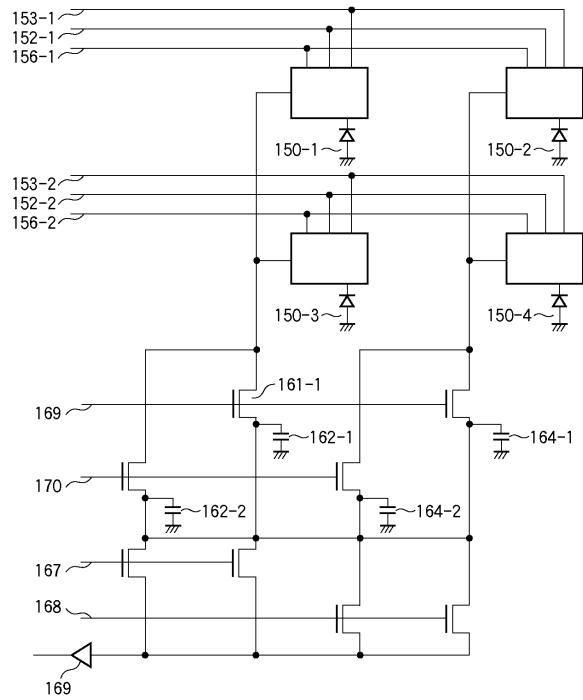

図7は、図6に示された画素を複数配列した画素領域を有する光電変換装置と読み出し回路とを有する撮像装置の回路構成図である。図7では簡略化のために $2 \times 2$ の画素が示されているが、これに限定されず、任意の数の画素が配置されうる。

**【0019】**

非加算制御では、PD150-1の電荷は、図7に示されるMOSトランジスタ161-1が信号ライン169により導通されることで容量162-1に蓄積される。同様に、PD150-2の電荷は、信号ライン156-1、153-1、152-1及び169によるPD150-1の読み出し制御の際に容量164-1へ読み出される。続いて、信号ライン167と信号ライン168とが交互にオンされることにより、PD150-1及びPD150-2の撮像信号が増幅器169を通して順次読み出される。垂直方向への動作は、信号ライン156-2、153-2、152-2の制御により、上述の動作と同様の動作により行われる。10

**【0020】**

加算制御では、図7に示される信号ライン156-1、153-1、152-1及び169の制御により、PD150-1及びPD150-2の電荷がそれぞれ容量162-1及び164-1へ蓄積される。続いて、信号ライン156-2、153-2、152-2及び170の制御により、PD150-3及びPD150-4の電荷がそれぞれ容量162-2及び164-2へ蓄積される。この後、信号ライン167及び信号ライン168を同時にオンすると、PD150-1、PD150-2、PD150-3及びPD150-4の電荷を加算した撮像信号が増幅器169を通して読み出される。また、PD150-1及びPD150-4の信号の電荷を容量162-1及び容量164-1へ蓄積する。その後、信号ライン167及び信号ライン168を同時にオンすると、PD150-1及びPD150-4の電荷を加算した撮像信号が増幅器169を通して読み出される。上記した制御手段により、非加算制御及び加算制御を行わせることができる。20

**【0021】**

次に、本発明の特徴である電子ズーム倍率の変更などにより駆動モードが変更された場合において、フレーム内の蓄積時間を統一する方法について説明する。

**【0022】**

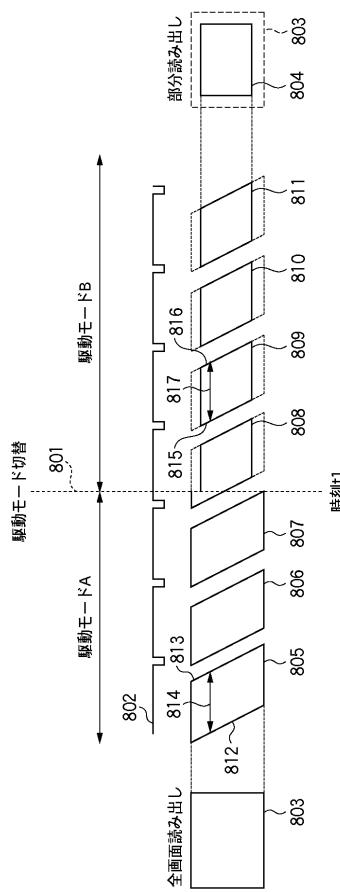

図8は、CMOSイメージセンサの垂直方向の位置に対して、駆動モードにかかわらず同じタイミングでリセット及び読み出しを行う場合の概念図である。図8の横軸は時間を表し、縦軸はCMOSイメージセンサにおける読み出し位置を示す。図8では、時刻t1(801)において駆動モードAから駆動モードBに切り替えた場合における蓄積時間(フレーム805～811)が示されている。802は垂直同期信号VDである。駆動モードAでは全画面読み出し803を行い、駆動モードBでは部分読み出し804を行う。駆動モードAのフレーム805では、リセットタイミング812から読み出しタイミング813までが蓄積時間814に対応する。同様に、駆動モードBのフレーム809では、リセットタイミング815から読み出しタイミング816までが蓄積時間817に対応する。駆動モードAにおけるフレーム806及び807並びに駆動モードBにおけるフレーム810及び811においても同様である。3040

**【0023】**

図8は、時刻t1以降のフレーム808～811のリセットタイミング及び読み出しタイミングの傾きが時刻t1以前のフレーム805～807と同じである点で図5と相違する。すなわち、駆動モードAと駆動モードBとで蓄積時間が一定に保たれる。これは、駆動モードAと駆動モードBとでCMOSイメージセンサの垂直方向の位置を基準に同じタイミングでリセット及び読み出しを行うことにより実現される。

**【0024】**

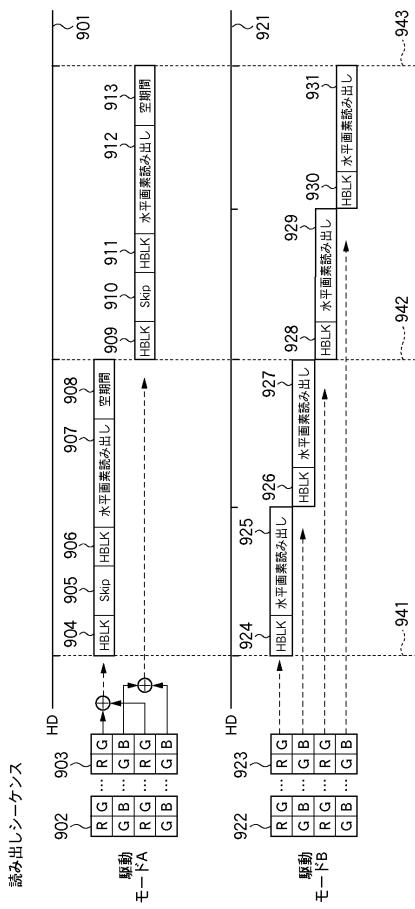

図9、図10は、空期間の挿入によるタイミング合わせを行った際の読み出しシーケンス及びリセットシーケンスを示す図である。図9における901、921は水平同期信号HD(HDとHDの間の期間は、ある1ラインの信号の読み出し開始から、次に読み出され50

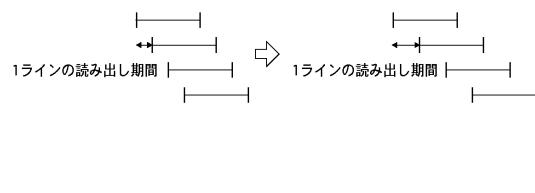

る 1 ラインの信号の読み出し開始までの期間を示す)である。902、903、922 及び 923 は、1 ブロックが R、G、G、B の画素の繰り返しで構成された、撮像部 4 の画素領域の一部である。駆動モード A における 1 ラインの読み出しシーケンスは、904～908 及び 909～913 で構成される。駆動モード B における 1 ラインの読み出しシーケンスは、924～927 及び 928～931 で構成される。904、906、909、911、924、926、928 及び 930 は、水平プランキング期間 (HBLK) である。905 及び 910 は、1 ラインを間引くのに必要となる期間 (Skip) である。907、912、925、927、929 及び 931 は、水平画素数 × 基準クロック時間で表される水平方向の読み出し期間である。908 及び 913 は、空期間である。

## 【0025】

10

駆動モード B は、駆動モード A に対する電子ズーム倍率が 2 倍の場合を示す。すなわち、駆動モード A の読み出し領域は図 1 (a) の太枠 102 であり、駆動モード B の読み出し領域は図 1 (b) の中央部 103 であるとする。駆動モード A において水平方向の 1 ラインの読み出しに要する期間は 904～907 である。これに対し、駆動モード B において水平方向の 1 ラインの読み出しに要する期間は 924～925 である。したがって、駆動モード A において水平方向の 1 ラインの読み出しに要する期間は、駆動モード B において水平方向の 1 ラインの読み出しに要する期間よりも長い。一方、駆動モード A における垂直方向の読み出しライン数は、駆動モード B における垂直方向の読み出しライン数の 1/2 で済む。垂直方向の読み出し期間は、駆動モード A よりも駆動モード B の方が時間がかかる。そのため、駆動モード A では、駆動モード B における 2 ライン分の期間 941～942 及び 942～943 に合わせて、空期間 908、913 を読み出しシーケンスに挿入する。これにより、駆動モード A 及び駆動モード B のいずれにおいても、垂直方向の位置を基準としてほぼ同じタイミングで読み出しを行うことができる。

20

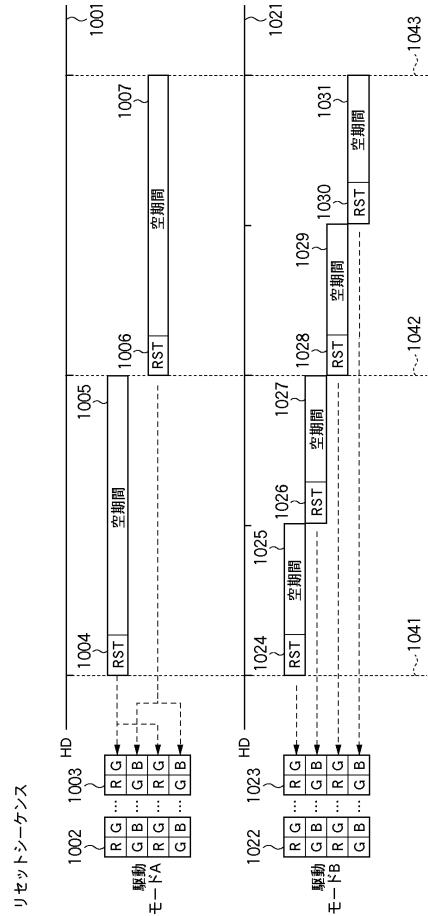

## 【0026】

図 10 における 1001 及び 1021 は水平同期信号 HD (HD と HD の間の期間は、ある 1 ラインの信号の読み出し開始から、次に読み出される 1 ラインの信号の読み出し開始までの期間を示す) である。1002、1003、1022 及び 1023 は、1 ブロックが R、G、G、B の画素の繰り返しで構成された、撮像部 4 の画素領域の一部である。駆動モード A における 1 ラインの読み出しシーケンスは、1004 及び 1005、1006 及び 1007 でそれぞれ構成される。駆動モード B における 1 ラインの読み出しシーケンスは、1024 及び 1025、1026 及び 1027、1028 及び 1029、1030 及び 1031 でそれぞれ構成される。1004、1006、1024、1026、1028 及び 1030 は、リセット期間 (RST) である。1005、1007、1025、1027、1029 及び 1031 は、空期間である。リセットシーケンスにおいても、空期間 1005、1007、1025、1027、1029 及び 1031 を挿入することにより、駆動モード A 及び駆動モード B で 1041、1042、1043 のタイミングを合わせることができる。これにより、駆動モード A 及び駆動モード B のいずれにおいても、垂直方向の位置を基準としてほぼ同じタイミングでリセットを行うことができる。

30

## 【0027】

40

他の駆動の場合も、同様にして空期間を挿入することによって、垂直方向の位置を基準としてほぼ同じタイミングでリセット及び読み出しを行うことができる。

## 【0028】

このように、本実施形態によれば、CMOS イメージセンサの垂直方向の位置に対して、駆動モード (モード) にかかわらず同じタイミングでリセット及び読み出しを行うことができる。その結果、駆動モードの切り替え時にも蓄積時間をほぼ一定に保つことができる。これにより、画面上下の明暗差の発生を防ぐことができ、EVF 表示や動画録画などの動画処理における該当フレームの廃棄によるコマ落ち、明暗差の補正処理や画質劣化などを防止することができる。

## 【0029】

(第 1 の実施形態の変形例)

50

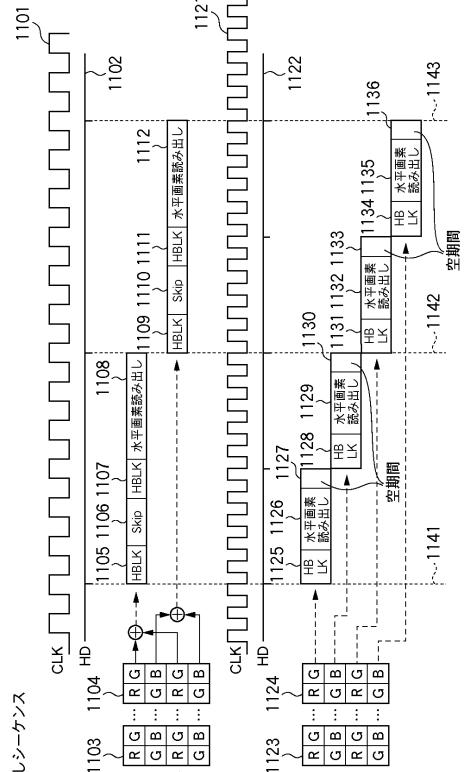

図11は、クロック周波数の変更と空期間の挿入によるタイミング合わせを行った際の読み出しシーケンスを示す図である。本変形例は、CMOSイメージセンサの垂直方向の位置に対して、ほぼ同じタイミングでリセット及び読み出しを行うことにより蓄積時間をほぼ一定に保つ点において、第1の実施形態1と共に通する。しかしながら、本変形例では、CMOSイメージセンサの垂直方向の位置を基準としてほぼ同じタイミングでリセット及び読み出しを行う制御手段において、CMOSイメージセンサ用の同期クロックの周波数変更を利用する点が相違する。

#### 【0030】

図11における1101及び1121は、CMOSイメージセンサ用の同期クロックである。1102及び1122は、水平同期信号HDである。1103、1104、1123及び1124は、1ブロックがR、G、G、Bの画素の繰り返し構成された、撮像部4の画素領域の一部である。駆動モードAにおける1ラインの読み出しシーケンスは、1105～1108及び1109～1112でそれぞれ構成される。駆動モードBにおける1ラインの読み出しシーケンスは、1125～1127、1128～1130、1131～1133、1134～1136でそれぞれ構成される。1105、1107、1109、1111、1125、1128、1131及び1134は、水平プランギング期間(HBLK)である。1106及び1110は、1ラインを間引くのに必要となる期間(Skip)である。1108、1112、1126、1129、1132及び1135は、水平画素数×基準クロック時間で表される水平方向の読み出し期間である。1127、1130、1133及び1136は、空期間である。

10

20

#### 【0031】

駆動モードBは、駆動モードAに対する電子ズーム倍率が2倍の場合を示す。すなわち、駆動モードAの読み出し領域は図1(a)の太枠102であり、駆動モードBの読み出し領域は図1(b)の中央部103であるとする。駆動モードBにおける垂直方向の読み出しライン数は、駆動モードAにおける垂直方向の読み出しライン数の2倍である。CMOSイメージセンサの垂直方向の読み出し期間を短縮するため、駆動モードBではCMOSイメージセンサ用の同期クロック1121を、駆動モードAにおけるCMOSイメージセンサ用の同期クロック1101よりも高い周波数にする。そして、駆動モードAの1ライン分の期間1141～1142及び1142～1143に、駆動モードBの2ライン分の期間1141～1142及び1142～1143を合わせる。駆動モードBでは、空期間1127、1130、1133及び1136を読み出しシーケンスに挿入する。これにより、駆動モードA及び駆動モードBのいずれにおいても、CMOSイメージセンサの垂直方向の位置を基準としてほぼ同じタイミングで読み出しを行うことができる。

30

#### 【0032】

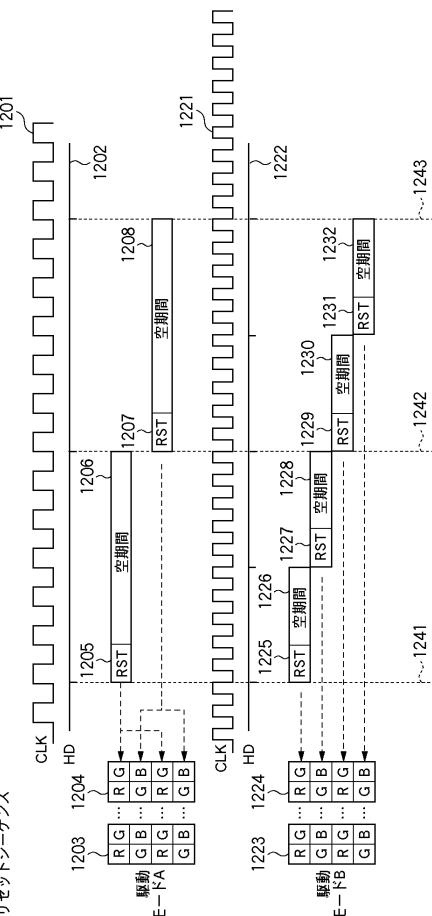

図12は、クロック周波数の変更と空期間の挿入によるタイミング合わせを行った際のリセットシーケンスを示す図である。図12における1201、1221は、CMOSイメージセンサ用の同期クロックである。1202、1222は、水平同期信号HDである。1203、1204、1223及び1224は、1ブロックがR、G、G、Bの画素の繰り返し構成された、撮像部4の画素領域の一部である。駆動モードAにおける1ラインのリセットシーケンスは、1205及び1206並びに1207及び1208でそれぞれ構成される。駆動モードBにおける1ラインのリセットシーケンスは、1225～1228、1229～1232でそれぞれ構成される。1205、1207、1225、1227、1229及び1231は、リセット期間(RST)である。1206、1208、1226、1229、1230及び1232は、空期間である。リセットシーケンスにおいても、空期間1206、1208、1226、1228、1230及び1232を挿入することにより、駆動モードA及び駆動モードBで1241、1242、1243のタイミングを合わせることができる。これにより、駆動モードA及び駆動モードBのいずれにおいても、CMOSイメージセンサの垂直方向の位置を基準としてほぼ同じタイミングでリセットを行うことができる。

40

#### 【0033】

50

他の駆動の場合も同様に C M O S イメージセンサ用の同期クロックの周波数の変更と空期間の挿入を利用することにより、C M O S イメージセンサの垂直方向の位置を基準としてほぼ同じタイミングでリセット及び読み出しを行うことができる。

#### 【 0 0 3 4 】

このように、本実施形態 1 の変形例によれば、駆動モードにかかわらず C M O S イメージセンサの垂直方向の位置を基準にして同じタイミングでリセット及び読み出しを行うことができる。その結果、駆動の切り替え時にも蓄積時間をほぼ一定に保つことができる。これにより、画面上下の明暗差の発生を防ぐことができ、E V F 表示や動画録画などの動画処理における該当フレームの廃棄によるコマ落ち、明暗差の補正処理や画質劣化を避けることができる。

10

#### 【 0 0 3 5 】

また、第 1 の実施形態 1 では、読み出し期間及びリセット期間を C M O S イメージセンサの垂直方向における最長の読み出し期間の駆動時に合わせて、他の駆動では空期間の挿入をするため 1 フレームあたりの読み出し期間が長くなるという問題がある。この変形例では C M O S イメージセンサ用の同期クロックを高周波数にすることにより読み出し期間を短縮することができる。

#### 【 0 0 3 6 】

##### ( 第 2 の実施形態 )

本発明の特徴である電子ズーム倍率の変更などにより駆動モードが変更された場合において、フレーム内の蓄積時間を統一する方法の第 2 の実施形態について説明する。

20

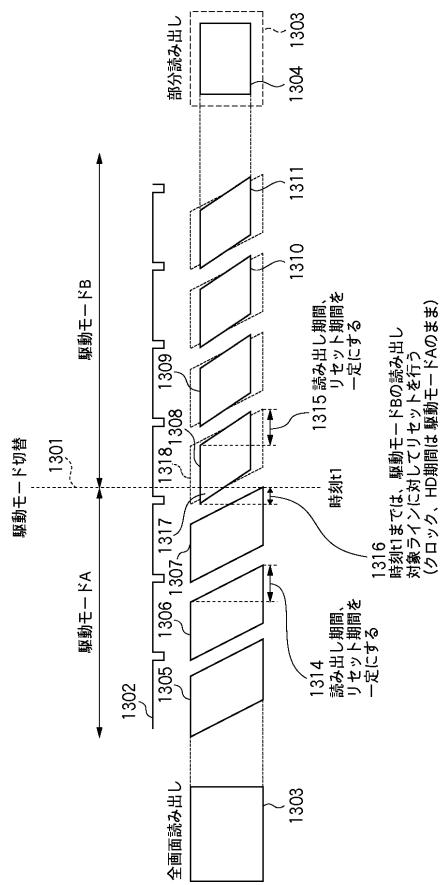

#### 【 0 0 3 7 】

第 1 の実施形態及びその変形例では、図 8 で示したように、C M O S イメージセンサの垂直方向の位置に対して、駆動モードにかかわらず同じタイミングでリセット及び読み出しを行うことによりフレーム内の蓄積時間を統一した。第 2 の実施形態では、読み出し対象ラインのリセットタイミング及び読み出しタイミングを一定にすることにより、フレーム内の蓄積時間を統一する。このとき、読み出し期間及びリセット期間は一定となる。

#### 【 0 0 3 8 】

図 13 は、読み出し対象ラインのリセットタイミング及び読み出しタイミングを一定にする場合の概念図である。図 13 の横軸は時間を表し、縦軸は C M O S イメージセンサにおける読み出し位置を示す。フレーム 1305 ~ 1311 は、各駆動におけるライン位置あたりの蓄積タイミングと蓄積時間を表している。図 13 では、時刻 t1 ( 1301 ) までは駆動モード A で駆動し、時刻 t1 ( 1301 ) で駆動モード B に切り替えた場合におけるフレーム 1305 ~ 1311 の蓄積時間を示す。1302 は垂直同期信号 V D である。駆動モード A では全画面読み出し 1303 を行い、駆動モード B では部分読み出し 1304 を行う。図 13 では、時刻 t1 を境にしてフレーム 1308 ~ 1311 のリセット期間及び読み出し期間が駆動モード A と駆動モード B とで同じとなる点で図 4 と相違する。すなわち、蓄積時間を一定に保つことができる。これは、駆動モード A と駆動モード B とで読み出し対象ラインを基準としたリセットタイミングと読み出しタイミングを一定にすることにより実現することができる。このためには、時刻 t1 における駆動切り替え 1301 を行う際に、駆動モード B における読み出し領域に対して、フレーム 1308 の時刻 t1 以前のリセット期間 1317 のリセットを事前に行う。

30

#### 【 0 0 3 9 】

このように、第 2 の本実施形態によれば、読み出し対象ラインのリセットタイミングと読み出しタイミングを駆動モードにかかわらず一定に保つことができる。これによって、画面上下の明暗差の発生を防ぐことができ、E V F 表示や動画録画などの動画処理における該当フレームの廃棄によるコマ落ち、明暗差の補正処理や画質劣化を避けることができる。

#### 【 0 0 4 0 】

上記の第 1 の実施形態、第 2 の実施形態では、駆動 A では 2 ラインの加算を行う駆動を行っているが、その 2 ラインのうちの 1 ラインを間引く駆動であっても良い。

40

50

**【 0 0 4 1 】**

また、駆動 A では、全画面を 2 ライン加算で読み出し、駆動 B では、一部分を非加算で読み出す駆動を行っているが、駆動 A では、全画面を 4 ライン加算で読み出し、一部分を非加算で読み出す駆動を行っても良い。

**【 図面の簡単な説明 】****【 0 0 4 2 】**

【 図 1 】 C M O S イメージセンサの特徴を利用した電子ズーム動作の概念図である。

【 図 2 】 垂直 2 画素加算平均におけるライン蓄積時間差を示す概念図である。

【 図 3 】 駆動モードが変化したときのローリングシャッタの動作を示す図である。

【 図 4 】 画面上下で蓄積時間がずれる様子を示す概念図である。 10

【 図 5 】 本発明の好適な実施の形態に係る撮像システムの構成を示す図である。

【 図 6 】 本実施形態に係る光電変換装置の回路構成図である。

【 図 7 】 本実施形態に係る撮像装置の回路構成図である。

【 図 8 】 C M O S イメージセンサの垂直方向の位置に対して同じタイミングでリセット及び読み出しを行う場合の概念図である。

【 図 9 】 空期間の挿入によるタイミング合わせを行った際の読み出しシーケンスを示す図である。

【 図 1 0 】 空期間の挿入によるタイミング合わせを行った際のリセットシーケンスを示す図である。 20

【 図 1 1 】 クロック周波数変更と空期間の挿入によるタイミング合わせを行った際の読み出しシーケンスを示す図である。

【 図 1 2 】 クロック周波数変更と空期間の挿入によるタイミング合わせを行った際のリセットシーケンスを示す図である。

【 図 1 3 】 読み出し対象ラインに対して同じタイミングでリセット及び読み出しを行う場合の概念図である。

**【 符号の説明 】****【 0 0 4 3 】**

4 撮像部

1 4 M P U

【図1】

【図4】

【図2】

【図3】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

リセットシーケンス

---

フロントページの続き

審査官 若林 治男

(56)参考文献 特開2005-086245(JP,A)

特開2002-330329(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/353

H04N 5/374