(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4954626号

(P4954626)

(45) 発行日 平成24年6月20日(2012.6.20)

(24) 登録日 平成24年3月23日(2012.3.23)

(51) Int.Cl.

F 1

|               |                |                  |        |       |         |

|---------------|----------------|------------------|--------|-------|---------|

| <b>G 11 C</b> | <b>11/413</b>  | <b>(2006.01)</b> | G 11 C | 11/34 | 3 3 5 A |

| <b>H 01 L</b> | <b>27/11</b>   | <b>(2006.01)</b> | H 01 L | 27/10 | 3 8 1   |

| <b>H 01 L</b> | <b>21/8244</b> | <b>(2006.01)</b> | G 11 C | 11/34 | K       |

| <b>G 11 C</b> | <b>11/41</b>   | <b>(2006.01)</b> | G 11 C | 11/34 | 3 4 5   |

|               |                |                  | G 11 C | 11/40 | B       |

請求項の数 4 (全 21 頁)

(21) 出願番号 特願2006-200448 (P2006-200448)

(22) 出願日 平成18年7月24日 (2006.7.24)

(65) 公開番号 特開2007-59043 (P2007-59043A)

(43) 公開日 平成19年3月8日 (2007.3.8)

審査請求日 平成21年7月17日 (2009.7.17)

(31) 優先権主張番号 特願2005-220530 (P2005-220530)

(32) 優先日 平成17年7月29日 (2005.7.29)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 岩田 周祐

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 園田 康弘

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

電源制御回路と、メモリセルと、第1乃至4のワード線と、グランド線と、電源線と、第1乃至3のデータ線とを有し、

前記電源制御回路は、

4つの入力端子と1つの出力端子を有し、少なくともいずれか1つの前記入力端子にハイレベルが入力されると前記出力端子にハイレベルが出力され、すべての前記入力端子にロウレベルが入力されると前記出力端子にロウレベルが出力される回路と、第1のインバータ回路と、第1及び2のトランジスタと、クロックが入力されるフリップフロップ回路とを有し、

前記4つの入力端子と1つの出力端子を有する回路の4つの入力端子は、それぞれ前記第1乃至4のワード線に電気的に接続され、

前記第1及び2のワード線は、前記フリップフロップ回路の出力端子にそれが電気的に接続され、前記第3及び4のワード線は、前記フリップフロップ回路の入力端子にそれが電気的に接続され、

前記4つの入力端子と1つの出力端子を有する回路の出力端子は、前記第1のインバータ回路の入力端子と、かつ、前記第1のトランジスタのゲート電極とに電気的に接続され、

前記第1のトランジスタの一方の電極は、第1の電圧を供給する配線に電気的に接続され、前記第1のトランジスタの他方の電極は、前記電源線と、かつ、前記第2のトランジ

10

20

スタの一方の電極とに電気的に接続され、

前記第2のトランジスタの他方は、第2の電圧を供給する配線に電気的に接続され、前記第2のトランジスタのゲート電極は、前記第1のインバーター回路の出力端子に電気的に接続され、

前記メモリセルは、

第3乃至6のトランジスタと、互いに出力端子と入力端子が接続された第2及び3のインバーター回路と、を有し、

前記第2及び3のインバーター回路は、前記電源線に一方の電極が電気的に接続された第7及び8のトランジスタを有し、

前記第2及び3のインバーター回路は、前記グランド線に一方の電極が電気的に接続された第9及び10のトランジスタを有し、

前記第3のトランジスタの一方の電極は、前記第2のインバーター回路の出力端子に電気的に接続され、前記第3のトランジスタの他方の電極は、前記第1のデータ線に電気的に接続され、前記第3のトランジスタのゲート電極は、前記第1のワード線に電気的に接続され、

前記第4のトランジスタの一方の電極は、前記第2のデータ線と接続され、前記第4のトランジスタの他方の電極は、前記第3のインバーター回路の出力端子に電気的に接続され、前記第4のトランジスタのゲート電極は、前記第1のワード線に電気的に接続され、

前記第5のトランジスタの一方の電極は、前記第10のトランジスタの他方の電極に電気的に接続され、前記第5のトランジスタの他方の電極は、前記第6のトランジスタの一方の電極に電気的に接続され、前記第5のトランジスタのゲート電極は、前記第2のインバーター回路の入力端子に電気的に接続され、

前記第6のトランジスタの他方の電極は、前記第3のデータ線に電気的に接続され、前記第6のトランジスタのゲート電極は、前記第2のワード線に電気的に接続されていることを特徴とする半導体装置。

#### 【請求項2】

請求項1において、前記4つの入力端子と1つの出力端子を有する回路は、OR回路、NOR回路とインバーター回路とからなる回路、2つのインバーター回路とNAND回路とからなる回路のいずれかからなることを特徴とする半導体装置。

#### 【請求項3】

請求項1又は2において、前記第1乃至10のトランジスタは絶縁基板上に形成された薄膜トランジスタからなることを特徴とする半導体装置。

#### 【請求項4】

請求項1乃至3のいずれか一において、前記第1乃至3のデータ線は、前記第1乃至10のトランジスタのソース電極及びドレイン電極と同一層から設けられることを特徴とする半導体装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、メモリ素子を有する半導体装置及び半導体装置の駆動方法に関する。

#### 【背景技術】

#### 【0002】

L S I (Large Scale Integration) 製造技術の発展による配線の微細化に伴い、リーク電流の問題が顕著になってきている。リーク電流により、L S I の発熱や消費電力の増大などの問題が発生してしまう。特に携帯電話や、ノート型のパソコンやスマートフォンなどのモバイル機器では消費電力の問題はその連続動作時間に直結し、大きな問題となっている。そのため L S I の低消費電力化に関しては、様々な技術が提案されている。

#### 【0003】

例えば L S I の動作には、その性能を最大限に必要とするときとそうでないときがある。

10

20

30

40

50

L S I の動作速度をそれほど必要としないときには、クロックの周波数を下げて動作させる技術がある。その他にも、同様に動作速度を最大限に必要としないときに、基板バイアスをシフトさせ閾値を制御することによってリーク電流を低減させる技術がある。

#### 【 0 0 0 4 】

また最近の L S I では内部に、キャッシュなどの非常に大容量のメモリが存在し S R A M ( S t a t i c R a n d o m A c c e s s M e m o r y ) で構成されることが多い。S R A M はインバーター回路同士をつなぐことによって値を保持する。一度、値を保持すると電気的な状態は変化しないが、インバーター回路につながる電源線から、グランド線にリーク電流が流れてしまう。

#### 【 0 0 0 5 】

消費電力を低減された S R A M の構成として、S R A M の行デコーダの各ワード線で選択されるメモリセル群の電源ラインと、電圧供給源側の電源ラインとの間に、スイッチングM O S トランジスタを設け、ワード線の選択信号で、スイッチングM O S トランジスタを開閉するものがある（特許文献1参照）。

【特許文献1】特開平10-106267号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【 0 0 0 6 】

S R A M の動作には、書き込みと読み出しがあり、この動作を行っているときにはメモリ全体の一部だけが動作し、他の部分は値を保持しているだけである。書き込み、読み出し時には既定の電圧を必要とするが、値を保持するだけであれば既定の電圧は必要とせず、また電源電圧を下げるによりオフ電流を低減することが出来る。

#### 【 0 0 0 7 】

特許文献1に記載の S R A M では、アドレスの電源を変化させ、電源をカットする構成が記載されている。しかし、電源をカットすると、S R A M に適用されるトランジスタのオフ電流によって電気がグランド線に流れてしまい、値を保持することが難しいと考えられる。

#### 【 0 0 0 8 】

そこで本発明は、L S I 動作時に、特許文献1とは異なる方法によってメモリ内で電源の供給方法を制御し、トランジスタのリーク電流を低減することによってL S I の消費電力を抑制することを課題とする。

#### 【課題を解決するための手段】

#### 【 0 0 0 9 】

上記課題を鑑み本発明は、値を書き込む期間又は読み出す期間と比べて、保持する期間における駆動電圧を低くすることを特徴とする。すなわち、本発明に係るメモリセルに値を書き込む期間では、メモリセルの電源線に第1の電圧が与えられ、書き込まれた値を保持する期間では、メモリセルの電源線には第1の電圧より低い第2の電圧が与えられることを特徴とする駆動方法である。

#### 【 0 0 1 0 】

以下に本発明の具体的な構成を示す。

#### 【 0 0 1 1 】

本発明の一形態は、電源線に接続されたインバーター回路を有するメモリセルを有し、前記メモリセルに値を書き込む期間には、第1の電圧が前記電源線に供給され、前記メモリセルに書き込まれた値を保持する期間には、前記第1の電圧より低い第2の電圧が前記電源線に供給され、前記メモリセルに書き込まれた値を読み出す期間には、前記第1の電圧が前記電源線に供給される半導体装置である。

#### 【 0 0 1 2 】

本発明の別形態は、電源制御回路とメモリセルとを有し、前記電源制御回路は、第1のワード線及び第2のワード線と、第1のワード線又は第2のワード線にそれぞれ接続された2つの入力端子と一つの出力端子とを有し、いずれか一方の入力端子に H I G H ( ハイ )

10

20

30

40

50

レベルが入力されると出力端子に H I G H レベルが出力され、両方の入力端子に L O W (ロウ) レベルが入力されると出力端子に L O W レベルが出力される回路と、出力端子に入力端子が接続された第 1 のインバーター回路と、回路及び第 1 のインバーター回路に電気的に接続され、メモリセルに第 1 の電圧又は第 1 の電圧より低い第 2 の電圧を供給する手段と、を有し、前記メモリセルは、第 2 のインバーター回路を有し、第 1 のワード線及び第 2 のワード線に接続される半導体装置である。

#### 【 0 0 1 3 】

本発明の別形態は、電源制御回路とメモリセルとを有し、前記電源制御回路は、第 1 のワード線及び第 2 のワード線と、第 1 のワード線又は第 2 のワード線にそれぞれ接続された 2 つの入力端子と一つの出力端子とを有し、いずれか一方の入力端子に H I G H レベルが入力されると出力端子に H I G H レベルが出力され、両方の入力端子に L O W レベルが入力されると出力端子に L O W レベルが出力される回路と、出力端子に入力端子が接続された第 1 のインバーター回路と、回路及び第 1 のインバーター回路に電気的に接続され、メモリセルに第 1 の電圧又は第 1 の電圧より低い第 2 の電圧を供給する手段と、を有し、前記メモリセルは、グランド線及び電源線に接続された第 2 のインバーター回路を有し、第 1 のワード線及び第 2 のワード線に接続される半導体装置である。 10

#### 【 0 0 1 4 】

本発明の別形態は、電源制御回路とメモリセルとを有し、前記電源制御回路は、第 1 のワード線及び第 2 のワード線と、第 1 のワード線又は第 2 のワード線にそれぞれ接続された 2 つの入力端子と一つの出力端子とを有し、いずれか一方の入力端子に H I G H レベルが入力されると出力端子に H I G H レベルが出力され、両方の入力端子に L O W レベルが入力されると出力端子に L O W レベルが出力される回路と、出力端子に入力端子が接続された第 1 のインバーター回路と、回路及び第 1 のインバーター回路に電気的に接続され、メモリセルに第 1 の電圧又は第 1 の電圧より低い第 2 の電圧を供給する手段と、を有し、前記メモリセルは、グランド線及び電源線に接続された第 2 のインバーター回路と、第 2 のインバーター回路に接続されたトランジスタとを有し、トランジスタのゲート電極に接続された第 1 のワード線と、第 1 のワード線及び第 2 のワード線に接続される半導体装置である。 20

#### 【 0 0 1 5 】

本発明の別形態は、電源制御回路とメモリセルとを有し、前記電源制御回路は、第 1 のワード線及び第 2 のワード線と、第 1 のワード線又は第 2 のワード線にそれぞれ接続された 2 つの入力端子と一つの出力端子とを有し、いずれか一方の入力端子に H I G H レベルが入力されると出力端子に H I G H レベルが出力され、両方の入力端子に L O W レベルが入力されると出力端子に L O W レベルが出力される回路と、出力端子に入力端子が接続された第 1 のインバーター回路と、回路及び第 1 のインバーター回路に電気的に接続され、メモリセルに第 1 の電圧又は第 1 の電圧より低い第 2 の電圧を供給する手段と、を有し、前記メモリセルは、グランド線及び電源線に接続された第 2 のインバーター回路と、第 2 のインバーター回路に接続された第 1 乃至第 3 のトランジスタと、第 1 のトランジスタのゲート電極に接続された第 1 のワード線と、第 2 及び第 3 のトランジスタの一方の電極に接続されたデータ線と、を有し、第 2 及び第 3 のトランジスタのゲート電極に接続された第 2 のワード線と、第 1 のワード線及び第 2 のワード線に接続される半導体装置である。 30 40

#### 【 0 0 1 6 】

本発明において、メモリセルに第 1 の電圧又は第 1 の電圧より低い第 2 の電圧を供給する手段は、2 つのトランジスタからなる。

#### 【 0 0 1 7 】

本発明において、2 つの入力端子と一つの出力端子を有し、いずれか一方の入力端子に H I G H レベルが入力されると H I G H レベルが出力され、両方の入力端子に L O W レベルが入力されると L O W レベルが出力される回路は、O R 回路、N O R 回路とインバーター回路とからなる回路、2 つのインバーター回路と N A N D 回路とからなる。

#### 【 0 0 1 8 】

50

本発明において、ワード線及び電源線は、薄膜トランジスタのゲート電極と同一層から設けられることができる。

【0019】

本発明において、データ線は、薄膜トランジスタのソース電極及びドレイン電極と同じ材料で作製することができる。

【0020】

本発明の別形態は、第1のワード線及び第2のワード線に接続された、第1のインバータ回路を有するメモリセルと、第1のワード線及び第2のワード線と、第1のワード線又は第2のワード線にそれぞれ接続された2つの入力端子と一つの出力端子とを有し、いずれか一方の入力端子にHIGHレベルが入力されると出力端子にHIGHレベルが出力され、両方の入力端子にLOWレベルが入力されると出力端子にLOWレベルが出力される回路と、出力端子に入力端子が接続された第2のインバータ回路と、第2のインバータ回路の出力端子にゲート電極が接続された第1のトランジスタと、回路の出力端子に接続された第2のトランジスタと、第1及び第2のトランジスタに接続された電源線と、を有する電源制御回路と、を有し、メモリセルに値を書き込む期間では、第1のワード線がHIGHレベルとなり、第2のワード線がLOWレベルとなり、第1のトランジスタがオンとなり、電源線に第1の電圧が与えられ、メモリセルに書き込まれた値を保持する期間では、第1のワード線及び第2のワード線がLOWレベルとなり、第2のトランジスタがオンとなり、電源線には第1の電圧より低い第2の電圧が与えられる半導体装置の駆動方法である。

10

20

【0021】

本発明の別形態は、グランド線及び電源線に接続された第1のインバータ回路を有し、第1のワード線及び第2のワード線に接続されたメモリセルと、第1のワード線及び第2のワード線と、第1のワード線又は第2のワード線にそれぞれ接続された2つの入力端子と一つの出力端子とを有し、いずれか一方の入力端子にHIGHレベルが入力されると出力端子にHIGHレベルが出力され、両方の入力端子にLOWレベルが入力されると出力端子にLOWレベルが出力される回路と、出力端子に入力端子が接続されたインバータ回路と、回路及びインバータ回路に接続され、メモリセルに第1の電圧又は第1の電圧より低い第2の電圧を供給する手段と、を有する電源制御回路と、を有し、メモリセルに値を書き込む期間では、第1のワード線がHIGHレベルとなり、第2のワード線がLOWレベルとなり、第1のトランジスタがオンとなり、電源線に第1の電圧が与えられ、メモリセルに書き込まれた値を保持する期間では、第1のワード線及び第2のワード線がLOWレベルとなり、第2のトランジスタがオンとなり、電源線には第1の電圧より低い第2の電圧が与えられる半導体装置の駆動方法である。

30

【0022】

本発明の別形態は、第1のワード線及び第2のワード線に接続された、インバータ回路を有するメモリセルと、第1のワード線及び第2のワード線と、第1のワード線又は第2のワード線に接続された2つの入力端子と一つの出力端子とを有し、いずれか一方の入力端子にHIGHレベルが入力されると出力端子にHIGHレベルが出力され、両方の入力端子にLOWレベルが入力されると出力端子にLOWレベルが出力される回路と、出力端子に入力端子が接続されたインバータ回路と、インバータ回路の出力端子にゲート電極が接続された第1のトランジスタと、回路の出力端子に接続された第2のトランジスタと、第1及び第2のトランジスタに接続された電源線と、を有する電源制御回路と、を有し、メモリセルに値を書き込む期間では、第1のワード線がHIGHレベルとなり、第2のワード線がLOWレベルとなり、第1のトランジスタがオンとなり、第1のトランジスタに接続された電源線に第1の電圧が与えられ、メモリセルに書き込まれた値を保持する期間では、第1のワード線及び第2のワード線がLOWレベルとなり、第2のトランジスタがオンとなり、電源線には第1の電圧より低い電圧が与えられ、前記メモリセルに書き込まれた値を読み出す期間では、前記第1のワード線及び第2のワード線がHIGHレベルとなり、第2のトランジスタがONとなり、電源線には第1の電圧より低い電圧が与えられ、前記メモリセルに書き込まれた値を読み出す期間では、前記第1のワード線がLOWレベルとなり、前記第2のワード線がHIGHレベルとなり、前記第1のトランジスタがONとなり、前記第1のトランジ

40

50

スタに接続された電源線に第1の電圧が与えられる半導体装置の駆動方法である。

**【0023】**

本発明の別形態は、グランド線及び電源線に接続されたインバーター回路を有し、第1のワード線及び第2のワード線に接続されたメモリセルと、第1のワード線及び第2のワード線と、第1のワード線又は第2のワード線にそれぞれ接続された2つの入力端子と一つの出力端子とを有し、いずれか一方の入力端子にHIGHレベルが入力されると出力端子にHIGHレベルが出力され、両方の入力端子にLOWレベルが入力されると出力端子にLOWレベルが出力される回路と、出力端子に入力端子が接続されたインバーター回路と、回路及びインバーター回路に接続され、メモリセルに第1の電圧又は第1の電圧より低い第2の電圧を供給する手段と、を有する電源制御回路と、を有し、メモリセルに値を書き込む期間では、第1のワード線がHIGHレベルとなり、第2のワード線がLOWレベルとなり、第1のトランジスタがオンとなり、第1のトランジスタに接続された電源線に第1の電圧が与えられ、メモリセルに値を保持する期間では、第1のワード線及び第2のワード線がLOWレベルとなり、第2のトランジスタがオンとなり、電源線には第1の電圧より低い電圧が与えられ、前記メモリセルに書き込まれた値を読み出す期間では、前記第1のワード線がロウレベルとなり、前記第2のワード線がハイレベルとなり、前記第1のトランジスタがオンとなり、前記第1のトランジスタに接続された電源線に第1の電圧が与えられる半導体装置の駆動方法である。

10

**【発明の効果】**

**【0024】**

本発明によって、メモリを備えた半導体装置の低消費電力化を図ることができる。特にLSIの機能が複雑化するのに伴い、LSIに必要とされるメモリの容量も大きくなり、さらにチップ内でメモリの占める面積の割合も大きくなっている。メモリの容量が大きくなればなる程、既定の電圧を必要とするメモリセルのSRAM全体に対しての比率は小さくなることから、本発明の効果は大きくなる。

20

**【発明を実施するための最良の形態】**

**【0025】**

本発明に係る半導体装置は、メモリセルを複数個配列したメモリセルアレイと、書き込み及び読み出しを行うビット線を制御する読み出し回路と、ワード線を制御するアドレスデコーダを有している。さらに、アドレスデコーダとメモリセルアレイとの間には、電源制御回路が設けられている。電源制御回路は、アドレスデコーダからワード線へ信号を出力する際に、その信号に同期してメモリセルアレイに延びメモリセルに接続する電源線を制御する。このとき電源線には所定の電源電圧が印加される。

30

**【0026】**

メモリセルは、インバーター回路が直列に接続されて構成されている。具体的には、二つのインバーター回路が、一方のインバーター回路の出力端子が他方のインバーター回路の入力端子に接続され、一方のインバーター回路の入力端子が他方のインバーターの出力端子に接続されている。すなわち、スタティックRAMを構成している。

**【0027】**

電源制御回路は、少なくとも2本のワード線と、該ワード線にそれぞれ接続された2つの入力端子と一つの出力端子とを有し、いずれか一方の入力端子にHIGHレベルが入力されるとHIGHレベルが出力され、両方の入力端子にLOWレベルが入力されるとLOWレベルが出力される回路と、回路に接続されたインバーター回路と、回路及びインバーター回路に接続され、メモリセルに第1の電圧又は第1の電圧より低い第2の電圧を供給する手段とを有する。メモリセルに第1の電圧又は第1の電圧より低い第2の電圧を供給する手段として、直列に接続された2つのトランジスタを適用することができる。メモリセルに値を書き込む又は読み込むときには、第1の電圧を供給し、値を保存するときには第2の電圧を供給する。その結果、値を書き込む期間又は読み出す期間と比べて、保持する期間における駆動電圧を低くすることができ、メモリセルの低消費電力化を図ることができる。

40

50

## 【0028】

このようなメモリアレイはCPU(Central Processing Unit)若しくはマイクロプロセッサMPU(Microprocessor)のキャッシュメモリとして用いることができる。CPUやMPUに適用することによって、CPUやMPUの低消費電力化を達成することができる。

## 【0029】

以下に、本発明の実施例を図面に基づいて説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、以下に示す実施例の記載内容に限定して解釈されるものではない。なお、実施例を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。10

## 【0030】

また以下に示す実施例における電圧値は一例であり、本発明はこの値に限定されるものではない。

## 【0031】

## (実施例1)

本実施例では、本発明のSRAMメモリの構成について説明する。また本発明のSRAMメモリのような半導体素子を有する装置を半導体装置と呼ぶこともできる。

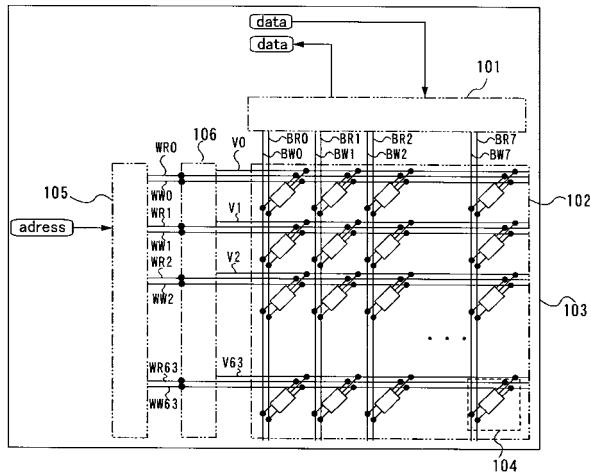

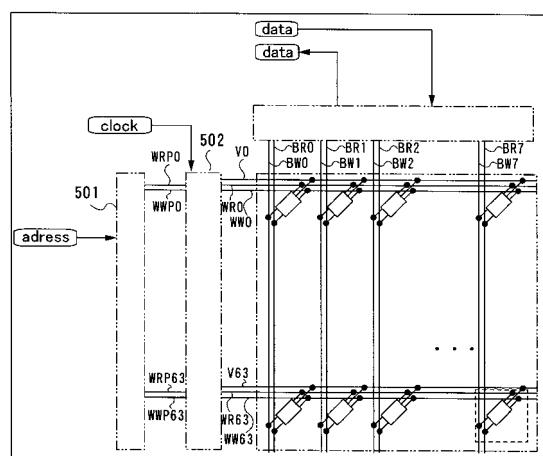

## 【0032】

図1に本発明のSRAMメモリ構成の一例を示す。メモリ103はバイトアドレス方式のメモリで、アドレスが0から63まであり、横方向に8ビットのメモリセルが並び、縦にアドレス0からアドレス63までの64ラインを有する構成を有する。20

## 【0033】

メモリセル104は、1ビットの値を保持することができ、メモリセルアレイ102はメモリセル104を8ビット×64ライン有する。

## 【0034】

書き込み、読み出し回路101はメモリの外部からのデータをメモリセルアレイ102に書き込む処理と、メモリセルアレイ102からのデータを読み出してメモリの外部にデータを送信する処理を行う。30

## 【0035】

アドレスデコーダ105はメモリの外部からの6ビットのアドレスを64本のワード線に復号する。

## 【0036】

アドレスデコーダ105はワード線WR0～WR63、WW0～WW63へ信号を出力し、これが電源制御回路106へ入力され、メモリセルアレイ102の電源線V0～V63を制御する。電源線には所定の電源電圧が印加される。

## 【0037】

ワード線WR0～WR63、WW0～WW63はアドレスデコーダ105からの出力信号によって、それぞれ、読み出し用と書き込み用のワード線として機能することができる。すなわち書き込み時には、WW0～WW63の一つが高電位側の状態（以下、「HIGHレベル」と記す）となり、読み出し時にはWR0～WR63の一つがHIGHレベルとなる。例えばアドレスが00で読み出しの場合は、WR0のみがHIGHレベルになり、アドレスが63で書き込みの場合はWW63のみがHIGHレベルとなる。40

## 【0038】

BR0～BR7、BW0～BW7はそれぞれ読み出し用と書き込み用のビット線である。読み出し時にはアドレスによって選択された8ビットのメモリセルの値がBR0～BR7に入力され、書き込み時には外部からのデータがBW0～BW7に入力される。

## 【0039】

このようなSRAMメモリによって、8ビット×64＝512ビット分の情報を記憶する50

ことができる。

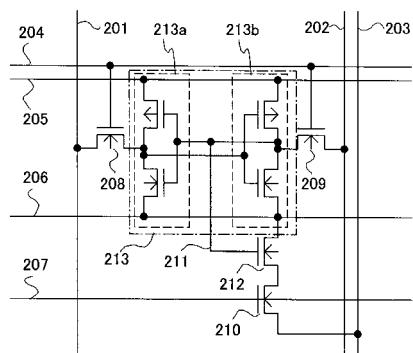

**【0040】**

次にメモリセル104の構成例を示す。なお本実施例では、読み出し期間及び書き込み期間において電源電圧として5V、保持する期間において電源電圧として3Vを供給する場合について説明するが、この値に限定されるものではない。

**【0041】**

図2に示すメモリセル104は、書き込み時のデータ線201、202、データ線203、書き込み時のワード線204、電源線205、グランド線206、読み出し時のワード線207、Nチャネル型トランジスタ208、209、210、212、ノード211、インバーター回路213を有する。

10

**【0042】**

インバーター回路213は、2つのインバーター回路213a、213bを有し、互いに入力端子と出力端子がそれぞれ接続される。インバーター回路213が有するインバータ回路213a、213bの一方の電極は電源線205に接続され、他方の電極はグランド線206に接続される。トランジスタ208のゲート電極及びトランジスタ209のゲート電極は、ワード線204に接続される。トランジスタ208の一方の電極はデータ線201に接続され、他方の電極はインバーター回路213内の一つのインバーター回路213aの出力端子に接続される。トランジスタ209のゲート電極は、ワード線204に接続され、一方の電極はデータ線202に接続され、他方の電極はインバーター回路213内の一つのインバーター回路213bの出力端子に接続される。トランジスタ212のゲート電極は、ノード211に接続され、一方の電極はグランド線206に接続され、他方の電極はトランジスタ210の一方の電極に接続される。トランジスタ210のゲート電極は、ワード線207に接続され、他方の電極はデータ線203に接続される。

20

**【0043】**

書き込み時のデータ線201には書き込み値である正転の値が、書き込み時のデータ線202には反転の値が入力される。読み出し時のデータ線203には、読み出し時以外ではメモリセルが1を保持している場合は正転の値の書き込みが行われ、0を保持している場合は反転の値の書き込みが行われ、読み出し回路101によって5Vにプリチャージされる。

**【0044】**

30

書き込み時、ワード線204が5Vであり、トランジスタ208、209がオンになることにより、メモリセルに値を書き込むことができる。

**【0045】**

読み出し時、ワード線207がHIGHレベルであり、トランジスタ210がオンになる。メモリセルの値が0の場合、ノード211の電圧が5Vでありトランジスタ212がオンになり、プリチャージされたデータ線203はトランジスタ210、212により電圧が0Vとなる。メモリセルの値が1の場合、データ線203はトランジスタ212がオンにならない事から、プリチャージされた5Vのまま保持される。

**【0046】**

このようにメモリセルは書き込み時、読み出し時には装置全体の電源電圧と同じ電圧を必要とするが、書き込み、読み出し以外であって、書き込まれた値を保持する期間は、インバーター回路のみがLSIのシステムから電気的に切り離された状態で値を保持している。すなわち、値を保持する期間は、メモリセルの外部との信号のやりとりがなくインバーター回路213内の2個のインバーター回路が動作すればよい。メモリセルに値が一度書き込まれると、インバーター回路213の4個のトランジスタのうち、オン状態のトランジスタが2個、オフ状態のトランジスタが2個になるが、電源線205からグランド線206に流れるメモリセルのリーク電流の大きさはこの2つのオフ状態のトランジスタによって決定される。従来のメモリセルでは値を保持する期間も5Vの電圧が供給されていたが、本発明により保持する期間は3Vの電圧が供給される。オフ状態のトランジスタのリーク電流は電源電圧を低くすることにより小さくなる。その結果、メモリ素子の低消費電

40

50

力化を図ることができる。このような動作を行うために電源制御回路 106 を設ける。

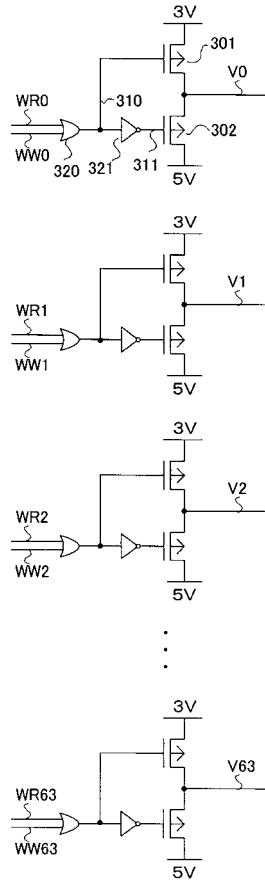

#### 【0047】

次に、電源制御回路 106 の構成例及びその動作について示す。図 3 に示すように電源制御回路 106 は、OR320、インバーター回路 321、Pチャネル型トランジスタ 301、302、ワード線 WR0 ~ WR63、WW0 ~ WW63 を有する。OR320 の変わりに、NOR とインバーター回路、又は 2 つのインバーター回路と NAND を用いることもできる。すなわち、2 つの入力端子と一つの出力端子を有し、いずれか一方の入力端子に高電位側の信号が入力されると HIGH レベルが出力され、両方の入力端子に低電位側の信号（以下、「LOW レベル」と記す）が入力されると LOW レベルが出力される機能を奏する回路であればよい。なお、ここで、2 つの入力端子はそれぞれワード線 WR0 又は WW0 と接続されており、出力端子はインバーター回路の入力端子と接続されている。

10

#### 【0048】

OR320 の入力端子にはワード線 WR0 ~ WR63、WW0 ~ WW63 が接続され、出力端子にはトランジスタ 301 のゲート電極及びインバーター回路 321 の入力端子が接続される。インバーター回路 321 の出力端子にはトランジスタ 302 のゲート電極が接続される。トランジスタ 301 の一方の電極と、トランジスタ 302 の一方の電極とは接続され、さらに電源線 V0 に接続される。

#### 【0049】

このような電源制御回路 106 はアドレスデコーダ 105 のワード線からの出力を入力とし、それぞれのラインのワード線 WR と WW を OR の入力端子とし、OR の出力によって、該当するアドレスが読み出しか書き込み時には電源電圧 5V をラインに供給し、それ以外の時には 3V を供給する。例えばアドレス 00 の読み出し時には、WR0 が 1 になりノード 311 が LOW レベルになりノード 310 が HIGH レベルになるため、トランジスタ 302 がオンになり電源線 V0 には 5V が供給される。他のアドレスの電源電圧は、3V に接続されるトランジスタ 301 がオンになり、3V が電源線 V1 ~ V63 に供給されることになる。つまり、例えば、メモリセルに値を書き込む期間では、ワード線 WR0 が HIGH レベルとなり、ワード線 WW0 が LOW レベルとなり、トランジスタ 302 がオンとなり、トランジスタ 301 に接続された電源線に第 1 の電圧が与えられる。そして、メモリセルに書き込まれた値を保持する期間では、ワード線 WR0 及びワード線 WW0 が LOW レベルとなり、トランジスタ 301 がオンとなり、電源線には前記第 1 の電圧より低い電圧が与えられる。そして、メモリセルに書き込まれた値を読み出す期間では、ワード線 WR0 が LOW レベルとなり、ワード線 WW0 が HIGH レベルとなり、トランジスタ 302 がオンとなり、トランジスタ 301 に接続された電源線に第 1 の電圧が与えられる。ここで、トランジスタ 301、302 は、メモリセルに第 1 の電圧又は第 1 の電圧より低い第 2 の電圧を供給する手段に相当する。

20

30

#### 【0050】

このように本発明を用いることにより保持する期間は 3V の電圧が供給されるため、保持する期間も 5V の電圧が供給されていた従来のメモリセルと比べてメモリ素子の低消費電力化を図ることができる。つまり、本発明により、書き込み又は読み出しを行う期間に電源線に供給される電圧に比べて、値を保持する期間に電源線に供給される電圧を低くすることが可能となるため、メモリセルの低消費電力化を図ることができる。

40

#### 【0051】

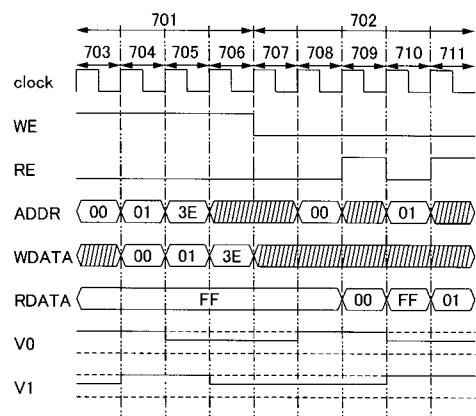

##### (実施例 2)

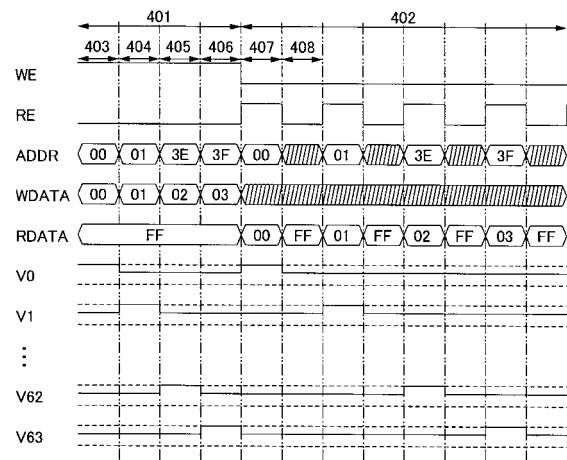

本実施例では、実施例 1 の場合における本発明の SRAM メモリの動作を、タイミングチャートを用いて説明する。

#### 【0052】

本発明の SRAM メモリのタイミングチャートを図 4 に示す。本発明の SRAM の信号は、書き込み期間を示すための信号：WE (write enable)，読み出し期間を示すための信号：RE (read enable)，書き込み期間に SRAM に書き込むデータバスの信号：W DATA (write date)，読み出し期間に

50

S R A M のデータが読み出されるデータバスの信号：R D A T A ( r e a d d a t a ) , 書き込み又は読み出しを行うアドレスバスの信号：A D D R ( r e a d o r w r i t e a d d r e s s ) , 電源線V 0 ~ V 6 3 へ入力される信号を有する。W E は1の時にメモリが書き込み期間であると判断し外部からの書き込みデータをアドレスのラインに書き込む動作を行い、0の時には書き込みの動作はしない。

#### 【 0 0 5 3 】

W E はS R A M に値を書き込む時にH I G H レベルになり、それ以外ではL O W レベルになる。R E はS R A M から値を読み出す時にH I G H レベルになり、それ以外ではL O W レベルになる。またR E は図2のデータ線2 0 3 をプリチャージするタイミングに用いることができ、読み出し時以外のタイミングで書き込み、読み出し回路1 0 1 によってデータ線2 0 3 がプリチャージされる。

10

#### 【 0 0 5 4 】

W D A T A は8ビットのバスで、書き込み時にS R A M に書き込まれる値が入力される。R D A T A は8ビットのバスで、読み出し時にS R A M から読み出された値が入力される。A D D R は6ビットのバスで、書き込み、又は読み出しするアドレスが入力される。入力されたアドレスは、デコーダ1 0 5 によって64ビットの読み出しづード線、書き込みワード線に復号される。電源線V 0 ~ V 6 3 として示すパルス信号は、それぞれアドレス0 ~ アドレス6 3 に供給される電源電圧である。

#### 【 0 0 5 5 】

期間4 0 1 はW E がH I G H レベルになりS R A M に書き込みを行う期間であり、期間4 0 2 はR E がH I G H レベルになり読み出しを行う期間である。

20

#### 【 0 0 5 6 】

期間4 0 3 は、A D D R バスに入力されたアドレス0 0 にW D A T A バスに入力されたデータ0 0 を書き込む動作を行う。このとき、アドレス0 0 に供給される電源線V 0 の電圧は5 V になり、それ以外のアドレスの電源線V 1 ~ V 6 3 の電圧は3 V となる。同様に期間4 0 4 はアドレス0 1 にデータを書き込む期間であり、アドレス0 1 のメモリセルに供給される電源線V 1 にのみ5 V が供給され、他の電源線V 0 、V 2 ~ V 6 3 には3 V が供給される。期間4 0 5 、期間4 0 6 も同様にそれぞれアドレス6 2 、アドレス6 3 の電源線V 6 2 、V 6 3 にのみ5 V が供給され、他のアドレスには3 V が供給される。

#### 【 0 0 5 7 】

30

期間4 0 7 は、A D D R バスに入力されたアドレス0 0 からデータが読み出されR D A T A バスにその値0 0 が入力される。このとき、アドレス0 0 のメモリセルの電源線V 0 には5 V が供給され、それ以外のアドレスの電源電圧V 1 ~ V 6 3 は3 V が供給される。

#### 【 0 0 5 8 】

期間4 0 8 は、S R A M の読み出しのデータバスR D A T A をH I G H レベルにプリチャージする期間である。実施例1で示したS R A M の構成の場合、S R A M のメモリセルがデータバスをH I G H レベルとすることが出来ないため、R E をL O W レベルにして書き込み、読み出し回路1 0 1 によってプリチャージする必要がある。よって読み出し期間4 0 2 ではあるアドレスから値を読み出し、次に違うアドレスのデータを読み出す場合、R E がL O W レベルの期間が必要となる。このようにW E がL O W レベルで、かつR E もL O W レベルの期間では、S R A M のメモリセルに供給されるすべての電源線V 0 ~ V 6 3 に3 V が供給される。この期間は、書き込まれた値を保持する期間となる。

40

#### 【 0 0 5 9 】

このような本発明により値を保持する期間は3 V の電圧が供給され、メモリセルでは値を保持する期間も5 V の電圧が供給されていた従来と比べてメモリ素子の低消費電力化を図ることができる。

#### 【 0 0 6 0 】

( 実施例3 )

実施例1で示した電源制御回路1 0 6 の構成の場合、S R A M メモリから書き込み又は読み出しを行うのと同じタイミングでその動作に必要な電源が供給される。しかし、この形

50

態だと電源の供給が間に合わず、S R A Mメモリの動作速度が遅くなる事が予想される。そこで本実施例では、必要なタイミングよりも前のタイミングで電源電圧を供給するS R A Mメモリの構成を示す。

**【 0 0 6 1 】**

本実施例のS R A Mメモリの構成を図5に示す。

**【 0 0 6 2 】**

本実施例のS R A Mメモリの構成では、アドレスがデータバス等に対して1つ前のタイミングで入力される。アドレスデコーダ5 0 1はアドレスの入力を復号する。復号された書き込みと読み出しのワード線を電源制御回路5 0 2が受信する。

**【 0 0 6 3 】**

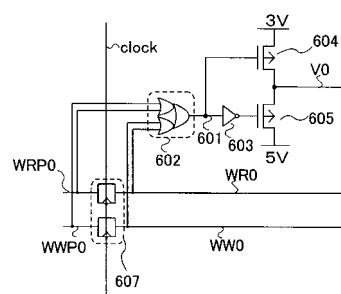

本実施例のS R A Mメモリにおける電源制御回路5 0 2の構成を図6に示す。

**【 0 0 6 4 】**

電源制御回路5 0 2は、読み出しのワード線W W P 0 ~ W W P 6 3、書き込みのワード線W R P 0 ~ W R P 6 3、4入力を有するO R 6 0 2、インバーター回路6 0 3、Pチャネル型トランジスタ6 0 4、6 0 5、フリップフロップ6 0 7を有する。

**【 0 0 6 5 】**

フリップフロップ6 0 7にはクロックが入力され、それぞれの出力端子と、O R 6 0 2の入力端子が接続される。O R 6 0 2の出力端子は、インバーター回路6 0 3の入力端子及びトランジスタ6 0 4のゲート電極に接続される。インバーター回路6 0 3の出力端子は、トランジスタ6 0 5のゲート電極に接続される。トランジスタ6 0 4の一方の電極と、トランジスタ6 0 5の一方の電極は接続され、電源線V 0と接続される。

**【 0 0 6 6 】**

このような電源制御回路5 0 2は、デコーダ5 0 1から信号入力された読み出しのワード線W W P 0 ~ W W P 6 3、書き込みのワード線W R P 0 ~ W R P 6 3を、その内部のフリップフロップ6 0 7を通し1クロック遅らせて書き込みのワード線W W 0 ~ W W 6 3、読み出しのワード線W R 0 ~ W R 6 3を信号出力する。

**【 0 0 6 7 】**

W W P 0又はW R P 0がH I G Hレベルになった場合、ノード6 0 1がH I G Hレベルになりアドレス0 0の電源線V 0には5 Vが供給される。又、W W P 0、W R P 0はフリップフロップを通りW W 0、W R 0となり、W W P 0又はW R P 0がH I G Hレベルの場合、1クロック後のタイミングでW W 0、W R 0がH I G Hレベルになりノード6 0 1がH I G Hレベルになりアドレス0 0の電源線V 0には5 Vが供給される。このようにして、読み出し、書き込みを行う1クロック前のタイミングから5 Vの電源を供給することが可能となる。その結果、電源の供給が間に合わず、S R A Mメモリの動作速度が遅くなることがない。

**【 0 0 6 8 】**

(実施例4)

本実施例では、電源制御回路5 0 2のタイミングチャートを図7に示す。

**【 0 0 6 9 】**

期間7 0 1は書き込みを行う期間であり、期間7 0 2は読み出しを行う期間である。期間7 0 3では、アドレスバスA D D Rに0 0が入力され電源線V 0に5 Vが供給され、電源線V 0以外の電源線には3 Vが供給される。期間7 0 3において、電源制御回路内でW W P 0はフリップフロップを通り、期間7 0 4で書き込みのワード線W W 0がH I G Hレベルとなり、W D A T Aバスの値0 0が書き込まれる。またW W 0がH I G Hレベルとなることにより、電源線V 0には引き続き5 Vが供給される。また7 0 4の期間でアドレスバスA D D Rに0 1が入力されV 1に5 Vが供給される。

**【 0 0 7 0 】**

期間7 0 5では、電源線V 0に3 Vが供給され、V 1には引き続き5 Vが供給される。又アドレス0 1にW D A T Aバスの値0 1が書き込まれる。

**【 0 0 7 1 】**

10

20

30

40

50

期間 708 では、RDATA が書き込み、読み出し回路によってプリチャージされると共に、アドレス 00 の電源線 V0 に 5V が供給され始める。期間 709 でも電源線 V0 には引き続き 5V が供給され、RDATA バスにはアドレス 00 の値 00 が入力される。期間 710 では、アドレス 01 の電源電圧 V1 に 5V が供給され始める。期間 711 でも V1 には 5V が供給され、RDATA バスにはアドレス 01 の値 01 が入力される。

#### 【0072】

##### (実施例 5)

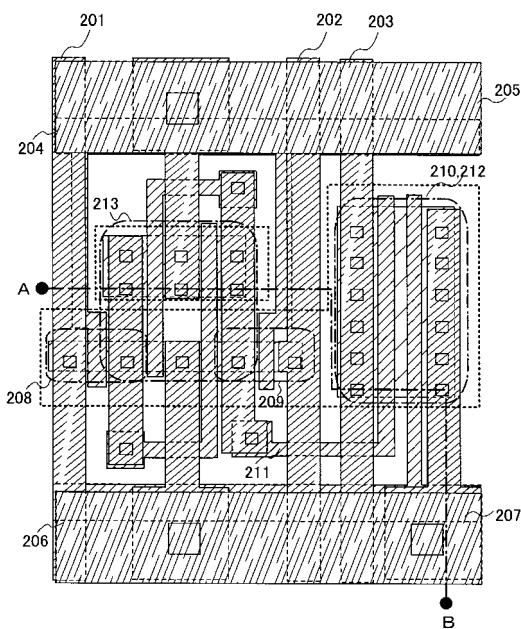

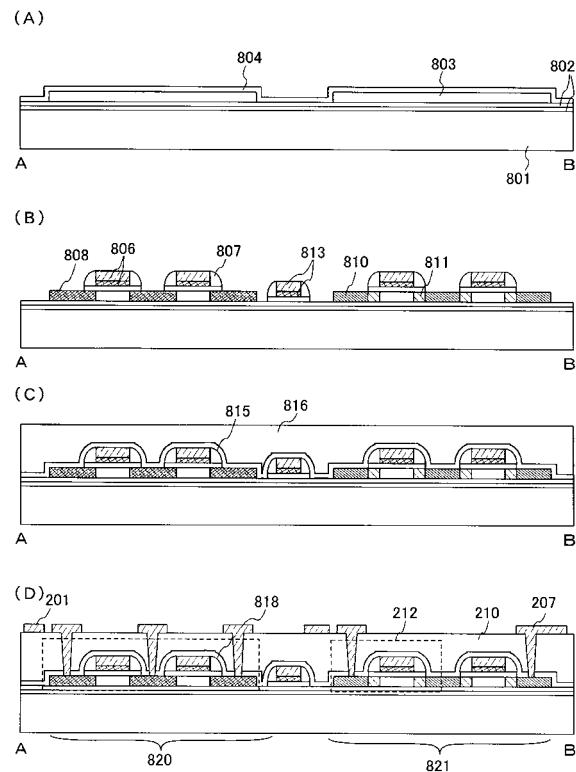

本実施例では、本発明のメモリセルの上面図及びその断面図の構成例について説明する。なお、本実施例ではトランジスタに薄膜トランジスタ（TFT）を用いる。

#### 【0073】

図 8 には、図 2 の回路図に対応するメモリセルの上面図を示す。メモリセル 104 は、書き込み時のデータ線 201、202、データ線 203、書き込み時のワード線 204、電源線 205、グランド線 206、読み出し時のワード線 207、N チャネル型 TFT 208、209、210、212、ノード 211、インバーター回路 213 を有する。そして N チャネル型 TFT 208、209 は同一の半導体層からなり、N チャネル型 TFT 210、212 は同一の半導体層からなり、インバーター回路 213 が有する P チャネル型 TFT は同一の半導体層からなる。N チャネル型 TFT 210、212 はチャネル幅が広く成るように設けられている。読み出し線 203 には大きな容量がつくため、これを既定の動作速度で 0V に落とすためには、チャネル幅の広いトランジスタを設けるとよい。またインバーター回路 213 内の P チャネル型 TFT は、N チャネル型 TFT よりもチャネル幅が広くなるように設けられている。これは P チャネル型 TFT の移動度を高くするためである。

#### 【0074】

これら半導体層上にはゲート電極及びゲート配線が設けられている。N チャネル型 TFT 210、212 が直列となるように設けられており、一方のゲート電極はノード 211 となり、他方のゲート電極はワード線 207 となる。インバーター回路 213 内の N チャネル型 TFT のゲート電極と、P チャネル型 TFT のゲート電極は接続されるため、同一ゲート電極となる。

#### 【0075】

ゲート電極及び半導体層上に、ソース電極、ドレイン電極及び配線が設けられている。ソース電極、ドレイン電極及び配線の線幅は、ゲート電極及びゲート配線の線幅より広く設けられている。ワード線 204 と、電源線 205 は、インバーター回路 213 を介して配置される。ソース電極、ドレイン電極及び配線と、半導体層又はゲート配線等とを接続するため、これらの間に設けられる絶縁層にコンタクトホール（四角で示す）が設けられている。コンタクトホールの数を増やす又はその面積を広くすることにより、接触不良を低減することができる。

#### 【0076】

ソース電極、ドレイン電極及び配線上に、配線が設けられている。配線は、グランド線 206、ワード線 207 となり、ソース電極、ドレイン電極及び配線の線幅より広くなるように設けられている。線幅の広いグランド線 206、ワード線 207 によって、電圧降下を抑えることができる。配線と、ゲート配線又配線とを接続するため、これらの間に設けられる絶縁層にコンタクトホール（四角で示す）が設けられている。

#### 【0077】

次に、図 8 における A - B 間の断面図を参照しながら、メモリセルの作製工程について説明する。

#### 【0078】

図 9 (A) には、絶縁表面を有する基板（絶縁基板）801 を用意する。絶縁基板とは、ガラス基板、石英基板、プラスチック基板等が挙げられる。また、これら基板において、その裏面を研磨する等の手法によって薄くすることができる。さらに、金属元素等の導電性基板や、シリコン等の半導体性基板上に絶縁性を有する材料を用いて層を形成した基板

10

20

30

40

50

を用いることも可能である。メモリセルを、例えばプラスチック基板に形成することにより、柔軟性が高く、軽量で薄型な装置を作製することができる。

#### 【0079】

絶縁基板801上に下地層802を形成する。下地層802は、酸化珪素、窒化珪素、または酸化窒化珪素等の絶縁性を有する材料を用い、単層構造または積層構造で形成することができる。本実施例では、下地層802として2層構造を用いる場合を説明する。下地層802の一層目として、膜厚10nm以上200nm以下(好ましくは50nm以上100nm以下)の酸化窒化珪素層を形成する。当該酸化窒化珪素層は、プラズマCVD法を用い、SiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>O及びH<sub>2</sub>を反応ガスとして形成することができる。次いで下地層802の2層目として、膜厚50nm以上200nm以下(好ましくは100nm以上150nm以下)の酸化窒化珪素層を形成する。当該酸化窒化珪素層は、プラズマCVD法を用い、SiH<sub>4</sub>及びN<sub>2</sub>Oを反応ガスとして形成することができる。10

#### 【0080】

下地層802上に半導体層を形成する。半導体層は、珪素を有する材料から形成することができる。半導体層の状態は、非晶質状態、結晶状態、微結晶状態のいずれとすることもできる。結晶状態を有すると、TFTの移動度を高めることができ好ましい。

#### 【0081】

結晶状態の半導体層を形成するには、非晶質半導体層に対して加熱処理を行う手法がある。加熱処理には、レーザ照射、加熱炉、ランプ照射等が挙げられ、これらのいずれか一又は複数を用いることができる。20

#### 【0082】

レーザ照射には、連続発振型のレーザビーム(CWレーザ)やパルス発振型のレーザビーム(パルスレーザ)を用いることができる。レーザビームとしては、Arレーザ、Krレーザ、エキシマレーザ、YAGレーザ、Y<sub>2</sub>O<sub>3</sub>レーザ、YVO<sub>4</sub>レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、ガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、Ti:サファイヤレーザ、銅蒸気レーザまたは金蒸気レーザのうち一種または複数種から発振されるものを用いることができる。このようなレーザビームの基本波と、当該基本波の第2高調波から第4高調波といった高調波のレーザビームのいずれかを照射することで、粒径の大きな結晶を有するシリコン層を得ることができる。高調波には、Nd:YVO<sub>4</sub>レーザ(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を用いることができる。レーザ照射におけるエネルギー密度は0.01~100MW/cm<sup>2</sup>程度(好ましくは0.1~10MW/cm<sup>2</sup>)が必要である。そして、走査速度を10~2000cm/sec程度として照射する。30

#### 【0083】

なお、基本波のCWレーザと高調波のCWレーザとを照射するようにしてもよいし、基本波のCWレーザと高調波のパルスレーザとを照射するようにしてもよい。複数のレーザ光を照射することにより、広範囲のエネルギー領域を補うことができる。

#### 【0084】

また、パルスレーザであって、非晶質状態を有するシリコン層がレーザによって溶融してから固化するまでに、次のパルスのレーザを照射できるような発振周波数でレーザを発振させるレーザビームを用いることもできる。このような周波数でレーザを発振させることで、走査方向に向かって連続的に成長した結晶粒を有するシリコン層を得ることができる。このようなレーザの発振周波数は10MHz以上であり、通常用いられている数十Hz~数百Hzの周波数帯よりも著しく高い。40

#### 【0085】

加熱処理として加熱炉を用いる場合には、非晶質状態を有する半導体層を400~550で2~20時間かけて加熱する。このとき、徐々に高温となるように温度を400~550の範囲で多段階に設定するとよい。最初の400程度の低温加熱工程により、非晶質状態を有する半導体層に含まれる水素等が出てくるため、結晶化の際に層表面が荒れるのを低減することができる。50

**【0086】**

上記加熱処理の工程において、半導体層の結晶化を促進させる金属、例えばニッケル(Ni)を添加する。例えば、非晶質状態を有する珪素層上にニッケルを含む溶液を塗布し、加熱処理を行うことができる。このように金属を用いて加熱処理を行うことで、加熱温度を低減することができ、さらに、結晶粒界の連続した多結晶珪素層を得ることができる。ここで結晶化を促進するための金属としてはNiの他に、鉄(Fe)、ルチニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)、白金(Plt)、銅(Cu)、銀(Au)等を用いることもできる。

**【0087】**

結晶化を促進させる金属はメモリセル等の汚染源となるため、半導体層を結晶化した後に10、金属を除去するゲッタリング工程を行うことが望ましい。ゲッタリング工程では、半導体層を結晶化した後、半導体層上にゲッタリングシンクとなる層を形成し、加熱することで金属をゲッタリングシンクへ移動させる。ゲッタリングシンクには、多結晶半導体層や不純物が添加された半導体層を用いることができる。例えば、多結晶珪素層上にアルゴン等の不活性元素が添加された多結晶半導体層を形成し、これをゲッタリングシンクとして用いることができる。ゲッタリングシンクに不活性元素を添加することによって、ひずみを生じさせ、より効率的に金属を捕獲することができる。また新たにゲッタリングシンクを形成することなく、TFTの半導体層の一部にリン等の元素を添加することによって、金属を捕獲することもできる。

**【0088】**

20このように形成された半導体層を、所定の形状に加工し、島状の半導体層803を形成する。加工手段には、フォトリソグラフィ法によって形成されたマスクを用いて、エッチングする。エッチングには、ウェットエッチング法又はドライエッチング法を適用することができる。

**【0089】**

半導体層803を覆うようにゲート絶縁層804として機能する絶縁層を形成する。ゲート絶縁層804は、下地層802と同様の材料、方法により形成することができる。

**【0090】**

図9(B)に示すように、ゲート絶縁層804上にゲート電極及びゲート配線として機能する導電層を形成する。導電層はアルミニウム(Al)、チタン(Ti)、モリブデン(Mo)、タンタル(Ta)、タンゲステン(W)もしくはシリコン(Si)の元素からなる膜又はこれらの元素を有する合金膜を用いることができる。導電層は、単層構造又は積層構造とすることが可能、積層構造として窒化タンタルとタンゲステンの積層構造を適用することができる。導電層を所定の形状に加工し、積層構造を有するゲート電極806、ゲート配線813を形成することができる。加工手段には、フォトリソグラフィ法によって形成されたマスクを用いて、エッチングする。エッチングには、ウェットエッチング法又はドライエッチング法を適用することができる。

**【0091】**

ゲート電極806の側面には、サイドウォール807と呼ばれる絶縁物を形成する。サイドウォール807は、下地層802と同様の材料、方法により形成することができる。またサイドウォール807の端部をテーパ形状にするためには、等方性エッチングを用いればよい。サイドウォールにより、ゲート長が狭くなるにつれて生じる短チャネル効果を防止することができる。短チャネル効果はNチャネル型TFTに顕著であるため、少なくともNチャネル型TFTのゲート電極側面に設けるとよい。またゲート配線にも、同様にサイドウォールを形成してもかまわない。

**【0092】**

この状態で、ゲート電極806及びサイドウォール807を用いて、半導体層803に不純物元素を添加する。Nチャネル型TFTとする場合、不純物元素はリン(P)を用い、Pチャネル型TFTとする場合、不純物元素はボロン(B)を用いることができる。不純物元素が添加されると半導体層803に不純物領域が形成される。不純物領域には、高濃

10

20

30

40

50

度不純物領域 808、810、及びサイドウォール 807 下方の低濃度不純物領域 809、811 が形成される。

#### 【0093】

不純物添加後、必要に応じて加熱処理を行い、不純物元素の活性化及び半導体層の表面改善を図ることができる。加熱処理には、結晶化と同様な手法を用いることができる。

#### 【0094】

図 9 (C) に示すように、半導体層やゲート電極を覆って、層間膜として機能する絶縁層 815、816 を形成する。層間膜は、単層構造又は積層構造とすることができます、本実施例では積層構造を示す。層間膜には、無機材料又は有機材料を用いることができる。無機材料は、酸化珪素、窒化珪素、酸化窒化珪素等を用いることができる。有機材料はポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテン、シリコサン、ポリシラザンを用いることができる。なお、シリコサンとは、シリコン (Si) と酸素 (O) の結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基（例えばアルキル基、芳香族炭化水素）が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。ポリシラザンは、シリコン (Si) と窒素 (N) の結合を有するポリマー材料を出発原料として形成される。無機材料を用いると不純物元素の侵入を防止することができ、有機材料を用いると平坦性を高めることができる。そのため、本実施例では、絶縁層 815 に無機材料を用い、絶縁層 816 に有機材料を用いる。

#### 【0095】

図 9 (D) に示すように、絶縁層 816、815 を貫通するコンタクトホールを形成し、コンタクトホールを充填するように配線 818 を形成する。配線 818 は、アルミニウム (Al)、チタン (Ti)、モリブデン (Mo)、タンタル (Ta)、タンゲステン (W) もしくはシリコン (Si) の元素からなる膜又はこれらの元素を有する合金膜を用いることができる。配線 818 は、単層構造又は積層構造を用いることができ、例えば第 1 層にタンゲステン、窒化タンゲステン等を用い、第 2 層にアルミニウムとシリコンの合金 (Al-Si)、アルミニウムとチタンの合金 (Al-Ti) を用い、第 3 層に窒化チタン膜、チタン膜等を順次積層した構造を適用することができる。配線 818 の加工には、フォトリソグラフィ法で形成されたマスクを用いた、エッチング法がある。エッチング法には、ウェットエッチング法又はドライエッチング法を適用することができる。配線 818 は、半導体層 803 では不純物領域に接続し、このような配線をソース電極、ドレイン電極と呼ぶことができる。

#### 【0096】

このようにして P チャネル型 TFT 820、N チャネル型 TFT 821 を形成することができる。なお N チャネル型 TFT 821 は、それぞれトランジスタ 210、212 に相当し、配線 818 の一部はデータ線 201、ワード線 207 に相当する。

#### 【0097】

このようにして本発明のメモリセルは絶縁基板上の TFT を用いて形成することができる。勿論本発明のメモリセルはこれに限定されるものではなく、シリコンウェハを用いたトランジスタによっても形成することができる。但し、絶縁基板上に形成することによって安価なメモリセル、さらにはこれを有する装置を提供することができる。

#### 【0098】

##### (実施例 6)

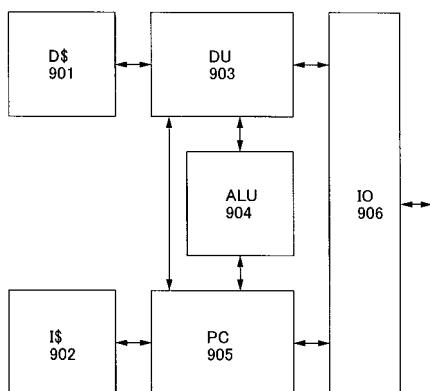

本発明の SRAM は、CPU に適用することができる。本実施例では、本発明の SRAM を搭載した CPU の構成について説明する。CPU の簡単な構成を図 10 に示す。

#### 【0099】

CPU は、D\$ ブロック（データキャッシュ）901、I\$ ブロック（インストラクションキャッシュ）902、DU ブロック（データユニット）903、ALU ブロック（Arithmetic Logic Unit, 算術論理演算回路）904、PC ブロック（プログラムカウンター）905、IO (In Out) ブロック 906 を有する。

**【0100】**

D \$ 901 は最近アクセスされたアドレスのデータを一時的に保持しそのアドレスのデータに高速でアクセス出来るようにする機能を有するものである。I \$ 902 は最近アクセスされたアドレスの命令を一時的に保持しそのアドレスの命令に高速でアクセス出来るようする機能を有するものである。D U 903 はストア又はロード命令が実行された時、D \$ にアクセスするか、I O にアクセスするかを決定する機能を有するものである。

A L U 904 は算術論理演算回路であり、四則演算、比較演算、論理演算などを行う機能を有するものである。P C 905 は、現在実行中の命令のアドレスを保持し、その実行終了後、次の命令をフェッチする機能を有する。又、次の命令をフェッチする時にI \$ にアクセスするか、I O にアクセスするかを決定する機能を有するものである。I O 906 は D U 、P C からのアクセスを受け外部とデータの送受信を行う機能を有するものである。

以下にそれぞれの関係を説明する。

**【0101】**

P C 905 が命令をフェッチする時に、はじめにI \$ 902 にアクセスし、I \$ 902 に該当するアドレスの命令がない場合にI O 906 にアクセスする。これによって得られた命令はI \$ 902 に格納すると共に実行を行う。実行すべき命令が算術論理演算の場合は A L U 904 が演算を行う。実行すべき命令がストア又はロード命令の場合は、D U 903 が演算を行う。この際、D U 903 はまずD \$ 901 にアクセスし、該当するアドレスのデータがD \$ 901 にない場合にI O 906 にアクセスする。

**【0102】**

このようなC P Uにおいて、本発明のS R A Mは、D \$ 901 とI \$ 902 、A L U 904 の内部に存在するG P Rに適用することができる。その結果、低消費電力化を達成したC P Uを提供することができる。

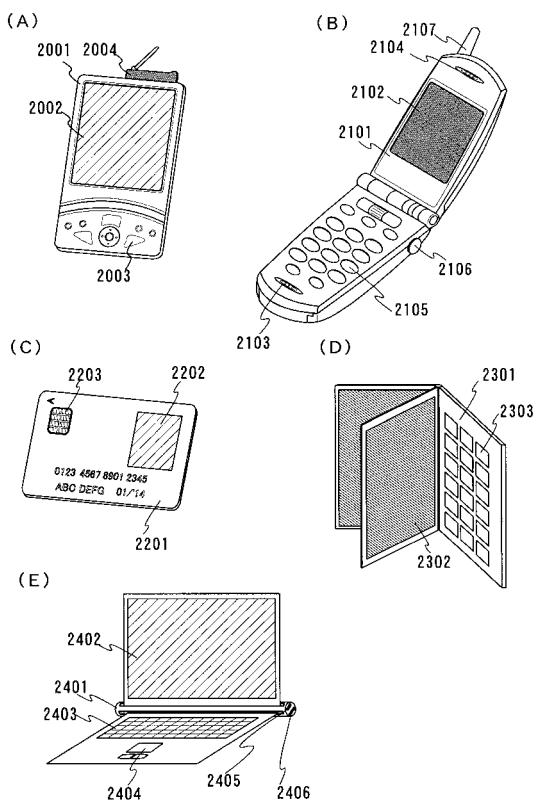

**【0103】****(実施例7)**

本発明のS R A Mを実装しうる半導体装置として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはD V D : D i g i t a l V e r s a t i l e D i s c 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。それら半導体装置の具体例を図11に示す。

**【0104】**

図11(A)は携帯情報端末(所謂P D A : P e r s o n a l D i g i t a l A s s i s t a n t )であり、本体2001、表示部2002、操作キー2003、モデム2004等を含み、本体2001が有するメモリ素子として本発明のS R A Mメモリが設けられている。本発明のS R A Mメモリにより、携帯情報端末の低コスト化を図ることができる。

**【0105】**

図11(B)は携帯電話機であり、本体2101、表示部2102、音声入力部2103、音声出力部2104、操作キー2105、外部接続ポート2106、アンテナ2107等を含み、本体2101が有するメモリ素子として本発明のS R A Mメモリが設けられている。本発明のS R A Mメモリにより、携帯電話機の低コスト化を図ることができる。

**【0106】**

図11(C)は電子カードであり、本体2201、表示部2202、接続端子2203等を含み、本体2201が有するメモリ素子として本発明のS R A Mメモリが設けられている。本発明のS R A Mメモリにより、電子カードの低コスト化を図ることができる。なお、図11(C)では接触型の電子カードを示しているが、非接触型の電子カードや、接触型と非接触型の機能を持ち合わせた電子カードにも、本発明のS R A Mメモリを用いることができる。

10

20

30

40

50

**【 0 1 0 7 】**

図11(D)は電子ブックであり、本体2301、表示部2302、操作キー2303等を含み、本体2301が有するメモリ素子として本発明のS R A Mメモリが設けられている。また電子ブックには、モデムが本体2301に内蔵されていてもよい。本発明のS R A Mメモリにより、電子ブックの低コスト化を図ることができる。

**【 0 1 0 8 】**

図11(E)はコンピュータであり、本体2401、表示部2402、キーボード2403、タッチパッド2404、外部接続ポート2405、電源プラグ2406等を含み、本体2401が有するメモリ素子として本発明のS R A Mメモリが設けられている。本発明のS R A Mメモリにより、コンピュータの低コスト化を図ることができる。

10

**【 0 1 0 9 】**

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の半導体装置に用いることが可能である。なお、本実施例の半導体装置は、実施の形態、実施例に示したいずれの構成及びその作製方法とも組み合わせて実施することができる。

**【図面の簡単な説明】****【 0 1 1 0 】**

【図1】本発明のS R A Mメモリ構成を示した図である

【図2】本発明のメモリセルの構成を示した回路図である

【図3】本発明の電源制御回路の構成を示した回路図である

【図4】本発明のS R A Mメモリのタイミングチャートである

20

【図5】本発明のS R A Mメモリ構成を示した図である

【図6】本発明の電源制御回路の構成を示した回路図である

【図7】本発明の電源制御回路のタイミングチャートである

【図8】本発明のメモリセルに対応する上面図である

【図9】本発明のメモリセルに対応する断面図である

【図10】本発明のS R A Mメモリを搭載しうるC P Uを示したブロック図である

【図11】本発明の電子機器を示した図である

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

## 【図 1 1】

---

フロントページの続き

(56)参考文献 特開2003-123479(JP,A)

特開2005-044456(JP,A)

特開平03-192595(JP,A)

特開平08-147978(JP,A)

特開2003-060077(JP,A)

特開2005-038557(JP,A)

特開2001-266580(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11 / 413

G 11 C 11 / 41

H 01 L 21 / 8244

H 01 L 27 / 11