(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2017-85424

(P2017-85424A)

(43) 公開日 平成29年5月18日(2017.5.18)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>H03K 7/08</b> (2006.01)  | H03K 7/08  | B 5H73O     |

| <b>H03F 3/345</b> (2006.01) | H03F 3/345 | B 5J50O     |

| <b>H02M 3/155</b> (2006.01) | H02M 3/155 | P           |

審査請求 未請求 請求項の数 7 O L (全 23 頁)

|           |                              |          |                                                     |

|-----------|------------------------------|----------|-----------------------------------------------------|

| (21) 出願番号 | 特願2015-213414 (P2015-213414) | (71) 出願人 | 395011665<br>株式会社オートネットワーク技術研究所<br>三重県四日市市西末広町1番14号 |

| (22) 出願日  | 平成27年10月29日 (2015.10.29)     | (71) 出願人 | 000183406<br>住友電装株式会社<br>三重県四日市市西末広町1番14号           |

|           |                              | (71) 出願人 | 000002130<br>住友電気工業株式会社<br>大阪府大阪市中央区北浜四丁目5番33号      |

|           |                              | (74) 代理人 | 100114557<br>弁理士 河野 英仁                              |

|           |                              | (74) 代理人 | 100078868<br>弁理士 河野 登夫                              |

最終頁に続く

(54) 【発明の名称】信号発生回路、電圧変換装置及びコンピュータプログラム

## (57) 【要約】

【課題】設定された値に応じたオン時間を持つ第1信号及び該第1信号とオン期間が重ならない第2信号を周期的に発生する発生部に設定する値の最小の増分を、比較的小さい処理負荷で実際の増分よりも実質的に小さくすることが可能な信号発生回路、電圧変換装置及びコンピュータプログラムを提供する。

【解決手段】CPU11は、発生部16が発生する第1信号のN周期毎に、目標の値Xに最も近い設定値Y及び2番目に近い設定値Zを特定し、特定したY及びZの大きさとXの大きさとを比較した結果により、Y及びZの中から第1信号のN個の設定値を決定して、第1信号の1周期毎に1つずつ発生部16に設定する。CPU11は、また、N周期の第1周期における第2信号のオフ時間を設定するための値を、同じN周期について決定した設定可能値のうち小さい方の設定可能値及び所定値の加算値として算出し、算出した値を発生部16に設定する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

設定された値に応じたオン時間有する第1信号及び該第1信号とオン期間が重ならない第2信号を周期的に発生する発生部と、所定の値に応じて前記発生部に設定可能な設定可能値を前記第1信号の1周期毎に設定する制御部とを備える信号発生回路において、

前記発生部は、前記第2信号のオフ時間を、前記第1信号のオン時間と同一の精度で設定可能であり、

前記制御部は、

前記第1信号のN周期（Nは2以上の自然数）毎に、前記所定の値に最も近い設定可能値及び2番目に近い設定可能値を特定する特定部と、

該特定部で特定した2つの設定可能値及び前記所定の値夫々の大きさに基づいて、前記2つの設定可能値の中からN個の設定可能値を決定する決定部と、

前記N周期の第1周期における前記第2信号のオフ時間を、前記決定部で決定した設定可能値のうち小さい方の設定可能値及び所定値の加算値により前記発生部に設定する設定部と

を有する

ことを特徴とする信号発生回路。

**【請求項 2】**

前記所定値は、前記第2信号のオフ時間を前記第1及び第2信号が共にオフになるべき時間に設定するための値よりも前記設定可能値の最小単位だけ大きい値であることを特徴とする請求項1に記載の信号発生回路。

**【請求項 3】**

前記決定部は、前記N個の設定可能値を、M個（Mは2～M～Nを満たす自然数）の設定可能値の平均的な値が前記所定の値に最も近くなるように順次決定することを特徴とする請求項1又は2に記載の信号発生回路。

**【請求項 4】**

前記決定部は、前記N個の設定可能値を、各設定可能値の平均的な値が、前記所定の値に最も近くなるように決定することを特徴とする請求項1又は2に記載の信号発生回路。

**【請求項 5】**

所定の値及びN個の設定可能値の対応関係を記憶する記憶部を備え、

該記憶部は、N個の設定可能値を、各設定可能値の平均的な値が、対応する所定の値に最も近くなるように予め決定して記憶してあり、

前記決定部は、前記所定の値に対応するN個の設定可能値を前記記憶部から読み出して決定する

ことを特徴とする請求項1又は2に記載の信号発生回路。

**【請求項 6】**

請求項1から5の何れか1項に記載の信号発生回路と、該信号発生回路が発生した第1信号のデューティに応じたスイッチングによって電圧を変換する電圧変換回路と、該電圧変換回路が変換した電圧を検出する検出部とを備える電圧変換装置であって、

前記信号発生回路が備える制御部は、前記検出部が検出した電圧に基づくPWM制御により、前記所定の値を算出する算出部を備えることを特徴とする電圧変換装置。

**【請求項 7】**

設定された値に応じたオン時間有する第1信号及び該第1信号とオン期間が重ならない第2信号を周期的に発生する発生部と、所定の値に応じて前記発生部に設定可能な設定可能値を前記第1信号の1周期毎に設定する制御部とを備える信号発生回路における前記制御部で実行可能なコンピュータプログラムにおいて、

前記制御部を、

前記第1信号のN周期（Nは2以上の自然数）毎に、前記所定の値に最も近い設定可能値及び2番目に近い設定可能値を特定する特定部、

該特定部で特定した2つの設定可能値及び前記所定の値夫々の大きさに基づいて、前記

2つの設定可能値の中からN個の設定可能値を決定する決定部、並びに

前記N周期の第1周期における前記第2信号のオフ時間を、前記決定部で決定した設定可能値のうち小さい方の設定可能値及び所定値の加算値により前記発生部に設定する設定部

として機能させることを特徴とするコンピュータプログラム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、設定された値に応じたオン時間を有する第1信号及び該第1信号とオン期間が重ならない第2信号を周期的に発生する発生部と、目標の値に応じて発生部に設定可能な値を設定する制御部とを備える信号発生回路、電圧変換装置及びコンピュータプログラムに関する。 10

【背景技術】

【0002】

従来、スイッチング素子をPWM信号で駆動することによって電圧を変換する電圧変換装置が広く利用されている。このPWM制御方式の電圧変換装置では、例えば電圧の目標値に基づいて電圧指令値を算出し、算出した電圧指令値に応じた値をPWM信号の発生部に設定することによって、設定された値に応じたデューティのPWM信号を発生する。このように、スイッチング素子を駆動するPWM信号のデューティを電圧の目標値に応じて変化させることにより、電圧の目標値に応じた出力電圧が得られる。 20

【0003】

PWM信号により駆動されるスイッチング素子がブリッジ接続されている場合、又はスイッチングに伴ってインダクタンスを有する回路に還流する電流を同期整流する場合には、直列的に接続された2つのスイッチング素子が同時にオンするタイミングが生じないようにするために、一方のスイッチング素子がオフしてから他のスイッチング素子がオンするまでの間に、所謂デッドタイムが設けられる。

【0004】

ここで、PWM信号の発生部に設定可能な値（以下、設定可能値という）の最小の増分（即ち最小単位）が比較的大きい場合は、目標値の変化に対してPWM信号のデューティを滑らかに変化させることができなくなり、出力電圧が階段状に変化することとなる。また例えば、PWM制御による操作量としてPWM信号の発生部に設定すべき目標の値が算出される場合、目標の値の最小の増分よりも設定可能値の最小の増分の方が大きいときは、目標値の変化及び負荷変動に対してPWM信号のデューティを滑らかに変化させることができなくなり、出力電圧に誤差が生じる。 30

【0005】

これに対し、特許文献1には、PWM信号のオン／オフ時間をPWM制御の1周期毎に演算する際に、電圧指令値を被除数とする除算の剰余を切り捨てて演算することによってオン／オフ時間を算出し、算出結果に基づいてPWMパルスを出力するPWMインバータが開示されている。上記の演算で生じた剰余は、オン／オフ時間に反映されずに切り捨てられた電圧指令値に相当する。 40

【0006】

このPWMインバータでは、切り捨てた剰余を次の周期以降の演算における電圧指令値に順次加算することにより、前回の演算でオン／オフ時間に反映されなかつた剰余が次の演算の際に新たなオン／オフ時間に反映され、その際の剰余が更に次の演算に反映されることが繰り返される。このため、PWM信号の発生部に対して設定されるオン／オフ時間の平均値を、本来設定されるべき目標のオン／オフ時間に近づけることができる。つまり、発生部に設定される値の最小の増分を、平均的には実際の増分よりも小さくすることができます。

【先行技術文献】

【特許文献】

**【0007】**

【特許文献1】特開平3-98470号公報

**【発明の概要】****【発明が解決しようとする課題】****【0008】**

しかしながら、特許文献1に開示された技術では、PWM制御の1周期毎に除算を含む演算を実行してPWM信号のオン／オフ時間を決定するため、1周期毎に多大な処理負荷が発生する。また、特許文献1では、上述のデッドタイムが考慮されていないため、一定のデッドタイムが確保されるようにするために、インバータ変換器部に含まれる少なくとも2つのスイッチング素子に対するPWM信号のオン時間を別々に算出する必要がある。このため、処理能力が低い安価なマイクロコンピュータでは、目標値の変化が比較的少ない場合であっても、上記の演算処理と通信等の他の処理とを並列的に、且つ安定的に実行することができない虞があった。

10

**【0009】**

本発明は斯かる事情に鑑みてなされたものであり、その目的とするところは、設定された値に応じたオン時間を有する第1信号及び該第1信号とオン期間が重ならない第2信号を周期的に発生する発生部に設定する値の最小の増分を、比較的小さい処理負荷で実際の増分よりも実質的に小さくすることが可能な信号発生回路、電圧変換装置及びコンピュータプログラムを提供することにある。

20

**【課題を解決するための手段】****【0010】**

本発明に係る信号発生回路は、設定された値に応じたオン時間を有する第1信号及び該第1信号とオン期間が重ならない第2信号を周期的に発生する発生部と、所定の値に応じて前記発生部に設定可能な設定可能値を前記第1信号の1周期毎に設定する制御部とを備える信号発生回路において、前記発生部は、前記第2信号のオフ時間を、前記第1信号のオン時間と同一の精度で設定可能であり、前記制御部は、前記第1信号のN周期（Nは2以上の自然数）毎に、前記所定の値に最も近い設定可能値及び2番目に近い設定可能値を特定する特定部と、該特定部で特定した2つの設定可能値及び前記所定の値夫々の大きさに基づいて、前記2つの設定可能値の中からN個の設定可能値を決定する決定部と、前記N周期の第1周期における前記第2信号のオフ時間を、前記決定部で決定した設定可能値のうち小さい方の設定可能値及び所定値の加算値により前記発生部に設定する設定部とを有することを特徴とする。

30

**【0011】**

本発明に係る信号発生回路は、前記所定値は、前記第2信号のオフ時間を前記第1及び第2信号が共にオフになるべき時間に設定するための値よりも前記設定可能値の最小単位だけ大きい値であることを特徴とする。

**【0012】**

本発明に係る信号発生回路は、前記決定部は、前記N個の設定可能値を、M個（Mは2M-Nを満たす自然数）の設定可能値の平均的な値が前記所定の値に最も近くなるように順次決定することを特徴とする。

40

**【0013】**

本発明に係る信号発生回路は、前記決定部は、前記N個の設定可能値を、各設定可能値の平均的な値が、前記所定の値に最も近くなるように決定することを特徴とする。

**【0014】**

本発明に係る信号発生回路は、所定の値及びN個の設定可能値の対応関係を記憶する記憶部を備え、該記憶部は、N個の設定可能値を、各設定可能値の平均的な値が、対応する所定の値に最も近くなるように予め決定して記憶しており、前記決定部は、前記所定の値に対応するN個の設定可能値を前記記憶部から読み出して決定することを特徴とする。

**【0015】**

本発明に係る電圧変換装置は、上述の信号発生回路と、該信号発生回路が発生した第1

50

信号のデューティに応じたスイッチングによって電圧を変換する電圧変換回路と、該電圧変換回路が変換した電圧を検出する検出部とを備える電圧変換装置であって、前記信号発生回路が備える制御部は、前記検出部が検出した電圧に基づく PWM 制御により、前記所定の値を算出する算出部を備えることを特徴とする。

#### 【 0 0 1 6 】

本発明に係るコンピュータプログラムは、設定された値に応じたオン時間を有する第 1 信号及び該第 1 信号とオン期間が重ならない第 2 信号を周期的に発生する発生部と、所定の値に応じて前記発生部に設定可能な設定可能値を前記第 1 信号の 1 周期毎に設定する制御部とを備える信号発生回路における前記制御部で実行可能なコンピュータプログラムにおいて、前記制御部を、前記第 1 信号の N 周期（N は 2 以上の自然数）毎に、前記所定の値に最も近い設定可能値及び 2 番目に近い設定可能値を特定する特定部、該特定部で特定した 2 つの設定可能値及び前記所定の値夫々の大きさに基づいて、前記 2 つの設定可能値の中から N 個の設定可能値を決定する決定部、並びに前記 N 周期の第 1 周期における前記第 2 信号のオフ時間を、前記決定部で決定した設定可能値のうち小さい方の設定可能値及び所定値の加算値により前記発生部に設定する設定部として機能させることを特徴とする。

10

#### 【 0 0 1 7 】

本発明にあっては、所定の値が、発生部に設定すべき目標の値であり、制御部は、目標の値に応じて発生部に設定可能な設定可能値を決定して設定し、発生部は、設定された設定可能値に応じたオン時間を有する第 1 信号と、該第 1 信号とはオン期間の重なりがない第 2 信号とを周期的に発生する。具体的に、制御部は、発生部が発生する第 1 信号の N 周期毎に、目標の値に最も近い設定可能値及び 2 番目に近い設定可能値を特定し、特定した 2 つの設定可能値の大きさと目標の値の大きさとを比較した結果により、特定した 2 つの設定可能値の中から N 個の設定可能値を決定して、第 1 信号の 1 周期毎に 1 つずつ発生部に設定する。制御部は、また、N 周期の第 1 周期における第 2 信号のオフ時間を設定するための値を、同じ N 周期について決定した設定可能値のうち小さい方の設定可能値及び所定値の加算値として算出し、算出した値を発生部に設定する。

20

これにより、制御部が決定する N 個の設定可能値について目標の値に最も近い設定可能値及び 2 番目に近い設定可能値の割合が適宜決定されるため、N 個の設定可能値の平均的な値が、設定可能値の最小の増分よりもきめ細かく調整される。また、第 2 信号のオフ時間の設定が N 周期に 1 回で済むため、制御部の処理負荷が低減される。

30

#### 【 0 0 1 8 】

本発明にあっては、第 2 信号のオフ時間を第 1 及び第 2 信号が共にオフになるべき時間に設定するための値よりも、第 1 信号の設定可能値の最小単位だけ大きい値を、上記の所定値とする。

これにより、N 周期内で第 1 信号のオン時間が変動した場合であっても、第 1 信号及び第 2 信号についてのデッドタイムが確保される。

#### 【 0 0 1 9 】

本発明にあっては、制御部は、目標の値に最も近い設定可能値を 1 個目の設定可能値と決定し、1 個目から M 個目（2 ≤ M ≤ N）までの設定可能値の平均的な値が目標の値に最も近くなるように、M 個目の設定可能値を決定することを N - 1 回だけ繰り返す。

40

これにより、信号の N 周期中のどの周期にあっても、第 1 周期からその周期までに発生部に設定された設定可能値の平均的な値が目標の値に最も近くなる。

#### 【 0 0 2 0 】

本発明にあっては、制御部は、N 個全ての設定可能値の平均的な値が目標の値に最も近くなるように N 個の設定可能値を決定する。

これにより、信号の N 周期全体について、発生部に設定された N 個の設定可能値の平均的な値が目標の値に最も近くなる。

#### 【 0 0 2 1 】

本発明にあっては、その平均的な値が目標の値に最も近くなるように予め算出された N

50

個の設定可能値と、目標の値との対応関係が記憶部に記憶されている。制御部は、目標の値に対応して発生部に設定すべきN個の設定可能値を記憶部から読み出して決定する。

これにより、目標の値に応じて決定すべきN個の設定可能値が、制御部による制御の実行時に容易に決定される。

#### 【0022】

本発明にあっては、上述の信号発生回路が発生した第1信号のデューティに応じたスイッチングによって電圧変換回路が電圧を変換し、変換された電圧に基づくPWM制御により、信号発生回路の制御部が発生部に設定すべき目標の値を算出する。

これにより、信号を周期的に発生する発生部に設定する値の最小の増分を、比較的小さい処理負荷で実際の増分よりも実質的に小さくすることが可能な信号発生回路が電圧変換装置に適用されて、出力電圧の精度が向上する。

10

#### 【発明の効果】

#### 【0023】

本発明によれば、制御部が決定するN個の設定可能値について目標の値に最も近い設定可能値及び2番目に近い設定可能値の割合が適宜決定されるため、N個の設定可能値の平均的な値が、設定可能値の最小の増分よりもきめ細かく調整される。また、第2信号のオフ時間の設定がN周期に1回で済むため、制御部の処理負荷が低減される。

従って、設定された値に応じたデューティを有する信号を周期的に発生する発生部に設定する値の最小の増分を、比較的小さい処理負荷で実際の増分よりも実質的に小さくすることが可能となる。

20

#### 【図面の簡単な説明】

#### 【0024】

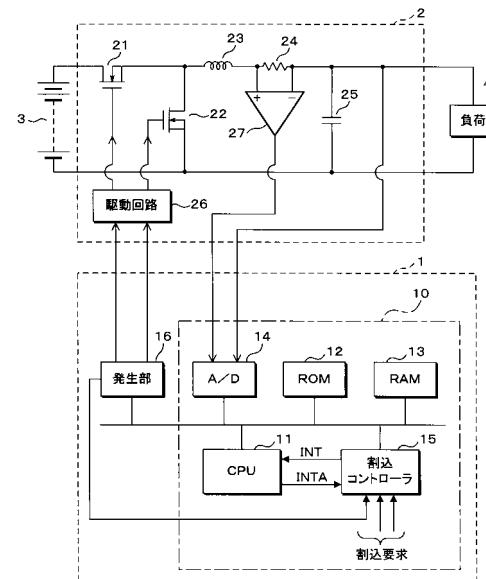

【図1】本発明の実施の形態1に係る電圧変換装置の構成例を示すブロック図である。

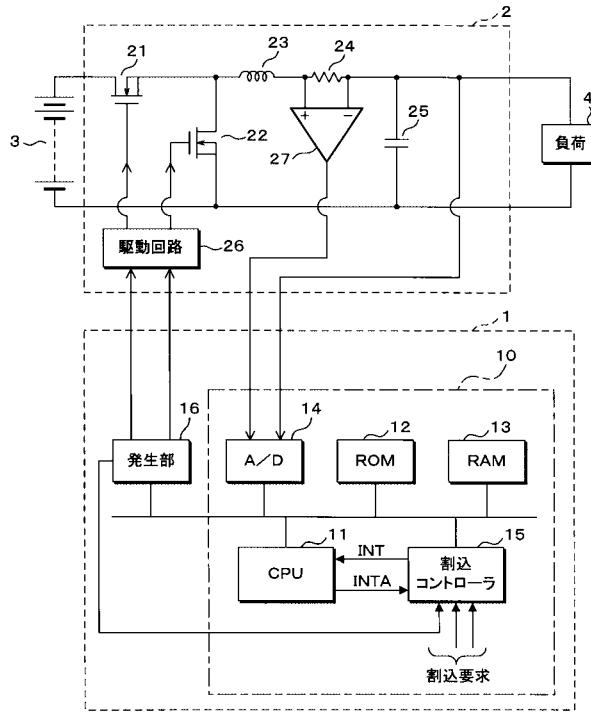

【図2】本発明の実施の形態1に係る信号発生回路の一部の構成例を示すブロック図である。

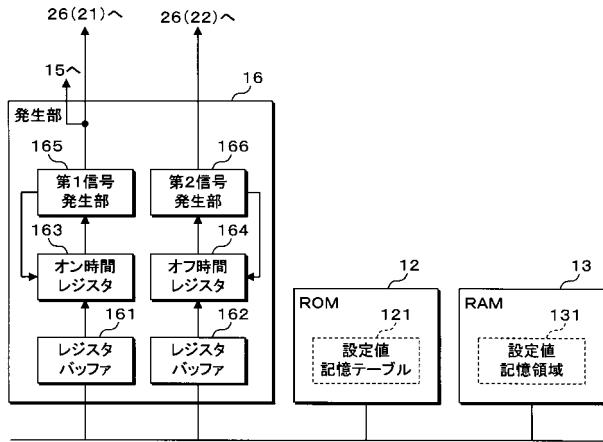

【図3】発生部が第1信号を発生する動作を説明するためのタイミング図である。

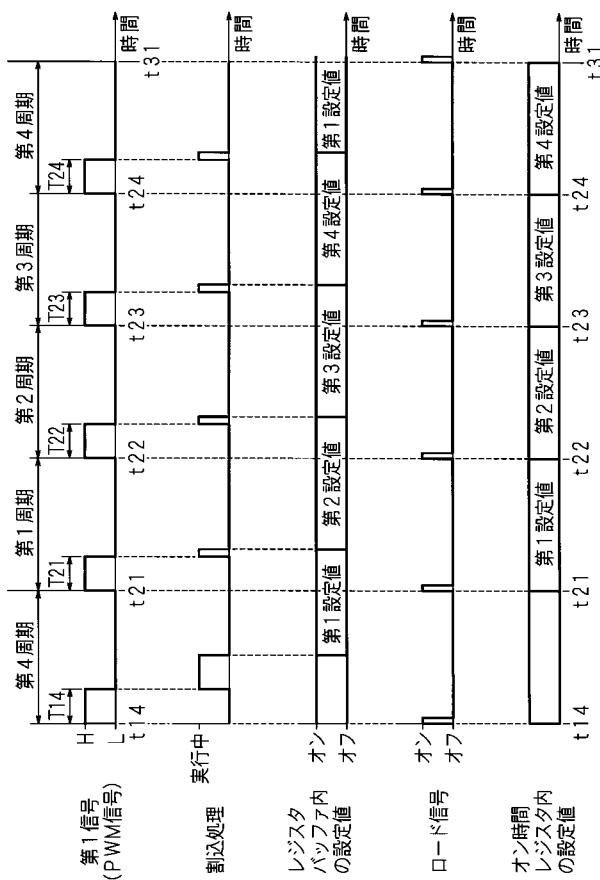

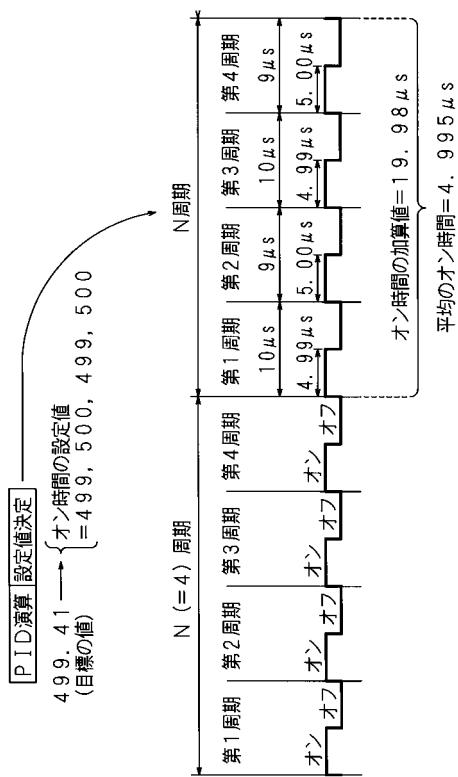

【図4】N周期分の設定値によってPWM信号の平均的なオン時間が定まる動作を説明するためのタイミング図である。

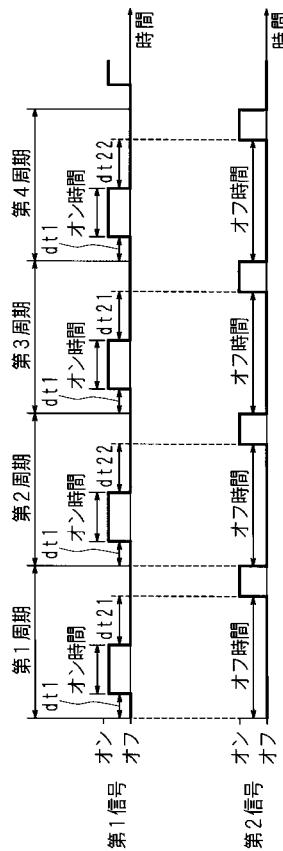

【図5】第1信号のオン時間、第2信号のオフ時間、及びデッドタイムの関係を説明するためのタイミング図である。

30

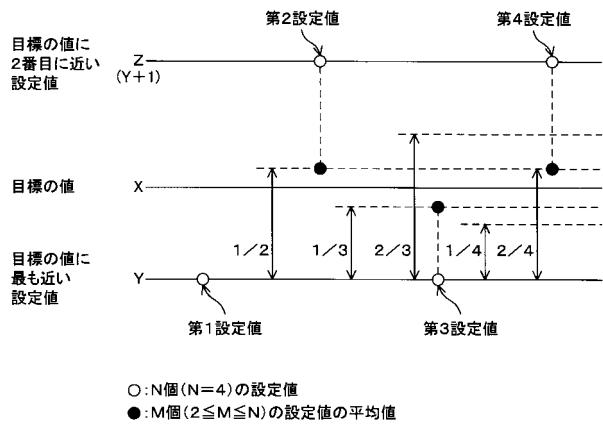

【図6】本発明の実施の形態1に係る信号発生回路でN個の設定値を決定する方法を説明するための説明図である。

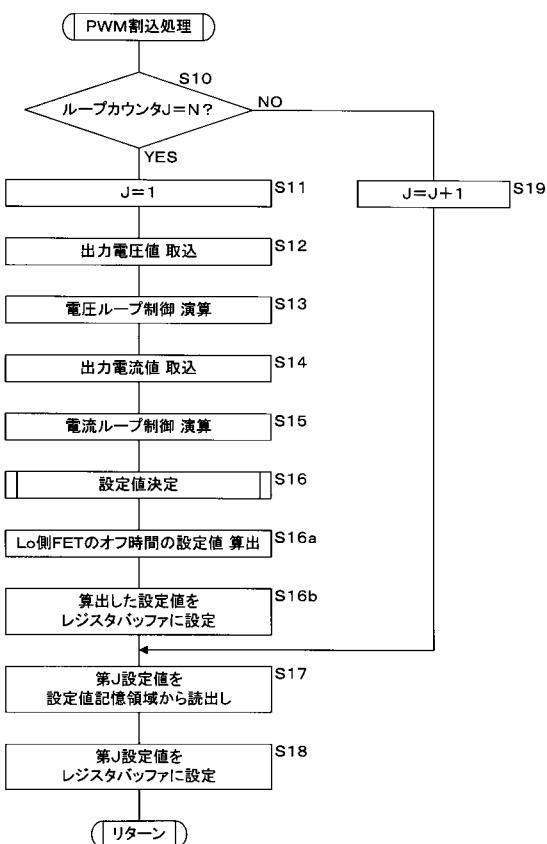

【図7】本発明の実施の形態1に係る信号発生回路でPWM割込処理を実行するCPUの処理手順を示すフローチャートである。

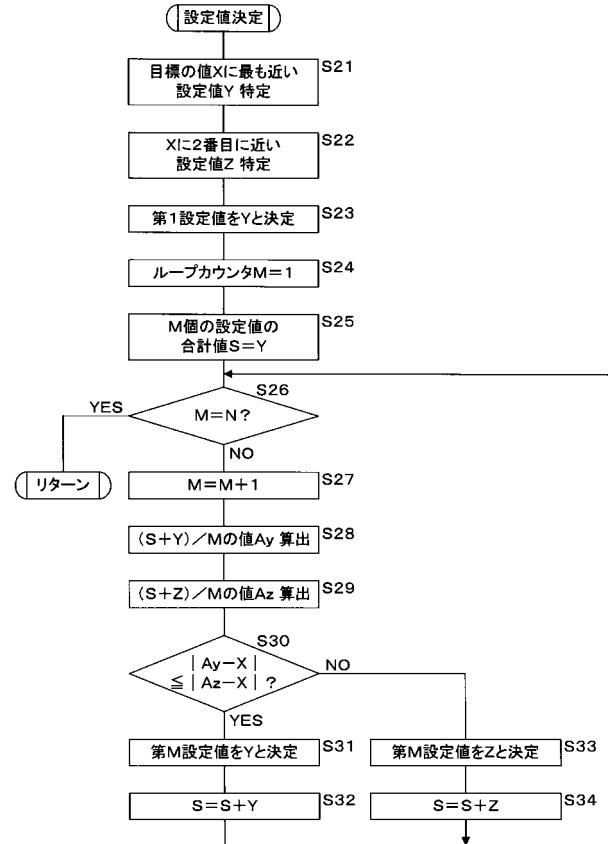

【図8】本発明の実施の形態1における設定値決定のサブルーチンに係るCPUの処理手順を示すフローチャートである。

【図9】本発明の実施の形態1に係る信号発生回路で目標の値に応じて決定されたN個の設定値の一覧を示す図表である。

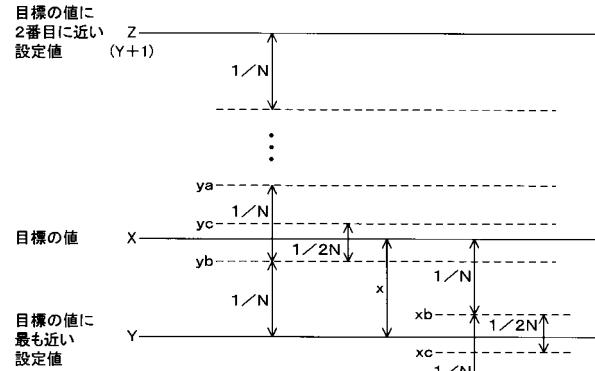

【図10】本発明の実施の形態2に係る信号発生回路でN個の設定値を決定する方法を説明するための説明図である。

40

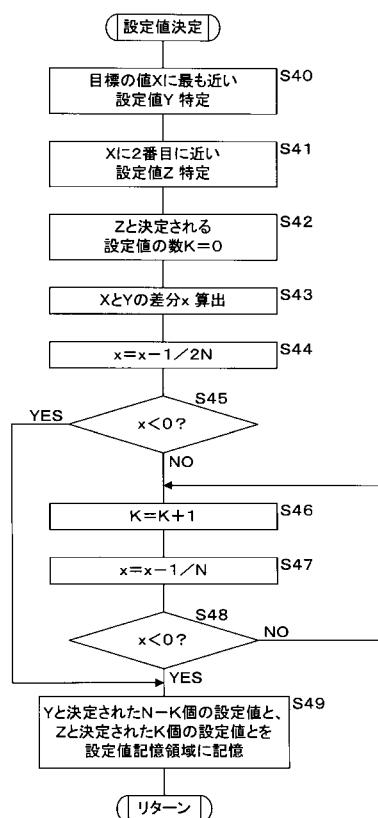

【図11】本発明の実施の形態2における設定値決定のサブルーチンに係るCPUの処理手順を示すフローチャートである。

【図12】本発明の実施の形態2に係る信号発生回路で目標の値に応じて決定されたN個の設定値の一覧を示す図表である。

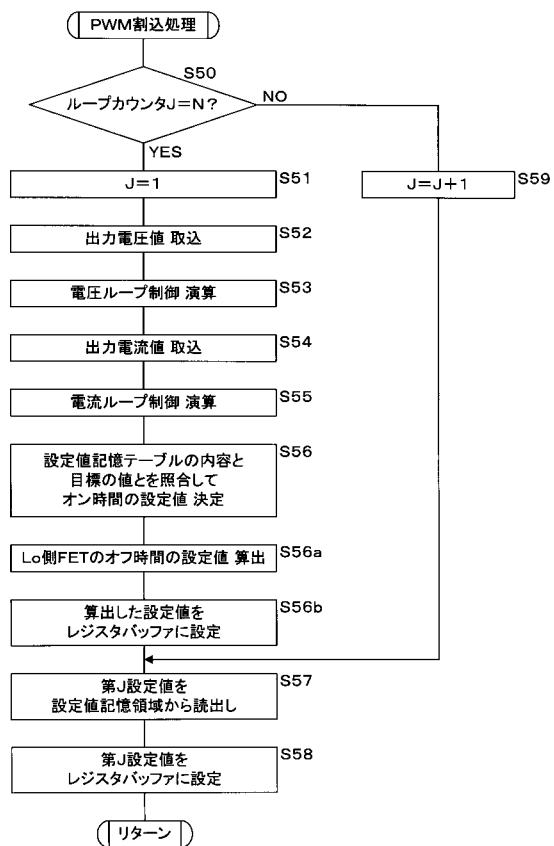

【図13】本発明の実施の形態3に係る信号発生回路でPWM割込処理を実行するCPUの処理手順を示すフローチャートである。

#### 【発明を実施するための形態】

#### 【0025】

以下、本発明をその実施の形態を示す図面に基づいて詳述する。

(実施の形態1)

50

図1は、本発明の実施の形態1に係る電圧変換装置の構成例を示すブロック図であり、図2は、本発明の実施の形態1に係る信号発生回路の一部の構成例を示すブロック図である。図中1は信号発生回路であり、信号発生回路1は、周期が一定でオン時間及びオフ時間が夫々変化する2つのPWM信号を発生して電圧変換回路2に与える。電圧変換回路2は、外部のバッテリ3の電圧を変換して外部の負荷4に供給する。ここでは電圧変換回路2がバッテリ3の電圧を降圧するが、バッテリ3の電圧を昇圧又は昇降圧するものであってもよい。

#### 【0026】

信号発生回路1は、CPU(Central Processing Unit)11を有するマイクロコンピュータである。CPU11は、プログラム等の情報を記憶するROM(Read Only Memory)12、一時的に発生した情報を記憶するRAM(Random Access Memory)13、アナログの電圧をデジタル値に変換するA/D変換器14、複数の割込要求を処理する割込コントローラ15、及び2つのPWM信号を発生する発生部16と互いにバス接続されている。信号発生回路1のうち、発生部16を除いたものが制御部10であるが、発生部16が制御部10に含まれていてもよい。

10

#### 【0027】

割込コントローラ15は、複数の割込要求を受け付け可能に構成されており、何れかの割込要求を受け付けた場合、CPU11に対してインタラプトを要求する信号(所謂INT信号)を与え、CPU11からアクノレッジ信号(所謂INTA信号)が与えられたときに、各割込要求に対応する割込ベクタをバスに送出する。バスに送出された割込ベクタがCPU11に読み込まれた場合、CPU11が各割込要求に対応する割込処理を実行するようになっている。

20

#### 【0028】

電圧変換回路2は、ドレインがバッテリ3の正極端子に接続されたNチャネル型のMOSFET(Metal Oxide Semiconductor Field Effect Transistor:以下、単にFETという)21と、該FET21のソース及びバッテリ3の負極端子夫々にドレイン及びソースが接続された同期整流用のFET22と、発生部16から与えられたPWM信号に基づいてFET21及びFET22夫々のゲートに駆動信号を与える駆動回路26とを備える。以下、FET21及び22夫々をHi側FET及びLo側FETともいう。

30

#### 【0029】

FET22のドレイン及びソース間には、インダクタ23及び抵抗器24の直列回路を介して負荷4が接続されている。負荷4には、コンデンサ25が並列に接続されている。抵抗器24及びコンデンサ25の接続点の電圧が、A/D変換器14に与えられる。抵抗器24の両端には電流検出器27が接続されており、電流検出器27の検出電圧がA/D変換器14に与えられる。

#### 【0030】

図2に移って、ROM12は、後述する目標の値に対応付けて予め決定された複数の設定値を記憶する設定値記憶テーブル(記憶部に相当)121を含む。但し、本実施の形態1では、設定値記憶テーブル121を用いない。

40

#### 【0031】

RAM13は、発生部16が有するレジスタバッファ161に対して設定されるべき複数の設定値が記憶される設定値記憶領域131を含んでいる。設定値記憶領域131に記憶された設定値は、割込コントローラ15が制御する後述の割込処理にて、順次レジスタバッファ161に設定されるようになっている。

#### 【0032】

発生部16は、後述するオン時間の設定値及びオフ時間の設定値夫々が設定されるレジスタバッファ161及び162と、レジスタバッファ161及び162夫々の内容が周期的にロードされるオン時間レジスタ163及びオフ時間レジスタ164と、オン時間レジスタ163の内容に応じたオン時間を有する第1信号を発生する第1信号発生部165と、オフ時間レジスタ164の内容に応じたオフ時間を有する第2信号を発生する第2信号

50

発生部 166 を有する。以下、信号がオンである状態がオン時間だけ継続する期間をオン期間という。

#### 【0033】

発生部 16 は、また、第 1 信号及び第 2 信号に共通の周期を設定するための不図示の周期レジスタと、第 1 信号及び第 2 信号に共通のオフ時間（所謂デッドタイム）のうち第 1 信号のオン期間に先立つデッドタイムを設定するための不図示のデッドタイムレジスタとを有する。周期レジスタ及びデッドタイムレジスタには、C P U 11 による初期化時に所定の値が各別に設定される。

#### 【0034】

第 1 信号発生部 165 及び第 2 信号発生部 166 夫々は、オン時間レジスタ 163 及びオフ時間レジスタ 164 夫々に対してレジスタバッファ 161 及び 162 の内容をロードするためのロード信号を与える。第 1 信号発生部 165 及び第 2 信号発生部 166 夫々が発生する第 1 信号及び第 2 信号は、不図示の内部クロックの整数倍のオン時間及びオフ時間を有しており、互いにオン期間が重ならない相補的な P W M 信号である。第 1 信号発生部 165 が発生した P W M 信号は、駆動回路 26 を介して F E T 21 ( H i 側 F E T ) に与えられると共に、割込要求の 1 つとして割込コントローラ 15 に与えられる。第 2 信号発生部 166 が発生した P W M 信号は、駆動回路 26 を介して F E T 22 ( L o 側 F E T ) に与えられる。

#### 【0035】

上述の構成において、信号発生回路 1 の C P U 11 は、例えば電圧ループ制御及び電流ループ制御を並列的に実行する電流モード制御方式によって負荷 4 に供給する電圧を制御する。電圧ループ制御では、C P U 11 は負荷 4 に供給された出力電圧を A / D 変換器 14 で変換したデジタル値を、目標の電圧値から減算した偏差に基づいて、後段の電流ループ制御で目標の電流値となる操作量を演算する。この電圧ループ制御では、電圧変換回路 2 が出力する電圧が制御量である。

#### 【0036】

電流ループ制御では、C P U 11 は電流検出器 27 の検出電圧を A / D 変換器 14 で変換したデジタル値を、前段の電圧ループ制御からの目標の電流値から減算した偏差に基づいて、発生部 16 に対する操作量を演算する。C P U 11 は、演算した操作量（所定の値に相当：以下、目標の値という）に応じて発生部 16 の第 1 信号発生部 165 に設定可能なオン時間の設定可能値を決定する。C P U 11 は、また、上記オン時間の設定可能値と、上述のデッドタイムレジスタに設定された値に基づいて、第 2 信号発生部 166 に設定可能なオフ時間の設定可能値を算出する。詳細については後述する。

#### 【0037】

上述の設定可能値とは、発生部 16 に設定されたときに出力の P W M 信号の変化に反映される最小単位（最小の増分）の整数倍の値をいう。第 1 信号発生部 165 及び第 2 信号発生部 166 は、設定可能値の最小単位が同一であり、設定可能値によって設定されるオン時間及びオフ時間は、精度が同一である。以下、簡単のために、発生部 16 に設定すべく決定又は算出された設定可能値を単に設定値という。発生部 16 は、決定されたオン時間の設定値及び算出されたオフ時間の設定値が設定されることにより、決定された設定値に応じたオン時間を有する第 1 信号と算出された設定値に応じたオフ時間を有する第 2 信号とを発生する。この電流ループ制御では、電圧変換回路 2 が出力する電流が制御量である。

#### 【0038】

ここで、電圧変換装置の出力電圧及び出力電流が時間的に比較的穏やかに変動する場合、上記の電圧ループ制御及び電流ループ制御の制御周期を P W M 周期の N 倍（N は 2 以上の自然数）の周期で行っても十分であると言える。そこで本実施の形態 1 では、P W M 周期の N 周期毎に発生部 16 に対する N 周期分のオン時間の設定値をまとめて決定して設定値記憶領域 131 に記憶しておき、P W M 周期で発生する割込処理にてオン時間の設定値を発生部 16 に設定する。

10

20

30

40

50

## 【0039】

以下では、簡単のために $N = 4$ とするが、これに限定されるものではなく、 $N$ は2、3又は5以上であってもよい。また、 $N$ 周期分の設定値は必ずしも1周期毎に発生部16に設定する必要はなく、ある周期と次の周期とで第1信号のオン時間の設定値が変わるとときにのみ設定するようにしてもよい。

## 【0040】

次に、第1信号発生部165がレジスタバッファ161の内容に応じたオン時間を有する第1信号を発生する仕組みについて説明する。第2信号発生部166がレジスタバッファ162の内容に応じたオフ時間を有する第2信号を発生する仕組みについては、オン時間をオフ時間に読み替えることにより、以下の図3の場合と同様になるため、その説明を省略する。但し、第2信号についてレジスタバッファ162の内容が $N$ 周期の間に1回だけ設定される点が、第1信号の場合と異なる（詳細については後述する）。

10

## 【0041】

図3は、発生部16が第1信号を発生する動作を説明するためのタイミング図である。図3に示す5つのタイミング図は、何れも同一の時間軸を横軸にしてあり、縦軸には、図の上から、第1信号（PWM信号）の信号レベル、PWM信号に応じて実行される割込処理の実行状態、発生部16のレジスタバッファ161の内容、レジスタバッファ161の内容をオン時間レジスタ163にロードするためのロード信号のオン／オフ状態、並びにオン時間レジスタ163の内容を示してある。

20

## 【0042】

PWM信号は、時刻 $t_{21}$ から $t_{22}$ まで、時刻 $t_{22}$ から $t_{23}$ まで、時刻 $t_{23}$ から $t_{24}$ まで、及び時刻 $t_{24}$ から $t_{31}$ までの夫々が、 $N$ 周期（ $N = 4$ ）における第1周期、第2周期、第3周期、及び第4周期であり、時刻 $t_{14}$ から $t_{21}$ までが、1つ前の $N$ 周期における第4周期である。PWM信号が立ち上がるタイミングは、各周期の開始時点と一致している。但し、簡単のために、図3では上述のデッドタイムを図示していない。PWM信号の各周期における信号レベルがHからLに変化する時の立ち下がりが、割込コントローラ15に対する割込要求として受け付けられて割込処理が1回実行される。

20

## 【0043】

具体的には、時刻 $t_{14}$ 、 $t_{21}$ 、 $t_{22}$ 、 $t_{23}$ 及び $t_{24}$ 夫々から、各周期におけるオン時間 $T_{14}$ 、 $T_{21}$ 、 $T_{22}$ 、 $T_{23}$ 及び $T_{24}$ が経過した時に割込処理が実行される。このうち、第4周期における割込処理は、第1周期、第2周期及び第3周期における割込処理と比較して、次の $N$ 周期のための設定値をまとめて決定するための時間だけ実行時間が長くなる。決定された設定値は、RAM13に含まれる設定値記憶領域131における第1アドレスから第4アドレスまでの連続した記憶領域に、夫々第1設定値、第2設定値、第3設定値及び第4設定値として記憶される。

30

## 【0044】

設定値記憶領域131に記憶された第1設定値、第2設定値、第3設定値及び第4設定値夫々は、各設定値が記憶されたときの第4周期における割込処理、並びに次の $N$ 周期における第1周期、第2周期及び第3周期夫々における割込処理により順次読み出されて、レジスタバッファ161に設定される。これにより、第1周期、第2周期、第3周期及び第4周期夫々における割込処理では、レジスタバッファ161の内容が、第2設定値、第3設定値、第4設定値及び次の $N$ 周期のための第1設定値に書き替えられる。

40

## 【0045】

一方、PWM信号の信号レベルがLからHに変化する時の立ち上がり、即ち時刻 $t_{14}$ 、 $t_{21}$ 、 $t_{22}$ 、 $t_{23}$ 、 $t_{24}$ 及び $t_{31}$ では、第1信号発生部165からオン時間レジスタ163に対してレジスタバッファ161の内容をロードするためのロード信号が与えられる。これにより、第1周期、第2周期、第3周期及び第4周期夫々の間、オン時間レジスタ163の内容は、第1周期分、第2周期分、第3周期分及び第4周期分の設定値に保持される。これらの設定値により、第1周期、第2周期、第3周期及び第4周期夫々におけるPWM信号のオン時間が定まる。

50

## 【0046】

なお、図3に示す例では、1つ前のN周期における第4周期内に、次のN周期のための4つの設定値を決定したが、この決定が第4周期内に完了しない場合は、設定値記憶領域131をダブルバッファとしておき、設定値記憶領域131に対する書き込みと読み出しが競合しないようにすればよい。具体的には、連続する第4周期、第1周期、第2周期及び第3周期の間に4つの設定値を決定して一方の設定値記憶領域に書き込み、これに続く第4周期、第1周期、第2周期及び第3周期の間に次の4つの設定値を決定して他方の設定値記憶領域に書き込むと共に、各周期における割込処理にて一方の設定値記憶領域から先に決定した4つの設定値を順次読み出すようにすればよい。

## 【0047】

10

次に、目標の値に応じたオン時間の設定値を発生部16に設定する具体例について説明する。

図4は、N周期分の設定値によってPWM信号の平均的なオン時間が定まる動作を説明するためのタイミング図である。図の横軸は時間を表し、縦軸は第1信号(PWM信号)の信号レベルを表す。図4では、2つの連続するN周期について、PWM周期の第1周期、第2周期、第3周期及び第4周期におけるPWM信号がオン/オフに変化する様子を示してある。各PWM周期におけるPWM信号は、前半がオンであり、後半がオフである。ここでも簡単のためにN=4とする

## 【0048】

20

本実施の形態1では、発生部16が発生するPWM信号の周期が $10\mu s$ であり、発生部16に設定可能なオン時間の設定値の最小単位(即ち最小の増分)が1であって、この最小単位の1がPWM信号のオン時間の $0.01\mu s$ に対応する。換言すれば、発生部16が発生する第1信号のオン時間は、 $0.01\mu s$ の精度で設定が可能である。その一方で、CPU11がPID演算によって算出した目標の値の最小単位は $0.01$ であるものとする。演算が行われるタイミング及び発生部16に設定値が設定されるタイミングの例は、図3に示した通りである。

## 【0049】

30

図4に示すタイミングにおいて、先のN周期におけるPID演算の結果、例として目標の値が499.41である場合を想定する。この目標の値に対してPWM信号のオン時間の設定値を499に設定したときは、PWM信号のオン時間が $4.99\mu s$ となる。また、PWM信号のオン時間の設定値を500に設定したときは、PWM信号のオン時間が $5.00\mu s$ となる。このように、オン時間の設定値を1ずつ変更した場合、PWM信号のオン時間が $0.01\mu s$ 単位で変化し、目標の値に対応する目標のオン時間である $4.9940\mu s$ に対する誤差(ここでは $0.004\mu s$ 又は $0.006\mu s$ )が大きい。

## 【0050】

40

そこで本実施の形態1では、目標の値に対応する目標のオン時間に近いオン時間が得られるオン時間の設定値を決定する。ここでは、目標のオン時間に最も近いオン時間が得られるオン時間の設定値を決定することが好ましい。具体的には、目標の値(499.41)に対応する目標のオン時間が $4.9941\mu s$ であるから、上述の第1設定値、第2設定値、第3設定値及び第4設定値の夫々が、例えば499、500、499及び500と決定される。

## 【0051】

40

この場合、各設定値によって次のN周期に発生するPWM信号のオン時間は、夫々 $4.99\mu s$ 、 $5.00\mu s$ 、 $4.99\mu s$ 及び $5.00\mu s$ となり、オン時間の加算値が $19.98\mu s$ であるから平均のオン時間が $4.995\mu s$ となる。従って、目標のオン時間である $4.9941\mu s$ に対する誤差が $0.0009\mu s$ にまで抑えられる。本実施の形態1のようにN=4である場合、平均のオン時間は、 $0.0025\mu s$ の精度で設定が可能となる。

## 【0052】

50

次に、第1信号のオン時間に基づいて第2信号のオフ時間を決定する方法について説明

する。

図 5 は、第 1 信号のオン時間、第 2 信号のオフ時間、及びデッドタイムの関係を説明するためのタイミング図である。図 5 に示す 2 つのタイミング図は、何れも同一の時間軸を横軸にしてあり、縦軸には、第 1 周期から第 4 周期までの時間の流れに応じた第 1 信号及び第 2 信号夫々の信号レベルを示してある。

【 0 0 5 3 】

上述したように、第1信号のオン時間及び第2信号のオフ時間は、設定値の最小単位が1であるが、第1信号のオン期間に先立つデッドタイム $d_t1$ を設定するためにデッドタイムレジスタに設定される設定値の最小単位も1であるものとする。また、第1信号及び第2信号夫々について設定されるオン時間及びオフ時間は、精度が同一であるが、デッドタイム $d_t1$ の精度もオン時間及びオフ時間の精度と同一であるものとする。

【 0 0 5 4 】

図 5 では、第 1 信号について、第 2 周期及び第 4 周期におけるオン時間が、第 1 周期及び第 3 周期におけるオン時間よりも長い場合を例にしている。一方、図 4 を用いて説明したように、N 周期内における第 1 信号のオン時間の設定値の変動は、最大で 1 である。従って、第 1 信号の第 2 周期及び第 4 周期におけるオン時間は、第 1 周期及び第 3 周期におけるオン時間よりも、オン時間の精度に相当する分だけ長いと言える。

〔 0 0 5 5 〕

ここで、第1周期から第4周期までの第1信号のオン期間に夫々続くデッドタイムを  $d_{t21}$ ,  $d_{t22}$ ,  $d_{t21}$ ,  $d_{t22}$  とする。一般的に、デッドタイム  $d_{t1}$  の長さは一定でよく、デッドタイム  $d_{t21}$  及び  $d_{t22}$  の長さは、デッドタイム  $d_{t1}$  の長さと同等又はそれ以上になるようにする必要がある。仮にデッドタイム  $d_{t21}$  及び  $d_{t22}$  の長さが同一になるようにする場合、図5から明らかのように、第1信号のオン時間の変動に応じて第2信号のオフ時間がN周期内で変動することとなり、第2信号のオフ時間の設定値を算出するためのCPU11の負荷が増大する。

【 0 0 5 6 】

そこで、本実施の形態 1 にあっては、デッドタイム  $d_t 2\ 2$  の長さを必要最小限の長さ（具体的には、例えばデッドタイム  $d_t 1$  と同じ長さ）とし、デッドタイム  $d_t 2\ 1$  の長さがデッドタイム  $d_t 2\ 2$  の長さよりもデッドタイムの精度に相当する分だけ長くなることを許容する。一方、第 1 信号のオン時間は、N 周期の中でデッドタイムの精度と同じ分だけ変動するから、第 2 信号のオフ時間の設定値を以下の式（1）により算出することにより、第 1 信号のオン期間に続くデッドタイムが、デッドタイム  $d_t 2\ 1$  又はデッドタイム  $d_t 2\ 2$  の何れかに自動的に定まることがある。

【 0 0 5 7 】

## 第2信号のオフ時間の設定値

[ 0 0 5 8 ]

次に、目標の値に対応する第1設定値、第2設定値、第3設定値及び第4設定値の決定方法について説明する。

図6は、本発明の実施の形態1に係る信号発生回路1でN個の設定値を決定する方法を説明するための説明図である。図中「 $\square$ 」はN個( $N = 4$ )の設定値を表し、「 $\triangle$ 」はM個( $2 \leq M \leq N$ )の設定値の平均値を表す。第1設定値について平均値が意味を持たないので、「 $\square$ 」の個数は「 $\triangle$ 」の個数よりも1つだけ少ない。

[ 0 0 5 9 ]

目標の値  $X$  に対して、先ず最も近い設定値  $Y$  及び 2 番目に近い設定値  $Z$  が特定される。図 6 の例では、 $X$  より小さく、且つ  $X$  より  $1/2$  以上小さくない  $Y$  が最初に特定され、 $Z$  が  $Y + 1$  と特定される。図 6 に示す場合とは異なって、 $X$  より大きく、且つ  $X$  より  $1/2$

以上大きくないYが最初に特定される場合(図示を省略)は、ZがY-1と特定される。

#### 【0060】

本実施の形態1では、Y及びZ( $= Y + 1$ )のうちからN個の設定値が順次決定される。その際に、第1設定値から第M( $2 \leq M \leq N$ )設定値までの平均値が目標の値Xに最も近い値となるように第M設定値が順次決定される。第1設定値については、第1及び第2設定値の平均値が目標の値Xに最も近くなることを見越して第2設定値よりも先に決定されるため、第1設定値は、常にYと決定される。第2設定値の候補値はY又はZである。

#### 【0061】

第2設定値が決定される場合、第1設定値と第2設定値の2つの候補値夫々との平均値のうち、どちらがXに近いのかが判定される。この場合、第1設定値はYであり、2つの候補値はY又はZであるから、YとYとの平均値であるY、及びYとZ( $Y + 1$ )との平均値である $Y + 1 / 2$ を比較してどちらがXに近いのかが判定される。図6の場合は、Yよりも $Y + 1 / 2$ の方がXに近いため、第2設定値はZと決定される。

10

#### 【0062】

第3設定値が決定される場合、第1設定値と、第2設定値と、第3設定値の2つの候補値夫々との平均値のうち、どちらがXに近いのかが判定される。この場合、第1設定値はYであり、第2設定値はZ( $= Y + 1$ )であり、第3設定値の2つの候補値はY又はZであるから、YとY+1とYとの平均値である $Y + 1 / 3$ 、及びYとY+1とY+1との平均値である $Y + 2 / 3$ のうちのどちらがXに近いのかが判定される。図6の場合は、Y+2/3よりもY+1/3の方がXに近いため、第3設定値はYと決定される。

20

#### 【0063】

第4設定値が決定される場合、第1設定値と、第2設定値と、第3設定値と、第4設定値の2つの候補値夫々との平均値のうち、どちらがXに近いのかが判定される。この場合、第1設定値はYであり、第2設定値はZ( $= Y + 1$ )であり、第3設定値はYであり、第4設定値の2つの候補値はY又はZであるから、YとY+1とY+1とYとの平均値である $Y + 1 / 4$ 、及びYとY+1とY+1とY+1との平均値である $Y + 2 / 4$ のうちのどちらがXに近いのかが判定される。図6の場合は、Y+1/4よりもY+2/4の方がXに近いため、第3設定値はZと決定される。

20

#### 【0064】

以上の図3から図6では、Nが4の場合について説明したが、Nが2、3又は5以上の場合についても同様である。以下では、上述したN個の設定値を決定する信号発生回路1の動作を、それを示すフローチャートを用いて説明する。以下に示す処理は、ROM12に予め格納されている制御プログラムに従って、CPU11により実行される。

30

図7は、本発明の実施の形態1に係る信号発生回路1でPWM割込処理を実行するCPU11の処理手順を示すフローチャートであり、図8は、本発明の実施の形態1における設定値決定のサブルーチンに係るCPU11の処理手順を示すフローチャートである。

#### 【0065】

図7におけるループカウンタJと、図8における目標の値X、目標の値に最も近い値Y、2番目に近い値Z、ループカウンタM、M個の設定値の合計値S、値Ay及び値Azは、RAM13に記憶される。ループカウンタJの初期値はNである。図8の処理で決定されたN個の設定値は、設定値記憶領域131内の連続したアドレスに順次記憶されことが好ましい。

40

#### 【0066】

PWM周期の割込が発生してCPU11の制御が図7の処理に移った場合、CPU11は、ループカウンタJがN(ここでは4)であるか否かを判定し(S10)、Nである場合(S10: YES)、Jを1とする(S11)。その後、CPU11は、負荷4に供給された出力電圧をA/D変換器14で変換したデジタルの出力電圧値を取り込み(S12: 検出部に相当)、取り込んだ出力電圧値に基づいて電圧ループ制御に係る演算を実行し(S13)、操作量として目標の電流値を算出する。

#### 【0067】

50

その後、CPU11は、電流検出器27の検出電圧をA/D変換器14で変換したデジタルの出力電流値を取り込み(S14)、取り込んだ出力電流値に基づいて電流ループ制御に係る演算を実行し(S15)、操作量として発生部16に設定すべき目標の値Xを算出して(算出部に相当)RAM13に記憶する。電流ループ制御を省略するために、ステップS14及びS15を実行しないようにしてもよい。

#### 【0068】

次いで、CPU11は、設定値決定に係るサブルーチンを呼び出して実行する(S16)。設定値決定に係るサブルーチンからリターンした場合、CPU11は、FET22(Lo側FET)のオフ時間の設定値を式(1)により算出し(S16a)、算出した設定値をレジスタバッファ161に設定する(S16b:設定部に相当)。その後、CPU11は、N個の設定値のうちの第J設定値を設定値記憶領域131から読み出し(S17)、読み出した第J設定値をレジスタバッファ161に設定して(S18)、割り込まれたルーチンにリターンする。

10

#### 【0069】

一方、ステップS10でJがNではない場合(S10:NO)、CPU11は、Jを1だけインクリメントした(S19)後、第J設定値をレジスタバッファ161に設定するためにステップS17に処理を移す。

#### 【0070】

図8に移って、PWM割込処理から設定値決定に係るサブルーチンが呼び出された場合、CPU11は、RAM13に記憶された目標の値Xに最も近い設定値Yを特定する(S21:特定部に相当)と共に、2番目に近い設定値Zを特定し(S22:特定部に相当)、更に第1設定値をYと決定する(S23:決定部に相当)。この時点で、ZはY+1又はY-1の何れか一方に特定される。次いで、CPU11は、ループカウンタMを1とし(S24)、M個の設定値の合計値SをYとする(S25)。

20

#### 【0071】

その後、CPU11は、MがNであるか否かを判定し(S26)、Nである場合(S26:YES)、呼び出されたルーチンにリターンする。MがNではない場合(S26:NO)、CPU11は、Mを1だけインクリメントした(S27)後、(S+Y)/Mの値Ayを算出する(S28)と共に、(S+Z)/Mの値Azを算出する(S29)。ここで算出したAy及びAzは、M個の設定値の平均値になり得る2つの候補値である。

30

#### 【0072】

次いで、CPU11は、|Ay-X|が|Az-X|以下であるか否かを判定する(S30)。ここでの判定は、上記2つの候補値のうち、何れが目標の値Xに近いのかを判定するものである。 $|Ay - X| < |Az - X|$ の場合(S30: YES)、CPU11は、第M設定値をYと決定し(S31:決定部に相当)、M個の設定値の合計値SをS+Yに置き換えた(S32)後、ステップS26に処理を移す。一方、 $|Ay - X| \geq |Az - X|$ の場合(S30: NO)、CPU11は、第M設定値をZと決定し(S33:決定部に相当)、M個の設定値の合計値SをS+Zに置き換えた(S34)後、ステップS26に処理を移す。

40

#### 【0073】

上述のフローチャートでは、目標の値Xに最も近い設定値Yと共に2番目に近い設定値Zを先に特定して、Zの値(Y+1又はY-1)をRAM13に記憶したが、この方法に限定されるものではない。例えば、第M設定値を決定する際に、第1設定値から第M-1設定値までの平均値を算出しておき、この平均値と目標の値Xとの大小関係を判定することによって、目標の値Xに最も近い設定値Yを都度特定し、更に2番目に近い設定値ZがY+1であるのか、又はY-1であるのかを特定するようにしてもよい。

#### 【0074】

次に、上述のようにして決定されたN個の設定値の複数の例について説明する。

図9は、本発明の実施の形態1に係る信号発生回路1で目標の値に応じて決定されたN個の設定値の一覧を示す図表である。目標の値は、小数以下2桁の数値で表されるものと

50

する。以下、代表的な目標の値の範囲について、N個の設定値を列挙して説明する。例えば目標の値が0.13から0.16の範囲内にある場合、第1、第2、第3及び第4設定値は、夫々0、0、0及び1と決定される。この場合、N個の設定値の平均値は0.25であり、これによるPWM信号のオン時間の平均値は0.0025μsである。

#### 【0075】

目標の値が0.38から0.50の範囲内にある場合、第1、第2、第3及び第4設定値は、夫々0、1、0及び1と決定され、N個の設定値の平均値は0.50であり、これによるPWM信号のオン時間の平均値は0.005μsである。目標の値が0.51から0.62の範囲内にある場合、第1、第2、第3及び第4設定値は、夫々1、0、1及び0と決定され、N個の設定値の平均値は0.50であり、これによるPWM信号のオン時間の平均値は0.005μsである。目標の値が0.88から1.12の範囲内にある場合、第1、第2、第3及び第4設定値は、夫々1、1、1及び1と決定され、N個の設定値の平均値は1.00であり、これによるPWM信号のオン時間の平均値は0.010μsである。

10

#### 【0076】

以下、目標の値の範囲が0.13から1.12の範囲内にある9つの範囲の夫々について、目標の範囲の下限及び上限が1.00だけ大きくなる毎に、N個の設定値も1だけ大きくなるように決定される。特に図4に対応する場合について言えば、目標の値が499.38から499.50の範囲内にある場合、第1、第2、第3及び第4設定値は、夫々499、500、499及び500と決定され、N個の設定値の平均値は499.50であり、これによるPWM信号のオン時間の平均値は4.995μsである。

20

#### 【0077】

以上のように本実施の形態1によれば、制御部10の中核として機能するCPU11は、発生部16に設定すべき目標の値Xに応じて発生部16のレジスタバッファ161に設定可能な設定値を決定して設定する。発生部16は、レジスタバッファ161に設定された設定値に応じたオン時間を有する第1信号と、該第1信号との間にデッドタイムが設けられた第2信号とを周期的に発生する。具体的に、CPU11は、発生部16が有する第1信号発生部165が発生する第1信号のN(=4)周期毎に、目標の値Xに最も近い設定値Y及び2番目に近い設定値Zを特定し、特定したY及びZの大きさとXの大きさとを比較した結果により、Y及びZの中からN個の設定値を決定して、第1信号の1周期毎に1つずつ発生部16のレジスタバッファ161に設定する。CPU11は、また、N周期の第1周期における第2信号のオフ時間を設定するための値を、同じN周期について決定した小さい方の設定可能値及び所定値の加算値として算出し、算出した値を発生部16のレジスタバッファ162に設定する。

30

これにより、CPU11が決定するN個の設定値について目標の値Xに最も近い設定値Y及び2番目に近い設定値Zの割合が適宜決定されるため、N個の設定値の平均的な値が、発生部16のレジスタバッファ161に設定可能な値の最小の増分よりもきめ細かく調整される。また、第2信号のオフ時間の設定がN周期に1回で済むため、CPU11の処理負荷が低減される。

30

従って、設定された値に応じたオン時間を有する第1信号及び該第1信号とオン期間が重ならない第2信号を周期的に発生する発生部16に設定する値の最小の増分を、比較的小さい処理負荷で実際の増分よりも実質的に小さくすることが可能となる。

40

#### 【0078】

また、実施の形態1によれば、第2信号のオフ時間を第1及び第2信号が共にオフになるべきデッドタイムと同じ長さに設定するための値よりも、第1信号のオン時間の設定可能値の最小単位だけ大きい値を、上記の所定値とする。

これにより、N周期内で第1信号のオン時間が変動した場合であっても、第1信号及び第2信号についてのデッドタイムを確保することが可能となる。

#### 【0079】

更に、実施の形態1によれば、CPU11は、目標の値Xに最も近い設定値Yを第1設

50

定値と決定し、第1設定値から第M設定値(2 M N)までの平均的な値が目標の値Xに最も近くなるように、第M設定値を決定することをN-1回だけ繰り返す。

従って、PWM信号のN周期中のどの周期にあっても、第1周期からその周期までに発生部16に設定された設定値の平均的な値を目標の値Xに最も近い値にすることが可能となる。

#### 【0080】

##### (実施の形態2)

実施の形態1が、第1設定値及び第M設定値(2 M N)を順次決定する形態であるのに対し、実施の形態2は、M個の設定値のうち目標の値に2番目に近い設定値の個数を算出することにより、N個の設定値を一括して決定する形態である。

実施の形態2における電圧変換装置の構成は、実施の形態1における図1及び2に示すものと同様であるため、実施の形態1に対応する箇所には同一の符号を付してその説明を省略する。

#### 【0081】

図10は、本発明の実施の形態2に係る信号発生回路1でN個の設定値を決定する方法を説明するための説明図である。目標の値Xに対して、先ず最も近い設定値Y及び2番目に近い設定値Zが特定される。図10の例では、Xより小さく、且つXより1/2以上小さくないYが最初に特定され、ZがY+1と特定される。

#### 【0082】

さて、第1設定値から第N設定値までが全てYと決定されたと仮定すると、全ての設定値の平均値はYとなる。次に、N個の設定値のうち1つだけ設定値がYではなくZ(図10の場合はY+1)と決定された場合、全ての設定値の平均値は、Yに対して1/Nだけ増加(又は減少)する(図10の場合は増加する)。同様に、Zと決定される設定値が1つ増加する毎に全ての設定値の平均値が1/Nだけ増加(又は減少)する(図10の場合は増加する)。

#### 【0083】

Zと決定される設定値の数と全ての設定値の平均値との関係が上述のとおりであることを考慮して、Zと決定される設定値の数を求めるには、YからZに向けて1/Nずつ加算(又は減算)した値とXとの大小関係を都度判定すればよい。より具体的には、Yに対して1/NをK回加算(又は減算)した値とXとの大小関係が逆転した場合、K回加算(又は減算)した値y<sub>a</sub>と、K-1回加算(又は減算)した値y<sub>b</sub>とで、どちらがXに近いかを判定し、近い方の回数(K又はK-1)をZと決定される設定値の数とすればよい。

#### 【0084】

具体的に図10の場合は、Yに対して1/NをK-1回加算(又は減算)した値y<sub>b</sub>に更に1/2Nを加算(又は減算)した値y<sub>c</sub>とXとの大小関係を判定すればよい。図10の場合は(図10の左半分参照)、K=2であり、y<sub>c</sub>の方がXより大きいと判定されるため、K-1の値(=1)がZと決定される設定値の数となる。

#### 【0085】

上述したアルゴリズムをXの側から見れば(図10の右半分参照)、XとYとの差分xから1/Nを減算することを繰り返し、K回減算したときに減算結果x<sub>a</sub>が負になった場合、xから1/NをK-1回減算した値x<sub>b</sub>から更に1/2Nを減算した値x<sub>c</sub>が負になるか否かによって、Zと決定される設定値の数を決定すればよい。図10の例ではK=2であり、x<sub>c</sub>が負になるから、Zの数が1と決定される。仮にx<sub>c</sub>が正であればZの数が2と決定される。

#### 【0086】

なお、XとYとの差分xから先に1/2Nを減算しておき、この減算結果から1/Nを何回減算したときに減算結果が負になるかによって、Zと決定される設定値の数を決定してもよい。1/2Nを減算したときの減算結果が負であれば、Zの数が0と決定され、1/NをK回減算したときの減算結果が負であればZの数がKと決定される。後述するフローチャートでは、このアルゴリズムで説明する。図10の例では、xから1/2Nを減算

した結果から  $1/N$  を 1 回減算したときに減算結果が負になるから、Z の数が 1 と決定される。

#### 【0087】

以下では、上述した信号発生回路 1 の動作を、それを示すフローチャートを用いて説明する。以下に示す処理は、ROM12 に予め格納されている制御プログラムに従って、CPU11 により実行される。

図 11 は、本発明の実施の形態 2 における設定値決定のサブルーチンに係る CPU11 の処理手順を示すフローチャートである。図 11 における設定値の数 K、及び X と Y の差分 x は、RAM13 に記憶される。PWM 割込処理に係る CPU11 の処理手順は、実施の形態 1 における図 7 に示すものと同様であるため、図示及び説明を省略する。

10

#### 【0088】

PWM 割込処理から設定値決定に係るサブルーチンが呼び出された場合、CPU11 は、RAM13 に記憶された目標の値 X に最も近い設定値 Y を特定する (S40：特定部に相当) と共に、2 番目に近い設定値 Z を特定し (S41：特定部に相当)、更に Z と決定される設定値の数 K を 0 とする (S42)。その後、CPU11 は、X と Y の差分 x を算出し (S43)、算出した x から  $1/2N$  を減算した値を新たに x とする (S44)。

#### 【0089】

次いで、CPU11 は、x が負であるか否かを判定し (S45)、負である場合 (S45：YES)、後述するステップ S49 に処理を移す。x が負ではない場合 (S45：NO)、CPU11 は、K の値を 1 だけインクリメントし (S46)、x から  $1/N$  を減算した値を新たに x とする (S47)。

20

#### 【0090】

次いで、CPU11 は、x が負であるか否かを判定し (S48)、負ではない場合 (S48：NO)、ステップ S46 に処理を移す。x が負である場合 (S48：YES)、N 個の設定値に含まれる Y 及び Z の個数が決定される (決定部に相当)。CPU11 は、(値が) Y と決定された N - K 個の設定値と、(値が) Z と決定された K 個の設定値とを設定値記憶領域 131 に記憶し (S49)、呼び出されたルーチンにリターンする。

30

なお、ステップ S45 及び S48 では、x が負であるか否かを判定したが、判定に等号を含めて、x が 0 以下で有るか否かを判定するようにしてもよい。

#### 【0091】

次に、上述のようにして決定された N 個の設定値の複数の例について説明する。

図 12 は、本発明の実施の形態 2 に係る信号発生回路 1 で目標の値に応じて決定された N 個の設定値の一覧を示す図表である。図 12 では、値が異なる N 個の設定値が N 個の並びの中で概ね均等に分散されるように並べてあるが、これに限定されるものではなく、第 1 設定値、第 2 設定値、第 3 設定値及び第 4 設定値を数値の昇順又は降順に並べてもよいし、順不同に並べてもよい。

40

#### 【0092】

図 12 に示す目標の値及び N 個の設定値は、実施の形態 1 における図 9 に示すものと比較して、N 個の設定値の平均値が同じものが図表に含まれていない点が異なる。これは、N 個の設定値を決定するアルゴリズムが異なるためである。また、図 9 では N 個の設定値の並び順がアルゴリズムによって決まるものであるのに対し、図 12 では、電圧変換回路 2 に対する PWM 制御にとって好ましくなるように (例えば出力のノイズが最も小さくなるように) N 個の設定値の並び順が適宜決定され得る点が異なる。

#### 【0093】

以上のように本実施の形態 2 によれば、CPU11 は、N 個全ての設定値の平均的な値が目標の値に最も近くなるように N 個の設定値を決定する。

従って、信号の N 周期全体について、発生部 16 に設定された N 個の設定値の平均的な値を目標の値に最も近い値にすることが可能となる。

#### 【0094】

(実施の形態 3)

50

実施の形態1は、N個の設定値がN周期毎に順次決定される形態であるのに対し、実施の形態3は、N個の設定値が、ROM12に含まれる設定値記憶テーブル121に予め記憶された内容から選択されることにより、N周期毎に一括して決定される形態である。

実施の形態3における電圧変換装置の構成は、実施の形態1における図1及び2に示すものと同様であるため、実施の形態1に対応する箇所には同一の符号を付してその説明を省略する。設定値記憶テーブル121の内容は、実施の形態2における図12に示すものと同様である。

#### 【0095】

N個の設定値は、例えばN周期における第4周期で決定される。設定値記憶テーブル121に記憶された内容から決定された第1設定値、第2設定値、第3設定値及び第4設定値夫々は、各設定値が決定された第4周期における割込処理、並びに次のN周期における第1周期、第2周期及び第3周期夫々における割込処理により順次読み出されて、レジスタバッファ161に設定される。

10

#### 【0096】

以下では、上述したN個の設定値を決定する信号発生回路1の動作を、それを示すフローチャートを用いて説明する。以下に示す処理は、ROM12に予め格納されている制御プログラムに従って、CPU11により実行される。

図13は、本発明の実施の形態3に係る信号発生回路1でPWM割込処理を実行するCPU11の処理手順を示すフローチャートである。図13におけるループカウンタJ及び目標の値Xは、RAM13に記憶される。ループカウンタJの初期値はNである。

20

#### 【0097】

なお、ステップS50からS59までの処理のうち、ステップS56以外の処理は、実施の形態1における図7に示すステップS10からS19までの処理と同様であるため、詳細な説明を省略する。

#### 【0098】

PWM周期の割込が発生してCPU11の制御が図13の処理に移った場合、CPU11は、ループカウンタJがN(ここでは4)であるか否かを判定し(S50)、Nである場合(S50: YES)、Jを1とする(S51)。その後、CPU11は、出力電圧に基づく電圧ループ制御、及び出力電流に基づく電流ループ制御に係る演算を実行する(S52~S55)。

30

#### 【0099】

次いで、CPU11は、設定値記憶テーブル121の内容、即ちテーブルに記憶された目標の値の各範囲と、上述の演算によって算出した目標の値Xとを照合して、オン時間の設定値を決定する(S56:特定部に相当)。具体的には、照合の結果、目標の値Xが含まれる範囲に対応して設定値記憶テーブル121に記憶されているN個の設定値が、決定された設定値となる。決定されたN個の設定値は、設定値記憶テーブル121に記憶されていた順序で、設定値記憶領域131内の連続したアドレスに一旦記憶されることがほしい。

#### 【0100】

次いで、CPU11は、FET22(Lo側FET)のオフ時間の設定値を式(1)により算出して(S56a)レジスタバッファ161に設定した(S56b:設定部に相当)後、第J設定値を設定値記憶領域131から読み出し(S57)、読み出した第J設定値をレジスタバッファ161に設定して(S58)、割り込まれたルーチンにリターンする。

40

なお、ステップS56で設定値記憶テーブル121におけるN個の設定値の先頭アドレスを記憶しておき、ステップS57では、ループカウンタJの値に応じて設定値記憶テーブル121から第J設定値を読み出すようにしてもよい。

#### 【0101】

以上のように本実施の形態3によれば、その平均的な値が目標の値Xに最も近くなるように予め算出されたN個の設定値と、目標の値の範囲との対応関係が設定値記憶テーブル

50

121に記憶されている。C P U 11は、目標の値に対応して発生部16のレジスタバッファ161に設定すべきN個の設定値を割込処理にて設定値記憶テーブル121から順次読み出して決定する。

従って、目標の値Xに応じて決定すべきN個の設定値を、C P U 11による制御の実行時に容易に決定することが可能となる。

#### 【0102】

更に、実施の形態1、2又は3によれば、上述の信号発生回路1が発生した第1信号のデューティに応じたスイッチングによって電圧変換回路2が電圧を変換し、変換された電圧に基づくP W M制御により、信号発生回路1のC P U 11が発生部16に設定すべき目標の値を算出する。

従って、第1及び第2信号を周期的に発生する発生部16に設定する値の最小の増分を、比較的小さい処理負荷で実際の増分よりも実質的に小さくすることが可能な信号発生回路1を電圧変換装置に適用して、出力電圧の精度を向上させることができることが可能となる。

#### 【0103】

今回開示された実施の形態は、全ての点で例示であって、制限的なものではないと考えられるべきである。本発明の範囲は、上述した意味ではなく、特許請求の範囲によって示され、特許請求の範囲と均等の意味及び範囲内での全ての変更が含まれることが意図される。また、各実施の形態で記載されている技術的特徴は、お互いに組み合わせることが可能である。

#### 【符号の説明】

10

20

30

40

1 信号発生回路

1 0 制御部

1 1 C P U

1 2 R O M

1 2 1 設定値記憶テーブル

1 3 R A M

1 3 1 設定値記憶領域

1 4 A / D 変換器

1 5 割込コントローラ

1 5 3 P W M 信号発生部

1 6 発生部

1 6 1、1 6 2 レジスタバッファ

1 6 5 第1信号発生部

1 6 6 第2信号発生部

2 電圧変換回路

2 1、2 2 F E T

2 3 インダクタ

2 6 駆動回路

2 7 電流検出器

3 バッテリ

4 負荷

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

| 目標の値          | N個の設定値    |           |           |           | N個の設定値の平均値<br>(μs) |

|---------------|-----------|-----------|-----------|-----------|--------------------|

|               | 第1<br>設定値 | 第2<br>設定値 | 第3<br>設定値 | 第4<br>設定値 |                    |

| 0.00~0.12     | 0         | 0         | 0         | 0         | 0.00               |

| 0.13~0.16     | 0         | 0         | 0         | 1         | 0.25               |

| 0.17~0.25     | 0         | 0         | 1         | 0         | 0.25               |

| 0.26~0.37     | 0         | 1         | 0         | 0         | 0.25               |

| 0.38~0.50     | 0         | 1         | 0         | 1         | 0.50               |

| 0.51~0.62     | 1         | 0         | 1         | 0         | 0.50               |

| 0.63~0.75     | 1         | 0         | 1         | 1         | 0.75               |

| 0.76~0.83     | 1         | 1         | 0         | 1         | 0.75               |

| 0.84~0.87     | 1         | 1         | 1         | 0         | 0.75               |

| 0.88~1.12     | 1         | 1         | 1         | 1         | 1.00               |

| ⋮             | ⋮         | ⋮         | ⋮         | ⋮         | ⋮                  |

| 498.88~499.12 | 499       | 499       | 499       | 499       | 499.00             |

| 499.13~499.16 | 499       | 499       | 499       | 500       | 499.25             |

| 499.17~499.25 | 499       | 499       | 500       | 499       | 499.25             |

| 499.26~499.37 | 499       | 500       | 499       | 499       | 499.25             |

| 499.38~499.50 | 499       | 500       | 499       | 500       | 499.50             |

| ⋮             | ⋮         | ⋮         | ⋮         | ⋮         | ⋮                  |

【図10】

【図11】

【図12】

| 目標の値          | N個の設定値 |       |       |       |

|---------------|--------|-------|-------|-------|

|               | 第1設定値  | 第2設定値 | 第3設定値 | 第4設定値 |

| 0.00~0.12     | 0      | 0     | 0     | 0     |

| 0.13~0.37     | 0      | 0     | 0     | 1     |

| 0.38~0.62     | 0      | 1     | 0     | 1     |

| 0.63~0.87     | 1      | 0     | 1     | 1     |

| 0.88~1.12     | 1      | 1     | 1     | 1     |

| 1.13~1.37     | 1      | 1     | 1     | 2     |

| 1.38~1.62     | 1      | 2     | 1     | 2     |

| ⋮             | ⋮      | ⋮     | ⋮     | ⋮     |

| 499.13~499.37 | 499    | 499   | 499   | 500   |

| 499.38~499.62 | 499    | 500   | 499   | 500   |

| ⋮             | ⋮      | ⋮     | ⋮     | ⋮     |

【図13】

---

フロントページの続き

(72)発明者 東 誠

三重県四日市市西末広町1番14号 株式会社オートネットワーク技術研究所内

(72)発明者 阿部 武徳

三重県四日市市西末広町1番14号 株式会社オートネットワーク技術研究所内

F ターム(参考) 5H730 AS05 BB13 BB57 DD04 EE13 EE59 FD01 FD31 FF09 FG05

5J500 AA03 AA58 AC88 AH10 AH25 AH29 AH33 AK00 AK28 AK33

AK34 AK47 AM20 AM21 AT06 AT07