(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5989018号

(P5989018)

(45) 発行日 平成28年9月7日(2016.9.7)

(24) 登録日 平成28年8月19日(2016.8.19)

(51) Int.Cl.

F 1

G06F 3/041 (2006.01)

G06F 3/044 (2006.01)G06F 3/041 412

G06F 3/044 120

請求項の数 18 外国語出願 (全 17 頁)

(21) 出願番号 特願2014-22336 (P2014-22336)

(22) 出願日 平成26年2月7日 (2014.2.7)

(65) 公開番号 特開2014-238816 (P2014-238816A)

(43) 公開日 平成26年12月18日 (2014.12.18)

審査請求日 平成26年3月12日 (2014.3.12)

(31) 優先権主張番号 201310223963.3

(32) 優先日 平成25年6月6日 (2013.6.6)

(33) 優先権主張国 中国 (CN)

(73) 特許権者 515217270

フォーカルテック・エレクトロニクス・リミテッド

F o c a l T e c h E l e c t r o n i c s , L t d .

イギリス領ケイマン諸島、KY1-111

2 グランド・ケイマン、ピーオーボックス2804、クリケット・スクエア、ウイロー・ハウス、フロア4

(74) 代理人 110001508

特許業務法人 津国

(72) 発明者 莫良華

中華人民共和国広東省深▲せん▼市南山区

科技園南区アール3-ビー棟4樓

最終頁に続く

(54) 【発明の名称】タッチディスプレイ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

タッチディスプレイ装置であって：

第一の基板、第二の基板、液晶層及び複数個の画素ユニットを含むディスプレイタッチスクリーンであって、液晶層及び画素ユニットが第一の基板と第二の基板との間に位置し、かつ二次元アレイに配列された複数個の共通電極をさらに含むディスプレイタッチスクリーンと、

ディスプレイ制御回路及びタッチ制御回路を含むディスプレイタッチ制御回路であって、それが配線を通じて複数個の共通電極に接続され、ディスプレイング状態中、複数個の共通電極がディスプレイ制御回路に提供されたコモンレベルに接続され、タッチ検知状態中、複数個の共通電極の各々がタッチ検知電極としてタッチ制御回路に個別の配線により接続されるディスプレイタッチ制御回路と

を含み、

タッチ制御回路が共通電極の各々の自己容量を検出するように適応され、

タッチ制御回路が、

当該 (current) 共通電極に印加される信号に応じて、当該共通電極及び当該共通電極の周りの共通電極を同時に駆動する工程、又は

当該共通電極に印加される信号に応じて、当該共通電極及び他の共通電極のすべてを同時に駆動する工程

を含む方法によって、当該共通電極の自己容量を検出するように適応される、タッチデ

10

20

イスプレイ装置。

【請求項 2】

複数個の共通電極が提供された層に配線が配置された、又は複数個の共通電極が提供された層とは異なる層に配置され、ビアホールを通じて複数個の共通電極に配線が接続される、請求項 1 記載のタッチディスプレイ装置。

【請求項 3】

データ線が提供された層に配線が配置され、ビアホールを通じて複数個の共通電極に配線が接続される、請求項 1 記載のタッチディスプレイ装置。

【請求項 4】

画素ユニットの各々が画素電極を含み、画素電極が提供された層に配線が配置され、ビアホールを通じて複数個の共通電極に配線が接続される、請求項 1 記載のタッチディスプレイ装置。 10

【請求項 5】

配線がブラックマトリクスの直下に配置される、請求項 1 記載のタッチディスプレイ装置。

【請求項 6】

ディスプレイタッチ制御回路が单一のチップであり、ディスプレイ制御回路及びタッチ制御回路が单一のチップに一体化されているか、

ディスプレイタッチ制御回路が二つ以上のチップを含み、ディスプレイ制御回路とタッチ制御回路とが異なるチップにあるか、又は 20

ディスプレイタッチ制御回路が二つ以上のチップを含み、チップの各々がディスプレイタッチスクリーンの一部分を制御する、請求項 1 記載のタッチディスプレイ装置。

【請求項 7】

ディスプレイタッチ制御回路用のチップがチップオングラス方式で第一の基板又は第二の基板上に実装されるか、又は

ディスプレイ制御回路用のチップ及びタッチ制御回路用のチップがチップオングラス方式で第一の基板又は第二の基板上に実装される、請求項 6 記載のタッチディスプレイ装置。

【請求項 8】

タッチ制御回路が、当該共通電極に印加される信号に応じて、データ線を同時に駆動するように適応される、請求項 1 記載のタッチディスプレイ装置。 30

【請求項 9】

タッチ制御回路が二次元容量検知アレイによってタッチ位置を決定するように適応される、請求項 1 記載のタッチディスプレイ装置。

【請求項 10】

ディスプレイタッチスクリーンが面内切替構造、フリンジフィールド切替構造又はねじれネマチック構造を有する、請求項 1 記載のタッチディスプレイ装置。

【請求項 11】

共通電極が正多角形の形状、長方形の形状、又は円の形状もしくは橢円の形状である、請求項 1 記載のタッチディスプレイ装置。 40

【請求項 12】

凹凸構造が共通電極の端部に提供される、請求項 1 記載のタッチディスプレイ装置。

【請求項 13】

複数個の共通電極の材料が酸化インジウムスズ又はグラフェンである、請求項 1 記載のタッチディスプレイ装置。

【請求項 14】

ディスプレイタッチスクリーンの画素ユニットの各々が薄膜トランジスタを含み、薄膜トランジスタのソースにはデータ線を通じて薄膜トランジスタを駆動するように適応される駆動回路が提供されている、請求項 1 記載のタッチディスプレイ装置。

【請求項 15】

10

20

30

40

50

タッチディスプレイ装置が複数個のタッチ制御回路を含み、タッチ制御回路の各々が複数個の共通電極のうち対応する共通電極に接続される、請求項1記載のタッチディスプレイ装置。

**【請求項16】**

タッチ制御回路がクロック同期されるか、又は時分割モードで動作する、請求項15記載のタッチディスプレイ装置。

**【請求項17】**

ディスプレイタッチ制御回路がディスプレイ制御回路によりスキャンを実行することと、次に、タッチ制御回路によりスキャンを実行することとを含む第一の工程を繰り返し行うように適応されるか、

10

ディスプレイタッチ制御回路がタッチ制御回路によりスキャンを実行することと、次に、ディスプレイ制御回路によりスキャンを実行することとを含む第二の工程を繰り返し行うように適応される、請求項1記載のタッチディスプレイ装置。

**【請求項18】**

ディスプレイタッチ制御回路がディスプレイ制御回路により実行されるフレームスキャンを複数個のセグメントに分割し、

ディスプレイ制御回路により実行されるフレームスキャンの前、セグメントの間及びフレームスキャンの後に毎回タッチ制御回路によるスキャンを実行するように構成される、請求項1記載のタッチディスプレイ装置。

20

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本出願は、「TOUCH DISPLAY APPARATUS」の名称で2013年6月6日に中国特許庁に出願された中国特許出願第201310223963.3号の優先権を主張するものであり、その全体を参照として本明細書に取り込む。

**【0002】**

**技術分野**

本発明は、タッチ技術の分野、とりわけ、タッチディスプレイ装置に関する。

**【0003】**

30

**発明の背景**

現在、容量式タッチスクリーンは、さまざまなエレクトロニクス製品に広く応用され、人々の仕事や生活において徐々に普及している。容量式タッチスクリーンのサイズは、絶え間なく増大し、例として、3~6.1インチのスマートモバイルフォン及び10インチよりも大きいタブレットがある。その上、容量式タッチスクリーンの応用分野は、スマートテレビなどにさらに広がるかもしれない。しかし、既存の容量式タッチスクリーンは、一般的に、例えば、いくつかの問題、例えば、貧弱な耐干渉性能、低いフレームレート、より大きい厚さ及び製造プロセスにおける高い複雑性を有する。

**【0004】**

**発明の概要**

40

この観点から、先に述べた問題の少なくとも一つを解決するために、本開示の実施態様によるタッチディスプレイ装置が提供される。

**【0005】**

本開示の実施態様によるタッチディスプレイ装置は：

第一の基板、第二の基板、液晶層及び複数の画素ユニットを包むディスプレイタッチスクリーンであって、液晶層及び複数の画素ユニットが第一の基板と第二の基板との間に位置し、二次元アレイに配列された複数の共通電極をさらに包含するディスプレイタッチスクリーンと、

ディスプレイ制御回路及びタッチ制御回路を含むディスプレイタッチ制御回路であって、それが配線を通じて複数の共通電極に接続され、ディスプレイング状態中、複数の共通

50

電極がディスプレイ制御回路に提供されたコモンレベルに接続され、タッチ検知状態中、複数の共通電極の各々がタッチ検知電極としてタッチ制御回路に接続される、ディスプレイタッチ制御回路とを包含する。

**【0006】**

好ましくは、配線は、複数の共通電極が提供された層に配置されるか、又は

複数の共通電極が提供された層とは異なる層に配置され、それぞれ、ピアホールを通じて複数の共通電極に接続される。

**【0007】**

好ましくは、配線は、データ線が提供された層に配置され、ピアホールを通じて複数の共通電極に接続される。

10

**【0008】**

好ましくは、画素ユニットの各々は画素電極を包含し、配線は、画素電極が提供された層に配置され、ピアホールを通じて複数の共通電極に接続される。

**【0009】**

好ましくは、配線は、ブラックマトリクスの直下に配置される。

**【0010】**

好ましくは、ディスプレイタッチ制御回路は単一のチップであり、ディスプレイ制御回路及びタッチ制御回路が一体化されているか、

ディスプレイタッチ制御回路は二つ以上のチップを包含し、ディスプレイ制御回路とタッチ制御回路とが異なるチップにあるか、又は

20

ディスプレイタッチ制御回路は二つ以上のチップを包含し、チップの各々がディスプレイタッチスクリーンの一部分を制御する。

**【0011】**

好ましくは、ディスプレイタッチ制御回路のチップは、チップオングラス方式で第一の基板又は第二の基板上に実装される。

**【0012】**

好ましくは、ディスプレイ制御回路のチップ及びタッチ制御回路のチップは、チップオングラス方式で第一の基板又は第二の基板上に実装される。

**【0013】**

好ましくは、タッチ制御回路は、共通電極の各々の自己容量を検出するように適応される。

30

**【0014】**

好ましくは、タッチ制御回路は、電流 (current) 共通電極に印加される信号に応じて、電流共通電極及び電流共通電極の周りの共通電極を同時に駆動する工程、又は

電流共通電極に印加される信号に応じて、電流共通電極及び他の共通電極のすべてを同時に駆動する工程を包含する方法によって、電流共通電極の自己容量を検出するように適応される。

**【0015】**

好ましくは、タッチ制御回路は、電流共通電極に印加される信号に応じて、データ線を同時に駆動するようにさらに適応される。

40

**【0016】**

好ましくは、タッチ制御回路は、二次元容量検知アレイによってタッチ位置を決定するように適応される。

**【0017】**

好ましくは、ディスプレイタッチスクリーンは、面内切替構造、フリンジフィールド切替構造又はねじれネマチック構造を有する。

**【0018】**

好ましくは、共通電極は、正多角形の形状、又は

長方形の形状、

円の形状もしくは

50

楕円の形状である。

**【0019】**

凹凸構造が共通電極の端部に提供される。

**【0020】**

好ましくは、複数の共通電極の材料は、酸化インジウムスズのような金属酸化物、又はグラフェンである。

**【0021】**

好ましくは、ディスプレイタッチスクリーンの画素ユニットの各々は薄膜トランジスタを包含し、各薄膜トランジスタのソースにはデータ線を通じて薄膜トランジスタを駆動するように適応された駆動回路が提供される。

10

**【0022】**

好ましくは、タッチ制御ディスプレイ装置は複数のタッチ制御回路を包含し、タッチ制御回路の各々は複数の共通電極のうち対応する共通電極に接続される。

**【0023】**

好ましくは、タッチ制御回路は、クロック同期されるか、又は時分割モードで動作する。

**【0024】**

本開示の実施態様の解決法により、共通電極は、タッチ検知電極としても使用される。それ故に、先行技術と比較して、本開示の解決法では、一つのタッチ検知電極層が省かれ、したがって、ディスプレイタッチスクリーンの厚さ及び重量、ならびにタッチ検知電極層によって引き起こされる光学的損失を減少させ、材料及び製造コストを節減する。その上、本開示の実施態様によるディスプレイタッチスクリーンでは、タッチ検知電極（すなわち、タッチ検知が実行される場合の共通電極）は、二次元アレイに配列される。それ故に、タッチ検知電極間に相互干渉が生じず、ノイズの蓄積が引き起こされない。結果として、ノイズが大幅に減少し、信号対ノイズ比が増大する。

20

**【0025】**

本開示の実施態様による技術的解決法を明確にするために、実施態様の記載に使用される添付図面を、以下のように簡潔に記載する。以下の記載における添付図面が本発明の一部の実施態様にすぎないことは自明である。当業者は、創造的な作業をせずとも、これらの添付図面によって他の添付図面を得ることができる。

30

**【図面の簡単な説明】**

**【0026】**

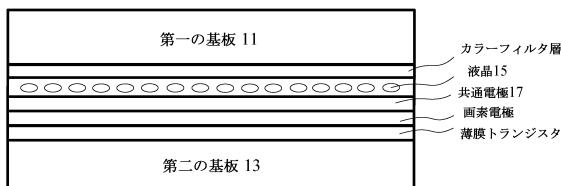

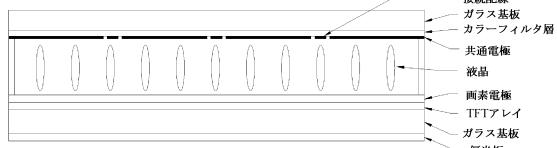

**【図1(a)】**本開示の第一の実施態様によるタッチディスプレイ装置の概略側面図である。

**【図1(b)】**本開示の第一の実施態様によるタッチディスプレイ装置の概略側面図である。

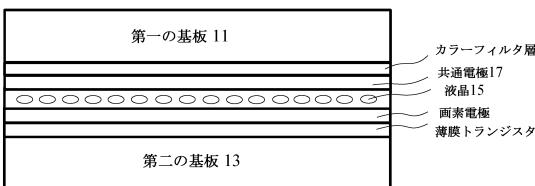

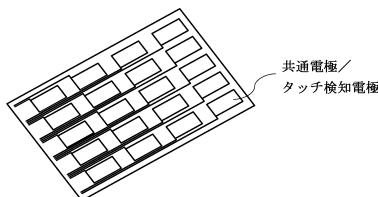

**【図1(c)】**本開示の第一の実施態様による共通電極層の平面図を図示する。

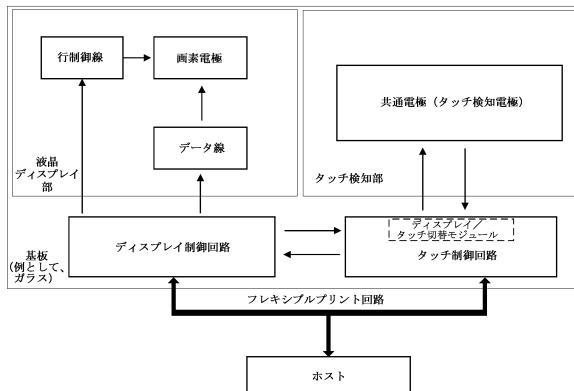

**【図1(d)】**本開示の第一の実施態様によるタッチディスプレイ装置のディスプレイ制御回路及びタッチ制御回路の例を図示する。

**【図1(e)】**本開示の第一の実施態様によるタッチディスプレイ装置のディスプレイタッチ制御回路の概略図である。

40

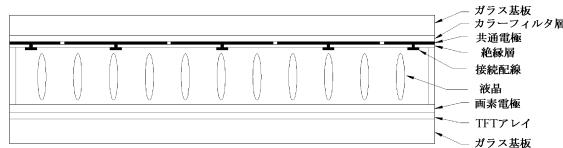

**【図2(a)】**本開示の第二の実施態様によるタッチディスプレイ装置の概略側面図である。

**【図2(b)】**本開示の第二の実施態様による共通電極層の平面図を図示する。

**【図3】**本開示の第二の実施態様による配線の例を図示する。

**【図4】**本開示の第三の実施態様による配線の例を図示する。

**【図5】**本開示の第四の実施態様による配線の例を図示する。

**【図6(a)】**本開示の第五の実施態様による配線の例を図示する。

**【図6(b)】**本開示の第五の実施態様による配線の例を図示する。

**【図7】**本開示の第六の実施態様によるタッチディスプレイ装置の概略側面図である。

50

【図8】本開示の第六の実施態様による配線の例を図示する。

【図9】本開示の第七の実施態様による配線の例を図示する。

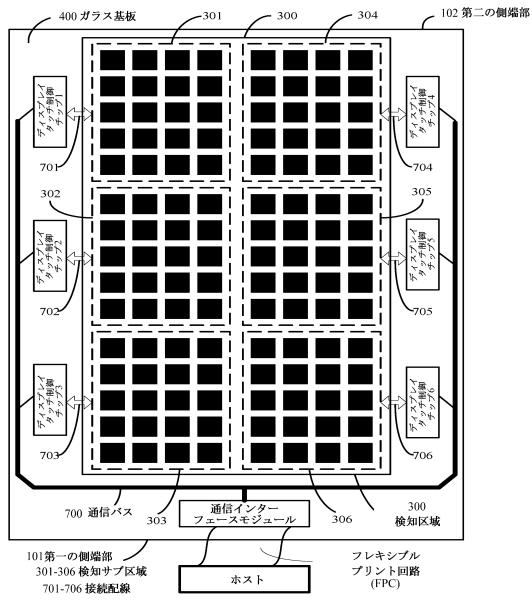

【図10(a)】本開示の第八の実施態様によるタッチディスプレイ装置を図示する。

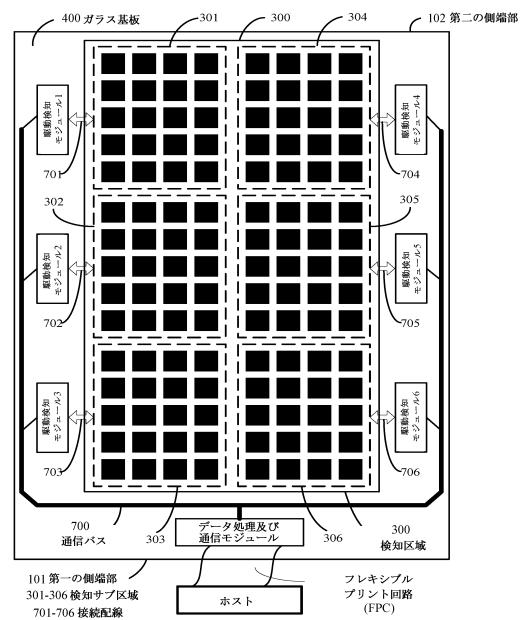

【図10(b)】本開示の第八の実施態様によるタッチディスプレイ装置を図示する。

【0027】

#### 発明の詳細な説明

本開示の目的、特徴及び効果がより明らかとなり、よりよく理解されることができるよう、以下に、本開示の技術的解決法を本開示の実施態様における添付図面と併せて記載する。記載した実施態様が本発明の実施態様の一部分にすぎないことは自明である。創造的な作業をせずとも本開示の実施態様に基づき当業者によって得られる他の実施態様のすべては、本発明の保護範囲に属する。図示を容易にするため、構造を示す断面図は、通常のスケール上で部分的に拡大され、そして図は例にすぎず、本発明の保護範囲を限定するものではないことが理解される。さらに、実際の製造プロセスでは、三次元空間のサイズ、すなわち、長さ、幅及び奥行が考慮される。

10

【0028】

#### 第一の実施態様

本開示の第一の実施態様によるタッチディスプレイ装置は：

第一の基板11、第二の基板13、液晶層15及び複数の画素ユニットを含むディスプレイタッチスクリーンであって、液晶層15及び複数の画素ユニットが第一の基板と第二の基板との間に挟まれ、ディスプレイタッチスクリーンが二次元アレイに配列された複数の共通電極17をさらに包含するディスプレイタッチスクリーンと、

20

ディスプレイ制御回路及びタッチ制御回路を含むディスプレイタッチ制御回路であって、それが配線を通じて複数の共通電極に接続され、ディスプレイが実行される場合では、複数の共通電極がディスプレイ制御回路に提供されたコモンレベルに接続され、タッチ検知が実行される場合では、複数の共通電極の各々がタッチ検知電極としてタッチ制御回路に接続されるディスプレイタッチ制御回路とを包含する。

【0029】

ディスプレイタッチスクリーンは、面内切替(IPSと略される)構造、プリンジフィールド切替(FFSと略される)構造又はねじれネマチック(TNと略される)構造を有することができる。

30

【0030】

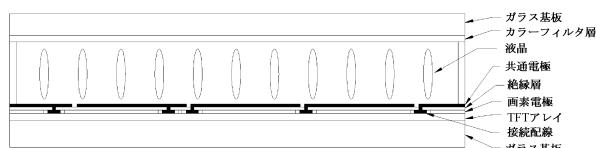

図1(a)は、本開示の第一の実施態様によるタッチディスプレイ装置の例の概略側面図である。タッチディスプレイ装置は、IPS又はFFS構造を有することができる。

【0031】

図1(b)は、本開示の第一の実施態様によるタッチディスプレイ装置のもう一つの例の概略側面図である。タッチ制御ディスプレイ装置は、TN構造を有することができる。

【0032】

図1(c)は、本開示の第一の実施態様によるタッチディスプレイ装置の共通電極層の例を図示する。共通電極の形状が円、楕円、三角形、ストリップ形状、正方形又は他の正多角形であることができる事が当業者に理解されるべきである。その上、共通電極の端部にいくつかの歯(teeth)が提供されることができる。好ましくは、複数の共通電極の材料は、酸化インジウムスズ(ITO)のような金属酸化物、又はグラフェンである。

40

【0033】

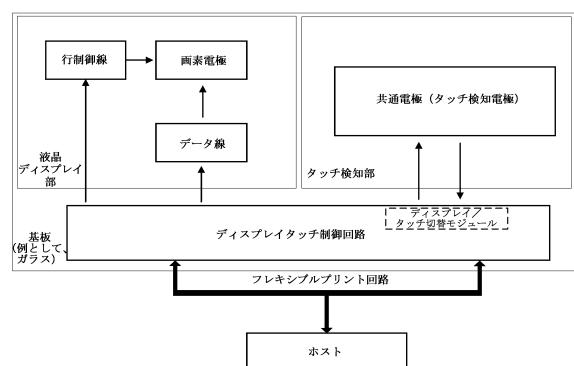

図1(d)は、本開示の第一の実施態様によるタッチディスプレイ装置のディスプレイ制御回路及びタッチ制御回路の例を図示する。本例では、タッチディスプレイ装置は、フレキシブルプリント回路を通じてホストに接続されることができる。図1(d)に図示するように、ディスプレイ制御回路及びタッチ制御回路は、それぞれ、二つの独立したチップに提供される。ディスプレイ制御回路は、配線を通じてタッチディスプレイ装置の液晶ディスプレイ部のデータ線及び行ゲート線に接続される。タッチ制御回路は、配線を通じてタッチ検知部のタッチ検知電極(共通電極)に接続される。タッチ制御回路内のディス

50

プレイ／タッチ切替モジュールを手段として、ディスプレイが実行される場合では、複数の共通電極がディスプレイ制御回路に提供されたコモンレベルに接続され、タッチ検知が実行される場合では、複数の共通電極の各々がタッチ検知電極としてタッチ制御回路に接続される。

**【0034】**

図1(e)は、本開示の第一の実施態様によるタッチディスプレイ装置のディスプレイタッチ制御回路のもう一つの例を図示する。本例では、タッチディスプレイ装置は、フレキシブルプリント回路を通じてホストに接続することができる。図1(e)に図示するように、ディスプレイタッチ制御回路は単一のチップであり、ディスプレイタッチ制御回路は、液晶ディスプレイ部のデータ線及び行ゲート線、ならびにタッチ検知部のタッチ検知電極(共通電極)に接続される。ディスプレイタッチ制御回路内のディスプレイ/タッチ切替モジュールを手段として、ディスプレイが実行される場合では、複数の共通電極がディスプレイ制御回路に提供されたコモンレベルに接続され、タッチ検知が実行される場合では、複数の共通電極の各々がタッチ検知電極としてタッチ制御回路に接続される。

10

**【0035】**

ディスプレイが実行される場合では、共通電極は、ディスプレイタッチスクリーンのディスプレイモジュールの一部分となる。具体的には、共通電極は、共通レベル(Vcom)によって駆動される。共通電極は、異なる画素ユニットと組み合わせられ、スクリーン上の異なる区域における液晶材料にわたり電界を作り出して、各画素ユニットの光束を制御する。

20

**【0036】**

好ましくは、画素ユニットは、画素トランジスタ及び画素電極を包含する。カラーディスプレイモジュールについて、各画素ユニットは、一般的に、それぞれ赤、緑及び青に対応する三つのサブ画素ユニットを包含し、サブ画素ユニットの各々は画素トランジスタ及び画素電極を包含する。

**【0037】**

好ましくは、画素トランジスタは薄膜トランジスタ(TFT)である。

**【0038】**

タッチ検知が実行される場合では、共通電極は、スクリーン上のタッチを検知するためのタッチ検知電極としても使用される。タッチスクリーンがタッチされると、共通電極の容量が変化する。

30

**【0039】**

好ましくは、タッチ位置は、共通電極の各々の自己容量を検出することによって決定される。例として、共通電極の自己容量は、接地に対する共通電極の容量ができる。

**【0040】**

先行技術におけるディスプレイタッチスクリーンでは、タッチ検知電極はディスプレイモジュールと分離し、ディスプレイタッチスクリーンはタッチスクリーンとディスプレイスクリーンとを重畳することにより形成される。しかし、本開示の実施態様の解決法によると、共通電極は、タッチ検知電極としても使用される。それ故に、先行技術と比較して、本開示の解決法ではタッチ検知電極層が省かれ、したがって、ディスプレイタッチスクリーンの厚さ及び重量、ならびにタッチ検知電極層によって引き起こされる光学的損失を減少させ、材料及び製造コストを節減する。その上、本開示の実施態様の解決法を用いると、先行技術におけるタッチ検知電極とディスプレイモジュールとの間の電気的干渉がさらに減少する。

40

**【0041】**

さらに、先行技術におけるディスプレイタッチスクリーンでは、タッチ検知電極が行電極及び列電極を包含し、各行又は各列でノイズが重畳することがある。例として、複数の指が同じ行又は同じ列に置かれた場合では、指の各々によって誘発される電源ノイズが同じ行又は同じ列に重畳することがある。指が多くなるほど、重畳したノイズは大きくなる

50

。しかし、本開示の実施態様によるディスプレイタッチスクリーンでは、タッチ検知電極（すなわち、タッチ検知プロセスにおける共通電極）は、二次元アレイに配列される。タッチ検知電極の各々は、アレイ内のユニットである。ユニット間の相互干渉はない。各行又は各列におけるマトリクスユニットは、互いに異なり、ノイズの重畠が引き起こされない。それ故に、本開示の実施態様によるタッチディスプレイ装置では、最大ノイズの振幅が大幅に減少し、信号対ノイズ比が増大する。

#### 【0042】

好ましくは、タッチ制御回路は、共通電極の各々の自己容量を検出するように構成される。例として、共通電極の自己容量は、接地に対する共通電極の容量であることができる。

10

#### 【0043】

共通電極の各々について、共通電極を駆動すると、タッチ制御回路は、当該共通電極を駆動する信号に応じて、当該共通電極の周りの共通電極又は当該共通電極を除く他の共通電極を同時に駆動することができる。その上、共通電極を駆動すると、タッチ制御回路は、当該共通電極を駆動する信号に応じて、データ線を同時に駆動することもできる。このようにして、検出された共通電極と、検出されていない共通電極との間の電圧の差を減少させることで、検出された電極の容量を減少させ、水滴によって形成される誤タッチを防ぐことができる。

#### 【0044】

20

場合により、タッチ制御回路は：共通電極の各々を駆動し、共通電極の各々から検知したデータを受信するように適応される信号駆動／受信ユニットと；検知したデータによってタッチ位置を決定するように適応される信号処理ユニットとを包含する。具体的には、共通電極の各々について、信号駆動／受信ユニットは、当該共通電極を駆動する信号に応じて、信号駆動／受信ユニットが当該共通電極を駆動するときに同時に、当該共通電極の周りの共通電極又は当該共通電極を除く他の共通電極を駆動するように適応されることがある。その上、共通電極の各々について、信号駆動／受信ユニットは、当該共通電極を駆動する信号に応じて、信号駆動／受信ユニットが当該共通電極を駆動するときに同時にデータ線を駆動するよう構成されることもできる。

30

#### 【0045】

好ましくは、タッチ制御回路は、二次元容量変化アレイによってタッチ位置を決定するように構成される。

#### 【0046】

その上、共通電極は、同時に又は群ごとに駆動させることができる。換言すれば、共通電極のすべて又は共通電極の一部分は、一緒に検出される。

#### 【0047】

先行技術では、タッチ検知電極が行電極及び列電極を包含するため、プログレッシブスキャンが採用され、各フレームのタッチ検出時間が長い。この欠陥は、殊のほか、インセルタッチスクリーンに悪影響を及ぼす。動作したディスプレイスクリーンと、動作したタッチスクリーンとの間の相互干渉を減少させるために、ディスプレイスクリーンが動作している際はタッチスクリーンの動作を停止させ、タッチスクリーンが動作している際はディスプレイスクリーンの動作を停止させる。例として、60Hz（すなわち、フレーム当たり16.7ms）の動作周波数を用いるインセルスクリーンは、一般的に、ディスプレイのスキヤニング時間に10～12msを必要とする。したがって、タッチを検出するためのスキヤニング時間が極めて短いと、既存のインセルスクリーンにより低い信号対ノイズ比をもたらす。しかし、本開示の実施態様によるタッチディスプレイ装置では、電極の各々は、タッチ検出チップに接続される。並列スキヤニングモードを使用することにより、タッチを検出するためのスキヤニング時間は、理論上、先行技術において一つの行を検出するための時間と等しくすることができ、先行技術における信号対ノイズ比を達成し得る。例

40

50

として、16行及び28列のインセルタッチスクリーンでは、各行を検出するための時間をTと仮定すると、既存の構造のスキャニングには16Tが費やされる。しかし、本開示の実施態様の構造によると、各フレームでタッチを検出するための最短時間は1Tにすぎない。

#### 【0048】

ディスプレイタッチ制御回路は、第一の工程を繰り返し行うように構成されることがある。第一の工程は、ディスプレイ制御回路によりフレームスキャンを実行することと、次に、タッチ制御回路によりフレームスキャンを実行することとを包含する。すなわち、一つのフレームにディスプレイスキャニングを実行し、次に、そのフレームにタッチ検出スキャニングを実行し、これを何度も繰り返す。

10

#### 【0049】

あるいは、ディスプレイタッチ制御回路は、第二の工程を繰り返し行うように構成される。第二の工程は、タッチ制御回路によりフレームスキャンを実行することと、次に、ディスプレイ制御回路によりフレームスキャンを実行することとを包含する。すなわち、一つのフレームにタッチ検出スキャニングを実行し、次に、そのフレームにディスプレイスキャニングを実行し、これを何度も繰り返す。

#### 【0050】

さらに、各フレームについて、ディスプレイスキャニングを複数のセグメントに分割することができ、セグメントの各々においてタッチ検出スキャニングを実行する。このようにして、タッチ検出の周波数は、ディスプレイの周波数の複数倍大きくなる。それ故に、タッチ検出のフレームレートが増大する。換言すると、ディスプレイ制御回路により実行される各フレームスキャンを複数のセグメントに分割し、タッチ制御回路は、ディスプレイ制御回路により実行されるスキャンの前及び後、ならびにセグメントの間に毎回スキャンを実行する。

20

#### 【0051】

##### 第二の実施態様

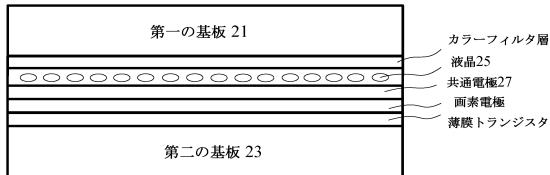

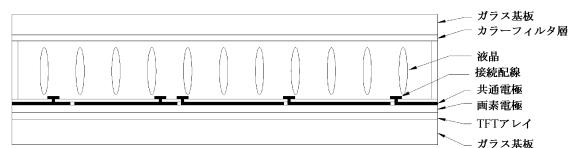

図2(a)は、本開示の第二の実施態様によるタッチディスプレイ装置の例の概略側面図である。

#### 【0052】

図2(a)に図示するように、タッチディスプレイ装置は、第一の基板21、第二の基板23、液晶層25、共通電極層27、薄膜トランジスタ層及びカラーフィルタ(CF)層を包含し、液晶層25、共通電極層27、薄膜トランジスタ層及びCF層が第一の基板21と第二の基板23との間に配置される。共通電極層は、薄膜トランジスタ層の、液晶層と向かい合う側に配置される。場合により、タッチディスプレイ装置は、第二の偏光層、第一の偏光層及びカバーレンズをさらに包含する。例として、タッチディスプレイ装置は、IPS構造を有する。タッチディスプレイ装置は、本実施態様ではFFS構造を有することもできる。

30

#### 【0053】

複数の画素ユニットは、薄膜トランジスタ層に形成される。

#### 【0054】

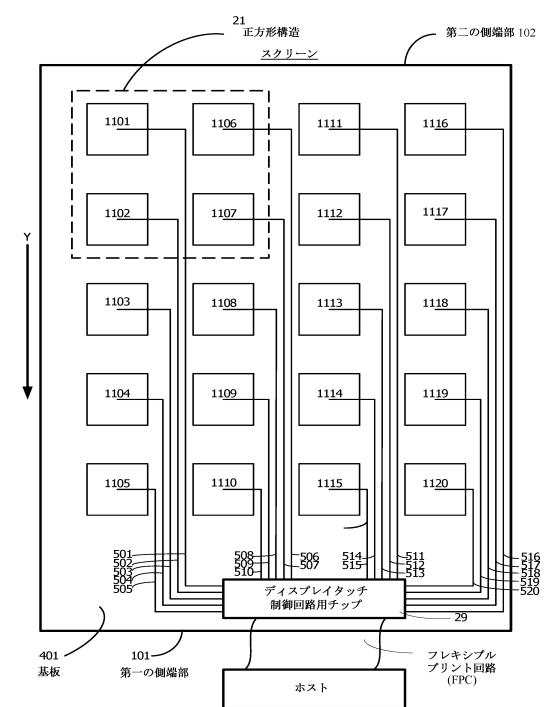

複数の共通電極は共通電極層に形成され、複数の共通電極は二次元アレイ、例えば、マトリクスアレイに配列される。図2(b)は、本開示の第二の実施態様による共通電極層の例の平面図を図示する。

40

#### 【0055】

タッチディスプレイ装置は、ディスプレイタッチ制御回路をさらに包含する。ディスプレイタッチ制御回路は、ディスプレイ制御回路及びタッチ制御回路を包含する。ディスプレイが実行される場合では、複数の共通電極がディスプレイ制御回路に提供されたコモンレベルに接続されるように、ディスプレイタッチ制御回路が配線を通じて複数の共通電極に接続され、タッチ検知が実行される場合では、複数の共通電極の各々がタッチ検知電極としてタッチ制御回路に接続される。

50

**【0056】**

図2(b)に図示するように、例として、共通電極層は、複数の共通電極(タッチ検知電極)1101～1120を包含する。例として、図2(b)は、フレキシブルプリント回路(FPC)、ディスプレイタッチ制御回路29及びホストをさらに図示する。本例では、タッチディスプレイ装置は、フレキシブルプリント回路を通じてホストに接続されることができる。好ましくは、共通電極の材料は、酸化インジウムスズ(ITO)のような金属酸化物、又はグラフェンである。

**【0057】**

共通電極は、正方形、矩形、ストリップ、菱形又は任意の他の多角形の形状であることができ、三角形、円又は楕円の形状であることもできる。さらに、いくつかの歯を共通電極の端部に提供することができる。共通電極のパターンは、一貫していることも、一貫していないこともできる。例えば、図2(b)では、共通電極は、すべて正方形の形状(例えば、長さ及び幅の両方が5mmに等しい)であり、長方形アレイに配列される。

10

**【0058】**

本実施態様では、共通電極1101～1120をディスプレイタッチ制御回路に接続するための配線501～520は、共通電極層に配置される。例えば、共通電極層は、第一の側端部101及び第二の側端部102を有する。共通電極1101に接続された配線501は共通電極層の内側でY方向に第一の側端部101に向かって伸長し、共通電極1102に接続された配線502は共通電極層の内側でY方向に第一の側端部101に向かって伸長し、などである。共通電極層内の配線501～520の配置の設計は、簡素な構造及び低コストを有する。

20

**【0059】**

図3は、本開示の第二の実施態様による配線の例を図示する。

**【0060】**

配線501～520の材料は、酸化インジウムスズ(ITO)などの金属酸化物、又はグラフェン、又は金属であることができる。好ましくは、配線501～520は、共通電極が提供された層に配置され、ブラックマトリクスの直下に位置する。ブラックマトリクスの下に配線を配置することにより、金属配線によって引き起こされる可能性がある光反射及び酸化インジウムスズのエッチングによって生成されるトレースを回避することができる。

30

**【0061】**

好ましくは、図2(b)のディスプレイタッチ制御回路用チップ29は、チップオングラス(COGと略される)方式で基板に実装される。例えば、5インチのスクリーンでは、(対応する配線を包含する)共通電極の各々が5mm×5mmの面積を有し、スクリーンが264個の共通電極を包含すると仮定される。従来の方式でパッケージされたディスプレイタッチ制御回路用チップ29には少なくとも264個のピンが必要であり、そうすることではじめて、チップは、プリント回路基板上に表面実装ができる。このケースでは、極めて幅広のフレキシブルプリント回路を要する。それ故に、歩留まりが低くなり、コストが高くなる。しかし、COG方式を使用することにより、ディスプレイタッチ制御回路用チップ29は、基板上に直接実装される。そのようにして、歩留まりが増大し、パッケージコストを減少させ、タッチディスプレイ装置の容積が減少する。

40

**【0062】**

場合により、ディスプレイタッチ制御回路29は、フレキシブルプリント回路を通じてホストに接続される。ホストは、フレキシブルプリント回路を通じてディスプレイタッチ制御回路29と通信する。

**【0063】**

一般的に、タッチが発生したときのタッチ検知電極の容量の変化は、タッチ検知電極の覆われた面積に比例する。それ故に、各タッチ検知電極の容量の変化は、覆われた面積を指示する。例として、重心アルゴリズムを使用することにより、タッチ位置は、二次元容量変化アレイによって決定される。

50

**【 0 0 6 4 】**

ディスプレイタッチ制御回路 29 は単一のチップであることができ、ディスプレイ制御回路及びタッチ制御回路が一体化されている。あるいは、ディスプレイタッチ制御回路 29 は、二つ以上のチップを包含することができ、ディスプレイ制御回路とタッチ制御回路とが異なるチップに提供される。

**【 0 0 6 5 】**

好ましくは、本開示の実施態様によるタッチディスプレイ装置では、薄膜トランジスタの各々のソース電極用に駆動回路が提供され、駆動回路がデータ線を通じて薄膜トランジスタを駆動する。このようにして、液晶層における電界分布を、薄膜トランジスタのソース電極の電圧を調節することにより変化させることができ、共通電極の自己容量を減少させ、タッチ制御の感度を増大させる。10

**【 0 0 6 6 】****第三の実施態様**

本実施態様によるタッチディスプレイ装置は、IPS 構造又はFFS 構造も有する。この実施態様と第二の実施態様との間の差は、配線の位置にある。図 4 は本開示の第三の実施態様による配線の例を図示し、配線 501 ~ 503 は共通電極が提供された層とは異なる層に配置される。具体的には、配線は、画素電極が提供された層に配置され、ピアホールを通じてそれぞれの共通電極に接続することができる。

**【 0 0 6 7 】**

配線 501 ~ 503 の材料は、酸化インジウムスズ (ITO) などの金属酸化物、又はグラフェン、又は金属であることができる。好ましくは、配線 501 ~ 503 は、ブラックマトリクスの直下に配置される。ブラックマトリクスの下に配線を配置することにより、金属配線によって引き起こされる可能性がある光反射及び酸化インジウムスズのエッティングによって生成されるトレースを回避することができる。20

**【 0 0 6 8 】**

本実施態様の他の部分の記載は、第二の実施態様を参照し、ここでは繰り返さない。

**【 0 0 6 9 】****第四の実施態様**

この実施態様と第三の実施態様との間の差は、配線の位置にある。図 5 は本開示の第四の実施態様による配線の例を図示し、配線 501 ~ 503 は共通電極が提供された層とは異なる層に配置される。具体的には、配線は、個別層に配置され、ピアホールを通じてそれぞれの共通電極に接続することができる。30

**【 0 0 7 0 】**

本実施態様の他の部分の記載は、第三の実施態様を参照し、ここでは繰り返さない。

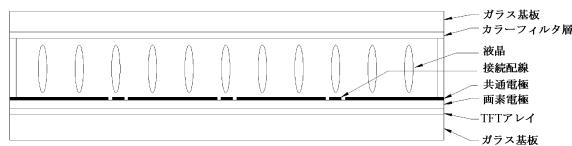

**【 0 0 7 1 】****第五の実施態様**

この実施態様と第四の実施態様との間の差は、配線の位置にある。図 6 (a) 及び 6 (b) は本開示の第五の実施態様による配線の例を図示し、配線 501 ~ 503 は共通電極が提供された層とは異なる層に配置される。具体的には、配線は、データ線が提供された層に配置される。図 6 (a) に図示するように、データ線層は、TFT アレイの下に位置する。図 6 (b) に図示するように、データ線層は、TFT アレイ上に位置する。配線は、ピアホールを通じてそれぞれの共通電極に接続することができる。40

**【 0 0 7 2 】**

本実施態様の他の部分の記載は、第四の実施態様を参照し、ここでは繰り返さない。

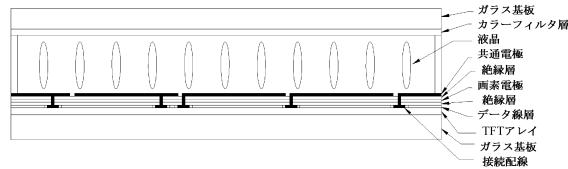

**【 0 0 7 3 】****第六の実施態様**

図 7 は、本開示の第六の実施態様によるタッチディスプレイ装置の概略側面図である。図 7 に図示するように、タッチディスプレイ装置は第一の基板 61、第二の基板 63、液晶層 65、共通電極層 67、薄膜トランジスタ層及びカラーフィルタ層を包含し、液晶層 65、共通電極層 67、薄膜トランジスタ層及びカラーフィルタ層は第一の基板 61 と第50

二の基板 63との間に配置される。共通電極層は、カラーフィルタ層の、液晶層と向かい合う側に配置される。場合により、タッチディスプレイ装置は、第二の偏光層、第一の偏光層及びカバーレンズをさらに包含する。例として、タッチディスプレイ装置は、TN構造を有する。

#### 【0074】

複数の画素ユニットは、薄膜トランジスタ層に形成される。複数の共通電極は、共通電極層に形成され、二次元アレイに配列される。

#### 【0075】

タッチディスプレイ装置は、ディスプレイタッチ制御回路をさらに包含する。ディスプレイタッチ制御回路は、ディスプレイ制御回路及びタッチ制御回路を包含する。ディスプレイが実行される場合では、複数の共通電極がディスプレイ制御回路に提供されたコモンレベルに接続されるように、ディスプレイタッチ制御回路が配線を通じて複数の共通電極に接続され、タッチ検知が実行される場合では、複数の共通電極の各々がタッチ検知電極としてタッチ制御回路に接続される。10

#### 【0076】

タッチ制御回路用チップは、COG方式で基板に実装することができる。

#### 【0077】

本実施態様の共通電極層の平面図は、第二の実施態様のそれと同じ又は同様である。図2(b)に図示するように、共通電極層は、複数の共通電極(タッチ検知電極)を包含する。20

#### 【0078】

図8は、本開示の第六の実施態様による配線の例を図示する。

#### 【0079】

本実施態様では、共通電極1101～1120をディスプレイタッチ制御回路に接続するための配線501～520は、共通電極層に配置される。例えば、共通電極層は、第一の側端部101及び第二の側端部102を有する。共通電極1101に接続された配線501は共通電極層の内側でY方向に第一の側端部101に向かって伸長し、共通電極1102に接続された配線502は共通電極層の内側でY方向に第一の側端部101に向かって伸長し、などである。30

#### 【0080】

本実施態様の他の部分の記載は、第二の実施態様を参照し、ここでは繰り返さない。

#### 【0081】

### 第七の実施態様

本実施態様によるタッチディスプレイ装置は、TN構造も有する。この実施態様と第六の実施態様との間の差は、配線の位置にある。図9は本開示の第七の実施態様による配線の例を図示し、配線501～503は共通電極が提供された層とは異なる層に配置される。具体的には、配線は、個別層に配置され、ピアホールを通じてそれぞれの共通電極に接続されることができる。

#### 【0082】

本実施態様の他の部分の記載は、第六の実施態様を参照し、ここでは繰り返さない。40

#### 【0083】

### 第八の実施態様

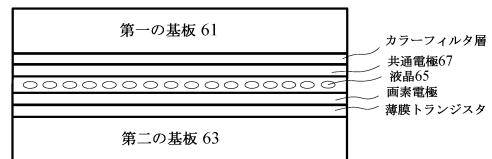

図10(a)は、本開示の第八の実施態様によるタッチディスプレイ装置を図示する。この実施態様は、ディスプレイタッチ制御チップが二つ以上のチップにおいて提供され、チップの各々がディスプレイタッチスクリーンの対応する区域を制御するように適応されるという点において、先に挙げた実施態様とは異なる。

#### 【0084】

例として、共通電極層は、複数のサブ区域に分割される。サブ区域の各々は、二次元アレイに配列され、一つのディスプレイタッチ制御チップに接続された複数の共通電極を包含する。50

**【0085】**

ディスプレイタッチ制御チップの各々は、クロック同期されることがある。あるいは、ディスプレイタッチ制御チップは、時分割モードで動作することができる。

**【0086】**

図10(a)に図示するように、共通電極層は複数のサブ区域301～306を包含し、サブ区域の各々は複数の共通電極を包含する。共通電極の形状は、正方形、菱形もしくは他の多角形、又は三角形、円もしくは楕円である。その上、いくつかの歯を共通電極の端部に提供することができる。サブ区域の各々について、共通電極のパターンは、一貫していることも、一貫していないこともできる。好ましくは、共通電極の材料は、酸化インジウムスズ(ITO)などの金属酸化物、又はグラフェン、又は金属などの導電材料である。

10

**【0087】**

サブ区域の各々について、共通電極の各々は、それぞれ、配線を通じて、共通電極に対応するディスプレイタッチ制御チップ1～6の一つに接続されることができる。ディスプレイタッチ制御チップ1～6は、COG方式で第一の基板又は第二の基板に実装されるこができる。

**【0088】**

ディスプレイタッチ制御チップ1～6は通信バス700を通じて、通信バス接続ターミナルに接続されることができ、通信バス接続ターミナルはフレキシブルプリント回路13を通じてホストに接続されることができる。好ましくは、通信バス700は、検知区域を除く非透明区域に配置され、酸化インジウムスズ(ITO)線などの金属酸化物線、又はグラフェン線であることができ、金属線であることもできる。

20

**【0089】**

図10(b)は、本開示の第七の実施態様によるもう一つのタッチディスプレイ装置を図示する。この実施態様は、駆動検知モジュールが二つ以上のチップにおいて提供され、モジュールの各々がディスプレイタッチスクリーンの対応する区域を制御するように適応されるという点において図10(a)に記載した実施態様とは異なる。

**【0090】**

例として、共通電極層は、複数のサブ区域に分割される。サブ区域の各々は、二次元アレイに配列され、一つの駆動検知モジュールに接続された複数の共通電極を包含する。

30

**【0091】**

駆動検知モジュールは、クロック同期されることがある。あるいは、駆動検知モジュールは、時分割モードで動作することができる。

**【0092】**

図10(b)に図示するように、共通電極層は複数のサブ区域301～306を包含し、サブ区域の各々は複数の共通電極を包含する。共通電極の形状は、正方形、菱形もしくは他の多角形、又は三角形、円もしくは楕円である。いくつかの歯を共通電極の端部に提供することができる。サブ区域の各々について、それぞれの共通電極のパターンは、一貫していることも、一貫していないこともできる。好ましくは、共通電極の材料は、酸化インジウムスズ(ITO)などの金属酸化物、又はグラフェンである。

40

**【0093】**

サブ区域の各々について、共通電極の各々は、それぞれ、配線を通じて、共通電極に対応する駆動検知モジュール1～6の一つに接続されることができる。駆動検知モジュール1～6は、COG方式で基板に実装されることができる。

**【0094】**

駆動検知モジュール1～6は通信バス700を通じてデータ処理・通信モジュールに接続されることができ、データ処理・通信モジュールはフレキシブルプリント回路13を通じてホストに接続されることができる。好ましくは、通信バス700は、検知区域を除く非透明区域に配置され、酸化インジウムスズ(ITO)線などの金属酸化物線、又はグラフェン線であることができ、金属線であることもできる。

50

## 【0095】

本実施態様は、大型スクリーンに特に好適である。二つ以上のディスプレイタッチ制御チップは、同時にタッチパネルをスキャンすることができる。それ故に、良好な画像取得速度を達成することができる。

## 【0096】

詳細な説明では、実施態様間の差に重きを置いた。実施態様間の同じ又は同様の部分について、それらを互いから参照することができる。

## 【0097】

本明細書に開示した実施態様の先の記載は、当業者による本発明の実施又は使用を可能にする。実施態様に対する非常に多くの変形が当業者に明らかであり、本発明の範囲を逸することなく、本明細書における一般原理を他の実施態様にて実施することができる。それ故に、本発明は、本明細書に記載した実施態様に限定されず、本明細書に開示した原理及び新規の特徴に矛盾しない最も広い範囲に従う。10

【図1(a)】

【図1(b)】

【図1(c)】

【図1(d)】

【図1(e)】

【図2(a)】

【図2(b)】

【図3】

【図4】

【図5】

【図6(a)】

【図6(b)】

【図7】

【図8】

【図9】

【図10(a)】

【図10(b)】

---

フロントページの続き

(72)発明者 欧陽広

中華人民共和国広東省深 せん 市南山区科技園南区アール3 - ビー棟4楼

審査官 原 秀人

(56)参考文献 米国特許出願公開第2013/0076648(US, A1)

特開2010-198615(JP, A)

特開2013-097469(JP, A)

特開2012-059073(JP, A)

米国特許出願公開第2011/0050585(US, A1)

米国特許出願公開第2008/0309627(US, A1)

特開2010-191504(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 3 / 041

G 06 F 3 / 044