(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6065554号

(P6065554)

(45) 発行日 平成29年1月25日(2017.1.25)

(24) 登録日 平成29年1月6日(2017.1.6)

(51) Int.CI.

HO3K 5/08 (2006.01)

F 1

HO3K 5/08

E

請求項の数 5 (全 13 頁)

(21) 出願番号 特願2012-264808 (P2012-264808)

(22) 出願日 平成24年12月3日 (2012.12.3)

(65) 公開番号 特開2014-110569 (P2014-110569A)

(43) 公開日 平成26年6月12日 (2014.6.12)

審査請求日 平成27年9月14日 (2015.9.14)

(73) 特許権者 000005234

富士電機株式会社

神奈川県川崎市川崎区田辺新田1番1号

(74) 代理人 100112003

弁理士 星野 裕司

(74) 代理人 100145344

弁理士 渡辺 和徳

(72) 発明者 中島 洋至

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

審査官 白井 亮

最終頁に続く

(54) 【発明の名称】 比較器

## (57) 【特許請求の範囲】

## 【請求項 1】

差動対をして基準電圧および入力電圧をゲートにそれぞれ入力する一対の入力MOS-FET、ゲートを相互に接続すると共にドレインを前記一対の入力MOS-FETの各ドレインにそれぞれ接続した一対の負荷MOS-FET、および前記一対の入力MOS-FETのソースに一定電流を供給する定電流源とを具備した差動増幅型の比較器本体と、

前記入力MOS-FETにおけるゲート酸化膜の耐圧以下のブレークダウン電圧特性を有し、前記一対の入力MOS-FETの各ゲート・ソース間にそれぞれ順方向に並列接続されたツェナーダイオードと、

前記比較器本体の出力電圧を前記一対の負荷MOS-FETのゲートに負帰還して該出力電圧の出力振幅を制限する帰還MOS-FETと

電源電圧以上の逆耐圧特性を有し、前記定電流源と前記一対の入力MOS-FETの各ソースとの間にそれぞれ介装された半導体整流素子とを具備したことを特徴とする比較器。

## 【請求項 2】

前記一対の入力MOS-FETはpチャネル型のMOS-FETであって、前記一対の負荷MOS-FETはnチャネル型のMOS-FETからなる請求項1に記載の比較器。

## 【請求項 3】

前記帰還MOS-FETは、ドレインおよびゲートを前記一対の入力MOS-FETの一方のドレインに接続すると共に、ソースを前記一対の負荷MOS-FETのゲートに接続

10

20

したものである請求項1に記載の比較器。

**【請求項 4】**

前記半導体整流素子は、整流ダイオードまたはダイオード接続したMOS-FETからなる請求項1に記載の比較器。

**【請求項 5】**

請求項1に記載の比較器であって、

更に前記比較器本体の比較出力電圧を反転して外部出力するCMOS構造のインバータ回路を備えることを特徴とする比較器。

**【発明の詳細な説明】**

**【技術分野】**

10

**【0001】**

本発明は、CMOS構成の差動増幅型の比較器に係り、特に入力MOS-FETのゲート酸化膜の保護機能を備えた比較器に関する。

**【背景技術】**

**【0002】**

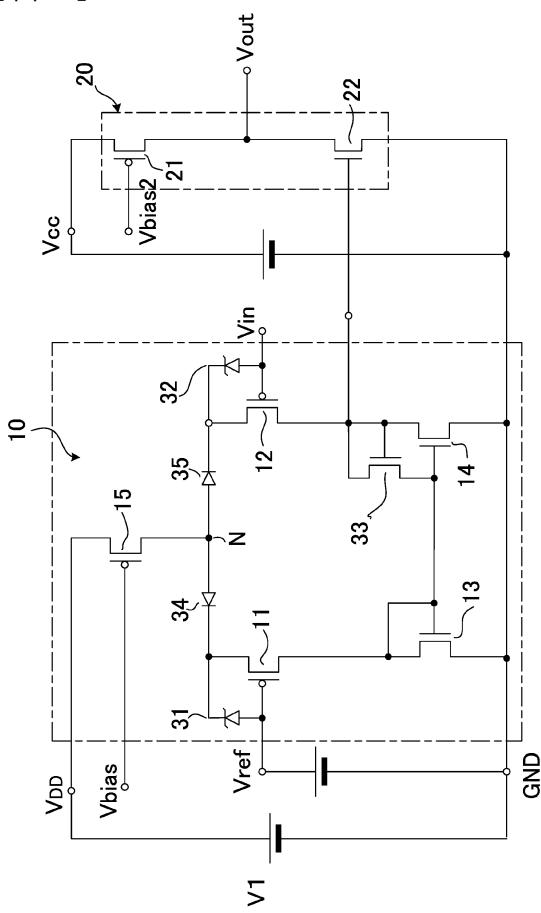

基準電圧V<sub>ref</sub>と入力電圧V<sub>in</sub>とを比較し、その大小関係に応じて出力電圧V<sub>out</sub>を反転する比較器は、各種適用されている。図8はCMOS構成の差動増幅型の従来一般的な比較器の概略構成を示している。この比較器は、概略的には差動増幅型の比較器本体10と、この比較器本体10の出力電圧を反転して出力するインバータ回路20とにより構成される。

20

**【0003】**

前記比較器本体10は、差動対をして基準電圧V<sub>ref</sub>および入力電圧V<sub>in</sub>をそれぞれゲートに入力する一対のpチャネル型の入力MOS-FET11,12を備える。これらの入力MOS-FET11,12は、そのソースを定電流源に接続すると共に、各ドレインにnチャネル型の負荷MOS-FET13,14をそれぞれ能動負荷として接続して、CMOS構成の差動増幅器を構築する。

**【0004】**

ここで前記負荷MOS-FET13,14は、ソースを接地すると共にゲートを相互に接続し、ドレインを前記一対の入力MOS-FET11,12の各ドレインにそれぞれ接続したものである。また前記負荷MOS-FET13,14の内、前記基準電圧V<sub>ref</sub>が与えられる側の前記負荷MOS-FET13は、そのゲート・ドレイン間を接続することでダイオードとして用いられている。尚、前記定電流源は、ソースを電源Vに接続し、ゲートに所定のバイアス電圧V<sub>bias</sub>が印加されて前記一対の入力MOS-FET11,12のソースに一定電流を供給するpチャネル型のMOS-FET15により構成される。

30

**【0005】**

一方、前記インバータ回路20は、カスケード接続されて前記電源Vと接地(GND)間に介装されたpチャネル型のMOS-FET21およびnチャネル型のMOS-FET22により構成される。これらのMOS-FET21,22からなるCMOS構成のインバータ回路20は、前記比較器本体10の出力である入力MOS-FET12のドレイン電圧を各ゲートに入力して相補的にオン動作し、その出力電圧(ドレイン電圧)V<sub>out</sub>を反転する。

40

**【0006】**

このように構成された比較器は、前記入力電圧V<sub>in</sub>が前記基準電圧V<sub>ref</sub>よりも低いとき(V<sub>in</sub><V<sub>ref</sub>)、前記基準電圧V<sub>ref</sub>が印加される入力MOS-FET11がオフし、前記入力電圧V<sub>in</sub>が印加される入力MOS-FET12がオンする。すると前記入力MOS-FET11のドレイン電圧が略接地電位(0V)となり、前記負荷MOS-FET13,14をオフにする。そして前記入力MOS-FET12のドレイン電圧(比較器本体10の出力)がHレベルとなる。この結果、前記インバータ回路20における前記MOS-FET21がオフし、前記MOS-FET22がオンとなって該インバータ回路20の出力電圧V<sub>out</sub>はLレベル(接地電位;0V)となる。

50

## 【0007】

また前記入力電圧  $V_{in}$  が前記基準電圧  $V_{ref}$  を超えたときには ( $V_{in} > V_{ref}$ ) 、前記基準電圧  $V_{ref}$  が印加される入力 MOS-FET 11 がオンし、前記入力電圧  $V_{in}$  が印加される入力 MOS-FET 12 がオフする。すると前記負荷 MOS-FET 13, 14 がオンとなり、前記入力 MOS-FET 12 のドレイン電圧 (比較器本体 10 の出力) が前記負荷 MOS-FET 14 を介して略接地電位 (0 V) となる。この結果、前記インバータ回路 20 における前記 MOS-FET 21 がオンし、前記 MOS-FET 22 がオフとなって該インバータ回路 20 の出力電圧  $V_{out}$  が H レベル (略電源電圧 ; 例えは 5 V) に反転する。

## 【0008】

10 このように構成され、入力電圧  $V_{in}$  に応じて反転動作する比較器については、例えは特許文献 1 等に詳しく紹介されている。

## 【先行技術文献】

## 【特許文献】

## 【0009】

## 【特許文献 1】特開昭 55 - 104766 号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0010】

20 上述した構成の比較器は、その入力段が入力 MOS-FET 11, 12 により構成されるので、その入力インピーダンスが高いと言う利点を有する。しかしその反面、比較器に入力可能な入力電圧  $V_{in}$  の電圧範囲が前記入力 MOS-FET 11, 12 のゲート酸化膜の厚みによって規定されると言う欠点がある。例えはゲート酸化膜の薄い MOS-FET に高いゲート・ソース間電圧  $V_{gs}$  が印加されると、その強い電界によってゲート酸化膜に破壊が生じる。

## 【0011】

ちなみに一般的な  $\text{SiO}_2$  からなるゲート酸化膜の場合、その破壊電界強度は略  $2.0 \times 10^6 \text{ V/cm}$  程度である。従って高い入力電圧  $V_{in}$  を直接比較可能な比較器を構築するには、例えはゲート酸化膜の厚い MOS-FET を用いれば良い。しかしゲート酸化膜の厚い MOS-FET を用いると、比較器を集積回路化する上でその微細化が困難となる。しかも MOS-FET の閾値電圧の上昇や、スイッチング速度の低下等の問題が生じることが否めない。

## 【0012】

図 9 は前述した構成の比較器において、電源電圧  $V_{DD}$  を 4.2 V、基準電圧  $V_{ref}$  を  $V_{DD}/2$  (= 2.1 V) とし、入力電圧  $V_{in}$  を 0 ~  $V_{DD}$  に亘って変化させたときの前記入力 MOS-FET 11, 12 のゲート・ソース間電圧  $V_{gs}$  の変化を示すシミュレーション結果である。この例の場合、前記 入力 MOS-FET 12 のゲート・ソース間 には、該入力 MOS-FET 11, 12 のゲート間の電圧差が直接加わるので、最大で  $\pm V_{DD}/2$  ( $\pm 2.1 \text{ V}$ ) の電圧が加わることになる。

## 【0013】

40 また前記基準電圧  $V_{ref}$  を、例えは接地電位 (0 V) に近い低電位、または電源電圧  $V_{DD}$  の近い高電位に設定した場合、入力電圧  $V_{in}$  の変化に伴って前記入力 MOS-FET 12 のゲート・ソース間には前述した 4.2 V の電源電圧  $V_{DD}$  に近い高電圧が印加される可能性がある。すると前記入力 MOS-FET 11, 12 のゲート酸化膜が薄い場合には、前述したように該入力 MOS-FET 11, 12 のゲート酸化膜が破壊する虞が生じる。

## 【0014】

このような問題を解消する為に、従来一般的には図 8 に記すように、直列接続した抵抗  $R_1, R_2$  を用いて入力電圧  $V_{in}'$  を分圧して入力することが行われている。しかし分圧抵抗  $R_1, R_2$  を用いた場合、比較器を集積回路化する上で回路面積の増大のみならず、分圧抵抗比のバラツキに起因する精度の低下、更には S/N 比の劣化に伴う誤動作の発生等

10

20

30

40

50

の新たな問題が生じることが否めない。

**【0015】**

本発明はこのような事情を考慮してなされたもので、その目的は、ゲート酸化膜の薄いMOS-FETの破壊を招くことなく、高い入力電圧を直接比較することのできる簡易な構成の比較器を提供することにある。

**【課題を解決するための手段】**

**【0016】**

上述した目的を達成するべく本発明に係る比較器は、差動対をなして基準電圧および入力電圧をゲートにそれぞれ入力する一対の入力MOS-FETと、ゲートを相互に接続すると共にドレインを前記一対の入力MOS-FETの各ドレインにそれぞれ接続した一対の負荷MOS-FETと、前記一対の入力MOS-FETのソースに一定電流を供給する定電流源とを具備した差動増幅型の比較器本体を備え、10

特に前記一対の入力MOS-FETの各ゲート・ソース間に、該入力MOS-FETにおけるゲート酸化膜の耐圧以下のブレークダウン電圧特性を有するツェナーダイオードをそれぞれ順方向に並列接続したことを特徴としている（第1の発明）。

**【0017】**

また本発明に係る比較器は、前記ツェナーダイオードに加えて、更に前記比較器本体の出力電圧を前記一対の負荷MOS-FETのゲートに負帰還して該出力電圧の振幅を制限する帰還MOS-FETを設けたことを特徴としている（第2の発明）。20

**【0018】**

更に本発明に係る比較器は、前記ツェナーダイオードおよび帰還MOS-FETに加えて、更に電源電圧以上の逆耐圧特性を有する半導体整流素子を、前記定電流源と前記一対の入力MOS-FETの各ソースとの間にそれぞれ介装したことを特徴としている（第3の発明）。

**【0019】**

好ましくは前記一対の入力MOS-FETはpチャネル型のMOS-FETであって、前記一対の負荷MOS-FETはnチャネル型のMOS-FETからなり、CMOS構成の差動増幅回路を構築する。また前記帰還MOS-FETは、そのドレインおよびゲートを前記一対の入力MOS-FETの一方のドレインに接続すると共に、ソースを前記一対の負荷MOS-FETのゲートに接続して設けられる。また前記半導体整流素子は、好ましくは整流ダイオードまたはダイオード接続したMOS-FETからなる。30

**【0020】**

尚、比較器は、出力バッファとして前記比較器本体の出力電圧を反転して外部出力するCMOS構成のインバータ回路を備えることが好ましい。またこのインバータ回路については、前記比較器本体とは別の電源電圧で駆動するようにすることも好ましい。

**【発明の効果】**

**【0021】**

第1の発明に係る比較器によれば、ツェナーダイオードによって差動対をなす入力MOS-FETの各ゲート・ソース間に加わる電圧をクンランプし、そのゲート・ソース間電圧V<sub>gs</sub>を抑えることができる。従って前記入力MOS-FETのゲート酸化膜に高電圧（高電界）が加わることがなくなり、ゲート酸化膜を確実に保護して、その破壊を防ぐことができる。40

**【0022】**

また第2の発明に係る比較器によれば、更に帰還MOS-FETを介する負帰還制御によって前記入力MOS-FETのドレイン電位（出力電位）の変化幅を制限することができる。従って前記入力MOS-FETのゲート・ソース間に加わる電圧を制限し、そのゲート・ソース間電圧V<sub>gs</sub>を抑えることができる。故に前述したツェナーダイオードによる作用・効果と相俟って、前記入力MOS-FETのゲート酸化膜を更に効果的に保護することができる。

**【0023】**

50

そして第3の発明に係る比較器によれば、入力MOS-FETのソース電位が前記定電流源の電流出力端の電位よりも高くなつた際、半導体整流素子によって定電流源からの電流を遮断し、これによつて前記入力MOS-FETのゲート・ソース間に加わる電圧を抑制することができる。従つて上述したツェナーダイオードおよび帰還MOS-FETによる前記入力MOS-FETのゲート酸化膜の保護作用と相俟つて、該入力MOS-FETのゲート酸化膜に対する保護を更に確実にし、その破壊を効果的に防ぐことが可能となる。

#### 【0024】

従つて上記構成の比較器によれば、ゲート酸化膜の薄いMOS-FETを用いた場合であつても、MOS-FETのゲート酸化膜の破壊を招来することなしに高い入力電圧 $V_{in}$ を直接比較することが可能となる。故に、前述したゲート酸化膜の厚いMOS-FETを用いる場合や、分圧抵抗 $R_1, R_2$ を用いた場合のような不具合がない。しかも回路構成自体が簡単なのでその実用的利点が多大である。

10

#### 【図面の簡単な説明】

#### 【0025】

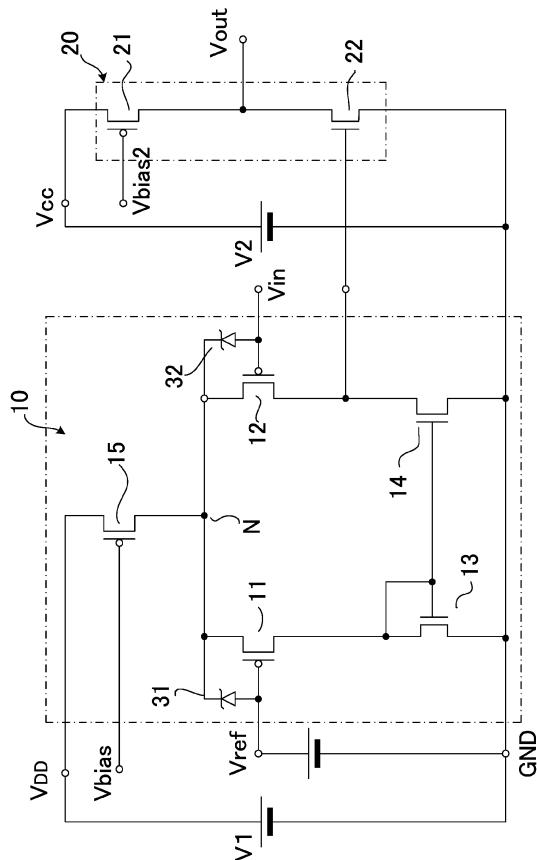

【図1】本発明の第1の実施形態に係る比較器の概略構成図。

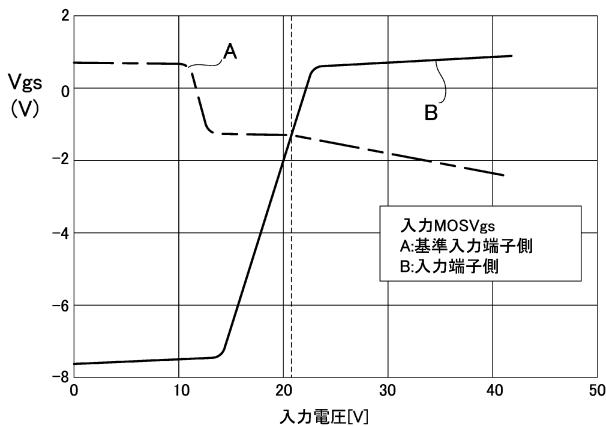

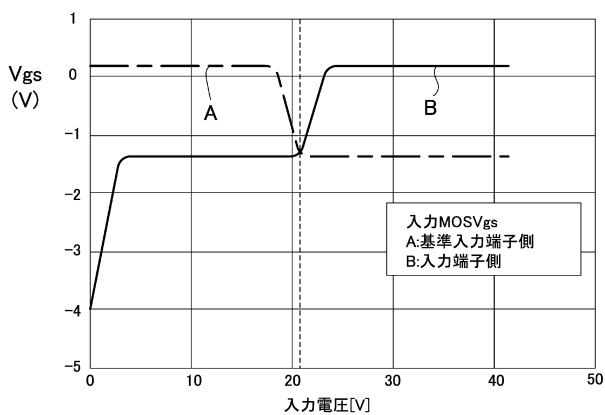

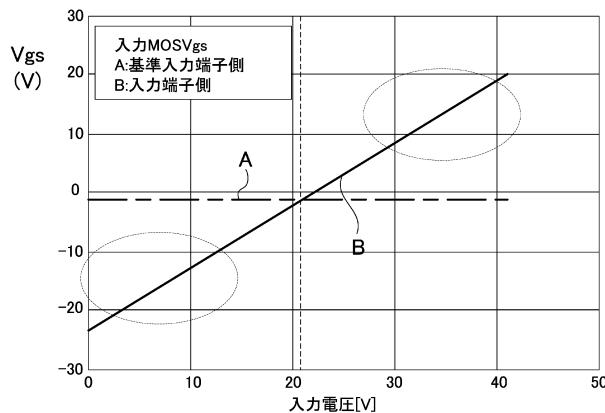

【図2】図1に示す比較器における一対の入力MOS-FETの入力電圧 $V_{in}$ に対するゲート・ソース間電圧 $V_{gs}$ の変化を示す図。

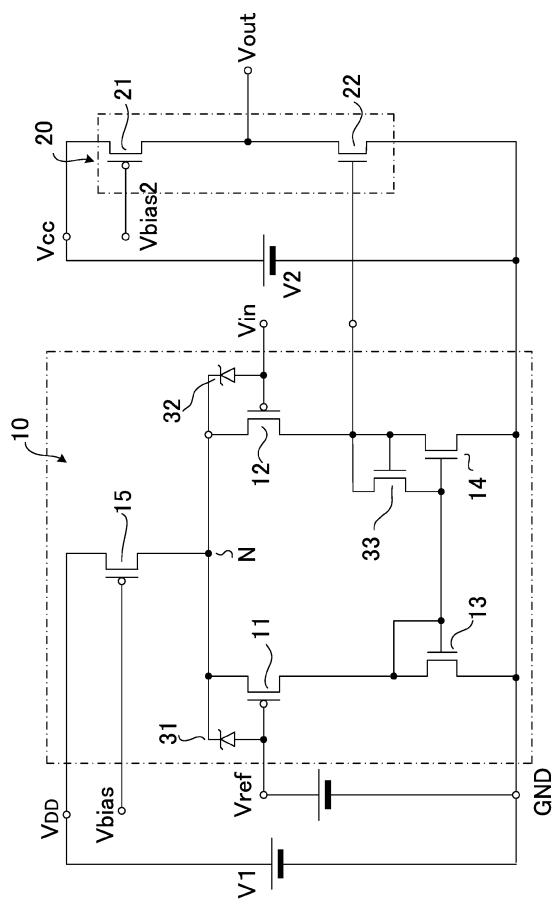

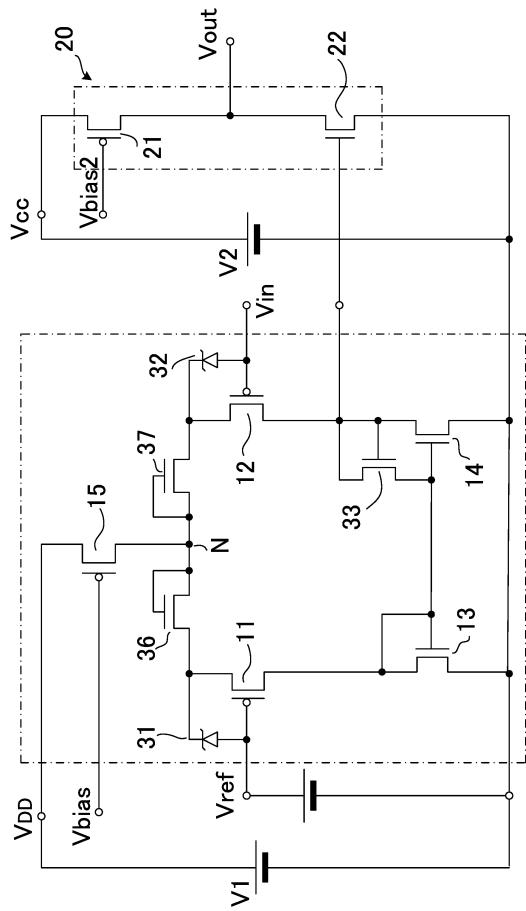

【図3】本発明の第2の実施形態に係る比較器の概略構成図。

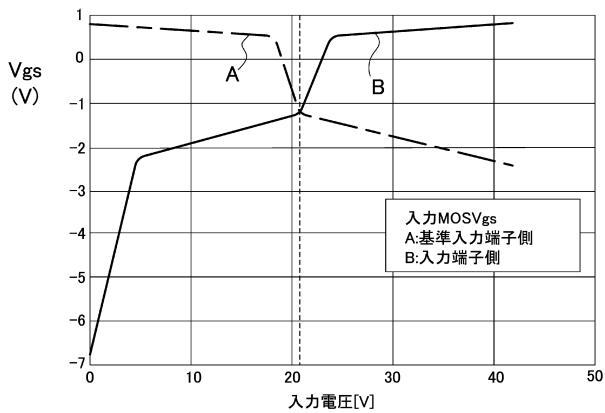

【図4】図3に示す比較器における一対の入力MOS-FETの入力電圧 $V_{in}$ に対するゲート・ソース間電圧 $V_{gs}$ の変化を示す図。

20

【図5】本発明の第3の実施形態に係る比較器の概略構成図。

【図6】図5に示す比較器における一対の入力MOS-FETの入力電圧 $V_{in}$ に対するゲート・ソース間電圧 $V_{gs}$ の変化を示す図。

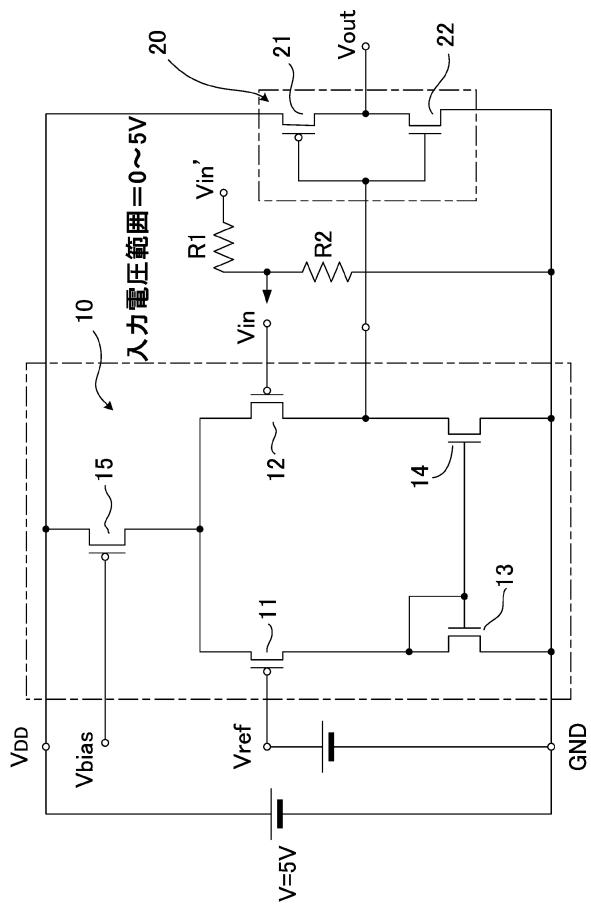

【図7】本発明の第4の実施形態に係る比較器の概略構成図。

【図8】従来の一般的なCMOS構成の比較器の概略構成図。

【図9】図8に示す比較器における一対の入力MOS-FETの入力電圧 $V_{in}$ に対するゲート・ソース間電圧 $V_{gs}$ の変化を示す図。

#### 【発明を実施するための形態】

#### 【0026】

以下、図面を参照して本発明の実施形態について説明する。

30

図1は本発明の第1の実施形態(第1の発明)に係る比較器の概略構成図である。この比較器は、基本的には前述した図8に示した従来の比較器と同様に構成されるものであり、同一構成部分には同一符号を付して示してある。尚、この比較器においては、比較器本体10とインバータ回路20とをそれぞれ別の電源 $V_1, V_2$ にて駆動するように構成してある。

#### 【0027】

ちなみに前記比較器本体10に電源電圧 $V_{DD}$ を供給する電源 $V_1$ は、例えば4.2Vの電圧源である。そして前記比較器本体10は、0~4.2Vの入力電圧 $V_{in}$ を、例えば $V_{DD}/2 (= 2.1V)$ として設定された基準電圧 $V_{ref}$ と直接比較するように構成される。

#### 【0028】

40

また前記インバータ回路20に電源電圧 $V_{CC}$ を供給する電源 $V_2$ は、例えば電子機器用の5Vの電圧源である。そしてCMOS構成の前記インバータ回路20は、pチャネル型のMOS-FET21と、このMOS-FET21を負荷とするnチャネル型のMOS-FET22とからなる。このMOS-FET22は、そのゲートに前記比較器本体10の出力であるMOS-FET12のドレイン電圧を受け、該出力を反転した0V/5Vの出力電圧 $V_{out}$ を外部出力する。尚、前記MOS-FET21は、そのゲートにバイアス電圧 $V_{bias2}$ を受けて前記MOS-FET22に対する定電流源として動作する。

#### 【0029】

さてこの比較器が特徴とするところは、差動対をなす前記一対の入力MOS-FET11, 12の各ゲート・ソース間に、それぞれツェナーダイオード31, 32を順方向に並列

50

接続した点にある。これらのツエナーダイオード 31, 32 は、前記各入力MOS-FET 11, 12におけるゲート酸化膜の耐圧以下のブレークダウン電圧特性を有する。例えば前記入力MOS-FET 11, 12のゲート酸化膜の厚みが25nm厚であり、その耐圧が7Vである場合には、7V以下のブレークダウン電圧特性を有するツエナーダイオード 31, 32 が用いられる。

#### 【0030】

このようなツエナーダイオード 31, 32 を備えて構成される比較器によれば、前記入力MOS-FET 11, 12 のゲート・ソース間にその耐圧以上の電圧が掛かりそうになると、前記ツエナーダイオード 31, 32 がブレークダウンする。そして前記入力MOS-FET 11, 12 のゲート・ソース間に加わる電圧（ゲート・ソース間電圧  $V_{gs}$ ）が前記ツエナーダイオード 31, 32 のブレークダウン電圧（降伏電圧）に抑えられる。この結果、前記入力MOS-FET 11, 12 のゲート・ソース間に前記ツエナーダイオード 31, 32 のブレークダウン電圧を超える高電圧、換言すればゲート酸化膜の耐圧を超える高電圧が加わることがなくなり、そのゲート酸化膜の破壊が防止される。10

#### 【0031】

図2は、基準電圧  $V_{ref}$  を  $V_{DD}/2$  (= 21V) とし、入力電圧  $V_{in}$  を 0 ~ 42V の範囲で変化させたときの前記入力MOS-FET 11, 12 のゲート・ソース間電圧  $V_{gs}$  の変化を示すシミュレーション結果である。この図2に示されるように前記入力電圧  $V_{in}$  が前記基準電圧  $V_{ref}$  よりも 7V 以上低いとき ( $V_{in} < V_{ref} - 7$ )、前記入力電圧  $V_{in}$  が印加されてオンとなる前記入力MOS-FET 12 のゲート・ソース間電圧  $V_{gs}$  は、前記ツエナーダイオード 32 によってクランプされ、略7Vに保持される（特性Bを参照）。20

#### 【0032】

即ち、前記入力電圧  $V_{in}$  が前記基準電圧  $V_{ref}$  よりも低いとき ( $V_{in} < V_{ref}$ )、前述のように前記基準電圧  $V_{ref}$  が印加される入力MOS-FET 11 がオフし、前記入力電圧  $V_{in}$  が印加される入力MOS-FET 12 がオンする。そして前記入力MOS-FET 12 のゲート・ソース間には、前記入力電圧  $V_{in}$  と前記基準電圧  $V_{ref}$  との電圧差に相当する電圧が加わる。

#### 【0033】

特に前記入力電圧  $V_{in}$  が前記基準電圧  $V_{ref}$  よりも前記ツエナーダイオード 32 のブレークダウン電圧 (7V) 以上低いと ( $V_{in} < V_{ref} - 7$ )、前記入力MOS-FET 12 のゲート・ソース間に加わる電圧が前記ツエナーダイオード 32 のブレークダウン電圧を上回る。すると前記ツエナーダイオード 32 がブレークダウンする。そして図2に示すように前記入力MOS-FET 12 のゲート・ソース間電圧  $V_{gs}$  は、前記ツエナーダイオード 32 のブレークダウン電圧（降伏電圧；7V）に抑制される。この結果、前記入力MOS-FET 12 のゲート酸化膜への高電圧の印加が阻止され、その破壊が防止される。尚、このとき前記入力MOS-FET 11 はオフしているので、該入力MOS-FET 11 のゲート・ソース間には前記ツエナーダイオード 31 の順方向降下電圧だけが加わることになる。尚、このとき前記入力MOS-FET 12 のゲート・ソース間には、前記基準電圧  $V_{ref}$  によりバイアスされて該入力MOS-FET 12 に流れる電流に相当する電圧だけが印加される。従って前記入力MOS-FET 11 のゲート・ソース間にも、その耐圧を超える電圧（ゲート・ソース間電圧  $V_{gs}$ ）が印加されることなく、該入力MOS-FET 11 のゲート酸化膜の破壊が防止される。30

#### 【0034】

また逆に前記入力電圧  $V_{in}$  が前記基準電圧  $V_{ref}$  よりも高いときには ( $V_{in} > V_{ref}$ )、前述のように前記基準電圧  $V_{ref}$  が印加される入力MOS-FET 11 がオンし、前記入力電圧  $V_{in}$  が印加される入力MOS-FET 12 がオフする。そして前記入力MOS-FET 12 のゲート・ソース間には、前記ツエナーダイオード 32 の順方向降下電圧だけが加わることになる。また前記入力MOS-FET 11 のゲート・ソース間には、前記基準電圧  $V_{ref}$  によりバイアスされて該入力MOS-FET 11 に流れる電流に相当する電圧だけが印加される。従って前記入力MOS-FET 11 のゲート・ソース間にも、その耐圧を超える電圧（ゲート・ソース間電圧  $V_{gs}$ ）が印加されることなく、該入力MOS-FET 11 のゲート酸化膜の破壊が防止される。40

#### 【0035】

尚、上述したシミュレーション結果は、前記基準電圧  $V_{ref}$  を  $V_{DD}/2$  (= 21V) 50

としたときの例である。しかし前記基準電圧  $V_{ref}$  を、例えば接地電位 (0 V) に近い低電位 (-0 V)、または電源電圧  $V_{DD}$  の近い高電位 ( $-V_{DD}$ ) に設定した場合、前述したように入力電圧  $V_{in}$  の変化に伴って前記入力MOS-FET 11, 12 のゲート・ソース間に、更に高い電圧が印加される可能性がある。しかしこのような場合であっても、前記ツェナーダイオード 31, 32 によって前記入力MOS-FET 11, 12 のゲート・ソース間に加わる電圧 (ゲート・ソース間電圧  $V_{gs}$ ) が抑制される。従って前記入力MOS-FET 11, 12 のゲート酸化膜の破壊が防止される。

#### 【0036】

ところで比較器を図3に示すように構成することもできる(第2の発明)。

この比較器は、前述したツェナーダイオード 31, 32 に加えて、更に前記比較器本体 10 の出力電圧(入力MOS-FET 12 のドレイン電圧)を前記一対の負荷MOS-FET 13, 14 のゲートに負帰還して該出力電圧の振幅を制限する帰還MOS-FET 33 を設けたことを特徴としている。この帰還MOS-FET 33 は、ゲートおよびドレンを前記入力MOS-FET 12 のドレンに接続すると共に、ソースを前記負荷MOS-FET 14 のゲートに接続したnチャネル型のものからなる。

#### 【0037】

このような帰還MOS-FET 33 を更に備えて構成される比較器によれば、前記入力MOS-FET 12 のドレイン電圧に応じて前記負荷MOS-FET 14 に流れる電流が抑制される。そしてこの負帰還による電流抑制により前記入力MOS-FET 12 のゲート・ソース間に加わる電圧が抑制される。この結果、図4に前記入力MOS-FET 11, 12 のゲート・ソース間電圧  $V_{gs}$  のシミュレーション結果を示すように、該入力MOS-FET 11, 12 のゲート・ソース間電圧  $V_{gs}$  が、その耐圧以下の電圧に制限される。

#### 【0038】

即ち、前記入力MOS-FET 11, 12 のゲート・ソース間電圧  $V_{gs}$  が前述したツェナーダイオード 31, 32 によるクランプ作用の下で、前記帰還MOS-FET 33 による負帰還制御により更に制限される。従って前述した図1に示した構成の比較器以上に前記入力MOS-FET 11, 12 のゲート酸化膜の破壊を効果的(確実に)に防止することが可能となる。

#### 【0039】

また前記帰還MOS-FET 33 による負帰還制御により前記入力MOS-FET 12 のドレイン電圧を制限し、以て比較器本体 10 の出力電圧の振幅を抑えることができる。この結果、前記インバータ回路 20 における前記MOS-FET 22 のゲートに加わる電圧の振幅が抑制される。従って前記MOS-FET 22 のゲートに過大な電圧が加わることがなくなり、該MOS-FET 22 のゲート・ソース間電圧  $V_{gs}$  を抑えてそのゲート酸化膜の破壊を防止することも可能となる。

#### 【0040】

更に比較器を図5に示すように構成することもできる(第3の発明)。

この比較器は、前述したツェナーダイオード 31, 32 および帰還MOS-FET 33 に加えて、更に前記定電流源と前記一対の入力MOS-FET 11, 12 の各ソースとの間に整流ダイオード(半導体整流素子) 34, 35 をそれぞれ介装して構成される。これらの整流ダイオード 34, 35 には、前記電源電圧  $V_{DD}$  以上の逆耐圧特性を有するものが用いられる。

#### 【0041】

前記整流ダイオード 34, 35 は、前記入力MOS-FET 11, 12 のゲートに印加される電圧が、図5においてノードNとして示す前記定電流源の電流出力端の電圧(前記MOS-FET 15 のドレンの電圧)以上になったとき、該入力MOS-FET 11, 12 を前記MOS-FET 15 から切り離す役割を担う。これらの整流ダイオード 34, 35 により前記定電流源から前記入力MOS-FET 11, 12 を切り離すことで、該入力MOS-FET 11, 12 に流れる電流が遮断され、そのゲート酸化膜が保護される。

#### 【0042】

10

20

30

40

50

例えば前記基準電圧  $V_{ref}$  として電源電圧  $V_{DD}$  に近い高電圧が設定され、また前記入力電圧  $V_{in}$  が接地電位 (0 V) に近い低い電圧であるとする。そして前記入力MOS-FET 11, 12 および前記定電流源をなすMOS-FET 15のチャネル長  $L$  とチャネル幅  $W$  の比  $L/W$  が等しいと仮定する。するとこの場合、前記MOS-FET 15のゲート・ソース間には、電源電圧  $V_{DD}$  とバイアス電圧  $V_{bias}$ との差電圧が印加される。よって前記入力MOS-FET 12のゲート・ソース間にも、同様に電源電圧  $V_{DD}$  とバイアス電圧  $V_{bias}$ との差電圧が加わる。

#### 【0043】

このときの前記MOS-FET 15のドレイン電圧  $V_d$  は、前記入力MOS-FET 12のゲート・ソース間を  $V_{gs}$  とし、前記整流ダイオード 35の順方向降下電圧を  $V_f$  としたとき

$$V_d = V_{in} + V_{gs} + V_f \text{ となる。}$$

#### 【0044】

特に前記入力電圧  $V_{in}$  が 0 V であり、前記入力MOS-FET 12のゲート・ソース間に加わる電圧  $V_{gs}$  が前記MOS-FET 15のゲートに印加されるバイアス電圧  $V_{bias}$  に等しいと仮定する。すると上述したように前記MOS-FET 12のゲート・ソース間には、前記入力MOS-FET 15のゲート・ソース間電圧である電源電圧  $V_{DD}$  とバイアス電圧  $V_{bias}$ との差電圧が印加される。よって前記ドレイン電圧  $V_d$  は

$$V_d = V_{DD} - V_{bias} + V_f$$

となる。

#### 【0045】

ここで前記整流ダイオード 34 が存在しない場合には、前記入力MOS-FET 11のゲート電圧が前記電源電圧  $V_{DD}$  に近いので、前記電源電圧  $V_{DD}$  が高く、また前記バイアス電圧  $V_{bias}$  と前記入力電圧  $V_{in}$ との差が大きいと、前記電源電圧  $V_{DD}$  に近い前記バイアス電圧  $V_{bias}$  がそのまま前記入力MOS-FET 11のゲート・ソース間に加わることになる。すると前記バイアス電圧  $V_{bias}$  によって前記入力MOS-FET 11のゲート酸化膜の破壊を招来する虞が生じる。

#### 【0046】

この点、前記整流ダイオード 34 を設けておけば、前記入力MOS-FET 11のゲート電圧が前記バイアス電圧  $V_{bias}$  以上になったとき、前記整流ダイオード 34 により前記入力MOS-FET 11 が前記定電流源 (MOS-FET 15) から切り離される。換言すれば前記整流ダイオード 34, 35 は、前記入力MOS-FET 11, 12 のゲート電圧が前記バイアス電圧  $V_{bias}$  以上になったとき、ゲート電圧が高くなった側の入力MOS-FET 11, 12 を、定電流源から切り離す役割を担う。

#### 【0047】

すると前記定電流源は、オンとなる側の前記入力MOS-FET 11, 12 にだけ電流を供給するので、前記ノードNの電位はオンとなる側の前記入力MOS-FET 11, 12 のゲート電圧 (入力電圧  $V_{in}$  または基準電圧  $V_{ref}$ ) に応じて変化する。この結果、オンとなる側の前記入力MOS-FET 11, 12 のゲート・ソース間電圧  $V_{gs}$  が略一定に保たれる。従って前記入力MOS-FET 11, 12 のゲート電圧 (基準電圧  $V_{ref}$ , 入力電圧  $V_{in}$ ) が高い場合でも、そのゲート酸化膜の破壊が防止される。

#### 【0048】

尚、前記MOS-FET 11, 12, 15 のチャネル長  $L$  とチャネル幅  $W$ との比  $L/W$  が異なる場合には、前記バイアス電圧  $V_{bias}$  が前記ノードNにそのまま発生することはない。しかしこの場合であっても、前記入力MOS-FET 11 または 12 のゲート電圧が前記ノードNの電圧以上になったとき、前記整流ダイオード 34 または 35 により前記入力MOS-FET 11, 12 が前記定電流源から切り離される。従って前述した例と同様に前記入力MOS-FET 11, 12 のゲート酸化膜の破壊が防止される。

#### 【0049】

図 6 は、上述した如く整流ダイオード 34, 35 を備えて構成される比較器における、

10

20

30

40

50

前記入力MOS-FET 11, 12のゲート・ソース間電圧V<sub>gs</sub>のシミュレーション結果を示している。この図6に示されるように、前記整流ダイオード34, 35を備えて構成される比較器によれば、前記入力MOS-FET 11, 12のゲート・ソース間電圧V<sub>gs</sub>を十分低く抑えることが可能となる。即ち、前記整流ダイオード34, 35により、前記定電流源(MOS-FET 15)からゲート電圧の高い前記入力MOS-FET 11, 12を選択的に切り離すので、オンとなる側の前記入力MOS-FET 11, 12のゲート・ソース間電圧V<sub>gs</sub>を、図6に示すように略一定に保つことができる。

#### 【0050】

上記構成の比較器によれば、前述したツエナーダイオード31, 32および前記帰還MOS-FET 33による前記ゲート・ソース間電圧V<sub>gs</sub>の制限作用の下で、更に前記整流ダイオード34, 35を用いて前記入力MOS-FET 11, 12への電流供給自体を選択的に遮断する。従って前記入力MOS-FET 11, 12のゲート・ソース間電圧V<sub>gs</sub>を、該入力MOS-FET 11, 12の耐圧以下の電圧、例えば4V以下に抑えることができる。故に図5に示す比較器によれば、前述した図1および図3にそれぞれ示した比較器に比較して、更に確実に前記入力MOS-FET 11, 12のゲート酸化膜の破壊を効果的に防止することができる。

#### 【0051】

尚、前記整流ダイオード34, 35に代えて、図7に示すようにダイオード接続したMOS-FET(半導体整流素子)36, 37を前記定電流源と前記入力MOS-FET 11, 12のソースとの間にそれぞれ介装することも可能である。この場合であっても、前記整流ダイオード34, 35を介装した場合と同様な作用・効果が奏せられて前記入力MOS-FET 11, 12のゲート酸化膜が保護されることは説明するまでもない。

#### 【0052】

以上説明したように本発明に係る比較器によれば、CMOS構成された比較器本体10が有する基本的な利点を活かしながら、入力電圧V<sub>in</sub>および基準電圧V<sub>ref</sub>の差動入力部を形成する入力MOS-FET 11, 12のゲート・ソース間電圧V<sub>gs</sub>を、該入力MOS-FET 11, 12の耐圧以下に抑えることができる。しかも基本的には前記入力MOS-FET 11, 12のゲート・ソース間にツエナーダイオード31, 32を順方向に並列接続するだけで、該入力MOS-FET 11, 12のゲート・ソース間電圧V<sub>gs</sub>をその耐圧以下に抑制することができる。

#### 【0053】

更には帰還MOS-FET 33を用いて前記入力MOS-FET 12のドレイン電圧を負帰還制御し、該ドレイン電圧(出力電圧)の振幅を抑えるので、前述したツエナーダイオード32と相俟って該入力MOS-FET 12のゲート・ソース間電圧V<sub>gs</sub>を抑制することができる。同時に前記ドレイン電圧の負帰還制御により前記インバータ回路20におけるMOS-FET 22のゲート・ソース間電圧V<sub>gs</sub>についても、その耐圧以下に抑えることができる。また前記整流ダイオード34, 35またはダイオード接続されたMOS-FET 36, 37により、高いゲート電圧が加わる前記入力MOS-FET 11, 12を定電流源から切り離すので、そのゲート酸化膜を破壊から保護することができる。

#### 【0054】

従って本発明によれば簡易にして効果的に入力MOS-FET 11, 12の破壊を確実に防止することができる。そして前記入力電圧V<sub>in</sub>が電源電圧V<sub>DD</sub>と同程度の高い場合であっても、或いは前記基準電圧V<sub>ref</sub>の設定値が接地電位程度に低く設定されるような場合でも、前記入力電圧V<sub>in</sub>と基準電圧V<sub>ref</sub>とを直接比較することが可能となる。特にゲート酸化膜の薄いMOS-FETを用いて比較器を構築する場合であっても、前述した従来の不具合を招来することなく、その実用的利点が多大である。

#### 【0055】

尚、本発明は上述した各実施形態に限定されるものではない。ここではMOS-FETのゲート酸化膜の厚みが25nmであり、その耐圧が7Vであるとして説明した。しかし

10

20

30

40

50

ゲート酸化膜の厚みが異なる別の仕様のMOS-FETを用いる場合でも本発明を適用可能なことは言うまでもない。この場合、MOS-FETのゲート酸化膜の厚みによって定まる耐圧に応じて、前記ツェナーダイオード31,32のブレークダウン電圧を選定すれば良い。また半導体整流素子（整流ダイオード34,35,ダイオード接続したMOS-FET36,37）の逆耐圧特性については、前記電源電圧 $V_{DD}$ 以上のものを用いれば十分である。

### 【0056】

また前記入力MOS-FET11,12のゲートに印加する入力電圧 $V_{in}$ および基準電圧 $V_{ref}$ を逆にして用いることも勿論可能である。更には前記インバータ回路20を省略して比較器を構築することも可能であり、各種の制御用集積回路の一部に組み込むことも勿論可能である。その他、本発明はその要旨を逸脱しない範囲で種々変形して実施することができる。

10

### 【符号の説明】

### 【0057】

10 比較器本体

11,12 入力MOS-FET

13,14 負荷MOS-FET

15 MOS-FET（定電流源）

20 インバータ回路

21,22 MOS-FET（インバータ回路）

20

31,32 ツェナーダイオード

33 帰還MOS-FET

34,35 整流ダイオード

36,37 MOS-FET（ダイオード接続）

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(56)参考文献 特開2009-077003(JP,A)

特公昭56-049004(JP,B1)

特開2005-027392(JP,A)

特開昭50-115984(JP,A)

特開平01-151315(JP,A)

実開昭58-090748(JP,U)

特表2002-543650(JP,A)

米国特許第04180780(US,A)

特開2003-347906(JP,A)

特開昭50-073549(JP,A)

特開昭55-104766(JP,A)

米国特許第08164364(US,B2)

(58)調査した分野(Int.Cl., DB名)

H03K 5/08