(12) 发明专利

(10) 授权公告号 CN 109863591 B

(45) 授权公告日 2023.07.07

(21) 申请号 201780064943.2

(74) 专利代理机构 中科专利商标代理有限责任

公司 11021

(22) 申请日 2017.09.11

专利代理人 王晖

(65) 同一申请的已公布的文献号

申请公布号 CN 109863591 A

(51) Int.CI.

H01L 23/12 (2006.01)

(43) 申请公布日 2019.06.07

H01L 23/02 (2006.01)

(30) 优先权数据

H01L 23/13 (2006.01)

2016-206673 2016.10.21 JP

H05K 1/02 (2006.01)

(85) PCT国际申请进入国家阶段日

H05K 1/18 (2006.01)

2019.04.19

(56) 对比文件

JP H11214556 A, 1999.08.06

(86) PCT国际申请的申请数据

JP H11214556 A, 1999.08.06

PCT/JP2017/032658 2017.09.11

US 2001004942 A1, 2001.06.28

(87) PCT国际申请的公布数据

US 2009059540 A1, 2009.03.05

W02018/074100 JA 2018.04.26

US 2010308940 A1, 2010.12.09

(73) 专利权人 京瓷株式会社

JP 2012227887 A, 2012.11.15

地址 日本京都府

JP 2005050974 A, 2005.02.24

(72) 发明人 川头芳规

JP 2001044644 A, 2001.02.16

审查员 齐梦宇

权利要求书2页 说明书8页 附图18页

(54) 发明名称

高频基体、高频封装件以及高频模块

(57) 摘要

本发明的高频基体具备：绝缘基体、第1线路导体和第2线路导体。绝缘基体在上表面具有凹部。第1线路导体位于绝缘基体的上表面。第2线路导体位于绝缘基体的上表面，并且在俯视下与第1线路导体空出间隔并与第1线路导体并行地延伸。凹部位于第1线路导体与第2线路导体之间，并且凹部的介电常数比绝缘基体低。

1. 一种高频基体,其特征在于,具备:

绝缘基体,在上表面具有凹部;

第1线路导体,位于所述绝缘基体的上表面;和

第2线路导体,位于所述绝缘基体的上表面,并且在俯视下与所述第1线路导体空出间隔并与所述第1线路导体并行地延伸,

所述凹部位于所述第1线路导体与所述第2线路导体之间,在俯视下与第1线路导体和第2线路导体并行地延伸并且介电常数比所述绝缘基体的介电常数低,

所述第1线路导体具有在中途将该第1线路导体分离的第1分离部,所述第1线路导体的被分离的各个具备:与所述第1分离部连续的第1电极焊盘、和从该第1电极焊盘延伸设置的第1线路,

所述第2线路导体具有在中途将该第2线路导体分离的第2分离部,所述第2线路导体的被分离的各个具备:与所述第2分离部连续的第2电极焊盘、和从该第2电极焊盘延伸设置的第2线路,

在俯视下,所述第1电极焊盘和所述第2电极焊盘被设置为夹着所述凹部而对置,并且

所述凹部在俯视下从一个所述第1电极焊盘与所述第2电极焊盘之间,经由所述第1分离部和所述第2分离部之间,延伸到另一个所述第1电极焊盘和所述第2电极焊盘之间。

2. 根据权利要求1所述的高频基体,其特征在于,

所述凹部遍及各个所述第1电极焊盘的所述第1线路所连接的一侧的端部、以及各个所述第2电极焊盘的所述第2线路所连接的一侧的端部,与所述第1线路导体以及所述第2线路导体并行地延伸。

3. 根据权利要求1所述的高频基体,其特征在于,

在第1电极焊盘之间以及第2电极焊盘之间,所述绝缘基体凹陷。

4. 根据权利要求1至3的任意一项所述的高频基体,其特征在于,

在位于所述第1电极焊盘与所述第2电极焊盘之间的所述凹部的端部的侧壁具有切口部。

5. 根据权利要求4所述的高频基体,其特征在于,

在所述切口部的表面具有金属化层。

6. 根据权利要求1所述的高频基体,其特征在于,

在所述绝缘基体的上表面还具有接地导体层,所述接地导体层位于与所述第1线路导体、所述第2线路导体空出间隔的位置。

7. 根据权利要求1所述的高频基体,其特征在于,

所述高频基体具备:被配置于所述第1分离部的上表面的第1电容器、和被配置于所述第2分离部的上表面的第2电容器。

8. 根据权利要求3所述的高频基体,其特征在于,

在所述第1电极焊盘之间以及所述第2电极焊盘之间设置与所述凹部连续的槽。

9. 根据权利要求1所述的高频基体,其特征在于,

所述凹部在剖视下为矩形状、锥状或者阶梯形状。

10. 根据权利要求1所述的高频基体,其特征在于,

所述凹部在俯视下为矩形状、椭圆形状、正方形或者角部为圆形的矩形状。

11. 根据权利要求1所述的高频基体,其特征在于,

所述凹部由空气或者包含树脂材料、玻璃材料的电介质材料填满。

12. 根据权利要求1所述的高频基体,其特征在于,

所述第1电极焊盘的宽度比所述第1线路的宽度大,所述第2电极焊盘的宽度比所述第2

线路的宽度大。

13. 一种高频封装件,其特征在于,具备:

基板;

壳体,与所述基板的上表面接合,并且具有贯通孔;和

被固定于所述壳体的所述贯通孔的权利要求1至6的任意一项所述的高频基体。

14. 一种高频模块,其特征在于,具备:

权利要求13所述的高频封装件;

半导体元件,被安装于所述基板的上表面,并且与所述高频封装件的所述高频基体电

连接;和

盖体,与所述壳体的上端接合,覆盖所述半导体元件并且覆盖所述高频封装件的内部。

## 高频基体、高频封装件以及高频模块

### 技术领域

[0001] 本发明涉及高频基体、使用高频基体的高频封装件、以及高频模块。

### 背景技术

[0002] 近年来,由于便携电话等的普及,在无线通信设备中,为了传输更高速化、更大容量的信息,高频化被推进。其中,已知为了去除传输高频信号的直流电压分量而在信号线路之间设有电容器的高频基体(参照JP特开2008-311682号公报)。

[0003] 在JP特开2008-311682号公报所公开的技术中,在电介质基板设有传输信号的第1线路导体以及第2线路导体。第1线路导体与第2线路导体并行地延伸。但是,在专利文献1的技术中,有可能第1线路导体与第2线路导体之间的阻抗的值变低,高频的信号的传输中损耗变大。

### 发明内容

[0004] 本发明的一实施方式所涉及的高频基体具备绝缘基体、第1线路导体、和第2线路导体。绝缘基体在上表面具有凹部。第1线路导体位于绝缘基体的上表面。第2线路导体位于绝缘基体的上表面,并且在俯视下与第1线路导体空出间隔并与第1线路导体并行地延伸。凹部位于第1线路导体与第2线路导体之间,并且凹部的介电常数比绝缘基体低。

[0005] 本发明的一实施方式所涉及的高频封装件具备基板、壳体、以及上述的高频基体。壳体被接合于基板的上表面,并具有贯通孔。高频基体被固定于壳体的贯通孔。

[0006] 本发明的一实施方式所涉及的高频模块具备上述的高频封装件、半导体元件、和盖体。半导体元件被收纳于上述的高频封装件,与高频基体电连接。盖体被接合于壳体的上端,覆盖半导体元件并且覆盖高频封装件的内部。

### 附图说明

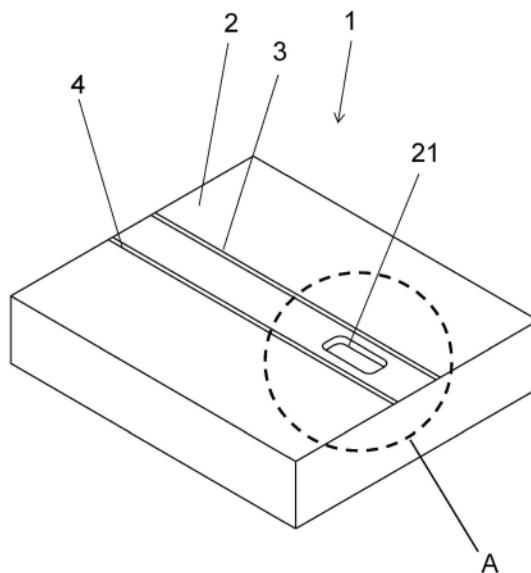

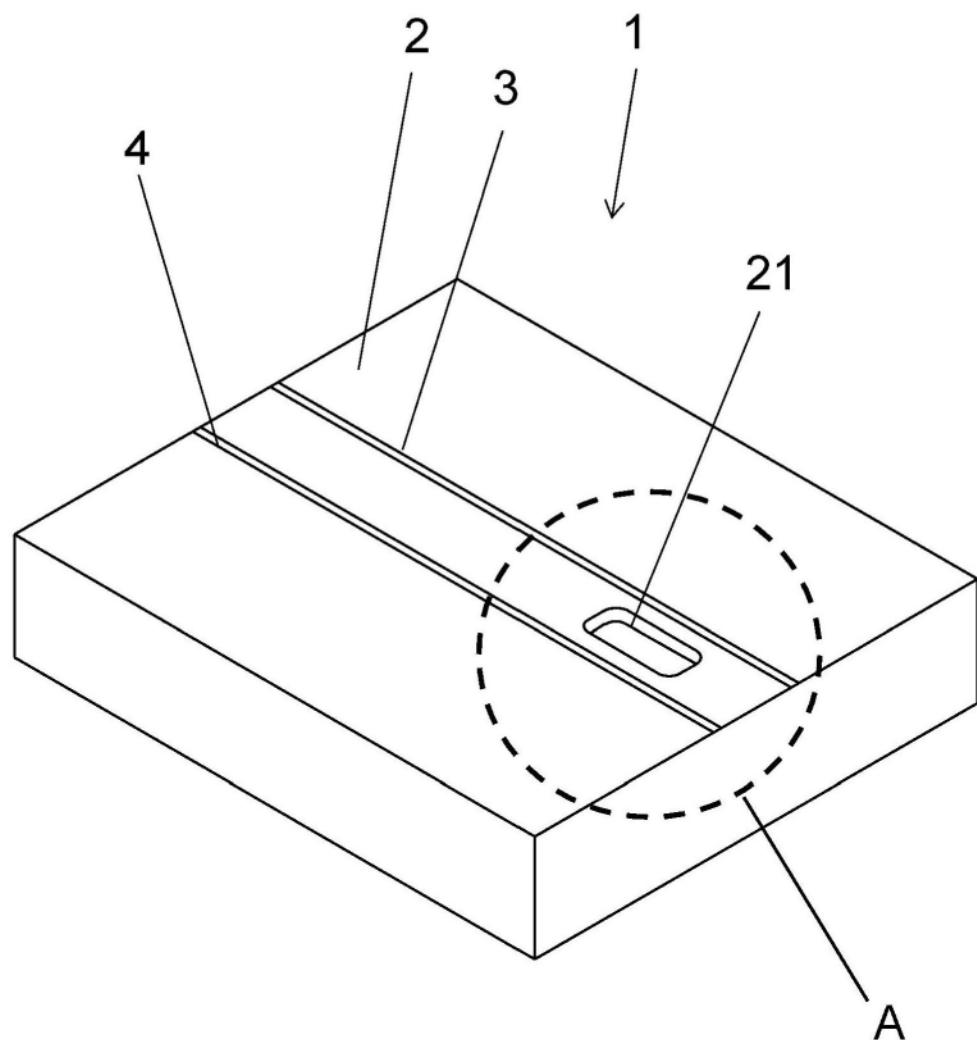

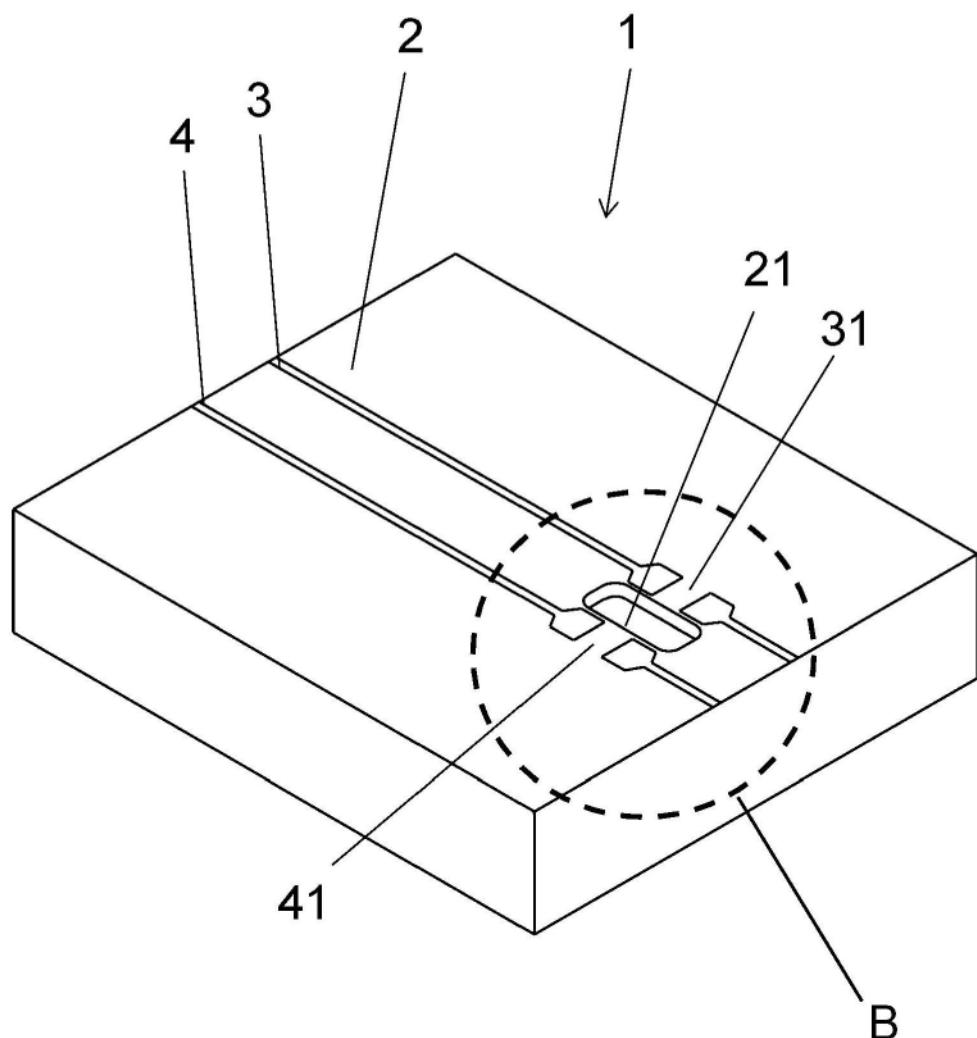

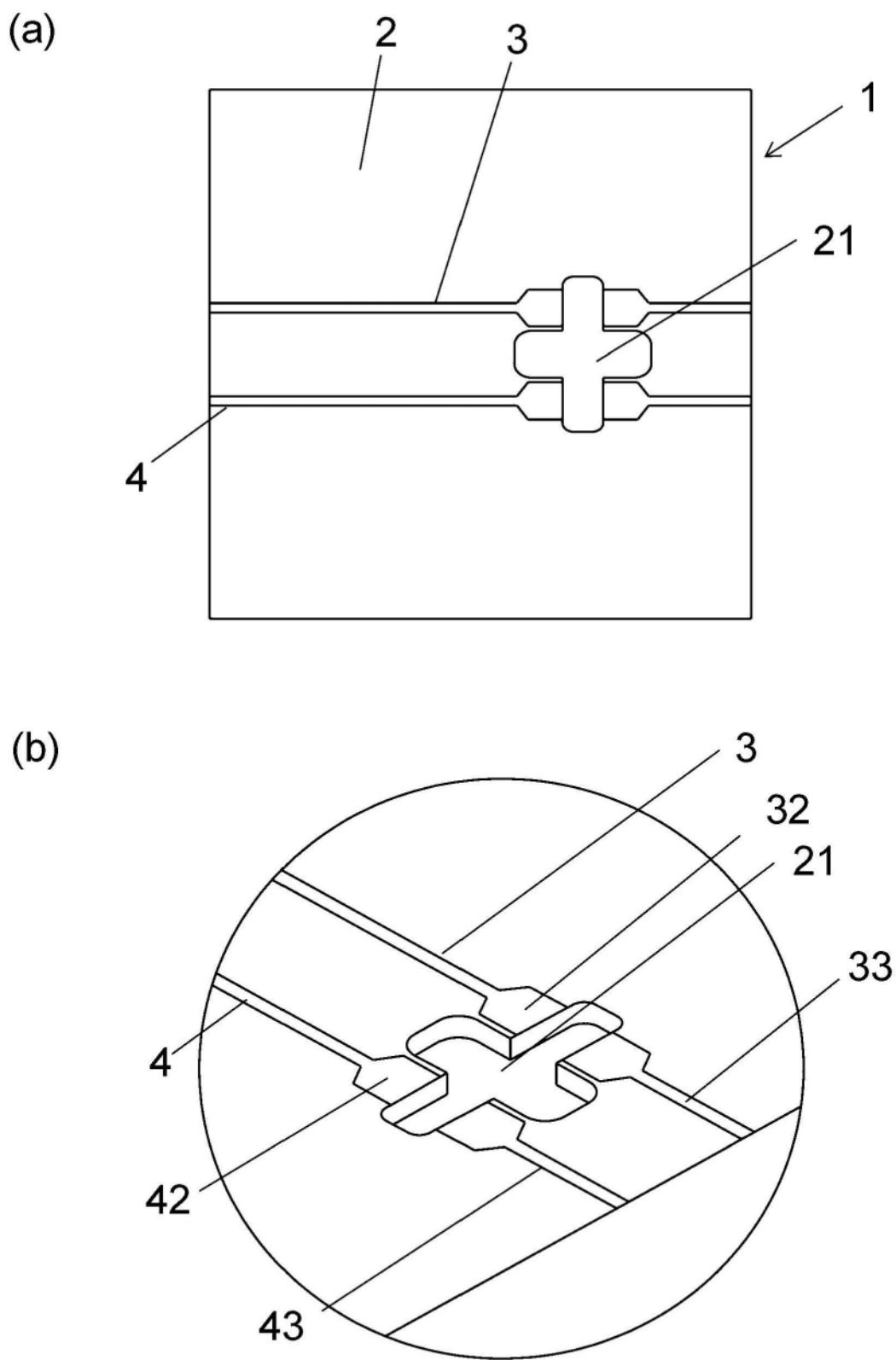

[0007] 图1是本发明的一实施方式所涉及的高频基体的立体图。

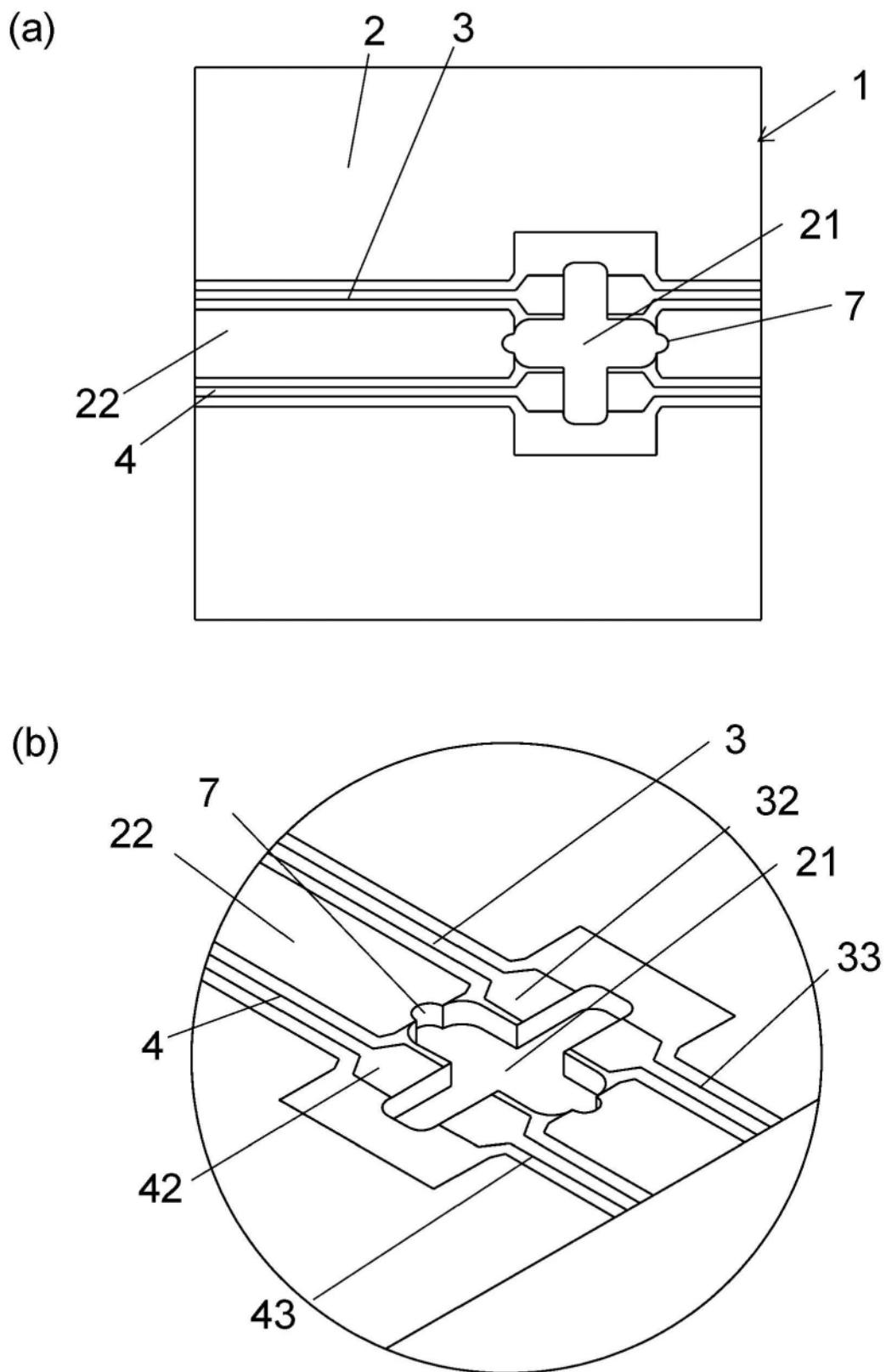

[0008] 图2是图1所示的本发明的一实施方式所涉及的高频基体,图2的(a)是本发明的一实施方式所涉及的高频基体的俯视图,图2的(b)是以图1的A表示的放大立体图。

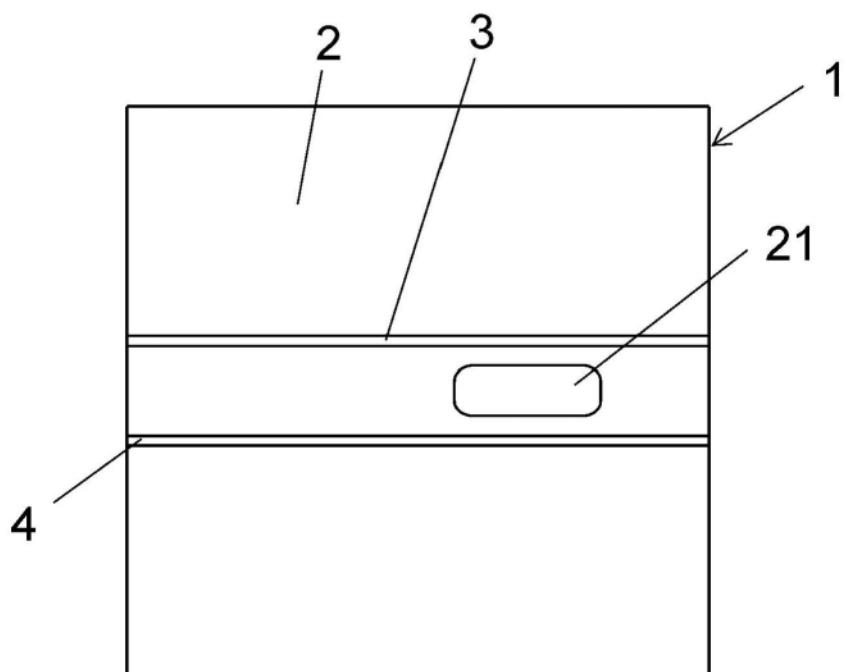

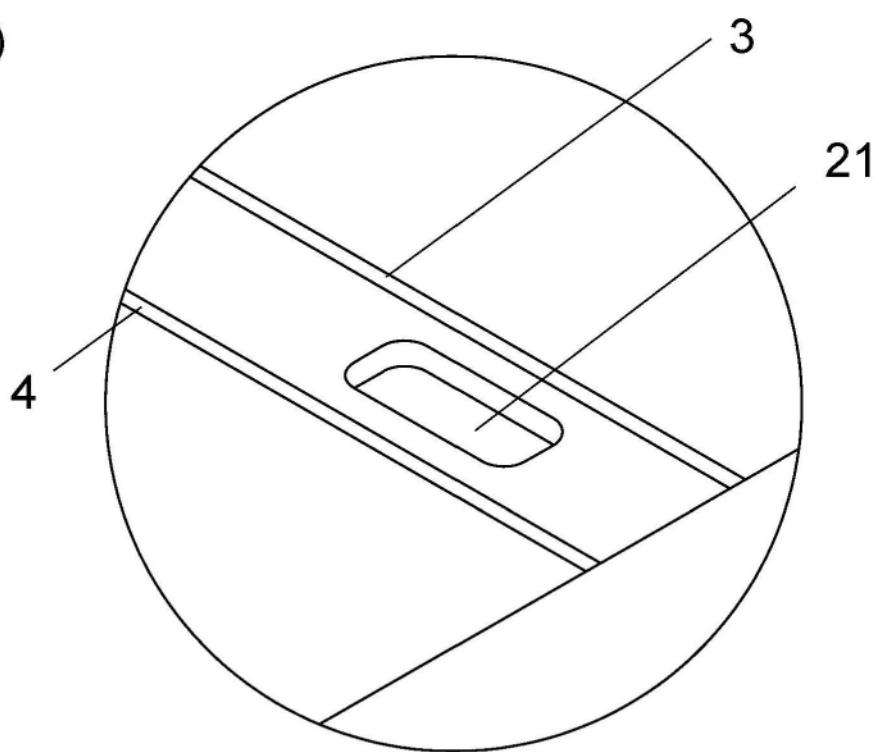

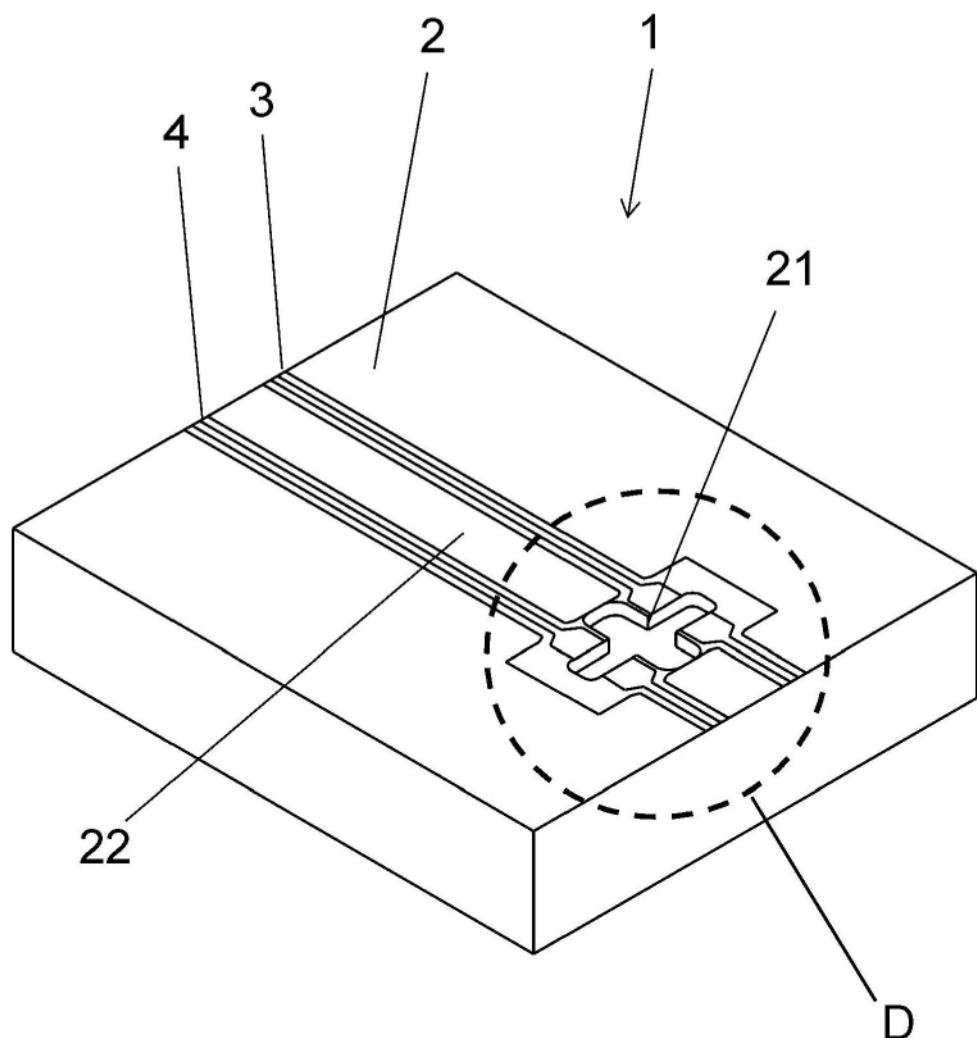

[0009] 图3是本发明的其他实施方式所涉及的高频基体的立体图。

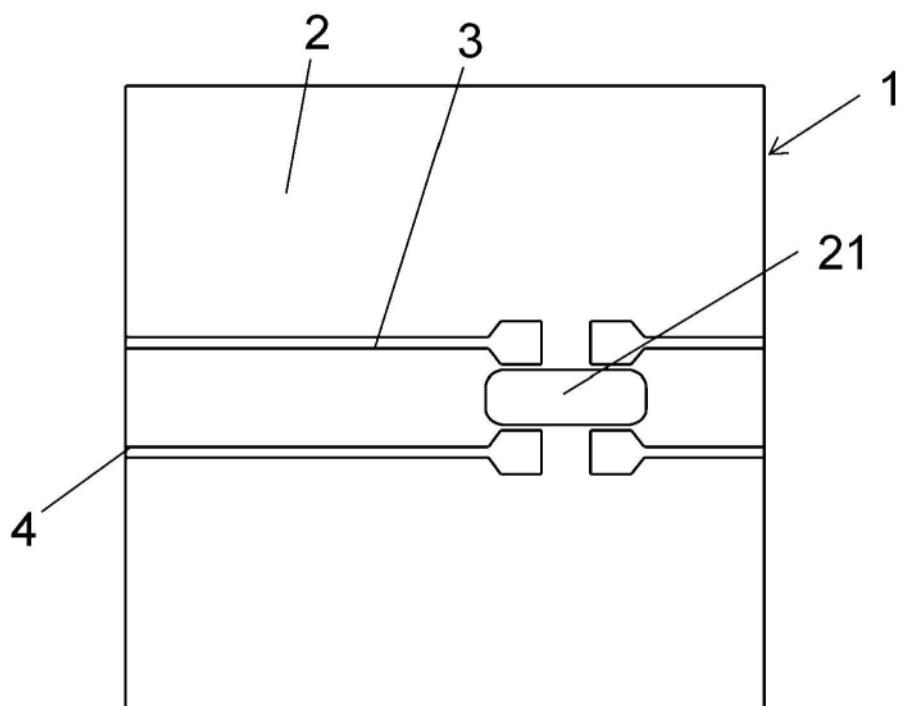

[0010] 图4是图3所示的本发明的其他实施方式所涉及的高频基体,图4的(a)是本发明的其他实施方式所涉及的高频基体的俯视图,图4的(b)是以图3的B表示的放大立体图。

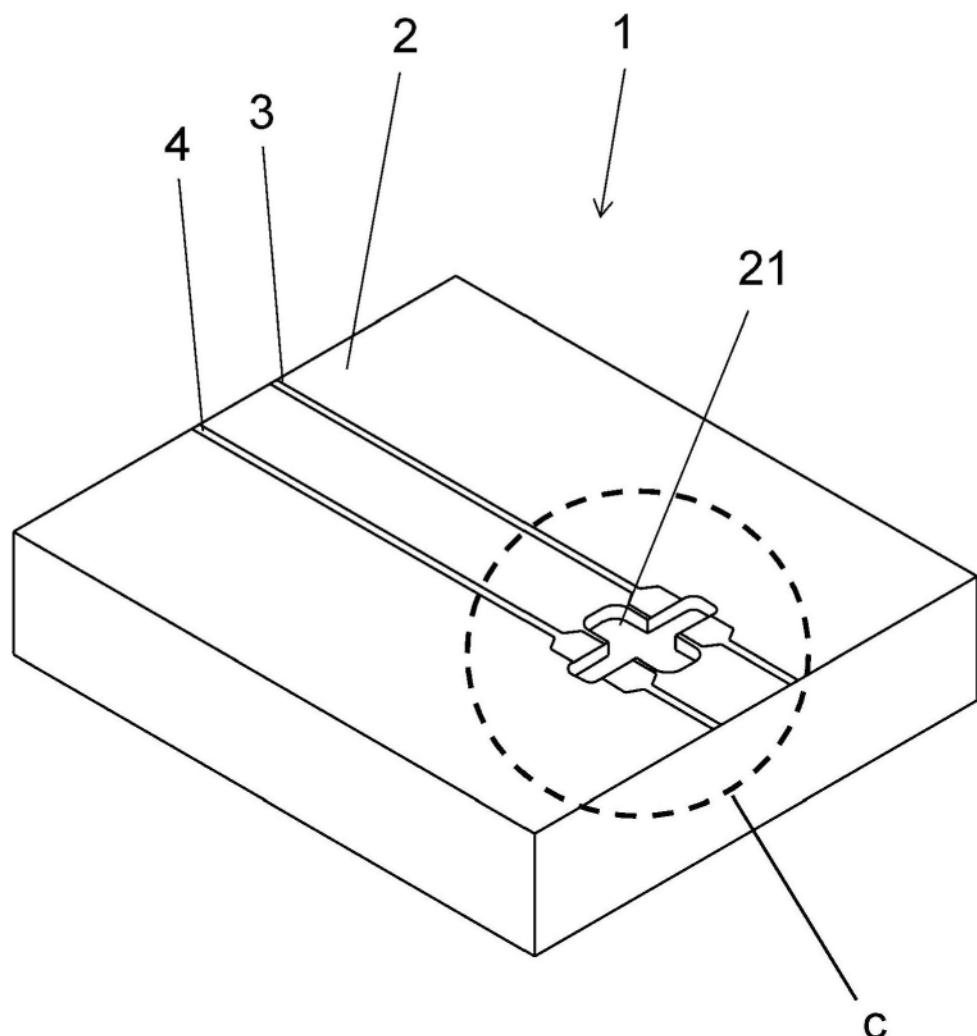

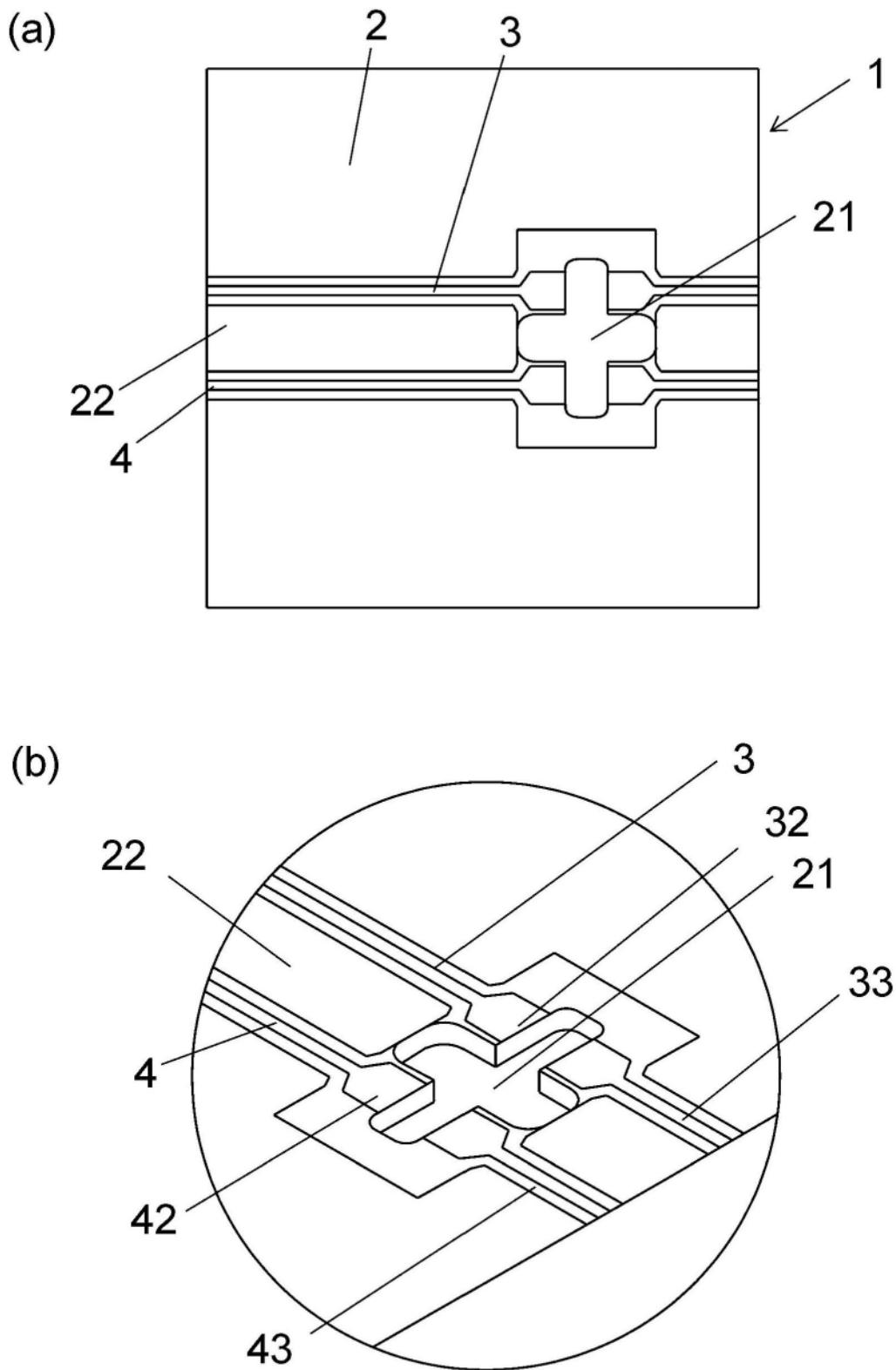

[0011] 图5是本发明的其他实施方式所涉及的高频基体的立体图。

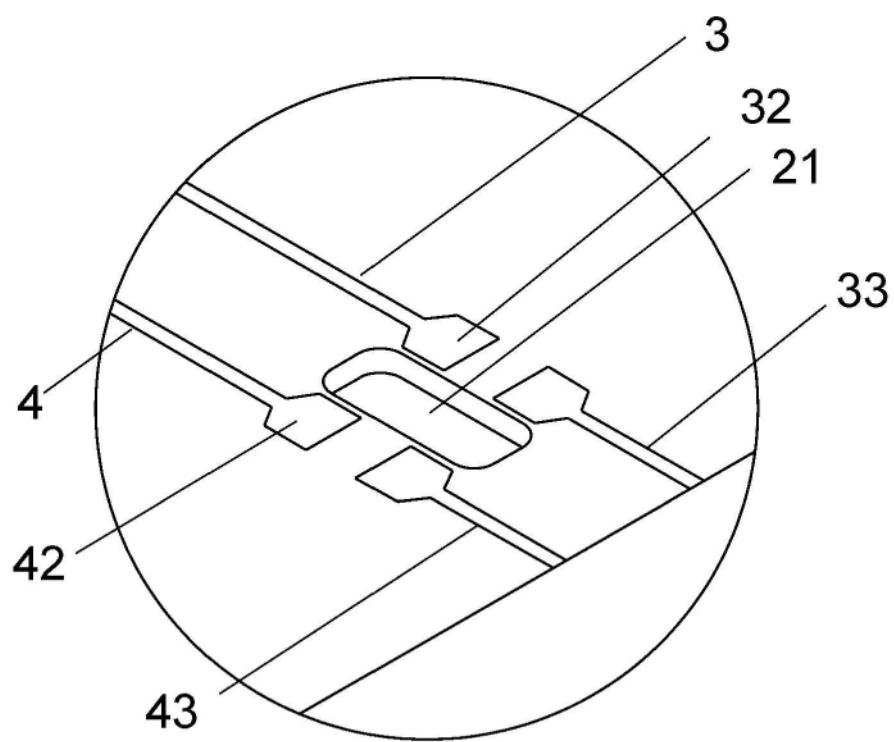

[0012] 图6是图5所示的本发明的其他实施方式所涉及的高频基体,图6的(a)是本发明的其他实施方式所涉及的高频基体的俯视图,图6的(b)是以图5的C表示的放大立体图。

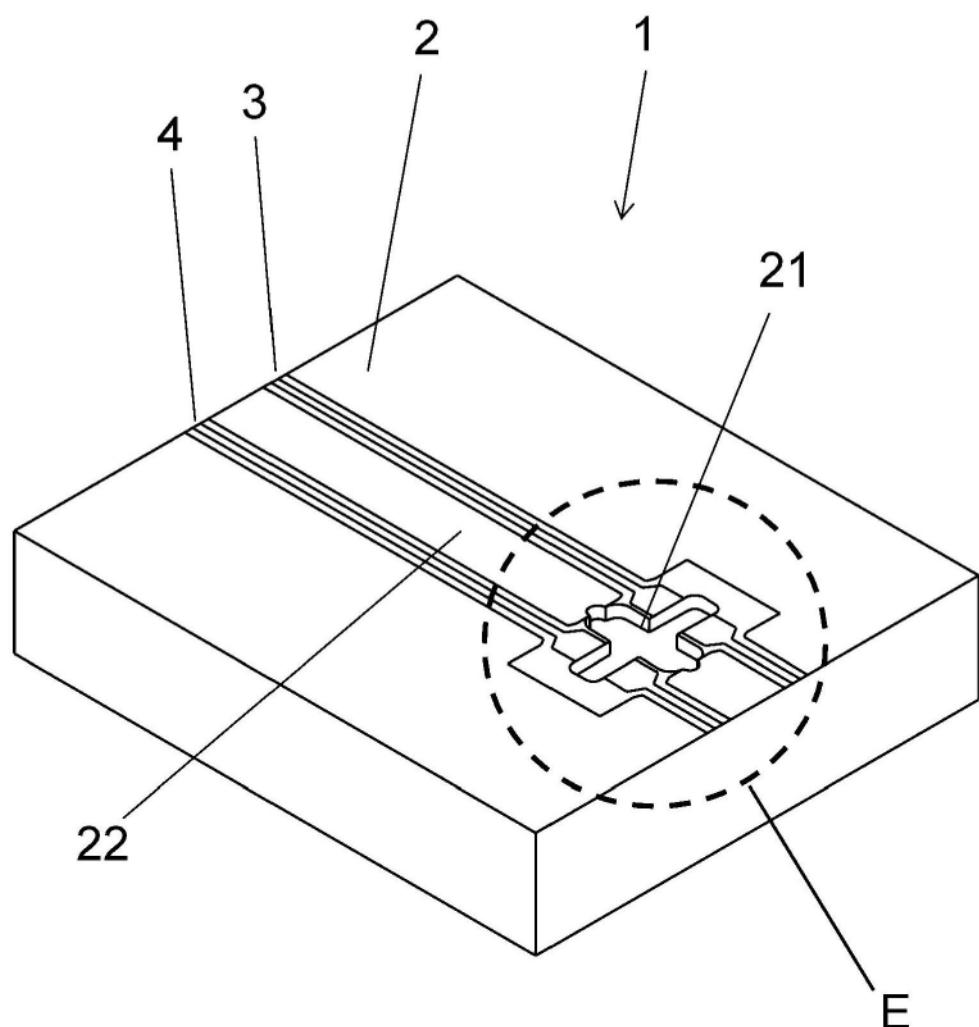

[0013] 图7是本发明的其他实施方式所涉及的高频基体的立体图。

[0014] 图8是图7所示的本发明的其他实施方式所涉及的高频基体,图8(a)是本发明的其他实施方式所涉及的高频基体的俯视图,图8(b)是以图7的D表示的放大立体图。

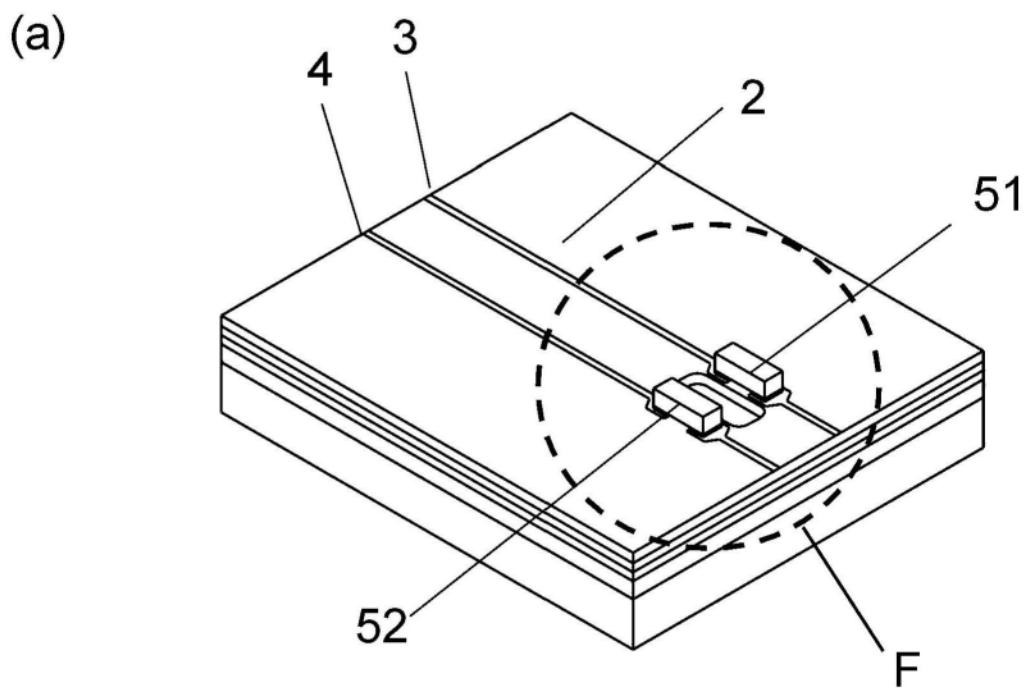

- [0015] 图9是本发明的其他实施方式所涉及的高频基体的立体图。

- [0016] 图10是图9所示的本发明的其他实施方式所涉及的高频基体,图10的(a)是本发明的其他实施方式所涉及的高频基体的俯视图,图10的(b)是以图9的E表示的放大立体图。

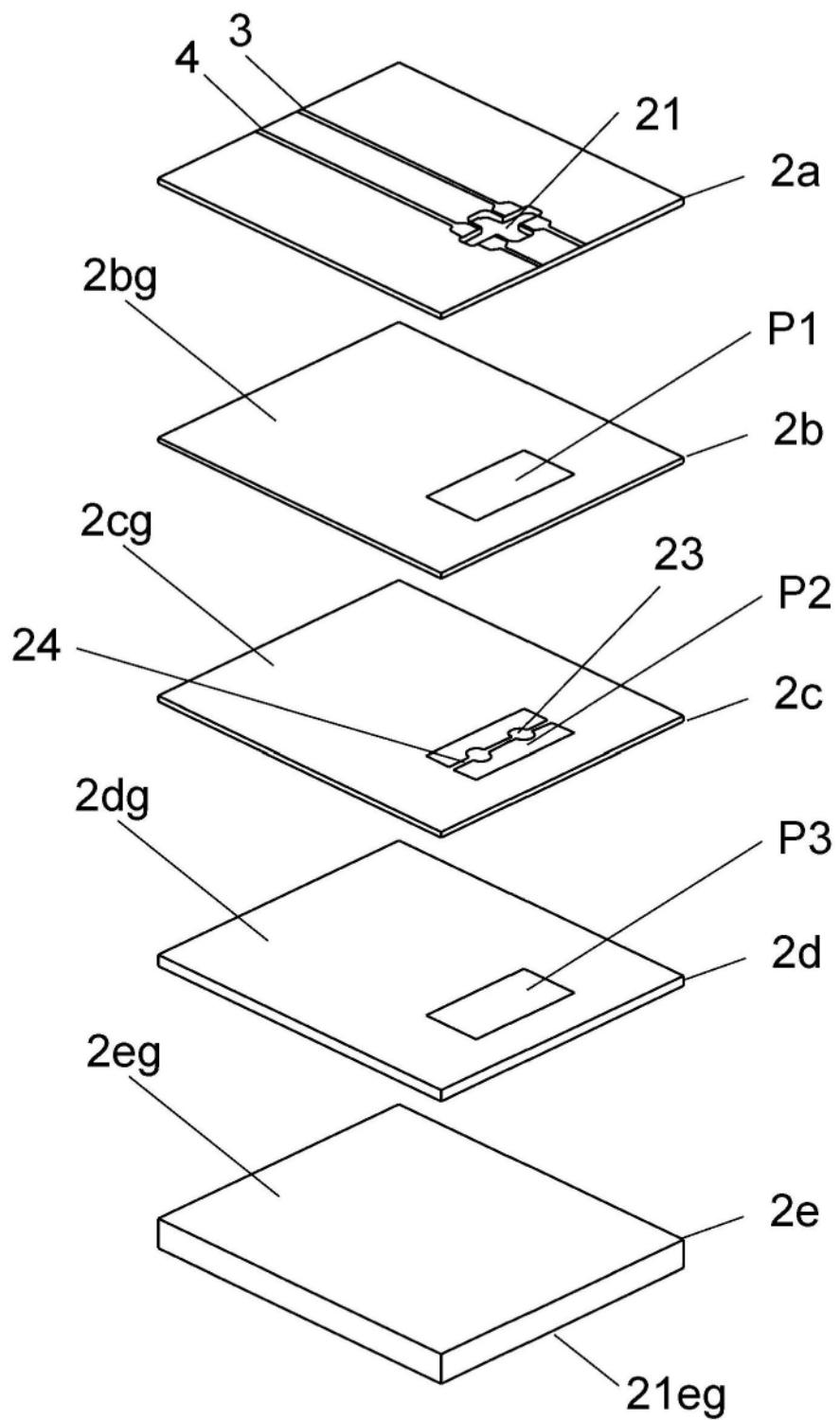

- [0017] 图11是本发明的其他实施方式所涉及的高频基体的分解立体图。

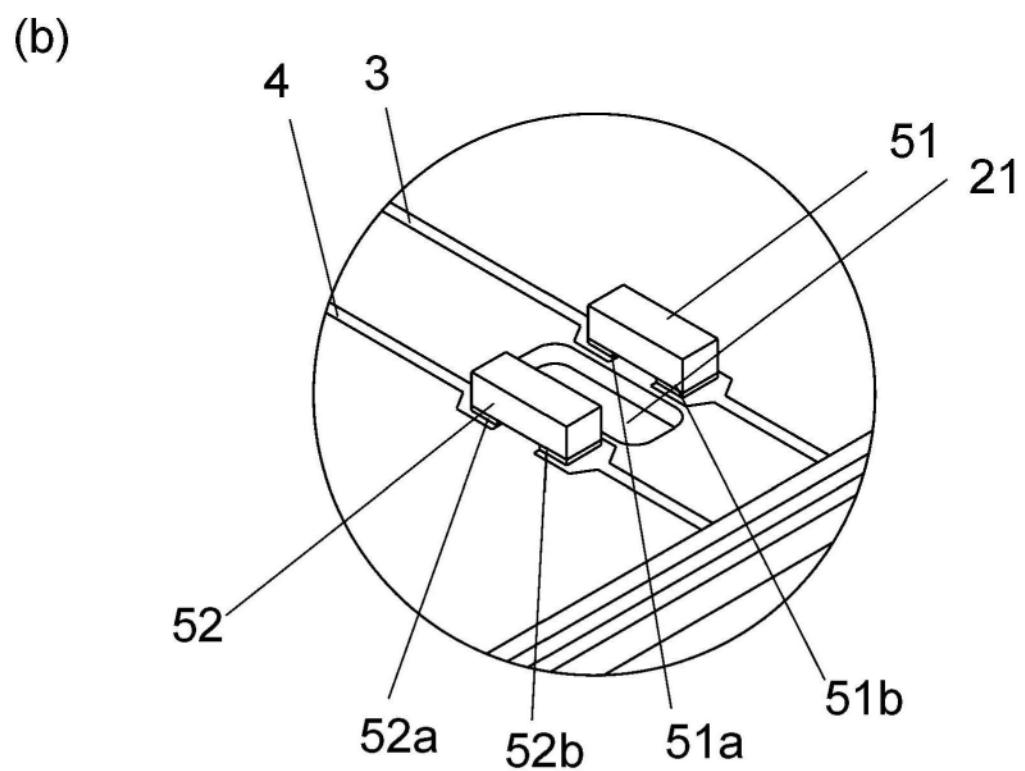

- [0018] 图12是本发明的其他实施方式所涉及的高频基体,图12的(a)是本发明的其他实施方式所涉及的高频基体的立体图,图12的(b)是表示图12的(a)的F的放大立体图。

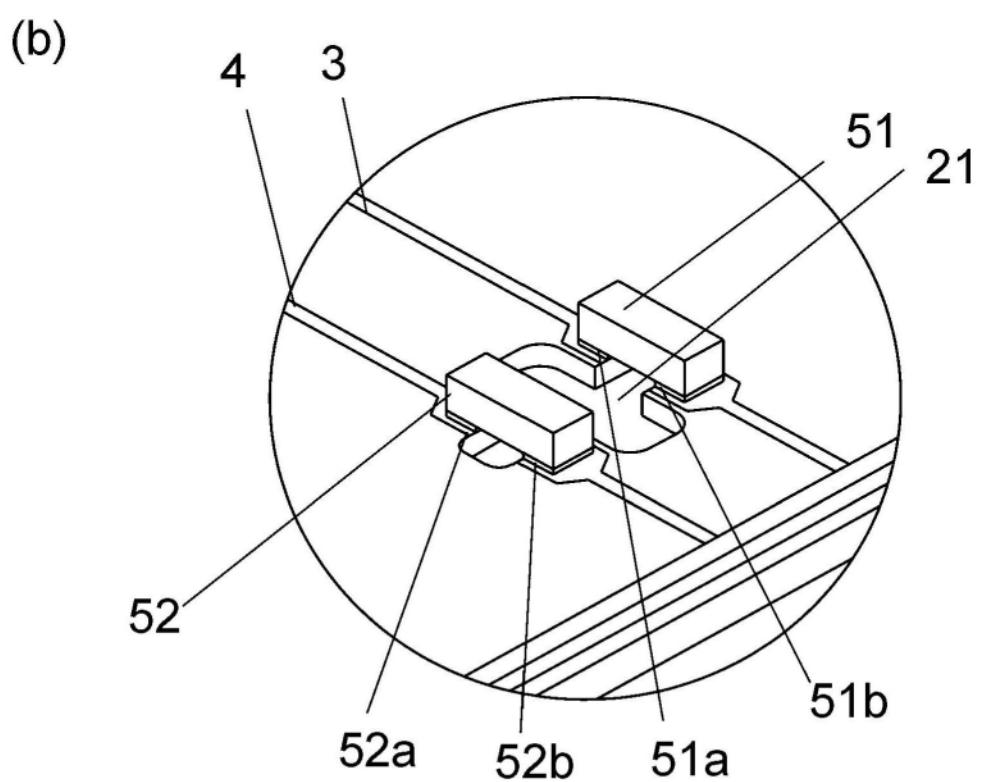

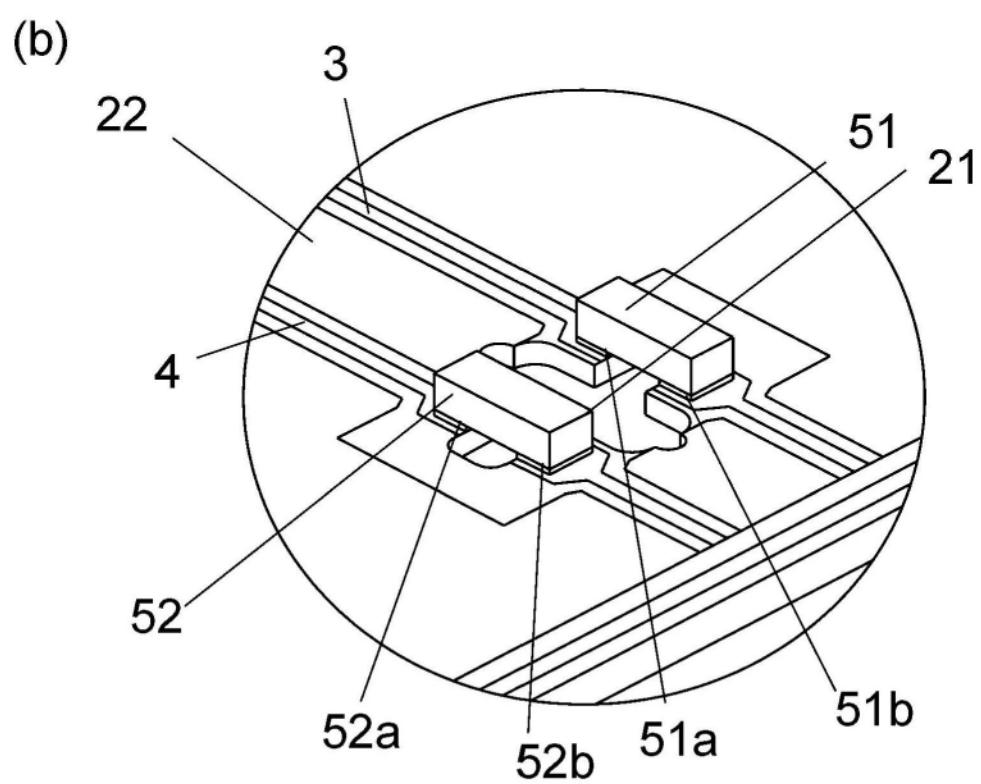

- [0019] 图13是本发明的其他实施方式所涉及的高频基体,图13的(a)是本发明的其他实施方式所涉及的高频基体的立体图,图13的(b)是表示图13的(a)的G的放大立体图。

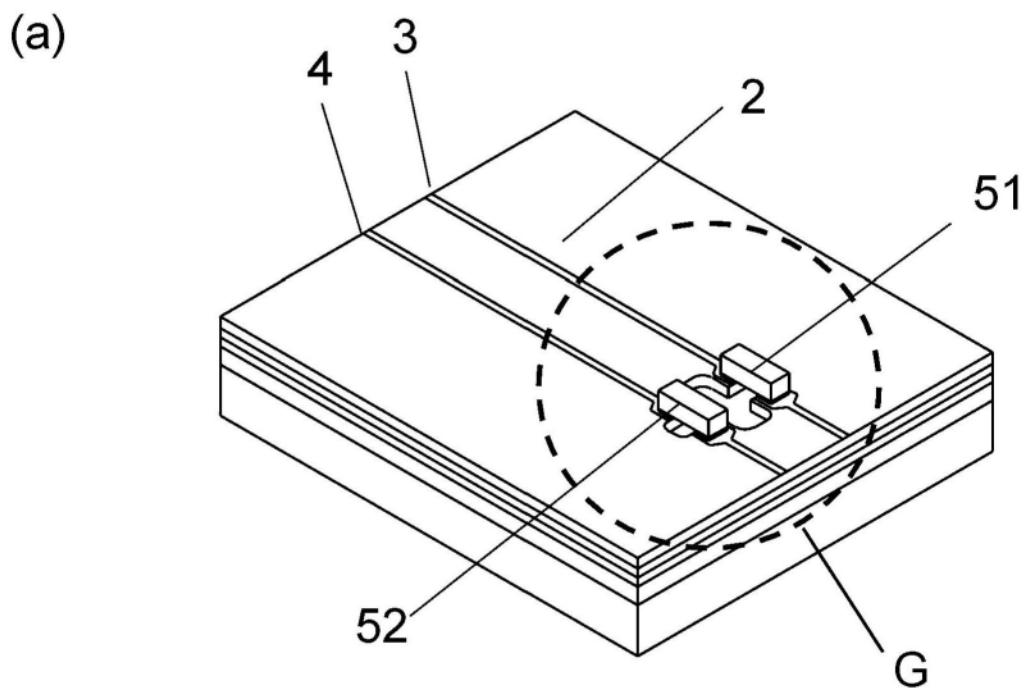

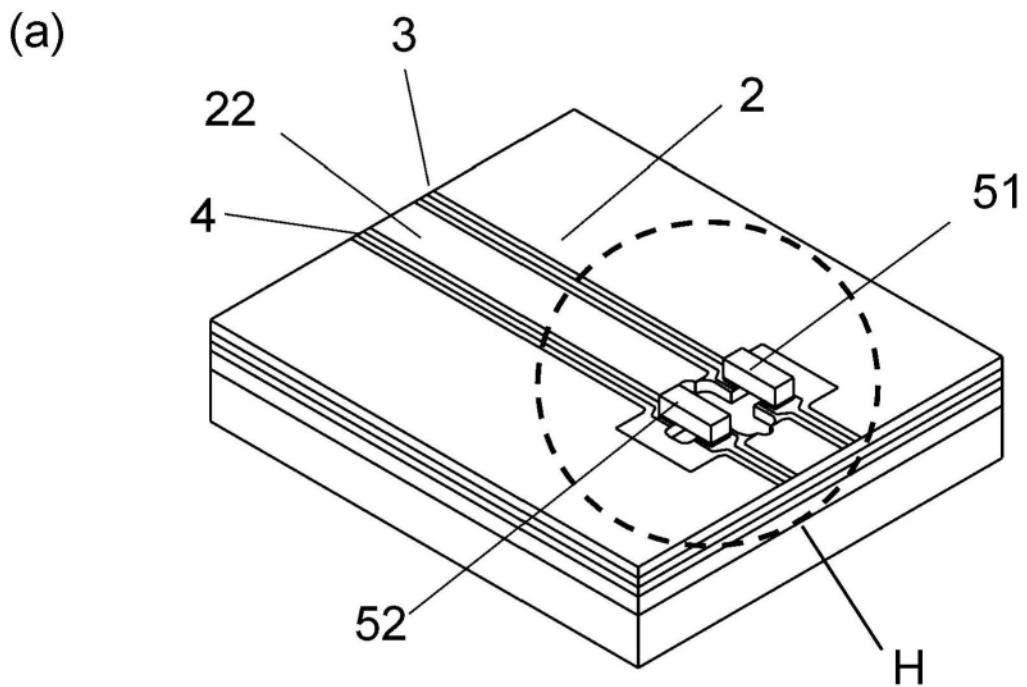

- [0020] 图14是本发明的其他实施方式所涉及的高频基体,图14的(a)是本发明的其他实施方式所涉及的高频基体的立体图,图14的(b)是表示图14的(a)的H的放大立体图。

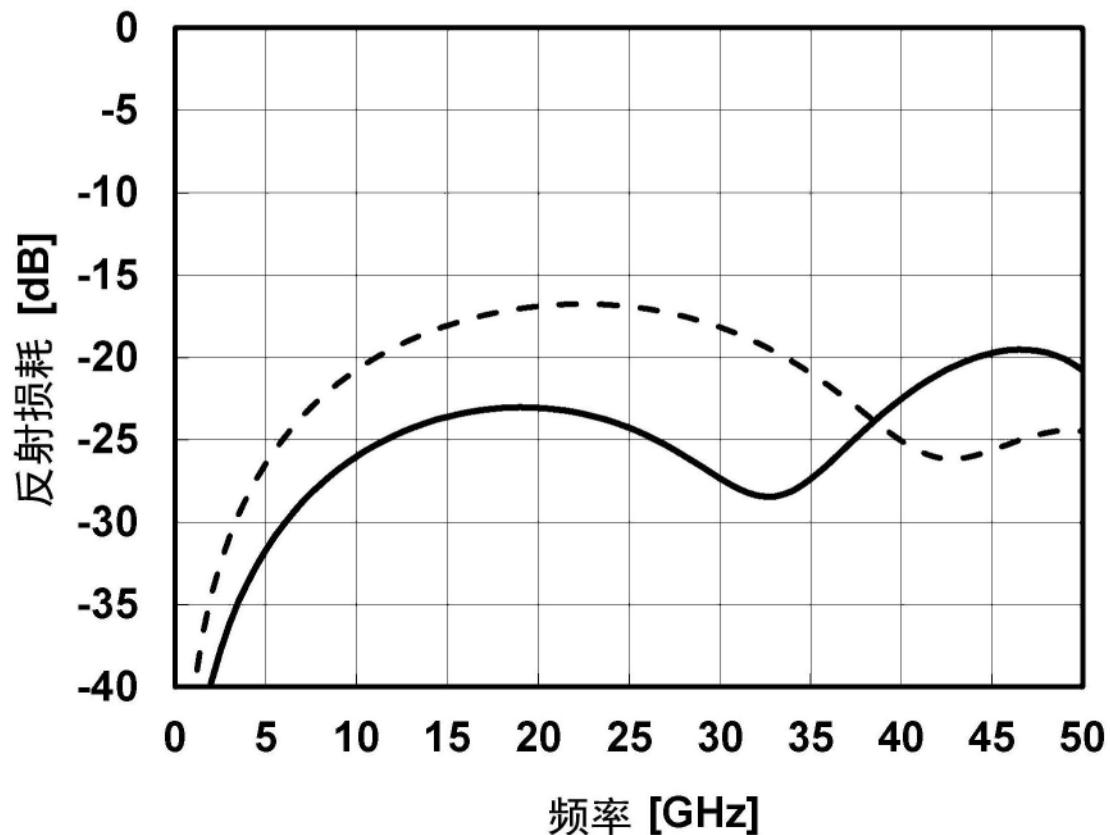

- [0021] 图15是表示本发明的其他实施方式所涉及的高频基体的阻抗的值的图表。

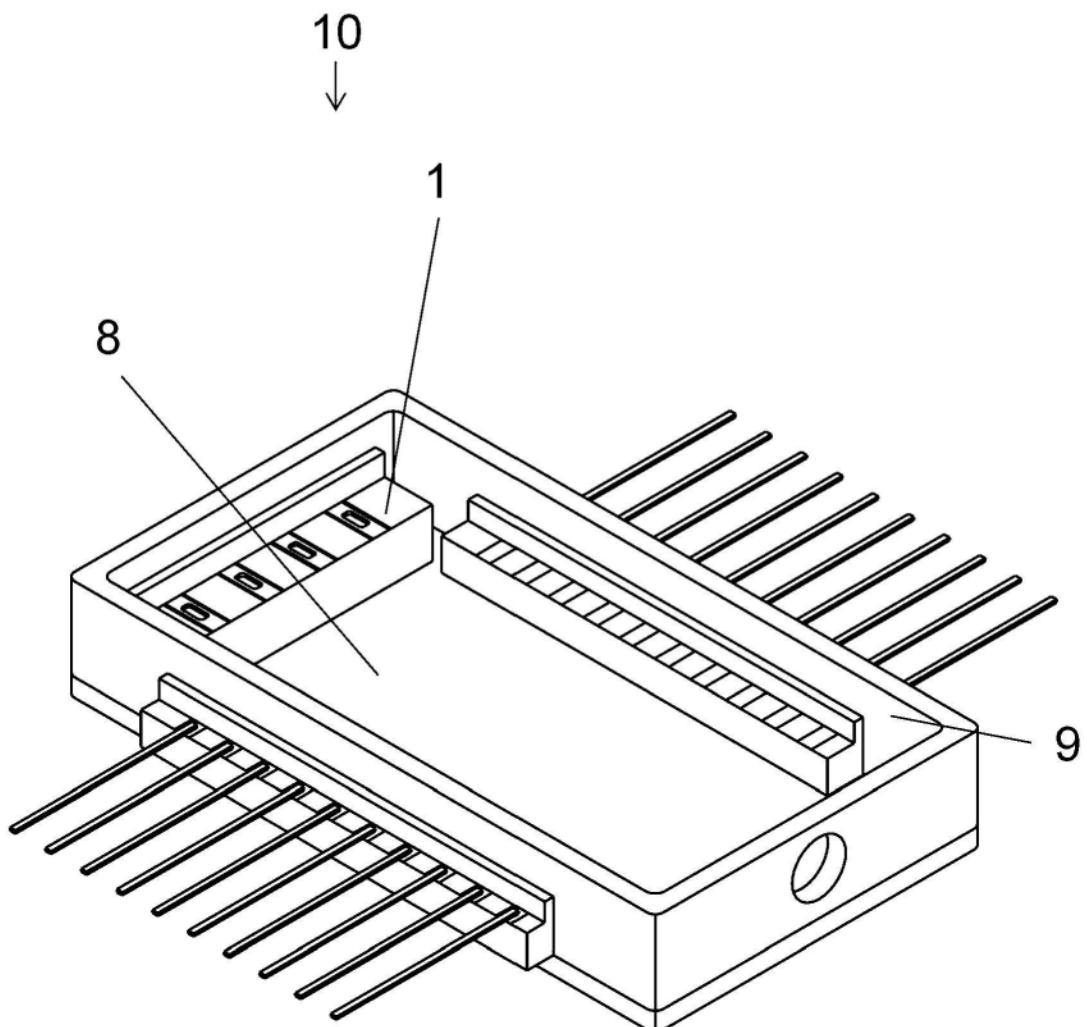

- [0022] 图16是本发明的一实施方式所涉及的高频封装件的立体图。

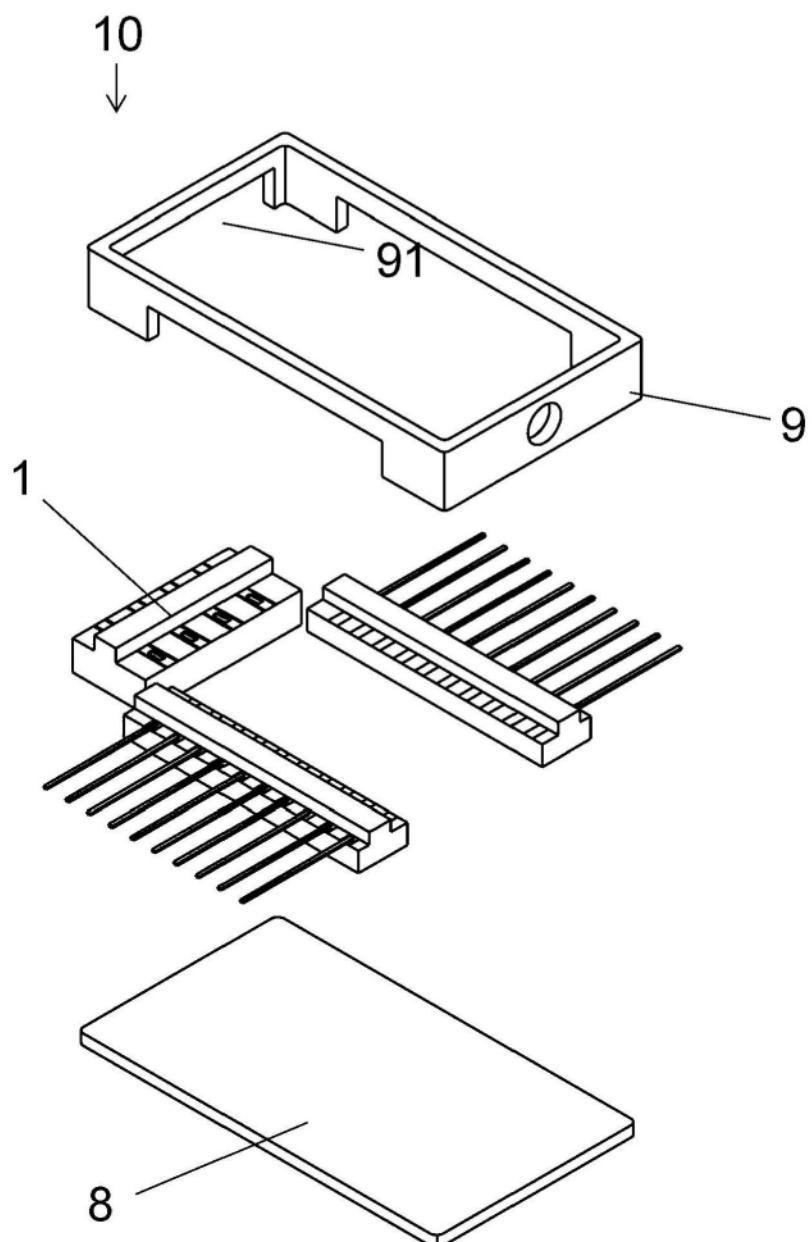

- [0023] 图17是本发明的一实施方式所涉及的高频封装件的分解立体图。

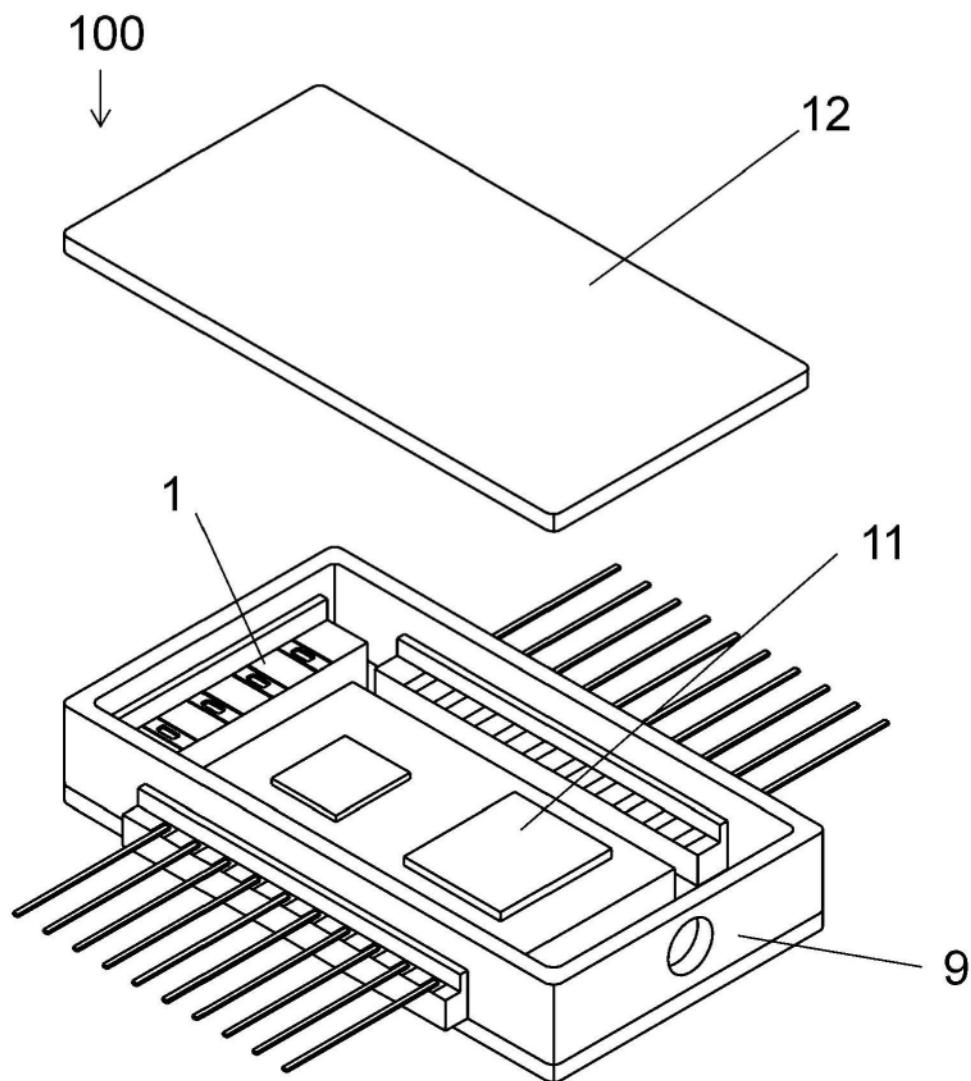

- [0024] 图18是本发明的一实施方式所涉及的高频模块的立体图。

## 具体实施方式

[0025] 以下,参照附图对本发明的实施方式所涉及的高频基体进行说明。

[0026] <高频基体的结构>

[0027] 图1表示本发明的一实施方式所涉及的高频基体1的立体图,图2是图1所示的本发明的一实施方式所涉及的高频基体,图2的(a)是本发明的一实施方式所涉及的高频基体的俯视图,图2的(b)是以图1的A表示的放大立体图。图3、图5、图7以及图9是本发明的其他实施方式所涉及的高频基体的立体图。图4、图6、图8以及图10分别是图3、图5、图7以及图9所示的本发明的其他实施方式所涉及的高频基体,图4的(a)、图6的(a)、图8(a)以及图10的(a)是本发明的其他实施方式所涉及的高频基体的俯视图,图4的(b)、图6的(b)、图8(b)以及图10的(b)分别是以图3的B、图5的C、图7的D以及图9的E表示的放大立体图。图11是本发明的其他实施方式所涉及的高频基体的分解立体图。图12、图13以及图14是本发明的其他实施方式所涉及的高频基体,图12的(a)、图13的(a)以及图14的(a)是本发明的其他实施方式所涉及的高频基体的立体图,图12的(b)是表示图12的(a)的F的放大立体图,图13的(b)是表示图13的(a)的G的放大立体图,图14的(b)是表示图14的(a)的H的放大立体图。并且,图15是表示本发明的其他实施方式所涉及的高频基体的阻抗的值的图表。在这些图中,高频基体1具备绝缘基体2、第1线路导体3和第2线路导体4。

[0028] 绝缘基体2是包含多个电介质的绝缘层2a、2b、2c、2d以及2e被层叠而成。绝缘基体2例如在俯视下为矩形状,大小为4mm×4mm~50mm×50mm,高度为1mm~10mm。构成绝缘基体2的绝缘层的各层包含电介质材料。作为电介质材料,例如能够利用氧化铝质烧结体、莫来石质烧结体、碳化硅质烧结体、氮化铝质烧结体或者氮化硅质烧结体这种的陶瓷材料、或者玻璃陶瓷材料。

[0029] 在绝缘基体2的上表面,设有将绝缘层2a贯通的凹部21。凹部21在俯视下例如为矩形状,大小为0.2mm×2mm~1mm×10mm。也可以凹部21在俯视下为椭圆形状、正方形、角部为圆形的矩形状。此外,凹部21在剖视下例如为矩形状,与绝缘基体2的上表面平行的方向

的长度为0.2mm～2mm,与绝缘基体2的上表面垂直的方向的长度、即凹部21的深度为0.2mm～2mm。也可以凹部21在剖视下为锥状、倒锥状以及阶梯形状。凹部21是空间或者由包含树脂材料、玻璃材料等的电介质材料填满,介电常数比绝缘基体2低。

[0030] 在绝缘层2b、2c、2d的上表面,在俯视下与凹部21重叠的位置的周围以及与第1线路导体3以及第2线路导体4重叠的位置,设有多个接地导体2bg、2cg以及2dg,通过贯通导体等而上下的接地导体2bg、2cg以及2dg被电连接。图11中,在四边形部P1、P2以及P3示出与凹部21重叠的位置,在其周围设有接地导体2bg、2cg、2dg。也就是说,接地导体2bg、2cg、2dg在俯视下与凹部21重叠的以四边形部P1、P2以及P3所示的位置并未设置。此外,可以在绝缘层2e的上表面设置接地导体2eg,可以在绝缘基体2的下表面、即绝缘层2e的下表面设置下表面接地导体层21eg。接地导体2eg、下表面接地导体层21eg经由贯通导体而电连接于各层的接地导体2bg、2cg、2dg、2eg。

[0031] 接地导体2eg或者下表面接地导体层21eg例如可以设置在绝缘层2e的上表面或者下表面的整体,此外,也可以设置在俯视下为矩形状且与凹部21重叠的以四边形部P1、P2以及P3表示的位置。另外,表示在俯视下与凹部21重叠的未设置接地导体2bg、2cg以及2dg的位置的四边形部P1、P2以及P3的大小为0.2mm×0.2mm～20mm×20mm。此外,接地导体2bg、2cg、2dg以及2eg例如包含钨、钼以及锰等的金属材料。此外,下表面接地导体层21eg是例如包含钨、钼以及锰等的金属材料,并在表面实施镀镍或镀金而成。

[0032] 如图1以及图2所示,在绝缘基体2的上表面、即绝缘层2a的上表面,设有与凹部21空出间隔而延伸的第1线路导体3。第1线路导体3例如可以包含金、银、铜、镍、钨、钼以及锰等的金属材料,是在绝缘层2a的表面以金属化层或镀覆层等形式被同时烧成、或者进行金属镀覆而成。此外,第1线路导体3的宽度为0.05mm～2mm,长度为4mm～50mm。

[0033] 此外,在绝缘基体2的上表面、即绝缘层2a的上表面,设有与凹部21空出间隔、与第1线路导体3并行地延伸的第2线路导体4。第2线路导体4例如可以包含金、银、铜、镍、钨、钼以及锰等的金属材料,是在绝缘层2a的表面以金属化层或镀覆层等形式被同时烧成、或者进行金属镀覆而成。此外,第2线路导体4的宽度为0.05mm～2mm,长度为4mm～50mm。

[0034] 本发明的实施方式所涉及的高频基体1通过在第1线路导体3与第2线路导体4之间存在凹部21而形成空间。由此,能够减小第1线路导体3与第2线路导体4之间的介电常数。因此,通过使第1线路导体3与第2线路导体4之间变窄从而静电电容变大。伴随于此,能够容易增大容易变得比期望的值小的特性阻抗。进而,能够控制在期望的特性阻抗。其结果,能够容易使得高频基体1第1线路导体3与第2线路导体4之间的特性阻抗匹配至期望的值,能够提高传输高频信号的第1线路导体3与第2线路导体4的高频特性。

[0035] 此外,如图3～图14所示,第1线路导体3以及第2线路导体4也可以在线路导体的中途具有分离部。该情况下,电容器与在各个分离部所设置的第1电极焊盘32以及第2电极焊盘42电连接而被设置。

[0036] 如图3以及图4所示,第1线路导体3可以具有在中途将线路导体分离的第1分离部31。该情况下,第1线路导体3包含:第1电容器51的第1电极51a以及第2电极51b所连接的第1电极焊盘32、和从第1电极焊盘32延伸设置的第1线路33。例如,在俯视下,第1电极焊盘32的长度为0.2mm～2mm,宽度为0.2mm～2mm,第1线路33的长度为1.5mm～25mm,宽度为0.05mm～2mm。此外,第1电极焊盘32以及第1线路33的厚度为0.01mm～0.1mm。

[0037] 第1电极焊盘32被设置为在俯视下至少与接地导体2eg或者下表面接地导体层21eg以及接地导体2bg、2cg以及2dg未被设置的位置即四边形部P1、P2、以及P3重叠。此外,第1线路33被设置为在俯视下至少与接地导体2bg重叠。通过这种结构,第1电极焊盘32以及第1线路33、与接地导体2eg或者下表面接地导体层以及接地导体2bg成为带状线构造,本发明的高频基体1能够顺利地进行高频信号的传输。

[0038] 此外,第1电极焊盘32以及第1线路33例如可以包含金、银、铜、镍、钨、钼以及锰等的金属材料。此外,可以是在绝缘层2a的上表面以金属化层或镀覆层等的形式被同时烧成、或者进行金属镀覆而成。

[0039] 如图3以及图4所示,第2线路导体4可以具有在中途将线路导体分离的第2分离部41。该情况下,第2线路导体4包含:第2电容器52的第1电极52a以及第2电极52b所连接的第2电极焊盘42、和从第2电极焊盘42延伸设置的第2线路43。第2电极焊盘42被设置为在俯视下夹着凹部21而与第1电极焊盘32对置。例如,在俯视下,第2电极焊盘42的长度为0.2mm~2mm,宽度为0.2mm~2mm,第2线路43的长度为1.5mm~25mm,宽度为0.05mm~2mm。此外,第2电极焊盘42以及第2线路43的厚度为0.01mm~0.1mm。此外,第2电极焊盘42以及第2线路43例如包含金、银、铜、镍、钨、钼以及锰等的金属材料,是在绝缘层2a的上表面以金属化层或镀覆层等的形式被同时烧成、或者进行金属镀覆而成。

[0040] 第2电极焊盘42被设置为在俯视下至少与接地导体2eg或者下表面接地导体层21eg以及接地导体2bg、2cg以及2dg未被设置的位置即四边形部P1、P2以及P3重叠。此外,第2线路43被设置为在俯视下至少与接地导体2bg重叠。通过这种结构,第2电极焊盘42以及第2线路43、与接地导体2eg或者下表面接地导体层以及接地导体2bg成为带状线构造,本发明的高频基体1能够顺利地进行高频信号的传输。

[0041] 在第1电容器51以及第2电容器52的下表面设有上述的电极。该电极经由接合材料而被电连接以及接合。接合材料例如使用Sn-Ag-Cu系焊料、Sn-Zn-Bi系焊料、Sn-Cu系焊料等即可。

[0042] 此外,高频基体1在第1线路导体3与第2线路导体4之间分别设置第1电容器51以及第2电容器52,以使得与第1分离部31以及第2分离部41重叠,第1电容器51以及第2电容器52经由接合材料而与第1电极焊盘32以及第2电极焊盘42电连接以及固定。第1电容器51以及第2电容器52例如在俯视下为矩形状,大小为0.3mm×0.4mm~2mm×4mm,高度为0.3mm~2mm。此外,第1电容器51以及第2电容器52例如包含镁橄榄石、氧化铝、铌镁酸钡、以及钛酸钕钡。第1电容器51以及第2电容器52经由第1电极焊盘32以及第2电极焊盘42而被设置于第1分离部31以及第2分离部41,进行电连接以及固定,从而能够去除在第1线路导体3与第2线路导体4传输的高频信号的直流电压分量。

[0043] 特别地,为了使高频基体1小型化而使第1线路导体3与第2线路导体4的间隔变窄的情况下,阻抗的值容易变小。因此,通过在第1线路导体3与第2线路导体4之间设置凹部21,能够抑制这种的阻抗变小的情况。此外,由于与没有凹部21的情况相比,能够使第1线路导体3与第2线路导体4接近,因此能够实现高频基体1的小型化。

[0044] 此外,凹部21在第1线路33以及第2线路43所连接的一侧的第1电极焊盘32以及第2电极焊盘42的端部,与第1线路导体3以及第2线路导体4并行地延伸。由此,能够更为降低第1电极焊盘32与第2电极焊盘42之间的介电常数。因此,能够进一步增大与第1电极焊盘32以

及第2电极焊盘42之间所产生的阻抗。

[0045] 此外,如图5~图8所示,第1分离部31以及第2分离部41也可以凹陷。换言之,可以在第1电极焊盘32之间以及第2电极焊盘42之间设置与凹部21连续的槽。此时,凹部21可以是交叉的形状,换言之可以是在第1分离部31、第2分离部41以及第1线路导体3与第2线路导体4之间连续的形状。

[0046] 此外,如图9以及图10所示,凹部21可以在位于第1电极焊盘32与第2电极焊盘42之间的端部的侧壁具有切口部7。通过具有切口部7,从而能够更为增大在第1线路导体3与第2线路导体4之间产生的阻抗的值。

[0047] 此外,切口部7可以在表面形成有金属化层71。金属化层71例如包含钨、钼、锰、镍或者金等。通过具有金属化层71,能够在第1线路导体3以及第2线路导体4所连接的一侧的第1电极焊盘32以及第2电极焊盘42的端部,抑制包含凹部21的大气中的层与包含绝缘基体2的电介质材料的边界部的电场的扩散,并且能够抑制与第1线路导体3以及第2线路导体4之间所产生的串扰、谐振,能够提高高频基体1的频率特性。

[0048] 如图11所示,在绝缘基体2的内部、即绝缘层2c的上表面,设有经由连接线路导体24而与接地导体2cg电连接的内部接地导体层23。内部接地导体层23例如在俯视下是椭圆形状的一部分经由连接线路导体24而与周围的接地导体2cg电连接的形状,椭圆的部分的大小为 $0.3\text{mm} \times 0.4\text{mm} \sim 2\text{mm} \times 8\text{mm}$ 。内部接地导体层23的一部分可以是圆形以及矩形状。此外,内部接地导体层23以及连接线路导体24例如包含钨、钼以及锰等的金属材料,可以在绝缘层2c的上表面以金属化层的形式被同时烧成而成。特别地,在内部接地导体层23在俯视下如椭圆形状那样具有曲线的端部的情况下,与在俯视下为矩形状的情况下相比,能够抑制第1电极焊盘32彼此与第2电极焊盘42彼此的阻抗的急剧的变化。其结果,能够抑制高频信号在第1电极焊盘32彼此、第2电极焊盘42彼此传输时产生的插入损耗、反射损耗。

[0049] 进而,如图11所示,内部接地导体层23被设置为在俯视下与位于第1电极焊盘32彼此以及第2电极焊盘42彼此之间的凹部21重叠。与没有内部接地导体层23的情况相比,能够增强如第1电容器51以及第2电容器52那样经由电容器而传输高频信号时所产生的、与配置于电容器的周边的接地导体之间的电场耦合。因此,内部接地导体层23能够抑制高频信号传输时的电场分布比期望的范围展宽从而产生的串扰、谐振,能够提高高频基体1的频率特性。其结果,第1线路导体3以及第2线路导体4能够经由电容器使高频信号顺利地传输。

[0050] 此外,内部接地导体层23被设置为在俯视下外周部重叠于第1电极焊盘32和第2电极焊盘42。由此,与上述的作用效果同样地,能够增强经由第1电极焊盘32与第2电极焊盘42以及电容器来传输时所产生的、第1电极焊盘32与第2电极焊盘42以及电容器的周边被配置的接地导体之间的电场耦合。因此,内部接地导体层23能够抑制高频信号传输时的电场分布比期望的范围展宽从而产生的串扰、谐振。其结果,第1线路导体3以及第2线路导体4能够经由电容器使高频信号在第1电极焊盘32与第2电极焊盘42顺利地传输。

[0051] 如图11所示,内部接地导体层23经由连接线路导体24而与接地导体2cg电连接。再有,也可以经由设置为将绝缘层2b、2c、2d以及2e的上下表面贯通的过孔等,设置于各层的上表面的接地导体2bg、2cg、2dg以及2eg被电连接。

[0052] 此外,在绝缘层2a的上表面设有接地导体层22。接地导体层22被设置于第1线路导体3与第2线路导体4各自的两侧、以及第1线路导体3与第2线路导体4之间,形成共面线路。

在这种情况下,与带状线构造相比,能够增强第1线路导体3以及第2线路导体4与成为基准电位的接地导体层22的电场耦合。其结果,高频基体1能够抑制高频信号在第1线路导体3以及第2线路导体4传输时所产生的电场的展宽,能够经由第1线路导体3以及第2线路导体4而顺利地传输高频信号。

[0053] 图15所示的图表是实验性地表示上述的特性阻抗的匹配。图表是在第1电极焊盘32与第2电极焊盘42之间、以及第1电极焊盘32之间及第2电极焊盘42之间存在连续的十字状的凹部21以及切口部7的情况下和不存在的情况下比较反射损耗相对于频率的变化的结果。图表中,横轴是频率,纵轴是传输信号的反射损耗。虚线是在绝缘基体2的上表面未设置凹部21以及切口部7的情况下,实线是在绝缘基体2的上表面设置有凹部21以及切口部7的情况下。例如,图15的图表中,在绝缘基体2的上表面设置有凹部21以及切口部7的情况下,传输信号的反射损耗在传输信号的频率直至40GHz为止是-20dB以下。该情况下,在未设置凹部21以及切口部7的情况下,传输信号的反射损耗在频率为40GHz之前大于-20dB。但是,通过设置凹部21以及切口部7,能够将高频信号的传输线路中的特性阻抗控制在期望的值,能够抑制传输线路所产生的反射损耗。

[0054] <高频基体的制造方法>

[0055] 例如,如果多个绝缘层2a、2b、2c、2d以及2e包含氧化铝质烧结体的情况下,绝缘基体2按照如下方式进行制作。首先,在氧化铝以及氧化硅等的原料粉末中添加混合适当的有机粘合剂以及溶剂等来制作浆料。接下来,利用刮刀法等的成形法将浆料成形为片状,由此制作多片的陶瓷生片。此时,在位于最上方的生片的一部分形成成为凹部21的贯通孔。

[0056] 之后,对上述的陶瓷生片进行层叠、压接。最后,将该层叠的陶瓷生片在还原气氛中以大约1600℃的温度进行烧成,并且进行切断加工、冲压加工形成为合适的形状,从而能够制作出包含期望的形状的绝缘基体2。

[0057] 在第1电极焊盘32、第1线路33、第2电极焊盘42、第2线路43、接地导体层22、内部接地导体层23、连接线路导体24以及各层的上表面所设置的接地导体2bg、2cg、2dg以及2eg、下表面接地导体层21eg例如包含由钨、钼、锰等的高熔点的金属构成的金属化层的情况下,能够按照如下方式形成。也就是说,首先将高熔点的金属的粉末与有机溶剂以及粘合剂一起搅拌以使得充分混合来制作金属糊膏,将制作出的金属糊膏通过丝网印刷等的方法印刷在成为绝缘层2a、2b、2c、2d以及2e的上表面、下表面的陶瓷生片的规定部位。之后,将印刷有这些金属糊膏的陶瓷生片进行层叠并且压接,同时进行烧成。通过以上工序,在绝缘基体2的上表面、内部即绝缘层之间,金属化层作为第1电极焊盘32、第1线路33、第2电极焊盘42、第2线路43、接地导体层22、内部接地导体层23、连接线路导体24、各层的上表面所设置的接地导体2bg、2cg、2dg以及2eg以及绝缘层2e的下表面所设置的下表面接地导体层21eg而被覆。此外,第1电极焊盘32、第1线路33、第2电极焊盘42、第2线路43、接地导体层22以及下表面接地导体层21eg也可以在表面设置镀镍、镀金。由此,能够提高各个金属层的表面的、钎料或焊料等接合材料的浸润性,能够提高基板8、电容器的接合性,并且能够提高耐腐蚀性、耐候性。

[0058] 例如在作为多个绝缘层2a、2b、2c、2d以及2e的陶瓷生片设置贯通孔,在贯通孔内填充与形成接地导体层22、内部接地导体层23、连接线路导体24、各层的上表面所设置的接地导体2bg、2cg、2dg及2eg以及绝缘层2e的下表面所设置的下表面接地导体层21eg时同样

的金属糊膏,将各个陶瓷生片进行层叠并且压接,同时进行烧成,由此能够设置过孔。贯通孔例如能够通过利用金属销的机械式的冲压加工、或者利用激光的加工等的开孔加工来形成。在金属糊膏向贯通孔填充时,一并使用真空吸引等的单元从而使得金属糊膏的填充变得容易。

[0059] <高频封装件的结构>

[0060] 图16表示本发明的一实施方式所涉及的高频封装件10的立体图,图17表示本发明的一实施方式所涉及的高频封装件10的分解立体图。这些图中,高频封装件10具备基板8、壳体9以及本发明的实施方式所涉及的高频基体1。

[0061] 基板8在俯视下为矩形状。此外,俯视下的大小为10mm×10mm~50mm×50mm,高度为0.5mm~20mm。

[0062] 设置壳体9,以使得包围基板8的上表面。壳体9在俯视下为矩形状,大小为10mm×10mm~50mm×50mm,高度为2mm~15mm。此外,厚度为0.5mm~2mm。

[0063] 基板8、壳体9例如能够使用铁、铜、镍、铬、钴、钼或钨这种的金属、或者这些金属的合金、例如铜-钨合金、铜-钼合金、铁-镍-钴合金等。通过对这种金属材料的胚料实施轧制加工法、冲压加工法这种的金属加工法,从而能够制作构成基板8的金属部件。

[0064] 在壳体9的侧壁部设有贯通孔91。在贯通孔91,插入固定上述记载的高频基体1、将高频封装件10的内侧与外侧电连接的包含化铝质烧结体的绝缘端子。换言之,在高频封装件10中,高频基体1发挥输入输出端子的作用。

[0065] <高频模块的结构>

[0066] 图18表示本发明的一实施方式所涉及的高频模块100的立体图。该图中,高频模块100具备本发明的实施方式所涉及的高频封装件10、半导体元件11以及盖体12。

[0067] 半导体元件11例如是激光二极管(LD)。半导体元件11也可以是PD等。在LD的情况下,可以在壳体9设置安装高频基体1、绝缘端子的贯通孔91以外,还设置贯通孔来安装光纤。

[0068] 盖体12在壳体9的上端被接合,以使得覆盖高频封装件10的内部。盖体12在俯视下为矩形状,大小为10mm×10mm~50mm×50mm,高度为0.5mm~2mm。盖体12例如能够利用铁、铜、镍、铬、钴、钼或钨这种的金属、或者这些金属的合金、例如铜-钨合金、铜-钼合金、铁-镍-钴合金等。通过对这种金属材料的胚料实施轧制加工法、冲压加工法这种的金属加工,从而能够制作构成盖体12的金属部件。

[0069] 以上,本发明并不限定于上述实施方式,在不脱离本发明的主旨的范围内能够进行各种的变更等。再有,属于权利要求书的变更等全部是在本发明的范围内。

[0070] -符号说明-

[0071] 1 高频基体

[0072] 2 绝缘基体

[0073] 21 凹部

[0074] 22 接地导体层

[0075] 23 内部接地导体层

[0076] 24 连接线路导体

[0077] 3 第1线路导体

- [0078] 31 第1分离部

- [0079] 32 第1电极焊盘

- [0080] 33 第1线路

- [0081] 4 第2线路导体

- [0082] 41 第2分离部

- [0083] 42 第2电极焊盘

- [0084] 43 第2线路

- [0085] 51 第1电容器

- [0086] 52 第2电容器

- [0087] 7 切口部

- [0088] 71 金属化层

- [0089] 8 基板

- [0090] 9 壳体

- [0091] 91 贯通孔

- [0092] 10 高频封装件

- [0093] 11 半导体元件

- [0094] 12 盖体

- [0095] 100 高频模块。

图1

(a)

(b)

图2

图3

(a)

(b)

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

图14

图15

图16

图17

图18