(19)

OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 967 320**

(51) Int. Cl.:

**H03M 7/30** (2006.01)

**G06F 9/30** (2008.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Fecha de presentación y número de la solicitud internacional: **27.07.2017 PCT/US2017/044227**

(87) Fecha y número de publicación internacional: **29.03.2018 WO18057115**

(96) Fecha de presentación y número de la solicitud europea: **27.07.2017 E 17749310 (3)**

(97) Fecha y número de publicación de la concesión europea: **29.11.2023 EP 3516774**

---

(54) Título: **Almacenamiento de datos en direcciones de memoria contiguas**

(30) Prioridad:

**22.09.2016 US 201615273366**

(45) Fecha de publicación y mención en BOPI de la traducción de la patente:

**29.04.2024**

(73) Titular/es:

**QUALCOMM INCORPORATED (100.0%)

5775 Morehouse Drive

San Diego, CA 92121-1714, US**

(72) Inventor/es:

**MAHURIN, ERIC y

HOYLE, DAVID**

(74) Agente/Representante:

**ISERN JARA, Jorge**

**ES 2 967 320 T3**

---

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín Europeo de Patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre Concesión de Patentes Europeas).

**DESCRIPCIÓN**

Almacenamiento de datos en direcciones de memoria contiguas

5    Campo

La presente divulgación se refiere, en general, al almacenamiento de datos.

10    Descripción de la técnica relacionada

15    Los avances en tecnología han dado como resultado dispositivos informáticos más potentes. Por ejemplo, dispositivos informáticos como ordenadores portátiles y de escritorio y servidores, así como dispositivos informáticos inalámbricos como teléfonos inalámbricos portátiles, asistentes digitales personales (PDA) y dispositivos de paginación, han mejorado sus capacidades informáticas y son capaces de realizar operaciones cada vez más complejas. Las 20    capacidades informáticas mejoradas también han mejorado las capacidades de los dispositivos en varias otras aplicaciones. Por ejemplo, los vehículos pueden incluir dispositivos de procesamiento para permitir operaciones del sistema de posicionamiento global u otras operaciones de ubicación, operaciones de conducción autónoma, operaciones de comunicación interactiva y entretenimiento, etc. Otros ejemplos incluyen electrodomésticos, cámaras de seguridad, equipos de medición, etc., que también incorporan dispositivos informáticos para permitir una funcionalidad mejorada, como la comunicación utilizando el internet de las cosas.

25    Un dispositivo informático puede incluir un procesador que es capaz de procesar uno o más vectores de datos dispersos. Como se utiliza en la presente memoria, un "vector de datos dispersos" es un vector de datos que incluye elementos de datos con datos inválidos (por ejemplo, valores de datos "no importa", valores de datos predeterminados, valores de datos nulos o valores de datos cero) y elementos de datos con datos válidos (por ejemplo, valores de datos "de interés"). Datos inválidos en un vector de datos conducen a una computación y almacenamiento ineficientes. Por ejemplo, debido a que los vectores de datos dispersos incluyen elementos de datos con elementos de datos inválidos que no necesitan ser procesados, los componentes (por ejemplo, hardware) incluidos en el procesador pueden ser utilizados de manera ineficiente al procesar los datos inválidos.

30    Una técnica para mejorar la eficiencia de uso del hardware incluye comprimir un vector de datos dispersos dentro de una tubería de procesamiento del procesador para generar un vector de datos comprimido. Para generar el vector de datos comprimidos, el procesador puede desplazar los datos (dentro de la tubería de procesamiento del procesador) de manera que los elementos de datos con datos válidos estén adyacentes entre sí y los elementos de datos con datos inválidos estén adyacentes entre sí. Sin embargo, generar vectores de datos comprimidos dentro de la tubería de procesamiento puede resultar en un número relativamente grande de vectores de datos con esquemas de direccionamiento complejos. Además, generar vectores de datos comprimidos dentro del flujo de procesamiento puede resultar en un aumento de los costos de hardware.

35    40    Sumario

La invención está definida por el objeto de las reivindicaciones independientes. Las realizaciones preferidas se definen en las reivindicaciones dependientes.

45    Breve descripción de las figuras

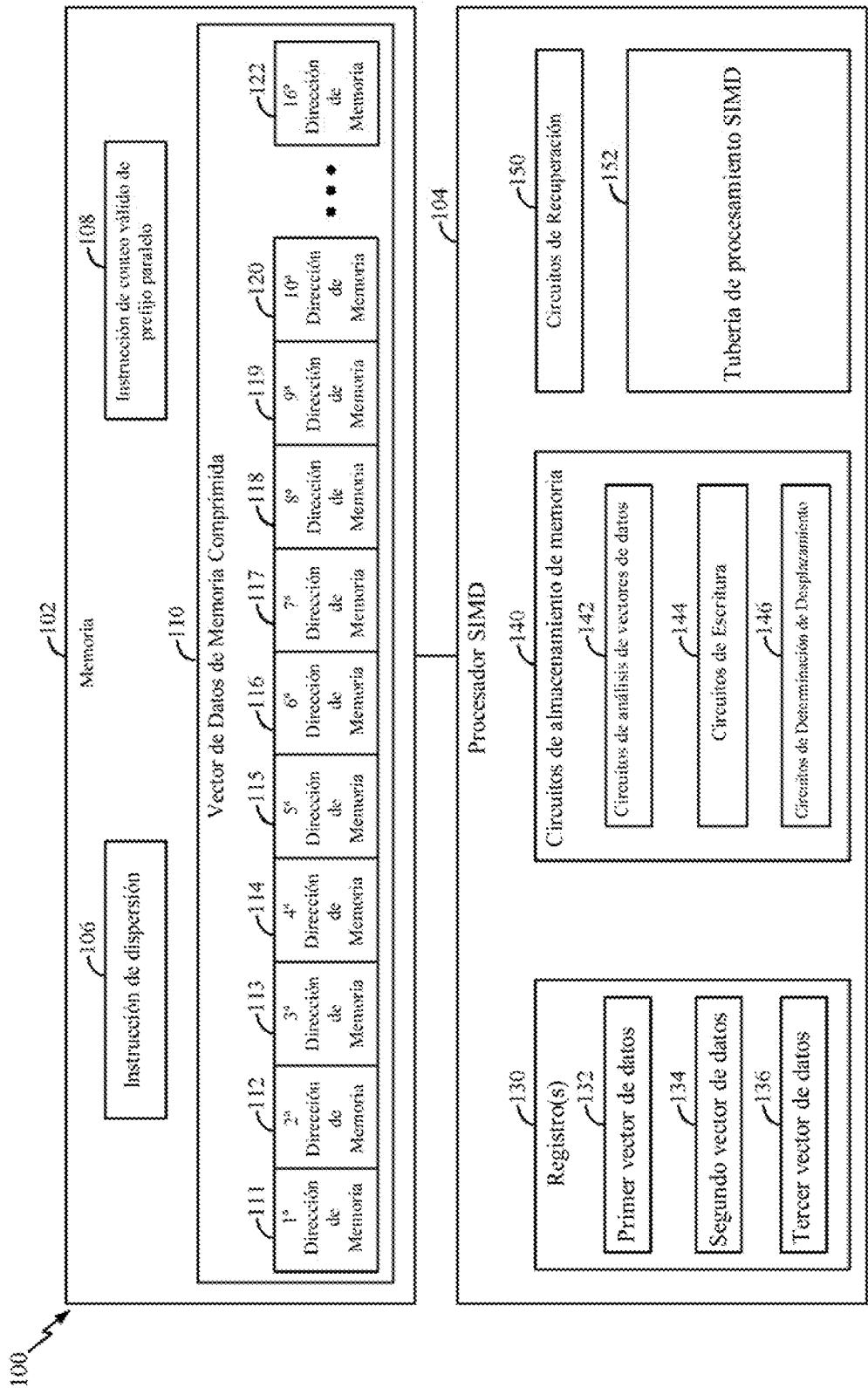

50    La Figura 1 es un diagrama de un sistema que es operable para almacenar datos en direcciones de memoria contiguas;

La Figura 2 ilustra vectores de datos dispersos que incluyen datos válidos e inválidos;

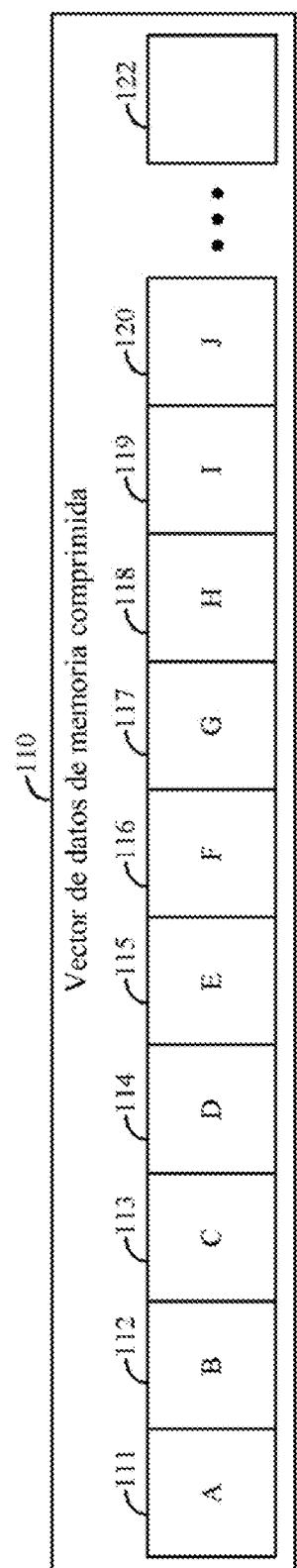

La Figura 3 ilustra un vector de datos de memoria comprimida;

La Figura 4 ilustra un gráfico para identificar un desplazamiento de valores de datos válidos en un vector de datos de memoria comprimida;

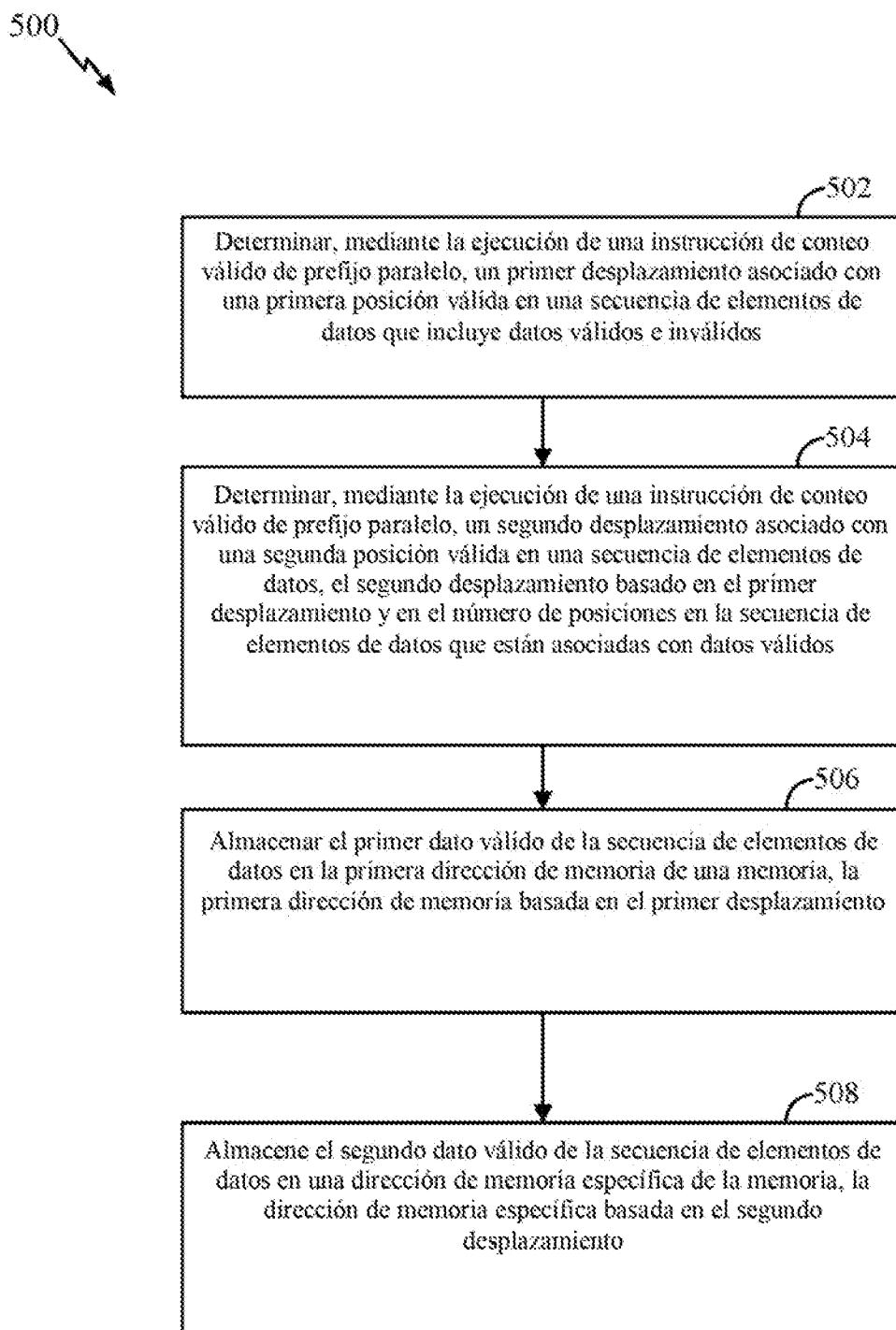

La Figura 5 ilustra un procedimiento para almacenar datos en direcciones de memoria contiguas; y

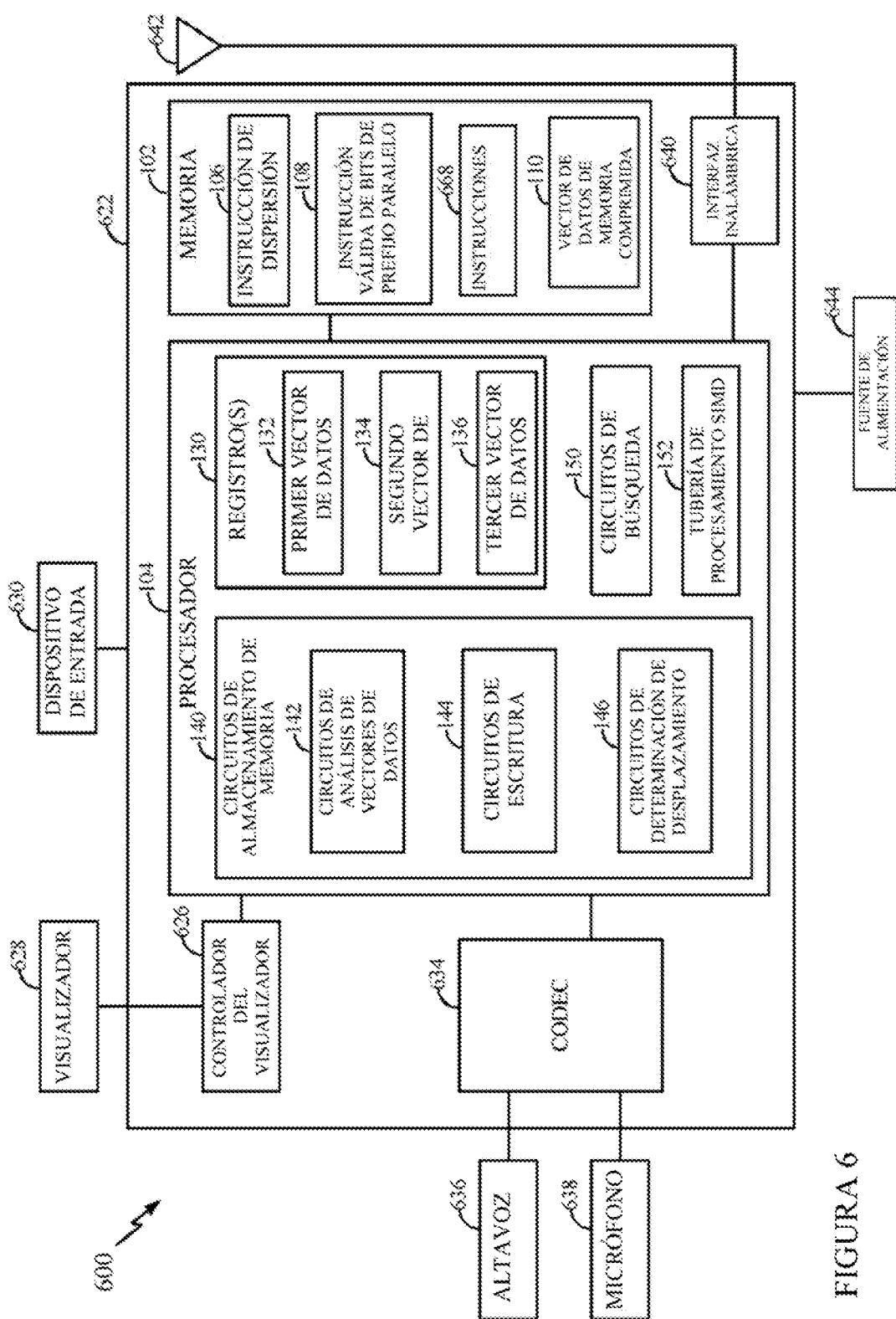

La Figura 6 es un diagrama de un dispositivo electrónico que incluye componentes operables para almacenar datos en direcciones de memoria contiguas.

55    Descripción detallada

60    Haciendo referencia a la Figura 1, se muestra un sistema 100 que es operable para almacenar datos en direcciones de memoria contiguas. El sistema 100 se puede implementar en un teléfono móvil, un asistente digital personal (PDA), una unidad de entretenimiento, un dispositivo de navegación, un reproductor de música, un reproductor de video, un reproductor de video digital, un reproductor de discos digitales de video (DVD) o cualquier otro dispositivo.

65    El sistema 100 incluye una memoria 102 que está acoplada a un procesador 104. De acuerdo con una realización, el procesador 104 incluye un procesador de instrucción única y múltiples datos (SIMD). La memoria 102 puede ser un medio legible por ordenador no transitorio que incluye instrucciones que son ejecutables por el procesador 104. Por

ejemplo, la memoria 102 incluye una instrucción de dispersión 106 que puede ser ejecutada por el procesador 104 y una instrucción de conteo válido de prefijo paralelo 108 que puede ser ejecutada por el procesador 104.

La memoria 102 también incluye un vector de datos de memoria comprimida 110. Como se describe a continuación, los datos válidos (en contraposición a los datos inválidos) de diferentes vectores de datos dispersos pueden almacenarse en el vector de datos de memoria comprimida 110 para generar un "vector de datos comprimido" en la memoria 102. El vector de datos de memoria comprimida 110 incluye una pluralidad de direcciones de memoria contiguas. Para ilustrar, el vector de datos de memoria comprimida 110 incluye una primera dirección de memoria 111, una segunda dirección de memoria 112 que es contigua a la primera dirección de memoria 111, una tercera dirección de memoria 113 que es contigua a la segunda dirección de memoria 112, una cuarta dirección de memoria 114 que es contigua a la tercera dirección de memoria 113, una quinta dirección de memoria 115 que es contigua a la cuarta dirección de memoria 114, una sexta dirección de memoria 116 que es contigua a la quinta dirección de memoria 115, una séptima dirección de memoria 117 que es contigua a la sexta dirección de memoria 116, una octava dirección de memoria 118 que es contigua a la séptima dirección de memoria 117, una novena dirección de memoria 119 que es contigua a la octava dirección de memoria 118, una décima dirección de memoria 120 que es contigua a la novena dirección de memoria 119, etc.

En la Figura 1, el vector de datos de memoria comprimida 110 incluye dieciséis direcciones de memoria. Por ejemplo, el vector de datos de memoria comprimida 110 incluye una decimosexta dirección de memoria 122 que es contigua a una decimoquinta dirección de memoria (no mostrada). Sin embargo, en otras realizaciones, el vector de datos de memoria comprimida 110 puede incluir direcciones de memoria contiguas adicionales (o menos). Como ejemplo no limitante, el vector de datos de memoria comprimida 110 puede incluir treinta y dos direcciones de memoria contiguas.

El procesador 104 incluye uno o más registros 130, circuitos de almacenamiento de memoria 140, circuitos de búsqueda 150 y una tubería de procesamiento SIMD 152. Aunque se muestra que uno o más registros 130 están incluidos en el procesador 104, en otras realizaciones, uno o más registros 130 pueden estar separados (y accesibles) al procesador 104. En otras realizaciones, el procesador 104 puede incluir componentes adicionales (o menos). Como ejemplo no limitante, en otras realizaciones, el procesador 104 también puede incluir una o más unidades aritmético-lógicas (ALU), una o más unidades de ejecución específicas de la aplicación, etc. Aunque el procesador 104 se muestra que incluye el circuito de almacenamiento de memoria 140, el circuito de búsqueda 150 y la tubería de procesamiento SIMD 152, en otras realizaciones, las operaciones de cada componente 140, 150, 152 pueden ser realizadas por un único componente de procesamiento.

Uno o más registros 130 pueden almacenar un primer vector de datos 132, un segundo vector de datos 134 y un tercer vector de datos 136. Una "secuencia de elementos de datos" puede incluir los elementos de datos almacenados en los vectores de datos 132, 134, 136. Aunque se muestra que tres vectores de datos 132, 134, 136 están incluidos en uno o más registros 130, en otras realizaciones, los uno o más registros 130 pueden incluir vectores de datos adicionales (o menos). Cada vector de datos 132, 134, 136 puede ser un "vector de datos dispersos" o un "matriz de datos dispersa". Por ejemplo, cada vector de datos 132, 134, 136 puede incluir datos válidos (por ejemplo, valores de datos de interés) y datos inválidos (por ejemplo, valores de datos "no importa", valores de datos predeterminados o valores de datos cero). De acuerdo con una implementación, los vectores de datos 132, 134, 136 pueden ser almacenados en la memoria 102 (en lugar de ser almacenados en uno o más registros 130).

Haciendo referencia a la Figura 2, se muestran con mayor detalle los vectores de datos 132, 134, 136. Cada vector de datos 132, 134, 136 incluye ocho posiciones (por ejemplo, "Posición 0" a "Posición 7"). De acuerdo con una realización, cada posición puede corresponder a una "posición de matriz". Aunque se muestra que cada vector de datos 132, 134, 136 incluye ocho posiciones, en otras realizaciones, cada vector de datos 132, 134, 136 puede incluir posiciones adicionales (o menos). Como ejemplo no limitante, cada vector de datos 132, 134, 136 puede incluir dieciséis posiciones. De acuerdo con otra realización, diferentes vectores de datos pueden incluir un número diferente de posiciones. Como ejemplo no limitante, un vector de datos puede incluir ocho posiciones y otro vector de datos puede incluir dieciséis posiciones.

De acuerdo con la Figura 2, el primer vector de datos 132 incluye tres valores de datos válidos y cinco valores de datos inválidos. Por ejemplo, "Posición 1" del primer vector de datos 132 almacena el valor de datos válidos "A", "Posición 3" del primer vector de datos 132 almacena el valor de datos válidos "B" y "Posición 6" del primer vector de datos 132 almacena el valor de datos válidos "C". Las otras posiciones del primer vector de datos 132 almacenan valores de datos inválidos. El segundo vector de datos 134 también incluye tres valores de datos válidos y cinco valores de datos inválidos. Por ejemplo, "Posición 2" del segundo vector de datos 134 almacena el valor de datos válidos "D", "Posición 3" del segundo vector de datos 134 almacena el valor de datos válidos "E", y "Posición 6" del segundo vector de datos 134 almacena el valor de datos válidos "F". Las otras posiciones del segundo vector de datos 134 almacenan valores de datos inválidos. El tercer vector de datos 136 incluye cuatro valores de datos válidos y cuatro valores de datos inválidos. Por ejemplo, "Posición 0" del tercer vector de datos 136 almacena el valor de datos válidos "G", "Posición 4" del tercer vector de datos 136 almacena el valor de datos válidos "H", "Posición 5" del tercer vector de datos 136 almacena el valor de datos válidos "I" y "Posición 7" del tercer vector de datos 136 almacena el valor de datos válidos "J". Las otras posiciones del tercer vector de datos 136 almacenan valores de datos inválidos.

- Haciendo referencia de nuevo a la Figura 1, el circuito de almacenamiento de memoria 140 incluye circuitos de análisis de vectores de datos 142, circuitos de escritura 144 y circuitos de determinación de desplazamiento 146. El circuito de análisis de vectores de datos 142 puede estar configurado para determinar si el primer vector de datos 132 incluye posiciones con datos válidos. Por ejemplo, el circuito de análisis de vector de datos 142 puede determinar que el valor de datos válidos "A" se encuentra en "Posición 1" del primer vector de datos 132 (por ejemplo, la primera posición secuencial que tiene datos válidos). El circuito de escritura 144 puede estar configurado para escribir (por ejemplo, almacenar) valores de datos válidos (en paralelo) en las direcciones de memoria contiguas del vector de datos de memoria comprimida 110. Por ejemplo, en respuesta a una determinación de que el valor de datos válidos "A" se encuentra en "Posición 1" del primer vector de datos 132, el circuito de almacenamiento de memoria 140 puede habilitar el circuito de escritura 144. El circuito de escritura 144 puede almacenar el valor de datos válidos "A" en la primera dirección de memoria 111 en respuesta a ser habilitado. Por ejemplo, el circuito de escritura 144 puede ejecutar la instrucción de dispersión 106 (por ejemplo, una instrucción de almacenamiento vectorial) para almacenar el valor de datos válidos "A" en la primera dirección de memoria 111.

- Después de que el valor de datos válidos "A" se almacene en la primera dirección de memoria 111, el circuito de análisis de vectores de datos 142 puede determinar si el primer vector de datos 132 incluye otra posición con datos válidos. Por ejemplo, el circuito de análisis de vector de datos 142 puede determinar que el valor de datos válidos "B" se encuentra en "Posición 3" del primer vector de datos 132 (por ejemplo, la siguiente posición secuencial que tiene datos válidos). En respuesta a una determinación de que el valor de datos válidos "B" se encuentra en "Posición 3" del primer vector de datos 132, el circuito de almacenamiento de memoria 140 puede habilitar el circuito de escritura 144. El circuito de escritura 144 puede almacenar el valor de datos válidos "B" en la segunda dirección de memoria 112 (por ejemplo, una dirección de memoria contigua a la primera dirección de memoria 111) en respuesta a estar habilitado. Por ejemplo, el circuito de escritura 144 puede ejecutar la instrucción de dispersión 106 para almacenar el valor de datos válidos "B" en la segunda dirección de memoria 112.

- Después de que el valor de datos válidos "B" se almacene en la segunda dirección de memoria 112, el circuito de análisis de vector de datos 142 puede determinar si el primer vector de datos 132 incluye otra posición con datos válidos. Por ejemplo, el circuito de análisis de vector de datos 142 puede determinar que el valor de datos válidos "C" se encuentra en "Posición 6" del primer vector de datos 132 (por ejemplo, la siguiente posición secuencial que tiene datos válidos). En respuesta a una determinación de que el valor de datos válidos "C" se encuentra en "Posición 6" del primer vector de datos 132, el circuito de almacenamiento de memoria 140 puede habilitar el circuito de escritura 144. El circuito de escritura 144 puede almacenar el valor de datos válidos "C" en la tercera dirección de memoria 113 (por ejemplo, una dirección de memoria contigua a la segunda dirección de memoria 112) en respuesta a estar habilitado. Por ejemplo, el circuito de escritura 144 puede ejecutar la instrucción de dispersión 106 para almacenar el valor de datos válidos "C" en la tercera dirección de memoria 113. Por lo tanto, los valores de datos inválidos del primer vector de datos 132 pueden ser omitidos y los valores de datos válidos del primer vector de datos 132 pueden ser almacenados en direcciones de memoria contiguas en la memoria 102.

- Después de que el valor de datos válidos "C" se almacene en la tercera dirección de memoria 113, el circuito de análisis de vector de datos 142 puede determinar si el primer vector de datos 132 incluye otra posición con datos válidos. En respuesta a una determinación de que el primer vector de datos 132 no incluye otra posición con datos válidos, el circuito de análisis de vectores de datos 142 puede determinar si el segundo vector de datos 134 incluye una posición con datos válidos. Por ejemplo, el circuito de análisis de vector de datos 142 puede determinar que el valor de datos válidos "D" se encuentra en "Posición 2" del segundo vector de datos 134 (por ejemplo, la primera posición secuencial con datos válidos). En respuesta a una determinación de que el valor de datos válidos "D" se encuentra en "Posición 2" del segundo vector de datos 134, el circuito de almacenamiento de memoria 140 puede habilitar el circuito de escritura 144. El circuito de escritura 144 puede almacenar el valor de datos válidos "D" en la cuarta dirección de memoria 114 (por ejemplo, una dirección de memoria contigua a la tercera dirección de memoria 113) en respuesta a estar habilitado. Por ejemplo, el circuito de escritura 144 puede ejecutar la instrucción de dispersión 106 para almacenar el valor de datos válidos "D" en la cuarta dirección de memoria 114.

- Después de que el valor de datos válidos "D" se almacene en la cuarta dirección de memoria 114, el circuito de análisis de vector de datos 142 puede determinar si el segundo vector de datos 134 incluye otra posición con datos válidos. Por ejemplo, el circuito de análisis de vector de datos 142 puede determinar que el valor de datos válidos "E" se encuentra en "Posición 3" del segundo vector de datos 134 (por ejemplo, la siguiente posición secuencial que tiene datos válidos). En respuesta a una determinación de que el valor de datos válidos "E" se encuentra en "Posición 3" del segundo vector de datos 134, el circuito de almacenamiento de memoria 140 puede habilitar el circuito de escritura 144. El circuito de escritura 144 puede almacenar el valor de datos válidos "E" en la quinta dirección de memoria 115 (por ejemplo, una dirección de memoria contigua a la cuarta dirección de memoria 114) en respuesta a estar habilitado. Por ejemplo, el circuito de escritura 144 puede ejecutar la instrucción de dispersión 106 para almacenar el valor de datos válidos "E" en la quinta dirección de memoria 115.

- Después de que el valor de datos válidos "E" se almacene en la quinta dirección de memoria 115, el circuito de análisis de vector de datos 142 puede determinar si el segundo vector de datos 134 incluye otra posición con datos válidos. Por ejemplo, el circuito de análisis de vector de datos 142 puede determinar que el valor de datos válidos "F" se encuentra en "Posición 6" del segundo vector de datos 134 (por ejemplo, la siguiente posición secuencial que tiene

datos válidos). En respuesta a una determinación de que el valor de datos válidos "F" se encuentra en "Posición 6" del segundo vector de datos 134, el circuito de almacenamiento de memoria 140 puede habilitar el circuito de escritura 144. El circuito de escritura 144 puede almacenar el valor de datos válidos "F" en la sexta dirección de memoria 116 (por ejemplo, una dirección de memoria contigua a la quinta dirección de memoria 115) en respuesta a estar habilitado.

5 Por ejemplo, el circuito de escritura 144 puede ejecutar la instrucción de dispersión 106 para almacenar el valor de datos válidos "F" en la sexta dirección de memoria 116. Por lo tanto, los valores de datos inválidos del segundo vector de datos 134 pueden ser omitidos y los valores de datos válidos del segundo vector de datos 134 pueden ser almacenados en direcciones de memoria contiguas en la memoria 102.

10 Después de que el valor de datos válidos "F" se almacene en la sexta dirección de memoria 116, el circuito de análisis de vector de datos 142 puede determinar si el segundo vector de datos 134 incluye otra posición con datos válidos. En respuesta a una determinación de que el segundo vector de datos 134 no incluye otra posición con datos válidos, el circuito de análisis de vectores de datos 142 puede determinar si el tercer vector de datos 136 incluye una posición con datos válidos. Por ejemplo, el circuito de análisis de vectores de datos 142 puede determinar que el valor de datos válidos "G" se encuentra en "Posición 1" del tercer vector de datos 136 (por ejemplo, la primera posición secuencial con datos válidos). En respuesta a una determinación de que el valor de datos válidos "G" se encuentra en "Posición 1" del tercer vector de datos 136, el circuito de almacenamiento de memoria 140 puede habilitar el circuito de escritura 144. El circuito de escritura 144 puede almacenar el valor de datos válidos "G" en la séptima dirección de memoria 117 (por ejemplo, una dirección de memoria contigua a la sexta dirección de memoria 116) en respuesta a estar habilitado. Por ejemplo, el circuito de escritura 144 puede ejecutar la instrucción de dispersión 106 para almacenar el valor de datos válidos "G" en la séptima dirección de memoria 117.

15 Despues de que el valor de datos válidos "G" se almacene en la séptima dirección de memoria 117, el circuito de análisis de vector de datos 142 puede determinar si el tercer vector de datos 136 incluye otra posición con datos válidos. Por ejemplo, el circuito de análisis de vectores de datos 142 puede determinar que el valor de datos válidos "H" se encuentra en "Posición 4" del tercer vector de datos 136 (por ejemplo, la siguiente posición secuencial que tiene datos válidos). En respuesta a una determinación de que el valor de datos válidos "H" se encuentra en "Posición 4" del tercer vector de datos 136, el circuito de almacenamiento de memoria 140 puede habilitar el circuito de escritura 144. El circuito de escritura 144 puede almacenar el valor de datos válidos "H" en la octava dirección de memoria 118 (por ejemplo, una dirección de memoria contigua a la séptima dirección de memoria 117) en respuesta a estar habilitado. Por ejemplo, el circuito de escritura 144 puede ejecutar la instrucción de dispersión 106 para almacenar el valor de datos válidos "H" en la octava dirección de memoria 118.

20 Despues de que el valor de datos válidos "H" se almacene en la octava dirección de memoria 118, el circuito de análisis de vector de datos 142 puede determinar si el tercer vector de datos 136 incluye otra posición con datos válidos. Por ejemplo, el circuito de análisis de vectores de datos 142 puede determinar que el valor de datos válidos "I" se encuentra en "Posición 5" del tercer vector de datos 136 (por ejemplo, la siguiente posición secuencial que tiene datos válidos). En respuesta a una determinación de que el valor de datos válidos "I" se encuentra en "Posición 5" del tercer vector de datos 136, el circuito de almacenamiento de memoria 140 puede habilitar el circuito de escritura 144. El circuito de escritura 144 puede almacenar el valor de datos válidos "I" en la novena dirección de memoria 119 (por ejemplo, una dirección de memoria contigua a la octava dirección de memoria 118) en respuesta a estar habilitado. Por ejemplo, el circuito de escritura 144 puede ejecutar la instrucción de dispersión 106 para almacenar el valor de datos válidos "I" en la novena dirección de memoria 119.

25 Despues de que el valor de datos válidos "J" se almacene en la novena dirección de memoria 119, el circuito de análisis de vector de datos 142 puede determinar si el tercer vector de datos 136 incluye otra posición con datos válidos. Por ejemplo, el circuito de análisis de vectores de datos 142 puede determinar que el valor de datos válidos "J" se encuentra en "Posición 7" del tercer vector de datos 136 (por ejemplo, la siguiente posición secuencial que tiene datos válidos). En respuesta a una determinación de que el valor de datos válidos "J" se encuentra en "Posición 7" del tercer vector de datos 136, el circuito de almacenamiento de memoria 140 puede habilitar el circuito de escritura 144. El circuito de escritura 144 puede almacenar el valor de datos válidos "J" en la décima dirección de memoria 120 (por ejemplo, una dirección de memoria contigua a la novena dirección de memoria 119) en respuesta a estar habilitado. Por ejemplo, el circuito de escritura 144 puede ejecutar la instrucción de dispersión 106 para almacenar el valor de datos válidos "J" en la décima dirección de memoria 120. Por lo tanto, los valores de datos inválidos del tercer vector de datos 136 pueden ser omitidos y los valores de datos válidos del tercer vector de datos 136 pueden ser almacenados en direcciones de memoria contiguas en la memoria 102.

30 Operaciones similares pueden realizarse para almacenar valores de datos adicionales válidos en el vector de datos de memoria comprimida 110 de la memoria 102. Haciendo referencia a la Figura 3, se muestra el vector de datos de memoria comprimida 110 después de completar las operaciones de almacenamiento descritas anteriormente. Cada valor de dato válido de los vectores de datos 132, 134, 136 puede ser almacenado en direcciones de memoria contiguas del vector de datos de memoria comprimida 110. Por lo tanto, los datos inválidos pueden separarse de los vectores de datos dispersos 132, 134, 136 para generar el vector de datos de memoria comprimida 110 que contiene datos válidos en cada dirección de memoria. Como se describe a continuación, el procesador 150 puede obtener el vector de datos de memoria comprimida 110 de la memoria 102 para procesar datos válidos en lugar de procesar datos válidos e inválidos, lo cual puede resultar en un uso ineficiente del procesador 104.

Haciendo referencia a la Figura 1, el circuito de determinación de desplazamiento 146 puede estar configurado para determinar (por ejemplo, contar) un desplazamiento para cada vector de datos 132, 134, 136 con respecto al vector de datos de memoria comprimida 110. Por ejemplo, el circuito de determinación de desplazamiento 146 puede determinar un recuento (por ejemplo, un recuento válido de prefijo paralelo) de habilitaciones de escritura para cada

- 5 vector de datos 132, 134, 136. El desplazamiento para cada vector de datos 132, 134, 136 puede basarse en el recuento válido de prefijos paralelos. El "desplazamiento" para un vector de datos particular es la primera dirección de memoria secuencial del vector de datos de memoria comprimida 110 donde se almacenan los datos válidos asociados con el vector de datos particular. El circuito de determinación de desplazamiento 146 puede generar múltiples desplazamientos 160 correspondientes a los vectores de datos 132-136, incluyendo un primer desplazamiento 162 del primer vector de datos 132, un segundo desplazamiento 164 del segundo vector de datos 134 y un tercer desplazamiento 166 del tercer vector de datos 136. Por ejemplo, como se describe más adelante con referencia a la Figura 4, el primer desplazamiento 162 puede tener un valor de "1" para indicar que los datos válidos del primer vector de datos 132 comienzan en la primera dirección de memoria 111 del vector de datos de memoria comprimida 110, el segundo desplazamiento 164 puede tener un valor de "4" para indicar que los datos válidos del segundo vector de datos 134 comienzan en la cuarta dirección de memoria 114, y el tercer desplazamiento 166 puede tener un valor de "7" para indicar que los datos válidos del tercer vector de datos 136 comienzan en la séptima dirección de memoria 117 del vector de datos de memoria comprimida 110. De acuerdo con una realización, el procesador 104 puede ejecutar la instrucción de conteo válido de prefijo paralelo 108 para determinar el desplazamiento.

- 10

- 15

- 20

- 25

- 30

- 35

- 40

- 45

- 50

- 55

- 60

- 65

- Para ilustrar, se muestra en la Figura 4 un gráfico 400 para identificar el desplazamiento de cada vector de datos 132, 134, 136. De acuerdo con el gráfico 400, la dirección de memoria "0" puede ser utilizada como la dirección base para el primer vector de datos 132. Un conteo de prefijo paralelo del primer vector de datos 132 puede aumentar (de cero a uno) en respuesta a una habilitación (por ejemplo, una habilitación de escritura) asociada con el almacenamiento del valor de datos válidos "A" en el vector de datos de memoria comprimida 110. Cada vez que aumenta el conteo de prefijo paralelo, también aumenta la dirección de memoria. Por lo tanto, en la columna "Posición 1" del gráfico 400, la dirección de memoria aumenta desde la dirección de memoria "0" hasta la dirección de memoria "1" (por ejemplo, la primera dirección de memoria 111). Por lo tanto, el desplazamiento 162 para el primer vector de datos 132 con respecto al vector de datos de memoria comprimida 110 es la primera dirección de memoria 111 y puede almacenarse como un valor de desplazamiento de "1" para indicar la primera dirección de memoria 111. En otras realizaciones, el desplazamiento 162 puede almacenarse con otro valor de desplazamiento que indica la primera dirección de memoria 111, como un valor de desplazamiento de "0" en una implementación de indexación basada en cero.

El conteo de prefijo paralelo puede aumentar (de uno a dos) en respuesta a una habilitación asociada con el almacenamiento del valor de datos válidos "B" en la segunda dirección de memoria 112 del vector de datos de memoria comprimida 110. El conteo de prefijo paralelo también puede aumentar (de dos a tres) en respuesta a una habilitación asociada con el almacenamiento del valor de datos válidos "C" en la tercera dirección de memoria 113 del vector de datos de memoria comprimida 110. Como se describe anteriormente, la dirección del último valor de datos válidos almacenado puede ser utilizada como base para un nuevo vector de datos. Debido a que la dirección de memoria "3" (por ejemplo, la tercera dirección de memoria 113) es la dirección del último valor de datos (por ejemplo, el valor de datos válidos "C") almacenado, la tercera dirección de memoria 113 se puede utilizar como base para el segundo vector de datos 134. Cuando el conteo de prefijo paralelo del segundo vector de datos 134 aumenta (de cero a uno), la dirección de memoria correspondiente puede ser el desplazamiento 164 para el segundo vector de datos 134. Por lo tanto, el desplazamiento 164 para el segundo vector de datos 134 con respecto al vector de datos de memoria comprimida 110 es la cuarta dirección de memoria 114 y puede representarse como un valor de desplazamiento de "4" (o "3" en una implementación de indexación basada en cero). De manera similar, de acuerdo con el gráfico 400, el desplazamiento 166 para el tercer vector de datos 136 con respecto al vector de datos de memoria comprimida 110 es la séptima dirección de memoria 117 y puede representarse como un valor de desplazamiento de "7" (o "6" en una implementación de indexación basada en cero).

Haciendo referencia de nuevo a la Figura 1, los desplazamientos (determinados por el circuito de determinación de desplazamiento 146) pueden ser utilizados para mapear los datos en la memoria 102 a los vectores de datos 132, 134, 136. Por ejemplo, el procesador 104 puede determinar que las direcciones de memoria primera, segunda y tercera 111, 112, 113 incluyen datos asociados con el primer vector de datos 132 si el desplazamiento 162 del primer vector de datos 132 es la primera dirección de memoria 111 y el desplazamiento 164 del segundo vector de datos 134 es la cuarta dirección de memoria 114. De manera similar, el procesador 104 puede determinar que las direcciones de memoria cuarta, quinta y sexta 114, 115, 116 incluyen datos asociados con el segundo vector de datos 134 si el desplazamiento 164 del segundo vector de datos 134 es la cuarta dirección de memoria 114 y el desplazamiento 166 del tercer vector de datos 136 es la séptima dirección de memoria 117.

Después de que los valores de datos se almacenen en el vector de datos de memoria comprimida 110, el circuito de búsqueda 150 puede configurarse para recuperar los datos almacenados en el vector de datos de memoria comprimida 110. El circuito de búsqueda 150 puede proporcionar el vector de datos de memoria comprimida 110 a la tubería de procesamiento SIMD 152. Debido a que cada dirección de memoria del vector de datos de memoria comprimida 110 incluye valores de datos válidos, los componentes de procesamiento y hardware en la tubería de procesamiento SIMD 152 pueden ser utilizados de manera eficiente. Por ejemplo, los componentes de procesamiento

en la tubería de procesamiento SIMD 152 pueden ser utilizados en valores de datos válidos en lugar de ser utilizados para valores de datos inválidos.

Las técnicas descritas con respecto a las Figuras 1-4 pueden mejorar la eficiencia de procesamiento al reducir la cantidad de valores de datos inválidos que son procesados por la tubería de procesamiento SIMD 152. Al almacenar valores de datos válidos en direcciones contiguas en la memoria 102, el circuito de búsqueda 150 puede proporcionar valores de datos válidos (en contraposición a valores de datos válidos e inválidos) a la tubería de procesamiento SIMD 152. Además, se puede lograr un esquema de direccionamiento relativamente simple mediante el seguimiento del recuento válido de prefijo paralelo para cada vector de datos 132, 134, 136 durante el proceso de almacenamiento. Por ejemplo, el procesador 104 puede identificar qué valores de datos y/o direcciones de memoria corresponden a cada vector de datos 132, 134, 136 en función del recuento válido de prefijo paralelo.

Como se describe con referencia a las Figuras 1-4, la instrucción de conteo válido de prefijo paralelo 108 se puede utilizar durante la compresión de datos dispersos de los múltiples vectores de datos 132-136 a una disposición de datos densos en el vector de datos de memoria comprimida 110. Alternativamente, o, además, se puede utilizar la instrucción de conteo válido de prefijo paralelo 108 durante la descompresión de los datos del vector de datos de memoria comprimida 110 a una disposición de datos dispersos en los vectores de datos 132-136. Por ejemplo, después de comprimir los datos en el vector de datos de memoria comprimida 110, los datos en el vector de datos de memoria comprimida 110 pueden ser procesados por la tubería de procesamiento SIMD 152 para generar datos modificados en el vector de datos de memoria comprimida 110. Los datos modificados pueden ser escritos de nuevo en las posiciones correspondientes de los vectores de datos 132-136 para sobrescribir los datos válidos originales con los datos modificados. En una operación de descompresión, se puede calcular un desplazamiento o dirección contigua para cada posición válida en los vectores de datos 132-136 utilizando la instrucción de conteo válido de prefijo paralelo 108 con acumulación desde el último conteo del vector anterior, como se describe en la Figura 4. Se puede realizar una carga/recolección para cargar los datos de cada dirección o desplazamiento en el vector de datos de memoria comprimida 110 en las posiciones de datos válidos de los vectores de datos 132-136, en base a los resultados de la instrucción de conteo válido de prefijo paralelo 108. Por lo tanto, la instrucción de conteo válido de prefijo paralelo 108 se puede utilizar durante operaciones de compresión de datos y también durante operaciones de descompresión de datos.

Haciendo referencia a la Figura 5, se muestra un diagrama de flujo de un procedimiento 500 para almacenar datos en direcciones de memoria contiguas. El procedimiento 500 se puede realizar utilizando el sistema 100 de la Figura 1.

El procedimiento 500 incluye determinar, mediante la ejecución de una instrucción de conteo válido de prefijo paralelo, un primer desplazamiento asociado con una primera posición válida en una secuencia de elementos de datos que incluye datos válidos e inválidos, en 502. Por ejemplo, haciendo referencia a la Figura 1, el procesador SIMD 104 puede ejecutar la instrucción de conteo válido de prefijo paralelo 108 para determinar el primer desplazamiento 162 del primer vector de datos 132.

El procedimiento 500 también incluye determinar, mediante la ejecución de la instrucción de conteo válido de prefijo paralelo, un segundo desplazamiento asociado con una segunda posición válida en la secuencia de elementos de datos, en 504. El segundo desplazamiento puede basarse en el primer desplazamiento y en un número de posiciones en la secuencia de elementos de datos que están asociados con datos válidos. Por ejemplo, haciendo referencia a la Figura 1, el procesador SIMD 104 puede ejecutar la instrucción de conteo válido de prefijo paralelo 108 para determinar el segundo desplazamiento 164 del segundo vector de datos 134. De acuerdo con una realización, el segundo desplazamiento puede calcularse sumando el número de posiciones en el primer vector de datos 132 que están asociadas con datos válidos al primer desplazamiento 162.

El procedimiento 500 también incluye almacenar los primeros datos válidos del primer vector de datos en una primera dirección de memoria de una memoria, en 506. La primera dirección de memoria puede estar basada en el primer desplazamiento. Por ejemplo, haciendo referencia a la Figura 1, en respuesta a una determinación de que el valor de datos válidos "A" se encuentra en "Posición 1" del primer vector de datos 132, el circuito de almacenamiento de memoria 140 puede habilitar el circuito de escritura 144. El circuito de escritura 144 puede almacenar el valor de datos válidos "A" en la primera dirección de memoria 111 en respuesta a ser habilitado. Por ejemplo, el circuito de escritura 144 puede ejecutar la instrucción de dispersión 106 para almacenar el valor de datos válidos "A" en la primera dirección de memoria 111.

El procedimiento 500 también incluye almacenar segundos datos válidos del segundo vector de datos en una dirección de memoria particular de la memoria, en 508. La dirección de memoria particular puede estar basada en el segundo desplazamiento. Por ejemplo, haciendo referencia a la Figura 1, el circuito de almacenamiento de memoria 140 puede habilitar el circuito de escritura 144. El circuito de escritura 144 puede almacenar el valor de datos válidos "D" en la cuarta dirección de memoria 114 (por ejemplo, la "segunda dirección de memoria" de acuerdo con el procedimiento 500) en respuesta a estar habilitado. Por ejemplo, el circuito de escritura 144 puede ejecutar la instrucción de dispersión 106 para almacenar el valor de datos válidos "D" en la cuarta dirección de memoria 114.

- De acuerdo con una realización, el procedimiento 500 puede incluir almacenar datos adicionales válidos del primer vector de datos en direcciones de memoria secuenciales adicionales que son contiguas a la primera dirección de memoria de la memoria. La dirección de memoria específica (donde se almacena el segundo dato válido) puede ser contigua a la última dirección de memoria de la dirección de memoria secuencial adicional. De acuerdo con una 5 realización del procedimiento 500, los primeros datos válidos y los segundos datos válidos pueden ser almacenados en paralelo. Por ejemplo, almacenar los segundos datos válidos en paralelo con los primeros datos válidos incluye almacenar los primeros datos válidos durante un primer período de tiempo (por ejemplo, durante un solo ciclo de reloj del procesador SIMD 104) y almacenar simultáneamente los segundos datos válidos durante el primer período de 10 tiempo.

- De acuerdo con una realización del procedimiento 500, la primera dirección de memoria y la dirección de memoria particular pueden ser direcciones de memoria de un vector de datos de memoria comprimido (por ejemplo, el vector 15 de datos de memoria comprimido 110). El procedimiento 500 también puede incluir la obtención de datos almacenados en el vector de datos de memoria comprimida y procesar los datos almacenados en el vector de datos de memoria comprimida en respuesta a la obtención de los datos almacenados en el vector de datos de memoria comprimida.

- De acuerdo con una realización del procedimiento 500, después de procesar los datos almacenados en el vector de 20 datos de memoria comprimida, se puede realizar una operación de "descompresión". La instrucción de conteo válido de prefijo paralelo se puede ejecutar para determinar desplazamientos que mapean las posiciones de los datos procesados en memoria contigua a las posiciones de los datos válidos en una secuencia dispersa de datos. Los datos procesados pueden ser cargados desde la memoria contigua a las posiciones de los datos válidos en la secuencia 25 dispersa de datos. Por lo tanto, la disposición comprimida de los datos procesados en la memoria contigua puede descomprimirse a una disposición dispersa de los datos procesados basada en las posiciones de los datos válidos en los vectores de datos 132-136.

- El procedimiento 500 de la Figura 5 puede mejorar la eficiencia de procesamiento al reducir la cantidad de valores de 30 datos inválidos que son procesados por la tubería de procesamiento SIMD 152. Al almacenar valores de datos válidos en direcciones contiguas en la memoria 102, el circuito de búsqueda 150 puede proporcionar valores de datos válidos (en contraposición a valores de datos válidos e inválidos) a la tubería de procesamiento SIMD 152. Además, se puede lograr un esquema de direccionamiento relativamente simple mediante el seguimiento del recuento válido de prefijo paralelo para cada vector de datos 132, 134, 136 durante el proceso de almacenamiento. Por ejemplo, el procesador 104 puede identificar qué valores de datos y/o direcciones de memoria corresponden a cada vector de datos 132, 134, 136 en función del recuento válido de prefijo paralelo.

- Haciendo referencia a la Figura 6, se muestra un diagrama de bloques de un dispositivo electrónico 600. El dispositivo 35 electrónico 600 puede corresponder a un dispositivo móvil (por ejemplo, un teléfono celular), como ejemplo ilustrativo. En otras realizaciones, el dispositivo electrónico 600 puede corresponder a un ordenador (por ejemplo, un servidor, un ordenador portátil, una tableta o un ordenador de escritorio), un dispositivo electrónico portátil (por ejemplo, una cámara personal, un visor montado en la cabeza o un reloj), un sistema o consola de control de vehículo, un 40 electrodoméstico, un decodificador, una unidad de entretenimiento, un dispositivo de navegación, un asistente digital personal (PDA), un televisor, un monitor, un sintonizador, una radio (por ejemplo, una radio satelital), un reproductor de música (por ejemplo, un reproductor de música digital o un reproductor de música portátil), un reproductor de video (por ejemplo, un reproductor de video digital, como un reproductor de discos digitales (DVD) o un reproductor de video digital portátil), un robot, un dispositivo de atención médica, otro dispositivo electrónico o una combinación de los 45 mismos.

- El dispositivo electrónico 600 incluye el procesador 104, como un procesador de señal digital (DSP), una unidad central de procesamiento (CPU), una unidad de procesamiento gráfico (GPU), otro dispositivo de procesamiento, o una combinación de los mismos. El procesador 104 incluye uno o más registros 130, circuitos de almacenamiento de memoria 140, circuitos de búsqueda 150 y la tubería de procesamiento SIMD 152. Uno o más registros 110 almacenan 50 el primer vector de datos 132, el segundo vector de datos 134 y el tercer vector de datos 136. El circuito de almacenamiento de memoria 140 incluye el circuito de análisis de vectores de datos 142, el circuito de escritura 144 y el circuito de determinación de desplazamiento 146. El procesador 104 puede operar de manera sustancialmente similar a como se describe con respecto a la Figura 1.

- El dispositivo electrónico 600 puede incluir además la memoria 102. La memoria 102 puede estar acoplada o integrada 55 dentro del procesador 104. La memoria 102 puede incluir memoria de acceso aleatorio (RAM), memoria de acceso aleatorio magnetoresistiva (MRAM), memoria flash, memoria de solo lectura (ROM), memoria de solo lectura programable (PROM), memoria de solo lectura programable y borrable (EPROM), memoria de solo lectura programable y borrable eléctricamente (EEPROM), uno o más registros, un disco duro, un disco extraíble, un disco compacto de solo lectura (CD-ROM), otro dispositivo de almacenamiento, o una combinación de los mismos. La memoria 102 puede almacenar la instrucción de dispersión 106, la instrucción de conteo válido de prefijo paralelo 108 y una o más instrucciones adicionales 668 ejecutables por el procesador 610. Por ejemplo, el procesador 104 puede ejecutar la instrucción de dispersión 106 para almacenar valores de datos válidos (de los vectores de datos 132, 134, 136) en el vector de datos de memoria comprimida 110. El procesador 104 también puede ejecutar la instrucción de conteo válido de prefijo paralelo 108 para determinar el desplazamiento de cada vector de datos 132, 134, 136 con

respecto al vector de datos de memoria comprimida 110. El procesador 104 también puede ejecutar una o más instrucciones adicionales 668 para llevar a cabo el procedimiento 500 de la Figura 5.

5 La Figura 6 también muestra un controlador de pantalla 626 que está acoplado al procesador 104 y a una pantalla 628. Un codificador/descodificador (CODEC) 634 también puede estar acoplado al procesador 104. Un altavoz 636 y un micrófono 638 pueden acoplarse al CODEC 634. La Figura 6 también indica que una interfaz inalámbrica 640, como un controlador inalámbrico y/o un transceptor, puede estar acoplada al procesador 104 y a una antena 642.

10 En un ejemplo particular, el procesador 104, el controlador de pantalla 626, la memoria 102, el CODEC 634 y la interfaz inalámbrica 640 están incluidos en un dispositivo de sistema en paquete o sistema en chip 622. Además, un dispositivo de entrada 630 y una fuente de alimentación 644 pueden estar acoplados al dispositivo de sistema en chip 622. Además, en un ejemplo particular, como se ilustra en la Figura 6, la pantalla 628, el dispositivo de entrada 630, el altavoz 636, el micrófono 638, la antena 642 y la fuente de alimentación 644 están externos al dispositivo de sistema en chip 622. Sin embargo, cada uno de los dispositivos de visualización 628, el dispositivo de entrada 630, el altavoz 636, el micrófono 638, la antena 642 y la fuente de alimentación 644 pueden estar acoplados a un componente del dispositivo de sistema en chip 622, como a una interfaz o a un controlador.

15 En relación con los ejemplos divulgados, un medio legible por ordenador (por ejemplo, la memoria 102) almacena las instrucciones que son ejecutables por un procesador (por ejemplo, el procesador 104) para realizar operaciones. Las operaciones incluyen almacenar los primeros datos válidos en una primera dirección de memoria de una memoria. El primer dato válido puede estar ubicado en una primera posición particular de un primer vector de datos que incluye datos válidos e inválidos. La primera posición particular puede estar asociada con datos válidos. Las operaciones también incluyen determinar si el primer vector de datos incluye otra posición asociada a datos válidos. Si el primer vector de datos incluye otra posición asociada a datos válidos, las operaciones incluyen almacenar los datos válidos ubicados en la otra posición en una segunda dirección de memoria que es contigua a la primera dirección de memoria. Las operaciones también incluyen almacenar segundos datos válidos en la segunda dirección de memoria si el primer vector de datos no incluye otra posición asociada con datos válidos. El segundo dato puede estar ubicado en una segunda posición particular de un segundo vector de datos que incluye datos válidos e inválidos. La segunda posición particular puede estar asociada con datos válidos.

20 30 En conjunto con las técnicas descritas, un aparato incluye medios para determinar un primer desplazamiento asociado con una primera posición válida en una secuencia de elementos de datos mediante la ejecución de una instrucción de conteo válido de prefijo paralelo. La secuencia de elementos de datos puede incluir datos válidos y datos inválidos. Por ejemplo, los medios para determinar el primer desplazamiento pueden incluir el circuito de almacenamiento de memoria 140 de las Figuras 1 y 6, el circuito de análisis de vectores de datos 142 de las Figuras 1 y 6, el circuito de determinación de desplazamiento 146 de las Figuras 1 y 6, el procesador 104 de las Figuras 1 y 6, uno o más dispositivos, circuitos, módulos u cualquier combinación de los mismos.

25 35 40 45 El aparato también puede incluir medios para determinar un segundo desplazamiento asociado con una segunda posición válida en la secuencia de elementos de datos mediante la ejecución de la instrucción de conteo válido de prefijo paralelo. El segundo desplazamiento puede basarse en el primer desplazamiento y en un número de posiciones en la secuencia de elementos de datos que están asociados con datos válidos. Por ejemplo, los medios para determinar el segundo desplazamiento pueden incluir el circuito de almacenamiento de memoria 140 de las Figuras 1 y 6, el circuito de análisis de vectores de datos 142 de las Figuras 1 y 6, el circuito de determinación de desplazamiento 146 de las Figuras 1 y 6, el procesador 104 de las Figuras 1 y 6, uno o más dispositivos, circuitos, módulos u cualquier combinación de los mismos.

50 Los dispositivos y funcionalidades divulgados anteriormente pueden ser diseñados y representados utilizando archivos informáticos (por ejemplo, RTL, GDSII, GERBER, etc.). Los archivos informáticos pueden ser almacenados en medios legibles por ordenador. Algunos o todos estos archivos pueden ser proporcionados a los manipuladores de fabricación que fabrican dispositivos basados en dichos archivos. Los productos resultantes incluyen obleas que luego se cortan en matrices y se empaquetan en circuitos integrados (o "chips"). Las fichas son luego utilizadas en dispositivos electrónicos, como el dispositivo electrónico 600 de la Figura 6.

55 60 65 Los pasos de un procedimiento o algoritmo descritos en relación con las implementaciones divulgadas en la presente memoria pueden ser incorporados directamente en hardware, en un módulo de software ejecutado por un procesador, o en una combinación de ambos. Un módulo de software puede residir en memoria de acceso aleatorio (RAM), memoria flash, memoria de solo lectura (ROM), memoria de solo lectura programable (PROM), memoria de solo lectura programable y borrible (EPROM), memoria de solo lectura programable y eléctricamente borrible (EEPROM), registros, disco duro, un disco extraíble, un disco compacto de solo lectura (CD-ROM), o cualquier otra forma de medio de almacenamiento conocido en la técnica. Un medio de almacenamiento no transitorio ejemplar (por ejemplo, tangible) está acoplado al procesador de manera que el procesador puede leer información desde y escribir información en el medio de almacenamiento. En su lugar, el medio de almacenamiento puede ser parte integral del procesador. El procesador y el medio de almacenamiento pueden residir en un circuito integrado de aplicación específica (ASIC). El ASIC puede residir en un dispositivo informático o en un terminal de usuario. En su lugar, el

procesador y el medio de almacenamiento pueden residir como componentes discretos en un dispositivo informático o terminal de usuario.

## REIVINDICACIONES

1. Un procedimiento para almacenar datos válidos en una pluralidad de direcciones de memoria contiguas (110) en un procesador de una instrucción, múltiples datos (SIMD) (104), el procesador accede a una o más ubicaciones (130) para almacenar una pluralidad de vectores de datos dispersos (132, 134, 136), incluyendo cada vector de datos dispersos, datos válidos e inválidos, comprendiendo el procedimiento:

- identificar un primer valor de datos válidos en una primera posición válida en una secuencia de elementos de datos de un primer vector de datos dispersos (132) de la pluralidad de vectores de datos dispersos y habilitar circuitos de escritura para almacenar el primer valor de datos válidos del primer vector de datos dispersos en una primera dirección de memoria (111) de la pluralidad de direcciones de memoria contiguas (110);

- determinar un primer desplazamiento (160) asociado a la primera dirección de memoria (111) de la pluralidad de direcciones de memoria contiguas;

- identificar un segundo valor de datos válidos en una segunda posición válida en una secuencia de elementos de datos de un segundo vector de datos dispersos (134) y habilitar circuitos de escritura para almacenar el segundo valor de datos válidos en una segunda dirección de memoria (114) de la pluralidad de direcciones de memoria contiguas;

- determinar un segundo desplazamiento asociado con la segunda dirección de memoria (114) de la pluralidad de direcciones de memoria contiguas, el segundo desplazamiento se basa en el primer desplazamiento y en el número de posiciones en la secuencia de elementos de datos del primer vector de datos dispersos (132) que están asociados con datos válidos,

- en el que la primera dirección de memoria (111) de la pluralidad de direcciones de memoria contiguas se basa en el primer desplazamiento y la segunda dirección de memoria (114) de la pluralidad de direcciones de memoria contiguas se basa en el segundo desplazamiento.

2. El procedimiento de la reivindicación 1, en el que el primer desplazamiento se determina simultáneamente con el segundo desplazamiento.

3. El procedimiento de la reivindicación 1, que además comprende agregar el número de posiciones en el primer vector de datos dispersos (132) que están asociadas con datos válidos al primer desplazamiento (162) para calcular el segundo desplazamiento.

4. El procedimiento de la reivindicación 1, que además comprende almacenar datos adicionales válidos del primer vector de datos dispersos (132) en direcciones de memoria secuenciales adicionales (112, 113) que son contiguas a la primera dirección de memoria.

5. El procedimiento de la reivindicación 4, en el que la segunda dirección de memoria es contigua a una última dirección de memoria de las direcciones de memoria secuenciales adicionales.

6. El procedimiento de la reivindicación 1, en el que los primeros datos válidos y los segundos datos válidos se almacenan simultáneamente.

7. El procedimiento de la reivindicación 1, en el que la pluralidad de direcciones de memoria contiguas forma un vector de datos de memoria comprimida (110).

8. El procedimiento de la reivindicación 1, que además comprende recuperar datos almacenados en el vector de datos de memoria comprimida (110).

9. El procedimiento de la reivindicación 8, que además comprende procesar los datos almacenados en el vector de datos de memoria comprimida (110) en respuesta a la obtención de los datos almacenados en el vector de datos de memoria comprimida.

10. El procedimiento de la reivindicación 9, que además comprende, después de procesar los datos almacenados en el vector de datos de memoria comprimida (110), realizar una operación de descompresión, en el que la operación de descompresión comprende:

- determinar desplazamientos que mapeen las posiciones de los datos procesados en el vector de datos de memoria comprimida a las posiciones de los datos válidos en una secuencia dispersa de datos; y

- cargar los datos procesados desde el vector de datos de memoria comprimida (110) a las posiciones de datos válidos en la secuencia dispersa de datos.

11. Un aparato para almacenar datos válidos en una pluralidad de direcciones de memoria contiguas (110), comprendiendo el aparato una memoria (102) y un procesador de una instrucción, múltiples datos, SIMD, (104), configurándose el procesador para acceder a una o más ubicaciones (130) para almacenar una pluralidad de

vectores de datos dispersos (132, 134, 136), incluyendo cada vector de datos dispersos, datos válidos e inválidos, configurándose el procesador además para:

- 5        identificar un primer valor de datos válidos en una primera posición válida en una secuencia de elementos de datos de un primer vector de datos dispersos (132) de la pluralidad de vectores de datos dispersos y habilitar circuitos de escritura para almacenar el primer valor de datos válidos del primer vector de datos dispersos en una primera dirección de memoria (111) de la pluralidad de direcciones de memoria contiguas (110);

- 10      determinar un primer desplazamiento (160) asociado a la primera dirección de memoria (111) de la pluralidad de direcciones de memoria contiguas;

- 15      identificar un segundo valor de datos válidos en una segunda posición válida en una secuencia de elementos de datos de un segundo vector de datos dispersos (134) y habilitar circuitos de escritura para almacenar el segundo valor de datos válidos en una segunda dirección de memoria de la pluralidad de direcciones de memoria contiguas; y

- 20      determinar un segundo desplazamiento asociado con la segunda dirección de memoria (114) de la pluralidad de direcciones de memoria contiguas, el segundo desplazamiento se basa en el primer desplazamiento y en el número de posiciones en la secuencia de elementos de datos del primer vector de datos dispersos (132) que están asociados con datos válidos, en el que la primera dirección de memoria (111) de la pluralidad de direcciones de memoria contiguas se basa en el primer desplazamiento y la segunda dirección de memoria (114) de la pluralidad de direcciones de memoria contiguas se basa en el segundo desplazamiento.

12. El aparato de la reivindicación 11, en el que el primer desplazamiento se determina simultáneamente con el segundo desplazamiento.

- 25      13. El aparato de la reivindicación 11, en el que el procesador está configurado además para agregar el número de posiciones en el primer vector de datos dispersos (132) que están asociadas con datos válidos al primer desplazamiento (162) para calcular el segundo desplazamiento.

- 30      14. El aparato de la reivindicación 11, en el que el procesador está configurado además para almacenar datos válidos adicionales del primer vector de datos dispersos (132) en direcciones de memoria secuenciales adicionales (112, 113) que son contiguas a la primera dirección de memoria de la memoria.

- 35      15. El aparato de la reivindicación 14, en el que la segunda dirección de memoria es contigua a una última dirección de memoria de las direcciones de memoria secuenciales adicionales.

- 40      16. El aparato de la reivindicación 11, en el que los primeros datos válidos y los segundos datos válidos se almacenan simultáneamente.

- 45      17. El aparato de la reivindicación 11, en el que la pluralidad de direcciones de memoria contiguas forma un vector de datos de memoria comprimida (110).

18. El aparato de la reivindicación 11, en el que el procesador está configurado además para recuperar datos almacenados en el vector de datos de memoria comprimida (110).

19. El aparato de la reivindicación 18, en el que el procesador está configurado para procesar los datos almacenados en el vector de datos de memoria comprimida (110) en respuesta a recuperar los datos almacenados en el vector de datos de memoria comprimida.

## FIGURA 1

|   | Posición 7 | Posición 6 | Posición 5 | Posición 4 | Posición 3 | Posición 2 | Posición 1 | Posición 0 |

|---|------------|------------|------------|------------|------------|------------|------------|------------|

| - | -          | C          | -          | -          | B          | -          | A          | -          |

| - | -          | F          | -          | -          | E          | D          | -          | -          |

| - | -          | I          | H          | -          | -          | -          | G          | -          |

| J | -          | -          | -          | -          | -          | -          | -          | -          |

132

134

136

FIGURA 2

FIGURA 3

|                      |    | Posición 7 | Posición 6 | Posición 5 | Posición 4 | Posición 3 | Posición 2 | Posición 1 | Posición 0 |

|----------------------|----|------------|------------|------------|------------|------------|------------|------------|------------|

| Datos                | -  | C          | -          | -          | B          | -          | A          | -          | -          |

| Habilitar            | 0  | 1          | 0          | 0          | 1          | 0          | 1          | 1          | 0          |

| Prefijo Paralelo     | 3  | 3          | 2          | 2          | 2          | 1          | 1          | 1          | 0          |

| Dirección de Memoria | 3  | 3          | 2          | 2          | 2          | 1          | 1          | 1          | 0          |

|                      |    |            |            |            |            |            |            |            |            |

| Datos                | -  | F          | -          | -          | E          | D          | -          | -          | -          |

| Habilitar            | 0  | 1          | 0          | 0          | 1          | 1          | 0          | 0          | 0          |

| Prefijo Paralelo     | 3  | 3          | 2          | 2          | 2          | 1          | 0          | 0          | 0          |

| Dirección de Memoria | 6  | 6          | 5          | 5          | 5          | 4          | 3          | 3          | 3          |

|                      |    |            |            |            |            |            |            |            |            |

| Datos                | J  | -          | I          | H          | -          | -          | -          | G          | -          |

| Habilitar            | 1  | 0          | 1          | 1          | 0          | 0          | 0          | 1          | 1          |

| Prefijo Paralelo     | 4  | 3          | 3          | 2          | 1          | 1          | 1          | 1          | 1          |

| Dirección de Memoria | 10 | 9          | 9          | 8          | 7          | 7          | 7          | 7          | 7          |

400

132

134

136

FIGURA 4

FIGURA 5

FIGURA 6