(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2017-138979

(P2017-138979A)

(43) 公開日 平成29年8月10日(2017.8.10)

(51) Int.Cl.

G06F 12/00 (2006.01)

G11C 11/405 (2006.01)

G11C 14/00 (2006.01)

F 1

G06F 12/00

G11C 11/34

G11C 11/34564A

352B

352A

テーマコード(参考)

5B060

5MO24

審査請求 未請求 請求項の数 8 O L (全 46 頁)

(21) 出願番号 特願2017-12854 (P2017-12854)

(22) 出願日 平成29年1月27日 (2017.1.27)

(31) 優先権主張番号 特願2016-16658 (P2016-16658)

(32) 優先日 平成28年1月29日 (2016.1.29)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2016-16660 (P2016-16660)

(32) 優先日 平成28年1月29日 (2016.1.29)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 石津 貴彦

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 田村 輝

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム(参考) 5B060 CC02

5M024 AA06 AA41 AA94 BB02 BB20

BB35 BB36 BB37 CC02 CC03

CC07 CC62 HH01 HH11 HH16

LL11 LL16 LL17 PP01 PP02

PP03 PP04 PP05 PP07 QQ01

QQ02 QQ03 QQ10

(54) 【発明の名称】半導体装置、電子部品、および電子機器

## (57) 【要約】

【課題】プロセッサに、1クロックサイクル時間よりも書き込みサイクル時間が長いメモリを搭載することを可能にする。

【解決手段】プロセッサは、プロセッサコア、バス、メモリ部を有する。メモリ部は第1メモリを有する。第1メモリのセルアレイは、ゲインセルで構成されている。プロセッサコアは、書き込みイネーブル信号を生成する機能を有する。第1メモリは、書き込みイネーブル信号に対応して、待機信号を生成する機能を有する。プロセッサコアは、待機信号に基づいて、メモリ部へのアクセスをnクロックサイクル時間延期する。第1メモリの書き込みサイクルに(n+1)クロックサイクルが割り当てられる。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

プロセッサコア、メモリ部、およびバスを有する半導体装置であり、

前記メモリ部は第1メモリを有し、

前記第1メモリはメモリセルを有し、

前記メモリセルは、第1トランジスタ、第2トランジスタ、および容量素子を有し、

前記第1トランジスタの第1端子は前記第2トランジスタのゲートに電気的に接続され

、前記第2トランジスタのゲートは、前記容量素子の第1端子に電気的に接続され、

前記プロセッサコアは、書き込みイネーブル信号を生成する機能を有し、

前記バスは、前記書き込みイネーブル信号を前記メモリ部に出力する機能を有し、

前記第1メモリは、前記書き込みイネーブル信号に基づいて、待機信号を生成する機能

を有し、

前記バスは前記待機信号を前記プロセッサコアに出力する機能を有し、

前記プロセッサコアは、前記待機信号に基づいて、前記メモリ部へのアクセスをnクロ

ックサイクル時間（nは1以上の整数）延期する機能を有する半導体装置。

## 【請求項 2】

プロセッサコア、メモリ部、バス、レジスタ、クロック生成部、およびロジック部を有

する半導体装置であり、

前記メモリ部は第1メモリを有し、

前記第1メモリはメモリセルを有し、

前記メモリセルは、第1トランジスタ、第2トランジスタ、および容量素子を有し、

前記第1トランジスタの第1端子は前記第2トランジスタのゲートに電気的に接続され

、前記第2トランジスタのゲートは、前記容量素子の第1端子に電気的に接続され、

前記プロセッサコアは、前記レジスタに第1データを書き込む機能を有し、

前記レジスタは前記第1データを前記クロック生成部に出力する機能と、前記第1データ

を前記ロジック部に出力する機能とを有し、

前記クロック生成部は、前記第1データに応じた周波数のクロック信号を生成する機能

を有し、

前記ロジック部は、前記第1データに基づいて第1信号を生成する機能と、前記第1信号

を前記第1メモリに出力する機能とを有し、

前記プロセッサコアは、書き込みイネーブル信号を生成する機能を有し、

前記バスは、前記書き込みイネーブル信号を前記メモリ部に出力する機能を有し、

前記第1メモリは、前記書き込みイネーブル信号および前記第1信号に基づいて、待機

信号を生成する機能を有し、

前記バスは前記待機信号を前記プロセッサコアに出力する機能を有し、

前記プロセッサコアは、前記待機信号に基づいて、前記メモリ部へのアクセスをmクロ

ックサイクル時間（mは0以上の整数）延期する機能を有する半導体装置。

## 【請求項 3】

請求項1又は2において、

第3トランジスタを有し、

前記第2トランジスタの第1端子と前記第3トランジスタの第1端子は互いに電気的に

接続されている半導体装置。

## 【請求項 4】

請求項1乃至3の何れか1項において、

前記第1トランジスタのチャネル形成領域は、酸化物半導体を有する半導体装置。

## 【請求項 5】

請求項1乃至4の何れか1項において、

前記メモリ部は、SRAM、フラッシュメモリ、強誘電体RAM、磁気抵抗RAM、抵

10

20

30

40

50

抗変化 R A M 、および相変化 R A M の少なくとも 1 つを有する半導体装置。

【請求項 6】

チップおよびリードを有し、

前記リードは前記チップに電気的に接続され、

前記チップには、請求項 1 乃至 5 の何れか 1 項に記載の半導体装置が設けられている電子部品。

【請求項 7】

請求項 6 に記載の電子部品と、

表示部、タッチセンサ、マイク、スピーカ、操作キー、及び筐体の少なくとも一と、

を有する電子機器。

10

【請求項 8】

複数の第 1 領域、およびダイシング用の領域を有する半導体ウエハであって、

前記複数の第 1 領域には、それぞれ、請求項 1 乃至 5 のいずれか 1 項に記載の半導体装置が設けられている半導体ウエハ。

【発明の詳細な説明】

【技術分野】

【0001】

本出願の明細書、図面、および特許請求の範囲（以下、本明細書等と呼ぶ）で開示する本発明の一形態は、半導体装置、その動作方法、その使用方法、およびその作製方法等に関する。なお、本発明の一形態は例示した技術分野に限定されるものではない。

20

【背景技術】

【0002】

一般的な D R A M ( ダイナミックランダムアクセスメモリ ) は、メモリセルが 1 個のトランジスタ ( 1 T ) と 1 個のキャパシタ ( 1 C ) で構成されている。 1 T 1 C 型 D R A M は、キャパシタに電荷を蓄積することで、データを保持することが可能なメモリであるため、原理的に無制限に書き込みができる。また、書き込みおよび読み出しの速度が高速であること、メモリセルの素子数が少ないため高集積が容易であることから、 D R A M は大容量なメモリ装置として、多くの電子機器に組み込まれている。しかしながら、 1 T 1 C 型 D R A M は、キャパシタに蓄積した電荷をそのままビット線に放出して電位の変動を測定することでデータの読み出しを行うため、キャパシタの静電容量を一定以上とすることが求められ、メモリセルの微細化によって必要な静電容量を確保することが困難となりつつある。

30

【0003】

1 T 1 C 型メモリセルに対して、 2 個のトランジスタまたは 3 個のトランジスタで形成されたゲインセルと呼ばれるメモリセルが提案されている（例えば、特許文献 1 、 2 ）。ゲインセルは、蓄積した電荷量を読み出しトランジスタで增幅して、ビット線に供給できるため、キャパシタの容量を小さくすることが可能とされる。

【0004】

チャネル形成領域に金属酸化物を有するトランジスタ（以下、「酸化物半導体トランジスタ」、または「 O S トランジスタ」と呼ぶ場合がある。）が知られている。また、ゲインセルの書き込みトランジスタが O S トランジスタであるメモリが提案されている（例えば、特許文献 3 、非特許文献 1 、 2 ）。

40

【0005】

本明細書等では、特許文献 3 のように、メモリセルに O S トランジスタが設けられているメモリのことを、「 O S メモリ」と呼ぶこととする。

【先行技術文献】

【特許文献】

【0006】

【特許文献 1】特開 2001-93988 号公報

【特許文献 2】特開 2006-12878 号公報

50

【特許文献3】特開2011-119675号公報

## 【非特許文献】

【 0 0 0 7 】

【非特許文献1】Y. Yakubo et al., "High-speed and Low-leakage Characteristics of 60-nm C-axis Aligned Crystalline Oxide Semiconductor FET with GHz-ordered Cutoff Frequency," Ext. Abstr. Solid-State Devices and Materials, 2014, pp. 648-649.

【非特許文献2】T. Matsuzaki et al., "A 128kb 4bit Cell Nonvolatile Memory with Crystalline In-Ga-Zn Oxide FET Using Vt Cancel Write Method," ISSCC Dig. Tech. Papers, 2015, pp. 306-307.

## 【発明の概要】

## 【発明が解決しようとする課題】

( 0 0 0 8 )

本発明の一形態の課題は、新規な半導体装置を提供すること、新規な半導体装置の動作方法を提供すること、新規な半導体装置の使用方法を提供すること、動作周波数を向上すること、動作周波数を変更できる半導体装置を提供すること、低消費電力の半導体装置を提供すること、および1クロックサイクル時間よりも書き込みサイクル時間が長いメモリを搭載する半導体装置を提供すること、である。

[ 0 0 0 9 ]

なお、本発明の一形態はこれらの課題の全てを解決する必要はない。複数の課題の記載は互いの課題の存在を妨げるものではない。列記した以外の課題は本明細書等の記載から自ずと明らかになり、これらの課題も本発明の一形態の課題となり得る。

### 【課題を解決するための手段】

【 0 0 1 0 】

(1) 本発明の一形態は、プロセッサコア、メモリ部、およびバスを有する半導体装置であり、メモリ部は第1メモリを有し、第1メモリはメモリセルを有し、メモリセルは、第1トランジスタ、第2トランジスタ、および容量素子を有し、第1トランジスタの第1端子は第2トランジスタのゲートに電気的に接続され、第2トランジスタのゲートは、容量素子の第1端子に電気的に接続され、プロセッサコアは、書き込みイネーブル信号を生成する機能を有し、バスは、書き込みイネーブル信号をメモリ部に出力する機能を有し、第1メモリは、書き込みイネーブル信号に基づいて、待機信号を生成する機能を有し、バスは待機信号をプロセッサコアに出力する機能を有し、プロセッサコアは、待機信号に基づいて、メモリ部へのアクセスをnクロックサイクル時間（nは1以上の整数）延期する機能を有する半導体装置である。

〔 0 0 1 1 〕

(2) 本発明の一形態は、プロセッサコア、メモリ部、バス、レジスタ、クロック生成部、およびロジック部を有する半導体装置であり、メモリ部は第1メモリを有し、第1メモリはメモリセルを有し、メモリセルは第1トランジスタ、第2トランジスタおよび容量素子を有し、第1トランジスタの第1端子は第2トランジスタのゲートに電気的に接続され、第2トランジスタのゲートは、容量素子の第1端子に電気的に接続され、プロセッサコアは、レジスタに第1データを書き込む機能を有し、レジスタは第1データをクロック生成部に出力する機能と、第1データをロジック部に出力する機能とを有し、クロック生成部は、第1データに応じた周波数のクロック信号を生成する機能を有し、ロジック部は、第1データに基づいて第1信号を生成する機能と、第1信号を第1メモリに出力する機能とを有し、プロセッサコアは書き込みイネーブル信号を生成する機能を有し、バスは書き込みイネーブル信号をメモリ部に出力する機能を有し、第1メモリは書き込みイネーブル

10

20

30

40

50

ル信号および第1信号に基づいて、待機信号を生成する機能を有し、バスは待機信号をプロセッサコアに出力する機能を有し、プロセッサコアは、待機信号に基づいて、メモリ部へのアクセスをmクロックサイクル時間(mは0以上の整数)延期する機能を有する半導体装置である。

【0012】

(3) 形態(1)または(2)において、第3トランジスタを有し、第2トランジスタの第1端子と第3トランジスタの第1端子は互いに電気的に接続されている半導体装置である。

【0013】

(4) 形態(1)乃至(3)の何れか1において、メモリ部は、SRAM、フラッシュメモリ、強誘電体RAM、磁気抵抗RAM、抵抗変化RAM、および相変化RAMの少なくとも1つを有することができる。

【0014】

本明細書等において、半導体装置とは、半導体特性を利用した装置であり、半導体素子(トランジスタ、ダイオード等)を含む回路、同回路を有する装置等をいう。また、半導体特性を利用することで機能しうる装置全般をいう。例えば、集積回路、集積回路を備えたチップは、半導体装置の一例である。また、記憶装置、表示装置、発光装置、照明装置及び電子機器等は、それ自体が半導体装置である場合があり、又は半導体装置を有している場合がある。

【0015】

また、本明細書等において、XとYとが接続されている、と明示的に記載されている場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とが、本明細書等に開示されているものとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも、図または文章に記載されているものとする。X、Yは、対象物(例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など)であるとする。

【0016】

トランジスタは、ゲート、ソース、およびドレインと呼ばれる3つの端子を有する。ゲートは、トランジスタの導通状態を制御する制御ノードとして機能するノードである。ソースまたはドレインとして機能する2つの入出力ノードは、トランジスタの型及び各端子に与えられる電位の高低によって、一方がソースとなり他方がドレインとなる。このため、本明細書等においては、ソースやドレインの用語は、入れ替えて用いることができるものとする。また、本明細書等では、ゲート以外の2つの端子を第1端子、第2端子と呼ぶ場合がある。

【0017】

ノードは、回路構成やデバイス構造等に応じて、端子、配線、電極、導電層、導電体、不純物領域等と言い換えることが可能である。また、端子、配線等をノードと言い換えることが可能である。

【0018】

電圧は、ある電位と、基準の電位(例えば接地電位またはソース電位)との電位差のことを示す場合が多い。よって、電圧を電位と言い換えることが可能である。なお、電位とは、相対的なものである。よって、接地電位と記載されていても、必ずしも、0Vを意味しない場合もある。

【0019】

本明細書等において、「膜」という言葉と「層」という言葉とは、場合によっては、または、状況に応じて、互いに入れ替えることが可能である。例えば、「導電層」という用語を「導電膜」という用語に変更することが可能な場合がある。例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

【0020】

10

20

30

40

50

本明細書等において、「第1」、「第2」、「第3」という序数詞は構成要素の混同を避けるために付す場合があり、その場合は数的に限定するものではなく、また順序を限定するものでもない。

【発明の効果】

【0021】

本発明の一形態によって、新規な半導体装置を提供すること、新規な半導体装置の動作方法を提供すること、新規な半導体装置の使用方法を提供すること、動作周波数を向上すること、動作周波数を変更できる半導体装置を提供すること、低消費電力の半導体装置を提供すること、および1クロックサイクル時間よりも書き込みサイクル時間が長いメモリを搭載する半導体装置を提供すること、を実現することができる。

10

【0022】

本発明の一形態は、必ずしも、例示した効果の全てを有する必要はない。複数の効果の記載は、他の効果の存在を妨げるものではない。本発明の一形態について、上記以外の課題、効果、および新規な特徴については、本明細書の記載および図面から自ずと明らかになるものである。

【図面の簡単な説明】

【0023】

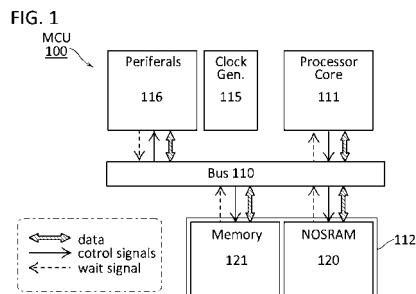

【図1】マイクロコントローラユニット（MCU）の構成例を示すブロック図。

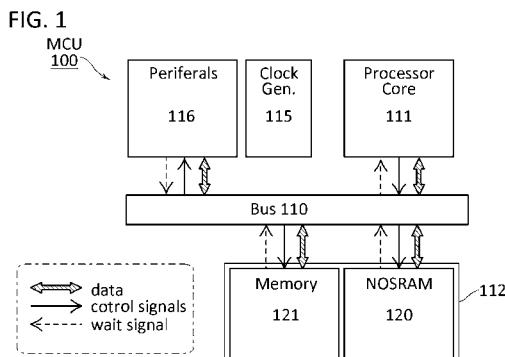

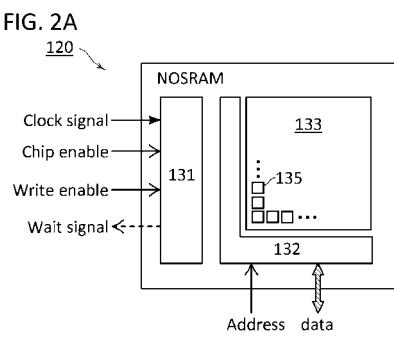

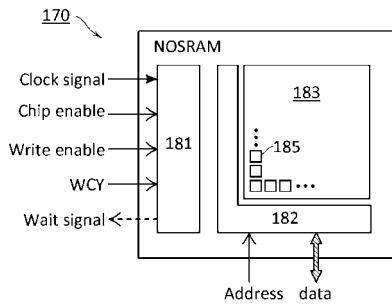

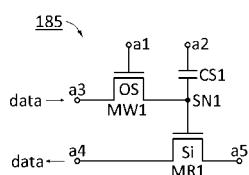

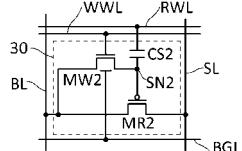

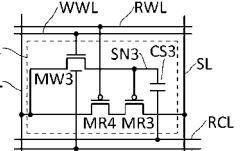

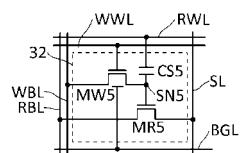

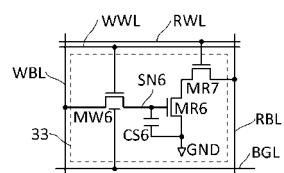

【図2】A：NOSRAMの構成例を示すブロック図。B：メモリセルの構成例を示す回路図。

20

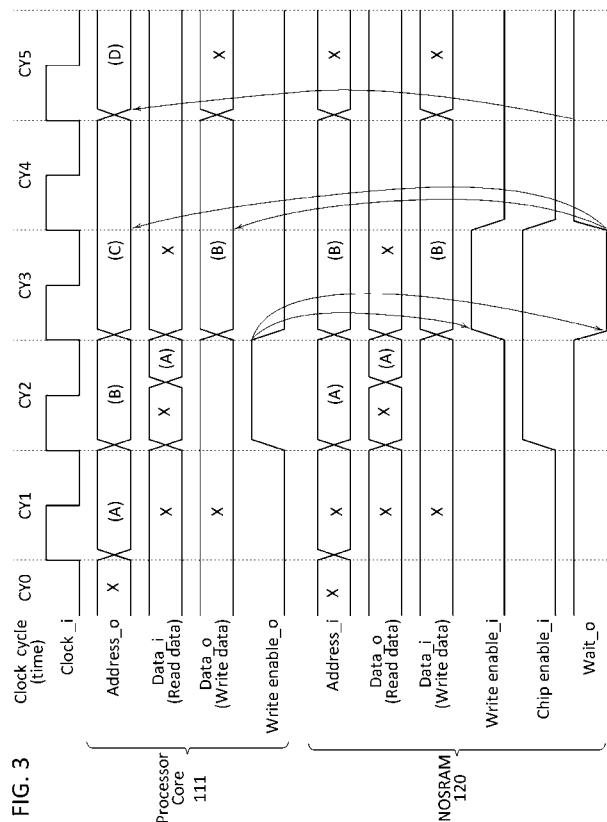

【図3】MCUの動作例を示すタイミングチャート。

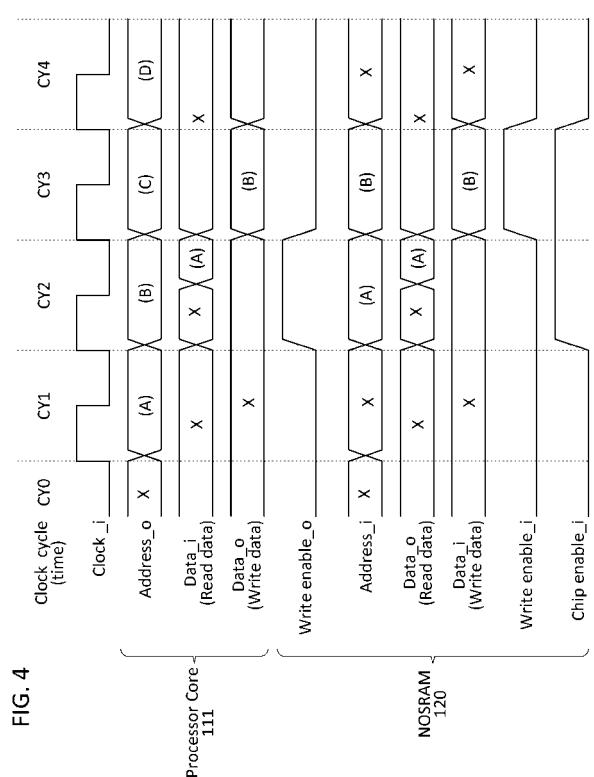

【図4】MCUの動作例を示すタイミングチャート。

【図5】A：マイクロコントローラユニット（MCU）の構成例を示すブロック図。B：クロック信号生成回路の構成例を示すブロック図。C：待機信号の構成例を示すタイミングチャート。

【図6】A：NOSRAMの構成例を示すブロック図。B：メモリセルの構成例を示す回路図。

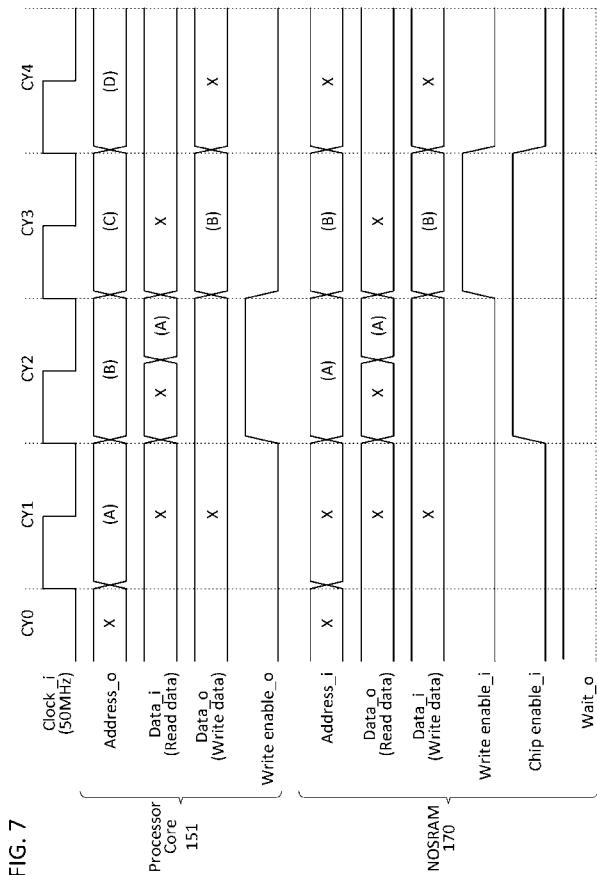

【図7】MCUの動作例を示すタイミングチャート。

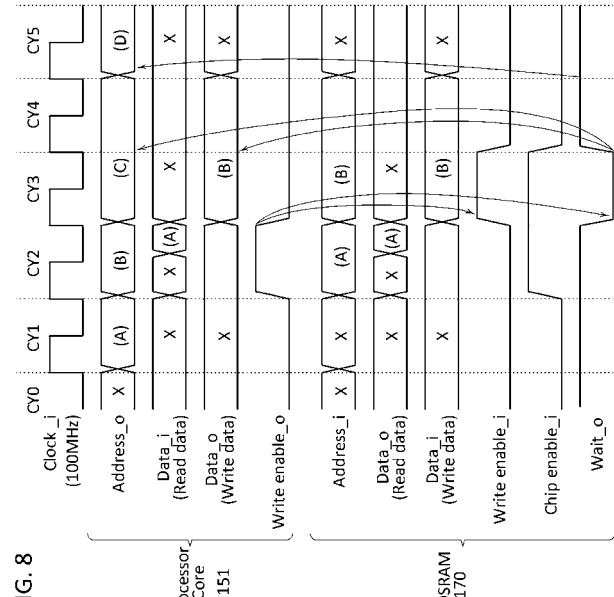

【図8】MCUの動作例を示すタイミングチャート。

【図9】A：NOSRAMの構成例を示すブロック図。B：メモリセルの構成例を示す回路図。

30

【図10】A-F：メモリセルの構成例を示す回路図。

【図11】列ドライバの構成例を示す回路図。

【図12】NOSRAMの読み出し動作例を示すタイミングチャート。

【図13】NOSRAMの書き込み動作例を示すタイミングチャート。

【図14】A、B：NOSRAMのブロックの構成例を示すブロック図。

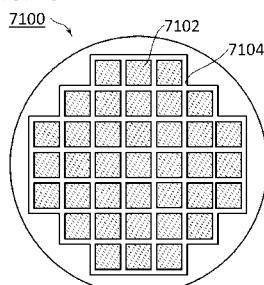

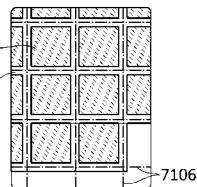

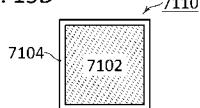

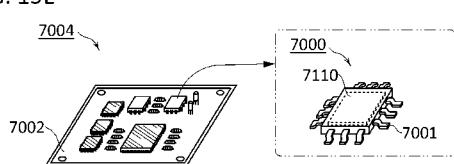

【図15】A：電子部品の作製方法例を示すフローチャート。B：半導体ウエハの上面図。C：半導体ウエハの部分拡大図。Dチップの拡大図。E：電子部品の構成例を示す斜視模式図。

【図16】A-F：電子機器の構成例を示す図。

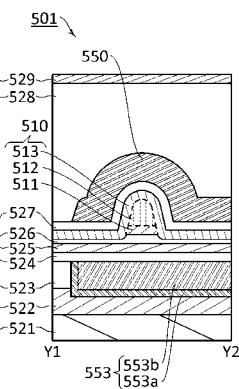

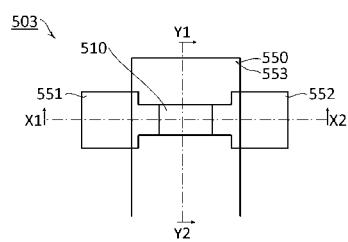

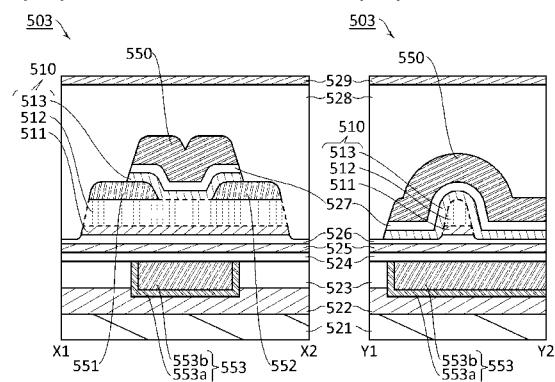

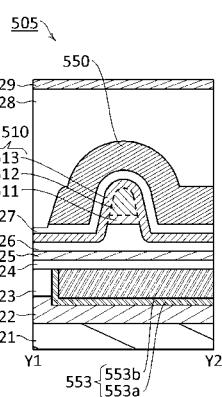

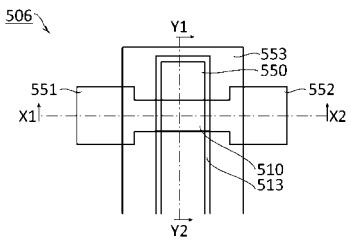

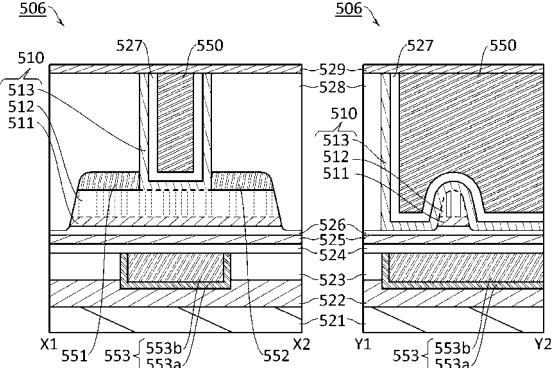

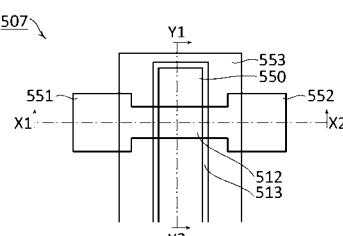

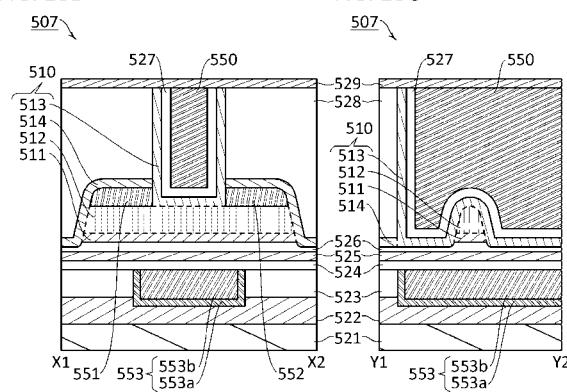

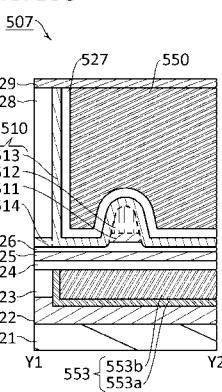

【図17】A：OS（酸化物半導体）トランジスタの構成例を示す平面図。B、C：図17AのOSトランジスタの断面図。

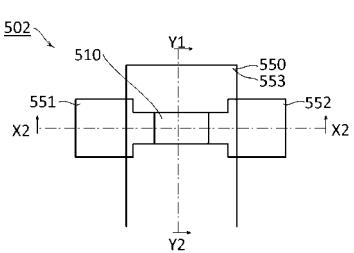

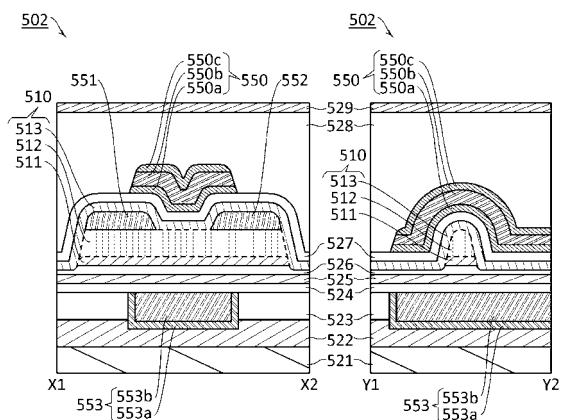

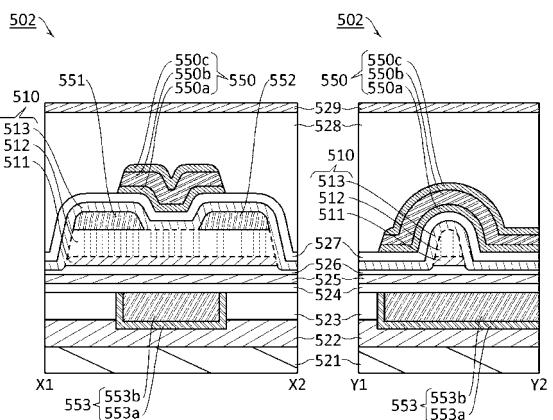

【図18】A：OSトランジスタの構成例を示す平面図。B、C：図18AのOSトランジスタの断面図。

【図19】A：OSトランジスタの構成例を示す平面図。B、C：図19AのOSトランジスタの断面図。

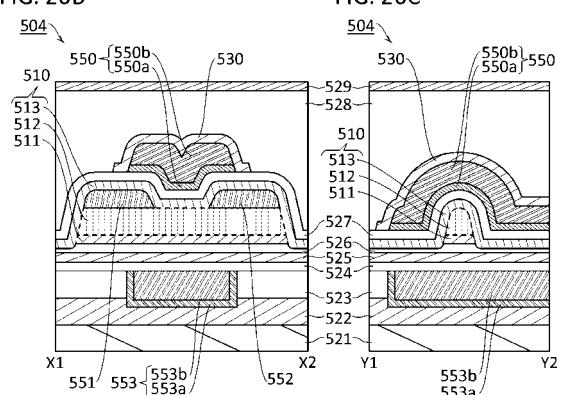

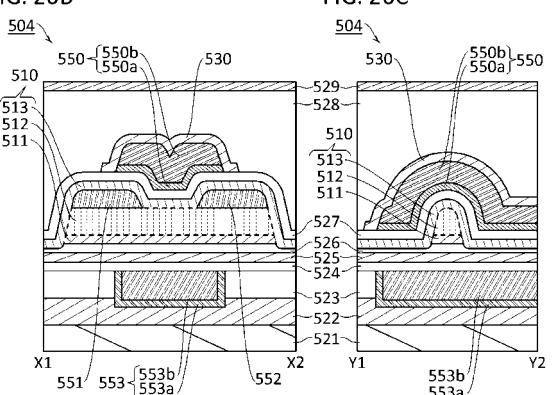

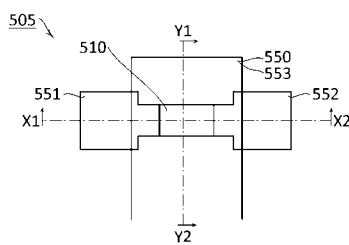

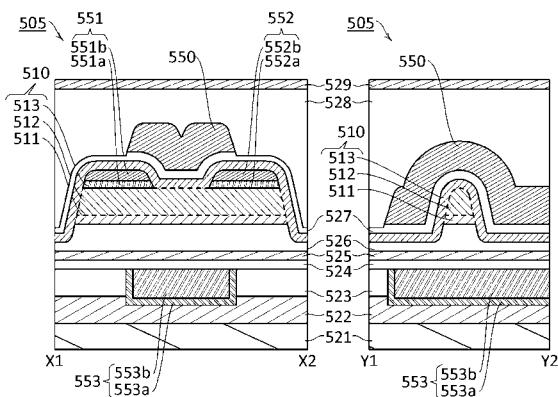

【図20】A：OSトランジスタの構成例を示す平面図。B、C：図20AのOSトランジスタの断面図。

【図21】A：OSトランジスタの構成例を示す平面図。B、C：図21AのOSトランジスタの断面図。

40

50

【図22】A:OSトランジスタの構成例を示す平面図。B、C:図22AのOSトランジスタの断面図。

【図23】A:OSトランジスタの構成例を示す平面図。B、C:図23AのOSトランジスタの断面図。

【図24】OSトランジスタのエネルギー・バンド図。

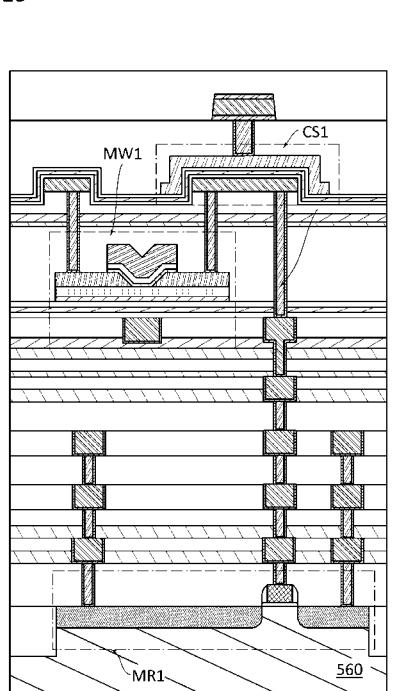

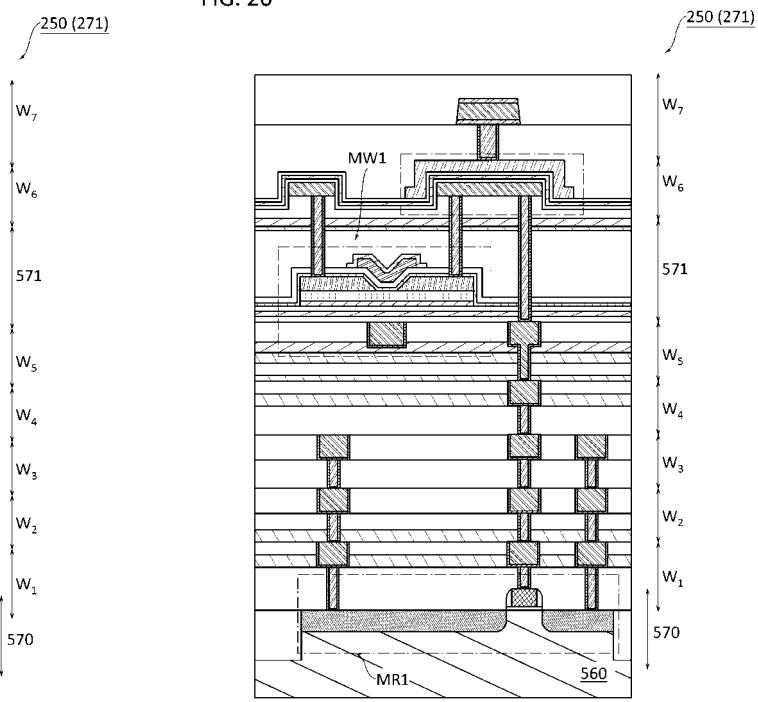

【図25】MCUの構成例を示す断面図。

【図26】MCUの構成例を示す断面図。

【発明を実施するための形態】

【0024】

以下に本発明の実施の形態を示す。ただし、本明細書に記載された実施の形態を適宜組み合わせることが可能である。また、1つの実施の形態の中に複数の構成例（動作例、使用方法例、製造方法例も含む）が示される場合は、互いに構成例を適宜組み合わせることが可能である。また、本発明は、多くの異なる形態で実施することが可能であり、趣旨及びその範囲から逸脱することなく、その形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

【0025】

図面において、大きさ、層の厚さ、および領域等は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。図面は、理想的な例を模式的に示したものであり、図面に示す形状又は値などに限定されない。例えば、ノイズによる信号、電圧、若しくは電流のばらつき、又は、タイミングのずれによる信号、電圧、若しくは電流のばらつきなどを含むことが可能である。

【0026】

本明細書において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている場合がある。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。従って、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。

【0027】

図面に記載したブロック図の各回路ブロックの配置は、説明のため位置関係を特定するものであり、本発明の一形態の回路ブロックの配置は、これに限定されない。ブロック図において、異なる回路ブロックで別々の機能を実現するよう示していても、実際の回路ブロックにおいては同じ回路ブロック内で別々の機能を実現しうるよう設けられている場合もある。また各回路ブロックの機能は、説明のため機能を特定するものであり、1個の回路ブロックで示されていても、実際の回路ブロックにおいては1個の回路ブロックで行う処理を、複数の回路ブロックで行うように設けられている場合もある。

【0028】

〔実施の形態1〕

本実施の形態では、OSメモリを備えた半導体装置について説明する。

【0029】

<<MCU>>

図1にマイクロコントローラユニット(MCU)の構成例を示す。図1に示すMCU100は、バス110、プロセッサコア111(以下、「コア111」と呼ぶ。)、メモリ部112、クロック生成回路115、周辺回路116を有する。MCU100は1チップ化された半導体装置である。

【0030】

クロック生成回路115は、MCU100で使用されるクロック信号を生成する機能を有する。周辺回路116の機能に特段の制約はない。周辺回路116には、MCU100の用途に応じて、様々な機能回路が設けられる。機能回路としては、例えば、電源回路、電源管理ユニット、タイマー装置、割り込みコントローラ、入出力ポート、アナログ・デジタルコンバータ(ADC)、コンパレータ、およびオペアンプ等が挙げられる。

10

20

30

40

50

## 【0031】

メモリ部112は、NOSRAM120、およびメモリ121を有する。「NOSRAM（登録商標）」とはOSメモリの1種である。NOSRAMの説明は追って行う。メモリ121は、書き換え可能なメモリであればよく、例えば、SRAM、フラッシュメモリ、FeRAM（強誘電体RAM）、MRAM（磁気抵抗RAM）、抵抗変化RAM（ReRAM）、相変化RAM（PRAM）等である。

## 【0032】

メモリ部112には、メモリ121を設けなくてもよいし、あるいは複数のメモリ121を設けてもよい。例えば、メモリ部112に、SRAMおよびフラッシュメモリを設けてもよい。メモリ部112に、読み出し専用メモリ（ROM）を設けてもよい。

10

## 【0033】

コア111は、バス110を介して、メモリ部112、および周辺回路116とデータのやり取りを行う。コア111からの制御信号はバス110に入力される。バス110は、制御対象の回路ブロックに制御信号を送信する。制御信号には、イネーブル信号、アドレス信号などがある。

## 【0034】

NOSRAM120、メモリ121、周辺回路116は、待機（Wait）信号を発行する機能を有する。待機信号は、アクセスの延期をコア111に要求するための信号である。バス110に入力された待機信号は、コア111に伝送される。

20

## 【0035】

## &lt; NOSRAM &gt;

図2AはNOSRAM120の構成例を示すブロック図である。図2Aに示すNOSRAM120は、制御部131、ドライバ部132、セルアレイ133を有する。

## 【0036】

制御部131は、NOSRAM120の動作全般を制御する機能を有するロジック回路である。制御部131は、チップイネーブル信号、および書き込みイネーブル信号を論理演算して、コア111のアクセスが書き込みアクセスであるか読み出しアクセスであるか判断する。制御部131は、この論理演算をもとに、ドライバ部132の制御信号を生成する。また、書き込みアクセスである場合、制御部131は待機信号を発行し、バス110に送信する。コア111は待機信号を受信すると、次のアクセスの実行を延期する。

30

## 【0037】

書き込みイネーブル信号はコア111が生成する信号である。チップイネーブル信号は、バス110が生成する信号である。バス110は、コア111が出力するアドレス信号および書き込みイネーブル信号をもとに、チップイネーブル信号を生成する。

## 【0038】

ドライバ部132は、セルアレイ133に対するデータの書き込みおよび読み出しをするための回路である。例えば、ドライバ部132は、アドレス信号をデコードするデコーダ、ワード線ドライバ、読み出し回路、および書き込み回路などを有する。

## 【0039】

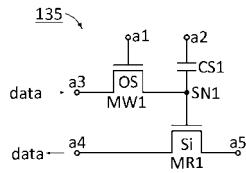

セルアレイ133には、複数のメモリセル135が行列状に配置されている。図2Bにメモリセル135の構成例を示す。ここでは、メモリセル135が2T型ゲインセルの例を示す。メモリセル135は、トランジスタMW1、トランジスタMR1、容量素子CS1、およびノードSN1、a1-a5を有する。トランジスタMW1は書き込みトランジスタであり、OSトランジスタである。トランジスタMR1は読み出しトランジスタであり、図2Bの例ではnチャネル型Siトランジスタである。ノードSN1はデータ保持ノードであり、容量素子CS1はノードSN1の電荷を保持するための保持容量素子である。

40

## 【0040】

OSトランジスタはオフ電流が極めて小さいため、メモリセルのトランジスタに好適である。ここでいう、オフ電流とは、トランジスタがオフ状態のときにソースとドレインとの間に流れる電流をいう。トランジスタがnチャネル型である場合、例えば、しきい値電圧

50

が 0 V 乃至 2 V 程度であれば、ゲートとソース間の電圧が負の電圧であるときのソースとドレインとの間に流れる電流をオフ電流と呼ぶことができる。また、オフ電流が極めて小さいとは、例えば、チャネル幅 1  $\mu$ m あたりのオフ電流が  $100 z$  A ( $z$  ; ゼプト、 $10^{-21}$ ) 以下であることをいう。オフ電流は小さいほど好ましいため、この規格化されたオフ電流が  $10 z$  A /  $\mu$ m 以下、あるいは  $1 z$  A /  $\mu$ m 以下とすることが好ましく、 $10 y$  A /  $\mu$ m ( $y$  ; ヨクト、 $10^{-24}$ ) 以下であることがより好ましい。

#### 【0041】

酸化物半導体のバンドギャップは  $3.0 \text{ eV}$  以上であるため、OSトランジスタは熱励起によるリーク電流が小さく、また上掲のようにオフ電流が極めて小さい。チャネル形成領域に適用される酸化物半導体は、インジウム (In) および亜鉛 (Zn) の少なくとも一方を含む酸化物半導体であることが好ましい。このような酸化物半導体としては、In-M-Zn 酸化物 (元素Mは、例えばAl、Ga、YまたはSn) が代表的である。電子供与体 (ドナー) となる水分または水素等の不純物を低減し、かつ酸素欠損も低減することで、酸化物半導体を i 型 (真性半導体) にする、あるいは i 型に限りなく近づけることができる。ここでは、このような酸化物半導体は高純度化された酸化物半導体と呼ぶことができる。高純度化された酸化物半導体を適用することで、チャネル幅で規格化されたOSトランジスタのオフ電流を数  $y$  A /  $\mu$ m 以上数  $z$  A /  $\mu$ m 以下程度に低くすることができる。OSトランジスタ、および酸化物半導体については、実施の形態 5、6 で説明する。

10

#### 【0042】

メモリセル 135 にデータを書き込むには、ノード a3 にデータを入力する。ノード a1 を "H" にしてトランジスタ MW1 をオンにすることで、ノード a3 のデータがノード SN1 に書き込まれる。トランジスタ MW1 をオフ状態にして、ノード SN1 をフローティング状態にすることで、データの書き込みが終了する。

20

#### 【0043】

ノード a4 の電圧をデータとして読み出す。データの読み出しは、例えば、以下のように行われる。ノード a5 の電位を固定する。ノード a4 をプリチャージした後、フローティング状態にする。トランジスタ MR1 には、ノード SN1 の電圧に応じたドレイン電流が流れる。よって、ノード a4 の電圧は、ノード SN1 の電圧に応じて変化する。

#### 【0044】

オフ電流が極めて小さいというOSトランジスタの特長によって、ノード SN1 の電圧の低下を抑えることができること、データの保持に電力を消費しないことから、メモリセル 135 はデータを長時間保持できるという不揮発性の特性を持つ。そこで、本明細書等では、ゲインセルでセルアレイが構成されるOSメモリを、NOSRAM (Nonvolatile Oxide Semiconductor RAM、ノスラム) と呼ぶこととする。NOSRAM は、データを長時間保持できることの他に、次のような特長を持つ。

30

#### 【0045】

容量素子の充放電によってデータを書き換えるため、NOSRAM には原理的には書き換え回数に制約はなく、かつ、低エネルギーで、データの書き込みおよび読み出しが可能である。メモリセルの回路構成が単純であるため、大容量化が容易である。つまり、NOSRAM と搭載することで、メモリ部の容量が大きく、低消費電力なMCUを提供することができる。したがって、書換え耐性が大容量メモリとして好適である。しかしながら、NOSRAM のメモリセルは回路構成が単純なため、NOSRAM のメモリモジュールとしての性能は、OSトランジスタの電気特性に大きく影響される。

40

#### 【0046】

OSトランジスタは、Siトランジスタと比較するとオン電流が小さい。NOSRAM のメモリセルは、OSトランジスタのスイッチング動作によってデータを書き込むため、読み出し速度に比較して、書き込み速度が遅い課題がある。そのため、NOSRAM を内蔵するMCUのクロック周波数は、NOSRAM の書き込み速度によって制約を受ける。別言すると、動作周波数の高いMCUにNOSRAM を搭載することは、非常に困難である。本実施の形態は、このような問題点を解消したMCUを提供することが可能である。

50

## 【0047】

より具体的には、図1に示すMCU100では、NOSRAM120からの待機信号をコア111が受信すると、コア111は、メモリ部112に対する書き込みサイクルに( $n+1$ )クロックサイクル( $n$ は1以上の整数)を割り当てる。以下、図3、図4を参照してMCU100の動作例を説明する。

## 【0048】

<<MCUの動作例>>

図3、図4は、コア111のメモリ部112へのアクセスを示すタイミングチャートである。図3、図4において、CY0、CY1等はクロックサイクルを示す。“\_o”はバス110への出力信号を示し、“\_i”はバス110からの入力信号を示す。例えば、“Address\_o”はコア111がバス110に出力するアドレス信号を表し、“Address\_i”は、バス110からNOSRAM120に入力されるアドレス信号である。コア111に入力されるデータは、NOSRAM120から読み出したデータである。コア111が出力するデータは、NOSRAM120に書き込むデータである。

10

## 【0049】

図3、図4には、アドレス(A)、(B)へのアクセスについて詳細に示され、その他の動作に関わるアドレス、およびデータは“X”で略記されている。アドレス(A)、(B)は、NOSRAM120のアドレスであり、アドレス(C)、(D)は、メモリ121のアドレスである。コア111は、アドレス(A)のデータ(A)の読み出しと、アドレス(B)へのデータ(B)の書き込みを行っている。

20

## 【0050】

(参考例) 先ず、参考例として、NOSRAM120が待機信号を生成する機能をもたない場合のMCU100の動作例を説明する。図4は、コア111のNOSRAM120へのアクセスを示すタイミングチャートである。

30

## 【0051】

クロックサイクルCY1で、コア111はアドレス(A)、“L”の書き込みイネーブル信号をバス110に出力する。次のクロックサイクルCY2で、NOSRAM120には、アドレス(A)、“L”の書き込みイネーブル信号、“H”のチップイネーブル信号が入力される。書き込みイネーブル信号が“L”であるので、NOSRAM120はアドレス(A)に記憶しているデータ(A)を読み出す。データ(A)はバス110を介してコア111に入力される。

30

## 【0052】

また、コア111はアドレス(A)を発行した後、次のクロックサイクルCY2で、アドレス(B)、“H”の書き込みイネーブル信号をバス110に出力し、クロックサイクルCY3で、データ(B)をバス110に出力する。クロックサイクルCY3で、NOSRAM120には、アドレス(B)、データ(B)、“H”の書き込みイネーブル信号、および“H”のチップイネーブル信号が入力される。クロックサイクルCY3において、NOSRAM120はデータ(B)をアドレス(B)に書き込む。

## 【0053】

クロックサイクルCY3でコア111はアドレス(C)をバス110に出力する。アドレス(C)はメモリ121のアドレスであるので、クロックサイクルCY4で、バス110は“L”のチップイネーブル信号をNOSRAM120に出力する。

40

## 【0054】

図4の例では、NOSRAM120の書き込みサイクルおよび読み出しサイクルには、1クロックサイクルが割り当てられている。そのため、NOSRAM120の書き込みサイクル時間よりも1クロックサイクル時間を短くすることができない。例えば、NOSRAM120がデータの書き込みサイクル時間が20nsである場合、MCU100の動作周波数を50MHz(1クロックサイクル時間=20ns)よりも高くすることができない。

## 【0055】

50

本実施の形態によって、動作周波数がN O S R A Mの書き込みサイクル時間に制約されないM C Uを提供することが可能になる。図3のタイミングチャートを参照して、このことを説明する。図3は、コア111のN O S R A M120へのアクセスを示すタイミングチャートである。

【0056】

図3では、待機信号は、“L”であるときがアクティブであり、“H”であるときは非アクティブである。

【0057】

読み出しアクセスの動作は、図4の参考例と同様であり、クロックサイクルC Y 1でコア111はアドレス(A)を発行し、クロックサイクルC Y 2で、N O S R A M120は、データ(A)を読み出す。N O S R A M120の読み出し動作は高速で行うことができるので、コア111がアドレスを発行したクロックサイクルで、N O S R A M120が読み出したデータがコア111に届く。

10

【0058】

書き込みアクセスの動作は、図4の参考例と異なる。クロックサイクルC Y 2で、コア111は、アドレス(B)、および“H”の書き込みイネーブル信号をバス110に出力する。クロックサイクルC Y 3で、N O S R A M120には、アドレス(B)、“H”の書き込みイネーブル信号、“H”のチップイネーブル信号が入力される。クロックサイクルC Y 3において、クロック信号の立ち上がり時の書き込みイネーブル信号が“H”であるため、N O S R A M120は“L”の待機信号を出力する。

20

【0059】

クロックサイクルC Y 4において、クロック信号立ち上がり時の待機信号の論理が“L”であるため、コア111は、メモリ部112に対するアクセス要求を延期し、クロックサイクルC Y 3と同じ処理を行う。よって、N O S R A M120は、2クロックサイクル(C Y 3、C Y 4)で、アドレス(B)へのデータ(B)の書き込みが可能となる。

【0060】

クロックサイクルC Y 5において、クロック信号立ち上がり時の待機信号の論理が“H”であるため、コア111は、延期していたアクセス要求を実行する。図3の例では、コア111はアドレス(D)を発行する。

30

【0061】

図3の例では、N O S R A M120の書き込みサイクルに、2クロックサイクルを割り当てているが、割り当てるクロックサイクル数は2に限定されない。N O S R A M120の書き込みサイクルには、(n+1)クロックサイクル(nは1以上の整数)を割り当てることができる。この場合、待機信号が“L”である時間はnクロックサイクル時間である。

【0062】

N O S R A M120の書き込みサイクル時間が20nsである場合を想定する。クロック信号の周波数が100MHz(クロックサイクル時間=10ns)である場合は、1クロックサイクルの間アクティブな待機信号が発行され、書き込みサイクルに2クロックサイクルが割り当てられる。クロック信号の周波数が200MHz(クロックサイクル時間=5ns)である場合は、3クロックサイクルの間アクティブな待機信号が発行され、書き込みサイクルに4クロックサイクルが割り当てられる。

40

【0063】

なお、待機信号が“H”であることは、N O S R A M120が、コア111のアクセスを受け付け可能な状態であることを表し、待機信号が“L”であることは、N O S R A M120が、コア111のアクセスを受け付けられない状態であることを表していることから、待機(Wait)信号は、準備(Ready)信号とみなすことができる。

【0064】

プロセッサコアの動作周波数はN O S R A Mの書き込みサイクル時間に制約されない。つまり、N O S R A Mの性能に合わせた動作を可能とすることで、M C Uのシステム全体のパフォーマンスを維持しつつ、低消費電力のN O S R A Mを内蔵することができる。NO

50

S R A M を内蔵できることから、大容量のメモリ部を備えた高性能かつ低消費電力の M C U を提供できる。

【 0 0 6 5 】

なお、本実施の形態では、 M C U を例に、発明の実施の形態を説明したが、本実施の形態は M C U に限定されず、プロセッサコアとメモリ部を備えた様々なプロセッサに適用することができる。

【 0 0 6 6 】

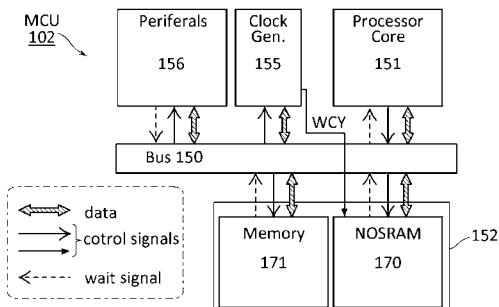

〔 実施の形態 2 〕

本実施の形態では、 O S メモリを備えた半導体装置一例として、 M C U について説明する。本実施の形態の M C U は、内部で使用するクロック信号の周波数に応じて、 N O S R A M の書き込みサイクル時間を変えができる。

【 0 0 6 7 】

< < M C U > >

図 5 A にマイクロコントローラユニット ( M C U ) の構成例を示す。図 5 A に示す M C U 1 0 2 は、バス 1 5 0 、プロセッサコア 1 5 1 ( 以下、「コア 1 5 1 」と呼ぶ。 ) 、メモリ部 1 5 2 、クロック生成回路 1 5 5 、周辺回路 1 5 6 を有する。 M C U 1 0 2 は 1 チップ化された半導体装置である。

【 0 0 6 8 】

コア 1 5 1 は、バス 1 5 0 を介して、メモリ部 1 5 2 、および周辺回路 1 5 6 とデータのやり取りを行う。コア 1 5 1 からの制御信号はバス 1 5 0 に入力される。バス 1 5 0 は、制御対象の回路ブロックに制御信号を送信する。制御信号には、イネーブル信号、アドレス信号などがある。

【 0 0 6 9 】

周辺回路 1 5 6 の機能に特段の制約はない。周辺回路 1 5 6 には、 M C U 1 0 2 の用途に応じて、様々な機能回路が設けられる。機能回路としては、例えば、電源回路、電源管理ユニット、タイマー装置、割り込みコントローラ、入出力ポート、アナログ デジタルコンバータ ( A D C ) 、コンパレータ、およびオペアンプ等が挙げられる。

【 0 0 7 0 】

メモリ部 1 5 2 は、 N O S R A M 1 7 0 、およびメモリ 1 7 1 を有する。メモリ 1 7 1 は、書き換え可能なメモリであればよく、例えば、 S R A M 、フラッシュメモリ、 F e R A M ( 強誘電体 R A M ) 、 M R A M ( 磁気抵抗 R A M ) 、抵抗変化 R A M ( R e R A M ) 、相変化 R A M ( P R A M ) 等である。

【 0 0 7 1 】

メモリ部 1 5 2 には、メモリ 1 7 1 を設けなくてもよいし、あるいは複数のメモリ 1 7 1 を設けてもよい。例えば、メモリ部 1 5 2 に、 S R A M およびフラッシュメモリを設けてもよい。メモリ部 1 5 2 に、読み出し専用メモリ ( R O M ) を設けてもよい。

【 0 0 7 2 】

N O S R A M 1 7 0 、メモリ 1 7 1 、周辺回路 1 5 6 は、待機 ( W a i t ) 信号を発行する機能を有する。待機信号は、アクセスの延期をコア 1 5 1 に要求するための信号である。バス 1 5 0 に入力された待機信号は、コア 1 5 1 に伝送される。

【 0 0 7 3 】

クロック生成回路 1 5 5 は、 M C U 1 0 2 で使用されるクロック信号を生成する機能を有する。クロック生成回路 1 5 5 は内部に記憶している周波数設定用データによって、クロック周波数を変更できる機能を備えている。周波数設定用データの書き換えは、コア 1 5 1 によって行われる。図 5 B にクロック生成回路 1 5 5 の構成例を示す。

【 0 0 7 4 】

< クロック生成回路 >

クロック生成回路 1 5 5 は、設定用レジスタ 1 6 1 、クロック生成部 1 6 2 、ロジック部 1 6 3 を有する。設定用レジスタ 1 6 1 は、クロック周波数設定用データ F Q ( 以下、データ F Q と呼ぶ。 ) を記憶する機能を有する。設定用レジスタ 1 6 1 のデータ F Q は、コ

10

20

30

40

50

ア 1 5 1 の制御によって書き換えを行うことができる。設定用レジスタ 1 6 1 はデータ F Q をクロック生成部 1 6 2 、ロジック部 1 6 3 に出力する。

【 0 0 7 5 】

クロック生成部 1 6 2 はデータ F Q に応じた周波数のクロック信号を生成する。クロック生成部 1 6 2 が生成するクロック信号は、M C U 1 0 2 内で使用される。

【 0 0 7 6 】

ロジック部 1 6 3 は、データ F Q に基づいて信号 W C Y を生成する機能を有する。信号 W C Y は、バス 1 5 0 を介さずにN O S R A M 1 7 0 に入力される。信号 W C Y は、N O S R A M 1 7 0 の書き込みサイクルに割り当てるクロックサイクル数を設定する機能を有する。

10

【 0 0 7 7 】

クロック生成回路 1 5 5 によって、クロック信号の周波数を変更することができるため、M C U 1 0 2 の高性能化と低消費電力化とを実現できる。高速処理が必要なときはクロック周波数を上げる。電力を下げたいとき（例えば、バッテリによる駆動時）は、クロック周波数を下げることができる。

【 0 0 7 8 】

< N O S R A M >

図 6 A はN O S R A M 1 7 0 の構成例を示すブロック図である。図 6 A に示すN O S R A M 1 7 0 は、制御部 1 8 1 、ドライバ部 1 8 2 、セルアレイ 1 8 3 を有する。

20

【 0 0 7 9 】

制御部 1 8 1 は、N O S R A M 1 7 0 の動作全般を制御する機能を有するロジック回路である。制御部 1 8 1 は、チップイネーブル信号、および書き込みイネーブル信号を論理演算して、コア 1 5 1 のアクセスが書き込みアクセスであるか読み出しアクセスであるかを判断する機能、チップイネーブル信号、書き込みイネーブル信号および信号 W C Y を論理演算して、ドライバ部 1 8 2 の制御信号を生成する機能、書き込みイネーブル信号と信号 W C Y に基づいて待機信号を発行する機能を有する。

【 0 0 8 0 】

コア 1 5 1 から書き込みアクセスがあると、制御部 1 8 1 は待機信号を発行し、バス 1 5 0 に送信する。コア 1 5 1 は待機信号を受信すると、次のアクセスの実行を延期する。

30

【 0 0 8 1 】

書き込みイネーブル信号はコア 1 5 1 が生成する信号である。チップイネーブル信号は、バス 1 5 0 が生成する信号である。バス 1 5 0 は、コア 1 5 1 が出力するアドレス信号および書き込みイネーブル信号をもとに、チップイネーブル信号を生成する。

【 0 0 8 2 】

ドライバ部 1 8 2 は、セルアレイ 1 8 3 に対するデータの書き込みおよび読み出しをするための回路である。例えば、ドライバ部 1 8 2 は、アドレス信号をデコードするデコーダ、ワード線ドライバ、読み出し回路、および書き込み回路などを有する。

【 0 0 8 3 】

セルアレイ 1 8 3 には、複数のメモリセル 1 8 5 が行列状に配置されている。図 6 B にメモリセル 1 8 5 の構成例を示す。メモリセル 1 8 5 の回路構成は、図 2 B のメモリセル 1 3 5 と同じである。

40

【 0 0 8 4 】

実施の形態 1 で説明したように、O S トランジスタは、S i トランジスタと比較するとオン電流が小さいため、N O S R A M を内蔵するM C U のクロック周波数は、N O S R A M の書き込み速度によって制約を受ける。本実施の形態は、このような問題点を解消し、動作周波数がN O S R A M の書き込み速度に制約されないM C U を提供することが可能である。

【 0 0 8 5 】

より具体的には、コア 1 5 1 によって、設定用レジスタ 1 6 1 のデータ F Q を書き換えることで、クロック周波数と、N O S R A M 1 7 0 の書き込みサイクル時間とを最適化する

50

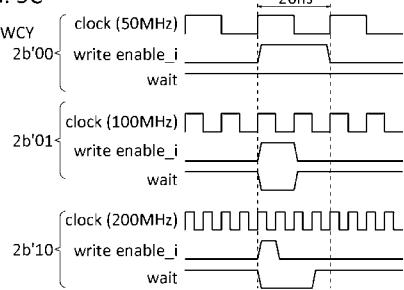

ことができる。表1に、データFQによるクロック周波数と書き込みサイクル時間の設定例を示す。ここでは、クロック周波数を、10MHz、50MHz、100MHz、および200MHzの何れかに設定する例を示す。

【0086】

【表1】

| 設定用レジスタ161 |         | ロジック部163 |           |

|------------|---------|----------|-----------|

| FQ         | クロック周波数 | WCY      | 書き込みサイクル  |

| 2'b00      | 10MHz   | 2'b00    | 1クロックサイクル |

| 2'b01      | 50MHz   | 2'b00    | 1クロックサイクル |

| 2'b10      | 100MHz  | 2'b01    | 2クロックサイクル |

| 2'b11      | 200MHz  | 2'b10    | 4クロックサイクル |

【0087】

データFQは2ビットのデータである。コア151が設定用レジスタ161に2'b00を書き込むと、クロック生成部162は10MHzのクロック信号を生成し、設定用レジスタ161に2'b11を書き込むと、クロック生成部162は200MHzのクロック信号を生成する。

【0088】

表1は、ロジック部163の真理値表に対応する。ここではNOSRAM170の書き込みサイクル時間が20nsに最適化されていることを想定している。20nsは、クロック周波数が50MHzのときの1クロックサイクル時間である。クロック周波数が50MHzを超える場合、NOSRAM170の書き込みサイクルに、2クロックサイクル以上を割り当てることが求められる。そこで、MCU102では、信号WCYによって、NOSRAM170の書き込みサイクルに要するクロックサイクル数を制御している。

【0089】

設定用レジスタ161に、2'b01が書き込まれると、ロジック部163は、2'b00の信号WCYをNOSRAM170に出力し、設定用レジスタ161に、2'b10が書き込まれると、ロジック部163は、2'b01の信号WCYをNOSRAM170に出力する。NOSRAM170は、書き込みイネーブル信号を受け取ると、信号WCYのデータに基づいて待機信号を生成する。ここでは、信号WCYの値が、NOSRAM170が待機信号を発行するクロックサイクル時間を表している。

【0090】

表1の例では、データFQおよび信号WCYのビット幅は2ビットであるが、これに限定されない。データFQのビット幅は、クロック周波数の使用数に応じて決めることができる。信号WCYのビット幅は、クロック周波数と、NOSRAM170の書き込み特性に応じて決めることができる。

【0091】

<<MCUの動作例>>

以下、図7、図8、を参照してMCU102の動作例を説明する。図7、図8は、コア151のメモリ部152へのアクセスを示すタイミングチャートである。図7の例では、クロック周波数が50MHzであり、図8の例では、クロック周波数は100MHzである。

【0092】

図7、図8において、CY0、CY1等はクロックサイクルを示す。“\_o”はバス150への出力信号を示し、“\_i”はバス150からの入力信号を示す。例えば、“Address\_o”はコア151がバス150に出力するアドレス信号を表し、“Address\_i”は、バス150からNOSRAM170に入力されるアドレス信号である。コア151に入力されるデータは、NOSRAM170から読み出したデータである。コア

10

20

30

40

50

151が出力するデータは、NOSRAM170に書き込むデータである。

【0093】

図7、図8には、アドレス(A)、(B)へのアクセスについて詳細に示され、その他の動作に関わるアドレス、およびデータは“X”で略記されている。アドレス(A)、(B)は、NOSRAM170のアドレスであり、アドレス(C)、(D)は、メモリ171のアドレスである。コア151は、アドレス(A)のデータ(A)の読み出しと、アドレス(B)へのデータ(B)の書き込みを行っている。

【0094】

ここでは、待機信号は、“L”であるときがアクティブであり、“H”であるときは非アクティブである。

【0095】

(動作例1)

図7を参照して、NOSRAM170の書き込みサイクル時間が1クロックサイクル時間であるときのMCU102の動作例を説明する。

【0096】

クロックサイクルCY1で、コア151はアドレス(A)、“L”の書き込みイネーブル信号をバス150に出力する。次のクロックサイクルCY2で、NOSRAM170には、アドレス(A)、“L”の書き込みイネーブル信号、“H”のチップイネーブル信号が入力される。書き込みイネーブル信号が“L”であるので、NOSRAM170はアドレス(A)に記憶しているデータ(A)を読み出す。データ(A)はバス150を介してコア151に入力される。

【0097】

また、コア151はアドレス(A)を発行した後、次のクロックサイクルCY2で、アドレス(B)、“H”の書き込みイネーブル信号をバス150に出力し、クロックサイクルCY3で、データ(B)をバス150に出力する。クロックサイクルCY3で、NOSRAM170には、アドレス(B)、データ(B)、“H”の書き込みイネーブル信号、および“H”のチップイネーブル信号が入力される。クロックサイクルCY3において、NOSRAM170はデータ(B)をアドレス(B)に書き込む。

【0098】

クロックサイクルCY3でコア151はアドレス(C)をバス150に出力する。アドレス(C)はメモリ171のアドレスであるので、クロックサイクルCY4でバス150は“L”のチップイネーブル信号をNOSRAM170に出力する。

【0099】

(動作例2)

図8を参照して、NOSRAM170の書き込みサイクル時間が2クロックサイクル時間であるときのMCU102の動作例を説明する。

【0100】

読み出しアクセスは、図7と同様に実行される。クロックサイクルCY1でコア151はアドレス(A)を発行し、クロックサイクルCY2で、NOSRAM170は、データ(A)を読み出す。NOSRAM170の読み出し動作は高速で行うことができるので、コア151がアドレスを発行したクロックサイクルで、NOSRAM170が読み出しデータがコア151に届く。

【0101】

書き込みアクセスは、図7の動作と異なり、NOSRAM170の書き込みサイクルは2クロックサイクルで実行される。

【0102】

クロックサイクルCY2で、コア151は、アドレス(B)、および“H”の書き込みイネーブル信号をバス150に出力する。クロックサイクルCY3で、NOSRAM170には、アドレス(B)、“H”の書き込みイネーブル信号、“H”のチップイネーブル信号が入力される。クロックサイクルCY3において、クロック信号の立ち上がり時の書き

込みイネーブル信号が“H”であるため、NOSRAM170は、アクティブな待機信号を出力する。クロックサイクルCY4において、NOSRAM170は、待機信号を非アクティブにする。

【0103】

クロックサイクルCY4において、クロック立ち上がり時の待機信号の論理が“L”であるため、コア151は、メモリ部152に対するアクセス要求を延期し、クロックサイクルCY3と同じ処理を行う。クロックサイクルCY5では、クロック立ち上がり時の待機信号の論理が“H”であるため、コア151は、延期していたアクセス要求を実行する。図8の例では、アドレス(D)を発行する。

【0104】

信号WCYに応じて、NOSRAM170の書き込みサイクルに、(m+1)クロックサイクルが割り当てられる。mは0以上の整数である。ここでは、信号WCYのデータは、待機信号をアクティブにするクロックサイクル時間を表す(図5C参照)。別言すると、信号WCYのデータは、コア151がメモリ部152へのアクセスを延期するクロックサイクル数を表す。

【0105】

信号WCYが2'b00であれば、書き込みイネーブル信号が入力されても、NOSRAM170は“H”的待機信号を出力する。つまり、NOSRAM170は待機信号を発行しないこととなる。NOSRAM170は、信号WCYが2'b01であれば、1クロックサイクルの間アクティブな待機信号を発行し、信号WCYが2'b10であれば、3クロックサイクルの間アクティブな待機信号を発行する。

【0106】

なお、待機信号が“H”であることは、NOSRAM170が、コア151のアクセスを受け付け可能な状態であることを表し、待機信号が“L”であることは、NOSRAM170が、コア151のアクセスを受け付けられない状態であることを表していることから、待機(Wait)信号は、準備(Ready)信号とみなすことができる。

【0107】

本実施の形態のMCUでは、NOSRAMの書き込みサイクル時間に制約されずに、動作周波数を変更することができる。MCUの処理内容等に応じて、MCUの動作周波数を設定できるため、MCU全体の消費電力を削減できる。

【0108】

本実施の形態では、NOSRAMの性能に合わせた制御を可能にすることで、MCUのシステム全体のパフォーマンスを維持しつつ、低消費電力のNOSRAMを内蔵することができる。NOSRAMを内蔵できることから、大容量のメモリ部を備えた高性能かつ低消費電力MCUを提供できる。

【0109】

なお、本実施の形態では、MCUを例に、発明の実施の形態を説明したが、本実施の形態はMCUに限定されず、プロセッサコアとメモリ部を備えた様々なプロセッサに適用することができる。

【0110】

〔実施の形態3〕

本実施の形態ではNOSRAMのより具体的な構成例を説明する。本実施の形態では、実施の形態2のMCUに搭載可能なNOSRAMを説明する。

<< NOSRAMの構成例 >>

図9Aは、NOSRAMの構成例を示すブロック図である。図9Aに示すNOSRAM300は、コントロール部311、ドライバ部312、セルアレイ313、および出力回路314を有する。

【0111】

NOSRAM300には、信号CLK、CE、GW、BW[3:0]、WCY[1:0]、ADDR[10:2]が入力され、信号WAITを出力する。信号CLKはクロック信

10

20

30

40

50

号であり、信号 C E はチップイネーブル信号であり、信号 G W は書き込みイネーブル信号であり、信号 B W [ 3 : 0 ] はバイト書き込みイネーブル信号であり、信号 A D D R [ 10 : 2 ] はアドレス信号である。信号 W A I T は待機信号である。データ W D A [ 31 : 0 ] は書き込みデータであり、データ R D A [ 31 : 0 ] は読み出しデータである。

【 0 1 1 2 】

N O S R A M 3 0 0 では信号 G W が上掲の書き込みイネーブル信号に対応する。N O S R A M 3 0 0 は信号 G W 、W C Y に基づいて信号 W A I T を発行する。ここでは、信号 W C Y と書き込みサイクルとの関係は表 1 に従う。

【 0 1 1 3 】

N O S R A M 3 0 0 には、電圧 V d d 、V s s 、V r f 、V b g が入力される。電圧 V d d は高電源電圧であり、V s s は低電源電圧である。電圧 V b g はセルアレイ 3 1 3 に入力され、電圧 V r f はドライバ部 3 1 2 に入力される。

10

【 0 1 1 4 】

セルアレイ 3 1 3 は、複数のメモリセル 3 0 、並びに、複数の配線 W W L 、R W L 、W B L 、R B L 、S L 、B G L を有する。複数のメモリセル 3 0 は行列状に配置されている。メモリセル 3 0 の配列に応じて、配線 W W L 等が設けられている。配線 W W L は書き込みワード線であり、配線 R W L は読み出しワード線である。配線 W B L は書き込みビット線であり、配線 R B L は読み出しビット線であり、配線 S L はソース線である。配線 B G L は電圧 V b g を供給するための配線である。

20

【 0 1 1 5 】

図 9 A では、N O S R A M 3 0 0 の容量は 2 K B である。セルアレイ 3 1 3 には、1 2 8 行 1 2 8 列にメモリセル 3 0 が配置されている。ここでは、1 2 8 本の W B L に対して、3 2 本の配線 G W B L ( グローバル書き込みビット線 ) が設けられ、1 2 8 本の R B L に対して、3 2 本の配線 G R B L ( グローバル読み出しビット線 ) が設けられている。

30

【 0 1 1 6 】

N O S R A M 3 0 0 において、各回路、各信号および各電圧は、必要に応じて、適宜取捨することができる。あるいは、他の回路または他の信号を追加してもよい。また、N O S R A M 3 0 0 の入力信号および出力信号の構造 ( 例えば、ビット長 ) は、M C U のアーキテクチャ、N O S R A M 3 0 0 の動作モード、およびセルアレイ 3 1 3 の構成等に基づいて設定される。

30

【 0 1 1 7 】

( セルアレイ )

図 9 B に、セルアレイ 3 1 3 の構成例を示す。図 9 B には、セルアレイ 3 1 3 の 1 行 1 列の要素を代表的に示す。メモリセル 3 0 は、2 トランジスタ型のゲインセルである例である。メモリセル 3 0 は、トランジスタ M W 2 、トランジスタ M R 2 、容量素子 C S 2 、ノード S N 2 を有する。

30

【 0 1 1 8 】

ノード S N 2 は保持ノードである。容量素子 C S 2 はノード S N 2 の電圧を保持するための容量素子である。容量素子 C S 2 の第 1 端子はノード S N 2 に、第 2 端子は配線 R W L に電気的に接続されている。トランジスタ M R 2 は p チャネル型 S i トランジスタである。トランジスタ M W 2 はバックゲートを有する O S トランジスタであり、バックゲートは配線 B G L に電気的に接続されている。トランジスタ M W 2 、容量素子 C S 2 は、トランジスタ M R 2 に積層して設けることができるため、セルアレイ 3 1 3 の集積度を向上することができる。トランジスタ M W 2 はバックゲートを有さない O S トランジスタとすることができる。

40

【 0 1 1 9 】

配線 B G L には、電圧 V b g が入力される。電圧 V b g は電圧 V s s よりも低い電圧、たとえば負電圧とする。バックゲート電圧を負電圧とすることができますためトランジスタ M W 2 のしきい値電圧を正電圧側にシフトさせることができる。

50

【 0 1 2 0 】

図10A - 図10Eにセルアレイの他の構成例を示す。各図には1行1列分の構成例が示されている。

【0121】

図10Aは、3トランジスタ型のゲインセルを有するセルアレイの構成例を示す。図10Aに示すメモリセルアレイには、行ごとに配線RCLが設けられている。メモリセル31は、配線WWL、RWL、WBL、RBL、SL、RCL、BGLに電気的に接続されている。メモリセル31はトランジスタMW3、MR3、MR4、容量素子CS3、ノードSN3を有する。トランジスタMW2はバックゲートをもつOSトランジスタであり、バックゲートは配線BGLに電気的に接続されている。トランジスタMR4、MR3はpチャネル型Siトランジスタである。

10

【0122】

図10Bに示すセルアレイは図9Bの変形例であり、図10Cに示すセルアレイは図10Aの変形例である。これらのセルアレイでは、配線WBL、RBLの代わりに、書き込みおよび読み出し用のビット線（配線BL）が設けられている。

【0123】

図10Dに示すセルアレイは図9Bの変形例であり、トランジスタMR2がnチャネル型Siトランジスタである例である。図10Dに示すメモリセル32は、配線WWL、RWL、WBL、RBL、SL、BGLに電気的に接続されている。メモリセル32は、トランジスタMW5、MR5、容量素子CS5、ノードSN5を有する。トランジスタMW5はバックゲートを有するOSトランジスタである。トランジスタMR5はnチャネル型Siトランジスタである。図10Dのセルアレイも、図10Bのように、配線WBL、RBLに代えて配線BLを設けてよい。

20

【0124】

図10Eに示すセルアレイは図10Aの変形例であり、トランジスタMR3、MR4がnチャネル型Siトランジスタである例である。図10Eに示すメモリセル33は、配線WWL、RWL、WBL、RBL、BGL、および電位GNDが入力される配線に電気的に接続されている。メモリセル33は、トランジスタMW6、MR6、MR7、容量素子CS6、ノードSN6を有する。トランジスタMW6はバックゲートを有するOSトランジスタである。トランジスタMR6、MR7はnチャネル型Siトランジスタである。図10Eのセルアレイも、図10Cのように、配線WBL、RBLに代えて配線BLを設けてよい。

30

【0125】

（コントロール部311）

コントロール部311は、NOSRAM300の動作全般を制御する機能を有するロジック回路である。コントロール部311は、信号GW、WCYに基づいて信号WAITを生成する機能を有する。さらに、コントロール部311は、信号CE、GW、BWを論理演算して、動作モードを決定する機能、決定した動作モードが実行されるように、ドライバ部312の制御信号を生成する機能を有する。

【0126】

（ドライバ部312、出力回路314）

40

ドライバ部312は、セルアレイ313の配線WWL、RWL、WBL、RBLおよびSLを駆動する。ドライバ部312によって、セルアレイ313に対するデータの書き込みおよび読み出しが行われる。

【0127】

データWDA[31:0]は、配線GWBにによって、ドライバ部312に入力される。ドライバ部312が読み出したデータDO[31:0]は、配線GRBLを経て、出力回路314に出力される。出力回路314はデータDO[31:0]を保持する機能を有する。出力回路314は、保持しているデータをNOSRAM300外部に出力する。この出力データがデータRDA[31:0]である。

【0128】

50

ドライバ部 312 は、行デコーダ 321、読み出しワード線ドライバ 322、書き込みワード線ドライバ 323、列デコーダ 325、列ドライバ 330 を有する。

【0129】

行デコーダ 321 は、アドレス信号をデコードする機能、読み出しワード線ドライバ 322 および書き込みワード線ドライバ 323 の制御信号を生成する機能を有する。列デコーダ 325 は、アドレス信号をデコードする機能、列ドライバ 330 の制御信号を生成する機能を有する。

【0130】

列ドライバ 330 は、データをセルアレイ 313 書き込む機能、セルアレイ 313 からデータを読み出す機能、読み出したデータを增幅する機能、読み出したデータを保持する機能等を有する。列ドライバ 330 のより具体的な機能には、例えば、WBL、RBL、およびSL の電圧を制御する機能がある。図9A に示す列ドライバ 330 は、プリチャージ回路 331、センスアンプ 332、出力MUX (マルチプレクサ) 333、書き込みドライバ 334、およびソース線ドライバ 335 を有する。

【0131】

読み出しワード線ドライバ 322 は、行デコーダ 321 が指定する行のメモリセル 30 を選択状態にする。列ドライバ 330 によって、選択状態のメモリセル 30 からはデータが読み出される。書き込みワード線ドライバ 323 は、行デコーダ 321 が指定する行のメモリセル 30 を選択状態にする。列ドライバ 330 によって、選択状態のメモリセル 30 にデータが書き込まれる。

【0132】

<列ドライバの構成例>

図11 を参照して、列ドライバ 330 の構成例を説明する。図11 に示す回路 340 は、列ドライバ 330 の基本要素となる回路ブロックである。

【0133】

信号 PRCHG、信号 SNS\_P、信号 SNS\_N、信号 RSEL [3:0]、信号 RSEL\_G [3:0]、信号 WSEL、および信号 WSEL\_G [15:0] は、列ドライバ 330 の制御信号であり、NOSRAM 300 内で生成される信号である。

【0134】

列ドライバ 330 には、列ごとに回路 340 が設けられている。回路 340 は、トランジスタ T60 T62、T65-T69、SA (センスアンプ) 60、TG (トランスマニアゲート) 61、62、AND回路 65 を有する。なお、図11 において、回路 340 には、ソース線ドライバ 335 を構成する素子は省略されている。

【0135】

(プリチャージ回路 331)

トランジスタ T60 はプリチャージ回路 331 に設けられている。トランジスタ T60 のゲートには、バッファ 341 を介して信号 PRCHG が入力される。トランジスタ T60 をオンにすることで、配線 RBL は電圧 Vss ("L") にプリチャージされる。

【0136】

(センスアンプ 332)

SA 60 はセンスアンプ 332 に設けられている。SA 60 は、ラッチ回路 75、トランジスタ T65、T66、ノード Q2、Q3 を有する。ラッチ回路 75 は 2 個のインバータ回路を有する。

【0137】

トランジスタ T65 のゲートにはバッファ 344 を介して、信号 SNS\_P が入力される。トランジスタ T66 のゲートにはバッファ 345 を介して、信号 SNS\_N が入力される。トランジスタ T65、T66 は、スリープトランジスタとして機能する。トランジスタ T65 によりラッチ回路 75 と Vdd 線 (電圧 Vdd の供給用配線) との接続が制御され、トランジスタ T66 により、ラッチ回路 75 と Vss 線 (電圧 Vss の供給用配線) との接続が制御される。信号 SNS\_P と信号 SNS\_N の論理は相補的に変化する。そ

10

20

30

40

50

のため、トランジスタ T 6 6 がオンであれば、トランジスタ T 6 5 もオンである。

【 0 1 3 8 】

(出力 MUX 3 3 3 )

出力 MUX 3 3 3 は、データを読み出す配線 RBL を選択する機能、配線 RBL のデータを配線 GRBL に出力する機能を有する。NOSRAM 3 0 0 には、4 本の配線 RBL に対して 1 本の配線 GRBL が設けられている。

【 0 1 3 9 】

出力 MUX 3 3 3 には、TG 6 1、6 2、トランジスタ T 6 1、T 6 2 が設けられている。信号 RSEL [ 3 : 0 ]、RSEL\_G [ 3 : 0 ] は、出力 MUX 3 3 3 の制御信号である。信号 RSEL [ 3 : 0 ] は、データを読み出す配線 RBL を選択するための選択信号である。信号 RSEL\_G [ 3 : 0 ] は、配線 GRBL へのデータの出力を制御するための信号である。

【 0 1 4 0 】

TG 6 1 は、ノード QB 2 と配線 RBL との接続を制御し、TG 6 2 は、ノード Q 2 と Vrf 線（電圧 Vrf の供給用配線）との接続を制御する。TG 6 1 において、信号 RSEL [ 3 : 0 ] の何れか 1 ビットが、バッファ 3 4 3 を介して n チャネル型トランジスタのゲートに入力され、かつバッファ 3 4 3 およびインバータ 3 4 9 を介して p チャネル型トランジスタのゲートに入力される。TG 6 2 も同様である。

【 0 1 4 1 】

直列に電気的に接続されているトランジスタ T 6 1、T 6 2 によって、スイッチ 7 8 が構成される。信号 RSEL\_G [ 3 : 0 ] の何れか 1 ビットが、バッファ 3 4 8 を介して、トランジスタ T 6 1 のゲートに入力される。トランジスタ T 6 2 のゲートは、ノード QB 2 に電気的に接続されている。

【 0 1 4 2 】

図 1 1 の例では、1 本の配線 GRBL に、4 個のスイッチ 7 8 が並列に電気的に接続されている。4 個のスイッチ 7 8 によって、4 入力 1 出力 MUX が構成される。この 4 入力 1 出力 MUX は、信号 RSEL\_G [ 3 : 0 ] に応じて、4 列から 1 列を選択し、選択列の SA 6 0 で保持しているデータを配線 GRBL に出力する機能を有する。

【 0 1 4 3 】

<書き込みドライバ>

AND 回路 6 5、トランジスタ T 6 7 - T 6 9 は書き込みドライバ 3 3 4 に設けられている。信号 WSEL、信号 WSEL\_G [ 15 : 0 ] は、書き込みドライバ 3 3 4 の制御信号である。書き込みドライバ 3 3 4 は、データを書き込む配線 WBL を選択する機能、および書き込みデータの列ドライバ 3 3 0 への入力を制御する機能等を有する。4 本の配線 WBL に対して、1 本の配線 GWB が設けられている。

【 0 1 4 4 】

信号 WSEL は、バッファ 3 4 2 を介して AND 回路 6 5 に入力される。AND 回路 6 5 は、ノード Q 2 と配線 WBL との接続を制御する。信号 WSEL\_G [ 15 : 0 ] は、データを書き込む WBL を選択するための選択信号である。

【 0 1 4 5 】

トランジスタ T 6 7 - T 6 9 によって、回路 7 7 が構成される。回路 7 7 は、配線 GWB がデータを SA 6 0 に書き込む機能を有する。信号 WSEL\_G [ 15 : 0 ] の何れか 1 ビットが、バッファ 3 4 7 を介して、トランジスタ T 6 7、T 6 8 のゲートに入力される。また、データ WDA [ 31 : 0 ] の何れか 1 ビットが、バッファ 3 4 6 を介して配線 GWB に入力される。配線 GWB にはトランジスタ T 6 9 のゲートが電気的に接続されている。配線 GWB に “H” が書き込まれているとき、トランジスタ T 6 8、T 6 7 がオンになると、ノード Q 2 に “H” のデータが書き込まれ、ノード QB 2 に “L” のデータが書き込まれる。

【 0 1 4 6 】

コントロール部 3 1 1 が信号 CE、GW、BW [ 3 : 0 ] を論理演算することで、NOS

10

20

30

40

50

R A M 3 0 0 の動作モードが決定される。表 2 に、N O S R A M 3 0 0 の動作モードを設定する真理値表を示す。N O S R A M 3 0 0 は、スタンバイモード、読み出しモード、並びに、3 つの書き込みモード（バイト書き込み、ハーフワード書き込み、ワード書き込み）、およびリフレッシュモードを有する。信号 R S E L [ 3 : 0 ]、信号 R S E L \_ G [ 3 : 0 ]、信号 W S E L \_ G [ 1 5 : 0 ] の論理は A D D R [ 1 0 : 2 ]、B W [ 3 : 0 ] によって決定される。

【 0 1 4 7 】

【 表 2 】

| モード        | CE | GW | BW[0] | BW[1] | BW[2] | BW[3] |

|------------|----|----|-------|-------|-------|-------|

| スタンバイ      | L  | X  | X     | X     | X     | X     |

| 読み出し       | H  | L  | L     | L     | L     | L     |

| バイト書き込み    | H  | H  | H     | L     | L     | L     |

| ハーフワード書き込み | H  | H  | H     | H     | L     | L     |

| ワード書き込み    | H  | H  | H     | H     | H     | H     |

| リフレッシュ     | H  | H  | L     | L     | L     | L     |

【 0 1 4 8 】

ここでは、1 ワードのビット幅は 3 2 ビットとする。信号 B W [ 3 ]、B W [ 2 ]、B W [ 1 ]、B W [ 0 ] の論理は、それぞれ、データ W D A [ 3 1 : 2 4 ]、W D A [ 2 3 : 1 6 ]、W D A [ 1 5 : 8 ]、W D A [ 7 : 0 ] の書き込みを決定する。

【 0 1 4 9 】

図 1 1 に示す回路 3 4 0 で列ドライバ 3 3 0 を構成することで、N O S R A M 3 0 0 は、階層ワード線構造を採用せずに、セルアレイ 3 1 3 のラインサイズよりも小さな単位でのデータの書き込みが可能である。ワード線分割回路（A N D 回路）による面積増大が生じないため、N O S R A M 3 0 0 は大容量化に非常に有利である。また、ワード線分割回路を有さないため、N O S R A M 3 0 0 は大容量化に伴う消費電力の増大を抑えることができる。

【 0 1 5 0 】

ここでは、セルアレイ 3 1 3 のラインサイズが 1 2 8 ビットであるが、N O S R A M 3 0 0 はワード（例えば、3 2 ビット）単位、ハーフワード（例えば、1 6 ビット）単位、およびバイト（8 ビット）単位での書き込みが可能である。

【 0 1 5 1 】

なおN O S R A M 3 0 0 の動作モードは、表 2 に限定されない。例えば、バーストモードを選択する制御信号を外部から入力し、バースト書き込み、バースト読み出しを行ってよい。図 1 2 、図 1 3 に示すタイミングチャートを参照して、N O S R A M 3 0 0 の動作例を説明する。

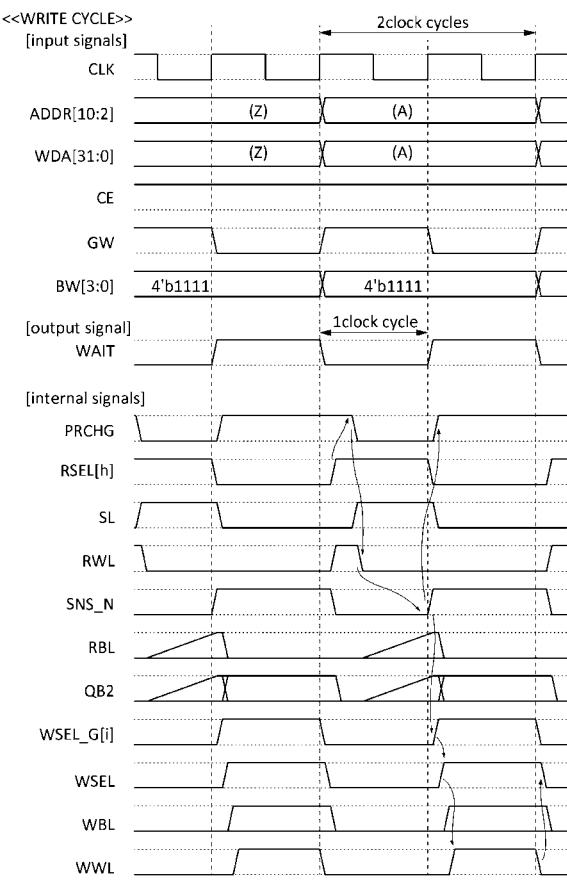

【 0 1 5 2 】

図 1 2 は、N O S R A M 3 0 0 の読み出しサイクルの動作例を示すタイミングチャートであり、図 1 3 は、N O S R A M 3 0 0 の書き込みサイクルの動作例を示すタイミングチャートである。図中の信号 R S E L [ h ] において、h は 0 以上 3 以下の整数であり、信号 R S E L \_ G [ k ] において、k は 0 以上 3 以下の整数であり、信号 W S E L \_ G [ i ] において、i は 0 以上 1 5 以下の整数である。また、N O S R A M 3 0 0 の動作の理解を容易にするため、図中に矢印を記入している。

【 0 1 5 3 】

ここでは、信号 W C Y のデータは 2 ' b 0 1 であり、書き込みサイクルに 2 クロックが割り当てられることとする。

【 0 1 5 4 】

< 読み出しサイクル >

図 1 2 では、アドレス（Z）、（A）が入力され、これらアドレスが指定するメモリセル

10

20

30

40

50

30から、データ(Z)、(A)が読み出されている。ここでは、アドレス(A)に注目して、読み出しサイクルを説明する。また、NOSRAM300の動作の理解を容易にするため、図12中に矢印を記入している。

#### 【0155】

読み出しサイクルであるので、信号CEは1'b1であり、信号GWは1'b0であり、信号BW[3:0]は4'b0000である(表2)。よって、NOSRAM300は、“H”的信号WAITを出力している。

#### 【0156】

データ(A)の読み出しには、先ず、配線RBLのプリチャージが行われる。信号SNS\_Nは”L”であるため、全ての列において、SA60へのVdd、Vssの供給が遮断されている。信号PRCHGは”H”であるので、各列の配線RBLは、トランジスタT60により”L”にプリチャージされている。全ての行の配線RWLは”H”であり、全てのメモリセル30は非選択状態である。

10

#### 【0157】

アドレス(A)が入力されると、信号RSEL[3:0]をアクティブにする。信号SNS\_Nは”L”的ままである。32の読み出し対象列において、TG61によりノードQB2が配線RBLと接続され、TG62によりノードQ2がVrf線と接続される。読み出し対象列では、ノードQB2は”L”となり、ノードQ2には電圧Vrfが供給される。

20

#### 【0158】

次に、信号PRCHGを”L”にして、プリチャージを終了する。プリチャージ終了に連動して、読み出し対象行のメモリセル30を選択する。まず、全ての列の配線SLを”H”にする。次に対象行の配線RWLを”L”にする。配線RWLの電位が低下するのに伴って、ノードSN2の電圧も下がる。ノードSN2が”H”的データを保持している場合、トランジスタMR2はオフ状態が維持され、配線RBLは”L”的ままである。ノードSN2が”L”的データを保持している場合、トランジスタMR2がオンとなるので、配線RBLの電圧は上昇する。読み出し対象列では、配線RBLの電圧に応じて、ノードQB2の電圧も変化する。つまり、ノードQB2には、ノードSN2の論理を反転したデータが出力されることとなる。

30

#### 【0159】

次に、信号SNS\_Nを”H”にし、SA60をアクティブにする。信号RSEL[3:0]を”L”にして、ノードQB2を配線RBLから電気的に分離する。SA60は、ノードQB2に書き込まれたデータの増幅と、その保持を行う。SA60のノードQ2は、ノードSN2と同じ論理のデータを保持することとなる。

#### 【0160】

次に、信号RSEL\_G[3:0]をアクティブにする。32の読み出し対象列において、トランジスタT61はオンになる。ノードQB2が”H”であれば、配線GRBLが”L”となり、ノードQB2が”L”であれば、配線GRBLは”H”となる。つまり、ノードSN2から読み出したデータと同じ論理のデータが、配線GRBLに書き込まれるので、データ(A)が読み出されることとなる。信号RSEL\_G[3:0]を一定期間アクティブにする。かかる後、非アクティブにすることで、読み出しサイクルが終了する。

40

#### 【0161】

なお、配線RBLのプリチャージは、メモリセル30からのデータの読み出しが終了次第、開始することができる。図11の例では、信号RSEL[3:0]を”L”にして、SA60と配線RBLとを電気的に分離した後、信号PRCHGを”H”して配線RBLのプリチャージを開始している。また、プリチャージの開始と連動して、対象行のメモリセル30を非選択状態に戻している。信号PRCHGを”H”にするのと連動して、配線SLを”L”にし、かかる後、配線RWLを”H”にしている。

#### 【0162】

NOSRAM300の読み出しサイクルは1クロックサイクルで完了し、NOSRAM3

50

00は、アドレス(A)を受信したクロックサイクルにおいて、データ(A)を出力することができる。

【0163】

<書き込みサイクル>

図13では、アドレス(Z)、(A)が入力され、これらアドレスが指定するメモリセル30にデータを書き込んでいる。アドレス(A)に注目して、書き込みサイクルを説明する。セルアレイ313のラインサイズよりも小さい単位でのデータ書き込みを行うため、書き込みサイクルでは、先ず読み出し動作が実行され、次いで書き込み動作が実行される。

【0164】

信号CEは1'b1であり、信号GWは1'b1であり、信号BW[3:0]は4'b1111である。また、信号WCYは2'b01である。したがって、アドレス(A)が入力されると、NOSRAM300は、1クロックサイクル時間“L”の信号WAITを出力する。

【0165】

まず、書き込み対象行の全てのメモリセル30のデータをノードQ\_B2に読み出す。この動作は、図12の読み出しモードでの動作と同様である。信号SNS\_Nを“H”にすることで、SA60において、メモリセル30から読み出したデータが増幅され、保持される。

【0166】

信号SNS\_Nを“H”にした後、信号PRCHGを“H”にして、配線RBLのプリチャージを開始する。また、プリチャージの開始と連動して、配線SLを“L”にする。

【0167】

信号SNS\_Nを“H”にした後、信号WSEL\_G[15:0]をアクティブにする。32の対象列において、回路77により、SA60のノードQ2には配線GWB\_Lのデータ(WDA[31:0]の何れか1)が書き込まれる。その他の列のSA60は、先に読み出されたデータをそのまま保持する。

【0168】

なお、ハーフワード書き込みモードでは、16の対象列のノードQ2に、それぞれWDA[15:0]の何れか1ビットが書き込まれる。バイト書き込みモードでは、8の対象列のノードQ2に、それぞれ、WDA[7:0]の何れか1ビットが書き込まれる。

【0169】

次に信号WSELを“H”にする。全ての列において、AND回路65によってノードQ2と同じ論理のデータが配線WBLに書き込まれる。なお、信号WSELが“L”である期間は、AND回路65によって、配線WBLは“L”に維持されている。次に、対象行の配線WWLを“H”にして、配線WBLのデータをメモリセル30に書き込む。32の対象列のメモリセル30にデータ(A)が書き込まれ、その他の列のメモリセル30には保持していたデータが書き戻される。

【0170】

配線WWLを“L”にして、書き込み対象行のメモリセル30を非選択状態にする。信号WSEL\_G[15:0]を非アクティブにして、配線GWB\_LとSA60とを電気的に分離する。そして、信号WSELを“L”にし、信号SNS\_Nを“L”にし、配線RWLを“H”にする。以上により、書き込みサイクルが終了する。

【0171】

以上述べたように、NOSRAM300は、ワード単位、ハーフワード単位、及びバイト単位での書き込みが可能となっているが、データの書き込み単位はこれに限定されない。ドライバ部312の回路構成、アドレス信号、制御信号等を適宜設定することで、NOSRAM300の書き込み単位はセルアレイ313のラインサイズよりも小さい任意の大きさとすることができます、例えば、Nバイト単位(Nは1以上8以下の整数)とすることができます。

10

20

30

40

50

## 【0172】

また、N O S R A M 3 0 0 の容量を2 K B としているが、これに限定されない。N O S R A M 3 0 0 には、ワード線分割回路を設ける必要がないので、ワード線分割回路によるチップ面積の増大や消費電力の増大がないため、N O S R A M 3 0 0 は大容量化に非常に有効な回路構成をもつ。

## 【0173】

例えば、セルアレイ313とドライバ部312とを有する回路ブロックを単位ブロックとし、複数の単位ブロックを設けることで、N O S R A M 3 0 0 の容量を増やすことができる。

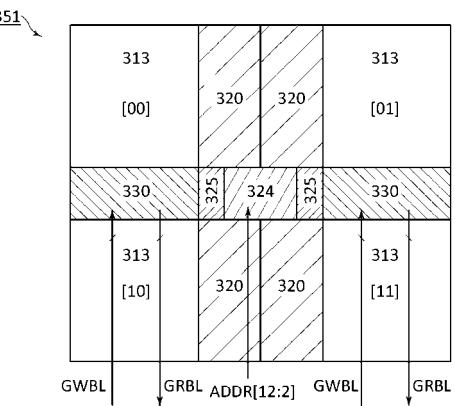

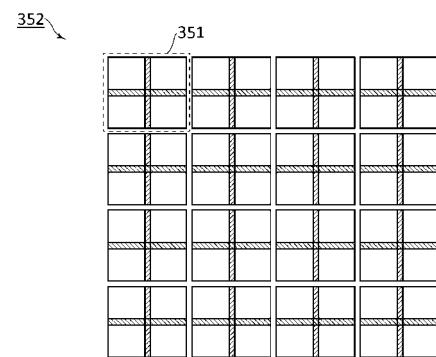

## 【0174】

例えば、図14Aに示すブロック351は、8 K B の容量を持つ。ブロック351は、4個のセルアレイ313[00]-313[11]、4個の行ドライバ320、1個のプレデコーダ324、2個の列デコーダ325、2個の列ドライバ330を有する。行ドライバ320は、行デコーダ321、読み出しワード線ドライバ322、書き込みワード線ドライバ323を有する。2個の列ドライバの一方は、セルアレイ313「00」、313[10]で共有され、他方は、セルアレイ313[01]、313[11]で共有されている。プレデコーダ324は、A D D R [12:11]をデコードし、4個のセルアレイ313[00]-313[11]からアクセス要求されているセルアレイを特定する。各セルアレイ313に付されている[00]等が、アドレスA D D R [12:11]の値である。

10

20

## 【0175】

図14Bに示すブロック352は、16個(4行×4列)のブロック351を有する。ブロック352の容量は128 K B である。アドレス信号として、信号A D D R [16:2]が用いられる。信号A D D R [16:13]がブロック351の選択に用いられる。

## 【0176】

## 〔実施の形態4〕

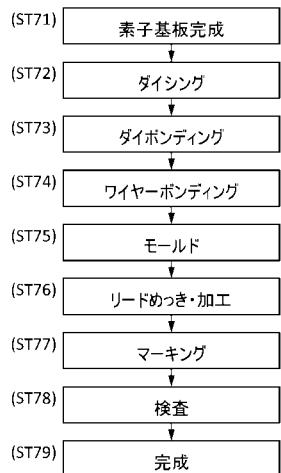

本実施の形態では、半導体装置の一例として、I Cチップ、電子部品、電子機器等について説明する。

## 【0177】

## &lt;電子部品の作製方法例&gt;

30

図15Aは、電子部品の作製方法例を示すフローチャートである。電子部品は、半導体パッケージ、またはI C用パッケージともいう。この電子部品は、端子取り出し方向や、端子の形状に応じて、複数の規格や名称が存在する。そこで、本実施の形態では、その一例について説明することにする。

40

## 【0178】

トランジスタで構成される半導体装置は、組み立て工程(後工程)を経て、プリント基板に脱着可能な部品が複数合わさることで完成する。後工程については、図15Aに示す各工程を経ることで完成させることができる。具体的には、前工程で得られる素子基板が完成(ステップS T 7 1)した後、基板の裏面を研削する。この段階で基板を薄膜化して、前工程での基板の反り等を低減し、部品の小型化を図る。次に、基板を複数のチップに分離するダイシング工程を行う(ステップS T 7 2)。

## 【0179】

図15Bは、ダイシング工程が行われる前の半導体ウエハ7100の上面図である。図15Cは、図15Bの部分拡大図である。半導体ウエハ7100には、複数の回路領域7102が設けられている。回路領域7102には、本発明の形態に係る半導体装置(例えば、M C U、記憶装置等)が設けられている。

## 【0180】

複数の回路領域7102は、それぞれが分離領域7104に囲まれている。分離領域7104と重なる位置に分離線(「ダイシングライン」ともいう。)7106が設定される。ダイシング工程S T 7 2では、分離線7106に沿って半導体ウエハ7100切断するこ

50

とで、回路領域 7102 を含むチップ 7110 を半導体ウエハ 7100 から切り出す。図 15D にチップ 7110 の拡大図を示す。

#### 【0181】

分離領域 7104 に導電層や半導体層を設けてもよい。分離領域 7104 に導電層や半導体層を設けることで、ダイシング工程時に生じうる ESD を緩和し、ダイシング工程に起因する歩留まりの低下を防ぐことができる。また、一般にダイシング工程は、基板の冷却、削りくずの除去、帯電防止などを目的として、炭酸ガスなどを溶解させて比抵抗を下げた純水を切削部に供給しながら行なう。分離領域 7104 に導電層や半導体層を設けることで、当該純水の使用量を削減することができる。よって、半導体装置の生産コストを低減することができる。また、半導体装置の生産性を高めることができる。

10

#### 【0182】

ステップ ST72 を行った後、分離したチップを個々にピックアップしてリードフレーム上に搭載し接合する、ダイボンディング工程を行う（ステップ ST73）。ダイボンディング工程におけるチップとリードフレームとの接着方法は製品に適した方法を選択すればよい。例えば、接着は樹脂やテープによって行えばよい。ダイボンディング工程は、インターポーザ上にチップを搭載し接合してもよい。ワイヤーボンディング工程で、リードフレームのリードとチップ上の電極とを金属の細線（ワイヤー）で電気的に接続する（ステップ ST74）。金属の細線には、銀線や金線を用いることができる。ワイヤーボンディングは、ボールボンディングとウェッジボンディングの何れでもよい。

20

#### 【0183】

ワイヤーボンディングされたチップは、エポキシ樹脂等で封止される、モールド工程が施される（ステップ ST75）。モールド工程を行うことで電子部品の内部が樹脂で充填され、機械的な外力による内蔵される回路部やワイヤーに対するダメージを低減することができる、また水分や埃による特性の劣化を低減することができる。リードフレームのリードをめっき処理する。そしてリードを切断及び成形加工する（ステップ ST76）。めっき処理によりリードの錆を防止し、後にプリント基板に実装する際のはんだ付けをより確実に行なうことができる。パッケージの表面に印字処理（マーキング）を施す（ステップ ST77）。検査工程（ステップ ST78）を経て、電子部品が完成する（ステップ ST79）。上掲した実施の形態の半導体装置を組み込むことで、低消費電力で、小型な電子部品を提供することができる。

30

#### 【0184】

完成した電子部品の斜視模式図を図 15E に示す。図 15E では、電子部品の一例として、QFP (Quad Flat Package) の斜視模式図を示している。図 15E に示すように、電子部品 7000 は、リード 7001 及びチップ 7110 を有する。

#### 【0185】

電子部品 7000 は、例えばプリント基板 7002 に実装される。このような電子部品 7000 が複数組み合わされて、それぞれがプリント基板 7002 上で電気的に接続されることで電子機器に搭載することができる。完成した回路基板 7004 は、電子機器等の内部に設けられる。電子部品 7000 を搭載することで、電子機器の消費電力を削減することができる。または、電子機器を小型化することが容易になる。

40

#### 【0186】

電子部品 7000 は、デジタル信号処理、ソフトウェア無線、アビオニクス（通信機器、航法システム、自動操縦装置、飛行管理システム等の航空に関する電子機器）、ASIC のプロトタイピング、医療用画像処理、音声認識、暗号、バイオインフォマティクス（生物情報科学）、機械装置のエミュレータ、および電波天文学における電波望遠鏡等、幅広い分野の電子機器の電子部品（IC チップ）に適用することが可能である。このような電子機器としては、カメラ（ビデオカメラ、デジタルスチルカメラ等）、表示装置、パーソナルコンピュータ（PC）、携帯電話、携帯型を含むゲーム機、携帯型情報端末（スマートフォン、タブレット型情報端末など）、電子書籍端末、ウェアラブル型情報端末（時計型、ヘッドマウント型、ゴーグル型、眼鏡型、腕章型、プレスレット型、ネックレス型等

50

)、ナビゲーションシステム、音響再生装置(カーオーディオ、デジタルオーディオプレイヤー等)、複写機、ファクシミリ、プリンタ、プリンタ複合機、現金自動預け入れ払い機(ATM)、自動販売機、家庭用電化製品などが挙げられる。

【0187】

図16A-図16Fを参照して、電子機器の構成例を示す。図16A等の電子機器の表示部には、タッチセンサを有するタッチパネル装置を用いることが好ましい。タッチパネル装置を用いることで、表示部を電子機器の入力部としても機能させることができる。

【0188】

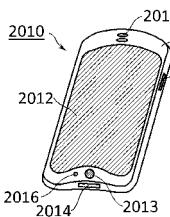

図16Aに示す情報端末2010は、筐体2011に組み込まれた表示部2012の他、操作ボタン2013、外部接続ポート2014、スピーカ2015、マイクロフォン2016を有する。ここでは、表示部2012の表示領域は、湾曲している。情報端末2010は、バッテリで駆動する携帯型情報端末であり、タブレット型情報端末、あるいはスマートフォンとして使用することができる。情報端末2010は、電話、電子メール、手帳、インターネット接続、音楽再生等の機能を有する。指などで表示部2012に触れることで、情報を入力することができる。また、電話を掛ける、文字を入力する、表示部2012の画面切り替え動作などの各種の操作は、指などで表示部2012に触れることで行われる。また、マイクロフォン2016から音声を入力することで、情報端末2010を操作することもできる。操作ボタン2013の操作により、電源のオン／オフ動作や、表示部2012の画面切り替え動作などの各種の操作を行うこともできる。

【0189】

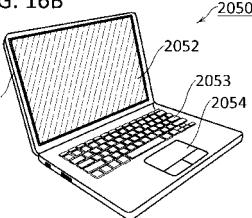

図16Bに示すノート型PC(パーソナルコンピュータ)2050は、筐体2051、表示部2052、キーボード2053、ポインティングデバイス2054を有する。表示部2052のタッチ操作で、ノート型PC2050を操作することができる。

【0190】

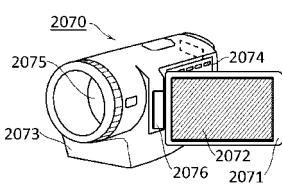

図16C示すビデオカメラ2070は、筐体2071、表示部2072、筐体2073、操作キー2074、レンズ2075、接続部2076を有する。表示部2072は筐体2071に設けられ、操作キー2074およびレンズ2075は筐体2073に設けられている。筐体2071と筐体2073とは、接続部2076により接続されており、筐体2071と筐体2073間の角度は、接続部2076により変更が可能である。接続部2076における筐体2071と筐体2073間の角度に従って、表示部2072の映像を切り替える構成としてもよい。表示部2072のタッチ操作によって、録画の開始および停止の操作、倍率ズーム調整、撮影範囲の変更などの各種の操作を実行できる。

【0191】

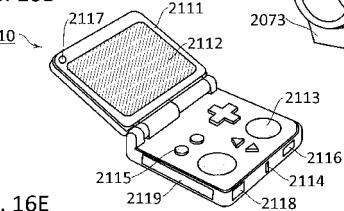

図16Dに示す携帯型遊技機2110は、筐体2111、表示部2112、スピーカ2113、LEDランプ2114、操作キーボタン2115、接続端子2116、カメラ2117、マイクロフォン2118、記録媒体読込部2119を有する。

【0192】

図16Eに示す電気冷凍冷蔵庫2150は、筐体2151、冷蔵室用扉2152、および冷凍室用扉2153等を有する。

【0193】

図16Fに示す自動車2170は、車体2171、車輪2172、ダッシュボード2173、およびライト2174等を有する。実施の形態3のプロセッサは、自動車2170内の各種のプロセッサに用いられる。

【0194】

〔実施の形態5〕

本実施の形態では、酸化物半導体トランジスタ等について説明する。

【0195】

<<OSトランジスタの構成例1>>

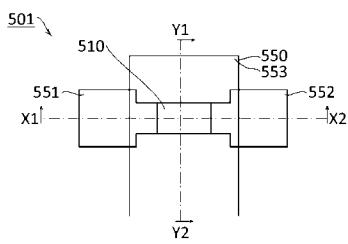

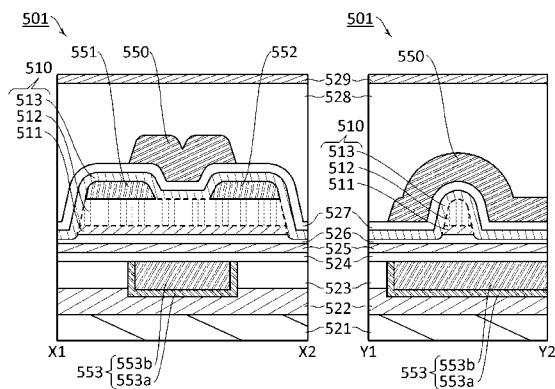

図17AはOSトランジスタの構成例を示す上面図である。図17Bは、図17AのX1-X2線断面図であり、図17CはY1-Y2線断面図である。ここでは、X1-X2線

10

20

30

40

50

の方向をチャネル長方向と、Y1-Y2線方向をチャネル幅方向と呼称する場合がある。図17Bは、OSトランジスタのチャネル長方向の断面構造を示す図であり、図17Cは、OSトランジスタのチャネル幅方向の断面構造を示す図である。なお、デバイス構造を明確にするため、図17Aでは、一部の構成要素が省略されている。

【0196】

OSトランジスタ501は絶縁表面に形成される。ここでは、絶縁層521上に形成されている。OSトランジスタ501は、絶縁層528、529で覆われている。OSトランジスタ501は、絶縁層522-527、金属酸化物層511-513、導電層550-553を有する。

【0197】

なお、図中の絶縁層、金属酸化物層、導電体等は、単層でも積層でもよい。これらの作製には、スパッタリング法、分子線エピタキシー法(MBE法)、パルスレーザ堆積法(PLD法)、CVD法、原子層堆積法(ALD法)などの各種の成膜方法を用いることができる。なお、CVD法には、プラズマCVD法、熱CVD法、有機金属CVD法などがある。

10

【0198】

金属酸化物層511-513をまとめて酸化物層510と呼ぶ。図17B、図17Cに示すように、酸化物層510は、金属酸化物層511、金属酸化物層512、金属酸化物層513の順に積層している部分を有する。OSトランジスタ501がオン状態のとき、チャネルは酸化物層510の金属酸化物層512に主に形成される。

20

【0199】

OSトランジスタ501のゲート電極は導電層550で構成され、ソース電極またはドレイン電極として機能する一対の電極は、導電層551、552で構成される。バックゲート電極は導電層553で構成される。導電層553は、導電層553a、553bを有する。なお、OSトランジスタ501はバックゲート電極を有さない構造としてもよい。後述するOSトランジスタ502-507も同様である。

【0200】

ゲート(フロントゲート)側のゲート絶縁層は絶縁層527で構成され、バックゲート側のゲート絶縁層は、絶縁層524-526の積層で構成される。絶縁層528は層間絶縁層である。絶縁層529はバリア層である。

30

【0201】

金属酸化物層513は、金属酸化物層511、512、導電層551、552でなる積層体を覆っている。絶縁層527は金属酸化物層513を覆っている。導電層551、552はそれぞれ、金属酸化物層513、絶縁層527を介して、導電層550と重なる領域を有する。

【0202】

導電層551、552は、金属酸化物層511と金属酸化物層512との積層を形成するために使用されるハードマスクから作製されている。例えば、次のような工程を経て、金属酸化物層511、512、導電層551、552を作製することができる。2層の金属酸化物膜を形成する。金属酸化物膜上に導電膜を形成する。この導電膜をエッチングしてハードマスクを形成する。ハードマスクを用いて、2層の金属酸化物膜をエッチングして、金属酸化物層511と金属酸化物層512の積層を形成する。次に、ハードマスクをエッチングして、導電層551および導電層552を形成する。このような工程を経て形成されるため、導電層551、552は、金属酸化物層511、512の側面に接する領域を有していない。

40

【0203】

(導電層)

導電層550-553に用いられる導電材料には、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体、ニッケルシリサイド等のシリサイド、モリブデン、チタン、タンタル、タンゲステン、アルミニウム、銅、クロム、ネオジム、スカンジウム

50

等の金属、または上述した金属を成分とする金属窒化物（窒化タンタル、窒化チタン、窒化モリブデン、窒化タンゲステン）等がある。また、インジウム錫酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの導電性材料を用いることができる。

【0204】

導電層550に仕事関数の高い導電性材料を用いることで、OSトランジスタ501のV<sub>t</sub>を大きくし、カットオフ電流を下げることができる。導電層550としては仕事関数が好ましくは、4.8eV以上、さらに好ましくは5.0eV以上、さらに好ましくは5.2eV以上、さらに好ましくは5.4eV以上、さらに好ましくは5.6eV以上の導電性材料を用いればよい。仕事関数の大きな導電性材料として、例えば、モリブデン、酸化モリブデン、Pt、Ptシリサイド、Niシリサイド、インジウム錫酸化物、窒素添加されたIn-Ga-Zn酸化物などが挙げられる。

10

【0205】

なお、カットオフ電流とは、ゲート-ソース間電圧が0Vであるときのドレイン電流のことという。

【0206】

例えば、導電層550は窒化タンタル、またはタンゲステン単層である。あるいは、導電層550が2層構造、および3層構造の場合、次のような組み合わせがある。（アルミニウム、チタン）、（窒化チタン、チタン）、（窒化チタン、タンゲステン）、（窒化タンタル、タンゲステン）、（窒化タンゲステン、タンゲステン）、（チタン、アルミニウム、チタン）、（窒化チタン、アルミニウム、チタン）、（窒化チタン、アルミニウム、窒化チタン）。先に記載した導電体が絶縁層527側の層を構成する。

20

【0207】

導電層551と導電層552は同じ層構造をもつ。例えば、導電層551が単層である場合、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、銀、タンタル、またはタンゲステンなどの金属、またはこれを主成分とする合金を用いればよい。導電層551が2層構造、および3層構造の場合、次のような組み合わせがある。（チタン、アルミニウム）、（タンゲステン、アルミニウム）、（タンゲステン、銅）（銅-マグネシウム-アルミニウム合金、銅）、（チタン膜、銅）、（チタン又は窒化チタン、アルミニウムまたは銅、チタンまたは窒化チタン）、（モリブデンまたは窒化モリブデン、アルミニウムまたは銅、モリブデンまたは窒化モリブデン）。先に記載した導電体が絶縁層527側の層を構成する。

30

【0208】

例えば、導電層553aは、水素に対するバリア性を有する導電層（例えば、窒化タンタル層）とし、導電層553bは、導電層553aよりも導電率の高い導電層（例えばタンゲステン層）とすることが好ましい。このような構造であることで、導電層553は配線としての機能と、酸化物層510への水素の拡散を抑制する機能とをもつ。

【0209】

（絶縁体）

絶縁層521-529に用いられる絶縁材料には、窒化アルミニウム、酸化アルミニウム、窒化酸化アルミニウム、酸化窒化アルミニウム、酸化マグネシウム、窒化シリコン、酸化シリコン、窒化酸化シリコン、酸化窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タンタル、アルミニウムシリケートなどがある。絶縁層521-529はこれらの絶縁材料でなる単層、または積層して構成される。絶縁層521-529を構成する層は、複数の絶縁材料を含んでいてもよい。

40

【0210】

なお、本明細書等において、酸化窒化物とは、酸素の含有量が窒素よりも多い化合物であり、窒化酸化物とは、窒素の含有量が酸素よりも多い化合物のことをいう。

50

## 【0211】

酸化物層510の酸素欠損の増加を抑制するため、絶縁層526-528は、酸素を含む絶縁層であることが好ましい。絶縁層526-528の少なくとも1つは、加熱により酸素が放出される絶縁膜（以下、「過剰酸素を含む絶縁膜」という。）で形成されることがより好ましい。過剰酸素を含む絶縁膜から酸化物層510に酸素を供給することで、酸化物層510の酸素欠損を補償することができる。したがって、OSトランジスタ501の信頼性および電気特性を向上することができる。

## 【0212】

過剰酸素を含む絶縁層膜とは、TDS（Thermal Desorption Spectroscopy：昇温脱離ガス分光法）において、膜の表面温度が100以上700以下、または100以上500以下の範囲における酸素分子の放出量が $1.0 \times 10^{18}$  [分子/cm<sup>3</sup>]以上である膜とする。酸素分子の放出量は、 $3.0 \times 10^{20}$  [分子/cm<sup>3</sup>]以上であることが好ましい。

10

## 【0213】

過剰酸素を含む絶縁膜は、絶縁膜に酸素を添加する処理を行って形成することができる。酸素を添加する処理は、酸素雰囲気下による熱処理や、イオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法、またはプラズマ処理などを用いて行うことができる。酸素を添加するためのガスとしては、<sup>16</sup>O<sub>2</sub>もしくは<sup>18</sup>O<sub>2</sub>などの酸素ガス、亜酸化窒素ガスまたはオゾンガスなどを用いることができる。

20

## 【0214】

酸化物層510の水素濃度の増加を防ぐために、絶縁層521-529中の水素濃度を低減することが好ましい。特に絶縁層523-528の水素濃度を低減することが好ましい。具体的には、水素濃度は、 $2 \times 10^{20}$  atoms/cm<sup>3</sup>以下であり、好ましくは $5 \times 10^{19}$  atoms/cm<sup>3</sup>以下が好ましく、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下がより好ましく、 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下がさらに好ましい。

20

## 【0215】

酸化物層510の窒素濃度の増加を防ぐために、絶縁層523-518の窒素濃度を低減することが好ましい。具体的には、窒素濃度は、 $5 \times 10^{19}$  atoms/cm<sup>3</sup>未満であり、 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下が好ましく、 $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下がより好ましく、 $5 \times 10^{17}$  atoms/cm<sup>3</sup>以下がより好ましい。

30

## 【0216】

上掲の水素濃度、窒素濃度は、二次イオン質量分析法（SIMS：Secondary Ion Mass Spectrometry）で測定された値である。

## 【0217】

OSトランジスタ501において、酸素および水素に対してバリア性をもつ絶縁層（以下、バリア層）によって酸化物層510が包み込まれる構造であることが好ましい。このような構造であることで、酸化物層510から酸素が放出されること、酸化物層510に水素が侵入することを抑えることができるので、OSトランジスタ501の信頼性、電気特性を向上できる。

40

## 【0218】

例えば、絶縁層529をバリア層として機能させ、かつ絶縁層521、522、524の少なくとも1つをバリア層と機能させればよい。バリア層は、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム、窒化シリコンなどの材料で形成することができる。

## 【0219】

酸化物層510と導電層550の間に、バリア層をさらに設けてよい。もしくは、金属酸化物層513として、酸素および水素に対してバリア性をもつ金属酸化物層を設けてよい。

## 【0220】

50

絶縁層 524、絶縁層 525、絶縁層 526 の膜厚をそれぞれ薄くすることで、導電層 550 の電圧によるOSトランジスタのしきい値電圧の制御が容易になり、好ましい。例えば、絶縁層 524 - 526 の各膜厚は 50 nm 以下にする。各膜厚は 30 nm 以下が好ましく、10 nm 以下がより好ましく、5 nm 以下がさらに好ましい。

#### 【0221】

絶縁層 521 - 528 の構成例を記す。この例では、絶縁層 521、522、525、529 は、それぞれ、バリア層として機能する。絶縁層 526 - 528 は過剰酸素を含む酸化物層である。絶縁層 521 は窒化シリコンであり、絶縁層 522 は酸化アルミニウムであり、絶縁層 523 は酸化窒化シリコンである。バックゲート側のゲート絶縁層 (524 - 526) は、酸化シリコン、酸化アルミニウム、酸化シリコンの積層である。フロントゲート側のゲート絶縁層 (527) は、酸化窒化シリコンである。層間絶縁層 (528) は、酸化シリコンである。絶縁層 529 は酸化アルミニウムである。

10

#### 【0222】

##### (金属酸化物層)

金属酸化物層 511 - 513 の各厚さは 3 nm 以上 500 nm 以下であり、3 nm 以上 100 nm 以下が好ましく、3 nm 以上 60 nm 以下がさらに好ましい。

#### 【0223】

OSトランジスタ 501 のオフ電流の低減のために、金属酸化物層 512 は、例えば、エネルギーギャップが大きいことが好ましい。金属酸化物層 512 のエネルギーギャップは、2.5 eV 以上 4.2 eV 以下であり、2.8 eV 以上 3.8 eV 以下が好ましく、3 eV 以上 3.5 eV 以下がさらに好ましい。

20

#### 【0224】

酸化物層 510 は、結晶性金属酸化物層であることが好ましい。少なくとも、金属酸化物層 512 は結晶性金属酸化物層であることが好ましい。信頼性、および電気特性の良いOSトランジスタ 501 を実現できる。

#### 【0225】

金属酸化物層 512 に適用できる酸化物は、代表的には、In-Ga酸化物、In-Zn酸化物、In-M-Zn酸化物 (M は Al、Ga、Y、またはSn) である。金属酸化物層 512 は、インジウムを含む酸化物層に限定されない。金属酸化物層 512 は、例えば、Zn-Sn酸化物、Ga-Sn酸化物、Zn-Mg酸化物等で形成することができる。金属酸化物層 511、513 も、金属酸化物層 512 と同様の酸化物で形成することができる。金属酸化物層 511、513 は、それぞれ、Ga酸化物で形成することができる。この場合、金属酸化物層 512 は Ga を含む金属酸化物層であることが好ましい。

30

#### 【0226】

金属酸化物層 512 と金属酸化物層 511 の界面に界面準位が形成されると、界面近傍の領域にもチャネル領域が形成されるために、OSトランジスタ 501 のしきい値電圧が変動してしまう。そのため、金属酸化物層 511 は、構成要素として、金属酸化物層 512 を構成する金属元素の少なくとも 1 つを含むことが好ましい。これにより、金属酸化物層 512 と金属酸化物層 511 の界面には、界面準位が形成されにくくなり、OSトランジスタ 501 のしきい値電圧等の電気特性のばらつきを低減することができる。

40

#### 【0227】

金属酸化物層 513 は、構成要素として、金属酸化物層 512 を構成する金属元素の少なくとも 1 つを含むことが好ましい。これにより、金属酸化物層 512 と金属酸化物層 513 との界面では、界面散乱が起こりにくくなり、キャリアの動きが阻害されにくくなるので、OSトランジスタ 501 の電界効果移動度を高くすることができる。

#### 【0228】

金属酸化物層 511 - 513 のうち、金属酸化物層 512 のキャリア移動度が最も高いことが好ましい。これにより、絶縁層 526、527 から離間している金属酸化物層 512 にチャネルを形成することができる。

#### 【0229】

50

例えば、In - M - Zn 酸化物等のIn含有金属酸化物は、Inの含有率を高めることで、キャリア移動度を高めることができる。In - M - Zn 酸化物では、主として重金属のs軌道がキャリア伝導に寄与しており、インジウムの含有率を多くすることにより、より多くのs軌道が重なるため、インジウムの含有率が多い酸化物はインジウムの含有率が少ない酸化物と比較して移動度が高くなる。そのため、酸化物半導体膜にインジウムの含有量が多い酸化物を用いることで、キャリア移動度を高めることができる。

#### 【0230】

例えば、In - Ga - Zn 酸化物で金属酸化物層512を形成し、Ga酸化物で金属酸化物層511、513を形成する。例えば、In - M - Zn 酸化物で、金属酸化物層511 - 513を形成する場合、3層のうち、金属酸化物層511を最もIn含有率が高いIn - M - Zn 酸化物層とする。In - M - Zn 酸化物をスパッタリング法で形成する場合、ターゲットの金属元素の原子数比を変えることで、In含有率を変化させることができる。

10

#### 【0231】

例えば、金属酸化物層512の成膜に用いるターゲットの金属元素の原子数比In : M : Znは、1 : 1 : 1、3 : 1 : 2、または4 : 2 : 4 . 1が好ましい。例えば、金属酸化物層511、513の成膜に用いるターゲットの金属元素の原子数比In : M : Znは、1 : 3 : 2、または1 : 3 : 4が好ましい。In : M : Zn = 4 : 2 : 4 . 1のターゲットで成膜したIn - M - Zn 酸化物の原子数比は、およそIn : M : Zn = 4 : 2 : 3である。

20

#### 【0232】

OSトランジスタ501に安定した電気特性を付与するには、酸化物層510の不純物濃度を低減することが好ましい。金属酸化物において、水素、窒素、炭素、シリコン、および主成分以外の金属元素は不純物となる。例えば、水素および窒素はドナー準位の形成に寄与し、キャリア密度を増大させてしまう。また、シリコンおよび炭素は酸化物半導体中で不純物準位の形成に寄与する。不純物準位はトラップとなり、トランジスタの電気特性を劣化させることがある。

#### 【0233】

例えば、酸化物層510は、シリコン濃度が $2 \times 10^{18}$  atoms / cm<sup>3</sup>以下の、好ましくは、 $2 \times 10^{17}$  atoms / cm<sup>3</sup>以下の領域を有する。酸化物層510の炭素濃度も同様である。

30

#### 【0234】

酸化物層510は、アルカリ金属濃度が $1 \times 10^{18}$  atoms / cm<sup>3</sup>以下の、好ましくは $2 \times 10^{16}$  atoms / cm<sup>3</sup>以下の領域を有する。アルカリ土類金属の濃度についても同様である。

#### 【0235】

酸化物層510は、窒素濃度が $5 \times 10^{19}$  atoms / cm<sup>3</sup>未満の、好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup>以下の、より好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup>以下の、さらに好ましくは $5 \times 10^{17}$  atoms / cm<sup>3</sup>以下の領域を有する。

40

#### 【0236】

酸化物層510は、水素濃度が $1 \times 10^{20}$  atoms / cm<sup>3</sup>未満の、好ましくは $1 \times 10^{19}$  atoms / cm<sup>3</sup>未満の、より好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup>未満の、さらに好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup>未満の領域を有する。

#### 【0237】

上掲した酸化物層510の不純物濃度は、SIMSにより得られる値である。

#### 【0238】

金属酸化物層512が酸素欠損を有する場合、酸素欠損のサイトに水素が入り込むことでドナー準位を形成することができる。その結果、OSトランジスタ501のオン電流を減少させてしまう。酸素欠損のサイトは、水素が入るよりも酸素が入る方が安定する。したがって、金属酸化物層512中の酸素欠損を低減することで、OSトランジスタ501のオ

50

ン電流を大きくできる場合がある。よって、金属酸化物層 512 の水素を低減することで、酸素欠損のサイトに水素が入りこまないようにすることが、オン電流特性の向上に有効である。

【0239】

金属酸化物に含まれる水素は、金属原子に結合している酸素と反応して水になるため、酸素欠損を形成することがある。酸素欠損に水素が入ることで、キャリアである電子が生成されることがある。また、水素の一部が金属原子に結合している酸素と結合して、キャリアである電子を生成することがある。金属酸化物層 512 にチャネル形成領域が設けられるので、金属酸化物層 512 に水素が含まれていると、OSトランジスタ 501 はノーマリーオン特性となりやすい。このため、金属酸化物層 512 中の水素はできる限り低減されていることが好ましい。

10

【0240】

図 17 は、酸化物層 510 が 3 層構造の例であるが、これに限定されない。例えば、酸化物層 510 を金属酸化物層 511 または金属酸化物層 513 のない 2 層構造とすることができる。または、金属酸化物層 511 の上もしくは下、または金属酸化物層 513 上もしくは下に、金属酸化物層 511、金属酸化物層 512 および金属酸化物層 513 として示した酸化物半導体層のいずれか一を有する 4 層構造とすることもできる。または、酸化物層 510 の任意の層の間、酸化物層 510 の上、酸化物層 510 の下のいずれか二箇所以上に、金属酸化物層 511～513 と同様の金属酸化物層を 1 層または複数を設けることができる。

20

【0241】

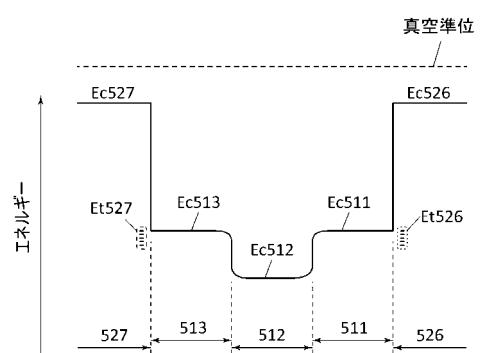

(エネルギー・バンド構造)

図 24 を参照して、金属酸化物層 511～513 の積層によって得られる効果を説明する。図 24 は、OSトランジスタ 501 のチャネル形成領域のエネルギー・バンド構造の模式図である。ここでは、OSトランジスタ 501 を例に説明するが、金属酸化物層 511～513 の積層による効果は、後述する OSトランジスタ 502、503 でも同様である。

【0242】

Ec526、Ec511、Ec512、Ec513、Ec527 は、それぞれ、絶縁層 526、金属酸化物層 511、金属酸化物層 512、金属酸化物層 513、絶縁層 527 の伝導帯下端のエネルギーを示している。

30

【0243】

ここで、真空準位と伝導帯下端のエネルギーとの差（「電子親和力」ともいう。）は、真空準位と価電子帯上端のエネルギーとの差（イオン化ポテンシャルともいう。）からエネルギー・ギャップを引いた値となる。なお、エネルギー・ギャップは、分光エリプソメータ（HORIBA JOBIN YVON社 UT-300）を用いて測定できる。また、真空準位と価電子帯上端のエネルギー差は、紫外線光電子分光分析（UPS：Ultraviolet Photoelectron Spectroscopy）装置（PHI社 Versa Probe）を用いて測定できる。

【0244】

絶縁層 526、527 は絶縁体であるため、Ec526 と Ec527 は、Ec511、Ec512、および Ec513 よりも真空準位に近い（電子親和力が小さい）。

40

【0245】

金属酸化物層 512 は、金属酸化物層 511、513 よりも電子親和力が大きい。例えば、金属酸化物層 512 と金属酸化物層 511 との電子親和力の差、および金属酸化物層 512 と金属酸化物層 513 との電子親和力の差は、それぞれ、0.07 eV 以上 1.3 eV 以下である。電子親和力の差は、0.1 eV 以上 0.7 eV 以下が好ましく、0.15 eV 以上 0.4 eV 以下がさらに好ましい。なお、電子親和力は、真空準位と伝導帯下端のエネルギーとの差である。

【0246】

OSトランジスタ 501 のゲート電極（導電層 550）に電圧を印加すると、金属酸化物

50

層 5 1 1、金属酸化物層 5 1 2、金属酸化物層 5 1 3 のうち、電子親和力が大きい金属酸化物層 5 1 2 に主にチャネルが形成される。

【 0 2 4 7 】

インジウムガリウム酸化物は、小さい電子親和力と、高い酸素ブロック性を有する。そのため、金属酸化物層 5 1 3 がインジウムガリウム酸化物を含むと好ましい。ガリウム原子割合 [  $Ga / (In + Ga)$  ] は、例えば、70%以上、好ましくは80%以上、さらに好ましくは90%以上とする。

【 0 2 4 8 】

また、金属酸化物層 5 1 1 と金属酸化物層 5 1 2 との間には金属酸化物層 5 1 1 と金属酸化物層 5 1 2 の混合領域が存在する場合がある。また、金属酸化物層 5 1 3 と金属酸化物層 5 1 2 との間には金属酸化物層 5 1 3 と金属酸化物層 5 1 2 の混合領域が存在する場合がある。混合領域は、界面準位密度が低くなるため、金属酸化物層 5 1 1 - 5 1 3 の積層体（酸化物層 5 1 0 ）は、それぞれの界面近傍においてエネルギーが連続的に変化する（連続接合ともいう。）バンド構造となる。

10

【 0 2 4 9 】

このようなエネルギー・バンド構造を有する酸化物層 5 1 0 において、電子は主に金属酸化物層 5 1 2 を移動することになる。そのため、金属酸化物層 5 1 1 と絶縁層 5 2 6 との界面に、または、金属酸化物層 5 1 3 と絶縁層 5 2 7 との界面に準位が存在したとしても、これらの界面準位により、酸化物層 5 1 0 中を移動する電子の移動が阻害されにくくなるため、OSトランジスタ 5 0 1 のオン電流を高くすることができる。

20

【 0 2 5 0 】

また、図 2 4 に示すように、金属酸化物層 5 1 1 と絶縁層 5 2 6 の界面近傍、および金属酸化物層 5 1 3 と絶縁層 5 2 7 の界面近傍には、それぞれ、不純物や欠陥に起因したトラップ準位  $E_{t526}$ 、 $E_{t527}$  が形成され得るもの、金属酸化物層 5 1 1、5 1 3 があることにより、金属酸化物層 5 1 2 をトラップ準位  $E_{t526}$ 、 $E_{t527}$  から離間することができる。

20

【 0 2 5 1 】

なお、 $E_{c511}$  と  $E_{c512}$  との差が小さい場合、金属酸化物層 5 1 2 の電子が該エネルギー差を越えてトラップ準位  $E_{t526}$  に達することがある。トラップ準位  $E_{t526}$  に電子が捕獲されることで、絶縁膜の界面にマイナスの固定電荷が生じ、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。 $E_{c512}$  と  $E_{c513}$  とのエネルギー差が小さい場合も同様である。

30

【 0 2 5 2 】

OSトランジスタ 5 0 1 のしきい値電圧の変動が低減され、OSトランジスタ 5 0 1 の電気特性を良好なものとするため、 $E_{c511}$  と  $E_{c512}$  との差、 $E_{c512}$  と  $E_{c513}$  との差は、それぞれ 0.1 eV 以上が好ましく、0.15 eV 以上がより好ましい。

30

【 0 2 5 3 】

<< OSトランジスタの構成例 2 >>

図 1 8 A - 図 1 8 C に示す OSトランジスタ 5 0 2 は、OSトランジスタ 5 0 1 の変形例である。OSトランジスタ 5 0 2 の導電層 5 5 0 は、導電層 5 5 0 a、導電層 5 5 0 b、導電層 5 5 0 c を有する。

40

【 0 2 5 4 】

導電層 5 5 0 a は、熱 CVD 法、MOCVD 法または ALD 法を用いて形成する。特に、原子層堆積 (ALD : A t o m i c L a y e r D e p o s i t i o n) 法を用いて形成することが好ましい。ALD 法等により形成することで、絶縁層 5 2 7 に対するプラズマによるダメージを減らすことができる。また、被覆性を向上させることができるために、導電層 5 5 0 a を ALD 法等により形成することが好ましい。従って、信頼性が高い OSトランジスタ 5 0 2 を提供することができる。

【 0 2 5 5 】

導電層 5 5 0 b は、タンタル、タンゲステン、銅、アルミニウムなどの導電性が高い材料

50

を用いて形成する。さらに、導電層 550b 上に形成する導電層 550c は、窒化タンゲステンなどの酸化しづらい導電体を用いて形成することが好ましい。絶縁層 528 に酸素が脱離する酸化物材料を用いる場合、導電層 550 が、脱離した酸素により酸化することを防止することができる。従って、導電層 550 の酸化を抑制し、絶縁層 528 から、脱離した酸素を効率的に酸化物層 510 へと供給することができる。

【0256】

過剰酸素領域を有する絶縁層 528 と接する面積が大きい導電層 550c に酸化しにくい導電体を用いることで、絶縁層 528 の過剰酸素が導電層 550 に吸収されることを抑制することができる。また、導電層 550b に導電性が高い導電体を用いることで、消費電力が小さい OS トランジスタ 502 を提供することができる。

10

【0257】

<< OS トランジスタの構成例 3 >>

図 19A - 図 19C に示す OS トランジスタ 503 は、OS トランジスタ 501 の変形例である。OS トランジスタ 503 では、導電層 550 をエッティングマスクに用いて、金属酸化物層 513 および絶縁層 527 がエッティングされている。

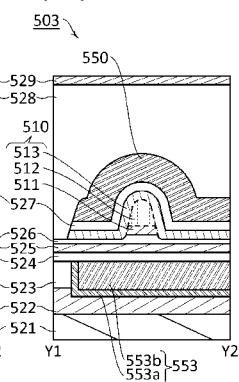

【0258】

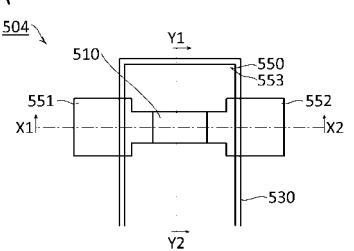

<< OS トランジスタの構成例 4 >>

図 20A - 図 20C に示す OS トランジスタ 504 は、OS トランジスタ 501 の変形例である。

20

【0259】

導電層 550 は導電層 550a と導電層 550b の 2 層構造である。導電層 550 は絶縁層 530 に覆われている。

【0260】

例えば、絶縁層 530 は、酸素に対してバリア性を有する絶縁層とする。これにより、絶縁層 528 等から離脱した酸素によって、導電層 550 が酸化することを抑制することができる。この場合、絶縁層 530 には、酸化アルミニウムなどの金属酸化物を用いることができる。絶縁層 530 の厚さは、導電層 550 の酸化を防止できる程度であればよく、例えば、1 nm 以上 10 nm 以下であり、好ましくは 3 nm 以上 7 nm 以下である。

【0261】

なお、OS トランジスタ 504 も、OS トランジスタ 503 と同様に、金属酸化物層 513 と絶縁層 527 を部分的に除去し、導電層 551、552 の上面の一部を露出させてもよい。あるいは、絶縁層 527 のみを部分的に除去してもよい。

30

【0262】

<< OS トランジスタの構成例 5 >>

図 21A - 図 21C に示す OS トランジスタ 505 は、OS トランジスタ 501 の変形例である。

【0263】

導電層 551 は導電層 551a と導電層 551b の 2 層構造であり、導電層 552 は導電層 552a と導電層 552b の 2 層構造である。

【0264】

導電層 551、552 において、導電層 551a、552a は金属酸化物層 512 との密着性が高い導電膜で形成することが好ましい。この導電膜を A L D 法で成膜することは、被覆性を向上させることができるので、好ましい。導電層 551b、552b は、導電層 551a、552a よりも高い導電率をもつ導電体で形成することが好ましい。導電層 551a、552a を設けることで、導電層 551b、552b に用いることのできる導電体材料の制約が小さくなる。導電層 551a、552a に、タンタル、タンゲステン、銅、アルミニウムなどの導電性が高い材料を用いることで、OS トランジスタ 505 で構成される回路の消費電力を低減できる。

40

【0265】

<< OS トランジスタの構成例 6 >>

50

図22A - 図22Cに示すOSトランジスタ506は、OSトランジスタ501の変形例であり、主に、ゲート電極の構造が異なる。

【0266】

絶縁層528に形成された開口部には、金属酸化物層513、絶縁層527、導電層550が設けられている。つまり、絶縁層528の開口部を利用して、ゲート電極を自己整合的に形成することができる。よって、OSトランジスタ506では、ゲート電極(550)は、ゲート絶縁層(527)を介してソース電極およびドレイン電極(551、552)と重なる領域を有していない。そのためゲート-ソース間の寄生容量、ゲート-ドレイン間の寄生容量が低減でき、周波特性を向上できる。また、絶縁層528の開口部によってゲート電極幅を制御できるため、チャネル長の短いOSトランジスタの作製が容易である。

10

【0267】

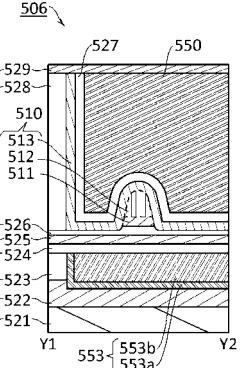

<<OSトランジスタの構成例7>>

図23A - 図23Cに示すOSトランジスタ507は、OSトランジスタ506の変形例である。

【0268】

酸化物層510は、さらに金属酸化物層514を有する。金属酸化物層514は、金属酸化物層511、512、導電層551、552を覆っている。

【0269】

金属酸化物層514によって、金属酸化物層512は絶縁層528から離間される。酸化物層510において、金属酸化物層512に主にチャネルが形成されるため、金属酸化物層512が絶縁層528と接している領域が存在しないようにすることで、チャネル近傍に浅い準位が生じることが抑制できる。よって、OSトランジスタ507の信頼性を向上できる。

20

【0270】

<<半導体装置の構成例>>

図25、図26を参照して、OSトランジスタとSiトランジスタとで構成されている半導体装置の構成例を説明する。

【0271】

図25、図26は、MCU100(図1)の積層構造を説明するための断面図である。図25にはMCU100に搭載されているNOSRAM120の要部を示す。

30

【0272】

MCU100は、CMOS層570、配線層W<sub>1</sub> - W<sub>5</sub>、OSFET層571、配線層W<sub>6</sub>、W<sub>7</sub>の積層で構成されている。

【0273】

CMOS層570には、MCU100を構成するSiトランジスタが設けられている。Siトランジスタの活性層は単結晶シリコンウェハ560に設けられている。

【0274】

OSFET層571には、MCU100のOSトランジスタが設けられている。OSFET層571には、NOSRAM120のメモリセル135のOSトランジスタが設けられる。図25には、メモリセル135を代表的に示している。なお、図25において、トランジスタMW1はバックゲートを有するOSトランジスタであり、OSトランジスタ503(図19A - 図19C)と同様の構造を有する。このバックゲート電極は、配線層W<sub>5</sub>に設けられている。配線層W<sub>6</sub>には、容量素子CS1が設けられている。

40

【0275】

図26は、OSFET層571に、OSトランジスタ504(図20A - 図20C)と同様の構造を有するトランジスタを設けた例を示している。図26は、図25と同様に、MCU100の要部を示す図である。

【0276】

[実施の形態6]

50

本実施の形態では、酸化物半導体について説明する。酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体と、に分けられる。非単結晶酸化物半導体としては、CAAC-OS (c-axis-aligned crystalline oxide semiconductor)、多結晶酸化物半導体、nc-OS (nanocrystalline oxide semiconductor)、擬似非晶質酸化物半導体 (a-like OS: amorphous-like oxide semiconductor) および非晶質酸化物半導体などがある。

#### 【0277】

また別の観点では、酸化物半導体は、非晶質酸化物半導体と、それ以外の結晶性酸化物半導体と、に分けられる。結晶性酸化物半導体としては、単結晶酸化物半導体、CAAC-OS、多結晶酸化物半導体およびnc-OSなどがある。

10

#### 【0278】

非晶質構造は、一般に、等方的であって不均質構造を持たない、準安定状態で原子の配置が固定化していない、結合角度が柔軟である、短距離秩序は有するが長距離秩序を有さない、などといわれている。

#### 【0279】

即ち、安定な酸化物半導体を完全な非晶質 (completely amorphous) 酸化物半導体とは呼べない。また、等方的でない (例えば、微小な領域において周期構造を有する) 酸化物半導体を、完全な非晶質酸化物半導体とは呼べない。一方、a-like OSは、等方的でないが、鬆 (ボイドともいう。) を有する不安定な構造である。不安定であるという点では、a-like OSは、物性的に非晶質酸化物半導体に近い。

20

#### 【0280】

(CAAC-OS)

CAAC-OSは、c軸配向した複数の結晶部 (ペレットともいう。) を有する酸化物半導体の一種である。

#### 【0281】

CAAC-OSは、c軸配向性を有し、かつa-b面方向において複数の結晶部 (ナノ結晶) が連結し、歪みを有した結晶構造となっている。結晶部一つの大きさは1nm以上、または3nm以上である。よって、CAAC-OSの結晶部をナノ結晶と称することができ、CAAC-OSを、CAAC-crystal (c-axis-aligned a-b-plane-anchored crystal) を有する酸化物半導体と称することもできる。

30

#### 【0282】

CAAC-OSは結晶性の高い酸化物半導体である。酸化物半導体の結晶性は不純物の混入や欠陥の生成などによって低下する場合があるため、CAAC-OSは不純物や欠陥 (酸素欠損など) の少ない酸化物半導体ともいえる。

#### 【0283】

不純物は、酸化物半導体の主成分以外の元素で、水素、炭素、シリコン、遷移金属元素などがある。例えば、シリコンなどの、酸化物半導体を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体から酸素を奪うことで酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径 (または分子半径) が大きいため、酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。

40

#### 【0284】

酸化物半導体が不純物や欠陥を有する場合、光や熱などによって特性が変動する場合がある。例えば、酸化物半導体に含まれる不純物は、キャリアトラップとなる場合や、キャリア発生源となる場合がある。例えば、酸化物半導体中の酸素欠損は、キャリアトラップとなる場合や、水素を捕獲することによってキャリア発生源となる場合がある。

#### 【0285】

50

## (n c - O S)

n c - O S は、微小な領域（例えば、1 nm 以上 10 nm 以下の領域、特に 1 nm 以上 3 nm 以下の領域）において原子配列に周期性を有する。n c - O S は、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。結晶部（ナノ結晶）間で結晶方位が規則性を有さないことから、n c - O S を、R A N C (R a n d o m A l i g n e d n a n o c r y s t a l s) を有する酸化物半導体、またはN A N C (N o n - A l i g n e d n a n o c r y s t a l s) を有する酸化物半導体と呼ぶこともできる。

## 【0286】

n c - O S の結晶は配向性を有さないので、n c - O S は、分析方法によっては、a - l i k e O S や非晶質酸化物半導体と区別が付かない場合がある。

## 【0287】

なお、a - l i k e O S は、n c - O S およびC A A C - O S と比べて密度の低い構造である。具体的には、a - l i k e O S の密度は、同じ組成の単結晶の密度の 78.6 % 以上 92.3 % 未満である。また、n c - O S の密度およびC A A C - O S の密度は、同じ組成の単結晶の密度の 92.3 % 以上 100 % 未満である。単結晶の密度の 78 % 未満である酸化物半導体は、成膜すること自体が困難である。

## 【0288】

例えば、In : Ga : Zn = 1 : 1 : 1 [原子数比] を満たす酸化物半導体において、菱面体晶構造を有する単結晶InGaZnO<sub>4</sub>の密度は 6.357 g / cm<sup>3</sup> である。よって、例えば、In : Ga : Zn = 1 : 1 : 1 [原子数比] を満たす酸化物半導体において、a - l i k e O S の密度は 5.0 g / cm<sup>3</sup> 以上 5.9 g / cm<sup>3</sup> 未満である。また、例えば、In : Ga : Zn = 1 : 1 : 1 [原子数比] を満たす酸化物半導体において、n c - O S の密度およびC A A C - O S の密度は 5.9 g / cm<sup>3</sup> 以上 6.3 g / cm<sup>3</sup> 未満である。

## 【0289】

なお、同じ組成の単結晶が存在しない場合、任意の割合で組成の異なる単結晶を組み合わせることにより、所望の組成における単結晶に相当する密度を見積もることができる。所望の組成の単結晶に相当する密度は、組成の異なる単結晶を組み合わせる割合に対して、加重平均を用いて見積もればよい。ただし、密度は、可能な限り少ない種類の単結晶を組み合わせて見積もることが好ましい。

## 【0290】

以上のように、酸化物半導体は、様々な構造をとり、それぞれが様々な特性を有する。なお、酸化物半導体は、例えば、非晶質酸化物半導体、a - l i k e O S、n c - O S、C A A C - O S のうち、二種以上を有する積層膜であってもよい。酸化物半導体の構造は、X線回折(X R D)、ナノビーム電子回折、T E M(透過型電子顕微鏡)観察などによって、特定することができる。

## 【0291】

## &lt;酸化物半導体のキャリア密度&gt;

次に、酸化物半導体のキャリア密度について説明する。酸化物半導体のキャリア密度に影響を与える因子としては、酸化物半導体中の酸素欠損(V<sub>o</sub>)、または酸化物半導体中の不純物などが挙げられる。

## 【0292】

酸化物半導体中の酸素欠損が多くなると、該酸素欠損に水素が結合（この状態をV<sub>oH</sub>ともいう）した際に、欠陥準位密度が高くなる。または、酸化物半導体中の不純物が多くなると、該不純物に起因し欠陥準位密度が高くなる。したがって、酸化物半導体中の欠陥準位密度を制御することで、酸化物半導体のキャリア密度を制御することができる。

## 【0293】

O Sトランジスタにおいて、V<sub>t</sub>のマイナスシフトを抑制する、またはオフ電流を低減するためには、酸化物半導体のキャリア密度が低い方が好ましい。酸化物半導体のキャリア

10

20

30

40

50

密度を低くするには、酸化物半導体中の不純物濃度を低くして、欠陥準位密度を低くすればよい。本明細書等において、不純物濃度が低く、欠陥準位密度の低いことを高純度真性または実質的に高純度真性と言う。

【0294】

OSトランジスタにおいて、オン電流の増加、電界効果移動度の増加のためには、酸化物半導体のキャリア密度を高くする方が好ましい場合がある。酸化物半導体の不純物濃度をわずかに高める、または酸化物半導体の欠陥準位密度をわずかに高めることで、酸化物半導体のキャリア密度を高くすることができる。例えば、OSトランジスタのオフ電流に対するオン電流比( $I_{on}/I_{off}$ )がとれる範囲において、不純物濃度がわずかに高い、または欠陥準位密度がわずかに高い酸化物半導体は、実質的に真性とみなせる。

10

【0295】

また、電子親和力が大きく、それにともなってバンドギャップが小さくなり、その結果、熱励起された電子(キャリア)の密度が増加した酸化物半導体は、実質的に真性とみなせる。なお、電子親和力がより大きな酸化物半導体を用いた場合には、OSトランジスタの $V_t$ はより低くなる。

【0296】

キャリア密度が高められた酸化物半導体は、わずかにn型化している。したがって、キャリア密度が高められた酸化物半導体を、「Slight - n」型の酸化物半導体と呼称してもよい。

【0297】

高純度真性の酸化物半導体のキャリア密度は、例えば、 $8 \times 10^{15} \text{ cm}^{-3}$ 未満であり、好ましくは $1 \times 10^{11} \text{ cm}^{-3}$ 未満が好ましく、 $1 \times 10^{10} \text{ cm}^{-3}$ 未満がさらに好ましく、 $1 \times 10^{-9} \text{ cm}^{-3}$ 以上であるとよい。

20

【0298】

実質的に高純度真性の酸化物半導体のキャリア密度は、例えば、 $1 \times 10^{15} \text{ cm}^{-3}$ 以上 $1 \times 10^{18} \text{ cm}^{-3}$ 未満であり、 $1 \times 10^{17} \text{ cm}^{-3}$ 以上 $1 \times 10^{17} \text{ cm}^{-3}$ 以下が好ましく、 $1 \times 10^{19} \text{ cm}^{-3}$ 以上 $5 \times 10^{16} \text{ cm}^{-3}$ 以下がより好ましく、 $1 \times 10^{10} \text{ cm}^{-3}$ 以上 $1 \times 10^{16} \text{ cm}^{-3}$ 以下がさらに好ましく、 $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{15} \text{ cm}^{-3}$ 以下がさらに好ましい。

【符号の説明】

30

【0299】

30、31、32、33：メモリセル、60：SA(センスアンプ)、61、62：TG(トランスファゲート)、65：AND回路、75：ラッチ回路、77：回路、78：スイッチ、

100、102：MCU(マイクロコントローラユニット)、110、150：バス、111、151：プロセッサコア、112、152：メモリ部、115、155：クロック生成回路、116、156：周辺回路、120、170：NOSRAM、121、171：メモリ、131、181：制御部、132、182：ドライバ部、133、183：セルアレイ、135、185：メモリセル、161：設定用レジ

40

スタ、162：クロック生成部、163：ロジック部、

300：NOSRAM、311：コントロール部、312：ドライバ部、313：セルアレイ、314：出力回路、320：行ドライバ、321：行デコーダ、322：読み出しワード線ドライバ、323：書き込みワード線ドライバ、324：ブレ

40

コーダ、325：列デコーダ、330：列ドライバ、331：プリチャージ回路、332：センスアンプ、333：出力MUX(マルチプレクサ)、334：書き込みドライバ、335：ソース線ドライバ、340：回路、341、342、343

50

、344、345、346、347、348：バッファ、349：インバータ、351、352：ブロック、

501、502、503、504、505、506、507：OSトランジスタ、

510：酸化物層、511、512、513、514：金属酸化物層、

50

521、522、523、524、525、526、527、528、529、530：

絶縁層、

550、550a、550b、550c、551、551a、551b、552、552a、552b、553、553a、553b：導電層、

560：単結晶シリコンウエハ、570：CMOS層、571：OSFET層、

2010：情報端末、2011：筐体、2012：表示部、2013：操作ボタン、

、2014：外部接続ポート、2015：スピーカ、2016：マイクロフォン、

2050：ノート型PC（パーソナルコンピュータ）、2051：筐体、2052

：表示部、2053：キーボード、2054：ポインティングデバイス、2070：

ビデオカメラ、2071：筐体、2072：表示部、2073：筐体、2074

：操作キー、2075：レンズ、2076：接続部、2110：携帯型遊技機、

2111：筐体、2112：表示部、2113：スピーカ、2114：LEDランプ、

、2115：操作キー、2116：接続端子、2117：カメラ、211

8：マイクロフォン、2119：記録媒体読込部、2150：電気冷凍冷蔵庫、2

151：筐体、2152：冷蔵室用扉、2153：冷凍室用扉、2170：自動車、

、2171：車体、2172：車輪、2173：ダッシュボード、2174：ライト、

7000：電子部品、7001：リード、7002：プリント基板、7004：回路基板、7100：半導体ウエハ、7102：回路領域、7104：分離領域、

7106：分離線、7110：チップ、

a1、a2、a3、a4、a5、Q2、QB2、SN1、SN2、SN3、SN5、SN6：ノード、

CS1、CS2、CS3、CS5、CS6：容量素子、

MR1、MR2、MR3、MR4、MR5、MR6、MR7、MW1、MW2、MW3、

MW5、MW6、T60、T61、T62、T65、T66、T67、T68、T69：トランジスタ、

BL、BGL、GRBL、GWL、RBL、RWL、RCL、SL、WBL、WWL：配線

【図1】

【図2】

FIG. 2B

【図3】

【図4】

【図5】

FIG. 5A

FIG. 5B

FIG. 5C

【図6】

FIG. 6A

FIG. 6B

【図7】

【図8】

【 図 9 】

FIG. 9A

FIG. 9B

【 図 1 1 】

FIG. 11

【 図 1 0 】

FIG. 10A

FIG. 10B

FIG. 10C

FIG. 10D

FIG. 10E

## 【図 13】

FIG. 13

## 【図 14】

FIG. 14A

FIG. 14B

## 【図 15】

FIG. 15A

FIG. 15B

FIG. 15C

FIG. 15D

FIG. 15E

## 【図 16】

FIG. 16A

FIG. 16B

FIG. 16C

FIG. 16D

FIG. 16E

FIG. 16F

【図 17】

FIG. 17A

FIG. 17B

FIG. 17C

【図 18】

FIG. 18A

FIG. 18B

FIG. 18C

【図 19】

FIG. 19A

FIG. 19B

FIG. 19C

【図 20】

FIG. 20A

FIG. 20B

FIG. 20C

【図 2 1】

FIG. 21A

FIG. 21B

FIG. 21C

【図 2 2】

FIG. 22A

FIG. 22B

FIG. 22C

【図 2 3】

FIG. 23A

FIG. 23B

FIG. 23C

【図 2 4】

FIG. 24

【図25】

FIG. 25

金属酸化物層

導電層

絶縁層

【図26】

FIG. 26

金属酸化物層

導電層

絶縁層