(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-209931

(P2005-209931A)

(43) 公開日 平成17年8月4日(2005.8.4)

(51) Int.Cl.<sup>7</sup>

H01L 21/8247

H01L 27/115

H01L 29/788

H01L 29/792

F 1

H01L 29/78 371

H01L 27/10 434

テーマコード(参考)

5FO83

5F1O1

審査請求 未請求 請求項の数 13 O L (全 17 頁)

(21) 出願番号

特願2004-15703 (P2004-15703)

(22) 出願日

平成16年1月23日 (2004.1.23)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 金光 賢司

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

(72) 発明者 森山 卓史

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

(72) 発明者 細田 直宏

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】不揮発性半導体記憶装置およびその製造方法

## (57) 【要約】

【課題】 不揮発性半導体記憶装置の製造歩留まり、信頼性を向上させる。

【解決手段】 半導体基板のp型ウエルに形成されたn型半導体領域(ソース、ドレイン)と3つのゲート(浮遊ゲート、制御ゲートおよび選択ゲート5)によってメモリセルを構成するAND型フラッシュメモリの製造に際し、選択ゲート5の一方の側壁近傍のp型ウエル3にヒ素(As)を導入してn型半導体領域(ソース、ドレイン)7を形成した後、ドレンインディスターブ対策として、n型半導体領域7が形成されている方の側壁の近傍に位置する第1ゲート絶縁膜4の膜厚を厚く形成するために、ISSG(In-Situ Steam Generation)酸化法を用いて基板1を熱処理する。

【選択図】 図6

**【特許請求の範囲】****【請求項 1】**

第1導電型の半導体基板の主面上に酸化シリコンを主体とする第1絶縁膜を介して形成された第1ゲートと、

前記第1ゲートの側壁に形成された第2絶縁膜からなるサイドウォールスペーサと、

前記半導体基板に形成された第2導電型の半導体領域からなるソース、ドレインと、

前記サイドウォールスペーサを覆うように形成され、その一部が前記第1絶縁膜によつて前記ソース、ドレインと絶縁された第2ゲートと、

前記第2ゲート上に形成され、第3絶縁膜を介して前記第2ゲートと絶縁された第3ゲートとで構成された複数のメモリセルが前記半導体基板の正面にマトリクス配置され、10

前記第3ゲートは、前記半導体基板の正面の第1方向に延在してワード線を構成し、

前記ソース、ドレインは、前記半導体基板の正面の前記第1方向と交差する第2方向に延在してビット線を構成している不揮発性半導体記憶装置。10

**【請求項 2】**

請求項1記載の不揮発性半導体記憶装置において、前記ソース、ドレインは、前記第1ゲートの一方の側壁下部に形成され、前記ワード線の延在方向に隣接する2個のメモリセルによって共有されていることを特徴とする不揮発性半導体記憶装置。

**【請求項 3】**

請求項1記載の不揮発性半導体記憶装置において、前記メモリセルへの情報の書き込みは、前記第1ゲートの下部のチャネル領域で発生するホットエレクトロンを前記第1絶縁膜を通じて前記第2ゲートに注入することにより行われることを特徴とする不揮発性半導体記憶装置。20

**【請求項 4】**

以下の工程を含む不揮発性半導体記憶装置の製造方法：

(a) 第1導電型の半導体基板の主面上に酸化シリコンを主体とする第1絶縁膜を形成した後、前記第1絶縁膜上に形成した第1導電膜をパターニングすることによって、前記半導体基板の正面の第1方向に延在する複数の第1ゲートを形成する工程、30

(b) 前記第1ゲートのそれぞれの一方の側壁近傍の前記半導体基板に斜めイオン注入法を用いて不純物を導入することにより、第2導電型の半導体領域からなるソース、ドレインを形成する工程、

(c) 前記工程(b)の後、ISSG酸化法を用いて前記半導体基板を熱処理することにより、前記第1ゲートのそれぞれの側壁の近傍を含む前記第1ゲート同士の間の前記第1絶縁膜を厚膜化する工程、30

(d) 前記工程(c)の後、前記半導体基板上に形成した第2絶縁膜を異方性エッチングすることにより、前記第1ゲートのそれぞれの側壁に、前記第2絶縁膜からなるサイドウォールスペーサを形成する工程、

(e) 前記工程(d)の後、前記半導体基板上に形成した第2導電膜をパターニングすることにより、前記第1ゲート同士の間に前記第2導電膜からなる第2ゲートを形成する工程。40

**【請求項 5】**

請求項4記載の不揮発性半導体記憶装置の製造方法において、前記工程(d)の後、前記工程(e)に先立って、前記工程(d)の異方性エッチングで削られた前記第1絶縁膜を再生するために、ISSG酸化法を用いて前記半導体基板を熱処理する工程をさらに含むことを特徴とする不揮発性半導体記憶装置の製造方法。

**【請求項 6】**

請求項4記載の不揮発性半導体記憶装置の製造方法において、前記工程(e)の後、

(f) 前記第2ゲート上に第3絶縁膜を形成し、前記第3絶縁膜上に第3導電膜を形成した後、前記第3導電膜をパターニングすることにより、前記半導体基板の正面の前記第1方向と交差する第2方向に延在する複数の第3ゲートを形成する工程、

をさらに含むことを特徴とする不揮発性半導体記憶装置の製造方法。50

**【請求項 7】**

請求項 4 記載の不揮発性半導体記憶装置の製造方法において、前記工程 ( b ) で前記半導体基板に導入する前記不純物は、ヒ素であることを特徴とする不揮発性半導体記憶装置の製造方法。

**【請求項 8】**

請求項 4 記載の不揮発性半導体記憶装置の製造方法において、前記工程 ( b ) で前記半導体基板に前記不純物を導入する際、斜めイオン注入法を用いることを特徴とする不揮発性半導体記憶装置の製造方法。

**【請求項 9】**

請求項 6 記載の不揮発性半導体記憶装置の製造方法において、前記第 1 、第 2 および第 3 ゲートと、前記ソース、ドレインと、前記第 1 絶縁膜と前記第 3 絶縁膜とによってメモリセルが構成され、

10

前記第 3 ゲートは、前記半導体基板の正面の第 1 方向に延在してワード線を構成し、

前記ソース、ドレインは、前記半導体基板の正面の前記第 1 方向と交差する第 2 方向に

延在してピット線を構成していることを特徴とする不揮発性半導体記憶装置の製造方法。

**【請求項 10】**

請求項 9 記載の不揮発性半導体記憶装置の製造方法において、前記ソース、ドレインは、

前記第 1 ゲートの一方の側壁下部に形成され、前記ワード線の延在方向に隣接する 2 個

のメモリセルによって共有されていることを特徴とする不揮発性半導体記憶装置の製造方

法。

20

**【請求項 11】**

請求項 9 記載の不揮発性半導体記憶装置の製造方法において、前記メモリセルへの情報

の書き込みは、前記第 1 ゲートの下部のチャネル領域で発生するホットエレクトロンを前

記第 1 絶縁膜を通じて前記第 2 ゲートに注入することにより行われることを特徴とする不

揮発性半導体記憶装置の製造方法。

**【請求項 12】**

以下の工程を含む不揮発性半導体記憶装置の製造方法：

( a ) 第 1 導電型の半導体基板上に第 1 絶縁膜を介して第 1 導電体片を形成する工程、

( b ) I S S G 酸化法により、前記第 1 導電体片の側壁及び前記半導体基板上に第 2 絶縁

膜を形成する工程、

30

( c ) 前記工程 ( b ) 後、前記第 1 導電体片を覆うように第 3 絶縁膜を形成する工程、

( d ) 前記第 2 および第 3 絶縁膜をエッチングすることにより、前記第 1 導電体片の側壁

に、サイドウォールスペーサを形成する工程、

( e ) 前記工程 ( d ) の後、I S S G 酸化法により、前記半導体基板上に第 4 絶縁膜を形

成する工程、

( f ) 前記工程 ( e ) の後、前記第 4 絶縁膜上および前記サイドウォールの側壁に第 2 導

電体片を形成する工程。

40

**【請求項 13】**

請求項 12 記載の不揮発性半導体記憶装置の製造方法において、

( g ) 前記工程 ( f ) の後、前記第 2 導電体片上に第 5 絶縁膜を形成する工程、

( h ) 前記第 5 絶縁膜上に第 3 導電体片を形成する工程、

をさらに含むことを特徴とする不揮発性半導体記憶装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、不揮発性半導体記憶装置およびその製造技術に関し、特に、不揮発性半導体

記憶装置の製造歩留まり、信頼性の向上に適用して有効な技術に関するものである。

**【背景技術】****【0002】**

10

20

30

40

50

携帯性に優れたデータ格納用メモリとして、半導体不揮発性メモリであるフラッシュメモリが広く用いられている。

#### 【0003】

フラッシュメモリのメモリアレイ方式には、代表的なものとしてメモリセルが直列に接続されたNAND型と並列に接続されたAND型とがあり、特に後者は、ホットエレクトロン書き込み方式を採用しているので、書き込みが高速である。加えて、メモリアレイ構成が並列接続であり、NAND型のように直列接続でないために、他のメモリセルの記憶情報の影響を受け難いという特徴を持っている。

#### 【0004】

AND型フラッシュメモリについては、特開2001-156275号公報（特許文献1参照）に開示されている。この公報に記載されたメモリセルは、半導体基板上にスイッチゲート電極を備えた選択トランジスタ部を有し、その両側に離散的にトラップを含むゲート絶縁膜とメモリゲート電極とを持つメモリセルトランジスタ部が形成され、その外側にソース線／ビット線に接続される拡散層が形成されている。

#### 【0005】

特開2001-28428号公報（特許文献2参照）は、半導体基板のp型ウエルに形成したn型半導体領域（ソース、ドレイン）と3つのゲートによってメモリセルを構成した仮想接地型のAND型フラッシュメモリを開示している。

#### 【特許文献1】特開2001-156275号公報

#### 【特許文献2】特開2001-28428号公報

10

20

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0006】

本発明者らが開発中のAND型フラッシュメモリは、半導体基板のp型ウエルに形成したn型半導体領域（ソース、ドレイン）と3つのゲートによってメモリセルを構成している。メモリセルを構成する3つのゲートは、浮遊ゲート、制御ゲートおよび選択ゲートである。選択ゲートは、第1ゲート絶縁膜（トンネル酸化膜）を介してp型ウエル上に形成され、浮遊ゲートは、隣接する2つの選択ゲートの間に形成され、第1ゲート絶縁膜を介してp型ウエルと絶縁される。浮遊ゲートと選択ゲートとは選択ゲートの側壁の絶縁膜により絶縁され、浮遊ゲートとその上部に形成される制御ゲートは、第2ゲート絶縁膜により絶縁される。制御ゲートは行方向に延在し、ワード線を構成している。選択ゲートは、ワード線に直交する列方向に延在する。n型半導体領域（ソース、ドレイン）は、選択ゲートの一方の側壁下部のp型ウエルに形成され、ワード線に直交する列方向に延在してローカルビット線を構成している。

30

#### 【0007】

上記メモリセルへの情報の書き込みは、選択されたメモリセルのワード線に15V（他のワード線は0V）、選択ゲートに1.2V（他の選択ゲートは0V）、n型半導体領域（ソース）に0V、同一ワード線に接続された隣接メモリセルのn型半導体領域（ドレイン）に4.5Vをそれぞれ印加し、ソースからドレインに流れる電子の一部（ホットエレクトロン）を第1ゲート絶縁膜（トンネル酸化膜）を通じて浮遊ゲートに注入する。

40

#### 【0008】

上記メモリセルは、微細化を進めた場合、浮遊ゲートとn型半導体領域との距離が非常に接近するようになる。そのため、浮遊ゲートに注入された電子が、書き込み時に4.5Vの電圧が印加される非選択メモリセルのn型半導体領域（ドレイン）に抜け、いわゆるドレインディスターク現象が発生し易くなるという問題がある。

#### 【0009】

そこで、本発明者らは、製造プロセス上の工夫により、n型半導体領域上の第1ゲート絶縁膜を局所的に厚膜化して電界を緩和し、浮遊ゲートからn型半導体領域（ドレイン）への電子の抜けを防ぐ対策を講じた。これは、半導体基板を熱酸化してその表面に酸化膜を形成する際、ヒ素（As）が高濃度にイオン注入されたn型半導体領域の表面は、増速

50

酸化が生じ易いために酸化膜の成長が促進されることを利用したものである。

【0010】

このように、ドレンインディスターブ対策として、n型半導体領域上の第1ゲート絶縁膜を局所的に厚膜化した場合には、選択ゲートの側壁近傍に位置する第1ゲート絶縁膜の膜厚が選択ゲートの左右両側で異なってくる。そのため、第1ゲート絶縁膜の一部を厚膜化した後の製造プロセスで半導体基板の表面をエッティングした際、第1ゲート絶縁膜の膜厚にはらつきが生じ、メモリセルの特性が変動し易くなるという問題が見出された。

【0011】

本発明の目的は、不揮発性半導体記憶装置の製造歩留まり、信頼性を向上させる技術を提供することにある。

10

【0012】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0013】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0014】

本発明の不揮発性半導体記憶装置は、第1導電型の半導体基板の主面上に酸化シリコンを主体とする第1絶縁膜を介して形成された第1ゲートと、前記第1ゲートの側壁に形成された第2絶縁膜からなるサイドウォールスペーサと、前記半導体基板に形成された第2導電型の半導体領域からなるソース、ドレンと、前記サイドウォールスペーサを覆うように形成され、その一部が前記第1絶縁膜によって前記ソース、ドレンと絶縁された第2ゲートと、前記第2ゲート上に形成され、第3絶縁膜を介して前記第2ゲートと絶縁された第3ゲートとで構成された複数のメモリセルが前記半導体基板の正面にマトリクス配置され、前記第3ゲートは、前記半導体基板の正面の第1方向に延在してワード線を構成し、前記ソース、ドレンは、前記半導体基板の正面の前記第1方向と交差する第2方向に延在してピット線を構成しているものである。

20

【0015】

本発明の不揮発性半導体記憶装置の製造方法は、以下の工程を含んでいる。

30

(a) 第1導電型の半導体基板の主面上に酸化シリコンを主体とする第1絶縁膜を形成した後、前記第1絶縁膜上に形成した第1導電膜をパターニングすることによって、前記半導体基板の正面の第1方向に延在する複数の第1ゲートを形成する工程、

(b) 前記第1ゲートのそれぞれの一方の側壁近傍の前記半導体基板に斜めイオン注入法を用いて不純物を導入することにより、第2導電型の半導体領域からなるソース、ドレンを形成する工程、

(c) 前記工程(b)の後、ISSG酸化法を用いて前記半導体基板を熱処理することにより、前記第1ゲートのそれぞれの側壁の近傍を含む前記第1ゲート同士の間の前記第1絶縁膜を厚膜化する工程、

(d) 前記工程(c)の後、前記半導体基板上に形成した第2絶縁膜を異方性エッティングすることにより、前記第1ゲートのそれぞれの側壁に、前記第2絶縁膜からなるサイドウォールスペーサを形成する工程、

40

(e) 前記工程(d)の後、前記半導体基板上に形成した第2導電膜をパターニングすることにより、前記第1ゲート同士の間に前記第2導電膜からなる第2ゲートを形成する工程。

【発明の効果】

【0016】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0017】

50

不揮発性半導体記憶装置の製造歩留まりおよび信頼性を向上させることができる。

【発明を実施するための最良の形態】

【0018】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

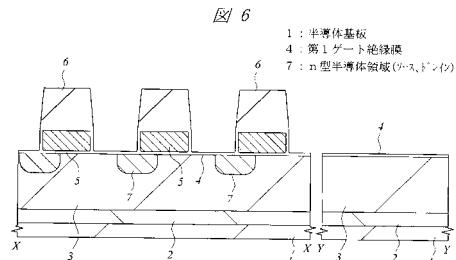

【0019】

(実施の形態1)

図1は、本実施の形態のAND型フラッシュメモリを示す回路図である。AND型フラッシュメモリのメモリセルは、半導体基板のメモリアレイ部MMにマトリクス配置される。後述するように、メモリセルは、半導体基板のp型ウエルに形成されたn型半導体領域(ソース、ドレイン)と3つのゲートによって構成されている。メモリセルを構成する3つのゲートは、浮遊ゲート、制御ゲートおよび選択ゲートである。制御ゲートは行方向に延在し、ワード線WL(WL0、WL1…WL<sub>n</sub>)を構成している。選択ゲートは、ワード線WLに直交する列方向に延在する。n型半導体領域(ソース、ドレイン)は、ワード線WLに直交する列方向に延在してローカルビット線BLを構成している。ローカルビット線BLは、互いに隣接する2本が1本のグローバルビット線G<sub>BL</sub>に接続され、選択トランジスタSTによっていずれか一本が選択される。n型半導体領域(ソース、ドレイン)は、行方向のピッチの縮小を図るために、隣接するメモリセルによって共用されている。

10

20

30

【0020】

メモリセルへの情報の書き込みは、選択されたメモリセルのワード線に15V(他のワード線は0V)、選択ゲートに1.2V(他の選択ゲートは0V)、n型半導体領域(ソース)に0V、同一ワード線に接続された隣接メモリセルのn型半導体領域(ドレイン)に4.5Vをそれぞれ印加し、ソースからドレインに流れる電子の一部(ホットエレクトロン)を第1ゲート絶縁膜(トンネル酸化膜)を通じて浮遊ゲートに注入する。このような書き込み方式は、SSI(Source-Side-Injection)書き込み方式と呼ばれ、高効率でホットエレクトロンを発生するために、少ないチャネル電流でメモリセルに書き込みを行うことができる。従って、チップ内の電源電圧の電流供給能力を超えない範囲で、複数のメモリセルに並列で書き込むことができ、書き込みのスループットを上げることができる。このとき、選択メモリセルと非選択メモリセルの素子分離は、n型半導体領域(ドレイン)ヒオーバーラップした選択ゲートによって行われる。すなわち、非選択のメモリセルの選択ゲートに、例えば0V程度を印加する。また他の選択ゲート電極には、例えば0Vを印加することで、選択、非選択のメモリセル間のアイソレーションを行う。

【0021】

読み出し時には、選択ゲートに3.5V、ソースに1V、ドレインに0Vを印加してメモリセルのしきい値を判定する。選択メモリセルと非選択メモリセルの素子分離は、書き込み時と同様、選択ゲートによって行われる。

【0022】

消去時には、選択ワード線に-18V、ソースに0V、ドレインに0V、選択ゲートに0Vを印加する。これにより浮遊ゲートからp型ウエルに電子が放出され、しきい値が低下する。

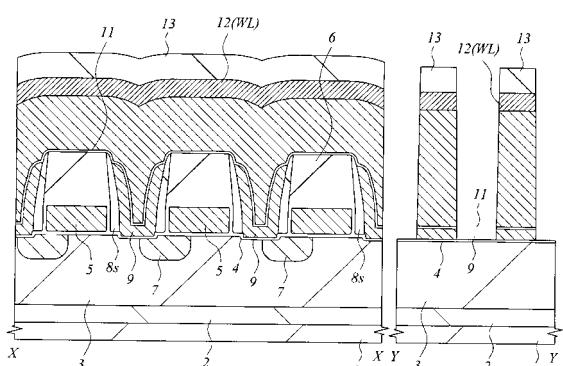

【0023】

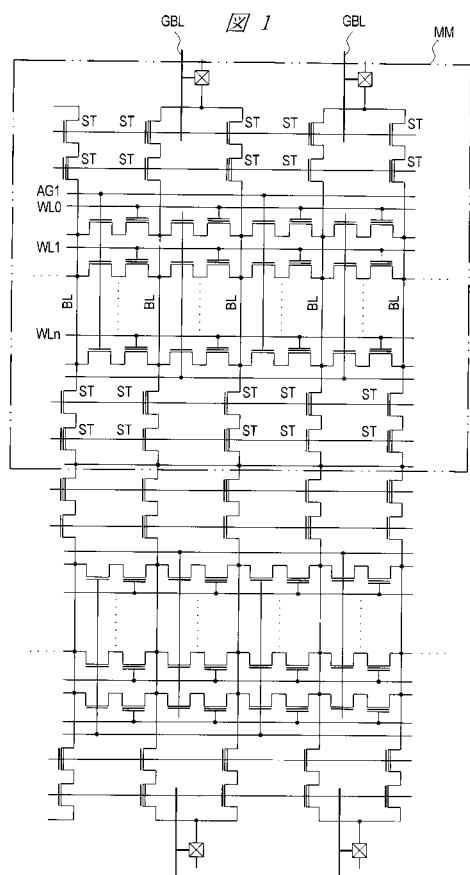

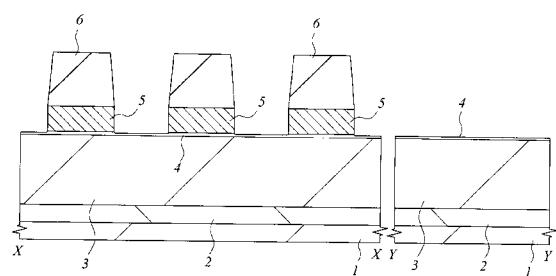

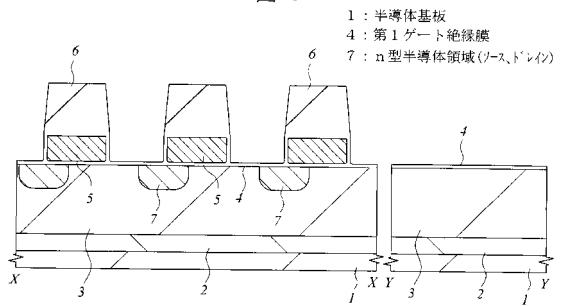

次に、本実施の形態のAND型フラッシュメモリの製造方法を図2～図16を用いて工程順に説明する。なお、図中のX-Xを付した断面図は、ワード線(WL)の延在方向(行方向)に沿った半導体基板の要部断面図、Y-Yを付した断面図はワード線(WL)の延在方向に直交する方向(列方向)に沿った半導体基板の要部断面図である。

40

【0024】

まず、図2に示すように、例えばp型の単結晶シリコンからなる半導体基板(以下、単に基板という)1上に周知の製造方法を用いてn型ウエル2を形成し、続いてn型ウエル

50

2 の上部に p 型ウエル 3 を形成した後、 p 型ウエル 3 の表面に絶縁膜として、酸化シリコン膜からなる第 1 ゲート絶縁膜（トンネル酸化膜）4 を形成する。

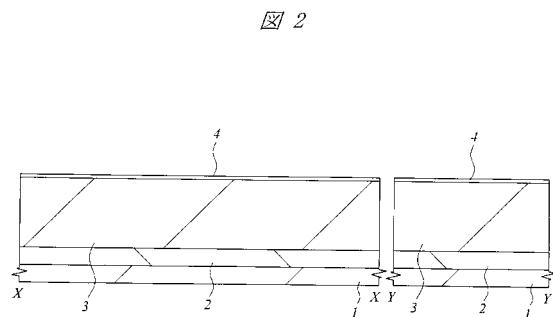

#### 【 0 0 2 5 】

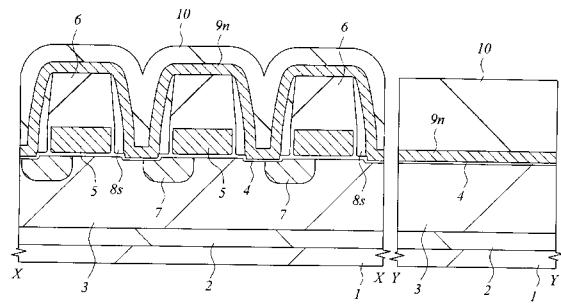

次に、図 3 に示すように、第 1 ゲート絶縁膜 4 の上部に導電膜および絶縁膜を形成する。導電膜および絶縁膜は、例えば、CVD 法で n 型多結晶シリコン膜 5n と酸化シリコン膜 6 として堆積される。その後、図 4 に示すように、フォトレジスト膜をマスクにした周知のドライエッチング技術を用いて酸化シリコン膜 6 と n 型多結晶シリコン膜 5n とをパターニングすることにより、n 型多結晶シリコン膜 5n からなる導電体片状の選択ゲート（第 1 ゲート）5 を形成する。このとき、選択ゲート 5 とその上部の酸化シリコン膜 6 は、列方向（図の紙面に垂直な方向）に沿って帯状に延在するようにパターニングされる。なお、酸化シリコン膜 6 をパターニングする際、その側壁にテープを設けることにより、後の工程で選択ゲート 5 同士の間に浮遊ゲート材料を堆積し易くなる。このテープ状の酸化シリコン膜 6 の角度は、半導体基板 1 に対して 85 度から 75 度の角度で設けられている。本実施の形態では、この後の工程で設けられる n 型半導体領域 7 側の側壁の角度を 82 度の角度、その反対側の側壁の角度を 80 度として設けている。すなわち、n 型半導体領域 7 側が設けられている側の側壁の角度を n 型半導体領域 7 側が設けられていない側の側壁の角度よりも大きい角度としている。また、酸化シリコン膜 6 はこの後の工程で選択ゲート 5 を保護する為の保護膜およびキャップ膜として機能する。

10

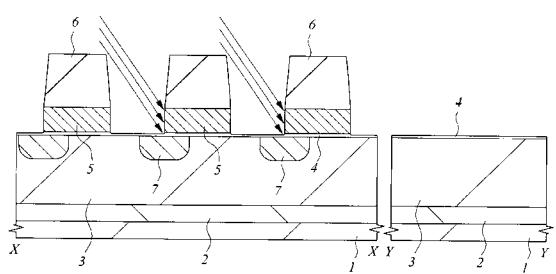

#### 【 0 0 2 6 】

次に、図 5 に示すように、斜めイオン注入法を用いて選択ゲート 5 の一方の側壁近傍の p 型ウエル 3 に n 型の導電型を示す為の不純物としてヒ素（As）を導入することにより、メモリセルのローカルビット線として機能する n 型半導体領域（ソース、ドレイン）7 を形成する。

20

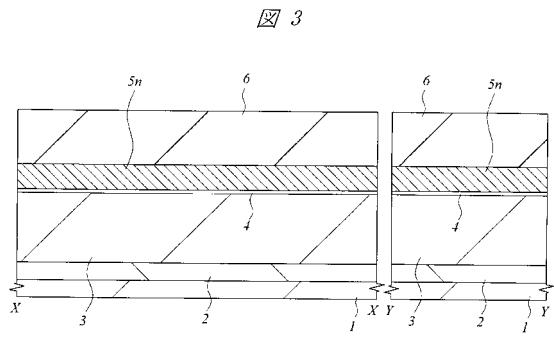

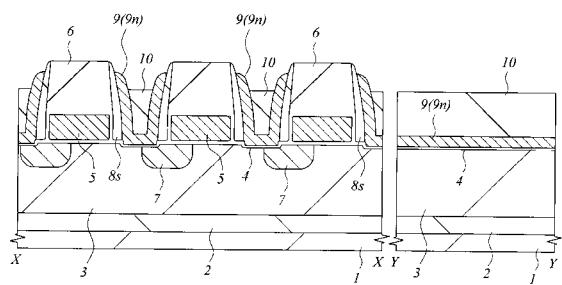

#### 【 0 0 2 7 】

後述するように、本実施の形態のフラッシュメモリは、選択ゲート 5 の側壁に沿って浮遊ゲートを配置するので、構造上、ドレインディスターブが生じ易い。そこで、ドレインディスターブ対策として、選択ゲート 5 の側壁のうち、n 型半導体領域 7 が形成されている方の側壁の近傍に位置する第 1 ゲート絶縁膜 4 の膜厚を他の部分よりも厚く形成し、後に形成する浮遊ゲートと n 型半導体領域 7 との距離を離す。

30

#### 【 0 0 2 8 】

本実施の形態では、第 1 ゲート絶縁膜 4 の膜厚を厚くする酸化方法として、ISSG (In-Situ Steam Generation) 酸化法（熱処理チャンバ内に水素と酸素を直接導入し、加熱した基板上でラジカル酸化反応を行う方法）を用いる。この ISSG 法は、例えば、900 の雰囲気で 10 % 以上の H<sub>2</sub> 濃度とすることにより、Si 上に 8 nm の膜厚の酸化シリコン膜を形成することができる。また、このときの温度を下げるにより n 型半導体領域 7 の横方向拡散が抑制できる。

30

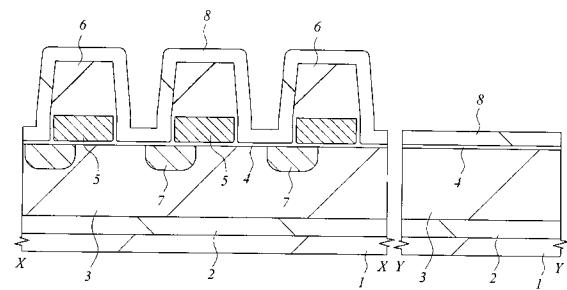

#### 【 0 0 2 9 】

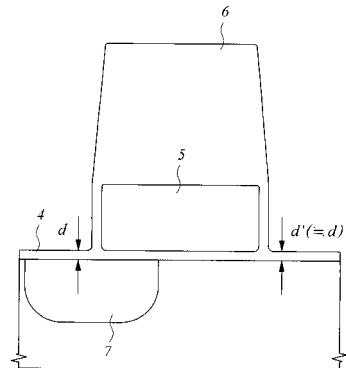

図 6 は、上記の ISSG 酸化法を用いて第 1 ゲート絶縁膜 4 を厚膜化した直後の基板 1 を示す断面図、図 7 は、図 6 の要部拡大断面図である。

40

#### 【 0 0 3 0 】

ISSG 酸化法は、既存の RTP (Rapid Thermal Process) 方式による熱酸化法と比較した場合、基板 1 中への酸素の增速拡散が抑制されるという特徴がある。そのため、ISSG 酸化法で基板 1 の表面を酸化すると、図 7 に示すように、ヒ素（As）が導入された n 型半導体領域 7 の上部における第 1 ゲート絶縁膜 4 の膜厚（d）は、ヒ素（As）が導入されていない領域の膜厚（d'）とほぼ等しくなる。すなわち、第 1 ゲート絶縁膜 4 の膜厚は、選択ゲート 5 の両側壁近傍を含む選択ゲート 5 同士の間でほぼ均一になる。また、このとき ISSG 法による酸化により、選択ゲート 5 の側面にも絶縁膜 4 が形成されている。

40

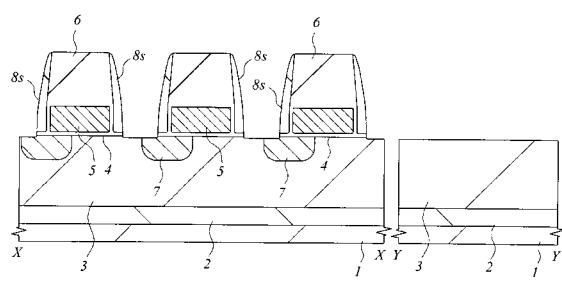

#### 【 0 0 3 1 】

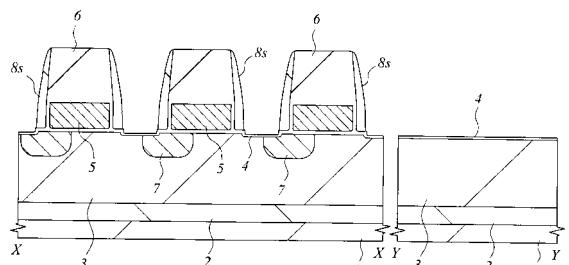

次に、図 8 に示すように、基板 1 上に CVD 法で絶縁膜として、酸化シリコン膜 8 を堆

50

積する。酸化シリコン膜8は、選択ゲート5同士の間を埋め込まない程度の膜厚で堆積する。続いて、図9に示すように、酸化シリコン膜8を異方性エッチングすることによって、選択ゲート5の両側壁に酸化シリコン膜8からなるサイドウォールスペーサ8sを形成する。サイドウォールスペーサ8sは、後に形成する浮遊ゲートと選択ゲート5との間の耐圧を確保するために形成する。

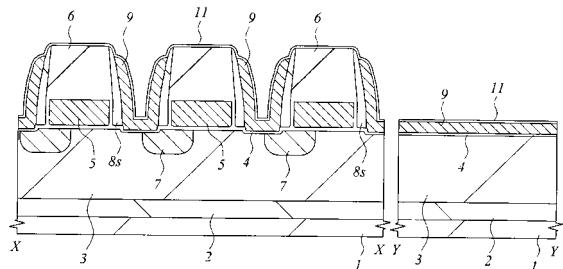

#### 【0032】

図9に示すように、上記の異方性エッチングを行うと、選択ゲート5同士の間の第1ゲート絶縁膜4もエッチングされて基板1が露出する。前述したように、ISSG酸化法を用いて厚膜化された第1ゲート絶縁膜4は、膜厚の均一性が高いために、異方性エッチングを行った際、膜厚の減少量の局所的なばらつきがほとんど生じない。他方、 RTP方式による熱酸化法で第1ゲート絶縁膜4を厚膜化した場合は、選択ゲート5の両側壁の近傍で第1ゲート絶縁膜4の膜厚が異なるために、上記の異方性エッチングを行った際、膜厚の減少量が局所的にばらつき、メモリセルの特性が変動する。また、膜厚のばらつきを無くすためにオーバーエッチングを行うと、基板1の表面が深く削るために、素子の特性が劣化する。従って、ISSG酸化法を用いて第1ゲート絶縁膜4を均一に厚膜化する本実施の形態によれば、ドレインディスターブを抑制しつつ、上記のような問題の発生を回避することが可能となる。

#### 【0033】

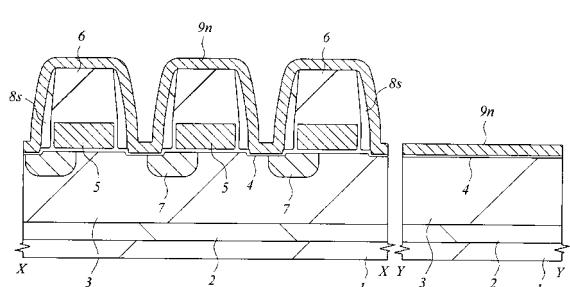

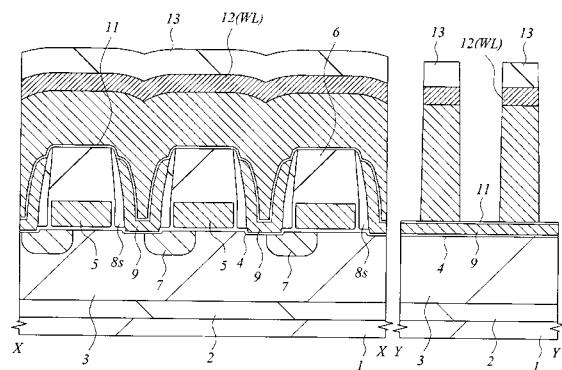

次に、図10に示すように、基板1を熱酸化することによって、選択ゲート5同士の間の基板1表面に酸化シリコン膜からなる第1ゲート絶縁膜4を再生する。この熱酸化は、周知の湿式酸化法で行ってもよいが、前述したISSG酸化法で行うことにより、より均一な膜厚の第1ゲート絶縁膜4を再生することができる。

#### 【0034】

次に、図11に示すように、基板1上にCVD法で導電膜として、n型多結晶シリコン膜9nを堆積する。n型多結晶シリコン膜9nは、選択ゲート5同士の間を埋め込まない程度の膜厚で堆積する。続いて、図12に示すように、基板1上に反射防止膜(BARC; Bottom-Anti-Reflective Coating)10を堆積する。反射防止膜10は、次の工程で選択ゲート5の上方のn型多結晶シリコン膜9nをエッチングする際、選択ゲート5の側壁および選択ゲート5の同士の間のn型多結晶シリコン膜9nがエッチングされないように保護する膜であり、選択ゲート5同士の間を埋め込む保護膜は、反射防止膜10に限定されず、n型多結晶シリコン膜9nや酸化シリコン膜6とエッチング選択比が異なるものであれば、他の絶縁膜を使用してもよい。

#### 【0035】

次に、図13に示すように、反射防止膜10とその下層のn型多結晶シリコン膜9nをエッチバックする。このとき、選択ゲート5の上方の反射防止膜10とn型多結晶シリコン膜9nとをエッチングすることにより、選択ゲート5の側壁および選択ゲート5同士の間にn型多結晶シリコン膜9nからなる導電体片状の浮遊ゲート(第2ゲート)9が形成される。このとき、浮遊ゲート9は、選択ゲート5の延在方向(列方向)に沿って帯状に延在するようにパターニングする。

#### 【0036】

次に、選択ゲート5同士の間に残った反射防止膜10をアッシングで除去した後、図14に示すように、浮遊ゲート9の表面に、浮遊ゲート9と制御ゲート12との間の絶縁膜として、第2ゲート絶縁膜11を形成する。第2ゲート絶縁膜11は、例えばCVD法で堆積した酸化シリコン膜、窒化シリコン膜および酸化シリコン膜の3層で構成する。

#### 【0037】

次に、図15に示すように、第2ゲート絶縁膜11の上部にメモリセルのワード線(WL)となる導電膜を形成する。この導電膜は、CVD法でn型多結晶シリコン膜とW(タンクステン)膜との積層膜であるポリサイド膜と酸化シリコン膜13とを堆積することで形成されている。その後、フォトレジスト膜をマスクにした周知のドライエッチング技術

10

20

30

40

50

を用いて酸化シリコン膜13とポリサイド膜とをパターニングすることにより、ポリサイド膜からなる導電体片状の制御ゲート(第3ゲート)12を形成する。このとき、制御ゲート12は、行方向(図の左右方向)に沿って帯状に延在するようにパターニングされ、ワード線(WL)を構成する。また、制御ゲート12をドライエッチングでパターニングする際に、第2ゲート絶縁膜がエッチングストップ層として機能している。

## 【0038】

次に、図16に示すように、露出した第2ゲート絶縁膜11を周知のドライエッチング技術やウェットエッチング技術等により除去し、続いて選択ゲート5をドライエッチングして分離することにより、メモリセルが完成する。

## 【0039】

## (実施の形態2)

本実施の形態は、MONOS(Metal Oxide Nitride Oxide Semiconductor)トランジスタを有する不揮発性メモリに適用したものである。

## 【0040】

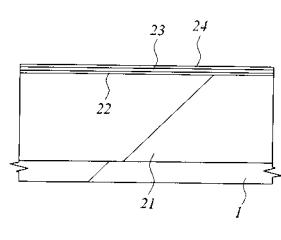

本実施の形態のMONOSトランジスタを形成するには、まず、図17に示すように、周知の製造方法を用いて基板1にp型ウエル21を形成した後、基板1上に電荷蓄積膜を含む積層の絶縁膜を形成する。この電荷蓄積膜を含む積層の絶縁膜は、基板1を熱酸化することによって、p型ウエル21の表面に酸化シリコン膜22を形成する。続いて、酸化シリコン膜22の上部にCVD法を用いて窒化シリコン膜からなる電荷蓄積膜23を形成し、電荷蓄積膜23の上部にCVD法を用いて絶縁膜として酸化シリコン膜24を形成する。この酸化シリコン膜24はISSG酸化法によって形成することも可能である。電荷蓄積膜23は、例えば酸窒化シリコン膜またはSiナノドットのように、膜中にトラップ準位を有するものであれば、窒化シリコン膜以外のものを使用してもよい。

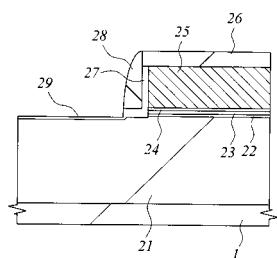

## 【0041】

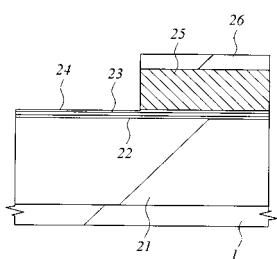

次に、図18に示すように、酸化シリコン膜24の上部にCVD法で、導電性膜としてn型多結晶シリコン膜と、絶縁膜として酸化シリコン膜26とを堆積した後、フォトレジスト膜をマスクにした周知のドライエッチング技術を用いて酸化シリコン膜26とn型多結晶シリコン膜とをパターニングすることにより、n型多結晶シリコン膜からなるメモリゲート25および酸化シリコン膜26を形成する。

## 【0042】

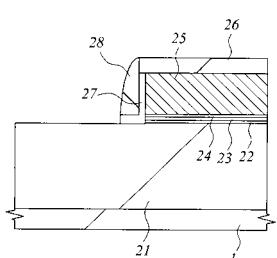

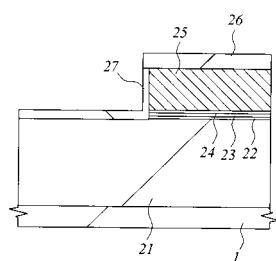

次に、図19に示すように、メモリゲート25の側壁を酸化することによって酸化シリコン膜27を形成する。本実施の形態では、メモリゲート25の側壁を酸化する方法として、前記ISSG酸化法により基板1を熱処理する。ISSG酸化法は、実施の形態1で前述したように、減圧した熱処理チャンバ内に水素と酸素を直接導入し、加熱した基板上でラジカル酸化反応を行う方法であるが、シリコンだけでなく窒化シリコンも酸化するという強力な酸化作用を有している。そのため、この方法を用いてメモリゲート25の側壁を酸化すると、メモリゲート25によって覆われていない領域の窒化シリコン膜からなる電荷蓄積膜23も酸化され、均一な膜厚を有する酸化シリコン膜27が形成される。

## 【0043】

このとき、周知の熱酸化法によって酸化シリコン膜27を形成した場合には、メモリゲート25端部(メモリゲート25と酸化シリコン膜24の界面)が酸化され、いわゆるバーズビークが発生してしまう(図示はしない)。このようなバーズビークの発生は、メモリゲート25端における電界が変化してしまうので、誤書き込みまたは誤消去等の問題を発生する要因となる。しかしながら、本実施の形態においては、ISSG酸化法を用いていることにより、周知の熱酸化法に比べてこのようなバーズビークの発生を抑制することができる。

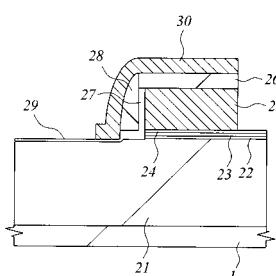

## 【0044】

次に、図20に示すように、基板1上にCVD法で堆積した絶縁膜を異方性エッチングすることによって、メモリゲート25の側壁にサイドウォールスペーサ28を形成する。サイドウォールスペーサ28を形成する絶縁膜としては、酸化シリコン膜または窒化シリ

コン膜を例示できる。

#### 【0045】

上記の異方性エッティングを行う際は、メモリゲート25によって覆われていない領域の酸化シリコン膜27もエッティングすることによって、基板1の表面を露出させる。前述したように、ISSG酸化法を用いて形成された酸化シリコン膜27は、膜厚の均一性が高いために、エッティングを行った際、膜厚の減少量の局所的なばらつきがほとんど生じない。これにより、基板1のオーバーエッティング量を少なくすることができる。また、メモリゲート25の側面にISSG酸化法にて酸化シリコン膜27を形成しているので、酸化シリコン膜27を既知の熱酸化方法を用いた場合と比較し、縦方向の膜厚が均一に形成できるとともに、メモリゲート25端部へのいわゆるバーズピーク形状の酸化が抑制できる。これらの形成方法と形状効果とにより、MONOSトランジスタの特性の劣化を防ぐことができる。10

#### 【0046】

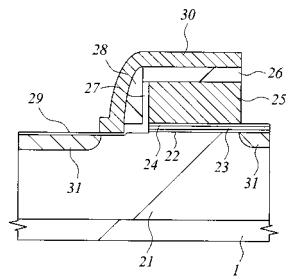

次に、図21に示すように、基板1を熱酸化することによって、上記のエッティングで露出した基板1の表面に酸化シリコンからなるゲート絶縁膜29を形成する。この熱酸化は、周知の湿式酸化法で行ってもよいが、前述したISSG酸化法で行うことにより、より均一な膜厚のゲート絶縁膜29を形成することができる。このゲート絶縁膜29は後述の工程で形成される制御ゲート30のゲート絶縁膜として形成される。

#### 【0047】

次に、図22に示すように、基板1上にCVD法で堆積したn型多結晶シリコン膜をパターニングすることによって、メモリゲート25の側壁と上部を覆う制御ゲート30を形成する。その後、図23に示すように、p型ウエル21に不純物（リンまたはヒ素）をイオン注入してn型半導体領域（ソース、ドレイン）31を形成することにより、MONOSトランジスタを有するメモリセルが完成する。20

#### 【0048】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### 【0049】

例えば、本実施の形態においては、メモリゲート25形成後にn型半導体領域（ソース、ドレイン）7を形成しているが（図5）、これを浮遊ゲート9nの形成後（図11）に行うこと也可能である。30

#### 【産業上の利用可能性】

#### 【0050】

本発明は、不揮発性半導体記憶装置に適用して有用な技術である。

#### 【図面の簡単な説明】

#### 【0051】

【図1】本発明の一実施の形態であるAND型フラッシュメモリを示す回路図である。

【図2】本発明の一実施の形態であるAND型フラッシュメモリの製造方法を示す半導体基板の要部断面図である。40

【図3】図2に続くAND型フラッシュメモリの製造方法を示す半導体基板の要部断面図である。

【図4】図3に続くAND型フラッシュメモリの製造方法を示す半導体基板の要部断面図である。

【図5】図4に続くAND型フラッシュメモリの製造方法を示す半導体基板の要部断面図である。

【図6】図5に続くAND型フラッシュメモリの製造方法を示す半導体基板の要部断面図である。

#### 【図7】図6の要部拡大断面図である。

#### 【図8】図6に続くAND型フラッシュメモリの製造方法を示す半導体基板の要部断面図50

である。

【図 9】図 8 に続く AND 型フラッシュメモリの製造方法を示す半導体基板の要部断面図である。

【図 10】図 9 に続く AND 型フラッシュメモリの製造方法を示す半導体基板の要部断面図である。

【図 11】図 10 に続く AND 型フラッシュメモリの製造方法を示す半導体基板の要部断面図である。

【図 12】図 11 に続く AND 型フラッシュメモリの製造方法を示す半導体基板の要部断面図である。

【図 13】図 12 に続く AND 型フラッシュメモリの製造方法を示す半導体基板の要部断面図である。 10

【図 14】図 13 に続く AND 型フラッシュメモリの製造方法を示す半導体基板の要部断面図である。

【図 15】図 14 に続く AND 型フラッシュメモリの製造方法を示す半導体基板の要部断面図である。

【図 16】図 15 に続く AND 型フラッシュメモリの製造方法を示す半導体基板の要部断面図である。

【図 17】本発明の他の実施の形態である MONOS ドランジスタを有する不揮発性メモリの製造方法を示す半導体基板の要部断面図である。 20

【図 18】図 17 に続く MONOS ドランジスタを有する不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図 19】図 18 に続く MONOS ドランジスタを有する不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図 20】図 19 に続く MONOS ドランジスタを有する不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図 21】図 20 に続く MONOS ドランジスタを有する不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図 22】図 21 に続く MONOS ドランジスタを有する不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図 23】図 22 に続く MONOS ドランジスタを有する不揮発性メモリの製造方法を示す半導体基板の要部断面図である。 30

#### 【符号の説明】

##### 【0052】

- 1 半導体基板

- 2 n型ウエル

- 3 p型ウエル

- 4 第1ゲート絶縁膜(トンネル酸化膜)

- 5 n型多結晶シリコン膜

- 6 選択ゲート(第1ゲート)

- 7 酸化シリコン膜

- 8 n型半導体領域(ソース、ドレイン)

- 9 酸化シリコン膜

- 8s サイドウォールスペーサ

- 9n n型多結晶シリコン膜

- 9 浮遊ゲート(第2ゲート)

- 10 反射防止膜

- 11 第2ゲート絶縁膜

- 12 制御ゲート(第3ゲート)

- 13 酸化シリコン膜

- 21 p型ウエル

40

50

2 2 酸化シリコン膜

2 3 電荷蓄積膜

2 4 酸化シリコン膜

2 5 メモリゲート

2 6、2 7 酸化シリコン膜

2 8 サイドウォールスペーサ

2 9 ゲート絶縁膜

3 0 制御ゲート

3 1 n型半導体領域(ソース、ドレイン)

B L ローカルビット線

G B L グローバルビット線

M M メモリアレイ部

Q s メモリセル

S T 選択トランジスタ

W L ワード線

10

【図1】

【図2】

【図3】

【図4】

図4

【図5】

図5

【図8】

図8

【図9】

図9

【図6】

図6

【図7】

図7

【図10】

図10

【図11】

図11

【図12】

図12

【図13】

図13

【図15】

図15

【図14】

図14

【図16】

図16

【図17】

図17

【図18】

図18

【図20】

図20

【図21】

図21

【図19】

図19

【図22】

図22

【図23】

図23

---

フロントページの続き

(72)発明者 原口 恵一

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 足立 哲生

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

F ターム(参考) 5F083 EP02 EP18 EP22 EP23 EP33 EP35 EP48 EP55 EP79 ER02

ER22 GA27 JA04 JA39 JA53 PR12 PR37

5F101 BA01 BA29 BA36 BA45 BB02 BB05 BD22 BD34 BE07 BH03

BH09