19 RÉPUBLIQUE FRANÇAISE

## INSTITUT NATIONAL DE LA PROPRIÉTÉ INDUSTRIELLE

**PARIS**

N° de publication :

(à n'utiliser que pour les commandes de reproduction)

2 536 224

21) N° d'enregistrement national :

82 19230

(51) Int Cl3: H 03 F 3/195.

DEMANDE DE BREVET D'INVENTION

Α1

- 22 Date de dépôt : 17 novembre 1982.

- (30) Priorité

- (71) Demandeur(s): SOCIETE ANONYME D'ETUDES ET REALISATIONS NUCLEAIRES SODERN. FR.

- (43) Date de la mise à disposition du public de la demande : BOPI « Brevets » n° 20 du 18 mai 1984.

- 60 Références à d'autres documents nationaux apparentés :

- (72) Inventeur(s): Rémy Paul Michel Fauvel.

- 73 Titulaire(s):

- 74 Mandataire(s): Henri Gaudel.

64 Amplificateur vidéofréquence.

(57) Amplificateur vidéo comportant quatre étages d'amplification 2, 3, 4 et 5, un circuit d'alignement en sortie 6 et une-liaison coaxiale 7 à la charge capacitive 8 du système de visualisation.

L'amplificateur de tension 3 est constitué de deux étages symétriques à contre-réaction de courant montés en opposition, chacun desdits étages comportant trois transistors MOS 24, 25, 26 montés en série pour permettre le fonctionnement sous des tensions élevées.

Le préamplificateur de courant 4 de type push-pull symétrique se trouve réduit à une paire de transistors MOS 38 et 38' par une disposition particulière permettant son alimentation à partir de l'étage final.

L'amplificateur de courant 5 également de type push-pull symétrique est constitué dans chacune de ses branches par un assemblage en parallèle de deux groupes de transistors MOS, chaque groupe comportant trois transistors montés en série 44 à 49.

Un pont de répartition de tensions symétriques 31, compensé en fréquence, assure l'équilibrage des puissances entre chacun des composants actifs de l'étage amplificateur de courant. Application : récepteurs de télévision.

AMPLIFICATEUR VIDEOFREQUENCE.

5

10

15

20

25

30

L'invention concerne un amplificateur vidéofréquence appliquant à une charge capacitive un signal de sortie vidéo de grande amplitude obtenu à partir d'une source vidéo suivie d'étages préamplificateur et amplificateur de tension, préamplificateur et amplificateur de courant.

Cet amplificateur constitue le maillon terminal de la chaîne de traitement vidéo d'un système de visualisation. Sa dynamique de sortie (140 V) et la valeur de sa charge capacitive (250 à 700 pF) influent sur le dimensionnement des étages de puissance, le principe de fonctionnement restant inchangé. Par ailleurs l'utilisation de standards dits à haute résolution nécessite des bandes passantes étendues à 15 MHz, voire à 20 et 30 MHz pour des systèmes plus performants.

Un grand nombre de composants bipolaires haute fréquence permet la réalisation de façon connue de l'étage préamplificateur de tension qui fonctionne à basse tension et à faibles courants. Pour les autres étages fonctionnant sous des tensions de l'ordre de 180 V avec des courants de 0,4 A moyen et 1,5 A crête, des composants de puissance doivent être recherchés.

La technologie des composants bipolaires ne permet pas de répondre au problème en ce qui concerne les caractéristiques de commutation : temps de montée et de descente trop longs, temps de retard et de stockage importants et très différents ne permettant pas leur utilisation dans un montage de type push-pull ; d'autre part leur sensibilité au phénomène de second claquage proscrit leur utilisation dans l'application présente.

Le but de l'invention est de proposer une réalisation de l'étage amplificateur de tension et des étages de puissance amplificateurs de courant utilisant des composants obtenus par une technologie différente et agencés de manière à pouvoir fonctionner sous des tensions élevées tout en restant insensibles au phénomène de second claquage.

5

10

15

20

25

30

35

Conformément à l'invention, ledit étage amplificateur de tension de structure symétrique et constitué d'un premier étage et d'un deuxième étage à contre-réaction de. courant montés en opposition comporte dans chacun desdits premier et deuxième étages des composants actifs complémentaires de ceux de l'autre étage et assemblés en série pour permettre le fonctionnement sous les tensions élevées imposées par l'amplitude dudit signal vidéo de sortie, lesdits étages préamplificateur et amplificateur de courant étant de type push-pull symétrique et l'étage amplificateur comportant également dans chacune de ses branches un assemblage de structure série de composants actifs complémentaires de ceux de l'autre branche, lesdits assemblages de composants actifs étant alimentés par une première source de tension continue, la sortie dudit étage amplificateur de tension et l'entrée dudit étage préamplificateur de courant étant interconnectées sur la prise médiane d'un pont de répartition de tensions symétrique, compensé en fréquence et alimenté par une seconde source de tension continue, les prises réparties sur ledit pont étant reliées à des électrodes de commande des composants actifs dudit étage amplificateur de courant de façon à assurer l'équilibrage des tensions entre chacun desdits composants actifs, ledit étage préamplificateur de courant étant alimenté par deux potentiels pris en deux points intermédiaires symétriques sur le trajet du courant circulant dans les branches de l'étage amplificateur de courant.

Les composants de technologie MOS de puissance à canal de type de conduction n et p présentent des caractéristiques intéressantes : tensions de claquage élevées (de 90 V à 350 V), capacités de dissipation et de courant importantes de l'ordre de quelques ampères et temps de commutation particulièrement courts de l'ordre de quelques nanosecondes pour

les plus rapides.

5

10

15

20

25

30

35

De plus, ces composants ont la particularité de ne pas présenter de phénomènes de "second claquage".

En contrepartie, les inconvénients inhérents à ces composants sont les suivants : capacités interélectrodes d'autant plus élevées que le composant accepte des tensions et courants importants ce qui réduit d'autant plus les vitesses de commutation, dissipation thermique limitée pour les versions les plus rapides.

Le choix final résulte d'un compromis entre ces différents paramètres où la vitesse de commutation, prédominante pour la bande passante, doit être privilégiée ; dès lors les tensions acceptables sont limitées à 90 V et les courants à 3 A.

En conséquence les assemblages élaborés de structure série dans les branches symétriques des étages amplificateurs de tension et de courant sont nécessaires pour permettre le fonctionnement sous les tensions requises. La mise en série des composants présente d'autre part les avantages suivants : répartition des puissances entre chacun d'eux, réduction de l'influence des capacités interélectrodes qui se trouvent connectées en série. En contrepartie la répartition des tensions doit être assurée par un atténuateur compensé, donc présentant une composante capacitive non négligeable.

La description suivante en regard du dessin annexé le tout donné à titre d'exemple, fera bien comprendre comment l'invention peut être réalisée.

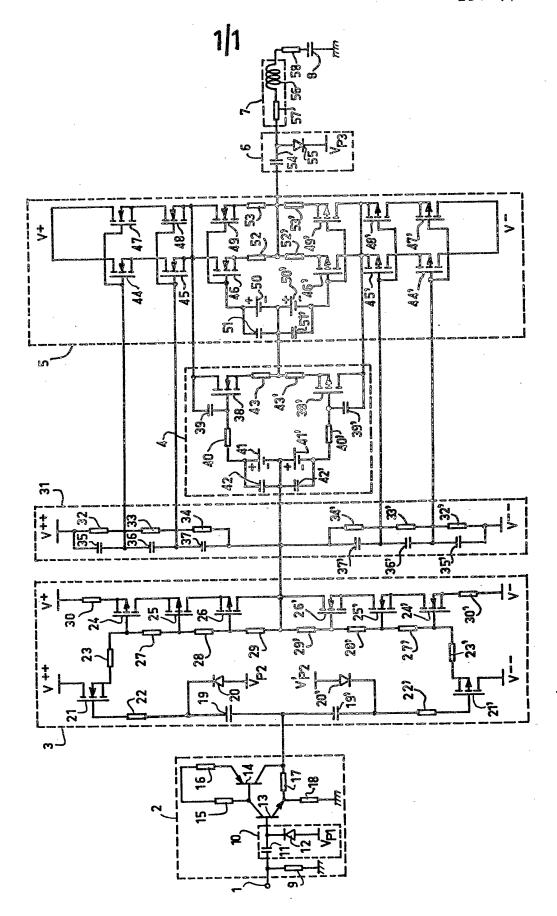

La figure unique représente le schéma complet de l'amplificateur vidéo dont les étages amplificateur de tension, préamplificateur et amplificateur de courant sont réalisés conformément à l'invention.

Cet amplificateur comporte, à partir d'une source vidéo positive appliquée à sa borne d'entrée 1, un étage préamplificateur de tension 2, un étage amplificateur de tension 3, un étage préamplificateur de courant 4, un étage amplificateur de courant 5, un circuit d'alignement en sortie 6 et une liaison coaxiale 7 à la charge capacitive du signal de visualisation représentée par le condensateur 8.

L'entrée de l'étage préamplificateur de tension adaptée sur une impédance 9 de valeur normalisée (75 ohms) accepte le signal vidéo de valeur 0,7 volt comportant les 'paliers d'alignement d'amplitude normalisée (ces caractéristiques pouvant évoluer aisément pour remplir des contraintes différentes).

5

10

15

. 20

25

30

35

Le circuit d'alignement en entrée 10 est constitué par un condensateur de liaison 11 et par une diode 12 dont l'anode est portée au potentiel positif V<sub>pl</sub> d'une source de tension continue permettant la polarisation de l'étage. Une borne du condensateur 11 est reliée à la borne d'entrée 1 par liaison directe et à la masse à travers l'impédance d'entrée 9, l'autre borne dudit condensateur étant connectée à là cathode de la diode 12.

Le point commun au condensateur 11 et à la diode 12 est relié à la base d'un transistor 13 de type NPN dont le collecteur est connecté à la base d'un transistor 14 de type PNP. Cet étage est alimenté par une source de tension continue à "basse tension" de valeur 35 volts appliquée entre la masse et une borne  $V_0^+$ , celle-ci étant reliée au collecteur du transistor 13 à travers une résistance de polarisation 15 et à l'émetteur du transistor 14 à travers une autre résistance de polarisation 16. L'émetteur du transistor 13 est connecté à la sortie de l'étage sur le collecteur du transistor 14 à travers une résistance 17 de valeur  $R_1$  et à la masse à travers une résistance 18 de valeur  $R_2$ .

Le dispositif est non inverseur et le gain de l'étage de valeur 17 est déterminé par le rapport  $R_1/R_2$  pour une excursion de tension minimale de 15 volts.

L'étage amplificateur de tension 3 se caractérise par une importante dynamique de sortie (140 volts minimum). La charge de cet amplificateur présentant une composante capacitive non négligeable, une structure symétrique à basse impédance de sortie s'impose. Cette structure est constituée par un premier étage et par un deuxième étage à contre-réaction de courant montés en opposition.

5

Conformément à l'invention, le premier étage à contre-réaction de courant est attaqué par un circuit intermédiaire d'alignement connecté à la sortie de l'étage préamplificateur de tension à travers le condensateur de liaison 19 et constitué de même que le circuit d'alignement en entrée par une diode 20 et une source de tension de polarisation positive V<sub>D2</sub>. Ce premier étage comporte :

10

- un étage suiveur constitué par un transistor MOS à canal n 21 dont la grille est couplée par une résistance d'entrée 22 audit circuit intermédiaire d'alignement, dont le drain est relié à la borne V<sup>++</sup> d'une source de tension d'alimentation continue à "haute tension" et dont la source est reliée à une borne d'une impédance de couplage d'entrée 23 de valeur Z<sub>a</sub>.

20

25

15

un assemblage de trois transistors MOS à canal p montés en série, la grille du premier transistor 24 étant reliée à l'autre borne de l'impédance 23, les grilles du premier transistor 24, du deuxième transistor 25 et du troisième transistor 26 étant interconnectées à travers une première impédance de réaction 27 de valeur  $\mathbf{Z}_{r1}$  et une deuxième impédance de réaction 28 de valeur  $\mathbf{Z}_{r2}$ , la grille et le drain du troisième transistor 26 étant reliés à travers une troisième impédance de réaction 29 de valeur  $\mathbf{Z}_{r3}$ ; la source du premier transistor 24 est reliée à la borne  $\mathbf{V}^+$  d'une autre source de tension d'alimentation continue à "haute tension" à travers une impédance 30 et le drain du troisième transistor 26 est connecté à la sortie de l'étage amplificateur de tension.

30

Le deuxième étage symétrique du premier et alimenté à partir des bornes de tension V et V desdites sources de tension d'alimentation continue à "haute tension"

comporte des transistors MOS complémentaires de ceux du premier étage. Chaque élément du deuxième étage est référencé au moyen du même nombre que son homologue du premier étage affecté du signe "  $^{\prime}$ ". Les sources de tension d'alimentation continue prises entre les bornes  $V^+$  et  $V^-$  d'une part, et  $V^{++}$  et  $V^-$  d'autre part ont pour valeurs respectives 180 volts et 210 volts.

20 -

L'assemblage formé par les transistors 24, 25 et 26 et par les impédances 23, 27, 28 et 29 constitue un amplificateur opérationnel dont le gain est déterminé par le rapport entre la somme des impédances de réaction 27, 28, 29 et l'impédance de couplage d'entrée 23. Chaque étage symétrique de l'autre a une même valeur de gain puisque les composants homologues sont identiques. On suppose ici que les valeurs des éléments sont telles que les paramètres propres des transistors MOS 21, 24, 25 et 26 peuvent être négligés. De point de vue dynamique, le montage est assimilé à deux amplificateurs en parallèle dont la résultante a le gain commun

$$-\frac{Z_{r1}+Z_{r2}+Z_{r3}}{Z_{e}} \text{ et 1'impédance de sortie la moitié de 1'im-}$$

pédance de sortie de chacun des amplificateurs pris séparément. Cet étage amplificateur de tension comporte deux entrées, à travers les impédances de même valeur 23 et 23', qui doivent être attaquées par des tensions égales et en phase. Les impédances 27, 28, 29 et leurs homologues assurent également la division de la tension de sortie par rapport à chacune des alimentations V<sup>+</sup> et V<sup>-</sup>. Afin de pouvoir maîtriser le gain dans une large gamme de fréquence, les impédances de valeurs Z<sub>e</sub>, Z<sub>r1</sub>, Z<sub>r2</sub>, Z<sub>r3</sub> doivent rester faibles devant les impédances qui résultent des capacités interélectrodes des transistors MOS 24, 25 et 26 : capacités grilles-drains qui modifient le gain en tension aux fréquences élevées (réseau RC parallèle et effet Miller), capacités drains-sources qui augmentent la charge capacitive et constituent avec les impédances 27, 28, 29 et leurs homologues la charge de l'ampli-

ficateur. Il en résulte une fréquence de coupure de la charge fixant la limite du fonctionnement résistif de l'amplificateur au-delà de laquelle le courant dépend de la fréquence.

5

10

15

20

25

30

35

Compte tenu du gain en tension souhaité (- 12), les impédances 23 et 23' sont des résistances pures de faible valeur (quelques dizaines d'ohms), ce qui est incompatible avec l'étage préamplificateur de tension. En conséquence les étages suiveurs constitués par les transistors 21 et 21' sur chacune des entrées assurent une haute impédance et facilitent donc la polarisation "en continu". Les liaisons avec ledit étage préamplificateur sont obligatoirement capacitives (décalage des niveaux continus). Les deux circuits de polarisation sur chacune des entrées (diodes 20 et 20', tensions de polarisation V p2 et V'p2) permettent de régler le point de fonctionnement de l'étage amplificateur : courant I dans l'ensemble des transistors MOS (24 ... 26') au repos et tênsion de sortie.

Des réseaux complexes constitués par les impédances 30 et 30' disposées dans les sources des transistors 24 et 24' respectivement assurent d'une part la stabilité du point de fonctionnement et d'autre part une compensation du gain en courant aux fréquences élevées.

La sortie de l'étage amplificateur de tension est reliée à l'entrée de l'étage préamplificateur de courant et à la borne médiane d'un pont de répartition de tensions 31 ayant pour rôle d'assurer l'équilibrage des tensions et donc des puissances entre chacun des composants actifs de l'étage final de puissance. Ce pont de répartition comporte, disposées en série entre les bornes d'alimentation  $V^{++}$  et  $V^{--}$  les résistances de même valeur 32, 33, 34, 34°, 33° et 32° shuntées respectivement par les condensateurs de valeur convenable 35, 36, 37, 37°, 36° et 35°.  $V_{\rm S}$  étant le niveau de tension continue en sortie de l'amplificateur de tension, les niveaux de tension disponibles sur les bornes intermédiaires dudit pont sont (par rapport aux alimentations  $V^{++}$  et  $V^{--}$ ):

$\frac{2}{3}(V^{++}-V_S)$ ,  $\frac{1}{3}(V^{++}-V_S)$ ,  $\frac{1}{3}(V_S-V^{--})$  et  $\frac{2}{3}(V_S-V^{--})$ . Le choix des tensions  $V^{++}$  et  $V^{--}$  plutôt que des tensions  $V^{+}$  et  $V^{--}$  résulte de la nécessité d'assurer une meilleure répartition des tensions drain-source aux grandes amplitudes, l'écart de tension  $V^{++}-V^{--}$  étant sensiblement plus important compte tenu des tensions grille-source des transistors MOS.

5

10

15

30

. 25

30

35

Le pont est du type compensé en fréquence, résistif aux basses fréquences et capacitif aux fréquences élevées. .

L'étage préamplificateur de courant 4 conforme à l'invention est de type push-pull symétrique ce qui permet de réduire au minimum la charge capacitive de l'amplificateur de tension. L'une de ses branches comporte un transistor MOS à canal n 38 dont la grille est reliée au drain à travers un condensateur 39 et à l'entrée de l'étage à travers la mise en série d'une résistance d'entrée 40 et d'une source de tension de polarisation 41 découplée par le condensateur 42. La source du transistor 38 est reliée à la sortie de l'étage à travers une résistance 43. L'autre branche comportant un transistor MOS à canal p est constituée de la même façon que la branche du même étage décrite ci-dessus avec des éléments référencés comme indiqué précédemment pour ceux de l'étage amplificateur de tension.

L'étage amplificateur de courant 5 conforme à l'invention est également de type push-pull symétrique. Chaque branche comporte deux groupes de transistors MOS disposés en parallèle, chaque groupe se composant de 3 transistors montés en série. Dans l'une des branches, un premier groupe est constitué par les transistors 44, 45 et 46 et un second groupe par les transistors 47,48 et 49, lesdits transistors étant des MOS à canal n. Les transistors 46 et 49 ont leurs grilles interconnectées au point commun à la sortie de l'étage préamplificateur et à l'entrée de l'étage amplificateur de courant à travers une source de tension continue de polarisation 50 découplée par le condensateur 51, leurs sources reliées à la sortie de l'étage respectivement à travers les ré-

sistances 52 et 53 et leurs drains reliés au drain du transistor 38 pour alimenter en tension l'étage préamplificateur de courant. Les grilles interconnectées des transistors 44 et 47 d'une part, 45 et 48 d'autre part sont reliées respectivement aux bornes communes aux résistances 32 et 33 d'une part, 33 et 34 d'autre part sur le pont de répartition des tensions. Les drains des transistors 44 et 47 sont interconnectés sur la borne d'alimentation V<sup>+</sup>. L'autre branche constituée de la même façon que la branche du même étage décrite ci-dessus est alimentée à partir de la borne V<sup>-</sup> et comporte des transistors MOS à canal p avec des éléments référencés comme indiqué précédemment pour ceux de l'étage amplificateur de tension.

Le préamplificateur de courant se trouve réduit à une paire de transistors MOS complémentaires grâce à une disposition particulière du montage permettant son alimentation à partir de l'étage final. On remarque en effet que les grilles des MOS de l'amplificateur de courant étant alimentées à partir des tensions divisées issues du pont de répartition, on dispose sur les sources des tensions divisées à basse impé-🧓 dance qui peuvent donc être utilisées pour alimenter l'étage préamplificateur. Cependant une telle configuration présente quelques difficultés. Les retards à chaque étage traduits en terme de déphasage représentent plusieurs dizaines de degrés aux limites fréquentielles supérieures. Une mise en phase rigoureuse entre la tension drain et la tension source des transistors complémentaires 38 et 38' est assurée par les réseaux de compensation R.C. formés par les résistances 40 et 40' et par les condensateurs 39 et 39'. En effet les tensions divisées issues du pont de répartition subissent un retard dans l'étage de sortie ; il s'ensuit que le signal appliqué sur les grilles de la paire de transistors complémentaires 38 et 38' du préamplificateur doit être retardé de la même quantité pour la mise en phase des tensions drainsource.

35

5

10

15

วับ

25

Cette condition n'est pas aussi stricte pour l'étage de sortie pour lequel l'attaque à basse impédance tolère les non-linéarités provoquées par l'annulation momentanée des tensions drain-source.

5

L'amplificateur de courant est de structure similaire à celle du préamplificateur. Les résistances 52, 53, 52' et 53' ont des valeurs plus faibles pour tenir compte de la nature de la charge et des courants importants qui y circulent.

10

15

2P

25

30

35

La structure des étages préamplificateur et amplificateur de courant de type push-pull utilisant des paires de composants actifs complémentaires a pour avantages une parfaite symétrie de fonctionnement sur les deux alternances d'une sinusoïde, une attaque à basse impédance de la charge, l'impédance de sortie intervenant dans la bande passante, enfin une consommation qui ne dépend que de la dérivée de la tensión sur la charge, la consommation à l'état stationnaire (tension fixe en sortie du lentement variable) étant faible.

La liaison à la charge est effectuée à travers le « circuit d'alignement en sortie 6 réglé sur le niveau du noir et la ligne coaxiale 7.

Le circuit d'alignement en sortie comporte le condensateur de liaison 54 dont une borne est reliée à la sortie de l'étage amplificateur de courant et dont l'autre borne est reliée à la borne de tension négative V<sub>p3</sub> d'une source de tension continue de polarisation à travers la diode 55. La borne commune au condensateur 54 et à l'anode de la diode 55 est connectée à l'entrée de la ligne coaxiale 7. Cette liaison étant nécessairement non adaptée est équivalente à la self-inductance 52 en série avec une résistance d'amortissement 57 insérée dans la ligne. La sortie de ladite ligne est reliée au condensateur 8 représentant la composante capacitive de la charge à travers la résistance 58 équivalente à l'ensemble des termes de perte (composante résistive de la charge).

Les caractéristiques de l'amplificateur vidéo qui vient d'être décrit sont les suivantes avec seulement trois transistors montés en série dans chaque branche de l'étage final amplificateur de courant :

- excursion de tension en sortie : 140 V

- gain global : 200

5

10

15

20

.. 25

30

35

- charge capacitive : 250 pF

- bande passante : 15 MHz

- courant dans la charge proportionnel à la fréquence et au niveau de tension,

- énergie dissipée au niveau de la charge uniquement due aux éléments parasites (ohmiques) de la charge et de la liaison à la charge ; elle représente une valeur faible par rapport

- · à l'énergie stockée ;

- quadrature du courant et de la tension dans la charge ; en conséquence les éléments actifs de l'amplificateur "Voient" la tension maximale (tension d'alimentation moins tension de sortie) en même temps que le courant maximal et donc dissipent des énergies instantanées importantes.

Le dispositif peut convenir à des charges plus élevées (500 à 700 pF) et à un domaine fréquentiel plus étendu (20 à 30 MHz) moyennant quelques aménagements :

- L'extension du domaine fréquentiel est lié à une amélioration de l'appairage de certains des composants actifs et à une compensation soignée des déphasages notamment dans le pont de répartition. Un deuxième pont équilibré avec l'étage final peut être nécessaire.

- L'augmentation de la charge signifie, corrélativement avec l'extension du domaine fréquentiel, une augmentation de la puissance de l'étage final. Bien que les composants disponibles actuellement ne permettent pas directement d'augmenter cette puissance, la mise en parallèle de plusieurs amplificateurs de courant permet de disposer de la puissance nécessaire, la sommation des courants étant effectuée dans la charge.

D'autre part la mise en oeuvre des "puces" assemblées dans une structure spécialement étudiée sous la forme d'un circuit intégré offre des possibilités particulièrement intéressantes :

- Augmentation des tenues en tension : "puces" disponibles en 200 volts et ayant la même rapidité que les "puces" de 90 volts.

5

10

- Augmentation de la capacité de dissipation en puissance, celle-ci dépendant directement de la résistance thermique. substrat/dissipateur, donc du boîtier.

- Réduction des capacités et self-inductances de câblage grâce à la simplification des connexions dont un nombre important va de "puce" à "puce".

On peut donc attendre de ces aménagements une amélioration sensible du coût de fabrication de série, de la fiabilité ainsi que de meilleures performances aux fréquences élevées.

## **REVENDICATIONS:**

5

10

15

20

25

30

- 1. Amplificateur vidéofréquence appliquant à une charge capacitive (8) un signal de sortie vidéo de grande amplitude obtenu à partir d'une source vidéo suivie d'étages préamplificateur (2) et amplificateur (3) de tension, préamplificateur (4) et amplificateur (5) de courant, caractérisé en ce que ledit étage amplificateur de tension de structure symétrique et constitué d'un premier étage et d'un deuxième étage à contre-réaction de courant montés en opposition comporte dans chacun desdits premier et deuxième étages des composants actifs (24,25, 26) complémentaires de ceux (24',25',26') de l'autre étage et assemblés en série pour permettre le fonctionnement sous les tensions élevées imposées par l'amplitude dudit signal vidéo de sortie, lesdits étages préamplificateur et amplificateur de courant étant de type push-pull symétrique et l'étage amplificateur comportant également dans chacune de ses branches un assemblage de structure série de composants actifs (44 à 49) complémentaires de ceux (44' à 49') de l'autre branche, lesdits assemblages de composants actifs étant alimentés par une première source de tension continue (V+, V-), la sortie dudit étage amplificateur de tension et l'entrée dudit étage préamplificateur de courant étant interconnectées sur la prise médiane d'un pont de répartition de tensions symétrique (31), compensé en fréquence et alimenté par une seconde source de tension continue (V++, V--), les prises réparties sur ledit pont étant reliées à des électrodes de commande des composants actifs dudit étage amplificateur de courant de façon à assurer l'équilibrage des tensions entre chacun desdits composants actifs, ledit étage préamplificateur de courant étant alimenté par deux potentiels pris en deux points intermédiaires symétriques sur le trajet du courant circulant dans les branches de l'étage amplificateur de courant.

- 2. Amplificateur vidéo selon la revendication l, caractérisé en ce que lesdits composants actifs sont des transistors MOS de type MOSFET à canal de type de conduction n et

p fonctionnant selon le mode dit à appauvrissement, les électrodes de commande, d'entrée et de sortie desdits composants actifs étant respectivement les grilles, les sources et les drains desdits transistors MOS.

5

10

15

20

25

30

35

Amplificateur vidéo selon les revendications 1 et 2, caractérisé en ce que chacun desdits premier et deuxième étages à contre-réaction de courant comporte à partir d'un circuit intermédiaire d'alignement (19,20,V<sub>p2</sub> ou 19',20',V'<sub>p2</sub>) : un étage suiveur constitué par un transistor MOS (21 ou 21') dont la grille est couplée par une première résistance d'entrée (22 ou 22') audit circuit intermédiaire d'alignement, dont le drain est relié à l'une des bornes de la seconde source de tension continue (V<sup>++</sup> ou V<sup>--</sup>) et dont la source est reliée à une borne d'une deuxième résistance de couplage d'entrée (23 ou 23') ; un assemblage en série de trois transistors MOS (24,25,26 ou 24',25', 26') complémentaires du transistor dudit étage suiveur, la grille du premier transistor (24 ou 24') étant reliée à l'autre borne de

la deuxième résistance de couplage d'entrée (23 ou 23'), les grilles des premier (24 ou 24'), deuxième (25 ou 25') et troisième (26 ou 26') transistors étant interconnectées à travers unc première (27 ou 27') et une deuxième (28 ou 28') impédance de réaction, la grille et le drain du troisième transistor (26 ou 26') étant reliés à travers une troisième impédance de réaction (29 ou 29'), la source du premier transistor (24 ou 24') étant reliée à l'une des bornes de la première source de tension continue (V<sup>+</sup> ou V<sup>-</sup>) à travers une impédance (30 ou 30') assurant la stabilité du point de fonctionnement et la compensation du gain aux fréquences élevées et le drain du troisième transistor (26 ou 26') étant relié à ladite sortie de l'étage amplificateur de tension.

4. Amplificateur vidéo selon les revendications 1 et 2, caractérisé en ce que chaque branche dudit étage préamplificateur de courant comporte un transistor MOS (38 ou 38') dont la grille est reliée au drain à travers un condensateur (39 ou 39') et à l'entrée de l'étage préamplificateur de courant à travers la

mise en série d'une résistance d'entrée (40 ou 40') formant avec ledit condensateur un réseau de compensation aux fréquences élevées et d'une première source de tension de polarisation (41 ou 41¹), la source dudit transistor étant reliée à la borne d'interconnexion de la sortie dudit étage préamplificateur de courant et de l'entrée dudit étage amplificateur de courant à travers une première résistance de sortie (43 ou 43'), chaque branche dudit étage amplificateur de courant comportant deux groupes de transistors MOS montés en parallèle, chaque groupe se composant de trois transistors assemblés en série (44,45,46 et 47,48,49 ou 44°,45°,46° et 47°,48°,49°), les grilles des deux premiers transistors correspondants de chaque groupe étant reliées à ladite borne d'interconnexion à travers une deuxième source de polarisation (50 ou 50°), l'une et l'autre sources desdits premiers transistors étant reliées à la sortie de l'étage amplificateur de courant, respectivement à travers une troisième (52 ou 52') et une quatrième (53 ou 53') résis tances de sortie, les drains desdits premiers transistors (46 et 49 ou 46' et 49') étant reliés au drain dudit transistor (38 ou 38') de l'étage préamplificateur de courant, les grilles des deuxièmes (45 et 48 ou 45° et 48°) et troisièmes (44 et 47 ou 44' et 47') transistors correspondants de chaque groupe étant reliées respectivement aux prises qui leurs correspondent sur le pont de répartition de tension (31), les drains desdits troisièmes transistors (44 et 47 ou 44% et 47°) étant interconnectés sur l'une des bornes de la première source de tension continue (V ou V).

30

5

10

15

20

25