US009853019B2

# (12) United States Patent

Clark et al.

# (54) INTEGRATED CIRCUIT DEVICE BODY BIAS CIRCUITS AND METHODS

(71) Applicant: Mie Fujitsu Semiconductor Limited,

Kuwana, MIE (JP)

(72) Inventors: Lawrence T. Clark, Phoenix, AZ (US);

**David A. Kidd**, San Jose, CA (US); **Augustine Kuo**, Berkeley, CA (US)

(73) Assignee: Mie Fujitsu Semiconductor Limited,

Kuwana (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 15/337,876

(22) Filed: Oct. 28, 2016

(65) Prior Publication Data

US 2017/0047100 A1 Feb. 16, 2017

# Related U.S. Application Data

- (63) Continuation of application No. 14/799,715, filed on Jul. 15, 2015, now Pat. No. 9,548,086, which is a (Continued)

- (51) Int. Cl. H03K 17/06 (2006.01) H01L 27/02 (2006.01)

- (Continued)

(52) **U.S. CI.**CPC ............. *H01L 27/0222* (2013.01); *G05F 3/205* (2013.01); *G06F 17/5045* (2013.01); (Continued)

(58) Field of Classification Search

CPC ...... G11C 5/146; H02M 2003/078; H02M 2003/076; H03K 2217/0018

See application file for complete search history.

# (10) Patent No.: US 9,853,019 B2

(45) **Date of Patent: Dec. 26, 2017**

# (56) References Cited

## U.S. PATENT DOCUMENTS

3,958,266 A 4,000,504 A 5/1976 Athanas 12/1976 Berger (Continued)

# FOREIGN PATENT DOCUMENTS

EP 0274278 7/1988 JP 59193066 1/1984 (Continued)

# OTHER PUBLICATIONS

Tschanz et al., "Adaptive Body Bias for Reducing Impacts of Die-to-Die and Within-Die Parameter Variations on Microprocessor Frequency and Leakage," IEEE Journal of Solid-State Circuits, vol. 37, No. 11, Nov. 2002.

(Continued)

Primary Examiner — Thomas J Hiltunen (74) Attorney, Agent, or Firm — Baker Botts L.L.P.

# (57) ABSTRACT

A system having an integrated circuit (IC) device can include a die formed on a semiconductor substrate and having a plurality of first wells formed therein, the first wells being doped to at least a first conductivity type; a global network configured to supply a first global body bias voltage to the first wells; and a first bias circuit corresponding to each first well and configured to generate a first local body bias for its well having a smaller setting voltage than the first global body bias voltage; wherein at least one of the first wells is coupled to a transistor having a strong body coefficient formed therein, which transistor may be a transistor having a highly doped region formed below a substantially undoped channel, the highly doped region having a dopant concentration greater than that the corresponding well.

# 3 Claims, 14 Drawing Sheets

# US 9,853,019 B2

Page 2

|       | Related U.S. Ap                                | oplication Data                    | 6,184,112                  |                          | Maszara et al.                   |              |

|-------|------------------------------------------------|------------------------------------|----------------------------|--------------------------|----------------------------------|--------------|

|       | 4:4:£1:                                        | 4: NI- 12/929 221 - 61-4           | 6,190,979                  |                          | Radens et al.                    |              |

|       |                                                | tion No. 13/838,221, filed on      | 6,194,259 I<br>6,218,895 I |                          | Nayak et al.<br>De et al.        |              |

|       | Mar. 15, 2013, now Par                         | t. No. 9,112,495.                  | 6,229,188 1                |                          | Aoki et al.                      |              |

| (51)  | T                                              |                                    | 6,245,618                  |                          | An et al.                        |              |

| (51)  | Int. Cl.                                       |                                    | 6,288,429 1                |                          | Iwata et al.                     |              |

|       | G11C 5/14                                      | (2006.01)                          | 6,300,177                  | B1 10/2001               | Sundaresan et al.                |              |

|       | H03K 3/012                                     | (2006.01)                          | 6,301,184                  | B1 * 10/2001             | Sasaki                           |              |

|       | $G06F\ 17/50$                                  | (2006.01)                          | 6 2 12 400 1               | D.1 11/2001              | T -4                             | 365/226      |

|       | $G05F\ 3/20$                                   | (2006.01)                          | 6,313,489 1<br>6,320,222 1 | BI 11/2001<br>BI 11/2001 | Letavic et al.<br>Forbes et al.  |              |

|       | H01L 27/092                                    | (2006.01)                          | 6,326,666                  | B1 12/2001               | Bernstein et al.                 |              |

|       | G11C 5/02                                      | (2006.01)                          | 6,358,806 1                |                          | Puchner                          |              |

|       | H02M 3/07                                      | (2006.01)                          | 6,380,019 1                | B1 4/2002                |                                  |              |

| (52)  | U.S. Cl.                                       | `                                  | 6,391,752 1                |                          | Colinge et al.                   |              |

| . ,   |                                                | 5/025 (2013.01); G11C 5/146        | 6,426,279 I<br>6,444,550 I |                          | Huster et al.<br>Hao et al.      |              |

|       |                                                | 5/147 (2013.01); G11C 5/148        | 6,444,551                  |                          |                                  |              |

|       |                                                | 1L 27/0928 (2013.01); H03K         | 6,461,920 1                |                          | Shirahata                        |              |

|       |                                                | 01); <i>H03K 17/063</i> (2013.01); | 6,461,928 1                |                          | Rodder                           |              |

|       |                                                | 6 (2013.01); <i>H02M 2003/078</i>  | 6,472,278 1                |                          | Marshall et al.                  |              |

|       |                                                | ; <i>H03K 2217/0018</i> (2013.01)  | 6,482,714 I<br>6,484,252 I |                          | Hieda et al.<br>Watanabe         |              |

|       | (2013.01)                                      | , 110311 221//0010 (2013.01)       | 6,489,224                  |                          |                                  |              |

| (56)  | Referenc                                       | es Cited                           | 6,492,232                  | B1 12/2002               | Tang et al.                      |              |

| (= =) |                                                |                                    | 6,500,739 1                | B1 12/2002               | Wang et al.                      |              |

|       | U.S. PATENT I                                  | DOCUMENTS                          | 6,503,801 1                |                          | Rouse et al.                     |              |

|       |                                                |                                    | 6,506,640 1<br>6,518,623 1 | BI 1/2003                | Ishida et al.<br>Oda et al.      |              |

|       |                                                | Etoh et al.                        | 6,534,373                  |                          |                                  |              |

|       | 4,208,728 A 6/1980 1<br>4,242,691 A 12/1980 1  | Blahut et al.<br>Kotani            | 6,541,829                  | B2 4/2003                | Nishinohara et al.               |              |

|       |                                                | Beilstein, Jr. et al.              | 6,548,842                  |                          | Bulucea et al.                   |              |

|       | 4,315,781 A 2/1982 I                           | Henderson                          | 6,551,885 1<br>6,573,129 1 | B1 4/2003                | Yu<br>Hoke et al.                |              |

|       |                                                | Mundt et al.                       | 6,600,200                  |                          | Lustig et al.                    |              |

|       | 4,617,066 A 10/1986 \<br>4,761,384 A 8/1988 I  | vasudev<br>Neppl et al.            | 6,620,671                  |                          | Wang et al.                      |              |

|       | 4,819,043 A 4/1989                             | Yazawa et al.                      | 6,624,488 1                |                          |                                  |              |

|       | 5,034,337 A 7/1991 I                           | Mosher et al.                      | 6,630,710 1                |                          | Augusto<br>Mizuno l              | H02V 10/0016 |

|       | 5,144,378 A 9/1992 I                           |                                    | 6,630,857                  | BZ · 10/2003             | MIZUIO                           | 327/391      |

|       | 5,156,989 A 10/1992 S<br>5,156,990 A 10/1992 B | Williams et al.<br>Mitchell        | 6,660,605                  | B1 12/2003               | Liu                              | 3211331      |

|       | 5,166,765 A 11/1992 I                          |                                    | 6,667,200 1                | B2 12/2003               | Sohn et al.                      |              |

|       | 5,208,473 A 5/1993 I                           | Komori et al.                      | 6,670,260 1                |                          | Yu et al.                        |              |

|       |                                                | Shen et al.                        | 6,693,333 I<br>6,730,568 I |                          | Yu<br>Sohn                       |              |

|       | 5,369,288 A 11/1994 T<br>5,384,476 A 1/1995 T  | Usuki<br>Nishizawa et al.          | 6,737,724                  |                          | Hieda et al.                     |              |

|       | 5,461,338 A 10/1995 1                          | Hirayama et al.                    | 6,743,291 1                | B2 6/2004                | Ang et al.                       |              |

|       | 5,557,231 A * 9/1996 `                         | Yamaguchi G11C 5/146               | 6,753,230 1                |                          | Sohn et al.                      |              |

|       |                                                | 257/E27.081                        | 6,770,944 I<br>6,787,424 I | B2 8/2004<br>B1 9/2004   | Nishinohara et al.               |              |

|       | 5,559,368 A 9/1996 1<br>5,608,253 A 3/1997 1   |                                    | 6,788,130 1                |                          | Pauletti                         | H02M 3/073   |

|       |                                                | Matloubian et al.                  | , ,                        |                          |                                  | 327/536      |

|       | 5,712,501 A 1/1998 1                           | Davies et al.                      | 6,797,994 1                |                          | Hoke et al.                      |              |

|       |                                                | Burr et al.                        | 6,808,994 I<br>6,821,825 I |                          | Wang<br>Todd et al.              |              |

|       |                                                | Watanabe<br>Okumura et al.         | 6,822,297                  |                          | Nandakumar et al.                |              |

|       | 5,780,899 A 7/1998 I                           |                                    | 6,831,292                  |                          | Currie et al.                    |              |

|       | 5,847,419 A 12/1998 I                          |                                    | 6,881,641                  |                          | Wieczorek et al.                 |              |

|       | 5,856,003 A 1/1999 G                           |                                    | 6,881,987                  |                          | Sohn                             |              |

|       | 5,861,334 A 1/1999 1                           |                                    | 6,893,947 1<br>6,916,698 1 |                          | Martinez et al.<br>Mocuta et al. |              |

|       | 5,877,049 A 3/1999 I<br>5,889,315 A 3/1999 I   | Liu<br>Farrenkopf et al.           | 6,930,007                  |                          | Bu et al.                        |              |

|       |                                                | Yasumura et al.                    | 6,930,360 1                |                          | Yamauchi et al.                  |              |

|       | 5,923,987 A 7/1999 I                           |                                    | 6,963,090 1                |                          | Passlack et al.                  |              |

|       |                                                | Yamaguchi et al.                   | 7,002,214 1<br>7,008,836 1 |                          | Boyd et al.<br>Algotsson et al.  |              |

|       | 5,989,963 A 11/1999 I<br>6,020,227 A 2/2000 I  | Luning et al.                      | 7,008,830 1                | B1 3/2006                |                                  |              |

|       |                                                | Itoh G11C 5/146                    | 7,015,546 1                | B2 3/2006                | Herr et al.                      |              |

|       |                                                | 257/E27.062                        | 7,057,216 1                |                          | Ouyang et al.                    |              |

|       | 6,087,210 A 7/2000 S                           |                                    | 7,061,058 1<br>7,064,039 1 |                          | Chakravarthi et al.              |              |

|       | 6,087,691 A 7/2000 1<br>6,096,611 A 8/2000 1   | Hamamoto<br>Wu                     | 7,064,399 1                |                          | Babcock et al.                   |              |

|       | 6,103,562 A 8/2000 S                           |                                    | 7,071,103                  | B2 7/2006                | Chan et al.                      |              |

|       | 6,121,153 A 9/2000 I                           | Kikkawa                            | 7,078,325 1                |                          | Curello et al.                   |              |

|       |                                                | Kaviani et al.                     | 7,078,776                  |                          | Nishinohara et al.               |              |

|       | 6,147,383 A 11/2000 I<br>6,157,073 A 12/2000 I |                                    | 7,089,515 I<br>7,106,128 I |                          | Hanafi et al.<br>Tschanz et al.  |              |

|       |                                                | Naito et al.                       | 7,119,381 1                |                          | Passlack et al.                  |              |

|       | , -,                                           |                                    | .,115,551 1                |                          |                                  |              |

# US 9,853,019 B2

Page 3

| (56) |                    |      | Referen          | ces Cited                        |                 | 7,723,750                    |      | 5/2010  | Zhu<br>Nowak                         |

|------|--------------------|------|------------------|----------------------------------|-----------------|------------------------------|------|---------|--------------------------------------|

|      |                    | TI C | DATENIT          | DOCUMENTS                        |                 | 7,750,405<br>7,750,670       |      |         | Goodnow et al.                       |

|      |                    | U.S  | PAIENI           | DOCUMENTS                        |                 | 7,750,682                    |      |         | Bernstein et al.                     |

| 7    | 138,851            | D2   | 11/2006          | Cumita                           |                 | 7,755,146                    |      |         | Helm et al.                          |

|      | 164,307            |      |                  | Tschanz et al.                   |                 | 7,759,714                    |      | 7/2010  | Itoh et al.                          |

|      | 170,120            |      |                  | Datta et al.                     |                 | 7,795,677                    |      | 9/2010  | Bangsaruntip et al.                  |

|      | 176,745            |      |                  | Itoh et al.                      |                 | 7,800,404                    |      | 9/2010  | Verma et al.                         |

| 7,   | 186,598            | B2   |                  | Yamauchi et al.                  |                 | 7,812,662                    | B2 * | 10/2010 | Lundberg G05F 3/205                  |

|      | 189,627            |      |                  | Wu et al.                        |                 | 7.010.702                    | Da   | 10/2010 | 327/534                              |

|      | 199,430            |      |                  | Babcock et al.                   |                 | 7,818,702<br>7,829,402       |      |         | Mandelman et al.<br>Matocha et al.   |

|      | 202,517<br>211,871 |      | 5/2007           | Dixit et al.                     |                 | 7,867,835                    |      |         | Lee et al.                           |

|      | 221,021            |      |                  | Wu et al.                        |                 | 7,883,977                    | B2   |         | Babcock et al.                       |

|      | 223,646            |      |                  | Miyashita et al.                 |                 | 7,888,747                    | B2   |         | Hokazono et al.                      |

|      | 226,833            |      |                  | White et al.                     |                 | 7,897,495                    |      |         | Ye et al.                            |

|      | 226,843            |      |                  | Weber et al.                     |                 | 7,906,413                    |      |         | Cardone et al.                       |

|      | 235,822            |      | 6/2007           |                                  |                 | 7,906,813                    |      |         | Kato et al.                          |

|      | 236,045            |      |                  | Tschanz et al.<br>Oh et al.      |                 | 7,919,791<br>7,948,008       |      |         | Flynn et al.<br>Liu et al.           |

|      | 247,896<br>294,877 |      |                  | Rueckes et al.                   |                 | 7,952,147                    |      |         | Ueno et al.                          |

|      | 297,994            |      |                  | Wieczorek et al.                 |                 | 7,960,232                    |      |         | King et al.                          |

|      | 301,208            |      |                  | Handa et al.                     |                 | 7,960,238                    |      |         | Kohli et al.                         |

|      | 304,350            |      | 12/2007          |                                  |                 | 7,968,400                    |      | 6/2011  |                                      |

|      | 312,500            |      |                  | Miyashita et al.                 |                 | 7,968,411                    |      |         | Williford                            |

|      | 323,754            |      |                  | Ema et al.                       | *****           | 7,978,001                    | B2 * | 7/2011  | Bertram H03K 19/0013                 |

| 7,   | 330,049            | B2 * | 2/2008           | Perisetty                        |                 | 8,004,024                    | R2   | 8/2011  | Furukawa et al.                      |

| 7    | 332,439            | B2   | 2/2008           | Lindert et al.                   | 257/E27.063     | 8,012,827                    |      |         | Yu et al.                            |

|      | 348,629            |      |                  | Chu et al.                       |                 | 8,039,332                    |      |         | Bernard et al.                       |

|      | 354,833            |      | 4/2008           |                                  |                 | 8,048,791                    |      |         | Hargrove et al.                      |

| 7,   | 355,437            | B2*  |                  | Perisetty                        | H03K 19/00315   | 8,048,810                    |      |         | Tsai et al.                          |

|      |                    |      |                  |                                  | 326/14          | 8,067,279                    |      |         | Sadra et al.                         |

|      | 427,788            |      |                  | Li et al.                        |                 | 8,105,891<br>8,106,424       |      |         | Yeh et al.<br>Schruefer              |

|      | 442,971            |      |                  | Wirbeleit et al.                 |                 | 8,106,481                    |      | 1/2012  |                                      |

|      | 443,641<br>462,908 |      | 10/2008          | Bol et al.                       |                 | 8,112,551                    |      |         | Sullam et al.                        |

|      | 485,536            |      |                  | Jin et al.                       |                 | 8,119,482                    |      | 2/2012  | Bhalla et al.                        |

|      | 491,988            |      | 2/2009           | Tolchinsky et al.                |                 | 8,120,069                    |      |         | Hynecek                              |

|      | 494,861            |      | 2/2009           | Chu et al.                       |                 | 8,129,246                    |      |         | Babcock et al.                       |

|      | 498,637            |      |                  | Yamaoka et al.                   |                 | 8,129,797<br>8,134,159       |      |         | Chen et al.<br>Hokazono              |

| 7,   | 501,324            | B2   |                  | Babcock                          | 110217 10/00215 | 8,143,120                    |      |         | Kerr et al.                          |

| /,   | 501,849            | B2 * | 3/2009           | Perisetty                        | 326/15          | 8,143,124                    |      | 3/2012  |                                      |

| 7    | 507,999            | B2   | 3/2009           | Kusumoto et al.                  | 320/13          | 8,143,678                    |      | 3/2012  |                                      |

| 7.   | 510,932            | B2   |                  | Oh et al.                        |                 | 8,148,774                    |      |         | Mori et al.                          |

|      | 514,953            |      |                  | Perisetty                        |                 | 8,163,619                    |      | 4/2012  | Yang et al.                          |

| 7,   | 521,323            | B2   |                  | Surdeanu                         |                 | 8,173,502                    |      |         | Yan et al.<br>Kim et al.             |

|      | 531,393            |      | 5/2009           |                                  |                 | 8,178,430<br>8,183,096       |      |         | Wirbeleit                            |

|      | 538,412            |      |                  | Schulze                          |                 | 8,183,107                    |      |         | Mathur et al.                        |

|      | 555,667<br>564,105 |      | 7/2009           | Burney                           |                 | 8,217,427                    |      | 7/2012  | Chuang et al.                        |

|      | 592,241            |      | 9/2009           |                                  |                 | 8,236,661                    |      | 8/2012  | Dennard et al.                       |

|      | 592,832            |      | 9/2009           | Perisetty                        | H03K 19/0013    | 8,970,289                    |      | 3/2015  |                                      |

|      |                    |      |                  | ·                                | 326/37          | 9,112,495<br>9,251,866       |      |         | Clark H03K 17/063<br>Chun G11C 5/146 |

| . ,  | 598,142            |      | 10/2009          |                                  |                 | 9,431,068                    |      |         | Clark G11C 5/146                     |

|      | 605,041<br>605,060 |      | 10/2009          | Ema<br>Meunier-Beillard          | at al           | 2001/0014495                 |      | 8/2001  |                                      |

| ,    | 605,429            |      |                  | Bernstein et al.                 | et al.          | 2003/0122203                 | A1   | 7/2003  | Nishinohara et al.                   |

|      | 608,496            |      | 10/2009          |                                  |                 | 2003/0183856                 |      |         | Wieczorek et al.                     |

|      | 615,802            |      |                  | Elpelt et al.                    |                 | 2004/0075118                 |      |         | Heinemann et al.                     |

|      | 622,341            |      |                  | Chudzik et al.                   |                 | 2004/0084731<br>2004/0263205 |      | 12/2004 | Matsuda et al.                       |

| 7,   | 639,041            | B1 * | 12/2009          | Perisetty                        |                 | 2005/0097196                 |      |         | Wronski et al.                       |

|      |                    |      |                  |                                  | 326/38          | 2005/0116282                 |      |         | Pattanavak                           |

|      | 642,140            |      |                  | Bae et al.                       |                 | 2005/0250289                 | A1   | 11/2005 | Babcock et al.                       |

| ,    | 645,665            |      |                  | Kubo et al.                      |                 | 2006/0022270                 |      |         | Boyd et al.                          |

|      | 651,920<br>655,523 |      | 1/2010<br>2/2010 | Siprak<br>Babcock et al.         |                 | 2006/0049464                 |      | 3/2006  |                                      |

|      | 667,527            |      |                  | Clark et al.                     |                 | 2006/0066388<br>2006/0068555 |      |         | Tschanz et al. Zhu et al.            |

|      | 675,126            |      | 3/2010           |                                  |                 | 2006/0068586                 |      | 3/2006  |                                      |

|      | 675,317            |      |                  | Perisetty                        |                 | 2006/0071278                 |      | 4/2006  |                                      |

|      | 678,638            |      |                  | Chu et al.                       |                 | 2006/0154428                 |      |         | Dokumaci                             |

| ,    | 681,628            |      |                  | Joshi et al.                     |                 | 2007/0004107                 |      |         | Lee et al.                           |

|      | 682,887            |      |                  | Dokumaci et al.                  |                 | 2007/0040222                 |      |         | Van Camp et al.                      |

|      | 683,442            |      |                  | Burr et al.                      |                 | 2007/0158790                 |      | 7/2007  |                                      |

| ,    | 696,000            |      |                  | Liu et al.                       |                 | 2007/0238253                 |      | 10/2007 |                                      |

| ,    | 704,844            |      |                  | Zhu et al.<br>Braithwaite et al. |                 | 2008/0001171<br>2008/0067589 |      |         | Tezuka et al.<br>Ito et al.          |

| /,   | 709,828            | DΖ   | 3/2010           | Dialinwaite et al.               |                 | 2006/000/389                 | AI   | 3/2008  | no et al.                            |

#### (56)References Cited

# U.S. PATENT DOCUMENTS

| 2008/0143423 | $\mathbf{A}1$ | 6/2008  | Komatsu et al.   |            |

|--------------|---------------|---------|------------------|------------|

| 2008/0169493 | A1            | 7/2008  | Lee et al.       |            |

| 2008/0197439 | $\mathbf{A}1$ | 8/2008  | Goerlach et al.  |            |

| 2008/0227250 | $\mathbf{A}1$ | 9/2008  | Ranade et al.    |            |

| 2008/0246533 | $\mathbf{A}1$ | 10/2008 | Barrows et al.   |            |

| 2008/0258198 | $\mathbf{A}1$ | 10/2008 | Bojarczuk et al. |            |

| 2008/0272409 | A1            | 11/2008 | Sonkusale et al. |            |

| 2009/0057746 | A1            | 3/2009  | Sugll et al.     |            |

| 2009/0108350 | $\mathbf{A1}$ | 4/2009  | Cai et al.       |            |

| 2009/0134468 |               | 5/2009  | Tsuchiya         |            |

|              | A1            | 7/2009  | Hidaka           |            |

| 2009/0302388 |               | 12/2009 | Cai              |            |

| 2009/0311837 |               | 12/2009 | Kapoor           |            |

| 2009/0321849 |               | 12/2009 | Miyamura et al.  |            |

| 2010/0012988 |               | 1/2010  | Yang et al.      |            |

| 2010/0038724 |               | 2/2010  | Anderson et al.  |            |

| 2010/0055886 |               | 3/2010  | Izumida et al.   |            |

| 2010/0073073 |               | 3/2010  |                  |            |

| 2010/0187641 | $\mathbf{A}1$ | 7/2010  | Zhu et al.       |            |

| 2011/0073961 | $\mathbf{A}1$ | 3/2011  | Dennard et al.   |            |

| 2011/0074498 | A1            | 3/2011  | Thompson         |            |

| 2011/0079860 | $\mathbf{A}1$ | 4/2011  | Verhulst et al.  |            |

| 2011/0079861 | A1            | 4/2011  | Shifren et al.   |            |

| 2011/0169082 | $\mathbf{A}1$ | 7/2011  | Zhu et al.       |            |

| 2011/0175170 | $\mathbf{A}1$ | 7/2011  | Wang et al.      |            |

| 2011/0180880 | $\mathbf{A}1$ | 7/2011  | Chudzik et al.   |            |

| 2011/0193164 | $\mathbf{A}1$ | 8/2011  | Zhu              |            |

| 2012/0021594 | $\mathbf{A}1$ | 1/2012  | Gurtej et al.    |            |

| 2012/0056275 | $\mathbf{A}1$ | 3/2012  | Cai et al.       |            |

| 2012/0108050 | A1            | 5/2012  | Chen et al.      |            |

| 2012/0190177 | A1            | 7/2012  | Kim et al.       |            |

| 2014/0119099 |               | 5/2014  | Clark            |            |

| 2014/0307513 |               | 10/2014 | Chun             | G11C 5/140 |

|              |               |         |                  | 365/189.09 |

|              |               |         |                  |            |

# 2015/0318026 A1 11/2015 Clark

# FOREIGN PATENT DOCUMENTS

| JP | 4186774       | 3/1992  |

|----|---------------|---------|

| JP | 8288508       | 1/1996  |

| JP | 8153873       | 6/1996  |

| JP | 2004087671    | 3/2004  |

| KR | 1020040024599 | 10/2005 |

| WO | 2011062788    | 5/2011  |

# OTHER PUBLICATIONS

Werner, P. et al., "Carbon Diffusion in Silicon," Applied Physics Letters, vol. 73, No. 17, pp. 2465-2467, Oct. 1998.

Yan, Ran-Hong et al., "Scaling the Si MOSFET: From Bulk to SOI to Bulk," IEEE Transactions on Electron Devices, vol. 39, No. 7, Jul. 1992.

Abiko, H. et al., "A Channel Engineering Combined with Channel Epitaxy Optimization and RED Suppression for 0.15µm n-n Gate

CMOS Technology." 1995 Symposium on VLSI Technology Digest of Technical Papers, pp. 23-24, 1995.

Chau, R. et al., "A 50nm Depleted-Substrate CMOS Transistor (DST)", Electron Device Meeting 2001, IEDM Technical Digest,

IEEE International, pp. 29.1.1-29.1.4, 2001.

Ducroquet, F. et al. "Fully Depleted Silicon-On Insulator nMOSFETs with Tensile Strained High Carbon Content Sil-yCy Channel", ECS 210th Meeting, Abstract 1033, 2006.

English Translation of JP 815383, 1996.

Ernst, T. et al., "Nanoscaled MOSFET Transistors on Strained Si, SiGe, Ge Layers: Some Integration and Electrical Properties Features", ECS Trans. 2006, vol. 3, Issue 7, pp. 947-961, 2006.

Goesele, U. et al., "Diffusion Engineering by Carbon in Silicon",

Mat. Res. Soc. Symp. vol. 610, pp. 1-12, 2000. Hokazono, A. et al., "Steep Channel & Halo Profiles Utilizing Boron-Diffusion-Barrier Layers (Si:C) for 32 nm Node and Beyond", 2008 Symposium on VLSI Technology Digest of Tech-

nical Papers, pp. 112-113, 2008. Hokazono, A. et al., "Steep Channel Profiles in n/pMOS Controlled by Boron-Doped Si:C Layers for Continual Bulk-CMOS Scaling", IEDM09-676 Symposium, pp. 29.1.1-29.1.4, 2009.

Holland, OW and Thomas, DK "A Method to Improve Activation of Implanted Dopants in SiC", Oak Ridge National Laboratory, Oak Ridge, TN, pp. 1-9, 2001.

Kotaki, H., et al., "Novel Bulk Dynamic Threshold Voltage MOSFET (B-DTMOS) with Advanced Isolation (SITOS) and Gate to Shallow-Well Contact (SSS-C) Processes for Ultra Low Power Dual Gate CMOS", IEDM 96, pp. 459-462, 1996.

Lavéant, P. "Incorporation, Diffusion and Agglomeration of Carbon in Silicon", Solid State Phenomena, vols. 82-84, pp. 189-194, 2002. Noda, K. et al., "A 0.1-µm Delta-Doped MOSFET Fabricated with Post-Low-Energy Implanting Selective Epitaxy" IEEE Transactions on Electron Devices, vol. 45, No. 4, pp. 809-814, Apr. 1998.

Ohguro, T. et al., "An 0.18-um CMOS for Mixed Digital and Analog Applications with Zero-Volt-Vth Epitaxial-Channel MOSFET's", IEEE Transactions on Electron Devices, vol. 46, No. 7, pp. 1378-1383, Jul. 1999.

Pinacho, R. et al., "Carbon in Silicon: Modeling of Diffusion and Clustering Mechanisms", Journal of Applied Physics, vol. 92, No. 3, pp. 1582-1588, Aug. 2002.

Robertson, LS et al., "The Effect of Impurities on Diffusion and Activation of Ion Implanted Boron in Silicon", Mat. Res. Soc. Symp. vol. 610, 2000.

Scholz, R. et al., "Carbon-Induced Undersaturation of Silicon Self-Interstitials", Appl. Phys. Lett. 72(2), pp. 200-202, Jan. 1998. Scholz, RF et al., "The Contribution of Vacancies to Carbon Out-Diffusion in Silicon", Appl. Phys. Lett., vol. 74, No. 3, pp. 392-394, Jan. 1999.

Stolk, PA et al., "Physical Mechanisms of Transient Enhanced Dopant Diffusion in Ion-Implanted Silicon", J. Appl. Phys. 81(9), pp. 6031-6050, May 1997.

Thompson, S. et al., "MOS Scaling: Transistor Challenges for the 21st Century", Intel Technology Journal Q3' 1998, pp. 1-19, 1998. Wann, C., et al., "Channel Profile Optimization and Devices Design for Low-Power High-Performance Dynamic Threshold MOSFET", IEDM 96, pp. 113-116.

\* cited by examiner

FIG. 1

FIG. 3

FIG. 4

VBB\_Global LOCAL BIAS LOCAL BIAS CIRCUIT BLKn CIRCUIT BLK0 CTRLn' CTRL0 • 612-0 612-n VBB BLK0 VBB BLKn COLLAPSE **EVENT EVENT** COLLAPSE Coll\_EN0 Coll\_ENn. DETECT CIRCUIT DETECT CIRCUIT BLK0 BLK0 BLKn BLKn 630-0 630-n 626-n 626-0 VCollapse

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10A

Dec. 26, 2017

FIG. 10B

FIG. 11B

1228-P VGlobal 1246'

Cx 1256 1236' VBP 1244'

Coll\_ENN 1240' 1208'

FIG. 12B

FIG. 14

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

FIG. 21

Dec. 26, 2017

FIG. 22

FIG. 23A

FIG. 23B

FIG. 23C

# INTEGRATED CIRCUIT DEVICE BODY **BIAS CIRCUITS AND METHODS**

### RELATED APPLICATIONS

This application is a continuation of U.S. Application Ser. No. is a continuation of U.S. application Ser. No. 14/799,715 filed Jul. 15, 2015 and entitled "Integrated Circuit Device Body Bias Circuits and Methods" which is a continuation of Ser. No. 13/838,221 filed Mar. 15, 2013 and entitled "Integrated Circuit Device Body Bias Circuits and Methods", now U.S. Pat. No. 9,112,495 which issued Aug. 18, 2015, the entirety of which is hereby incorporated by reference.

## TECHNICAL FIELD

The present invention relates generally to body biasing circuit solutions for systems including an integrated circuit (IC) device, and more particularly to body biasing circuit 20 techniques that provide different body bias voltages to different blocks of an IC device.

## **BACKGROUND**

Integrated circuit (IC) devices can include n-channel and p-channel transistors. In some IC devices, one or both types of transistors can be formed in wells. To increase the absolute value of the threshold voltage, the wells can be reverse biased ("back" biased). Thus, n-wells containing p-channel transistors can be reverse biased to a positive voltage greater than a high power supply for the transistors. Conversely, p-wells containing n-channel transistors can be reverse biased to a voltage more negative than their low source voltage (i.e., a voltage lower than ground).

Under certain operating conditions, IC devices can be subject to current transient events. Such events can result in a "droop" of a power supply voltage, which can slow the operation of some circuits. Conventionally, such circuits are mance, to ensure proper operation in the event of a current transient event. Further, in some conventional approaches, in response to current transient events, the IC device can increase a reverse body bias voltage (increase the setting of a reverse body bias).

# BRIEF DESCRIPTION OF THE DRAWINGS

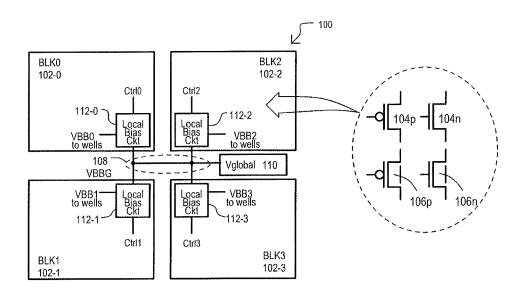

FIG. 1 is a block schematic diagram of an integrated circuit (IC) device according to one embodiment.

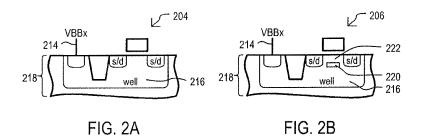

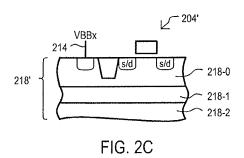

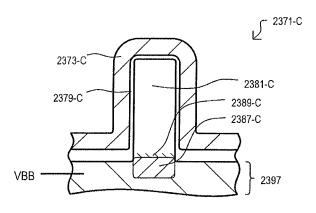

FIGS. 2A to 2C are side cross sectional representations showing body bias connections that can be included in embodiments.

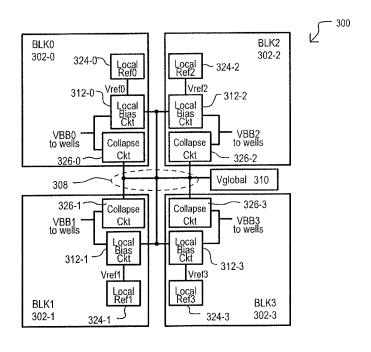

FIG. 3 is a block schematic diagram of an IC device according to another embodiment.

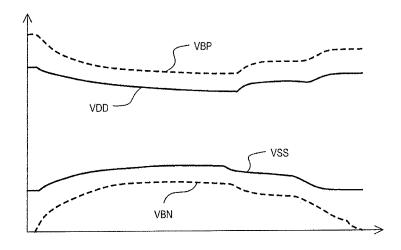

FIG. 4 is a graph showing reductions in body bias voltage during current transient events according to one particular embodiment.

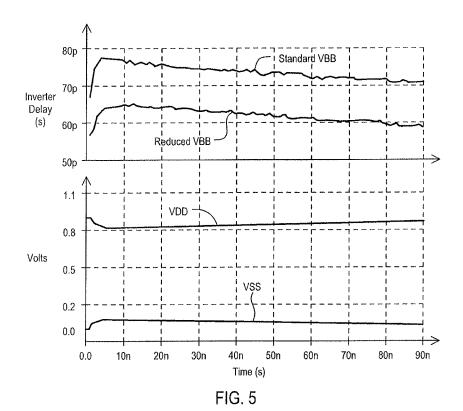

FIG. 5 shows graphs of how reductions in body bias voltage can increase circuit speed during current transient 60

FIG. 6 is a block schematic diagram of a body bias control circuit according to an embodiment.

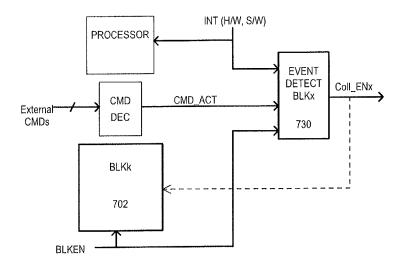

FIG. 7 is block schematic diagram of an event detect circuit that can be included in embodiments.

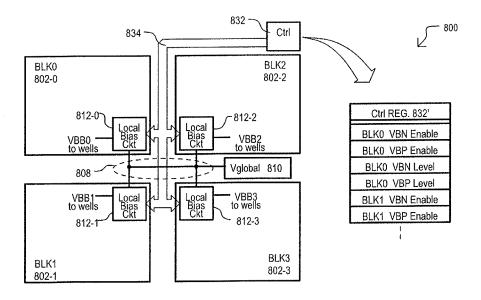

FIG. 8 is a block schematic diagram of an IC device according to another embodiment.

2

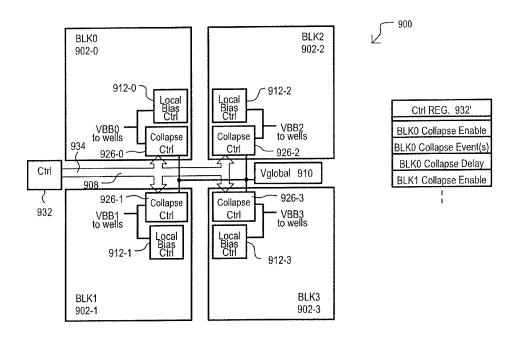

FIG. 9 is a block schematic diagram of an IC device according to a further embodiment.

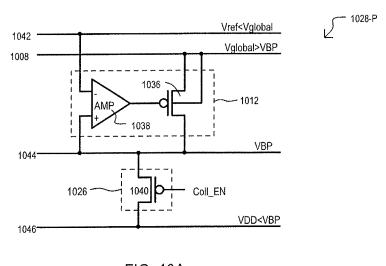

FIGS. 10A and 10B are schematic diagrams of body bias control circuits according to embodiments.

FIGS. 11A and 11B are schematic diagrams of local bias circuits according to embodiments.

FIGS. 12A and 12B are schematic diagrams of body bias control circuits according to further embodiments.

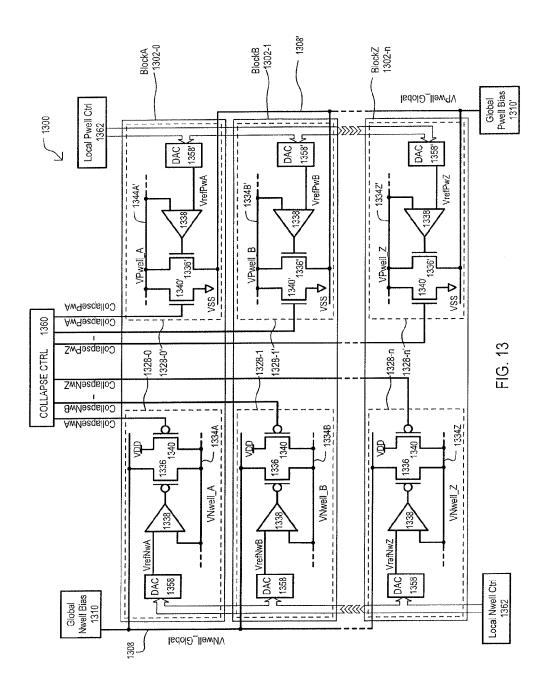

FIG. 13 is a block schematic diagram of an IC device according to another embodiment.

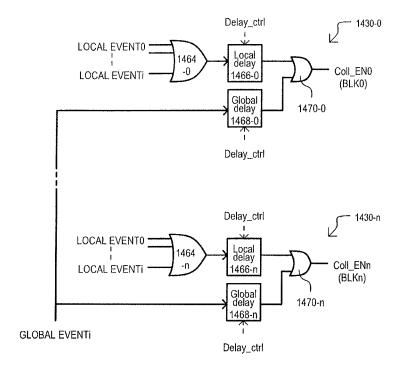

FIG. 14 is block schematic diagram of event detect circuits that can be included in embodiments.

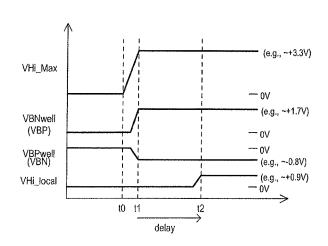

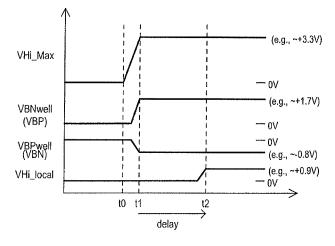

FIG. 15 is a timing diagram showing a power-up operation of an IC device according to an embodiment.

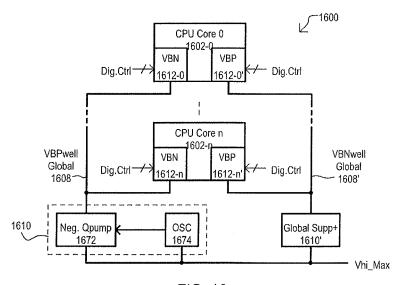

FIG. 16 is a block schematic diagram of an IC device according to another embodiment.

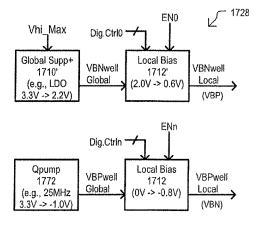

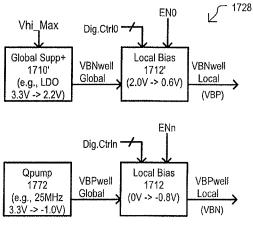

FIG. 17 is a block schematic diagram of a body bias control circuit that can be included in an IC device like that of FIG. 16, according to an embodiment.

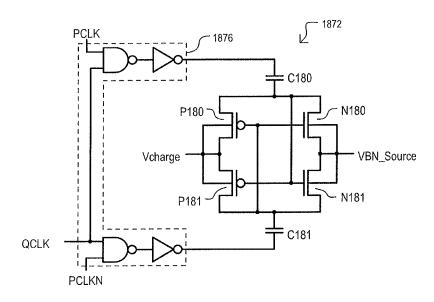

FIG. 18 is a schematic diagram of a charge pump circuit that can be included in embodiments.

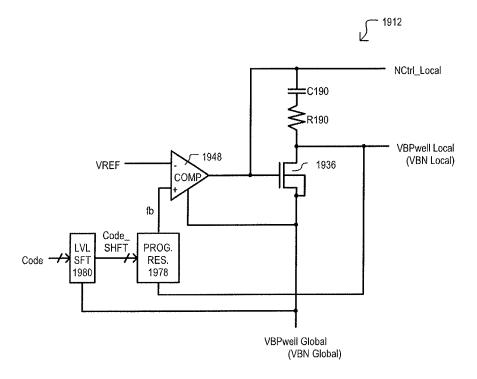

FIG. 19 is a block schematic diagram of a local bias circuit that can be included in an IC device like that of FIG. 16, according to an embodiment.

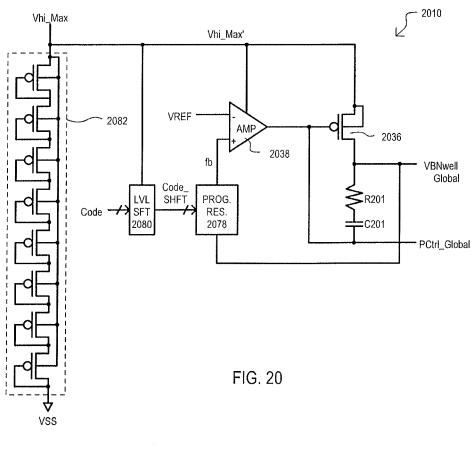

FIG. 20 is a block schematic diagram of a global bias supply circuit that can be included in an IC device like that of FIG. 16, according to an embodiment.

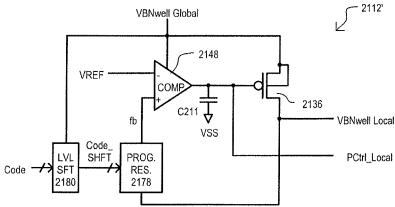

FIG. 21 is a block schematic diagram of another local bias circuit that can be included in an IC device like that of FIG. 16, according to an embodiment.

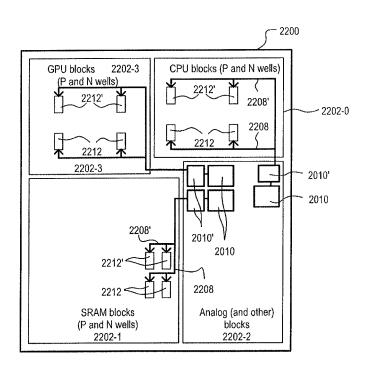

FIG. 22 is a top plan view of an IC device like that of FIG. 16, according to one particular embodiment.

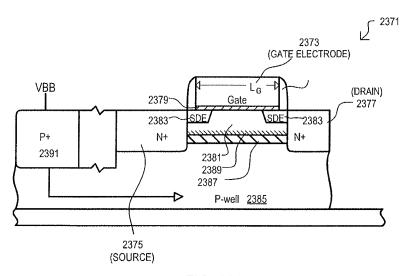

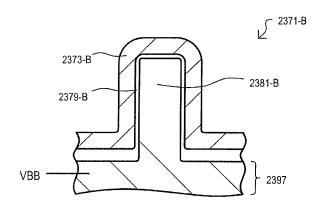

FIGS. 23A to 23C are side cross sectional views of transistors that can receive a body bias according to embodi-35 ments.

# DETAILED DESCRIPTION

Various embodiments of the present invention will now be designed with a timing "guard band", at the cost of perfor- 40 described in detail with reference to a number of drawings. The embodiments show integrated circuit devices, body bias control and generation circuits and related methods, including power up sequences. Body bias values can be varied between circuit blocks to vary (e.g., optimize) circuit block 45 performance. According to some embodiments, in response to current transient events, body bias voltages for circuit blocks can be "collapsed" to lower body bias voltage levels.

> In the various embodiments described below, like items are referred to with the same reference character but with the 50 leading digits corresponding to the figure number.

FIG. 1 is a top plan view of an integrated circuit (IC) device 100 according to an embodiment. An IC device 100 can include a number of blocks (102-0 to -3), each of which can include a number of transistors having body regions which can be reverse biased. Transistors can include any suitable insulated gate field effect transistor having sufficiently strong body coefficients (referred to herein as "MOS" type transistors, but not implying any particular gate or gate dielectric material). Accordingly, transistors can include any of: conventional p-channel (PMOS) transistors (e.g., 104n), conventional n-channel (NMOS) transistors (e.g., 104p), the conventional transistors having strong body coefficients, or deeply depleted channel (DDC) PMOS transistors (e.g., 106p), or DDC NMOS transistors (e.g., 106n) (which by way of a typical architecture of such transistor, has strong body coefficient). An embodiment of a DDC transistor will be described in more detail below. Other

transistor types, for instance, transistors with a three-dimensional gate and a heavily doped body region can be used. It is understood that there is inevitably be a certain degree of variation among conventional transistor construction (e.g., variations in threshold voltage, gate insulator thickness, source-drain diffusion profiles, etc.). DDC transistor constructions can have their own variation as well, though the degree of variation for DDC transistors is generally less than conventional counterparts. Though embodiments are provided contemplating a mix of transistor designs, preferably, DDC transistors are used wherever possible in IC device 100. Note that transistors having strong body coefficient and particularly with body biasing, are amenable for use in circuit applications operating in the subthreshold region or 15 near-threshold computing (having a supply voltage sufficiently low as to be near the threshold voltage setting).

Transistors receiving a body bias can also have a predetermined threshold voltage relationship with respect to a received power supply voltage. In some embodiments, transistors can have a threshold voltage setting that is less than or equal to 0.2V less than a supply voltage to the transistor.

Blocks (102-0 to 102-3) can include circuits of different types. According to particular embodiments, the blocks (102-0 to 102-3) can include but are not limited to any of: 25 memory circuits; e.g., dynamic random access memory, (DRAM), static RAM (SRAM) or nonvolatile memory); processor circuits, e.g., one or more central processing units (CPUs), application PUs (APUs), graphic PUs (GPUs); application specific logic circuits; or analog circuits. Such different types of blocks can have transistors with different threshold voltages, and can have different responses to current transient events. In some embodiments, an IC device 100 can be a system-on-chip (SoC) type device, integrating 35 processor circuits, memory circuits and other application specific circuits. In other embodiments, IC device 100 may be a system with one or more blocks segregated on individual die and assembled on one or more system boards.

IC device 100 includes a global body bias supply 110, 40 which can provide one or more global body bias voltages (VBBG) to each block (102-0 to -3) via a global network 108. A global body bias supply 110 can be a voltage generating circuit, or can be an IC device connection (e.g., bond pad, pin, etc.) that receives an external voltage. A 45 global body bias voltage generating circuit can generally include a charge pump circuit, a switched capacitor circuit, or a voltage regulator.

Each block (102-0 to -3) can include its own local bias circuit 112-0 to -3. Each local bias circuit (112-0 to -3) can 50 generate one or more local body bias voltages (VBB0 to VBB3) from global body bias voltage(s) VBBG. Such local body bias voltages can be reverse body bias voltages that are applied to bodies of transistors within its block (102-0 to -3). Accordingly, body bias voltages for each block (102-0 to -3) 55 can be tuned for the performance of the transistors within the block. Local body bias voltages (VBB0 to VBB3) can be static voltages, that generally do not change once the IC device is operational (but can vary between blocks) and/or can be dynamic voltages that change (e.g., change in 60 response to an IC device mode or event).

According to some embodiments, local body bias voltages (VBB0 to VBB3) can have smaller settings than the global body bias voltage (VBBG) from which they are generated. For example, if a global body bias voltage is a 65 positive voltage for p-channel transistors, corresponding local body bias voltages can have a lower positive voltage.

4

Similarly, if a global body bias voltage is a negative voltage for n-channel transistors, corresponding local body bias voltages can have a higher voltage (i.e., can be less negative)

In the particular embodiment shown, each local bias circuit (112-0 to -3) can generate a local body bias voltage (VBB0 to VBB3) that varies in response to a control value (Ctrl0 to Ctrl3). Thus, a local body bias voltage (VBB0 to VBB3) can be set according to such a value. A control value (Ctrl0 to Ctrl3) can be an analog value or can be a digital value. In this way, a body bias voltage to each different section can be adjusted independently.

It is understood that any of the blocks (102-0 to -3) can include transistors without a reverse body bias voltage (i.e., transistors with bodies biased to a power supply level).

FIGS. 2A to 2C are side cross sectional representations of body bias connections to transistors of a block that can be included in the embodiments described herein. FIG. 2A shows a conventional transistor 204 formed in a well 216. A well 216 can be of opposite conductivity type to a substrate 218 (or larger well) in which it is formed. A body bias voltage for the transistor can be applied via a body bias connection 214 to the well 216.

FIG. 2B is one very particular representation of a DDC transistor 206 formed in a well 216. As in the case of FIG. 2A, well 216 can be of opposite conductivity type to a substrate 218 (or larger well) in which it is formed. A body bias voltage for the transistor can be applied via a body bias connection 214 to the well 216. A DDC transistor 206 can include a highly doped screening region 220 and substantially undoped channel 222. Again, there are various embodiments of DDC transistors, some of which will be described in more detail below.

FIG. 2C shows a semiconductor on insulator (SOI) transistor 204' formed on an SOI substrate 218'. An SOI substrate 218' can include an active layer 218-0, insulating layer 218-1, and base substrate 218-2. Transistor 204' can be formed in active layer 218-0. A body bias voltage for the transistor can be applied via a body bias tap 214 to the active layer 218-0.

The various body bias connections shown in FIGS. 2A to 2C are intended to be exemplary and not limiting. A local body bias voltage as described herein can be applied to bias the body voltage of a transistor using any suitable means for the given transistor.

FIG. 3 is a top plan view of an IC device 300 according to another embodiment. An IC device 300 can include a number of blocks (302-0 to -3), global body bias supply 310, and global body bias network 308. Further, each block (302-0 to -3) can include a local body bias circuit (312-0 to -3). Such sections can be the same as, and subject to the same variations as those of FIG. 1. It is noted that in alternate embodiments, features shown as on the IC device 300 may be part of a system, for instance, a board having IC device(s) thereon; by way of example, global body bias supply 310 may be remote from IC device 300 and may feed in to IC device 300 from a system that includes IC device 300 assembled therein.

FIG. 3 further shows a local reference supply 324-0 to -3 and collapse circuit 326-0 to -3 corresponding to each block (302-0 to -3). A local reference supply (324-0 to -3) can provide a reference value (Vref0 to Vref3) to each local bias circuit (312-0 to -3). A local bias circuit (312-0 to -3) can control its body bias voltage (VBB0 to VBB3) by comparing a current body bias voltage to a reference voltage. A reference value (Vref0 to Vref3) can be a voltage, current, or digital value. In some embodiments, a reference value

(Vref0 to Vref3) remains constant, and body bias voltage can be adjusted by programming an allowable difference between the reference value and the body bias voltage. Alternatively, a reference value (Vref0 to Vref3) can be adjustable, and a body bias voltage can track the reference 5

Each collapse circuit (326-0 to -3) can selectively connect the bodies of transistors of its section to a "collapse" voltage. A collapse voltage can be a voltage having a setting less than the body bias voltage. In some embodiments, a collapse voltage can be a low power supply voltage level. As but one example, n-channel transistors can have a collapse voltage of zero volts (e.g., a low power supply level VSS), while p-channel transistors can have a collapse voltage of a high supply voltage (e.g., VDD, VCC). According to embodiments, collapse circuits (326-0 to -3) can collapse a body bias voltage to a collapse voltage in response to predetermined events. Such events can include events which can cause a current transient. In this way, a body bias voltage 20 setting for transistors can be reduced in the event of a current transient event. This is in contrast to conventional approaches which either do not modify or can increase a body bias voltage setting in such cases.

In some embodiments, collapse circuits (326-0 to -3) can 25 be programmable, being enabled in response to a selected set of events or modes of operation. In addition or alternatively, collapse circuits (326-0 to -3) can have a programmable delay between an event and the collapse operation.

FIG. 4 is a timing diagram showing a collapse operation 30 according to one very particular embodiment. In the embodiment of FIG. 4, collapse circuits can enable reverse body bias voltages to be selected to track a power supply level in the event of a current transient event.

FIG. 4 includes the following waveforms: VDD can be a 35 high power supply voltage; VSS can be a low power supply voltage (e.g., ground); VBN can be a reverse body bias voltage for n-channel transistors; and VBP can be a reverse body bias voltage for p-channel transistors. As shown, in the can "droop", moving towards each other. In response, collapse circuits can cause the body bias voltages (VBN/VBP) to track such power levels.

As noted above, in very particular embodiments, such a tracking can be accomplished by having VBN collapse to 45 VSS and VBP collapse to VDD.

FIG. 5 is a timing diagram showing how reducing the setting of a reverse body bias voltage can increase circuit speed over high body bias levels.

FIG. 5 includes the following waveforms: an inverter 50 delay with a standard reverse body bias (Standard VBB), an inverter delay with a reduced reverse body bias (i.e., a body bias having a lower setting than the Standard VBB) (Reduced VBB); as well as power supply levels (VDD/VSS) simulating a current transient event (i.e., droop).

As shown, reducing the setting of the reverse body bias can result in faster performance than maintaining the reverse body bias level. In this way, reducing a reverse body bias level during current transient events can increase performance, which can result in reduced guard-banding against 60 such events.

FIG. 6 is a block schematic diagram of a body bias control circuit **628** according to an embodiment. Body bias control circuit 628 can include local body bias circuits (612-0 to 612-n), collapse circuits (626-0 to 626-n), and event detect 65 circuits (630-0 to -n). Each local body bias control circuit (612-0 to 612-n) can provide a reverse body bias VBB

BLK0 to VBB BLKn to a corresponding group of transistors, as described herein, or equivalents.

A collapse circuit (626-0 to 626-n) can collapse body bias voltages to a set of transistors to a collapse voltage (VCollapse) as described herein, or equivalents. A collapse voltage (Vcollapse) can be static voltage or can be a dynamic voltage (e.g., a voltage that tracks power supply droop). In the embodiment shown, each collapse circuit (626-0 to 626-n) can collapse its body bias voltage in response to an enable signal (Coll\_EN0 to Coll\_ENn) generated by a corresponding event detect circuit (630-0 to -n).

Each event detect circuit (630-0 to -n) can activate its collapse enable signal (Coll\_EN0 to Coll\_ENn) in response to one or more predetermined conditions. Such conditions can include operations on an IC device and/or signals received from sources external to the IC device.

FIG. 7 is a block schematic diagram showing a collapse event detect arrangement of an IC device according to an embodiment. An event detect circuit 730 can activate its collapse enable signal Coll\_ENx in response to a number of events (or combinations of such events). In the particular embodiment shown, an event detect circuit 730 can receive an interrupt signal (INT). An interrupt signal INT can be generated by hardware (e.g., in response to circuits operations) or in response to software (e.g., instructions executed by a processor). Event detect circuit 730 can also receive signals applied from a source external to the integrated circuit device. In the particular embodiment shown, one or more signals external to the IC device (External CMDs) can be received by an intermediate circuit (in this embodiment a command decoder), in response to such external signal(s), a signal CMD\_ACT can be activated as an input to event detect circuit 730.

An event detect circuit 730 can also receive a block enable signal BLKEN as an input. A block enable signal BLKEN can enable a block 702 of the IC device. Enabling a block can include changing a state of the block, including from a "sleep" mode to an active mode. A block enable signal event of a transient event, power supply levels (VDD/VSS) 40 BLKEN can be for the block that includes the event detect circuit, or can be an entirely different block.

FIG. 8 is a top plan view of an IC device 800 according to another embodiment. An IC device 800 can include a number of blocks (802-0 to -3), global body bias supply 810, global body bias network 808, and local body bias circuits 812-0 to -3. Such sections can be the same as, and subject to the same variations as those of FIG. 1.

The embodiment of FIG. 8 also includes a digital bus 834 and control store 832. Local body bias circuits (812-0 to -3) can be controlled in response to multi-bit control values transmitted over digital bus 834, including values stored in control store 832. Note, that in embodiments that provide body biases for both NMOS and PMOS transistors, such blocks will have at least two local bias circuits, one for PMOS device and one for NMOS devices. A control store 832 can include any circuit structure suitable to provide digital values to digital bus 834. All or a portion of values within control store 832 can be writable from locations external to an IC device 800. In addition or alternatively, all or a portion of the values of control store 832 can be established by a manufacturing step of the IC device (i.e., mask option, assembly option etc.). It is noted that in some embodiments, an IC device 800 may be subdivided into components that are on die and are off die and feed in from a system in which IC device 800 is placed. For instance, control store 832 may be implemented on a system and coupled to IC device 800 via digital bus 834, without control

store 832 being fabricated onto the a die together with other components shown in IC device 800.

FIG. 8 shows a control store 832' according to one very particular embodiment. A control store 832' can be a register set that can store local bias control values for each block. In 5 the embodiment shown, control store 832' can include a body bias enable value for different conductivity type transistors (BLKx VBN Enable, BLKx VBP Enable, where x is a block identifier). Such values can enable or disable reverse body bias for transistors of the block. Control store reg. 832' 10 can also include a body bias level value for different conductivity type transistors (BLKx VBN Level, BLKx VBP Level, where x is a block identifier). Such values can establish the level of the reverse body bias for transistors of the block.

FIG. 9 is a top plan view of an IC device 900 according to another embodiment. An IC device 900 can include a number of blocks (902-0 to -3), global body bias supply 910, global body bias network 908, and local body bias circuit 912-0 to -3. IC device 900 can be on the same die or may 20 be subdivided so that some components are on a die and other components are off die and located on a system on which the die is assembled. Such sections can be the same as, and subject to the same variations as those of FIG. 1.

The embodiment of FIG. 9 also includes a digital bus 934 25 and control store 932. Collapse circuits (926-0 to -3) for each block can be controlled in response to multi-bit control values transmitted over digital bus 934, including values stored in control store 932. A control store 932 can include circuit structures such as those noted for 832 in FIG. 8, or 30 equivalents.

FIG. 9 shows a control store 932' according to one very particular embodiment. A control store 932' can be a register set that can store local collapse control values for each block. In the embodiment shown, control store 932' can 35 include a collapse enable value for each block (BLKx Collapse Enable, where x is a block identifier). Such values can enable or disable the collapse circuit for block. Control store 932' can also include a collapse event value (BLKx Collapse Event(s)). Such a value can establish for which 40 events/inputs a collapse operation can occur. Control store 932' can also include a collapse delay value (BLKx Collapse Delay). Such a value can establish a delay between an input to a collapse circuit, and the resulting collapse operation.

It is understood that embodiments can combine items of 45 FIGS. **8** and **9**, to provide an IC device with digital control of both reverse body bias levels, as well as collapse operations.

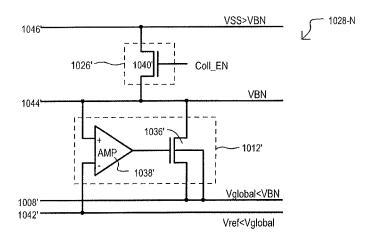

FIG. 10A is a block schematic diagram of a body bias control circuit 1028-P for p-channel transistors according to 50 an embodiment. Body bias control circuit 1028-P can include local body bias circuits 1012 and a collapse circuit 1026. A local body bias circuit 1012 can be a low dropout regulator (LDO) type circuit, and can include an amplifier **1038** and a bias device **1036**. Amplifier **1038** can have a (-) 55 input connected to receive a reference voltage (Vref), a (+) input connected to receive the generated body bias voltage VBP (i.e., a feedback value), and an output that drives the bias device. Reference voltage (Vref) can be carried on a reference line 1042 that can be for transistors of one block, 60 or multiple blocks. A reference voltage (Vref) can establish a reverse body bias voltage VBP. As shown, a reference voltage Vref can be less than a global body bias voltage Vglobal.

A bias device 1036 can be a p-channel transistor having 65 source and body connected to receive a global body bias value (Vglobal), a gate coupled to the output of amplifier

8

1038, and a drain connected to provide the body bias voltage (VBP) on body bias line 1044 (i.e., the drain is connected to one or more wells or other active regions containing p-channel transistors). A global body bias voltage (Vglobal) can be provided on a global body bias network 1008, which can provide such a value to multiple different blocks. In particular embodiments, a bias device 1036 can be a high voltage transistor (i.e., a transistor designed to withstand higher voltage levels than other transistors of the IC device, such as a thicker gate insulator, for example).

According to a difference between Vref and VBP, amplifier 1038 can drive bias device to raise or lower VBP with respect to Vglobal. In particular, as VBP falls below Vref, amplifier 1038 will increase the conductivity of bias device 1036 until VBP reaches a desired level.

A collapse circuit **1026** can include a collapse device **1040**. A collapse device **1040** can drive VBP to a lower power supply level VDD in response to signal Coll\_EN. A lower power supply (VDD) level can be lower than VBP.

To avoid large current draw through device 1036 (a contention state) the body bias control circuit may have a disable (not shown, but discussed for another embodiment below) asserted when Coll\_EN is asserted. Alternatively, Vref may be set to the local VDD value during collapse events, which will also essentially turn off bias device 1036.

FIG. 10B is a block schematic diagram of a body bias control circuit 1028-N like that of FIG. 10A, but for n-channel transistors. The operation of body bias control circuit 1028-N is understood from the description of FIG. 10A.

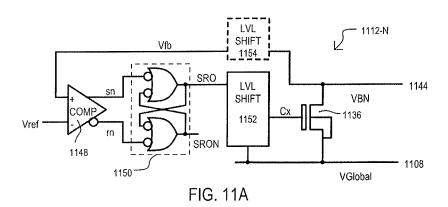

While embodiments can include continuous (e.g., analog) control of local reverse body bias voltages, alternate embodiments can include pulsed (e.g., digital) control of reverse body bias voltages. FIGS. 11A and 11B show particular examples of such embodiments.

FIG. 11A shows a local bias circuit 1112-N for n-channel transistors according to an embodiment. Local body bias circuit 1112-N can include a comparator 1148, toggle logic 1150, a level shifter 1152, a bias device 1136, and optionally, a second level shifter 1154. A comparator 1148 can have a (+) input connected to receive a feedback voltage (Vfb), that corresponds to the local body bias voltage VBN, a (-) input connected to receive a reference voltage (Vref), and an output connected to toggle logic 1150.

Toggle logic 1150 can toggle between high and low values based on an output of comparator 1148. In the particular embodiment shown, toggle logic 1150 can be an SR type flip-flop circuit, with an output to level shifter 1152. Level shifter 1152 can shift output values from a lower voltage domain to a higher voltage domain. In the embodiment shown, level shifter 1152 can ensure a low value from toggle logic 1150 is driven to VGlobal. An output of level shifter 1152 can turn bias device 1136 off and on.

Bias device 1136 can be an n-channel transistor having source and body connected to VGlobal, a gate connected to receive the output of level shifter 1152 (Cx), and a drain connected to provide the body bias voltage (VBN) on body bias line 1144 (i.e., the drain is connected to one or more wells or other active regions containing n-channel transistors). A global body bias voltage (Vglobal) can be provided on a global body bias network 1108, which can provide such a value to multiple different blocks. Optional level shifter 1154 can shift a body bias voltage VBN to ensure compatibility with the common mode input range of comparator 1148. A bias device 1136 can be a high voltage transistor. The comparator may be continuous-time as shown, or clocked (i.e., a dynamic comparator).

If VBN is above a predetermined level, Vfb will be greater than Vref, and the output of comparator 1148 will be driven high. Toggle logic 1150 will drive level shifter 1152 accordingly, which will drive signal Cx high. This turns on the bias device 1136, resulting in the local body bias VBN being driven lower. Once VBN is above a predetermined level, Vfb will be below Vref, and the output of comparator 1148 will be driven low. By operation of toggle logic 1150 and level shifter 1152, signal Cx will be driven low, turning off bias device 1136. Thus, bias device 1136 can be continually turning on and off to maintain VBN at a desired level.

FIG. 11B is a block schematic diagram of a local bias circuit 1112-P like that of FIG. 11A, but for p-channel transistors. The operation of local bias circuit 1112-P is understood from the description of FIG. 11A.

In some embodiments, the activation of a bias device (which establishes a body bias level from a global body bias) and the activation of a collapse device can be interlocked with one another. In particular, a bias device will be disabled when the corresponding collapse device is enabled. Particular examples of such embodiments will now be described.

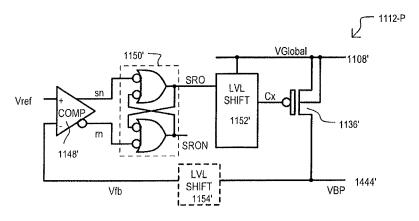

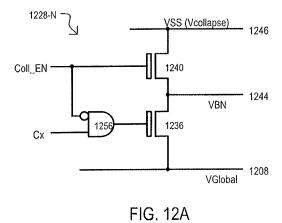

FIG. 12A is a block schematic diagram of a body bias control circuit 1228-N for n-channel transistors according to an embodiment. Body bias control circuit 1228-N can include a bias device 1240, a collapse device 1236, and 25 interlock logic 1256. Bias device 1240 can be an n-channel transistor having a source-drain path connected between a global body bias voltage (VGlobal) and a local body bias output 1244, and a gate connected to an output of interlock logic. Collapse device 1236 can have a source-drain path 30 connected between a collapse voltage (which is a lower power supply voltage VSS in this particular embodiment) and the local body bias output 1244. In particular embodiments, either or both of bias and collapse devices (1240/1236) can be high voltage tolerant transistors.

Interlock logic 1256 can ensure that bias device 1240 is turned off whenever a collapse operation occurs (i.e., CollEN is high). Further, interlock logic 1256 can ensure that bias device 1240 is turned on only when there is no collapse operation (i.e., CollEN is low).

FIG. 12B is a block schematic diagram of a body bias control circuit 1228-P like that of FIG. 12A, but for p-channel transistors. The operation of body bias control circuit 1228-P is understood from the description of FIG. 12A, where control signal Coll\_ENN is asserted active low rather 45 than high.

FIG. 13 is a block schematic diagram of an IC device 1300 according to another embodiment. In a very particular embodiment, IC device 1300 can be one implementation of a device like that shown in FIGS. 8 and/or 9. An IC device 50 1300 can include a number of blocks 1302-0 to -n, each of which can include p-wells which can contain n-channel transistors, as well as n-wells which can contain p-channel transistors. Transistors can take the form of any of those described herein, or equivalents. N-wells within each block 55 (1302-0 to -n) can be driven to a bias voltage (VNwell\_ A,  $B \dots Z$ ) by a corresponding bias control circuit 1328-0 to -n. Such n-well bias voltages can be connected to their n-wells via local bias lines (1334A to 1334Z). In a like fashion, p-wells within each block (1302-0 to -n) can be 60 driven to a bias voltage (VPwell\_A, \_B . . . \_Z) by a corresponding bias control circuit 1328-0' to -n'. Such p-well bias voltages can be connected to their p-wells via local bias lines (1334A' to 1334Z').

Bias control circuits for the p-wells (1328-0 to -n) can 65 each include a digital-to-analog converter (DAC) 1358, amplifier 1338, bias device 1336, and collapse device 1340.

10

DACs 1358 can receive input digital values from a local control circuit 1362, and from such values can generate reference voltages (VrefNwA to VrefNwZ). Amplifiers 1338 can have one input connected to receive the reference voltage (VrefNwA to VrefNwZ) and another input connected to the corresponding n-well (i.e., via 1334A to 1334Z). Output of amplifiers 1338 can control corresponding bias devices 1336. Bias devices 1336 can be p-channel transistors having source-drain paths connected between a global bias voltage VNwell\_Global and their corresponding n-well. In such an arrangement, based on a difference between a reference voltage (VrefNwA to VrefNwZ) and a well voltage, the conductivity of the bias device 1336 can be varied to maintain the n-well at a desired bias voltage.

Collapse devices 1340 can be p-channel transistors having source-drain paths connected between the local power supply voltage (e.g., VDD) and their corresponding n-well. Activation of collapse devices 1340 can be controlled via signals from a collapse control circuit 1360.

Bias control circuits for the n-wells (1328-0' to -n') can have structures like those for the p-wells, but include n-channel bias devices 1336' and collapse devices 1340'. Bias control circuits (1328-0' to -n') can operate in a similar fashion, varying the conductivity of the bias devices 1336' according to a difference between a reference voltage (Vref-PwA to VrefPwZ) and the voltage of their corresponding p-well. Reference voltages (VrefPwA to VrefPwZ) can be generated from digital values output from local control circuit 1362'. Collapse devices 1340', when activated by collapse control circuit 1360, can collapse their corresponding well to the local power supply voltage (e.g., VSS).

FIG. 14 shows event detect circuits 1430-0 to -n according to embodiments. Each event detect circuit (1430-0 to -n) can activate a collapse enable signal (Coll\_EN0 to Coll\_ENn), which can collapse a body bias (e.g., well) voltage to a predetermined level in response to particular events.

Each event detect circuit can include local logic 1464-0 to

-n, local delay 1466-0 to -n, global delay 1468-0 to -n, and

output logic 1470-0 to -n. Local logic (1464-0 to -n) can

combine signals corresponding to local events (i.e., events

occurring on the block itself) (LOCAL EVENT0 to i). In the

particular embodiment of FIG. 14, local logic can be an OR

gate, but any suitable logic can be employed. Local delay

(1466-0 to -n) can add delay to time the assertion or

de-assertion of a signal. In some embodiments, such delay

can be programmable. Global delay (global delay 1468-0 to

-n) can delay a global event indication (i.e., an event outside

of the block) (GLOBAL EVENTI). Output logic 1470-0 to

-n can combine local and global event indications to generate the collapse enable signal (Coll\_EN0 to Coll\_ENn).

According to an embodiment, during the IC power up sequence, the charge pumps may not have time to drive the global bias values to their correct values. In this case, the core devices may be temporarily forward body biased, causing excessive power up currents. Consequently, one such GLOBAL EVENT may be the power up sequence, whereby the local body biases may be driven to the local supply voltages (applying zero body bias rather than forward body bias). When the supplies, including the global well biases, have been determined to be at their nominal voltages, the GLOBAL EVENT condition may be de-asserted to allow local well biases to be reverse biased, further reducing leakage currents.

While embodiments herein can include IC devices that generate local body bias voltages from global body bias voltages, embodiments can also include power-on sequences

for such devices. A power-on sequence according to one particular embodiment is shown in FIG. 15.

FIG. **15** is a timing diagram of a power on sequence for an IC device. FIG. **15** includes the following waveforms: VHi\_Max shows a high power supply voltage that can be provided to particular circuits in the IC device; VBNWell can be a reverse body bias generated for p-channel devices (i.e., VBP); VBPWell can be a reverse body bias generated for n-channel devices (i.e., VBN); and VHi can be a power supply voltage less than VHi\_Max, provided to circuits with transistors subject to one or both reverse body bias voltages.

In one very particular embodiment, VHi\_Max can be a power supply for a charge pump circuit that generates a global negative body bias used to generate VBPwell, and can have a level of about +3.3V. A positive reverse body bias (VBNwell) can be about +1.7V (which is greater than Vhi). A reverse body bias (VBPwell) can be about -0.9V. Vhi can be about +0.9V, and can be a supply voltage to p-channel transistors having the reverse body bias voltage VBNwell 20 (of about +1.7V).

Referring still to FIG. 15, as shown, the power voltage Vhi can be enabled only after the VHi\_Max and VBNwell/VBPwell have been settled. In one particular embodiment, Vhi\_Max can rise first, enabling the local body bias voltages 25 (VBNwell/VBPwell) to be generated. Only after such actions is power supply Vhi allowed to rise (shown by "delay").

FIG. 16 is a block schematic diagram of an IC device 1600 according to another embodiment. An IC device 1600 30 can incorporate a power-up sequence like that shown in FIG. 15. An IC device 1600 can include a number of blocks 1602-0 to 1602-n, which in the particular embodiment shown, can be CPU cores. Each block (1602-0 to -n) can include local bias circuits 1612-0 to -n that can generate a 35 local n-channel body bias (i.e., a p-well bias) for its block, and local bias circuits 1612-0 to -n' that can generate a local p-channel body bias (i.e., an n-well bias) for its block.

Local bias circuits (1612-0 to -n) can generate their local body bias voltages (VBN) from a negative global body bias 40 voltage (VBPwell Global) provided to each block (1602-0 to -n) via a global network 1608. Local body bias voltages (VBN) can set with corresponding digital values (Dig. Ctrl). In a similar fashion, local bias circuits (1612-0' to -n') can generate their local body bias voltages (VBP) from a positive global body bias (VBNwell Global) provided to each block (1602-0 to -n) via a global network 1608'.

In the embodiment shown, a negative global body bias voltage (VBPwell Global) can be provided from a global source **1610**, which can include a charge pump circuit **1672** 50 controlled by an oscillator circuit **1674**. Charge pump circuit **1672** and oscillator circuit **1674** can operate at a voltage Vhi\_Max, which can be an externally provided high supply voltage, such as the high voltage input-output (VDDIO) power supply.

A positive global body bias voltage (VBNwell Global) can be provided from global bias circuit 1610', which in a particular embodiment can be DC-DC converter circuit, which can convert the voltage Vhi\_Max, to a lower voltage level with high efficiency.

In a power up operation, Vhi\_Max (e.g., ~+3.3V) can be applied. A lower power supply voltage (e.g., ~+0.9V) is not immediately enabled. In response to Vhi\_Max, oscillator circuit 1674 can generate an oscillating signal as an input to charge pump circuit 1672. In response, the charge pump 65 circuit 1672 can start to generate a negative global bias voltage (VBPwell Global). In response to negative global

12

bias voltage (VBPwell Global), local bias circuits (1612-0 to -n) can generate their local body bias voltages (VBN).

At the same time, global source **1610**' can generate a positive global supply voltage (VBNwell Global) (e.g., ~+2.2V) from the Vhi\_Max voltage (e.g., ~+3.3V). Once the high power supply voltage (VBNwell Global) is established, local bias circuits (**1612-0**' to -n') can generate their local body bias voltages (VBP).

After the local body bias voltages (VBN/VBP) are stable, a lower power supply voltage (e.g., ~+0.9V) can then be enabled. Alternatively, the body biases may be pinned to the supply voltage so as not to apply forward body biases, until such time as the global body biases are stable.