(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6949047号

(P6949047)

(45) 発行日 令和3年10月13日(2021.10.13)

(24) 登録日 令和3年9月24日(2021.9.24)

(51) Int.Cl.

F 1

|               |           |                   |

|---------------|-----------|-------------------|

| G 11 C 11/419 | (2006.01) | G 11 C 11/419     |

| G 11 C 7/22   | (2006.01) | G 11 C 7/22       |

| G 11 C 11/412 | (2006.01) | G 11 C 11/412 120 |

請求項の数 15 (全 24 頁)

(21) 出願番号 特願2018-550525 (P2018-550525)

(86) (22) 出願日 平成29年3月2日 (2017.3.2)

(65) 公表番号 特表2019-510332 (P2019-510332A)

(43) 公表日 平成31年4月11日 (2019.4.11)

(86) 國際出願番号 PCT/US2017/020351

(87) 國際公開番号 WO2017/172230

(87) 國際公開日 平成29年10月5日 (2017.10.5)

審査請求日 令和2年2月17日 (2020.2.17)

(31) 優先権主張番号 15/085,187

(32) 優先日 平成28年3月30日 (2016.3.30)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 フランソワ・イブラヒム・アタラー

アメリカ合衆国・カリフォルニア・921

21・サン・ディエゴ・モアハウス・ドラ

イブ・5775

最終頁に続く

(54) 【発明の名称】メモリピットセルにおける動的読み取り動作のための遅延キーパー回路の漏れ認識アクティブ化制御

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリピットセルに対する動的読み取り回路内の遅延キーパー回路のアクティブ化を制御するための漏れ認識アクティブ化制御回路であって、

動的読み取り回路内の少なくとも1つのN型電界効果トランジスタ(NFET)の漏れ電流を示すNFET漏れインジケータを生成するように構成されたNFET漏れ回路と、

前記動的読み取り回路内の少なくとも1つのP型電界効果トランジスタ(PFET)の漏れ電流を示すPFET漏れインジケータを生成するように構成されたPFET漏れ回路と、

比較器回路であって、

前記NFET漏れインジケータおよび前記PFET漏れインジケータを受け取り、

10

前記NFET漏れインジケータを前記PFET漏れインジケータと比較し、

前記NFET漏れインジケータと前記PFET漏れインジケータの前記比較に基づいて、PFET漏れ電流とPFET漏れ電流の比を示すFET漏れ信号を生成するように構成された比較器回路と、

遅延キーパー回路のアクティブ化タイミングを制御するために前記FET漏れ信号に基づいて少なくとも1つの制御信号を適応的に生成するように構成された制御信号生成器とを備える漏れ認識アクティブ化制御回路。

## 【請求項 2】

前記NFET漏れ回路は、前記動的読み取り回路の動作中に前記動的読み取り回路内の前記少なくとも1つのNFETの前記漏れ電流を示す前記NFET漏れインジケータを動的に生成するよう

20

に構成され、

前記PFET漏れ回路は、前記動的読取り回路の動作中に前記動的読取り回路内の前記少なくとも1つのPFETの前記漏れ電流を示す前記PFET漏れインジケータを動的に生成するよう構成される、請求項1に記載の漏れ認識アクティブ化制御回路。

#### 【請求項3】

前記NFET漏れ回路は、NFET漏れを判定するように構成されたNFET漏れセンサーを備え、

前記NFET漏れセンサーは、前記動的読取り回路内の前記判定されたNFET漏れに基づいて前記少なくとも1つのNFETの前記漏れ電流を示す前記NFET漏れインジケータを生成するよう構成され、

前記PFET漏れ回路は、PFET漏れを判定するように構成されたPFET漏れセンサーを備え、

10

前記PFET漏れセンサーは、前記動的読取り回路内の前記判定されたPFET漏れに基づいて前記少なくとも1つのPFETの前記漏れ電流を示す前記PFET漏れインジケータを生成するよう構成される、請求項1に記載の漏れ認識アクティブ化制御回路。

#### 【請求項4】

前記NFET漏れセンサーは、前記少なくとも1つのNFETの前記漏れ電流を示すNFET漏れ電流を生成するように構成された少なくとも1つの非アクティブ化されたNFETから構成され、

前記PFET漏れセンサーは、前記少なくとも1つのPFETの前記漏れ電流を示すPFET漏れ電流を生成するように構成された少なくとも1つの非アクティブ化されたPFETから構成される、請求項3に記載の漏れ認識アクティブ化制御回路。

20

#### 【請求項5】

前記NFET漏れセンサーは、リング発振器内で結合された複数の第1のバッファ回路を備えるNFETリング発振器回路からさらに構成され、前記複数の第1のバッファ回路の各々が、前記少なくとも1つの非アクティブ化されたNFETのうちの前記少なくとも1つのNFETの前記漏れ電流を示す前記NFET漏れ電流によってアクティブ化されるよう構成され、前記NFETリング発振器回路が、前記生成されたNFET漏れ電流に基づいて前記NFET漏れインジケータを更新するよう構成され、

前記PFET漏れセンサーは、リング発振器内で結合された複数の第2のバッファ回路を備えるPFETリング発振器回路からさらに構成され、前記複数の第2のバッファ回路の各々が、前記少なくとも1つの非アクティブ化されたPFETのうちの前記少なくとも1つのPFETの前記漏れ電流を示す前記PFET漏れ電流によってアクティブ化されるよう構成され、前記PFETリング発振器回路が、前記生成されたPFET漏れ電流に基づいて前記PFET漏れインジケータを更新するよう構成される、請求項4に記載の漏れ認識アクティブ化制御回路。

30

#### 【請求項6】

前記NFET漏れ回路は、NFET漏れ周波数カウントを記憶するように構成されたNFET漏れ周波数カウンタをさらに備え、

前記NFET漏れ回路は、前記少なくとも1つのNFETの判定された漏れ電流の関数として、前記NFET漏れ周波数カウントを更新するように前記NFET漏れ周波数カウンタを制御するよう構成され、

前記PFET漏れ回路は、PFET漏れ周波数カウントを記憶するように構成されたPFET漏れ周波数カウンタをさらに備え、

40

前記PFET漏れ回路は、前記少なくとも1つのPFETの前記判定された漏れ電流の関数として、前記PFET漏れ周波数カウントを更新するように前記PFET漏れ周波数カウンタを制御するよう構成される、請求項1に記載の漏れ認識アクティブ化制御回路。

#### 【請求項7】

前記比較器回路は、前記NFET漏れインジケータと前記PFET漏れインジケータの前記比較に基づいてFET漏れ制御信号を含むFET漏れ信号を生成するよう構成され、

前記制御信号生成器は、前記遅延キーパー回路の前記アクティブ化タイミングを制御するため前記FET漏れ制御信号に基づいてFET漏れ制御ワードを含む少なくとも1つの制御信号を適応的に生成するよう構成される、請求項1に記載の漏れ認識アクティブ化制御

50

回路。

**【請求項 8】**

前記比較器回路は、

少なくとも1つのPFET漏れ比較器回路であって、

公称漏れ限界を示す既定の公称漏れインジケータと前記PFET漏れインジケータとを受け取り、

前記公称漏れインジケータを前記PFET漏れインジケータと比較し、

前記公称漏れインジケータと前記PFET漏れインジケータとの前記比較に基づいて前記少なくとも1つのPFETの前記漏れ電流が前記公称漏れ限界を超えているか否かを示すように前記FET漏れ制御信号を制御するように構成される少なくとも1つのPFET漏れ比較器回路と、10

少なくとも1つのNFET漏れ比較器回路であって、

前記NFET漏れインジケータと前記既定の公称漏れインジケータとを受け取り、

前記NFET漏れインジケータを前記公称漏れインジケータと比較し、

前記NFET漏れインジケータと前記公称漏れインジケータとの前記比較に基づいて前記少なくとも1つのNFETの前記漏れ電流が前記公称漏れ限界を超えているか否かを示すように前記FET漏れ制御信号を制御するように構成される少なくとも1つのNFET漏れ比較器回路とを備える、請求項7に記載の漏れ認識アクティブ化制御回路。

**【請求項 9】**

前記比較器回路は、20

少なくとも1つのPFET低速漏れ比較器回路であって、

前記PFET漏れインジケータを受け取り、

PFET低速漏れ限界を示す既定のPFET低速漏れインジケータを受け取り、

前記PFET漏れインジケータを前記既定のPFET低速漏れインジケータと比較し、

前記PFET漏れインジケータと前記既定のPFET低速漏れインジケータとの前記比較に基づいて、前記少なくとも1つのPFETの前記漏れ電流が前記PFET低速漏れ限界未満である場合にPFET低速漏れ電流を示すように前記FET漏れ制御信号を制御するように構成された少なくとも1つのPFET低速漏れ比較器回路と、

少なくとも1つのNFET低速漏れ比較器回路であって、

前記NFET漏れインジケータを受け取り、30

NFET低速漏れ限界を示す既定のNFET低速漏れインジケータを受け取り、

前記NFET漏れインジケータを前記既定のNFET低速漏れインジケータと比較し、

前記NFET漏れインジケータと前記既定のNFET低速漏れインジケータとの前記比較に基づいて、前記少なくとも1つのNFETの前記漏れ電流が前記NFET低速漏れ限界未満である場合にNFET低速漏れ電流を示すように前記FET漏れ制御信号を制御するように構成された少なくとも1つのNFET低速漏れ比較器回路とをさらに備える、請求項7に記載の漏れ認識アクティブ化制御回路。

**【請求項 10】**

前記比較器回路は、

少なくとも1つのPFET高速漏れ比較器回路であって、40

前記PFET漏れインジケータを受け取り、

PFET高速漏れ限界を示す既定のPFET高速漏れインジケータを受け取り、

前記PFET漏れインジケータを前記既定のPFET高速漏れインジケータと比較し、

前記PFET漏れインジケータと前記既定のPFET高速漏れインジケータとの前記比較に基づいて、前記少なくとも1つのPFETの前記漏れ電流が前記PFET高速漏れ限界よりも大きい場合にPFET高速漏れ電流を示すように前記FET漏れ制御信号を制御するように構成された少なくとも1つのPFET高速漏れ比較器回路と、

少なくとも1つのNFET高速漏れ比較器回路であって、

前記NFET漏れインジケータを受け取り、

NFET高速漏れ限界を示す既定のNFET高速漏れインジケータを受け取り、50

前記NFET漏れインジケータを前記既定のNFET高速漏れインジケータと比較し、

前記NFET漏れインジケータと前記既定のNFET高速漏れインジケータとの前記比較に基づいて、前記少なくとも1つのNFETの前記漏れ電流が前記NFET高速漏れ限界よりも大きい場合にNFET高速漏れ電流を示すように前記FET漏れ制御信号を制御するように構成された少なくとも1つのNFET高速漏れ比較器回路とをさらに備える、請求項7に記載の漏れ認識アクティブ化制御回路。

#### 【請求項11】

前記制御信号生成器は、前記遅延キーパー回路のアクティブ化タイミングを制御するために前記FET漏れ制御信号を前記FET漏れ制御ワードに復号するように構成されたデコーダ回路を備える、請求項7に記載の漏れ認識アクティブ化制御回路。 10

#### 【請求項12】

前記制御信号生成器は、前記NFET漏れインジケータと前記PFET漏れインジケータとの前記比較に基づいて、前記遅延キーパー回路の前記アクティブ化タイミングを制御するように構成されたパルス発生器によって生成されたパルスのパルス幅の制御タイミングに基づいて前記少なくとも1つの制御信号を適応的に生成するように構成される、請求項1に記載の漏れ認識アクティブ化制御回路。

#### 【請求項13】

システムオンチップ(SoC)に組み込まれ、および/または

セットトップボックス、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、モバイルフォン、セルラーフォン、スマートフォン、タブレット、ファブレット、サーバ、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、携帯情報端末(PDA)、モニタ、コンピュータモニタ、テレビ、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、ポータブルデジタルビデオプレーヤ、および自動車からなるグループから選択されるデバイスに組み込まれた、請求項1に記載の漏れ認識アクティブ化制御回路。 20

#### 【請求項14】

メモリビットセルに対する動的読み取り回路内の遅延キーパー回路のアクティブ化を制御するための方法であって、 30

動的読み取り回路内の少なくとも1つのN型電界効果トランジスタ(NFET)の漏れ電流を示すNFET漏れインジケータを生成するステップと、

前記動的読み取り回路内の少なくとも1つのP型FET(PFET)の漏れ電流を示すPFET漏れインジケータを生成するステップと、

前記NFET漏れインジケータを前記PFET漏れインジケータと比較するステップと、

前記比較に基づき、NFET漏れ電流とPFET漏れ電流の比を示すFET漏れ信号を生成するステップと、

前記FET漏れ信号に基づいて遅延キーパー回路に対する少なくとも1つの制御信号を適応的に生成するステップとを含む方法。

#### 【請求項15】

メモリシステムであって、 40

メモリビットセルであって、

補完電圧を記憶するように構成された記憶回路と、

前記記憶回路に結合され、読み取り動作に応答して動的ノード上で前記補完電圧を生成するように構成された読み取りポート回路とを備えるメモリビットセルと、

動的読み取り回路であって、

前記動的ノードと、

評価フェーズの外側で前記動的ノード上に前記補完電圧を維持するためにパルスに応答してアクティブ化されるように構成され、前記読み取り動作の前記評価フェーズに応答して、前記パルスに応答して非アクティブ化されるように構成された遅延キーパー回路とを 50

備える動的読み取り回路と、

漏れ認識アクティブ化制御回路であって、

N型FET(NFET)漏れインジケータとP型FET(PFET)漏れインジケータとの比較に基づいて、PFET漏れ電流とPFET漏れ電流の比を示すFET漏れ信号を生成するように構成された漏れ回路であって、前記NFET漏れインジケータが、少なくとも1つのNFETの漏れ電流に基づき生成され、前記PFET漏れインジケータが、少なくとも1つのPFETの漏れ電流に基づき生成される、漏れ回路と、

前記遅延キーパー回路のアクティブ化タイミングを制御するために前記FET漏れ信号に基づいて少なくとも1つの制御信号を適応的に生成するように構成された制御信号生成器とを備える漏れ認識アクティブ化制御回路と、

前記少なくとも1つの制御信号に応答して前記遅延キーパー回路のアクティブ化および非アクティブ化のための制御アクティブ化タイミングに基づくパルス幅を有する前記パルスを生成するように構成されたパルス発生器とを備えるメモリシステム。

### 【発明の詳細な説明】

【技術分野】

[ 0 0 0 1 ]

優先權出願

本出願は、全体が参照により本明細書に組み込まれる、2016年3月30日に出願された、「LEAKAGE-AWARE ACTIVATION CONTROL OF A DELAYED KEEPER CIRCUIT FOR A DYNAMIC READ OPERATION IN A MEMORY BIT CELL」という名称の米国特許出願第15/085,187号の優先権を主張する。

〔 0 0 0 2 〕

本開示の技術は概して、データを記憶するためのメモリピットセルを使用するメモリシステムに関し、より詳細には、メモリピットセルにおける動的読み取り動作を実行するための動的読み取り回路に関する。

【背景技術】

[ 0 0 0 3 ]

中央処理ユニット(CPU)を含むプロセッサベースシステムまたは他のプロセッサは、様々な種類のメモリをシステム動作に利用する。このメモリは、データ記憶用のシステムメモリとして使用されてもよい。このメモリは、CPUまたはプロセッサによって実行すべきプログラムコードまたは命令を記憶するために使用されてもよい。

[ 0 0 0 4 ]

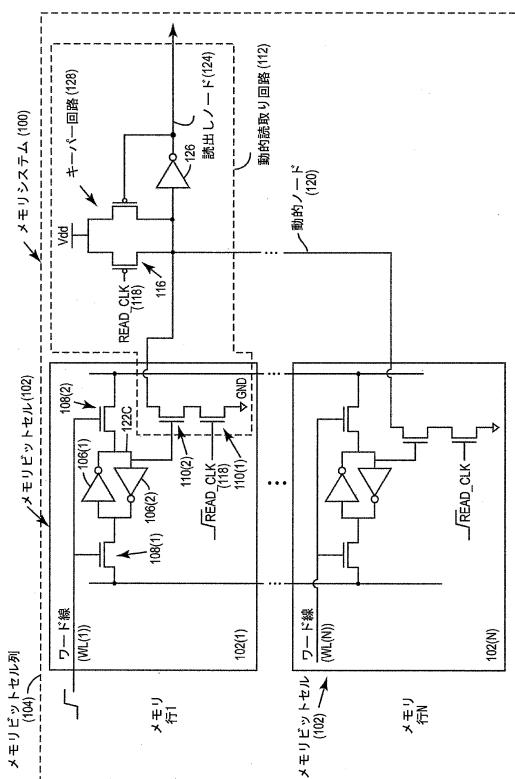

たとえば、図1は、プロセッサベースシステムに設けることができるメモリシステム100を示す。この特定の例におけるメモリシステム100は、図1に示すように、データを記憶するためのメモリビットセル102(1)～102(N)を使用する。各メモリビットセル102は、単一のビットの情報を記憶することができる。図1には、複数のメモリビットセル102(1)～102(N)を含む単一のメモリビットセル列104が示されている。ここで、「N」は所望のメモリビットセルの任意の数の行であってもよい。しかし、メモリビットセル102(1)～102(N)のデータアレイを形成するためにメモリシステム100内に複数のメモリビットセル列104が設けられてもよいことに留意されたい。この例では、メモリビットセル102(1)～102(N)は、8つのトランジスタ(T)(8-T)補メモリビットセルの形態で設けられる。メモリビットセル102(1)を参考例として使用する場合、各メモリビットセル102(1)～102(N)は、2つの交差結合インバータ106(1)、106(2)(すなわち、4つのトランジスタ)と、よく知られているように、書き込み動作を実行するためにメモリビットセル102(1)のアクセスされるメモリ行1に対して行ワード線WL(1)によってアクティブ化されるように構成された2つのアクセストランジスタ108(1)、108(2)とを含む。メモリビットセル102(1)における読み取り動作を実行するための動的読み取り回路112の一部として、メモリビットセル102(1)用に、2つの追加のトランジスタ、プルダウンNFET110(1)、および読み取りポートNFET110(2)が設けられる。動的読み取り回路112は、メモリビットセル列104に関するメモリビットセル102(1)～102(N)の各々に対する読み取り動作を実行する。所与のそれぞれのメモリ行1-Nに対して特定のワード

線WL(1)～WL(N)をアサートすると、読み取り動作中に動的読み取り回路112によってどのメモリビットセル102(1)～102(N)が読み取られるかが制御される。追加のプルダウンNFET110(1)および読み取りポートNFET110(2)を動的読み取り回路112内に設けると、メモリビットセル102(1)の書き込み実行がメモリビットセル102(1)の読み取り実行から分離される。

#### 【0005】

メモリビットセル102(1)のプリチャージフェーズの間に、読み取りクロック信号(read\_clk)118が、読み取り動作がアクティブではないことを示す低論理レベルであることに応答してチャージP型電界効果トランジスタ(PFET)116がアクティブ化される。これによって、動的読み取り回路112内の動的ノード120が電圧Vddにプリチャージされる。次いで、クロック信号(read\_clk)118が、読み取り動作を示す論理高レベルであることに応答した評価フェーズの間に、PFET116がオフにされ、プルダウンNFET110(1)がアクティブ化されグランド(GND)に結合される。選択されたメモリビットセル102(1)～102(N)における補ノード122C上の電荷が、読み取り動作の間論理「1」(すなわち、電圧Vdd)である場合、プルダウンNFET110(1)がアクティブされ動的ノード120をグランド(GND)にプルダウンする。動的ノード120をグランド(GND)にプルすると、インバータ126によって読み出しノード124上に論理「1」が生成される。しかし、読み取り動作の間論理「1」状態を有する補ノード122Cによって最初にキーパー回路128がアクティブ化され、インバータ126が読み出しノード124上で論理「0」を生成し、キーパー回路128をアクティブ化されたままにし、それによって、動的ノード120がプルダウンNFET110(1)と競合して電圧Vddまでプルされる

10

#### 【発明の概要】

20

#### 【課題を解決するための手段】

#### 【0006】

本開示の態様は、メモリビットセルにおける動的読み取り動作のための遅延キーパー回路の漏れ認識アクティブ化制御に関する。この点に関して、一態様では、メモリビットセルに対して読み取り動作を実行するように構成された動的読み取り回路用に漏れ認識アクティブ化制御回路が提供される。動的読み取り回路は、動的読み取り動作の評価フェーズの間動的読み取り回路内の動的ノード上でアサートされた選択されたメモリビットセルからの読み出し値を維持するように構成された遅延キーパー回路を含む。読み取り動作が開始されるときに動的ノードを逆の電圧レベルにプルする動的読み取り回路内の遅延キーパー回路と読み取りポート回路との間の競合を防止または軽減するために、遅延キーパー回路は、評価フェーズの間選択的に非アクティブ化される。しかし、プロセスばらつきおよび技術ノードスケーリングなどの要因が遅延キーパー回路および読み取りポート回路内のトランジスタの漏れ電流、およびそれらの回路の相対トランジスタ強度に影響を与えることがあるので、本明細書において開示する態様は、遅延キーパー回路のアクティブ化タイミングを制御するための漏れ認識アクティブ化制御回路を含む。漏れ認識アクティブ化制御回路は、N型電界効果トランジスタ(NFET)漏れ電流とP型FET(PFET)漏れ電流との比較に基づいて遅延キーパー回路のアクティブ化タイミングを適応的に制御するように構成される。このようにして、動的読み取り回路の遅延キーパー回路および読み取りポート回路内のNFETおよびPFETの相対強度が設計時仮定と異なる場合、漏れ認識アクティブ化制御回路は、読み取り動作の評価フェーズが開始したことに応答して読み取りポート回路との競合を回避または軽減するように、NFETおよびPFETの実際の相対強度に基づいて、遅延キーパー回路のアクティブ化タイミングを適応的に調整することができる。

30

#### 【0007】

40

この点に関して、例示的な一態様では、メモリビットセルに対する動的読み取り回路内の遅延キーパー回路のアクティブ化を制御するための漏れ認識アクティブ化制御回路が提供される。漏れ認識アクティブ化制御回路は、動的読み取り回路内の少なくとも1つのNFETの漏れ電流を示すNFET漏れインジケータを生成するように構成されたNFET漏れ回路を備える。漏れ認識アクティブ化制御回路は、動的読み取り回路内の少なくとも1つのPFETの漏れ電流を示すPFET漏れインジケータを生成するように構成されたPFET漏れ回路も備える。漏れ認識アクティブ化制御回路は比較器回路も備える。比較器回路は、NFET漏れインジケータ

50

およびPFET漏れインジケータを受け取るように構成される。比較器回路はまた、NFET漏れインジケータとPFET漏れインジケータを比較するように構成される。比較器回路はまた、NFET漏れインジケータとPFET漏れインジケータの比較に基づいてFET漏れ信号を生成するように構成される。漏れ認識アクティブ化制御回路は、遅延キーパー回路のアクティブ化タイミングを制御するためにFET漏れ信号に基づいて少なくとも1つの制御信号を適応的に生成するように構成された制御信号生成器も備える。

#### 【0008】

別の例示的な態様では、メモリビットセルに対する動的読取り回路内の遅延キーパー回路のアクティブ化を制御するための漏れ認識アクティブ化制御回路が提供される。漏れ認識アクティブ化制御回路は、動的読取り回路内の少なくとも1つのNFETの漏れ電流を示すNFET漏れインジケータを生成するための手段を備える。漏れ認識アクティブ化制御回路は、動的読取り回路内の少なくとも1つのPFETの漏れ電流を示すPFET漏れインジケータを生成するための手段も備える。漏れ認識アクティブ化制御回路は、NFET漏れインジケータおよびPFET漏れインジケータを受け取るための手段も備える。漏れ認識アクティブ化制御回路は、NFET漏れインジケータとPFET漏れインジケータを比較するための手段も備える。漏れ認識アクティブ化制御回路は、NFET漏れインジケータとPFET漏れインジケータの比較に基づいてFET漏れ信号を生成するための手段も備える。漏れ認識アクティブ化制御回路は、遅延キーパー回路のアクティブ化タイミングを制御するためにFET漏れ信号に基づいて少なくとも1つの制御信号を適応的に生成するための手段も備える。

#### 【0009】

別の例示的な態様では、メモリビットセルに対する動的読取り回路内の遅延キーパー回路のアクティブ化を制御するための方法が提供される。この方法は、動的読取り回路内の少なくとも1つのNFETの漏れ電流を判定するステップを含む。この方法は、動的読取り回路内の少なくとも1つのPFETの漏れ電流を判定するステップも含む。この方法は、少なくとも1つのNFETの判定された漏れ電流を少なくとも1つのPFETの判定された漏れ電流と比較するステップも含む。この方法は、少なくとも1つのNFETの判定された漏れ電流と少なくとも1つのPFETの判定された漏れ電流との比較に基づいて遅延キーパー回路に対する少なくとも1つの制御信号を適応的に生成するステップも含む。

#### 【0010】

別の例示的な態様では、メモリシステムが提供される。このメモリシステムは、補完電圧(Complement Voltage)を記憶するように構成された記憶回路と、記憶回路に結合された読み取りポート回路とを備えるメモリビットセルを備える。読み取りポート回路は、読み取り動作に応答して動的ノード上で補完電圧を生成するように構成される。メモリシステムは、動的読み取り回路も備える。動的読み取り回路は、動的ノードと、評価フェーズの外側で動的ノード上に補完電圧を維持するためにパルスに応答してアクティブ化されるように構成され、読み取り動作の評価フェーズに応答して、パルスに応答して非アクティブ化されるように構成された遅延キーパー回路とを備える。メモリシステムは、漏れ認識アクティブ化制御回路も備える。漏れ認識アクティブ化制御回路は、少なくとも1つのNFETの漏れ電流と少なくとも1つのPFETの漏れ電流との比較に基づいてFET漏れ信号を生成するように構成された漏れ回路を備える。漏れ認識アクティブ化制御回路は、第2の遅延キーパー回路のアクティブ化タイミングを制御するためにFET漏れ信号に基づいて少なくとも1つの制御信号を適応的に生成するように構成された制御信号生成器も備える。メモリシステムは、少なくとも1つの制御信号に応答して第2の遅延キーパー回路のアクティブ化および非アクティブ化のための制御アクティブ化タイミングに基づくパルス幅を有するパルスを生成するように構成されたパルス発生器も備える。

#### 【図面の簡単な説明】

#### 【0011】

【図1】8つのトランジスタ(T)(8-T)メモリビットセルと、メモリビットセルに対して読み取り動作を実行するための動的読み取り回路とを使用する例示的なメモリシステムの概略図である。

10

20

30

40

50

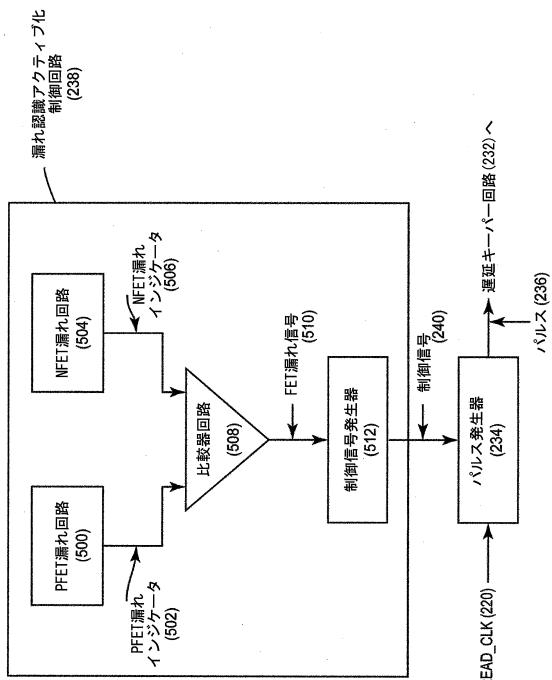

【図2】複数のメモリビットセルと、読み取り動作に応答して、N型電界効果トランジスタ(NFET)漏れ電流とP型FET(PFET)漏れ電流との比較に基づいて遅延キーパー回路のアクティブ化タイミングを制御するための漏れ認識アクティブ化制御回路を使用する動的読み取り回路とを備える例示的なメモリシステムの回路図である。

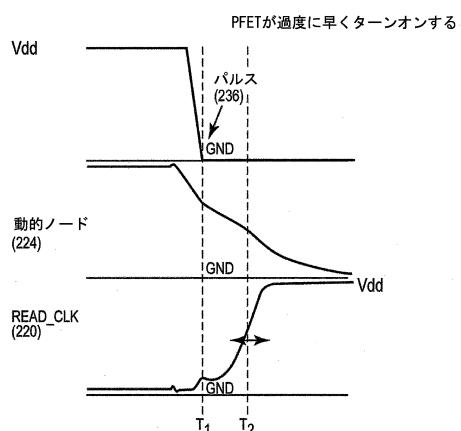

【図3A】図2における動的読み取り回路内のキーパー回路の作動が十分な時間にわたって遅延されず、それによって動的読み取り回路内の動的ノードのプルダウンがプッシュアウトされ、読み取り実行が影響を受けることを示す図である。

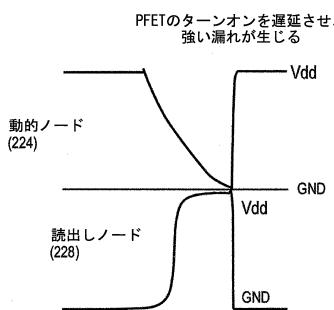

【図3B】図2における動的読み取り回路内の遅延キーパー回路のアクティブ化が過度に長く遅延され、それによって、動的読み取り回路内の動的ノードがグランドにドロープし、読み取り動作に応答して誤った読み出し値が生成されることを示すタイミング図である。 10

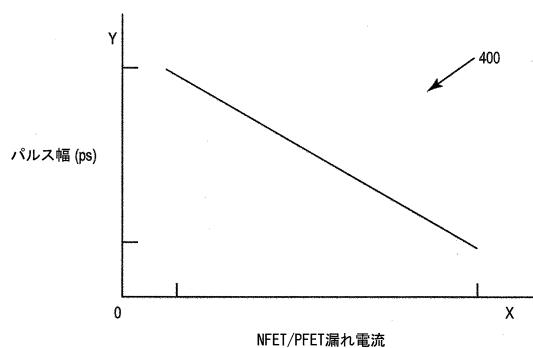

【図4】NFET漏れ電流/強度とPFET漏れ電流/強度の比と図2における動的読み取り回路内の遅延キーパー回路のアクティブ化タイミングとの例示的な関係を示すグラフである。

【図5】NFET漏れ電流とPFET漏れ電流との比較に基づいて遅延キーパー回路のアクティブ化タイミングを制御するために遅延キーパー回路に与えられるパルスのアクティブ化タイミングを制御するための少なくとも1つの制御信号を生成するために、図2における動的読み取り回路内に設けることができる例示的な漏れ認識アクティブ化制御回路の概略図である。

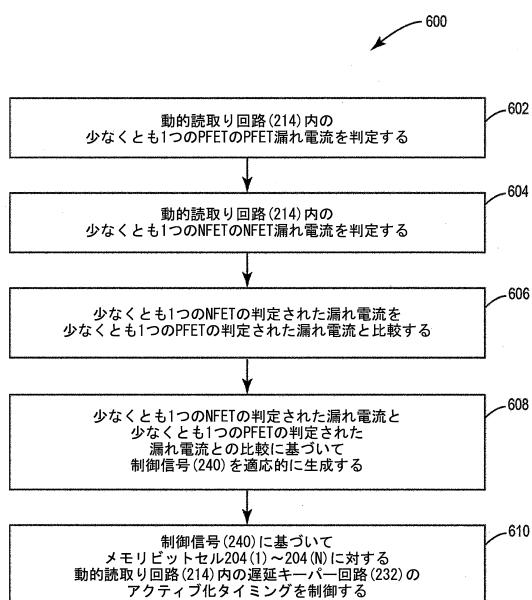

【図6】メモリビットセルにおける読み取り動作に関して図5における動的読み取り回路内の遅延キーパー回路のアクティブ化タイミングを制御する例示的なプロセスを示すフローチャートである。 20

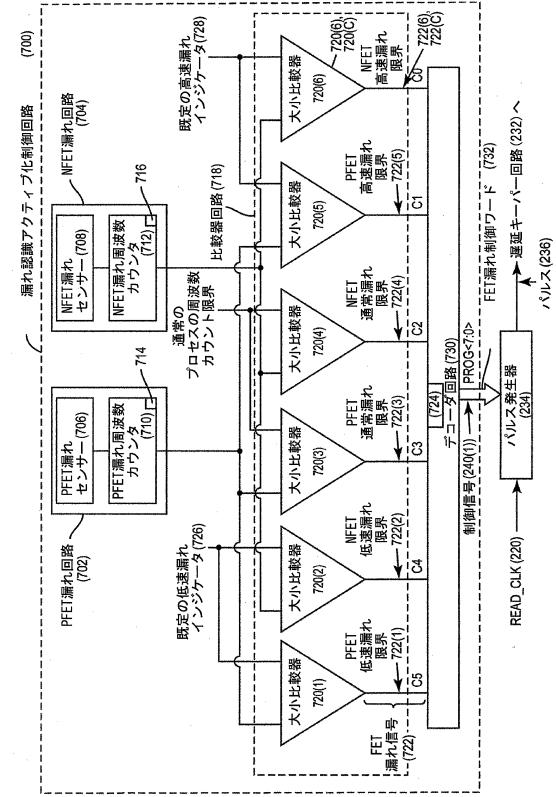

【図7】NFET漏れ電流とPFET漏れ電流との比較に基づいて遅延キーパー回路のアクティブ化タイミングを制御するために遅延キーパー回路に与えられるパルスの作動タイミングを制御するための制御信号を生成するために、図2における動的読み取り回路内に設けることができる別の例示的な漏れ認識アクティブ化制御回路の概略図である。

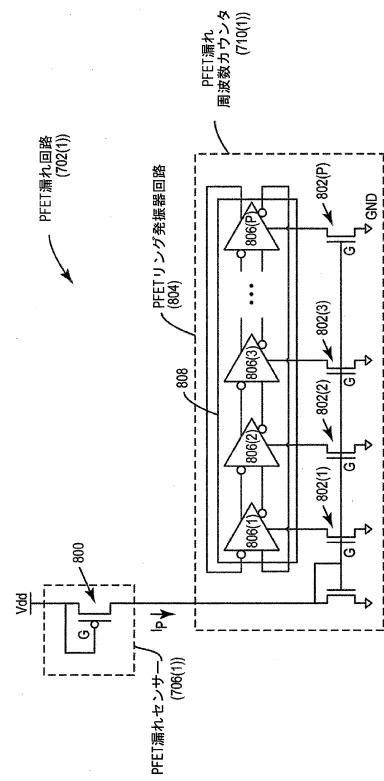

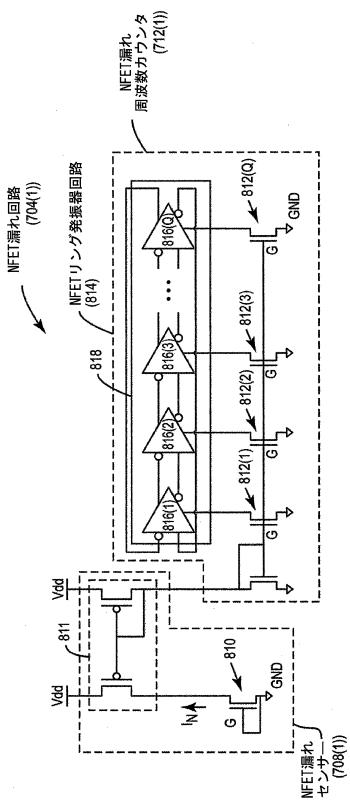

【図8A】図2における動的読み取り回路内の漏れ認識アクティブ化制御回路において使用できる例示的なNFET漏れ回路であって、動的読み取り回路内の少なくとも1つのNFETの漏れ電流を示すNFET漏れインジケータを生成するように構成されたNFET漏れ回路の回路図である。

【図8B】図2における動的読み取り回路内の漏れ認識アクティブ化制御回路において使用できる例示的なPFET漏れ回路であって、動的読み取り回路内の少なくとも1つのPFETの漏れ電流を示すPFET漏れインジケータを生成するように構成されたPFET漏れ回路の回路図である。 30

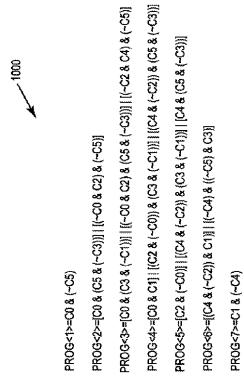

【図9】様々なNFET漏れインジケータおよびPFET漏れインジケータに基づいて遅延キーパー回路のアクティブ化タイミングを制御するために、図6における漏れ認識アクティブ化制御回路によって生成される例示的な漏れFET漏れ制御ワードを示す論理テーブルである。

【図10】遅延キーパー回路のアクティブ化タイミングを制御するために図9における論理テーブルに従ってFET漏れ制御ワードを生成するための図6における漏れ認識アクティブ化制御回路用の例示的な論理文のリストである。

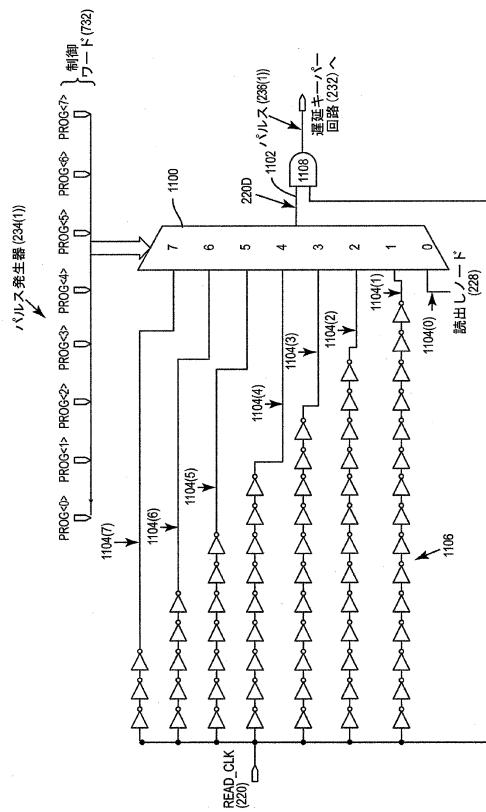

【図11】NFET漏れインジケータとPFET漏れインジケータとの比較に基づいて遅延キーパー回路のアクティブ化タイミングを制御するために、図7における漏れ認識アクティブ化制御回路から生成された制御信号を受け取るように構成された例示的なパルス発生器の回路図である。 40

【図12】読み取り動作に応答し、かつ本明細書において開示する態様のいずれかに従って遅延キーパー回路のアクティブ化タイミングを制御するための漏れ認識アクティブ化制御回路を使用する動的読み取り回路を含むメモリシステムを含むことができる例示的なプロセッサベースシステムのブロック図である。

#### 【発明を実施するための形態】

##### 【0012】

ここで図面を参照して、本開示のいくつかの例示的な態様について説明する。「例示的 50

」という語は、本明細書では「例、事例、または例示としての働きをすること」を意味するためには使用される。本明細書で「例示的」と記載されている任意の態様は、必ずしも他の態様よりも好ましいまたは有利であると解釈されるべきではない。

#### 【0013】

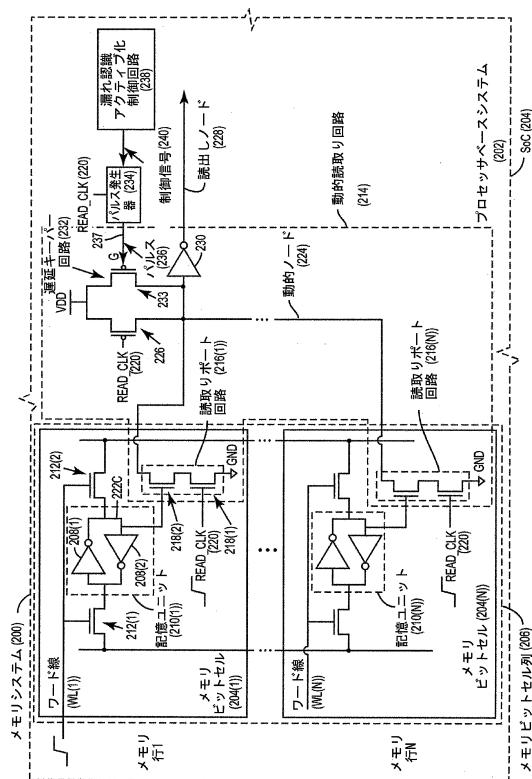

たとえば、図2は、プロセッサベースシステム202に設けることができるメモリシステム200を示す。プロセッサベースシステム202は、一例としてシステムオンチップ(SoC)204内に設けられてもよい。メモリシステム200は、データを記憶するための複数のメモリビットセル204(1)～204(N)を使用し、この場合、「N」は所望のメモリビットセル204(1)～204(N)の任意の数の行であってもよい。各メモリビットセル204(1)～204(N)は、単一のビットの情報を記憶することができる。図2には、複数のメモリビットセル204(1)～204(N)を含む単一のメモリビットセル列206が示されている。しかし、メモリビットセル204(1)～204(N)のデータアレイを形成するためにメモリシステム200内に複数のメモリビットセル列206が設けられてもよいことに留意されたい。この例では、各メモリビットセル204(1)～204(N)を示す参考例としてメモリビットセル204(1)を使用し、メモリビットセル204(1)は、記憶ユニット210(1)～210(N)を形成するための交差結合インバータ208(1)、208(2)(すなわち、4つのトランジスタ)と、6つのトランジスタ(T)(6-T)相補メモリビットセル構成における2つのアクセストランジスタ212(1)、212(2)とを含む。2つのアクセストランジスタ212(1)、212(2)は、読み取り動作および書き込み動作を実行するためにメモリビットセル204(1)～204(N)のアクセスされるメモリ行1に対して行ワード線WL(1)、WL(N)によってアクティブ化されるように構成される。10

20

#### 【0014】

引き続き図2を参照すると、選択されたメモリビットセル204(1)～204(N)に対して読み取り動作を実行するためにメモリシステム200内に動的読み取り回路214が設けられる。所与のそれぞれのメモリ行1-Nに対して特定のワード線WL(1)～WL(N)をアサートすると、読み取り動作中に動的読み取り回路214によってどのメモリビットセル204(1)～204(N)が読み取られるかが制御される。一例としてメモリビットセル204(1)に関して、メモリビットセル204(1)に対する読み取り動作のための動的読み取り回路214の一部として、メモリビットセル204(1)に読み取りポート回路216(1)が設けられる。この例における読み取りポート回路216(1)は、N-FETベース読み取りポート回路であり、2つのトランジスタと、プルダウンNFET218(1)と、読み取りポートNFET218(2)とを含み、メモリビットセル204(1)が8トランジスタ(8-T)メモリビットセルとして構成されるのを可能にする。プルダウンNFET218(1)は、読み取り動作に応答して、読み取りクロック信号(read\_clk)220に応答してアクティブ化される。読み取りポートNFET218(2)は、補ノード222C上の電圧(すなわち、データ)が論理高レベルであることに基づいてアクティブ化され、それによって、動的読み取り回路214の動的ノード224がグランド(GND)にプルされる。読み取りポートNFET218(2)は、補ノード222C上の電圧(すなわち、データ)が論理低レベルであることに基づいて非アクティブ化され、それによって、動的読み取り回路214の動的ノード224がその電荷を電圧Vddに保持する。いずれの場合も、メモリビットセル204(1)は、読み取り動作に応答して動的ノード224上の電圧を補ノード222C上の電圧になるように生成するように構成される。追加のプルダウンNFET218(1)および読み取りポートNFET218(2)を読み取りポート回路216(1)内に設けると、メモリビットセル204(1)の書き込み実行がメモリビットセル204(1)の読み取り実行から分離される。30

40

#### 【0015】

メモリビットセル204(1)のプリチャージフェーズの間に、読み取りクロック信号(read\_clk)220が、読み取り動作がアクティブではないことを示す低論理レベルであることに応答して動的読み取り回路214内のプリチャージPFET226がアクティブ化される。これによって、動的読み取り回路214内の動的ノード224が電圧Vddにプリチャージされる。次いで、クロック信号(read\_clk)220が、読み取り動作がアクティブであることを示す論理高レベルであることに応答した評価フェーズの間に、プリチャージPFET226がオフにされ、プルダウンNFET218(1)がアクティブ化されグランド(GND)に結合される。メモリビットセル204(1)内の補ノード222C上の電荷が、読み取り動作の間論理「1」(すなわち、電圧Vdd)である場合、読み取り50

ポートNFET218(2)がアクティブされ動的ノード224をグランド(GND)にプルダウンする。動的ノード224をグランド(GND)にプルすると、インバータ230によって読み出しノード228上に論理「1」が生成される。しかし、この例ではPFET233から構成されたPFETベース遅延キーパー回路である、動的読み取り回路214内に設けられた遅延キーパー回路232は、読み取り動作がアクティブ化されたときにオフにされる。しかし、遅延キーパー回路232は、PFETおよびNFETの漏れ電流の影響を受けない計画された時間の経過後にオンにされる。遅延キーパー回路232がオンにされるのが過度に早く、ノード222Cが論理「1」であるときに遅延キーパー回路232の漏れがプルダウンNFET218(1)および読み取りポートNFET218(2)と比較して大きくなった場合、動的ノード224は、読み取りポート回路216(1)内のプルダウンNFET218(1)と競合して電圧Vddに向けてプルアップされる。

10

#### 【0016】

図2におけるメモリシステム200内の動的ノード224上での遅延キーパー回路232と読み取りポート回路216(1)内のプルダウンNFET218(1)との間のこの競合を回避または軽減するために、図2に示すようにパルス発生器234が設けられる。パルス発生器234は、読み取りクロック信号(read\_clk)220に応答して遅延キーパー回路232をアクティブ化および非アクティブ化して、遅延キーパー回路232と読み取りポート回路216(1)内のプルダウンNFET218(1)との間の競合を回避または軽減するように構成される。パルス発生器234は、読み取り動作を示す読み取りクロック信号(read\_clk)220に応答してパルス236を生成するように構成される。この例では、パルス236は、遅延キーパー回路232のゲート(G)に与えられる。したがって、最初、動的読み取り回路214の評価フェーズの間に、パルス発生器234は出力ノード237上でパルス236を生成し、最初は、遅延キーパー回路232を非アクティブ化して動的ノード224上のプルダウンNFET218(1)との競合を回避する。この例では、パルス発生器234によって生成されるパルス236は、アクティブ低パルスである。その理由は、遅延キーパー回路232はこの例ではより低い信号レベルによってアクティブ化されるPFETであるからである。パルス236のパルス幅は、プルダウンNFET218(1)が動的ノード224上で評価フェーズを実行するのを可能にするための所望の期間にわたって遅延キーパー回路232の非アクティブ化を制御するようにパルス発生器234によって制御される。その後、動的読み取り回路214の以後の維持フェーズの間に、パルス236が出力ノード237上で満了し、遅延キーパー回路232がアクティブ化されて動的ノード224上に読み取り電圧(すなわち、データ)が維持される。

20

#### 【0017】

したがって、上述のように、メモリシステム200内のパルス発生器234によるパルス236の生成のタイミング制御は、遅延キーパー回路232と読み取りポート回路216(1)内のプルダウンNFET218(1)との間の競合を回避または軽減するうえで重要である。アクティブ化タイミング制御は、設計時に遅延キーパー回路232および読み取りポート回路216(1)内のプルダウンNFET218(1)内のトランジスタの駆動強度に基づいて計画されてもよい。しかし、遅延キーパー回路232およびプルダウンNFET218(1)内のトランジスタの駆動強度は、プロセスばらつきおよび技術ノードスケーリングなどの要因に起因して設計パラメータに対して変動する場合がある。トランジスタ駆動強度のこのような変動の結果として、遅延キーパー回路232のトランジスタ駆動強度が、設計時に読み取りポート回路216(1)に対して予想されたトランジスタ駆動強度よりも大きくなる場合がある。このシナリオにおいて、パルス発生器234によるパルス236の生成は、遅延キーパー回路232と読み取りポート回路216(1)内のプルダウンNFET218(1)との間の競合を回避または軽減するのに十分な程度に遅延されない場合がある。一方、読み取りポート回路216(1)のトランジスタ駆動強度よりも大きい場合、パルス発生器234によるパルス236の生成の遅延が過度に長くなり、遅延キーパー回路232と読み取りポート回路216(1)内のプルダウンNFET218(1)との間の競合が回避されることもあるいは軽減されることもなくなる場合がある。

40

#### 【0018】

たとえば、図2におけるメモリビットセル204(1)内の補ノード222Cが読み取り動作の前に論理「1」状態を有し、図3Aに示すように、遅延キーパー回路232をアクティブ化するため

50

の時間 $T_1$ におけるパルス236の生成が過度に早いかまたは十分に遅延されない場合、プルダウンNFET218(1)による動的ノード224のプルダウンは時間 $T_2$ においてプッシュアウトされる。このようにして、遅延キーパー回路232のアクティブ化が過度に早いと、メモリビットセル204(1)の読出しが遅延され、読み取り実行が影響を受ける。さらに、図2におけるメモリビットセル204(1)内の補ノード222Cが読み取り動作の前に論理「0」状態を有し、図3Bに示すように、遅延キーパー回路232のアクティブ化の遅延が過度に長く、遅延キーパー回路232の漏れ電流が強い場合、動的ノード224はグランド(GND)にドロープする。この場合、遅延キーパー回路232は論理「1」ではなく論理「0」を記憶し、それによって、読出しノード228において正しい論理「0」値ではなく論理「1」値が読み出される。

## 【0019】

10

遅延キーパー回路232における読み取りポート回路216(1)へのトランジスタ漏れ電流の関係は、この例では図4におけるチャート400に示すように認識される。図4におけるチャート400に示すように、NFET漏れ電流(すなわち、駆動強度)とPFET漏れ電流(すなわち、駆動強度)の比が低くなるにつれて、パルス236のパルス幅を大きくして、図3Aに関して上記で説明したように動的ノード224のプルダウンがプッシュアウトされ読み取り動作実行が影響を受けるのを回避する必要がある。しかし、図4におけるチャート400に示すように、NFET漏れ電流(すなわち、駆動強度)とPFET漏れ電流(すなわち、駆動強度)の比が高くなるにつれて、パルス236のパルス幅を小さくして、図3Bに関して上記で説明したように、動的ノード224がグランド(GND)にドロープするよりも早く遅延キーパー回路232をアクティブ化し、その後誤ったデータ(「0」ではなく論理「1」)を読み取られるのを減らす必要がある。

## 【0020】

20

この点に関して、図2のメモリシステム200は漏れ認識アクティブ化制御回路238を含む。以下でより詳細に説明するように、漏れ認識アクティブ化制御回路238は、NFET漏れ電流とPFET漏れ電流との比較に基づいて遅延キーパー回路232のアクティブ化タイミングを適応的に制御するように構成される。漏れ認識アクティブ化制御回路238は、制御信号240を生成して、NFET漏れ電流とPFET漏れ電流との比較に基づいてパルス発生器234によって生成されたパルス236のパルス幅のアクティブ化タイミングを制御するように構成される。上述のように、図2におけるメモリシステム200内の遅延キーパー回路232はPFETを含む。読み取りポート回路216(1)～216(N)はプルダウンNFET218(1)を含む。PFET漏れ電流およびNFET漏れ電流はそれぞれのトランジスタ駆動強度に関係付けられる。したがって、漏れ認識アクティブ化制御回路238は、NFET漏れ電流とPFET漏れ電流との比較に基づいて遅延キーパー回路232のアクティブ化タイミングを適応的に制御するように構成される。したがって、パルス236のパルス幅に対する調整は、動的読み取り回路214がメモリビットセル204(1)～204(N)からの読み取りデータをより正確に与えるようにメモリシステム200内のNFETトランジスタおよびPFETトランジスタの設計および/または製作におけるばらつきに起因するトランジスタ駆動強度のばらつきに対処するように施すことができる。

30

## 【0021】

40

この点に関して、図5は、NFET漏れ電流とPFET漏れ電流との比較に基づいて遅延キーパー回路232のアクティブ化タイミングを適応的に制御するように図2におけるメモリシステム200内に設けられた漏れ認識アクティブ化制御回路238の概略図である。図5に示すように、漏れ認識アクティブ化制御回路238は、動的読み取り回路214内の少なくとも1つのPFETの漏れ電流を示すPFET漏れインジケータ502を生成するように構成されたPFET漏れ回路500を含む。たとえば、PFET漏れ回路500は、遅延キーパー回路232におけるPFET漏れ電流を示すPFET漏れインジケータ502を生成するために、この例ではメモリシステム200の遅延キーパー回路232と同じ集積回路(IC)および/またはICの領域内に位置する1つまたは複数のPFETを含んでもよい。PFET漏れ回路500はまた、動的読み取り回路214において動作中に生じる場合があるPFET漏れ電流を測定することが望ましい場合、動的読み取り回路214の動作中にPFET漏れインジケータ502を生成するように構成されてもよい。さらに、漏れ認識アクティブ化制御回路238はまた、動的読み取り回路214内の少なくとも1つのNFETのNFET漏れ電流を

50

示すNFET漏れインジケータ506を生成するように構成されたNFET漏れ回路504を含む。また、NFET漏れ回路504は、読み取りポート回路216(1)～216(N)におけるNFET漏れ電流を示すNFE T漏れインジケータ506を生成するために、この例ではメモリシステム200の読み取りポート回路216(1)～216(N)と同じICおよび/またはICの領域内に位置する1つまたは複数のNFETを含んでもよい。NFET漏れ回路504はまた、動的読み取り回路214が動作中に生じる場合があるNFET漏れ電流を測定することが望ましい場合、動的読み取り回路214の動作中にNFET漏れインジケータ506を生成するように構成されてもよい。

#### 【 0 0 2 2 】

引き続き図5を参照すると、漏れ認識アクティブ化制御回路238は比較器回路508も含む。比較器回路508は、PFET漏れインジケータ502およびNFET漏れインジケータ506を受け取り、PFET漏れインジケータ502をNFET漏れインジケータ506と比較するように構成される。比較器回路508は、PFET漏れインジケータ502とNFET漏れインジケータ506の比較に基づいてFET漏れ信号510を生成するように構成される。FET漏れ信号510は、遅延キーパー回路232のアクティブ化タイミングを制御するためにFET漏れ信号510に基づいて制御信号240を適応的に生成するように構成された制御信号生成器512に備えられる。上述のように、この例では、制御信号240は、図5に示すようにパルス発生器234によって生成されるパルス236のアクティブ化タイミングを制御し、この例では遅延キーパー回路232のアクティブ化タイミングを制御する。パルス発生器234が必須ではないことに留意されたい。漏れ認識アクティブ化制御回路238は、制御信号240を生成して遅延キーパー回路232に直接与え、遅延キーパー回路232のアクティブ化タイミングを制御するように構成することができる。

#### 【 0 0 2 3 】

NFETの漏れ電流とPFETの漏れ電流との比は、設計および製作プロセスに基づいてばらつく場合がある。したがって、NFET漏れ電流とPFET漏れ電流の様々な動作速度シナリオに基づいて制御信号を生成する機能を有する漏れ認識アクティブ化制御回路238を提供することが望ましい場合がある。たとえば、PFETおよび/またはNFETはその公称(予想)挙動および切替え速度から変動する場合があり、IC内の電圧および温度のばらつきに影響を与える製作プロセスのばらつきに応じて比較的遅い切替え速度または速い切替え速度で動作することがある(回路シミュレーションの点では、遅いコーナーはデバイスの最も遅い予想挙動を表し、公称コーナーは平均予想挙動を表し、速いコーナーは最も速い予想挙動を表す)。製作プロセスのそのようなばらつきは、NFETおよびPFETの漏れ電流に影響を与える。さらに、PFETは、製作プロセスの結果としてNFETと異なるようにばらつく場合があり、したがって、切替え速度においてNFETとは異なるばらつきが生じることがあり、その逆も同様である。たとえば、製作されるPFETはより低速のデバイスである場合があり、一方、製作されるNFETはより高速のデバイスである場合がある。PFETおよびNFETの漏れ電流は、切替え速度に関連しており、より高速のデバイスはより大きい漏れ電流を有する。したがって、製作されるPFETおよびNFETにおいて生じる場合があるこれらの切替え速度差に起因して、漏れ認識アクティブ化制御回路238が、遅延キーパー回路232のアクティブ化タイミングをどのように制御するかを決定する際にPFETおよびNFETの相対切替え速度を考慮することが望ましい場合がある。

#### 【 0 0 2 4 】

図6は、図2における漏れ認識アクティブ化制御回路238が動的読み取り回路214内の遅延キーパー回路232のアクティブ化タイミングを制御する例示的なプロセス600を概略的に示すフローチャートである。図6に示すように、プロセス600は、動的読み取り回路214内の少なくとも1つのPFETのPFET漏れ電流を判定する(ブロック602)。プロセス600は、動的読み取り回路214内の少なくとも1つのNFETのNFET漏れ電流を判定する(ブロック604)。少なくとも1つのNFETの判定された漏れ電流が少なくとも1つのPFETの判定された漏れ電流と比較される(ブロック606)。少なくとも1つのNFETの判定された漏れ電流と少なくとも1つのPFETの判定された漏れ電流との比較に基づいて、遅延キーパー回路232に対して少なくとも1つの制御信号240が適応的に生成される(ブロック608)。プロセス600はまた、少なくとも1つの制御信号240に基づいてメモリビットセル204(1)～204(N)に対する動的読み取り回路214内の

10

20

30

40

50

遅延キーパー回路232のアクティブ化タイミングを制御することを含むことができる(プロック610)。

#### 【 0 0 2 5 】

図7は、図2の動的読み取り回路214内に設けることができる別の例示的な漏れ認識アクティブ化制御回路700の概略図である。以下で説明するように、漏れ認識アクティブ化制御回路700は、NFET漏れ電流とPFET漏れ電流との比較に基づいて、パルス発生器234によるパルス236の生成のタイミングを図2における遅延キーパー回路232のアクティブ化タイミングに制御するために使用することができる制御信号240(1)を生成するように構成される。この点に関して、それぞれPFETおよびNFETの漏れ電流を判定するためにPFET漏れ回路702およびNFET漏れ回路704が設けられる。この例では、PFET漏れ回路702は、PFETの漏れ電流を検知するように構成されたPFET漏れセンサー706を含む。同様に、NFET漏れ回路704は、NFETの漏れ電流を検知するように構成されたNFET漏れセンサー708を含む。上述のように、PFET漏れセンサー706および/またはNFET漏れセンサー708は、PFETおよび/またはNFETの判定された漏れ電流が動的読み取り回路214内のPFETおよび/またはNFETの漏れ電流を示すように、図2における動的読み取り回路214を含む同じ回路またはICの領域内に設けることができる。10

#### 【 0 0 2 6 】

図7を引き続き参照すると、PFET漏れ回路702およびNFET漏れ回路704はまた、それぞれ、PFET漏れ周波数カウンタ710およびNFET漏れ周波数カウンタ712を含む。PFET漏れ周波数カウンタ710およびNFET漏れ周波数カウンタ712はそれぞれ、PFETおよびNFETの漏れ電流を示すPFET漏れ周波数カウント714およびNFET漏れ周波数カウント716を記憶するように構成される。PFET漏れセンサー706およびNFET漏れセンサー708は、それぞれ、PFETおよびNFETの判定された漏れ電流の関数として、それぞれのPFET漏れ周波数カウンタ710およびNFET漏れ周波数カウンタ712におけるPFET漏れ周波数カウント714およびNFET漏れ周波数カウント716を更新するように構成される。たとえば、図7におけるPFET漏れ回路702の一例は、図8AにおけるPFET漏れ回路702(1)として提示される。図8Aに示すように、PFET800から構成されたPFET漏れセンサー706(1)が設けられる。PFET800のゲート(G)は、PFET800がオフにされるかまたは非アクティブ化されるように電圧Vddに結合される。したがって、PFET800からの漏れ電流として任意のPFET漏れ電流 $I_p$ がPFET漏れ周波数カウンタ710(1)に与えられる。PFET漏れ電流 $I_p$ は、PFET漏れ回路702(1)内のPFETリング発振器回路804内のNFET802(1)～802(P)の一連のゲート(G)に結合される。NFET802(1)～802(P)の各々は、PFETリング発振器回路804内の発振ループ808内に構成されたそれぞれのバッファ回路806(1)～806(P)のアクティブ化を制御するように構成される。したがって、PFET漏れ電流 $I_p$ の強度は、PFETリング発振器回路804内のNFET802(1)～802(P)のターンオン強度を制御し、それによって、バッファ回路806(1)～806(P)の速度または発振を制御してPFET漏れ電流を示す。たとえば、発振ループ808の各反復を使用して図7におけるPFET漏れ周波数カウント714などのPFET漏れ周波数カウントを増分させることができる。2030

#### 【 0 0 2 7 】

同様に、図7におけるNFET漏れ回路704の一例は、図8BにおけるNFET漏れ回路704(1)として提示される。図8Bに示すように、NFET810とPFET電流ミラー811とから構成されたNFET漏れセンサー708(1)が設けられる。NFET810のゲート(G)は、NFET810がオフにされるかまたは非アクティブ化されるようにグランド(GND)に結合される。したがって、NFET810からの漏れ電流として任意のNFET漏れ電流 $I_N$ がNFET漏れ周波数カウンタ712(1)に与えられる。NFET漏れ電流 $I_N$ は、NFET漏れ回路704(1)内のNFETリング発振器回路814内のNFET812(1)～812(Q)の一連のゲート(G)に結合される。NFET812(1)～812(Q)の各々は、発振ループ818内に構成されたそれぞれのバッファ回路816(1)～816(Q)のアクティブ化を制御するように構成される。したがって、NFET漏れ電流 $I_N$ の強度は、NFETリング発振器回路814内のNFET812(1)～812(Q)のターンオン強度を制御し、それによって、バッファ回路816(1)～816(Q)の速度または発振を制御してNFET漏れ電流を示す。たとえば、発振ループ818の各反復を使用して図7におけるNFET漏れ周波数カウント716などのNFET漏れ周波数カウントを増分させる4050

ことができる。

#### 【0028】

再び図7における漏れ認識アクティブ化制御回路700を参照すると、PFET漏れ電流をNFET漏れ電流と比較するように構成された比較器回路718が設けられる。この例では、比較器回路718は、PFET漏れ回路702およびNFET漏れ回路704から、それぞれ、PFET漏れ電流のNFE T漏れ電流に対する表示として、PFET漏れ周波数カウント714およびNFET漏れ周波数カウント716を受け取る。比較器回路718は複数の比較器720(1)～720(C)から構成される。各比較器720(1)～720(C)は、PFET漏れ電流および/またはNFET漏れ電流に基づいていくつかの比較を行い、それぞれのFET漏れ信号722(1)～722(C)を生成してPFET漏れ電流および/またはNFET漏れ電流の比を示すFET漏れ制御信号724を生成するように構成される。後述のように、複数の比較器720(1)～720(C)を設けることによって、比較器720(1)～720(C)の各々を、PFET漏れ電流および/またはNFET漏れ電流が低速漏れ電流(Slow Leakage Current)を示すか、公称(通常)漏れ電流(Nominal (Typical) Leakage Current)を示すか、それとも高速漏れ電流(Fast Leakage Current)を示すかを判定するように異なるように構成することができる。このようにして、FET漏れ信号722(1)～722(C)を組み合わせてFET漏れ制御信号724を形成し、相対的なPFET漏れ電流およびNFET漏れ電流ならびにPFETデバイスおよびNFETデバイスの速度に基づく図2における遅延キーパー回路232などの遅延キーパー回路のより厳密な制御を可能にすることができる。10

#### 【0029】

この点に関して、図7における漏れ認識アクティブ化制御回路700内の比較器回路718は、この例では6つの比較器720(1)～720(6)を含む。比較器720(3)は、PFET漏れ周波数カウント714をNFET漏れ周波数カウント716と比較してPFETがNFETよりも大きい漏れ電流を有するかどうかを示すように構成されたPFET公称漏れ比較器回路として構成される。PFETがNFETよりも大きい漏れ電流を有する場合、比較器720(3)は、そのような表示を有するFET漏れ信号722(3)を生成する。同様に、比較器720(4)は、NFET漏れ周波数カウント716をPFET漏れ周波数カウント714と比較してNFETがPFETよりも大きい漏れ電流を有するかどうかを示すように構成されたNFET公称漏れ比較器回路として構成される。NFETがPFETよりも大きい漏れ電流を有する場合、比較器720(4)は、そのような表示を有するFET漏れ信号722(4)を生成する。20

#### 【0030】

さらに、比較器720(1)は、PFET漏れ周波数カウント714を既定の低速漏れインジケータ726(または限界)と比較するように構成されたPFET低速漏れ比較器回路として構成される。比較器720(2)は、NFET漏れ周波数カウント716を既定の低速漏れインジケータ726(または限界)と比較するように構成されたNFET低速漏れ比較器回路として構成される。このようにして、比較器720(1)、720(2)はそれぞれ、PFETおよびNFETの判定された漏れ電流がそれぞれ低速デバイスを示すかどうかを示すFET漏れ信号722(1)、722(2)を生成することができる。さらに、比較器720(5)は、PFET漏れ周波数カウント714を既定の高速漏れインジケータ728(または限界)と比較するように構成されたPFET高速漏れ比較器回路として構成される。比較器720(6)は、NFET漏れ周波数カウント716を既定の高速漏れインジケータ728(または限界)と比較するように構成されたNFET高速漏れ比較器回路として構成される。このようにして、比較器720(5)、720(6)はそれぞれ、PFETおよびNFETの判定された漏れ電流がそれぞれ高速デバイスを示すかどうかを示すFET漏れ信号722(5)、722(6)を生成することができる。30

#### 【0031】

したがって、FET漏れ信号722(1)～722(6)によって、比較器回路718は、PFET漏れ電流をNFET漏れ電流に対して示し、ならびにPFETおよびNFETが低速切替え速度デバイスであるか、公称切替え速度デバイスであるか、それとも高速切替え速度デバイスであるかを示す。FET漏れ信号722(1)～722(6)はFET漏れ制御信号724を形成する。デコーダ回路730は、FET漏れ制御信号724を、以下に説明するようにこの例では8ビット(<7:0>)である、制御信号としてのFET漏れ制御ワード732に復号するように漏れ認識アクティブ化制御回路700内に4050

設けられる。FET漏れ制御ワード732は、上記で説明したように、パルス236の生成のタイミングおよび図2における動的読み取り回路214内の遅延キーパー回路232を制御するためにパルス発生器234に与えられてもよい。

#### 【 0 0 3 2 】

図9は、比較器回路718によって与えられるFET漏れ信号722(1)～722(6)に基づいて遅延キーパー回路232のアクティブ化タイミングを制御するために図7における漏れ認識アクティブ化制御回路700によって生成することができる例示的なFET漏れ制御ワードを示す論理テーブル900である。この例では、プロセス列902が、高速PFETデバイス、低速PFETデバイス、および公称PFETデバイスならびに高速NFETデバイス、低速NFETデバイス、および公称NFETデバイスの様々な可能な組合せを示す。Prog<0>-Prog<7>列904は、高速PFETデバイス、低速PFETデバイス、および公称PFETデバイスならびに高速NFETデバイス、低速NFETデバイス、および公称NFETデバイスの様々な可能な組合せに基づいてFET漏れ制御ワード732におけるビットの値を示す。パルス幅列906は、FET漏れ制御ワード732に応答してパルス発生器234によって生成されるパルス236のパルス幅設定を示す。たとえば、高速NFET漏れ電流(すなわち、既定の高速漏れインジケータを超える電流)および低速PFET漏れ電流(すなわち、既定の低速漏れインジケータよりも小さい電流)が、遅延キーパー回路232のアクティブ化タイミング制御に関するパルス236の「最小」パルス幅設定を示すように示される。低速NFET漏れ電流(すなわち、既定の低速漏れインジケータよりも小さい電流)および高速PFET漏れ電流(すなわち、既定の高速漏れインジケータを超える電流)が、遅延キーパー回路232のアクティブ化タイミング制御に関するパルス236の「最大」パルス幅設定を示すように示される。図10は、図7における比較器回路718のために、図9における論理テーブル900に示すように、デコーダ回路730によって生成されるFET漏れ制御ワード732のProg<0>-Prog<7>ビット用の例示的な式の図1000である。

10

20

#### 【 0 0 3 3 】

図11は、NFET漏れインジケータとPFET漏れインジケータとの比較に基づいて遅延キーパー回路232のアクティブ化タイミングを制御するために、漏れ認識アクティブ化制御回路700からFET漏れ制御ワード732を受け取るために図7におけるパルス発生器234として使用できる例示的なパルス発生器234(1)の回路図である。図11に示すように、パルス発生器234(1)はマルチプレクサ回路1100を含む。FET漏れ制御ワード732は、マルチプレクサ回路1100によって出力1102に与えられ、パルス発生器234によって使用される信号経路1104(0)～1104(7)を選択し、遅延キーパー回路232に与えるべきパルス236(1)を生成する。各信号経路1104(1)～1104(7)は、それぞれの信号経路1104(0)～1104(7)内に設けられたバッファ回路1106の数に基づいて受け取られた読み取りクロック信号(read\_clk)220を遅延させるように構成された異なる数のバッファ回路1106を含む。信号経路1104(0)は読み出しノード228に直接結合される。FET漏れ制御ワード732によって選択された信号経路1104(0)～1104(7)に従う遅延読み取りクロック信号(read\_clk)220Dが、ゲーティングされたANDゲート1108に与えられ、遅延されない読み取りクロック信号(read\_clk)220との論理積が計算され、遅延キーパー回路232のアクティブ化タイミングを制御するためのパルス236(1)が生成される。

30

#### 【 0 0 3 4 】

本明細書の態様については、プリチャージモードを使用し、次いで放電評価モードを使用する回路を参照して説明するが、プリディスチャージを使用し、次いで充電評価を使用する回路が本開示の範囲内であることに留意されたい。たとえば、一例として図2のメモリシステム200を参照すれば、当業者には、動的読み取り回路214の評価フェーズに関して、遅延キーパー回路232がNFETを使用し、読み取りポート回路216(1)がPFETを使用する場合、本明細書の概念をそのような回路に適用するにはどのように適応させればよいかが容易に理解されよう。この例では、パルス発生器234は、遅延キーパー回路232のアクティブ化および非アクティブ化を制御するために出力ノード237上でアクティブ低パルスを生成するように構成することができる。

40

#### 【 0 0 3 5 】

本明細書において開示する態様に従ってメモリビットセルにおいて読み取り動作を実行す

50

るための動的読み取り回路内の遅延キーパー回路と読み取りポート回路との間の競合を防止または軽減するための本明細書において開示する漏れ認識アクティブ化制御回路は、任意のプロセッサベースデバイスにおけるメモリ内に設けられてもよく、あるいはメモリに組み込まれてもよい。この例には、限定はしないが、セットトップボックス、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、モバイルフォン、セルラーフォン、スマートフォン、タブレット、ファブレット、サーバ、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、携帯情報端末(PDA)、モニタ、コンピュータモニタ、テレビ、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、ポータブルデジタルビデオプレーヤ、および自動車が含まれる。

10

#### 【0036】

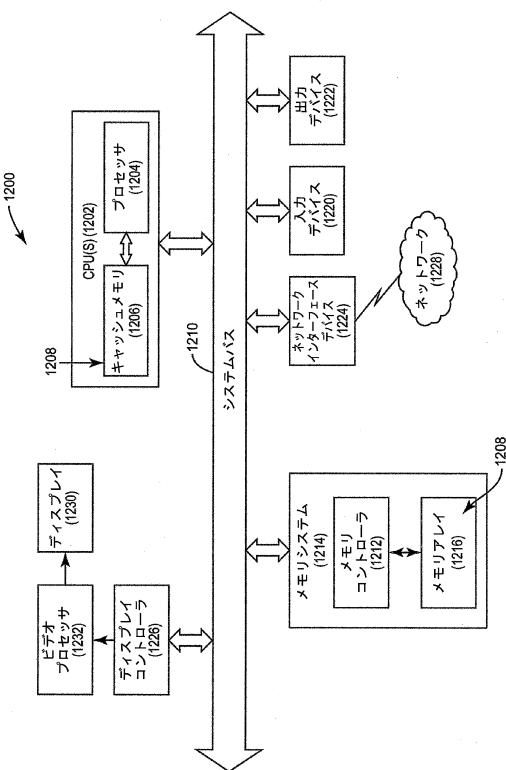

この点に関して、図12は、プロセッサベースシステム1200の一例を示す。プロセッサベースシステム1200の任意の構成要素または回路が、本明細書において開示する様に従つてメモリビットセルにおいて読み取り動作を実行するための動的読み取り回路内の遅延キーパー回路と読み取りポート回路との間の競合を防止または軽減するために漏れ認識アクティブ化制御回路を使用することができる。この例では、プロセッサベースシステム1200は、各々が1つまたは複数のプロセッサ1204を含む、1つまたは複数の中央処理ユニット(CPU)1202を含む。CPU1202は、一時的に記憶されたデータに迅速にアクセスするために、プロセッサ1204に結合されたキャッシュメモリ1206を有する場合がある。一例として、キャッシュメモリ1206は、それぞれ図2および図7における漏れ認識アクティブ化制御回路238および700を含む、本明細書において開示する任意の漏れ認識アクティブ化制御回路1208を使用することができる。

20

#### 【0037】

引き続き図12を参照すると、CPU1202は、システムバス1210に結合され、プロセッサベースシステム1200に含まれるマスターデバイスとスレーブデバイスとを相互結合することができる。よく知られているように、CPU1202は、システムバス1210を介してアドレス情報、制御情報、およびデータ情報を交換することによって、これらの他のデバイスと通信する。たとえば、CPU1202は、スレーブデバイスの一例として、メモリシステム1214内のメモリコントローラ1212にバストランザクション要求を伝達することができる。図12には示されていないが、複数のシステムバス1210を設けることができ、各システムバス1210は異なるファブリックを構成する。この例では、メモリコントローラ1212は、メモリシステム1214の中のメモリアレイ1216にメモリアクセス要求を提供するように構成される。一例として、メモリアレイ1216は、それぞれ図2および図7における漏れ認識アクティブ化制御回路238および700を含む、本明細書において開示する漏れ認識アクティブ化制御回路1208のうちの任意の漏れ認識アクティブ化制御回路1208を使用することができる。

30

#### 【0038】

他のデバイスをシステムバス1210に接続することができる。図12に示すように、これらのデバイスは、例として、メモリシステム1214、1つまたは複数の入力デバイス1220、1つまたは複数の出力デバイス1222、1つまたは複数のネットワークインターフェースデバイス1224、および1つまたは複数のディスプレイコントローラ1226を含むことができる。入力デバイス1220は、入力キー、スイッチ、音声プロセッサなどを含むが、これらに限定されない、任意のタイプの入力デバイスを含むことができる。出力デバイス1222は、限定はしないが、オーディオ、ビデオ、他の視覚インジケータなどを含む、任意のタイプの出力デバイスを含むことができる。ネットワークインターフェースデバイス1224は、ネットワーク1228との間のデータの交換を可能にするように構成された任意のデバイスであってよい。ネットワーク1228は、限定はしないが、有線ネットワークまたはワイヤレスネットワーク、プライベートネットワークまたは公衆ネットワーク、ローカルエリアネットワーク(LAN)、ワイヤレスローカルエリアネットワーク(WLAN)、ワイドエリアネットワーク(WAN)、BLUETOOTH(登録商標)ネットワーク、およびインターネットを含む、任意のタイプの

40

ネットワークであってもよい。ネットワークインターフェースデバイス1224は、必要に応じて、任意のタイプの通信プロトコルをサポートするように構成することができる。

#### 【 0 0 3 9 】

また、CPU1202は、1つまたは複数のディスプレイ1230に送信される情報を制御するために、システムバス1210を介してディスプレイコントローラ1226にアクセスするように構成される場合もある。ディスプレイコントローラ1226は、1つまたは複数のビデオプロセッサ1232を介して表示されるべき情報をディスプレイ1230に送信し、1つまたは複数のビデオプロセッサ1232は、表示されるべき情報をディスプレイ1230に適したフォーマットになるように処理する。ディスプレイ1230は、限定はしないが、陰極線管(CRT)、液晶ディスプレイ(LCD)、プラズマディスプレイなどを含む任意のタイプのディスプレイを含むことができる。

10

#### 【 0 0 4 0 】

本開示におけるPFETおよびNFETの使用に、金属酸化物半導体(MOS)であるPMOSFETおよびNMOSFETを含めることでできることに留意されたい。本明細書において説明するPFETおよびNFETは、金属以外の他の種類の酸化物層を含むことができる。

#### 【 0 0 4 1 】

本明細書で開示する態様に関して説明した様々な例示的な論理ブロック、モジュール、回路、およびアルゴリズムが、電子ハードウェア、メモリの中もしくは別のコンピュータ可読媒体の中に記憶されるとともにプロセッサもしくは他の処理デバイスによって実行される命令、または両方の組合せとして実装されてもよいことを、当業者はさらに諒解されよう。本明細書で説明するマスターデバイスおよびスレーブデバイスは、例として、任意の回路、ハードウェア構成要素、集積回路(IC)、またはICチップにおいて利用されてもよい。本明細書で開示するメモリは、任意のタイプおよびサイズのメモリであってもよく、任意のタイプの所望の情報を記憶するように構成されてもよい。この互換性を明確に示すために、様々な例示的な構成要素、ブロック、モジュール、回路、およびステップについて、概してそれらの機能に関して上記において説明した。そのような機能性がどのように実装されるのかは、特定の適用例、設計選択、および/またはシステム全体に課される設計制約によって決まる。当業者は、説明された機能性を特定の適用例ごとに様々な方法で実装してもよいが、そのような実施態様の決定は、本開示の範囲からの逸脱を引き起こすものと解釈されるべきではない。

20

#### 【 0 0 4 2 】

本明細書で開示する態様に関連して説明した様々な例示的な論理ブロック、モジュール、および回路は、プロセッサ、デジタル信号プロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)もしくは他のプログラマブル論理デバイス、個別ゲートもしくはトランジスタ論理、個別ハードウェア構成要素、または本明細書で説明する機能を実行するように設計されたこれらの任意の組合せを用いて実装または実行されてもよい。プロセッサは、マイクロプロセッサであってよいが、代替として、プロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、または状態機械であってもよい。プロセッサはまた、コンピューティングデバイスの組合せ、たとえば、DSPおよびマイクロプロセッサの組合せ、複数のマイクロプロセッサ、DSPコアと連携した1つもしくは複数のマイクロプロセッサ、または任意の他のそのような構成として実装されてもよい。

30

#### 【 0 0 4 3 】

本明細書の例示的な態様のいずれかにおいて説明する動作ステップが、例示および説明のために記載されていることにも留意されたい。説明する動作は、図示のシーケンス以外の数多くの異なるシーケンスにおいて実行される場合がある。さらに、単一の動作ステップにおいて説明する動作は、実際にはいくつかの異なるステップにおいて実行される場合がある。さらに、例示的な態様で説明した1つまたは複数の動作ステップは、組み合わせられてよい。フローチャート図に示された動作ステップが、当業者には容易に明らかであるような数多くの異なる変更を受けてよいことを理解されたい。当業者であれば、様々な

40

50

異なる技術および技法のいずれかを使用して情報および信号が表され得ることも理解するであろう。たとえば、上記の説明全体にわたって参照され得るデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場もしくは磁気粒子、光場もしくは光学粒子、またはそれらの任意の組合せによって表現されてよい。

#### 【0044】

本開示のこれまでの説明は、任意の当業者が本開示を作製または使用できるようにするために提供される。本開示の様々な変更が当業者に容易に明らかになり、本明細書で定義する一般原理は、本開示の趣旨または範囲から逸脱することなく他の変形形態に適用されてもよい。したがって、本開示は、本明細書で説明した例および設計に限定されるものではなく、本明細書で開示する原理および新規の特徴と一致する最も広い範囲を与えられるべきである。

#### 【符号の説明】

#### 【0045】

|                 |                      |    |

|-----------------|----------------------|----|

| 100             | メモリシステム              |    |

| 102(1) ~ 102(N) | メモリビットセル             |    |

| 104             | メモリビットセル列            |    |

| 106(1), 106(2)  | 交差結合インバータ            |    |

| 108(1), 108(2)  | アクセストランジスタ           |    |

| 110(1)          | プルダウンNFET            |    |

| 112             | 動的読み取り回路             | 20 |

| 116             | P型電界効果トランジスタPFET)    |    |

| 118             | 読み取りクロック信号(read_clk) |    |

| 120             | 動的ノード                |    |

| 122C            | 補ノード                 |    |

| 124             | 読み出しノード              |    |

| 126             | インバータ                |    |

| 128             | キーパー回路               |    |

| 200             | メモリシステム              |    |

| 202             | プロセッサベースシステム         |    |

| 204             | システムオンチップ(SoC)       | 30 |

| 204(1) ~ 204(N) | メモリビットセル             |    |

| 206             | メモリビットセル列            |    |

| 208(1), 208(2)  | 交差結合インバータ            |    |

| 210(1) ~ 210(N) | 記憶ユニット               |    |

| 212(1), 212(2)  | アクセストランジスタ           |    |

| 214             | 動的読み取り回路             |    |

| 216(1)          | 読み取りポート回路            |    |

| 218(1)          | プルダウンNFET            |    |

| 218(2)          | 読み取りポートNFET          |    |

| 220             | 読み取りクロック信号(read_clk) | 40 |

| 222C            | 補ノード                 |    |

| 224             | 動的ノード                |    |

| 226             | ブリチャージPFET           |    |

| 228             | 読み出しノード              |    |

| 230             | インバータ                |    |

| 232             | 遅延キーパー回路             |    |

| 233             | PFET                 |    |

| 234             | パルス発生器               |    |

| 236             | パルス                  |    |

| 237             | 出力ノード                | 50 |

|                   |                    |    |

|-------------------|--------------------|----|

| 238               | 漏れ認識アクティプ化制御回路     |    |

| 240               | 制御信号               |    |

| 500               | PFET漏れ回路           |    |

| 502               | PFET漏れインジケータ       |    |

| 504               | NFET漏れ回路           |    |

| 506               | NFET漏れインジケータ       |    |

| 508               | 比較器回路              |    |

| 510               | FET漏れ信号            |    |

| 512               | 制御信号発生器            |    |

| 700               | 漏れ認識アクティプ化制御回路     | 10 |

| 702、702(1)        | PFET漏れ回路           |    |

| 704               | NFET漏れ回路           |    |

| 706、706(1)        | PFET漏れセンサー         |    |

| 708               | NFET漏れセンサー         |    |

| 710、710(1)        | PFET漏れ周波数カウンタ      |    |

| 712               | NFET漏れ周波数カウンタ      |    |

| 714               | PFET漏れ周波数カウント      |    |

| 716               | NFET漏れ周波数カウント      |    |

| 718               | 比較器回路              |    |

| 720(1) ~ 720(C)   | 比較器                | 20 |

| 722(1) ~ 722(C)   | FET漏れ信号            |    |

| 724               | FET漏れ制御信号          |    |

| 726               | 既定の低速漏れインジケータ      |    |

| 728               | 既定の高速漏れインジケータ      |    |

| 730               | デコーダ回路             |    |

| 732               | FET漏れ制御ワード         |    |

| 800               | PFET               |    |

| 802(1) ~ 802(P)   | NFET               |    |

| 804               | PFETリング発振器回路       |    |

| 806(1) ~ 806(P)   | バッファ回路             | 30 |

| 808               | 発振ループ              |    |

| 810               | NFET               |    |

| 811               | PFET電流ミラー          |    |

| 812(1) ~ 812(Q)   | NFET               |    |

| 814               | NFETリング発振器回路       |    |

| 816(1) ~ 816(Q)   | バッファ回路             |    |

| 818               | 発振ループ              |    |

| 900               | 論理テーブル             |    |

| 902               | プロセス列              |    |

| 904               | Prog<0> - Prog<7>列 | 40 |

| 906               | パルス幅列              |    |

| 1100              | マルチプレクサ回路          |    |

| 1102              | 出力                 |    |

| 1104(0) ~ 1104(7) | 信号経路               |    |

| 1106              | バッファ回路             |    |

| 1108              | ANDゲート             |    |

| 1200              | プロセッサベースシステム       |    |

| 1202              | 中央処理ユニット(CPU)      |    |

| 1204              | プロセッサ              |    |

| 1206              | キャッシュメモリ           | 50 |

- 1208 漏れ認識アクティブ化制御回路

1210 システムバス

1212 メモリコントローラ

1214 メモリシステム

1216 メモリアレイ

1220 入力デバイス

1222 出力デバイス

1224 ネットワークインターフェースデバイス

1226 ディスプレイコントローラ

1228 ネットワーク

1230 ディスプレイ

1232 ビデオプロセッサ

WL(1) ~ WL(N) ワード線

10

【図1】

【図2】

【図3A】

【図4】

【図3B】

【図5】

【図6】

【 义 7 】

【図 8 A】

【図 8 B】

【 四 9 】

| プロセス (902) |         | PROG<br><>    |

|------------|---------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|---------------|

| 従来のキーバー回路  |         | 1          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | バルス幅<br>(906) |

| 高速N        | 低速P     | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | バルスなし         |

| 高速N        | 低速<1>通常 | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 2番目に小さい       |

| 通常<1>高速    | 0       | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 3番目に小さい       |

| 高速N        | 高速P     | 0          | 0          | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 4番目に小さい       |

| 通常<1>高速    | 低速P     | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 2番目に小さい       |

| 通常<1>高速    | 低速<1>通常 | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 3番目に小さい       |

| 通常<1>高速    | 通常<1>高速 | 0          | 0          | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 4番目に小さい       |

| 通常<1>高速    | 高速P     | 0          | 0          | 0          | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 0          | 5番目に小さい       |

| 通常<1>高速    | 低速P     | 0          | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 3番目に小さい       |

| 低速<1>通常    | 低速<1>通常 | 0          | 0          | 0          | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 0          | 4番目に小さい       |

| 低速<1>通常    | 通常<1>高速 | 0          | 0          | 0          | 0          | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 5番目に小さい       |

| 低速<1>通常    | 高速P     | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 6番目に小さい       |

| 低速N        | 通常<1>高速 | 0          | 0          | 0          | 0          | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 最大            |

| 低速N        | 高速P     | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 1          | 0          | 0          | 0          |               |

【図 1 0】

FIG. 10

【図 1 1】

【図 1 2】

---

フロントページの続き

(72)発明者 ホアン・フウ・グエン

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 キース・アラン・ボウマン

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

審査官 堀田 和義

(56)参考文献 米国特許出願公開第2014/0071776(US,A1)

米国特許第8482316(US,B1)

国際公開第2015/099748(WO,A1)

米国特許出願公開第2007/0146013(US,A1)

米国特許出願公開第2013/0106524(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11/419

G 11 C 7/22

G 11 C 11/412