(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4416410号

(P4416410)

(45) 発行日 平成22年2月17日(2010.2.17)

(24) 登録日 平成21年12月4日(2009.12.4)

|                     |                |

|---------------------|----------------|

| (51) Int.Cl.        | F 1            |

| HO4N 1/21 (2006.01) | HO4N 1/21      |

| B41J 5/30 (2006.01) | B41J 5/30 Z    |

| G06T 1/20 (2006.01) | G06T 1/20 B    |

| G06T 1/60 (2006.01) | G06T 1/60 450F |

請求項の数 1 (全 22 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2003-8574 (P2003-8574)      |

| (22) 出願日  | 平成15年1月16日 (2003.1.16)        |

| (65) 公開番号 | 特開2004-222069 (P2004-222069A) |

| (43) 公開日  | 平成16年8月5日 (2004.8.5)          |

| 審査請求日     | 平成18年1月13日 (2006.1.13)        |

| 審判番号      | 不服2008-9499 (P2008-9499/J1)   |

| 審判請求日     | 平成20年4月16日 (2008.4.16)        |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (74) 代理人  | 100130409<br>弁理士 下山 治                      |

| (74) 代理人  | 100134175<br>弁理士 永川 行光                     |

最終頁に続く

(54) 【発明の名称】 画像処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

画像データを格納する格納手段と、

前記格納手段から前記画像データを読み出して、画像処理を行い、処理後の画像データを前記格納手段に書き込む一連の処理を行う複数の第1の画像処理手段と、

前記複数の第1の画像処理手段のうち、指定された第1の画像処理手段を起動させる起動制御手段と、

起動した前記第1の画像処理手段による前記格納手段へのアクセスを調停するアクセス制御手段とを備える画像処理装置であって、

それぞれの前記第1の画像処理手段が、

前記格納手段より前記画像データを読み出すためのアドレスを生成する第1のアドレス生成手段と、

前記格納手段から前記アドレスに対応させて読み出された前記画像データを格納する第1のデータ保持手段と、

前記第1のデータ保持手段に保持された前記画像データを順次処理する複数の第2の画像処理手段と、

最終段の前記第2の画像処理手段で処理された出力データを格納する第2のデータ保持手段と、

前記第2のデータ保持手段の出力データを前記格納手段に書き込むためのアドレスを生成する第2のアドレス生成手段と、

10

20

前記第1のデータ保持手段に画像データが格納可能、又は前記第2のデータ保持手段から出力データが出力可能な場合、前記アクセス制御手段に対して前記格納手段へのアクセスを要求する第2のアクセス制御手段とを備え、

前記複数の第2の画像処理手段は、直列に接続され、該複数の第2の画像処理手段間ににおいて、各第2の画像処理手段で処理されるデータが伝送可能か否かを示す有効信号と、該データの受け取りが可能か否かを示す保持要求信号とによって前記画像データを順次処理し、前記画像データの画像処理の処理内容に基づいて、前記第2の画像処理手段の夫々にバイパスモードを設定可能であることを特徴とする画像処理装置。

【発明の詳細な説明】

【0001】

10

【発明の属する技術分野】

本発明は、メモリを介したデータの受け渡しによって画像処理を行う画像処理装置、画像処理方法、プログラム及び記憶媒体に関する。

【0002】

【従来の技術】

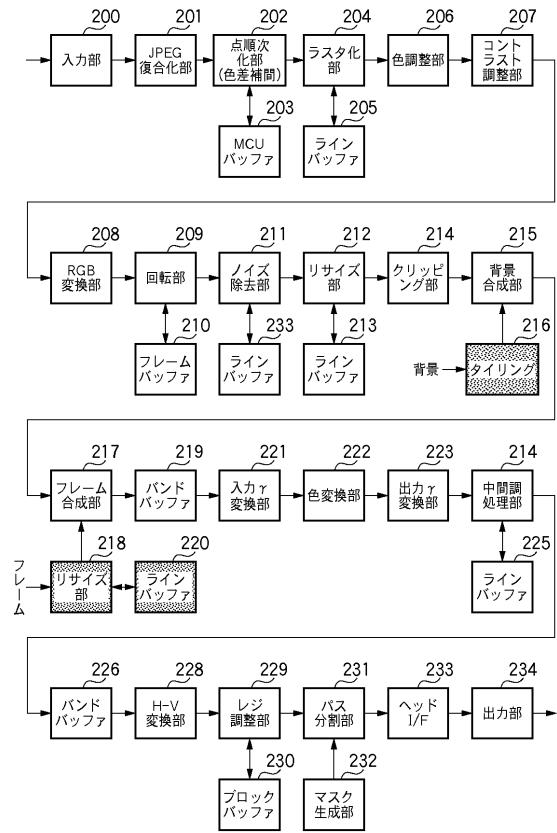

デジタルカメラ等を用いて撮影された画像データをプリンタで出力する際に良好な画像出力を得るためにには、通常、各種の画像処理が必要である。図14は、デジタルカメラを用いて撮影された画像データをプリンタで出力する際に画像処理を行う従来の画像処理部の構成を示すブロック図である。

【0003】

20

まず、入力部200より入力されたJPEG画像データ（デジタルカメラで撮影された撮影データ）をJPEG復号化部201において解凍する。解凍されたデータはYCrCbのブロック順に出力されるので、MCUバッファ203に一旦格納し、点順次化部202においてYCrCbの点順次データとして読み出す。この時、色差データCrCbがサブサンプルされている場合は、読み出し時に補間して出力する。点順次化された画像データはMCU順に出力されるので、MCUラインバッファ205に一旦格納し、ラスタ化部204によってYCrCbのラスターデータとして読み出す。ラスタ化された画像データは、色調整部206によりホワイトバランス等の色調整や、コントラスト調整部207によりコントラストが調整され、RGB変換部208においてRGBデータに変換される。

【0004】

30

そして、印刷の向きと画像の向きが異なる場合は、フレームバッファ210を用いて回転部209によって向きが合わされる。また、ノイズが目立つ画像においては、ノイズ除去部211においてノイズの低減処理が施される。この時、周囲の画素データを参照するためラインバッファ233が使用される。

【0005】

次に、リサイズ部212において、印刷解像度に合わせたサイズにリサイズされる。この時、周囲の画素データを参照するためラインバッファ213が使用される。リサイズされた画像データは、クリッピング部214において出力不要な部分を除去（トリミング）される。また、ページメモリの容量削減のため、ページの一部をバンド上に順次切り出して処理するバンド処理における有効バンド領域のデータが抽出される。

40

【0006】

クリッピングされた画像データは、背景データが背景合成部215において合成され、フレームデータがフレーム合成部217において合成され、バンドバッファ219に格納される。ここで、背景データとして、小さな画像をタイル状に並べた画像を使用する場合は、タイリング部216を用いて、背景データを横及び縦方向に繰り返して読み出して使用する。また、各種の用紙サイズ及びレイアウトに対応させるためにフレームデータのリサイズが必要な場合は、リサイズ部218によってフレームデータをリサイズしてから合成する。この時、周囲の画素データを参照するためラインバッファ220が使用される。

【0007】

バンドバッファ219に格納された印刷画像データは、入力変換部221において濃度

50

リニアな信号に変換され、色変換部 222においてプリンタの色材データ（出力デバイスカラー）に変換される。さらに、出力変換部 223において出力補正され、中間調処理部 224においてビットマップデータ（ドットパターン）に変換される。ここで、画像データの中間調処理に誤差拡散法を用いた場合、量子化誤差を周囲の画素に拡散させるためにラインバッファ 225が用いられる。そして、ビットマップデータはバンドバッファ 226に一旦格納される。

【0008】

次に、不図示のプリントエンジンが起動されると、H-V変換部 228はプリントエンジンの同期信号に合わせて、ビットマップデータをヘッドのドット構成要素（例えば、インクジェット方式においてはノズル）の並びに合わせてバンドバッファ 226より読み出し、ロックバッファ 230に格納する。通常、ビットマップデータは、ヘッドのスキャン方向の複数ドットを1ワードとしてバンドバッファ 226に格納されるので、ロックバッファ 230を用いて、ヘッドのドット構成要素列（ノズル列）方向のデータを抽出するようしている。また、レジ調整部 229によって、同時に読み出すビット位置をヘッドのドット構成要素列（ノズル列）毎にずらすことによってレジ調整を行う。

10

【0009】

さらに、プリント出力時のスジやムラを低減するため、複数回のパス（ヘッドのスキャン）に分割してプリント画像を形成する場合は、マスク生成部 232によって生成されたマスク信号に従って、パス分割部 231においてビットマップデータの出力ドットを複数のパスに分散させる。分割されたドットデータは、ヘッドインターフェース部 233においてヘッドへの伝送フォーマットに変換され、出力部 234よりヘッドへ出力される。

20

【0010】

尚、上述したような複雑な処理を行う場合、開発やメンテナンス性を容易にするため、上記各種の処理をモジュール化している。例えば、各画像処理をモジュール化し、各モジュール間にバッファメモリ設けて接続することにより、容易にバージョンアップを図ることができる画像処理方法が開示されている（例えば、特許文献 1 参照）。

【0011】

【特許文献 1】

特開平9-116660号公報

【0012】

30

【発明が解決しようとする課題】

しかしながら、上記特許文献 1 に開示された方法では、画像処理モジュールの数に比例して多数のバッファメモリが必要になるという欠点があった。また、任意の画像サイズに対応させるには、巨大なローカルメモリが必要になるという欠点もあった。例えば、図 14 に示したラインバッファ 205、213 及びフレームバッファ 210 は入力画像サイズに依存しており、バンドバッファ 219、226 及びラインバッファ 225 は出力サイズ（例えば、用紙サイズ、出力解像度及びバンドの高さ）に依存している。従って、これらのバッファを各種サイズの画像データに対応させるためには、想定する最大サイズのバッファメモリ容量を見積もる必要がある。

【0013】

40

一方、出力画像によって、必要な画像処理内容が異なってくる。例えば、印刷方向と入力画像の向きが一致している場合は、回転処理は不要である。また、背景、フレーム等が必要な場合は、合成処理は不要である。このような場合、従来は 0° の回転を行う、ブレンドのための値を不透明に設定して合成する等、結果的に何もしないためのパラメータ設定を行い、無駄な処理を施していた。

【0014】

また、上記特許文献 1 に開示された方法では、ハードウェアが完成してから一部の機能を置き換えることは不可能であった。例えば、RGB変換モジュールに仕様変更が発生した場合、上記一連の処理モジュールをハードウェア化した場合、RGB変換モジュールだけ別処理（ソフトウェア処理）で置き換えるようなことは不可能であったので、RGB変換

50

モジュールを含む一連の処理モジュールが無駄になってしまっていた。特に、一部のモジュールに致命的な欠陥が生じた場合は、関連する全ての処理モジュールが使用不可になっていた。

【0015】

本発明は、このような事情を考慮してなされたものであり、入力画像に対する各種画像処理を複数の処理ブロックに分割して処理ブロック単位にモジュール化し、各モジュール間のデータの受け渡しを、共有メモリを通じて行う構成とすることで、各画像処理モジュールのI/Fを汎用化し、画像処理モジュール単位の追加変更を容易にするだけでなく、無駄なバッファやメモリ及び処理の削減を図ることができる画像処理装置、画像処理方法、プログラム及び記憶媒体を提供することを目的とする。

10

【0016】

【課題を解決するための手段】

上記課題を解決するため、本発明の画像処理装置は、

画像データを格納する格納手段と、

前記格納手段から前記画像データを読み出して、画像処理を行い、処理後の画像データを前記格納手段に書き込む一連の処理を行う複数の第1の画像処理手段と、

前記複数の第1の画像処理手段のうち、指定された第1の画像処理手段を起動させる起動制御手段と、

起動した前記第1の画像処理手段による前記格納手段へのアクセスを調停するアクセス制御手段とを備える画像処理装置であって、

それぞれの前記第1の画像処理手段が、

前記格納手段より前記画像データを読み出すためのアドレスを生成する第1のアドレス生成手段と、

前記格納手段から前記アドレスに対応させて読み出された前記画像データを格納する第1のデータ保持手段と、

前記第1のデータ保持手段に保持された前記画像データを順次処理する複数の第2の画像処理手段と、

最終段の前記第2の画像処理手段で処理された出力データを格納する第2のデータ保持手段と、

前記第2のデータ保持手段の出力データを前記格納手段に書き込むためのアドレスを生成する第2のアドレス生成手段と、

前記第1のデータ保持手段に画像データが格納可能、又は前記第2のデータ保持手段から出力データが出力可能な場合、前記アクセス制御手段に対して前記格納手段へのアクセスを要求する第2のアクセス制御手段とを備え、

前記複数の第2の画像処理手段は、直列に接続され、該複数の第2の画像処理手段間ににおいて、各第2の画像処理手段で処理されるデータが伝送可能か否かを示す有効信号と、該データの受け取りが可能か否かを示す保持要求信号とによって前記画像データを順次処理し、前記画像データの画像処理の処理内容に基づいて、前記第2の画像処理手段の夫々にバイパスモードを設定可能であることを特徴とする。

20

【0017】

さらに、本発明による画像処理装置は、画像サイズに依存するバッファを前記格納手段上に設けることを特徴とする。

【0018】

【発明の実施の形態】

以下、本願発明の一実施形態について示す。もちろん以下の実施形態は、本願発明の技術分野における当業者による実施を容易にするために開示を提供するものであり、特許請求の範囲によって確定される本願発明の技術的範囲に含まれるほんの一部の実施形態にすぎない。従って、本願明細書に直接的に記載されていない実施形態であっても、技術思想が共通する限り本願発明の技術的範囲に包含されることは当業者にとって自明であろう。

【0019】

40

50

尚、以下には便宜上複数の実施形態を記載するが、これらは個別に発明として成立するだけでなく、もちろん、複数の実施形態を適宜組み合わせることでも発明が成立することは、当業者であれば容易に理解できよう。

【0020】

<第1の実施形態>

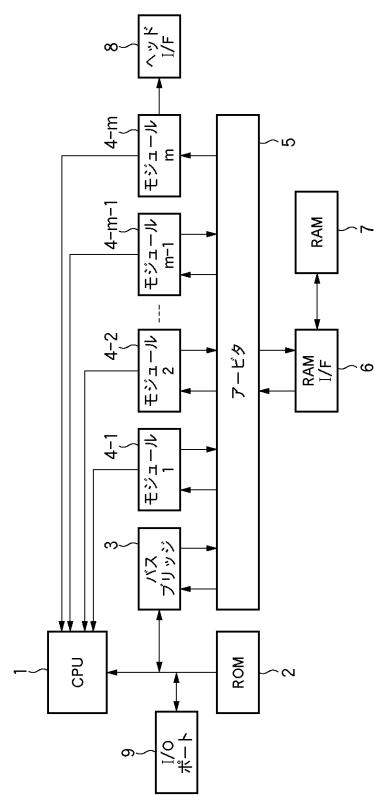

以下、図面を参照して、本発明の第1の実施形態について詳細に説明する。図1は、本発明の第1の実施形態に係る画像処理装置の一構成例を示すブロック図である。

【0021】

図1において、1は画像処理装置を制御するCPU、2はプログラム等を格納するROM、3はバスブリッジ、4はm個（但し、mは1以上の整数とする。）の画像処理モジュール（プロセッサ）、5はRAM7へのアクセスを調停するアービタ、6はRAMインターフェース部（I/F）、7はRAM、8はヘッドインターフェース（I/F）、9はI/Oポートである。尚、本実施形態においては上記RAM7は、CPU1、各画像処理モジュール4-1～4-mによって共有されているが、CPU1は別のRAMを持つような構成であっても良い。

10

【0022】

次に、上述した構成を有する画像処理装置の処理動作について説明する。

【0023】

CPU1は、ROM2に格納されているプログラムに従って、I/Oポート9より処理すべき画像データを受け取り、バスブリッジ3、アービタ5、RAMインターフェース部6を経てRAM7へ格納する。次に、CPUは画像処理モジュール4-1のコンフィギュレーションレジスタ（Configuration register）を設定し、画像処理モジュール4-1を動作させる。

20

【0024】

画像処理モジュール4-1は所定の処理を実行し、上記コンフィギュレーションレジスタにて設定された処理すべきデータの読み出しが終了するか、上記コンフィギュレーションレジスタにて設定された処理したデータの書き込みが終了すると割り込みを発生し、CPU1へ通知する。CPU1は、割り込みを受付けると、割り込み要因を解析し、上記画像処理モジュール4-1の処理すべきデータの読み出し終了の場合は、次の処理すべきデータの設定を行い、画像処理モジュール4-1の処理を続行させる。上記画像処理モジュール4-1の処理したデータの書き込み終了の場合は、次の処理データの格納先の設定を行い、画像処理モジュール4-1の処理を続行させると共に、次の画像処理モジュール4-2のコンフィギュレーションレジスタを設定し、画像処理モジュール4-2を動作させる。

30

【0025】

そして、画像処理モジュール4-2は所定の処理を実行し、上記コンフィギュレーションレジスタにて設定された処理すべきデータの読み出しが終了するか、上記コンフィギュレーションレジスタにて設定された処理したデータの書き込みが終了すると割り込みを発生し、CPU1へ通知する。CPU1は、割り込みを受け付けると、割り込み要因を解析し、上記画像処理モジュール4-2の処理すべきデータの読み出し終了の場合は、次の処理すべきデータの設定を行い、画像処理モジュール4-2の処理を続行させる。一方、上記画像処理モジュール4-2の処理したデータの書き込み終了の場合は、次の処理データの格納先設定を行い、画像処理モジュール4-2の処理を続行させると共に次の画像処理モジュール4-3のコンフィギュレーションレジスタを設定し、画像処理モジュール4-3を動作させる。

40

【0026】

上述したように、本画像処理装置では、前の画像処理モジュールでの処理が終わった直後に次の画像処理モジュールを起動し、処理データを次々と画像処理モジュールに受け渡しすることで、画像処理モジュール単位のパイプラインを構成することができる。

【0027】

50

そして、画像処理モジュール4-m-1までの処理が進み、所定以上のビットマップデータが生成されると、図示しないプリントエンジンが起動され、プリントエンジンの同期信号に合わせて画像処理モジュール4-mの処理が開始され、ヘッドI/F8を経てビットマップデータをプリントする。

【0028】

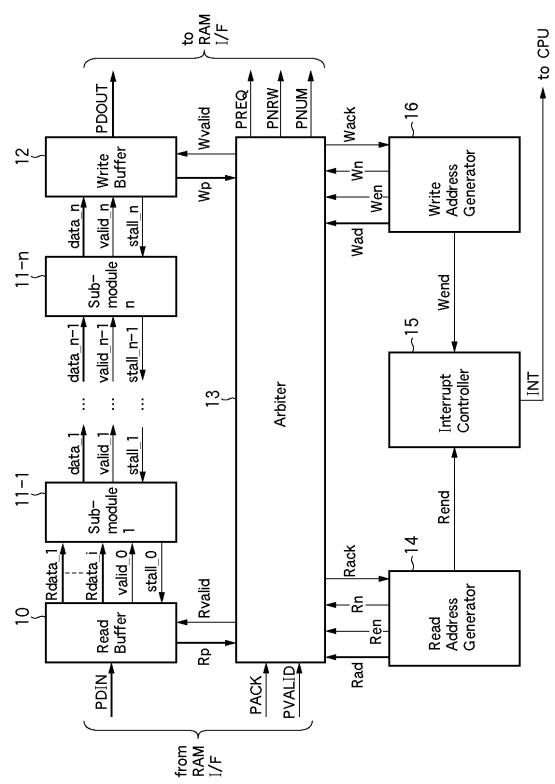

図2は、本発明の第1の実施形態に係る画像処理装置のモジュール4-1~4-m(以下、「画像処理モジュール4」と称す。)の詳細な内部構成を説明するためのブロック図である。図2において、7はリードバッファ(Read Buffer)、11-1~11-n(但し、nは1以上の整数とする。)はサブモジュール(Sub-module)、12はライトバッファ(Write Buffer)、13はアービタ(Arbitrer)、14はリードアドレス生成部(Read Address Generator)、15は割り込み制御部(Interrupt Controller)、16はライトアドレス生成部(Write Address Generator)である。

10

【0029】

CPU1は、画像処理モジュール4のコンフィギュレーションレジスタの設定により、リードアドレス生成部14にリード開始アドレスとリード終了アドレスを設定し、リードイネーブル(read enable)信号Renをセットする。また、ライトアドレス生成部16にライト開始アドレスとライト終了アドレスを設定し、ライトイネーブル(write enable)信号Wenをセットする。

【0030】

画像処理モジュール4におけるアービタ13は、リードバッファ10のバッファの空き容量Rp及びリードアドレス生成部14のイネーブル信号Renを検出し、リードアドレスが有効(Ren=1)であって、リードバッファ10にデータが格納可能(Rp=Rn)であれば、アービタ5へリードリクエスト(PREQ=1、PNRW=0、PNUM=Rn、PADD=Rad)を発行する。

20

【0031】

一方、ライトバッファ12のデータ蓄積数Wpが所定のワード数以上(Wp>Wn)になると、アービタ13はライトアドレス生成部16のイネーブル信号Wenを検出し、ライトアドレスが有効(Wen=1)であって、ライトバッファ12よりデータが出力可能(Wp>Wn)であれば、アービタ5へライトリクエスト(PREQ=1、PNRW=1、PNUM=Wnum、PADD=Wad)を発行する。

30

【0032】

そして、画像処理装置におけるアービタ5は、画像処理モジュール4からのリクエスト信号PREQを受け取ると、PNRWでリード/ライトの判別を行い、PNUMでワード数を、PADDでアドレスを検知する。ここで、CPU1及び他の画像処理モジュールからのリクエストがなければ、アービタ5は、RAMインターフェース部6を通じてRAM7の該当データのアクセスを開始する。また、リクエストが受け付けられると、アービタ5は受領信号PACKをリクエスト元の画像処理モジュールに返す。一方、CPU1及び他のモジュールからのリクエストがある場合は、優先順位に従ってリクエストを受け付ける。

【0033】

アービタ13は、アービタ5から受領信号PACKを受け取ると、リードリクエストの場合は受領信号Rackをリクエスト元のリードアドレス生成部14に返す。リードアドレス生成部14は、上記受領信号Rackを受け取ると次のアドレスを生成する。尚、リクエストしたアドレスが前記リード終了アドレスの場合は、リードイネーブル信号Renをリセットし、リード終了信号Renを割り込み制御部15に出力する。

40

【0034】

一方、アービタ13は、ライトリクエストの場合は受領信号Wackをリクエスト元のライトアドレス生成部16に返す。ライトアドレス生成部16は、上記受領信号Wackを受け取ると次のアドレスを生成する。尚、リクエストしたアドレスが前記ライト終了アドレスの場合は、ライトイネーブル信号Wenをリセットし、ライト終了信号Wendを割り込み制御部15に出力する。

50

## 【0035】

割り込み制御部15は、前記コンフィギュレーションレジスタによってリード終了割り込みマスク及びライト終了割り込みマスクの設定が可能になっている。そして、割り込み制御部15は、各割り込みマスクの設定が割り込みイネーブルとなっている場合は、上記リード終了信号Rendまたはライト終了信号Wendによって割り込み信号INTを生成し、CPU1へ通知する。CPU1は、上記割り込みを受け付けると、割り込み制御部15のステータスを読み取り、割り込み要因がリード終了の場合は、上記リード終了割り込みマスクをリセットして割り込みを解除する。さらに処理を続行する場合は、リード開始アドレスとリード終了アドレスの再設定、リードイネーブル信号のセット等の処置を行った後、上記リード終了割り込みマスクをセットする。

10

## 【0036】

同様に、割り込み要因がライト終了の場合、CPU1は、上記ライト終了割り込みマスクをリセットして割り込みを解除する。さらに処理を続行する場合、CPU1は、ライト開始アドレスとライト終了アドレスの再設定、ライトイネーブル信号のセット等の処置を行った後、上記ライト終了割り込みマスクをセットする。

## 【0037】

次に、RAM7よりデータが読み出されるとアービタ5はRAMデータ有効信号PVAILIDをリクエスト元のモジュールに返す。リクエスト元のモジュールでは、アービタ13よりリードバッファ10へデータ有効信号Rvalidを返す。リードバッファ10はデータ有効信号Rvalidがセットされている期間、RAMデータ出力信号PDIN上のデータを格納する。この操作により、RAM7のデータがリードバッファ10へ格納される。

20

## 【0038】

一方、RAM7にデータを書き込む場合は、RAM7の書き込みタイミングに合わせてアービタ5はRAMデータ有効信号PVALIDをリクエスト元のモジュールに返す。リクエスト元のモジュールでは、アービタ13よりライトバッファ12へデータ有効信号Wvalidを返す。ライトバッファ12はデータ有効信号Wvalidがセットされている期間、RAMデータ入力信号PDOUIT上に書き込むデータを出力する。この操作により、ライトバッファ12のデータがRAM7へ格納される。

## 【0039】

30

リードバッファ10は、サブモジュール11-1の処理に必要なデータが揃った時に有効信号valid\_0をセットし、サブモジュール11-1の処理に必要なデータが揃っていない場合は有効信号valid\_0をリセットする。また、サブモジュール11-1からの保持要求信号stall\_0がセットされていなければ、リードバッファ10は格納されたデータをクロックに同期して出力する。サブモジュール11-1からの保持要求信号stall\_0がセットされている場合は、データを更新しない。そして、サブモジュール11-1は、上記有効信号valid\_0がセットされているデータのみを受け取る。また、データの受け取りが不可能の場合は、保持要求信号stall\_0をセットし、リードバッファ7の出力をホールドする。

## 【0040】

40

尚、サブモジュール11-1は、入力データの並び替えが不要な場合は、上記リードバッファ10はFIFOでよい。同様に、出力データの並び替えが不要な場合は、上記ライトバッファ12はFIFOでよい。

## 【0041】

図2に示すように、本実施形態では、画像処理モジュール4の内部は1つ以上の画像処理サブモジュール11-1～11-nによって構成されており、各サブモジュール間では、上記と同様の動作（すなわち、有効信号validと保持要求信号stallによるハンドシェーク）によってデータの受け渡しが行われる。

## 【0042】

すなわち、本実施形態に係る画像処理装置は、画像データを格納する格納手段（例えば、

50

R A M 7 ) と、格納手段から画像データを読み出して、所定の画像処理を行い、処理後の画像データを格納手段に書き込む一連の処理を行う複数の画像処理手段( 例えば、画像処理モジュール 4 - 1 ~ 4 - m ) と、複数の画像処理手段のうち、所定の画像処理手段を起動させる起動制御手段( 例えば、C P U 1 ) と、起動した所定の画像処理手段による格納手段へのアクセスを制御するアクセス制御手段( 例えば、アービタ 5 ) とを備える画像処理装置であって、それぞれの画像処理手段( 画像処理モジュール 4 ) が、格納手段より画像データを読み出すためのアドレスを生成する第 1 のアドレス生成手段( 例えば、リードアドレス生成部 1 4 ) と、格納手段から当該アドレスに対応させて読み出された画像データを格納する第 1 のデータ保持手段( 例えば、リードバッファ 1 0 ) と、画像データを処理する少なくとも 1 つ以上の第 2 の画像処理手段( 例えば、サブモジュール 1 1 - 1 ~ 1 1 - n ) と、最終段の第 2 の画像処理手段で処理された出力データを格納する第 2 のデータ保持手段( 例えば、ライトバッファ 1 2 ) と、出力データを格納手段に書き込むためのアドレスを生成する第 2 のアドレス生成手段( 例えば、ライトアドレス生成部 1 6 ) と、上記第 1 のデータ保持手段に画像データが格納可能、又は上記第 2 のデータ保持手段から出力データが出力可能な場合、上記アクセス制御手段に対して格納手段へのアクセスを要求する第 2 のアクセス制御手段( アービタ 1 3 ) とを備えることを特徴とする。

10

【 0 0 4 3 】

また、本実施形態では、上記画像処理手段が、上記格納手段からの画像データ読み出し終了時、又は、前記格納手段へのデータ書き込み終了時に割り込み要求信号を出力し、上記起動制御手段が、前記割り込み要求信号に基づいて、次の画像処理手段を起動することを特徴とする。

20

【 0 0 4 4 】

さらに、本実施形態では、上記画像処理手段が、上記格納手段からの最終データの読み出し終了時、又は格納手段への最終データの書き込み終了時に割り込み要求信号を出力する要求手段( 割り込み制御部 1 5 ) をさらに備えることを特徴とする。

【 0 0 4 5 】

さらにまた、本実施形態に係る画像処理装置では、上記第 1 のデータ保持手段は、データ出力が可能な場合に有効信号をセットし、上記第 2 のデータ処理手段は、有効信号がセットされているデータのみを受け取り、上記第 2 のデータ保持手段は、データ入力が不可能な場合に保持要求信号をセットし、上記第 2 のデータ処理手段は、保持要求信号がセットされている第 2 の保持手段へのデータ出力をホールドすることを特徴とする。

30

【 0 0 4 6 】

さらにまた、本実施形態に係る画像処理装置では、上記画像処理手段が複数の第 2 の画像処理手段を備えている場合、それぞれの第 2 の画像処理手段間のデータ入出力は、前述した有効信号及び保持要求信号を用いて行われることを特徴とする。

【 0 0 4 7 】

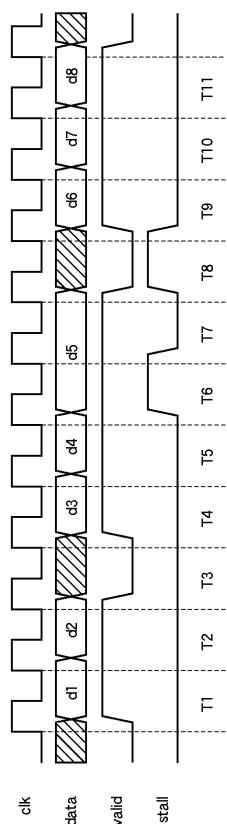

図 3 は、本発明の第 1 の実施形態における画像処理サブモジュール間 I / F の動作を示すタイミングチャートである。

【 0 0 4 8 】

図 3 に示すように、データ送信側の画像処理サブモジュールは、データが出力可能であればクロック c l k の立ち上がりに同期して、データ信号 d 1 及び有効信号 v a l i d をセットする( T 1 )。そして、当該画像処理サブモジュールは、次のクロックの立ち上がりで受信側からの保持要求信号 s t a l l がセットされなければデータが受信されたとみなし、次のデータが出力可能であればデータ信号 d a t a 及び有効信号 v a l i d をセットする( T 2 )。

40

【 0 0 4 9 】

また、データ送信側の画像処理サブモジュールは、次のデータが出力可能でなければ有効信号 v a l i d をリセットする( T 3 )。一方、当該画像処理サブモジュールは、次のクロックの立ち上がりで受信側からの保持要求信号 s t a l l がセットされていたら、データが受信されなかったとみなし、データ信号 d a t a 及び有効信号 v a l i d をホールド

50

する（T7）。

【0050】

尚、受信側からの保持要求信号s t a l l がセットされていても有効信号v a l i d がセットされなければ（T8）、それは無効データであるので、データ送信側の画像処理サブモジュールでは、データ信号d a t a 及び有効信号v a l i d はホールドされずに次の有効データが出力される（T9）。即ち、有効信号v a l i d がセットされていない時の保持要求信号s t a l l は無視される。

【0051】

ライトバッファ12は、バッファに空きがあれば、サブモジュール11-nからの有効信号v a l i d\_n がセットされた時のデータ信号d a t a\_n をバッファに格納する。一方、バッファに空きがなければ、保持要求信号s t a l l\_n をセットし、サブモジュール8-nの出力をホールドさせる。

10

【0052】

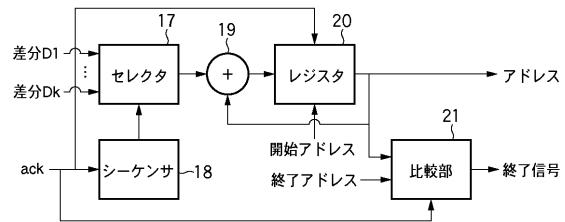

図4は、本発明の第1の実施形態に係る画像処理装置の各画像処理モジュールにおけるアドレス生成部（すなわち、リードアドレス生成部14やライトアドレス生成部16）の詳細な構成を説明するためのブロック図である。尚、図4において、17はセレクタ、18はシーケンサ、19は加算部、20はレジスタ、21は比較部である。

【0053】

まず、CPU1によって開始アドレスがレジスタ20にセットされる。シーケンサ18は、リクエスト受領信号a c k によって状態遷移し、状態に応じてセレクタ17のアドレス差分値を選択する。例えば、シーケンサ18は、内部に1つ以上のカウンタを持ち、受領信号a c k によって該当カウンタがカウントアップ又はカウントダウンし、各カウンタのキャリー（carry）又はボロー（borrow）によってセレクタ17を制御する。従って、所定回数のアクセス毎に、セレクタより出力されるアドレス差分値が切り替わる。

20

【0054】

尚、本実施形態においてはRAM7への転送効率アップのため、複数ワード数単位でアクセスする。従って、アクセス単位内に不要なデータが存在する場合（即ち、アクセス単位内でアドレスが不連続となる場合）は、アクセス単位のワード数n u mを変更して、不要なアクセスを防止するようにする。

【0055】

30

選択されたアドレス差分値は加算部19において直前のアドレスに加算され、受領信号a c k によってレジスタ20に保持される。レジスタ20の出力（即ち、アドレス生成部のアドレス出力）は比較部21において終了アドレスと比較され、レジスタ20の出力と終了アドレスとが一致した場合、受領信号a c k によって終了信号がセットされる。

【0056】

セレクタ17に入力されるアドレス差分値D1～Dk（但し、kは1以上の整数とする。）及びシーケンサ18のパラメータ（例えば、カウンタの進数等）は、前記コンフィギュレーションレジスタによって設定される。アドレス差分値のM S B（最上位ビット）と出力アドレスのM S Bの重みを一致させることにより、負の差分値を表現することができる。尚、バーストモードのように複数ワードをまとめてアクセスする場合もあるため、アドレス差分値と出力アドレスのビット数は必ずしも一致するとは限らない。また、通常、アドレス差分値の数は、シーケンサ18内のカウンタ数+1である。

40

【0057】

すなわち、本実施形態では、前述した第1又は第2のアドレス生成手段（例えば、リードアドレス生成部14やライトアドレス生成部16）が、アクセス要求アドレス（開始アドレス）を設定する設定手段（例えば、レジスタ20）と、複数のアドレス差分値から1つのアドレス差分値を選択する選択手段（例えば、セレクタ17）と、選択されたアドレス差分値とアクセス要求アドレスとを用いて新たなアクセス要求アドレスを生成する生成手段（例えば、加算部19）と、選択手段によるアドレス差分値の選択を制御する制御手段（例えば、シーケンサ18）とを備えることを特徴とする。

50

## 【0058】

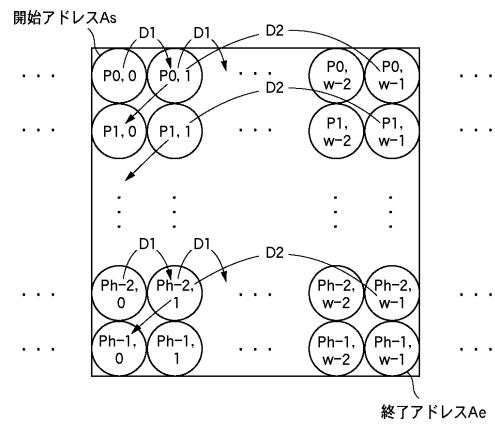

図5は、本発明の第1の実施形態に係るアドレス生成部におけるパラメータを説明する図である。

## 【0059】

例えば、図5に示すように、ブロック状にデータのアクセスを行う2次元アドレッシングの場合、レジスタ20には、まず、開始アドレスAsがロードされる。そして、シーケンサ18は、アドレス差分値D1を選択するようにセレクタ17を制御する。セレクタ17は、アドレス差分値D1を選択しているので、加算部19の出力はAs+D1となり、次のアドレスが生成される。レジスタ20は、受領信号ackが返ってくると、次のアドレスであるAs+D1を出力する。ここで、水平方向のアクセス数をwとすると、アドレス生成部は、上記操作をw-1回繰り返す。そして、w回目のアドレス生成において、シーケンサ18は、アドレス差分値D2を選択するようにセレクタ17を制御する。従って、w回目のアドレスはAs+(w-1)·D1+D2となって、次のラインの先頭データP1,0がアクセスされる。

## 【0060】

次に受領信号ackが返ってくると、シーケンサ18はアドレス差分値D1を選択するようにセレクタ17を制御する。このように、シーケンサ18はw回のアクセス毎に1回ずつアドレス差分値D2を選択し、それ以外ではアドレス差分値D1を選択するようにセレクタ17を制御する。従って、シーケンサ18では、w-1をロードして受領信号ackによってカウンタをデクリメント(-1)し、カウンタが0になった時に次の受領信号ackによってw-1をリロードするw進カウンタを構成し、w進カウンタが0になった時にアドレス差分値D2を選択する信号を生成すればよい。

## 【0061】

従って、この2次元アドレッシングの場合のアドレス生成部のパラメータは、開始アドレスAs、終了アドレスAe、水平方向のアクセス数w(設定値はw-1)、2つのアドレス差分値D1、D2の合計5つとなる。

## 【0062】

例えば、図5に示すように、アドレスが隣接している場合は、D1=1となる。また、右から左へアクセスする場合は、D1=-1とすれば良い。同様に、90°回転や、飛び飛びにアクセスするような場合においても、上記パラメータを適切に設定することにより可能となる。但し、90°回転の場合は、水平方向のアクセス数wの代わりに垂直方向のアクセス数hを用いる。

## 【0063】

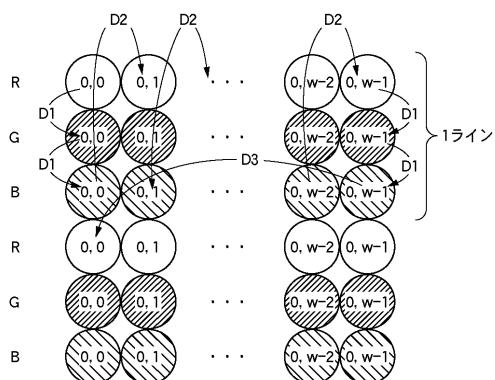

図6は、本発明の第1の実施形態に係る上記アドレス生成部の別のシーケンスを説明する図である。

## 【0064】

例えば、図6に示すようなRGB線順次データを点順次データに変換するような3次元アドレッシングの場合、シーケンサ18はアドレス差分値D1を2回選択した後、アドレス差分値D2を1回選択するようにセレクタ17を制御する。このシーケンスをw-1回繰り返すと、シーケンサ18はアドレス差分値D3を選択するようにセレクタ17を制御する。よって、シーケンサ18は内部に、c-1(本実施形態では、プレーン数c=3)をロードし、受領信号ackによって、カウンタを-1し、カウンタが0になった時に次の受領信号ackによってc-1をリロードするc進カウンタと、w-1をロードし、c進カウンタが0の時の受領信号ackによって、カウンタを-1し、カウンタが0かつc進カウンタが0の時の受領信号ackによってw-1をリロードするw進カウンタを構成し、c進カウンタとw進カウンタが共に0の時はアドレス差分値D3を、c進カウンタのみ0の時はアドレス差分値D2を、それ以外ではアドレス差分値D1を選択する信号を生成すればよい。

## 【0065】

従って、この3次元アドレッシングの場合のアドレス生成部のパラメータは、開始アドレ

10

20

30

40

50

ス A s、終了アドレス A e、プレーン数 c ( 設定値は c - 1 ) 、水平方向のアクセス数 w ( 設定値は w - 1 ) 、 3 つのアドレス差分値 D 1 、 D 2 、 D 3 の合計 7 つとなる。

#### 【 0 0 6 6 】

尚、各画像処理モジュールのインターフェースを共通化するため、リードバッファのデータ入力、ライトバッファのデータ出力は RAM インタフェース部 6 に合わせておく。また、画像処理モジュール内部のサブモジュールとのデータ線のビット数が合わない場合はサブモジュール 1 1 - 1 及びサブモジュール 1 1 - n にて変換する。尚、サブモジュールに入力データをそのまま出力するバイパスモードを設けることで、不要な処理をバイパスできる。この時、バイパスしたサブモジュールのクロックの供給を止めることで、消費電力の無駄も省くことができる。

10

#### 【 0 0 6 7 】

さらに、あるサブモジュール以降の全てのサブモジュールをバイパスモードとすることで、途中経過のデータ出力も可能となり、他の画像処理モジュールやサブモジュールの処理を任意のサブモジュール間に追加できる。従来は、サブモジュールの追加や変更が必要になった場合、画像処理モジュール全体が使用不可になってしまったが、バイパスモードにて処理を分断することで、画像処理モジュールを有効利用することができる。

#### 【 0 0 6 8 】

例えば、画像処理モジュール内に 3 つのサブモジュール、サブモジュール 1 、サブモジュール 2 及びサブモジュール 3 があり、サブモジュール 2 をサブモジュール 4 で置き換える場合、まず、最初にサブモジュール 2 以降をバイパスモードにして画像処理モジュールを起動し、次にサブモジュール 4 の処理を行った後、サブモジュール 2 までをバイパスモードにして画像処理モジュールを起動する。即ち、最初のステップでサブモジュール 1 を実行し、次のステップでサブモジュール 4 を実行し、最後のステップでサブモジュール 3 を実行するのである。このように、サブモジュール間の任意の位置に別の画像処理モジュールのサブモジュールによる処理を追加することが可能となる。ここで、上記各ステップでの処理結果は共有メモリ上に存在するので、追加する処理は CPU によってソフトウェア処理で行っても良い。

20

#### 【 0 0 6 9 】

次に、それぞれの画像処理モジュールへの画像処理の分割方法について説明する。

#### 【 0 0 7 0 】

本発明においては、画像処理モジュール間のデータの受け渡しは共有メモリ ( 例えは、 RAM 7 ) を介して行うので、画像処理モジュールの数が増加すると、メモリのバス占有率が上昇し、メモリアクセス待ち状態が増えて処理効率が低下する。一方、 1 つの画像処理モジュールに多くの処理を統合すると、データの抽出 ( 並び替え ) 等のために多くのローカルメモリが必要になってしまう。また、それぞれの画像処理モジュールの使い勝手も悪化してしまう。

30

#### 【 0 0 7 1 】

そこで、本実施形態では、データの抽出 ( 並び替え ) が必要となる部分において画像処理モジュールの分割を行う。具体的には、 ( 1 ) JPEG 復号化からラスタ化までの処理、 ( 2 ) ノイズ除去処理、 ( 3 ) バンドデータ作成処理、 ( 4 ) ビットマップデータ作成処理、 ( 5 ) ヘッドデータ作成処理、の 5 つの処理モジュールに分割する。そして、上記 5 つの処理をパイプライン化することで、バンドバッファのコヒーレンシ ( coherency ) を保ちつつ、処理効率の向上を図る。

40

#### 【 0 0 7 2 】

また、本実施形態では、データを削減する処理については可能な限り上流工程において行い、共有メモリへのアクセス量の最小化を図る。具体的には、バンドの抽出のためのクリッピングや、リサイズにおける縮小処理を、上記 ( 1 ) JPEG 復号化からラスタ化までの処理において前処理として実施する。さらに、MCU バッファを用いて回転処理を前処理として行うことにより、共有メモリへのアクセスの連続性を増加させ、バス使用効率を向上させる。さらに、容量の確定しないバッファ ( 例えは、上述した図 14 におけるライ

50

ンバッファ205、233、213、220、225、フレームバッファ210、バンドバッファ219、226)を共有メモリ上に構成し、処理内容に応じてバッファ容量の最適化を図ることとする。

【0073】

以下、上記各画像処理モジュール毎の画像データ処理の流れについて説明する。

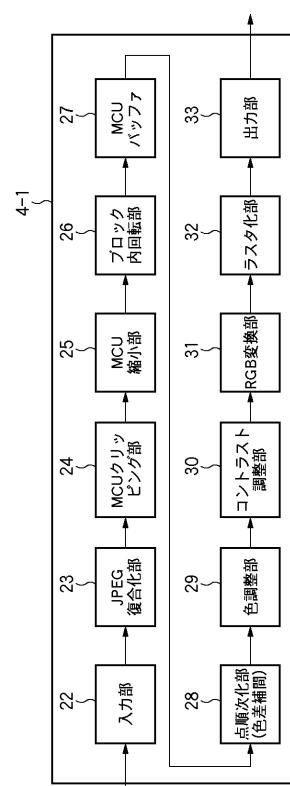

【0074】

図7は、本発明の第1の実施形態に係る画像処理モジュール4-1の構成を説明するためのブロック図である。図7において、22は入力部、23はJPEG復号化部、24はMCUクリッピング部、25はMCU縮小部、26はブロック内回転部、27はMCUバッファ、28は点順次化部、29は色調整部、30はコントラスト調整部、31はRGB変換部、32はラスタ化部、33は出力部である。尚、上記構成の画像処理モジュール4-1では、メモリの容量削減のために、ページの一部をバンド上に順次切り出して処理するバンド処理を行うものとする。

【0075】

まず、入力部22よりJPEG圧縮画像データがJPEG復号化部23に入力され、そこで復号化されてMCU単位で出力される。次いで、MCUクリッピング部24は、画像のトリミング領域及びバンド処理領域に基づいて、MCU単位にデータの有効又は無効を判定し、有効領域のMCUデータのみを出力する。有効MCUデータはMCU縮小部25において所望のMCUサイズに縮小される。即ち、MCU縮小部25では、1/8単位または1/16単位(4:2:0サンプリングの場合)の縮小が行われる。

【0076】

縮小されたMCUデータはブロック内回転部26のアドレス生成によりMCUバッファ27の回転(鏡像)後のアドレスに格納される。そして、MCU内の全データがMCUバッファ27に格納されると、点順次化部28はMCUバッファ27よりY、Cr、Cbのデータを同時に読み出す。ここで、Cr、Cbデータがサブサンプリングされている場合は、点順次化時に補間される。同時化されたYCrCbデータは、色調整部29においてホワイトバランス調整等の色調整が行われ、コントラスト調整部30においてコントラスト調整が行われる。さらに、RGB変換部31においてRGBデータに変換される。変換されたRGBデータは、ラスタ化部32のアドレス操作後出力部33から出力され、RAM7上にラスタ状に格納される。

【0077】

尚、上述したように、MCUブロック内の並び替えは、上記MCUバッファ27において行われているので、ラスタ化部32ではブロック単位の並び替えを行うことで、ラスタ化を行う。このブロック単位の並び替えは、上記ライトアドレス生成部16によって実現されるので、ラスタ化部32の実体はライトアドレス生成部となる。また、上記ブロック内回転、点順次化はMCUバッファのアドレッシングにて実行するので、ブロック内回転部26、MCUバッファ27、点順次化部28は同一のサブモジュールとした方が良い。尚、ブロックバッファの読み出し時にブロック内回転処理を行う場合は、ブロック内回転部26の位置はMCUバッファ27の後になる。

【0078】

また、色差Cr、Cbデータがサブサンプリングされている場合は、MCU縮小部25における倍率を輝度Yの2倍とすることで、点順次化時の補間を削除できる。この場合、MCU縮小部25での処理は、縮小だけでなく拡大となる場合もあるが、色差Cr、Cbデータの解像度は最大限保存される(縮小による劣化は最小になる)。

【0079】

尚、MCU縮小部25は、色調整のためのプリスキャンデータ作成、インデックス画像生成、リサイズ画像生成のために用いられる。特に、インデックス用画像のように、倍率の小さい画像を生成する場合は、このMCU縮小部25において1/8または1/16単位の縮小を行うことにより、メモリの使用量を大幅に削減することができる。尚、インデックス画像生成やリサイズ画像生成の場合は、MCU縮小部25において大まかな縮小を行

い、細かな調整については後述するリサイズ部38において実行することにより、メモリの使用量を削減しつつ所望のサイズに合わせることができる。

【0080】

図8は、本発明の第1の実施形態に係る画像処理モジュール4-2の構成を説明するためのブロック図である。図8において、34は入力部、35はノイズ除去部、36は出力部である。

【0081】

入力部34より入力された画像データ（例えば、画像処理モジュール4-1による処理後の画像データ）は、ノイズ除去部35において、画像に重畳されているノイズ成分が低減された後、出力部36よりメモリへ出力される。

10

【0082】

ここで、ノイズ除去アルゴリズムとしては、エッジ保存型LPF（Low Pass Filter）を用いたものや、メディアンフィルタを用いたものなどの各種方式が提案されているが、いずれも注目画素近傍（処理ウインドウ）の画素を使用するものである。従って、入力部34より上記注目画素近傍を読み出す操作、即ち、入力部34のアドレス操作によって、ラインバッファを用いずにノイズ除去を行うことができる。

【0083】

尚、ノイズ除去処理は1画素ごとに行われる逐次処理であるので、複数ラインのデータを必要とするリサイズ処理には直結することができない。従って、この画像処理モジュールはノイズ除去処理のみとなる。また、ノイズ除去処理が不要な場合は、この画像処理モジュールを起動する必要がないので、処理時間及び消費電力をさらに削減することが可能となる。

20

【0084】

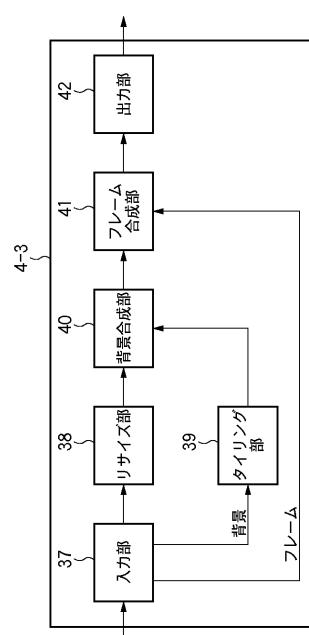

図9は、本発明の第1の実施形態に係る画像処理モジュール4-3の構成を説明するためのブロック図である。図9において、37は入力部、38はリサイズ部、39はタイリング部、40は背景合成部、41はフレーム合成部、42は出力部である。上記構成を有する本画像処理モジュールでは、背景やフレームの合成を行う。

【0085】

入力部37より注目画素データ及びリサイズ処理に必要な近傍画素データがリサイズ部38に入力される。リサイズ部38では、入力画像データをページ上のレイアウトサイズに合わせてリサイズする。一方、入力部37より背景データがタイリング部39に入力され、背景データがタイル状に敷き詰められる。そして、背景合成部40は、リサイズ処理後の画像データと背景データとを合成する。さらに、入力部37よりフレームデータがフレーム合成部41に入力されてフレームが合成され、出力部40よりメモリへ出力される。また、バンドの切り出し（クリッピング）は入力部37において、処理に必要な画素のみ読み出すことによって実現することが可能である。

30

【0086】

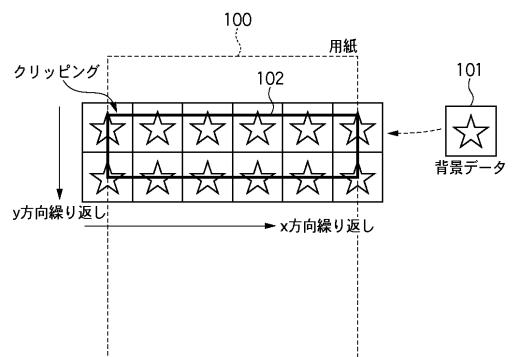

図10は、本発明の第1の実施形態に係る画像処理モジュール4-3におけるタイリング処理及びクリッピング処理の動作例を説明するための図である。

【0087】

40

背景データ101は、用紙100上のクリッピング有効領域102（図10中の太線で囲まれたバンド処理領域）に敷き詰められる。これらの操作は、全て共有メモリからの読み出し操作によって実行される。ここで、背景データ101のx方向のサイズをBw、y方向のサイズをBh、背景データのスタートアドレスをAsとすると、読み出しアドレスArは、Bw進カウンタCxとBh進カウンタCyの2つのカウンタ値を用いて、

$$Ar = As + Cy \times w + Cx \quad \dots \quad (1)$$

となる。

【0088】

ここで、2つのカウンタに初期値を与えれば、図10に示すように繰り返りのスタート位置にオフセットを付けることができる。また、クリッピング有効領域102を超えた時に

50

上記 B w 進カウンタに初期値をリロードし、上記 B h 進カウンタをインクリメントすることで、クリッピング処理を実現できる。

【 0 0 8 9 】

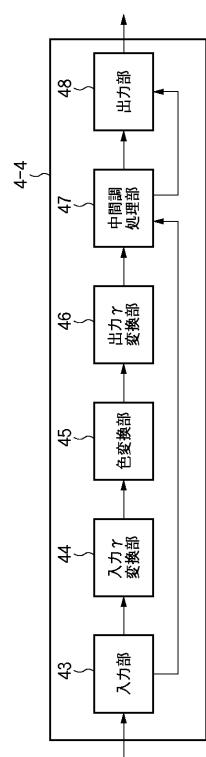

図 1 1 は、本発明の第 1 の実施形態に係る画像処理モジュール 4 - 4 の構成を説明するためのブロック図である。図 1 1 において、4 3 は入力部、4 4 は入力変換部、4 5 は色変換部、4 6 は出力変換部、4 7 は中間調処理部、4 8 は出力部である。この画像処理モジュール 4 - 4 では、ビットマップ生成処理を行う。

【 0 0 9 0 】

入力部 4 3 より印刷データが読み出され、入力変換部 4 4 において濃度リニアな信号に変換される。濃度リニアな信号に変換された印刷データは、色変換部 4 5 によってプリンタの色材の濃度データ（出力デバイスカラー）に変換される。次いで、出力変換 4 6 において出力補正され、中間調処理部 4 7 においてビットマップデータ（ドットバターン）に変換され、出力部 4 8 より出力される。ここで、画像データの中間調処理に誤差拡散法を用いた場合、前ラインの量子化誤差が入力部 4 3 より中間調処理部 4 7 に入力される。また、量子化誤差を周囲の画素に拡散させるために、出力部 4 8 より量子化誤差を共有メモリへ格納する。これにより、共有メモリ上に誤差バッファが構成される。

処理量（ハード量）の削減のため、色変換部 4 5 では 1 つの色材データのみが出力される。従って、例えば、プリンタの色材が C, M, Y, K の 4 色であったとすると、4 色のビットマップを生成するために当該画像処理モジュール 4 - 4 は 4 回起動されることになる。

【 0 0 9 1 】

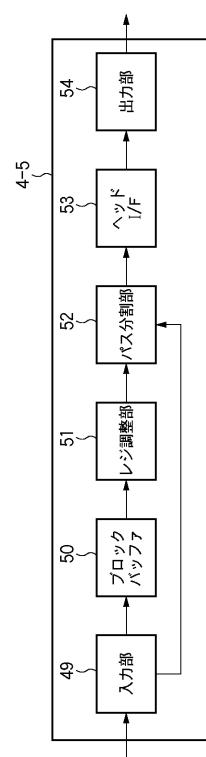

図 1 2 は、本発明の第 1 の実施形態に係る画像処理モジュール 4 - 5 の構成を説明するためのブロック図である。図 1 2 において、4 9 は入力部、5 0 はブロックバッファ、5 1 はレジ調整部、5 2 はパス分割部、5 3 はヘッド I / F、5 4 は出力部である。この画像処理モジュール 4 - 5 では、プリントエンジンに出力するためのデータ処理を行う。

【 0 0 9 2 】

まず、不図示のプリントエンジンが起動されると、入力部 4 9 よりビットマップデータがヘッドのドット構成要素（例えば、インクジェット方式においてはノズル）の並びに合わせて読み出され、ブロックバッファ 5 0 に格納される。レジ調整部 5 1 はプリントエンジンの同期信号に合わせて、ヘッドのドット構成要素列（ノズル列）に対応するドットデータを抽出する。通常、ビットマップデータは、ヘッドのスキャン方向の複数ドットを 1 ワードとして格納されるので、ブロックバッファ 5 0 の所定ビットのみを選択して取り出す。この時、同時に読み出すビット位置をヘッドのドット構成要素列（ノズル列）毎にずらすことによってレジ調整を行う。

【 0 0 9 3 】

抽出されたドットデータは、パス分割部 5 2 において、入力部 4 9 より読み出されたマスクデータに従って複数のパス（スキャン）に分割される。分割されたドットデータは、ヘッド I / F 5 3 においてヘッドへの伝送フォーマットに変換され、出力部 5 4 よりヘッドへ出力される。このように、複数のパス（スキャン）にて出力画像を形成することにより、ドットのヨレやメカ精度によるドットの位置ずれを知覚され難い高周波領域に変調（拡散）し、プリント出力時のスジやムラを低減することが可能となる。

【 0 0 9 4 】

以上説明したように、第 1 の実施形態によれば、上記一連の画像処理を入力画像データへのアクセスに着目して少数の処理ブロックに分割し、処理ブロック単位にモジュール化し、各モジュール間のデータの受け渡しを、共有メモリを通じて行う構成とすることで、各画像処理モジュールの I / F を汎用化し、画像処理モジュール単位の追加変更を容易にするだけでなく、無駄なバッファやメモリ及び処理の削減が可能となる。

【 0 0 9 5 】

また、容量を確定できないバッファを共有メモリ上に構成することにより、バッファ容量の最適化が可能となる。さらに、必要なバッファ容量が増加しても、共有メモリの容量変

10

20

30

40

50

更のみで対応することが可能となる。

【0096】

さらに、画像処理モジュール内を複数のサブモジュールにて構成し、サブモジュールにバイパスモードを設けることで、一部のサブモジュールの置き換えや新たな処理の追加を容易にすることができる。

【0097】

さらにまた、データが削減される処理を上流工程で行う構成により、共有メモリへのアクセス量が大幅に削減される。さらにまた、アドレスの連續性が向上するように処理することにより、共有メモリのバス使用効率が向上する。

【0098】

10

<第2の実施形態>

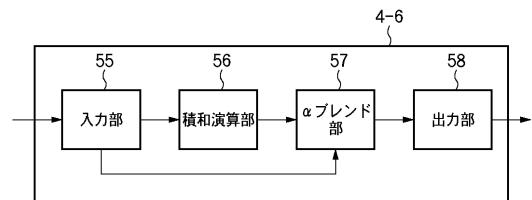

図13は、本発明の第2の実施形態に係る画像処理装置における画像処理モジュール4-6の構成を説明するためのブロック図である。図13において、55は入力部、56は積和演算部、57はブレンド部、58は出力部である。本実施形態では、前述した第1の実施形態に係る画像処理装置における画像処理モジュール4-2及び画像処理モジュール4-3における画像処理を1つの画像処理モジュール4-6を用いて実現するものである。従って、図1におけるモジュール数mは4となる。

【0099】

まず、画像処理モジュール4-2で実現されたノイズ除去機能を画像処理モジュール4-6で実現する方法について説明する。

20

【0100】

まず、入力部55よりLPF(ローパスフィルタ)のタップ(Tap)に対応する画素データが抽出され、積和演算部56において上記タップ上の画素データとタップ係数の積和演算が行われる。ブレンド部57では、上記積和演算部56の出力(積和演算出力)と注目画素データとの差分より値を決定し、積和演算出力と注目画素データとをブレンドし、出力部58より共有メモリへ出力する。

【0101】

ここで、前述した前記ノイズ除去部35において、LPF出力データと元データとの差分を比較し、差分が小さければ平坦部とみなしてLPFの出力を選択し、一方、差分が小さければエッジ部とみなして元データを選択する方法を用いるものとすると、上記LPFは入力データの積和演算によって実現することができ、上記データの選択はブレンディングによって実現することができる。

30

【0102】

例えば、入力データとLPF出力データとの差分絶対値と所定の閾値とを比較し、差分絶対値が閾値以上の場合、入力データの係数を1、LPF出力の係数を0としてブレンドする。一方、差分絶対値が閾値未満の場合、入力データの係数を0、LPF出力の係数を1としてブレンドする。或いは、入力データとLPF出力データとの差分絶対値が小さくなるにつれて、LPF出力の割合が大きくなるようにブレンドするようにしても良い。

【0103】

次に、第1の実施形態の画像処理モジュール4-3による背景合成機能を画像処理モジュール4-6で実現する方法について説明する。

40

【0104】

まず、入力部55よりリサイズ処理に必要な近傍の画素データが抽出され、積和演算部56において近傍画素データと補間係数の積和演算が行われる。即ち、積和演算部56は補間フィルタとして動作する。一方、背景画素データが入力部55よりブレンド部57に入力され、ブレンド部57では、上記積和演算部56の出力と上記背景画素データとを上記背景画素データの値を用いてブレンドし、出力部58より共有メモリへ出力する。尚、第1の実施形態と同様に、本実施形態においてもタイミング処理及びクリッピング処理は、入力部55におけるメモリアクセスによって実現するものとする。

【0105】

50

次に、第1の実施形態の画像処理モジュール4-3によるフレーム合成機能を画像処理モジュール4-6で実現する方法について説明する。

【0106】

まず、入力部55よりフレームのリサイズ処理に必要な近傍のフレーム画素データが抽出され、積和演算部56において近傍フレーム画素データと補間係数の積和演算が行われる。即ち、積和演算部56は補間フィルタとして動作する。尚、ここでフレーム画素データに付随している値も補間される。一方、画素データが入力部55よりブレンド部57に入力され、ブレンド部57では、上記積和演算部56の出力と上記画素データとを上記積和演算出力の値を用いてブレンドし、出力部58より共有メモリへ出力する。尚、第1の実施形態と同様に、本実施形態においてもクリッピング処理は入力部55におけるメモリアクセスによって実現するものとする。これにより、フレームデータをリサイズしつつ合成することが可能になる。

【0107】

従って、本実施形態では、1バンドの処理について、ノイズ除去のみ、又は背景との合成のみ、又はフレームとの合成のみの場合は1回画像モジュール4-6を起動する。また、背景とフレームを合成する、又はノイズ除去して背景と合成する、又はノイズ除去してフレームと合成する場合は2回画像モジュール4-6を起動する。さらに、ノイズ除去して背景とフレームを合成する場合は3回画像モジュール4-6を起動することとなる。そして、合成後にさらに1回当該画像処理モジュール4-6を起動することにより、合成結果をタイミングすることもできる。即ち、図13に示した本実施形態に係る画像処理モジュール4-6の起動シーケンスによって多様なパターンの合成が可能となる。

【0108】

以上説明したように、複数の機能を1つの画像処理モジュールの設定により実現することで、画像処理モジュールの起動シーケンスによって多様な処理を実現でき、コスト、パフォーマンス、消費電力の最適化が容易になる。

【0109】

<他の実施形態>

前述した第1及び第2の実施形態において、それぞれのサブモジュールを関数(スレッド(Thread))、モジュールをオブジェクト(クラス(Class))として実装すれば、ソフトウェアによって同様の機能を実現することも可能である。この場合、各サブモジュール間のデータの受け渡しはポインタで行い、アドレス生成部では、当該ポインタによって示される配列の配列要素を生成すればよい。

【0110】

従って、前述した第1及び第2の実施形態の機能を実現するソフトウェアのプログラムコードを記録した記憶媒体(記録媒体)を、システムあるいは装置に供給し、そのシステムあるいは装置のコンピュータ(またはCPUやMPU)が記憶媒体に格納されたプログラムコードを読み出し実行することによっても、本願発明の目的が達成されることは容易に理解できよう。

【0111】

この場合、記憶媒体から読み出されたプログラムコード自体が本願発明の新規な機能を実現することになり、そのプログラムコードを記憶した記憶媒体は本願発明を構成することになる。

【0112】

プログラムコードを供給するための記憶媒体としては、例えば、フレキシブルディスク、ハードディスク、光ディスク、光磁気ディスク、CD-ROM, CD-R、磁気テープ、不揮発性のメモリカード、ROMなどを用いることができる。

【0113】

また、コンピュータが読み出したプログラムコードを実行することによって、前述した実施形態の機能が実現される他、そのプログラムコードの指示に基づき、コンピュータ上で稼動しているOSなどが実際の処理の一部または全部を行い、その処理によっても前述し

10

20

30

40

50

た実施形態の機能が実現され得る。

【0114】

さらに、記憶媒体から読み出されたプログラムコードが、コンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書き込まれた後、そのプログラムコードの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるCPUなどが実際の処理の一部または全部を行い、その処理によっても前述した実施形態の機能が実現され得る。

【0115】

なお、本願発明は、前述した実施形態の機能を実現するソフトウェアのプログラムコードを記録した記憶媒体から、そのプログラムを、パソコン通信など通信ラインを介して要求者にそのプログラムを配信する場合にも適用できることは言うまでもない。

10

【0116】

【発明の効果】

入力画像に対する各種画像処理を複数の処理ブロックに分割して処理ブロック単位にモジュール化し、各モジュール間のデータの受け渡しを、共有メモリを通じて行う構成とすることで、各画像処理モジュールのI/Fを汎用化し、画像処理モジュール単位の追加変更を容易にするだけでなく、無駄なバッファやメモリ及び処理の削減を図ることができる。

【図面の簡単な説明】

【図1】本発明の第1の実施形態に係る画像処理装置の一構成例を示すブロック図である。

20

【図2】本発明の第1の実施形態に係る画像処理装置のモジュール4-1～4-mの詳細な内部構成を説明するためのブロック図である。

【図3】本発明の第1の実施形態における画像処理サブモジュール間I/Fの動作を示すタイミングチャートである。

【図4】本発明の第1の実施形態に係る画像処理装置の各画像処理モジュールにおけるアドレス生成部の詳細な構成を説明するためのブロック図である。

【図5】本発明の第1の実施形態に係るアドレス生成部におけるパラメータを説明する図である。

【図6】本発明の第1の実施形態に係る上記アドレス生成部の別のシーケンスを説明する図である。

30

【図7】本発明の第1の実施形態に係る画像処理モジュール4-1の構成を説明するためのブロック図である。

【図8】本発明の第1の実施形態に係る画像処理モジュール4-2の構成を説明するためのブロック図である。

【図9】本発明の第1の実施形態に係る画像処理モジュール4-3の構成を説明するためのブロック図である。

【図10】本発明の第1の実施形態に係る画像処理モジュール4-3におけるタイリング処理及びクリッピング処理の動作例を説明するための図である。

【図11】本発明の第1の実施形態に係る画像処理モジュール4-4の構成を説明するためのブロック図である。

40

【図12】本発明の第1の実施形態に係る画像処理モジュール4-5の構成を説明するためのブロック図である。

【図13】本発明の第2の実施形態に係る画像処理装置における画像処理モジュール4-6の構成を説明するためのブロック図である。

【図14】デジタルカメラを用いて撮影された画像データをプリンタで出力する際に画像処理を行う従来の画像処理部の構成を示すブロック図である。

【符号の説明】

1 CPU

2 ROM

3 バスブリッジ

50

- 4 - 1 ~ 4 - m 画像処理モジュール

5、13 アービタ

6 RAM インタフェース部

7 RAM

8 ヘッドインターフェース部

9 I/O ポート

10 リードバッファ

11 - 1 ~ 11 - n サブモジュール

12 ライトバッファ

14 リードアドレス生成部

15 割り込み制御部 10

16 ライトアドレス生成部

17 セレクタ

18 シーケンサ

19 加算部

20 レジスタ

21 比較部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(72)発明者 石川 尚

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

合議体

審判長 板橋 通孝

審判官 千葉 輝久

審判官 畑中 高行

(56)参考文献 特開2001-312457 (JP, A)

特開2001-338286 (JP, A)

特開2000-181648 (JP, A)

特開2002-10277 (JP, A)

特開平4-317259 (JP, A)

特開平2001-283211 (JP, A)

特開2001-28662 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N1/21