(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6710627号

(P6710627)

(45) 発行日 令和2年6月17日(2020.6.17)

(24) 登録日 令和2年5月29日(2020.5.29)

|              |           |

|--------------|-----------|

| (51) Int.Cl. | F 1       |

| HO1L 21/336  | (2006.01) |

| HO1L 29/78   | (2006.01) |

| HO1L 21/8238 | (2006.01) |

| HO1L 27/092  | (2006.01) |

| HO1L 21/8234 | (2006.01) |

| HO1L         | 29/78     |

| HO1L         | 27/092    |

| HO1L         | 27/092    |

| HO1L         | 27/092    |

請求項の数 11 (全 23 頁) 最終頁に続く

(21) 出願番号 特願2016-246521 (P2016-246521)

(22) 出願日 平成28年12月20日 (2016.12.20)

(65) 公開番号 特開2018-101683 (P2018-101683A)

(43) 公開日 平成30年6月28日 (2018.6.28)

審査請求日 平成31年4月19日 (2019.4.19)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

東京都江東区豊洲三丁目2番24号

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 藤井 宏基

茨城県ひたちなか市堀口751番地 ルネ

サスセミコンダクタマニュファクチュアリ

ング株式会社内

(72) 発明者 森 隆弘

茨城県ひたちなか市堀口751番地 ルネ

サスセミコンダクタマニュファクチュアリ

ング株式会社内

審査官 岩本 勉

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

主表面を有し、前記主表面に分離溝を有する半導体基板と、

前記半導体基板の前記主表面に配置された、第1導電型のソース領域と、

前記ソース領域との間で前記分離溝を挟むように前記主表面に配置された、第1導電型

のドレイン領域と、

前記分離溝の下側に位置し、かつ前記ドレイン領域に接続された、第1導電型のドリフ

ト領域と、

前記分離溝内を埋め込み、かつ上面に凹部を有する分離絶縁膜と、

前記ソース領域と前記ドリフト領域とに挟まれる前記主表面に絶縁しながら対向し、か

つ前記凹部内を埋め込むゲート電極と、

前記ドリフト領域の下側であって前記凹部の真下に位置する部分を有する、第2導電型

の第1不純物領域とを備え。

前記第1不純物領域は前記凹部の真下にのみ位置する、半導体装置。

## 【請求項2】

前記ソース領域から前記ドレイン領域へ向かう方向における前記ドリフト領域の長さが

$L_d$  であり、

前記第1不純物領域は、前記分離溝の前記ソース領域側の端部から前記長さ  $L_d$  の3分

の1の寸法の範囲内に位置している、請求項1に記載の半導体装置。

## 【請求項3】

前記第1不純物領域の前記ドレイン領域側の端部は、前記凹部の底部から前記分離溝の底部までの深さ方向の寸法分だけ前記凹部から前記ドレイン領域側へ離れた位置よりも前記ソース領域側に位置している、請求項1に記載の半導体装置。

【請求項4】

前記ドリフト領域の下側に位置する第2導電型の第1ウエル領域と、

前記ソース領域と前記ドリフト領域との間の前記主表面に位置する第2導電型の第2ウエル領域とをさらに備え、

前記第1ウエル領域は、前記第2ウエル領域よりも低い不純物濃度を有する、請求項1に記載の半導体装置。

【請求項5】

10

前記ドリフト領域内であって、前記凹部の真下に位置する、第1導電型の第2不純物領域をさらに備えた、請求項1に記載の半導体装置。

【請求項6】

前記第2不純物領域は、前記第1不純物領域の濃度ピークよりも低い濃度ピークを有する、請求項5に記載の半導体装置。

【請求項7】

前記第2不純物領域の前記ドレイン領域側の端部は、前記凹部の底部から前記分離溝の底部までの深さ方向の寸法分だけ前記凹部から前記ドレイン領域側へ離れた位置よりも前記ソース領域側に位置している、請求項5に記載の半導体装置。

【請求項8】

20

前記凹部は、複数の凹部分を有し、

前記第2不純物領域は、前記複数の凹部分のそれぞれの真下領域に位置する複数の第2領域部分を有している、請求項5に記載の半導体装置。

【請求項9】

前記凹部は、複数の凹部分を有し、

前記第1不純物領域は、前記複数の凹部分のそれぞれの真下領域に位置する複数の第1領域部分を有している、請求項1に記載の半導体装置。

【請求項10】

前記複数の凹部分の各々の幅は、前記複数の凹部分のうちの互いに隣り合う凹部分間の距離よりも大きい、請求項9に記載の半導体装置。

30

【請求項11】

主表面を有し、前記主表面に位置する分離溝と、前記主表面に位置する第1導電型のソース領域と、前記ソース領域との間で前記分離溝を挟むように前記主表面に位置する第1導電型のドレイン領域と、前記分離溝の下側に位置して前記ドレイン領域に接続された第1導電型のドリフト領域と、を有する半導体基板を形成する工程と、

前記分離溝内を埋め込み、かつ上面に凹部を有する分離絶縁膜を形成する工程と、

前記ドリフト領域の下側であって前記凹部の真下に位置する第2導電型の第1不純物領域を形成する工程と、

前記ソース領域と前記ドリフト領域とに挟まれる前記主表面の上にゲート絶縁膜を挟んで対向し、かつ前記凹部内を埋め込むゲート電極を形成する工程とを備え、

40

前記上面に前記凹部を有する前記分離絶縁膜を形成する工程は、

前記分離溝内を埋め込む埋込絶縁膜を形成する工程と、

前記埋込絶縁膜を貫通する貫通孔を形成する工程と、

前記貫通孔の内壁を覆う被覆絶縁膜を形成する工程とを有し、

前記第1不純物領域を形成する工程は、前記貫通孔を通じて第2導電型の不純物を前記半導体基板に導入する工程を有する、半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関するものである。

50

## 【背景技術】

## 【0002】

高耐圧化のために、高耐圧LDMOS (Laterally Diffused Metal Oxide Semiconductor) ドレインのゲートとドレインとの間にSTI (Shallow Trench Isolation) 構造を用いることが知られている。このような構造は、たとえば特開2015-162581号公報、特開2009-278100号公報などに開示されている。

## 【0003】

上記2つの公報には、分離溝内を埋め込む分離絶縁膜の上面に溝を形成し、その溝内にゲート電極の一部が埋め込まれた構成が開示されている。

## 【0004】

上記2つの公報に記載の構成では、ホットキャリア注入 (HCI : Hot Carrier Injection) と呼ばれる現象を改善することが可能である。ここでホットキャリア注入とは、LDMOSドレインのドレイン電界によって加速され高いエネルギーを持ったキャリア (ホットキャリア) がゲート絶縁膜に注入されてドレインの特性 ( $I_{ds}$ 、 $V_{th}$ ) が変動する現象である。

## 【先行技術文献】

## 【特許文献】

## 【0005】

【特許文献1】特開2015-162581号公報

【特許文献2】特開2009-278100号公報

10

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

しかしながら、上記2つの公報に記載の技術では、ゲート絶縁膜へのホットキャリアの注入を抑制する効果が十分でない場合がある。

## 【0007】

その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

## 【課題を解決するための手段】

## 【0008】

20

一実施の形態の半導体装置によれば、第1導電型のソース領域とドレイン領域との間の分離溝内を埋め込む分離絶縁膜の上面に凹部が形成されている。第1導電型のドリフト領域は、分離溝の下側に位置し、かつドレイン領域に接続されている。ゲート電極は、凹部内を埋め込んでいる。ドリフト領域の下側であって凹部の真下には、第2導電型の第1不純物領域が位置している。

## 【0009】

一実施の形態の半導体装置の製造方法によれば、分離溝内を埋め込み、かつ上面に凹部を有する分離絶縁膜が形成される。ドリフト領域の下側であって凹部の真下に位置する第2導電型の第1不純物領域が形成される。ソース領域とドリフト領域とに挟まれる主表面の上にゲート絶縁膜を挟んで対向し、かつ凹部内を埋め込むゲート電極が形成される。

40

## 【発明の効果】

## 【0010】

前記一実施の形態によれば、ゲート絶縁膜へのホットキャリアの注入をさらに抑制することが可能な半導体装置およびその製造方法を実現することができる。

## 【図面の簡単な説明】

## 【0011】

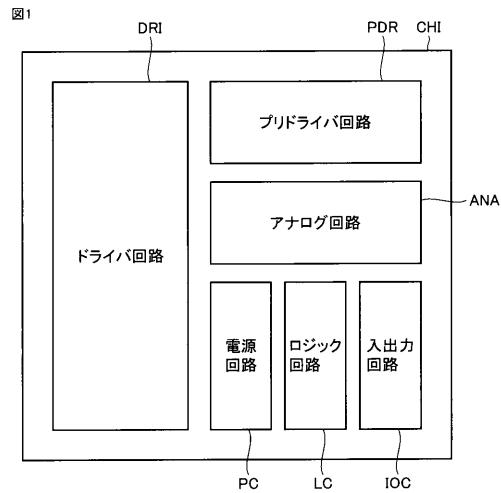

【図1】実施の形態1におけるチップ状態の半導体装置の構成を概略的に示す平面図である。

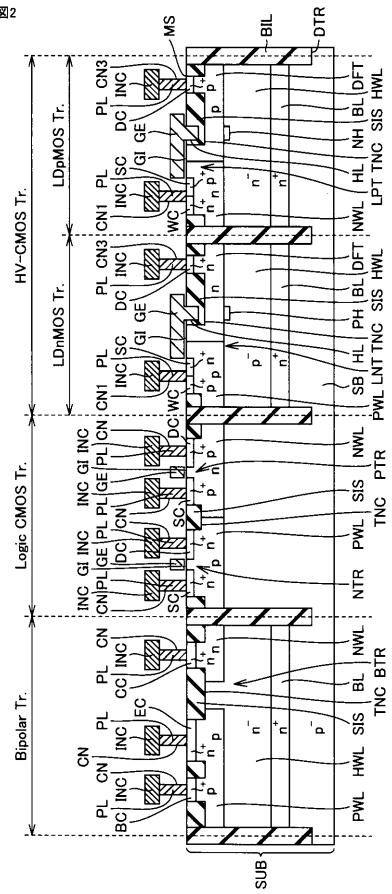

【図2】図1に示す半導体装置の構成を示す断面図である。

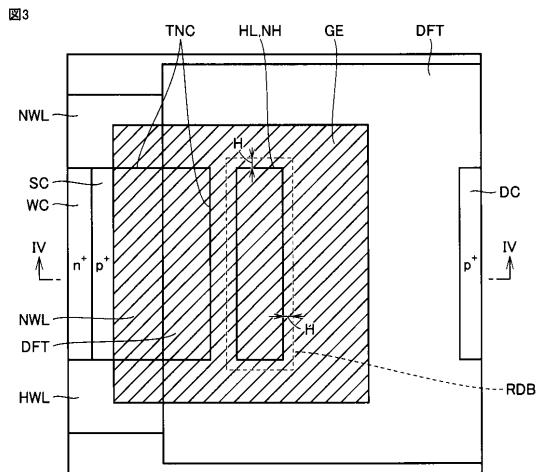

【図3】図2に示すLDMOSトランジスタ部の構成を示す平面図である。

50

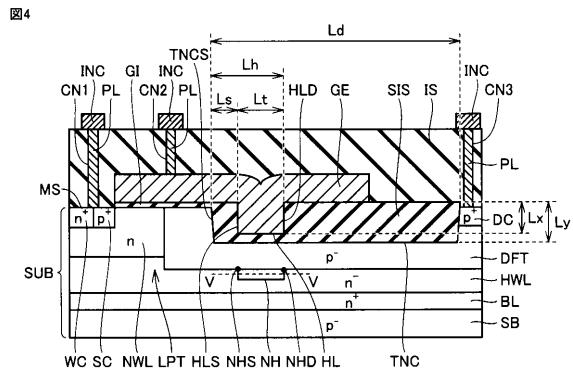

【図4】図3のI-V-I-V線に沿う概略断面図である。

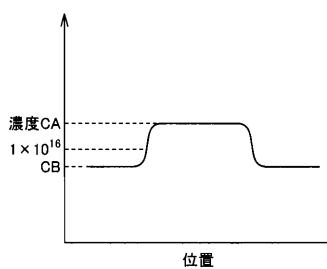

【図5】図4のV-V線に沿う不純物濃度分布を示す図である。

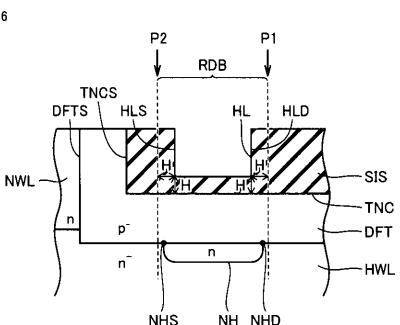

【図6】リセス下のn型不純物領域の位置を説明するための部分拡大断面図である。

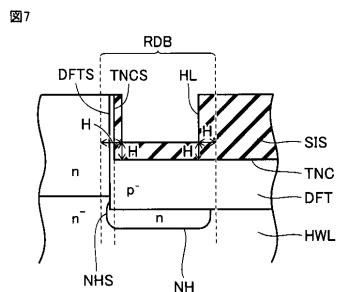

【図7】リセス下のn型不純物領域の位置を説明するための部分拡大断面図である。

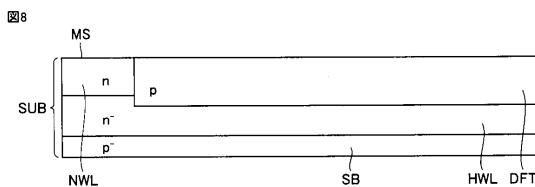

【図8】図4に示す半導体装置の製造方法の第1工程を示す断面図である。

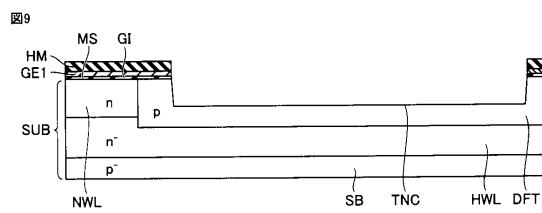

【図9】図4に示す半導体装置の製造方法の第2工程を示す断面図である。

【図10】図4に示す半導体装置の製造方法の第3工程を示す断面図である。

【図11】図4に示す半導体装置の製造方法の第4工程を示す断面図である。

【図12】図4に示す半導体装置の製造方法の第5工程を示す断面図である。

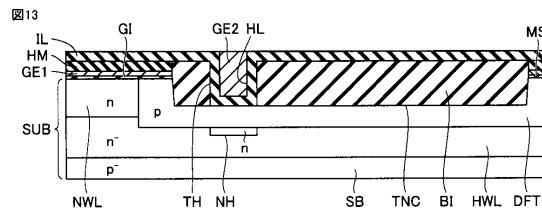

【図13】図4に示す半導体装置の製造方法の第6工程を示す断面図である。

10

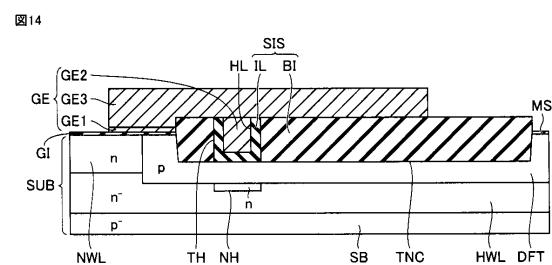

【図14】図4に示す半導体装置の製造方法の第7工程を示す断面図である。

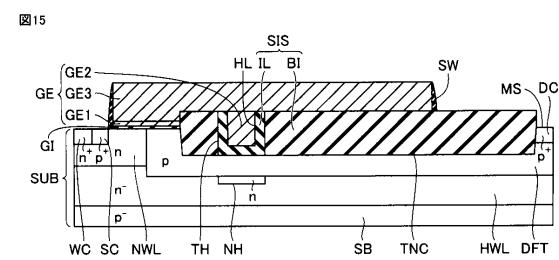

【図15】図4に示す半導体装置の製造方法の第8工程を示す断面図である。

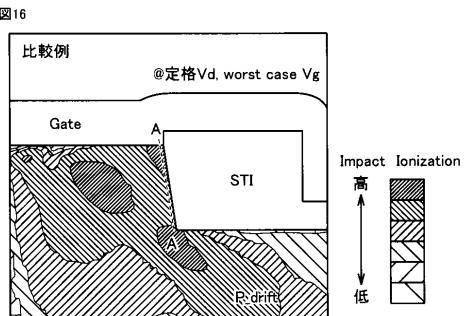

【図16】比較例における半導体装置のインパクトイオン化率分布を示す図である。

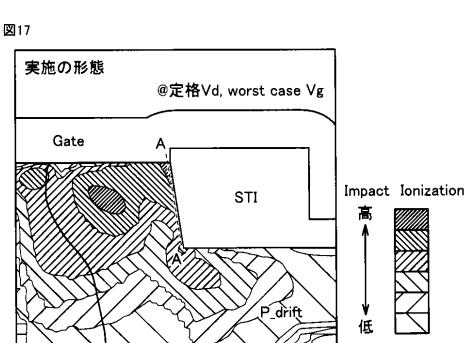

【図17】実施の形態1における半導体装置のインパクトイオン化率分布を示す図である。

。

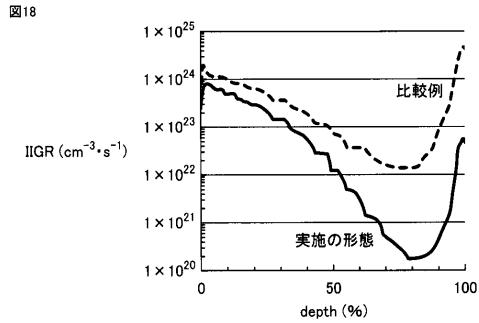

【図18】図16および図17のA-A線に沿う電界強度を示す図である。

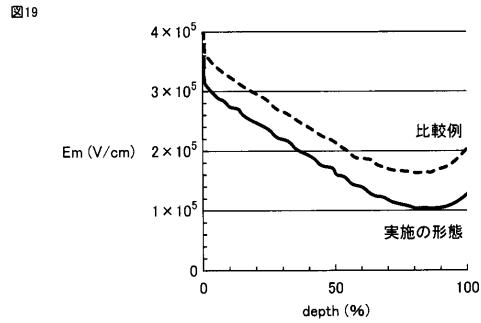

【図19】図16および図17のA-A線に沿うインパクトイオン化発生率を示す図である。

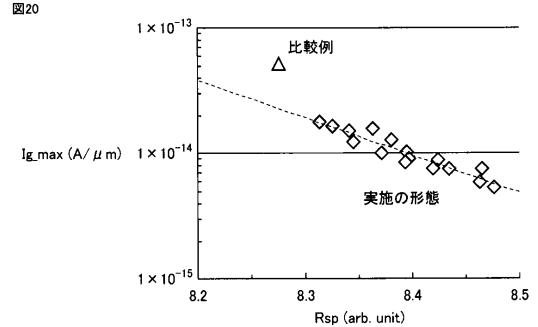

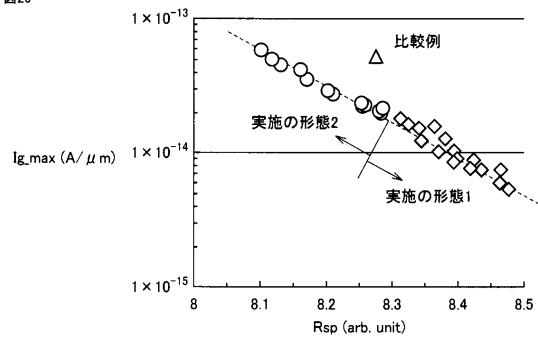

【図20】実施の形態1と比較例との各々におけるオン抵抗R<sub>sp</sub>とゲート電流I<sub>g</sub>との関係を示す図である。

20

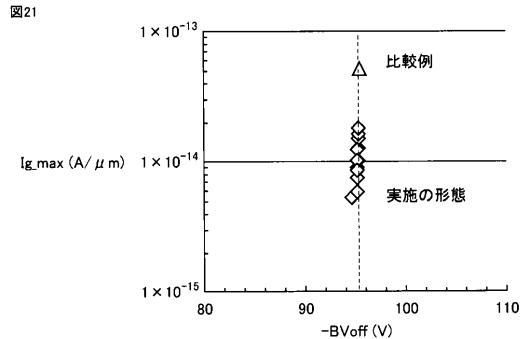

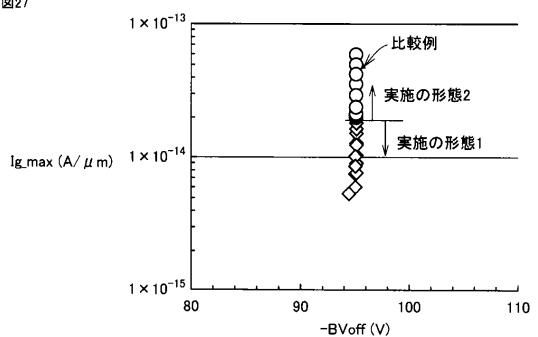

【図21】実施の形態1と比較例との各々におけるオフ耐圧B<sub>Voff</sub>とゲート電流I<sub>g</sub>との関係を示す図である。

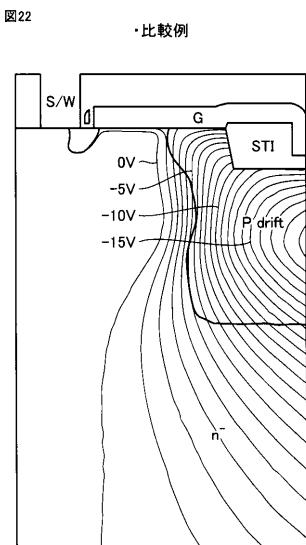

【図22】比較例における半導体装置の等電位線を示す図である。

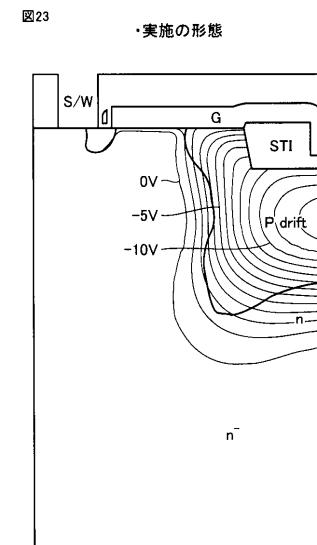

【図23】実施の形態1における半導体装置の等電位線を示す図である。

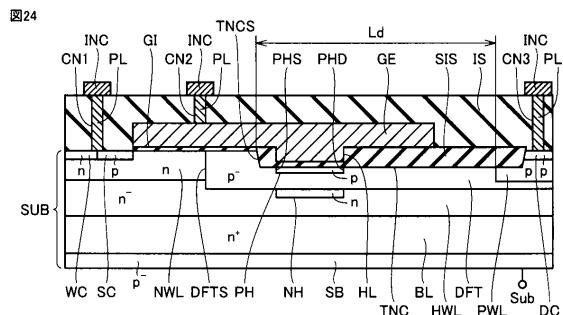

【図24】実施の形態2における半導体装置の構成を示す断面図である。

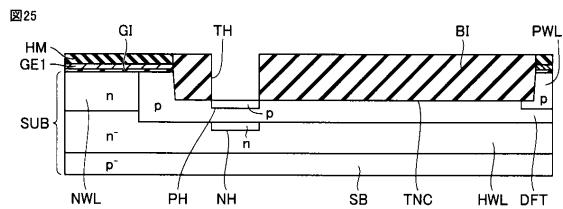

【図25】図24に示す半導体装置の製造方法を示す断面図である。

【図26】実施の形態1および2と比較例との各々におけるオン抵抗R<sub>sp</sub>とゲート電流I<sub>g</sub>との関係を示す図である。

【図27】実施の形態1および2と比較例との各々におけるオフ耐圧B<sub>Voff</sub>とゲート電流I<sub>g</sub>との関係を示す図である。

30

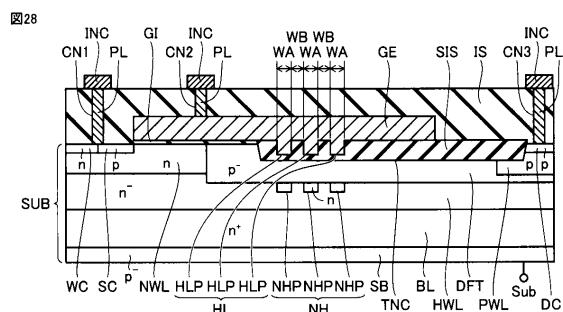

【図28】実施の形態3における半導体装置の構成を示す断面図である。

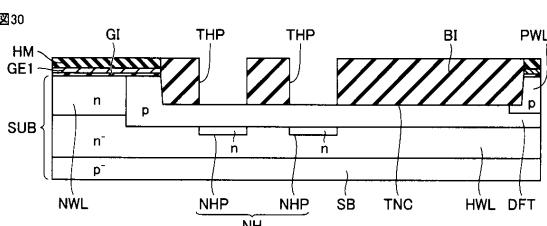

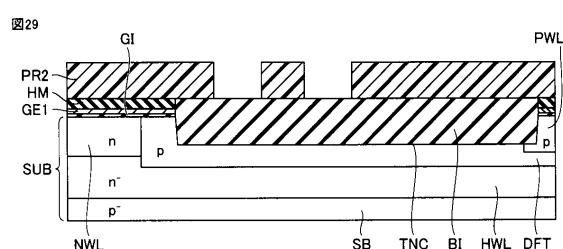

【図29】図28に示す半導体装置の製造方法の第1工程を示す断面図である。

【図30】図28に示す半導体装置の製造方法の第2工程を示す断面図である。

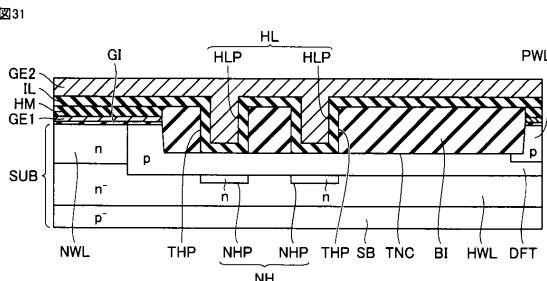

【図31】図28に示す半導体装置の製造方法の第3工程を示す断面図である。

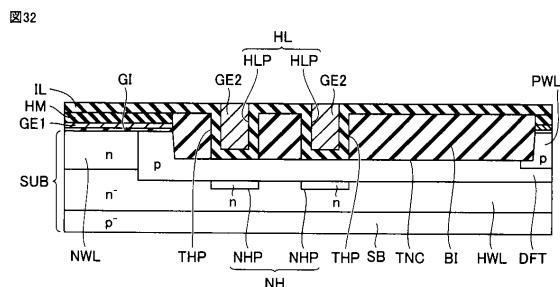

【図32】図28に示す半導体装置の製造方法の第4工程を示す断面図である。

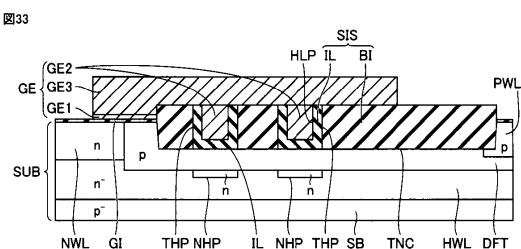

【図33】図28に示す半導体装置の製造方法の第5工程を示す断面図である。

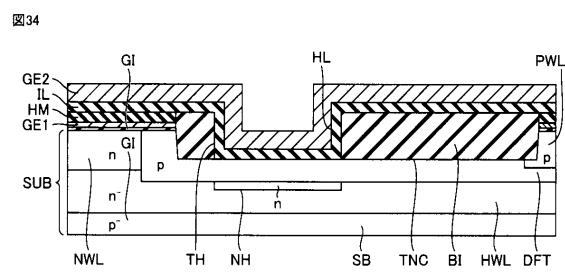

【図34】比較例の半導体装置の製造方法の第1工程を示す断面図である。

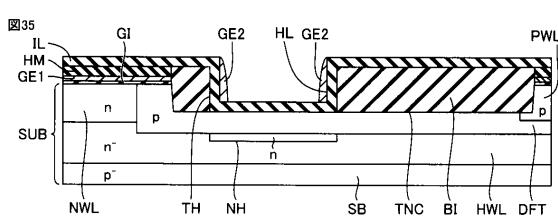

【図35】比較例の半導体装置の製造方法の第2工程を示す断面図である。

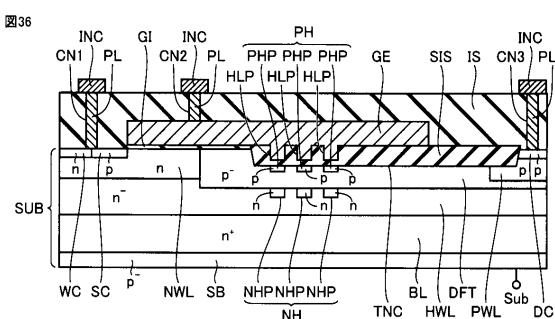

【図36】実施の形態3の変形例における半導体装置の構成を示す断面図である。

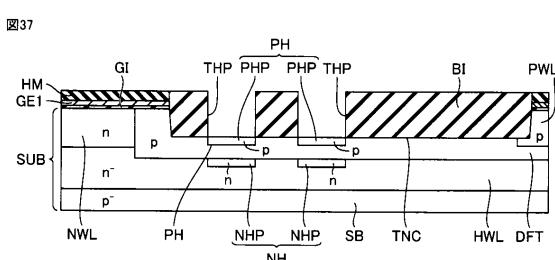

【図37】図36に示す半導体装置の製造方法を示す断面図である。

40

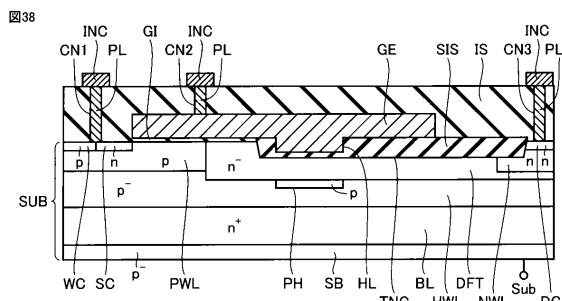

【図38】実施の形態1の構成をLDMOSトランジスタにも適用できることを説明するための断面図である。

### 【発明を実施するための形態】

#### 【0012】

以下、実施の形態について図に基づいて説明する。

##### (実施の形態1)

図1に示されるように、本実施の形態の半導体装置CHは、たとえばチップ状態であり、半導体基板を有している。半導体基板の表面には、ドライバ回路DRI、プリドライバ回路PDR、アナログ回路ANA、電源回路PC、ロジック回路LC、入出力回路IOCなどの各形成領域が配置されている。

50

## 【0013】

なお本実施の形態の半導体装置は、半導体チップに限定されず、ウエハ状態であってもよく、また封止樹脂で封止されたパッケージ状態であってもよい。

## 【0014】

図2に示されるように、本実施の形態の半導体装置は、高耐圧CMOS(Complementary Metal Oxide Semiconductor)トランジスタと、ロジックCMOSトランジスタと、バイポーラトランジスタとを含んでいる。

## 【0015】

高耐圧CMOSトランジスタは、nチャネル型LD(Laterally Diffused)MOSトランジスタLNTと、pチャネル型LDMOSトランジスタLPTとを有している。またロジックCMOSトランジスタは、nチャネル型MOSトランジスタNTRと、pチャネル型MOSトランジスタPTRとを有している。

10

## 【0016】

以下において、nチャネル型LDMOSトランジスタをnLDMOSトランジスタと記載し、pチャネル型LDMOSトランジスタをpLDMOSトランジスタと記載する。またnチャネル型MOSトランジスタをnMOSトランジスタと記載し、pチャネル型MOSトランジスタをpMOSトランジスタと記載する。

## 【0017】

各トランジスタは、半導体基板SUBの主表面MSに形成されている。各トランジスタの形成領域は、DTI(Deep Trench Isolation)により電気的に分離されている。DTIは、半導体基板SUBの主表面MSに形成された溝DTRと、その溝DTR内を埋め込む絶縁膜BILとを有している。

20

## 【0018】

ロジックCMOSトランジスタの形成領域には、半導体基板SUBの基板領域SB上に、p型ウエル領域PWLと、n型ウエル領域NWLとが並んで配置されている。p型ウエル領域PWLにはnMOSトランジスタNTRが配置されており、n型ウエル領域NWLにはpMOSトランジスタPTRが配置されている。

## 【0019】

nMOSトランジスタNTRの形成領域とpMOSトランジスタPTRの形成領域とは、STI(Shallow Trench Isolation)により電気的に分離されている。STIは、半導体基板SUBの主表面MSに形成された分離溝TNCと、その分離溝TNC内を埋め込む分離絶縁膜SISとを有している。

30

## 【0020】

STIの分離溝TNCは、DTIの溝DTRよりも主表面MSから浅く配置されている。STIの分離溝TNCは、p型ウエル領域PWLおよびn型ウエル領域NWLよりも浅く配置されている。

## 【0021】

上記nMOSトランジスタNTRは、n<sup>+</sup>ソース領域SCと、n<sup>+</sup>ドレイン領域DCと、ゲート絶縁膜GIと、ゲート電極GEとを有している。n<sup>+</sup>ソース領域SCとn<sup>+</sup>ドレイン領域DCとは、互いに間隔をあけて半導体基板SUBの主表面MSに配置されている。ゲート電極GEは、n<sup>+</sup>ソース領域SCとn<sup>+</sup>ドレイン領域DCとに挟まれる半導体基板SUBの主表面MS上にゲート絶縁膜GIを介在して配置されている。

40

## 【0022】

上記pMOSトランジスタPTRは、p<sup>+</sup>ソース領域SCと、p<sup>+</sup>ドレイン領域DCと、ゲート絶縁膜GIと、ゲート電極GEとを有している。p<sup>+</sup>ソース領域SCとp<sup>+</sup>ドレイン領域DCとは、互いに間隔をあけて半導体基板SUBの主表面MSに配置されている。ゲート電極GEは、p<sup>+</sup>ソース領域SCとp<sup>+</sup>ドレイン領域DCとに挟まれる半導体基板SUBの主表面MS上にゲート絶縁膜GIを介在して配置されている。

## 【0023】

バイポーラトランジスタの配置領域には、半導体基板SUBの基板領域SB上に、n<sup>+</sup>

50

埋め込み領域 B L が配置されている。その n<sup>+</sup>埋め込み領域 B L 上には、 n<sup>-</sup>ウエル領域 H W L が配置されている。その n<sup>-</sup>ウエル領域 H W L 上には、 p 型ウエル領域 P W L と n 型ウエル領域 N W L とが配置されている。 p 型ウエル領域 P W L と n 型ウエル領域 N W L とは、 n<sup>-</sup>ウエル領域 H W L の一部を間に挟んで互いに隣り合っている。

【 0 0 2 4 】

p 型ウエル領域 P W L には p<sup>+</sup>ベース領域 B C と n<sup>+</sup>エミッタ領域 E C とが配置されている。 n 型ウエル領域 N W L には n<sup>+</sup>コレクタ領域 C C が配置されている。 p<sup>+</sup>ベース領域 B C 、 n<sup>+</sup>エミッタ領域 E C および n<sup>+</sup>コレクタ領域 C C によりバイポーラトランジスタ B T R が構成されている。

【 0 0 2 5 】

10

p<sup>+</sup>ベース領域 B C と n<sup>+</sup>エミッタ領域 E C との間、 n<sup>+</sup>エミッタ領域 E C と n<sup>+</sup>コレクタ領域 C C との間には S T I が配置されている。これにより、 p<sup>+</sup>ベース領域 B C 、 n<sup>+</sup>エミッタ領域 E C および n<sup>+</sup>コレクタ領域 C C の各々は、互いに電気的に分離されている。

【 0 0 2 6 】

各不純物領域 ( n<sup>+</sup>ソース領域 S C 、 n<sup>+</sup>ドレイン領域 D C 、 p<sup>+</sup>ベース領域 B C 、 n<sup>+</sup>エミッタ領域 E C 、 n<sup>+</sup>コレクタ領域 C C ) には、配線層 I N C が電気的に接続されている。

【 0 0 2 7 】

具体的には、半導体基板 S U B の主表面 M S 上を覆うように層間絶縁膜 ( 図示せず ) が配置されている。この層間絶縁膜には、各不純物領域に達するコンタクトホール C N が配置されている。このコンタクトホール C N 内には、プラグ導電層 P L が埋め込まれている。層間絶縁膜上には、プラグ導電層 P L に接するように配線層 I N C が配置されている。これにより配線層 I N C は、プラグ導電層 P L を介在して各不純物領域に電気的に接続されている。

20

【 0 0 2 8 】

高耐圧 C M O S トランジスタの p L D M O S トランジスタについては、図 3 および図 4 を用いて以下に説明する。

【 0 0 2 9 】

図 3 および図 4 に示されるように、 p L D M O S トランジスタの配置領域には、半導体基板 S U B の基板領域 S B 上に、 n<sup>+</sup>埋め込み領域 B L が配置されている。その n<sup>+</sup>埋め込み領域 B L 上には、 n<sup>-</sup>ウエル領域 H W L ( 第 1 ウエル領域 ) が配置されている。その n<sup>-</sup>ウエル領域 H W L 上には、 p<sup>-</sup>ドリフト領域 D F T と n 型ウエル領域 N W L ( 第 2 ウエル領域 ) とが配置されている。 n<sup>-</sup>ウエル領域 H W L は、 n 型ウエル領域 N W L の n 型不純物濃度よりも低い n 型不純物濃度を有している。

30

【 0 0 3 0 】

p<sup>-</sup>ドリフト領域 D F T と n 型ウエル領域 N W L とは、 p n 接合を構成するように互いに隣り合っている。 p<sup>-</sup>ドリフト領域 D F T と n 型ウエル領域 N W L とにより構成される p n 接合は半導体基板 S U B の主表面 M S から深さ方向に沿って延びている。

【 0 0 3 1 】

半導体基板 S U B の主表面 M S には S T I が配置されている。この S T I は、分離溝 T N C と、分離絶縁膜 S I S とを有している。分離溝 T N C は、 p<sup>-</sup>ドリフト領域 D F T に配置されている。つまり p<sup>-</sup>ドリフト領域 D F T は、分離溝 T N C の周囲を取り囲むとともに、分離溝 T N C の下側に位置している。分離絶縁膜 S I S は、分離溝 T N C を埋め込んでいる。分離絶縁膜 S I S の上面には、凹部 H L が配置されている。この凹部 H L の底面は分離絶縁膜 S I S 内に位置している。つまり凹部 H L の底部は p<sup>-</sup>ドリフト領域 D F T に達していない。

40

【 0 0 3 2 】

n 型ウエル領域 N W L 内の主表面 M S には、 p<sup>+</sup>ソース領域 S C と、 n<sup>+</sup>コンタクト領域 W C とが配置されている。 p<sup>+</sup>ソース領域 S C と n<sup>+</sup>コンタクト領域 W C とは、互いに隣接している。 p<sup>+</sup>ソース領域 S C は、 n 型ウエル領域 N W L および n<sup>+</sup>コンタクト領域 W C の

50

各々と p-n 接合を構成している。n<sup>+</sup>コンタクト領域 W C は、n 型ウエル領域 N W L の n 型不純物濃度よりも高い n 型不純物濃度を有している。

【 0 0 3 3 】

p<sup>-</sup>ドリフト領域 D F T 内の主表面 M S には、p<sup>+</sup>ドレイン領域 D C が配置されている。p<sup>+</sup>ドレイン領域 D C は、分離溝 T N C に隣接している。p<sup>+</sup>ドレイン領域 D C は、p<sup>-</sup>ドリフト領域 D F T の p 型不純物濃度よりも高い p 型不純物濃度を有している。p<sup>+</sup>ドレイン領域 D C は、p<sup>+</sup>ソース領域 S C との間で分離溝 T N C を挟んでいる。

【 0 0 3 4 】

p<sup>+</sup>ソース領域 S C と p<sup>-</sup>ドリフト領域 D F T とに挟まれる主表面 M S の上にゲート絶縁膜 G I を介在してゲート電極 G E が配置されている。ゲート電極 G E は、p<sup>+</sup>ソース領域 S C と p<sup>-</sup>ドリフト領域 D F T とに挟まれる主表面 M S と絶縁されながら対向している。 10

【 0 0 3 5 】

ゲート電極 G E は、S T I の分離絶縁膜 S I S 上に乗り上げており、かつ分離絶縁膜 S I S の凹部 H L 内を埋め込んでいる。ゲート電極 G E は、凹部 H L 内を埋め込む部分からさらにドレイン領域 D C 側に延在している。このゲート電極 G E は、分離絶縁膜 S I S を介在して p<sup>-</sup>ドリフト領域 D F T および n<sup>-</sup>ウエル領域 H W L の各々と対向している。

【 0 0 3 6 】

p<sup>-</sup>ドリフト領域 D F T の下側には、凹部 H L の真下に位置する部分を有するよう n 型不純物領域 N H ( 第 1 不純物領域 ) が配置されている。n 型不純物領域 N H は、p<sup>-</sup>ドリフト領域 D F T に接していてもよいが、p<sup>-</sup>ドリフト領域 D F T に接していなくてもよい。 20

【 0 0 3 7 】

図 5 に示されるように、n 型不純物領域 N H は、たとえば  $1 \times 10^{17} \text{ cm}^{-3} \sim 6 \times 10^{17} \text{ cm}^{-3}$  の n 型不純物濃度 C A を有している。一方、n<sup>-</sup>ウエル領域 H W L は、たとえば  $5 \times 10^{15} \text{ cm}^{-3}$  の n 型不純物濃度 C B を有している。n 型不純物領域 N H と n<sup>-</sup>ウエル領域 H W L との境界は、たとえば  $1 \times 10^{16} \text{ cm}^{-3}$  の n 型不純物濃度を有する部分である。

【 0 0 3 8 】

図 6 に示されるように、本開示において凹部 H L の真下とは、凹部 H L の底面から分離溝 T N C の底面までの距離 H と同じ寸法 H だけ凹部 H L を平面視で拡大した領域 R D B ( 図 3 の破線で示す領域 ) 内の真下領域を意味する。 30

【 0 0 3 9 】

ここで、凹部 H L のドレイン領域 D C 側の端部 H L D から上記寸法 H 分だけドレイン領域 D C 側の位置を位置 P 1 とする。このとき、n 型不純物領域 N H のドレイン領域 D C 側の端部 N H D は、位置 P 1 よりもソース領域 S C 側に位置している。

【 0 0 4 0 】

また、凹部 H L のソース領域 S C 側の端部 H L S から上記寸法 H 分だけソース領域 S C 側の位置を位置 P 2 とする。このとき、n 型不純物領域 N H のソース領域 S C 側の端部 N H S は、位置 P 2 よりもドレイン領域 D C 側に位置していることが好ましい。

【 0 0 4 1 】

また n 型不純物領域 N H は凹部 H L の真下にのみ位置していることが好ましい。具体的には、n 型不純物領域 N H は、上記領域 R D B 内に配置されており、平面視においてこの領域 R D B からはみださないことが好ましい。なお平面視とは、たとえば図 3 に示されるように半導体基板 S U B の主表面 M S に対して直交する方向から見た視点を意味する。 40

【 0 0 4 2 】

また、n 型不純物領域 N H のソース領域 S C 側の端部 N H S は、分離溝 T N C のソース領域 S C 側の端部 T N C S よりもドレイン領域 D C 側に位置している。また n 型不純物領域 N H のソース領域 S C 側の端部 N H S は、p<sup>-</sup>ドリフト領域 D F T のソース領域 S C 側の端部 D F T S よりもドレイン領域 D C 側に位置している。

【 0 0 4 3 】

10

20

30

40

50

しかし図7に示されるように、n型不純物領域N Hのソース側端部N H Sは、分離溝T N Cのソース領域S C側の端部T N C Sよりもソース領域S C側に位置していてもよい。またn型不純物領域N Hのソース側端部N H Sは、p<sup>+</sup>ドリフト領域D F Tのソース領域S C側の端部D F T Sよりもソース領域S C側に位置していてもよい。

【0044】

図4に示されるように、ソース領域S Cからドレイン領域D Cへ向かう方向(ソース-ドレイン方向)における分離溝T N Cの長さはL dである。凹部H Lは、分離溝T N Cのソース領域S C側の端部T N C Sから、上記長さL dの3分の1の寸法の範囲内に位置している。

【0045】

具体的には、凹部H Lのドレイン領域D C側の端部H L Dと分離溝T N Cのソース領域S C側の端部T N C Sとの間の寸法L hは、上記長さL dの3分の1以下である。

【0046】

またn型不純物領域N Hも、分離溝T N Cのソース領域S C側の端部T N C Sから、分離溝T N Cの長さL dの3分の1の寸法の範囲内に位置している。

【0047】

具体的には、n型不純物領域N Hのドレイン領域D C側の端部N H Dと分離溝T N Cのソース領域S C側の端部T N C Sとの間の上記ソース-ドレイン方向の寸法は、上記長さL dの3分の1以下である。

【0048】

またn型不純物領域N Hのソース領域S C側の端部N H Sと分離溝T N Cのソース領域S C側の端部T N C Sとの間の上記ソース-ドレイン方向の寸法は、上記長さL dの3分の1以下である。

【0049】

また凹部H Lのソース領域S C側の端部H L Sと分離溝T N Cのソース領域S C側の端部T N C Sとの間の寸法L sは、ゲート絶縁膜G Iの膜厚以上である。

【0050】

半導体基板S U Bの主表面M S上には、層間絶縁膜I Sが配置されている。層間絶縁膜I Sには、複数のコンタクトホールC N 1、C N 2、C N 3が配置されている。コンタクトホールC N 1は、p<sup>+</sup>ソース領域S Cおよびn<sup>+</sup>コンタクト領域W Cの双方に達している。コンタクトホールC N 2は、ゲート電極G Eに達している。コンタクトホールC N 3は、p<sup>+</sup>ドレイン領域D Cに達している。

【0051】

各コンタクトホールC N 1、C N 2、C N 3の各々には、プラグ導電層P Lが埋め込まれている。層間絶縁膜I S上には複数の配線層I N Cが配置されている。複数の配線層の各々はプラグ導電層P Lに接している。

【0052】

これにより一の配線層I N Cは、プラグ導電層P Lを介在してp<sup>+</sup>ソース領域S Cおよびn<sup>+</sup>コンタクト領域W Cの双方に電気的に接続されている。他の配線層I N Cは、プラグ導電層P Lを介在してゲート電極G Eに電気的に接続されている。さらに他の配線層I N Cは、プラグ導電層P Lを介在してp<sup>+</sup>ドレイン領域D Cに電気的に接続されている。

【0053】

次に、本実施の形態の製造方法について図8～図15を用いて説明する。

図8に示されるように、p<sup>+</sup>基板領域S B上にn<sup>-</sup>ウエル領域H W Lが形成される。n<sup>-</sup>ウエル領域H W L上にn型ウエル領域N W Lとp型ドリフト領域D F Tとが形成される。これにより、p<sup>+</sup>基板領域S B、n<sup>-</sup>ウエル領域H W L、n型ウエル領域N W Lおよびp型ドリフト領域D F Tを内部に有する半導体基板S U Bが準備される。

【0054】

図9に示されるように、半導体基板S U Bの主表面上に、たとえばシリコン酸化膜となるゲート絶縁膜G Iが形成される。ゲート絶縁膜G Iは、たとえば数μm～数十μmの

10

20

30

40

50

膜厚で形成される。このゲート絶縁膜 G I 上に、たとえば不純物が導入された多結晶シリコン（ドープドポリシリコン）よりなる導電膜 G E 1 が形成される。この導電膜 G E 1 上に、たとえばシリコン窒化膜よりなるハードマスク層 H M が形成される。導電膜 G E 1 およびハードマスク層 H M の各々は、たとえば数十 nm の膜厚で形成される。

【0055】

この後、通常の写真製版技術およびエッティング技術によりハードマスク層 H M がパターニングされる。このパターニングされたハードマスク層 H M をマスクとして、導電膜 G E 1、ゲート絶縁膜 G I および半導体基板 S U B がエッティングされる。このエッティングにより、半導体基板 S U B の主表面 M S に分離溝 T N C が形成される。

【0056】

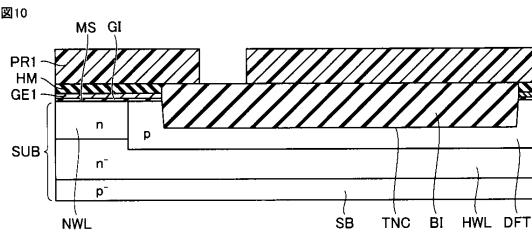

図 10 に示されるように、分離溝 T N C 内を埋め込むように、たとえばシリコン酸化膜よりなる絶縁膜 B I（埋込絶縁膜）が形成される。この絶縁膜 B I の形成においては、たとえば分離溝 T N C 内を埋め込むように半導体基板 S U B の主表面全体上に絶縁膜 B I が形成される。この後、たとえば CMP（Chemical Mechanical Polishing）でハードマスク層 H M の表面が露出するまで絶縁膜 B I が研磨される。これにより、絶縁膜 B I が分離溝 T N C 内のみに残存される。

【0057】

この後、通常の写真製版技術により、フォトレジストパターン P R 1 が形成される。このフォトレジストパターン P R 1 は、絶縁膜 B I の一部表面を露出する開口を有する。このフォトレジストパターン P R 1 をマスクとして絶縁膜 B I がエッティングされる。このエッティングの後、フォトレジストパターン P R 1 がたとえばアッシングなどにより除去される。

【0058】

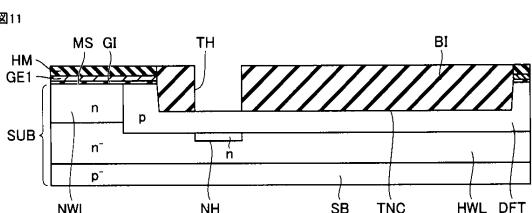

図 11 に示されるように、上記のエッティングにより絶縁膜 B I を貫通して p 型ドリフト領域 D F T に達する貫通孔 T H が絶縁膜 B I に形成される。この貫通孔 T H を通じて半導体基板 S U B に n 型の不純物が注入される。n 型不純物のイオン注入の条件は、たとえば注入エネルギーが数百 keV ~ 数 MeV で、ドーズ量が  $10^{12} \sim 10^{13} \text{ cm}^{-2}$  である。この n 型不純物の注入により、p 型ドリフト領域 D F T の下側であって貫通孔 T H の真下領域に n 型不純物領域 N H が形成される。

【0059】

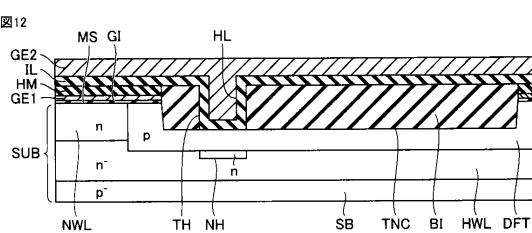

図 12 に示されるように、貫通孔 T H の内壁面を覆い、かつハードマスク層 H M および絶縁膜 B I の各上面を覆うように、たとえばシリコン酸化膜よりなる絶縁膜 I L（被覆絶縁膜）が形成される。絶縁膜 I L は、たとえば貫通孔 T H の深さの 1 / 3 程度の膜厚で形成される。貫通孔 T H の内壁面を覆う絶縁膜 I L の上面により凹部 H L の内壁面が構成される。

【0060】

この後、ドープドポリシリコンよりなる導電膜 G E 2 が、凹部 H L 内を埋め込むように、かつ絶縁膜 I L の上面を覆うように形成される。導電膜 G E 2 は、たとえば数百 nm の膜厚で形成される。この後、たとえば CMP で絶縁膜 I L の表面が露出するまで導電膜 G E 2 が研磨される。

【0061】

図 13 に示されるように、上記の CMP により凹部 H L の内部にのみ導電膜 G E 2 が残存される。この後、絶縁膜 I L の一部およびハードマスク層 H M がたとえばエッティングにより除去される。

【0062】

図 14 に示されるように、上記エッティング除去により導電膜 G E 1 の表面が露出する。また上記エッティング除去により絶縁膜 I L は貫通孔 T H 内にのみ残存される。この貫通孔 T H 内に残存する絶縁膜 I L と絶縁膜 B I とにより分離絶縁膜 S I S が形成される。

【0063】

半導体基板 S U B の主表面 M S 上の全面に、たとえばドープドポリシリコンよりなる導

10

20

30

40

50

電膜 G E 3 が形成される。導電膜 G E 3 は、たとえば数十 nm の膜厚で形成される。この後、通常の写真製版技術およびエッチング技術により導電膜 G E 3、G E 1 がパターニングされる。これにより、導電膜 G E 1、G E 2、G E 3 よりなるゲート電極 G E が形成される。

【 0 0 6 4 】

図 1 5 に示されるように、ゲート電極 G E の側壁に側壁絶縁膜 S W が形成される。この後、イオン注入などにより半導体基板 S U B の主表面 M S に n 型不純物および p 型不純物が注入される。これにより半導体基板 S U B の主表面 M S に p<sup>+</sup>ソース領域 S C、p<sup>+</sup>ドレイン領域 D C および n<sup>+</sup>コンタクト領域 W C が形成される。

【 0 0 6 5 】

図 4 に示されるように、層間絶縁膜 I S、プラグ導電層 P L、配線層 I N C などが形成されることにより、本実施の形態の半導体装置が製造される。

【 0 0 6 6 】

なお、図 1 5 における導電膜 G E 1、G E 2、G E 3 は、図 4 において 1 つのゲート電極 G E として示されている。また図 1 5 における絶縁膜 I L、B I は、図 4 において 1 つの分離絶縁膜 S I S として示されている。また、図 1 5 における側壁絶縁膜 S W は図 4 において省略されている。

【 0 0 6 7 】

また図 2 における n L D M O S トランジスタ L N T は、上記 p L D M O S トランジスタ L P T とは逆導電型の構成を有している。具体的には、n<sup>+</sup>埋め込み領域 B L 上に、p<sup>+</sup>ウエル領域 H W L (第 1 ウエル領域) が配置されている。その p<sup>+</sup>ウエル領域 H W L 上には、n<sup>-</sup>ドリフト領域 D F T と p 型ウエル領域 P W L (第 2 ウエル領域) とが配置されている。p 型ウエル領域 P W L 内の主表面 M S には、n<sup>+</sup>ソース領域 S C と、p<sup>+</sup>コンタクト領域 W C とが形成されている。n<sup>-</sup>ドリフト領域 D F T 内の主表面 M S には、n<sup>+</sup>ドレイン領域 D C が形成されている。n<sup>-</sup>ドリフト領域 D F T の下側には、凹部 H L の真下に位置する部分を有するように p 型不純物領域 P H (第 1 不純物領域) が配置されている。

【 0 0 6 8 】

次に、本実施の形態の作用効果について、図 4 における n 型不純物領域 N H を有しない比較例と対比して説明する。

【 0 0 6 9 】

B i C - D M O S (Bipolar Complementary Metal Oxide Semiconductor) 分野においては、図 2 に示されるように、L D M O S トランジスタ、C M O S トランジスタおよびバイポーラトランジスタが混載される。このような分野においても、デザインスケーリングが進んできている。これにより従来の L O C O S (LoCal Oxidation of Silicon) に代えて S T I が用いられるようになってきている。

【 0 0 7 0 】

この場合、L D M O S トランジスタのドリフト領域にも S T I が用いられることになる。S T I においては、分離溝のコーナー部の形状がシャープである。このため、ドレインに高電圧が印加された場合に電界が分離溝のコーナー部に集中しやすい。この電界集中により、S T I の端部でインパクトイオン化が発生しやすい。インパクトイオン化により発生した電子・ホール対は、界面準位を生成したり、散乱により酸化膜に注入される。これによりホットキャリア変動が大きくなるという問題が顕著になる。特に p L D M O S トランジスタにおいては、ゲート絶縁膜に電子が注入されることによりゲート絶縁膜が絶縁破壊を生じる。

【 0 0 7 1 】

そこで本発明者は、図 4 における本実施の形態の構成と、図 4 における n 型不純物領域 N H を有しない比較例の構成について、デバイス・シミュレーションによってインパクトイオン化の抑制効果について調べた。その結果を図 1 6 および図 1 7 に示す。

【 0 0 7 2 】

図 1 6 は比較例における半導体装置のインパクトイオン化率分布を示しており、図 1 7

10

20

30

40

50

は本実施の形態における半導体装置のインパクトイオン化率分布を示している。この結果から、比較例においては、図16に示すようにSTIのソース領域側の下端においてインパクトイオン化率が高くなっていることがわかる。これに対して本実施の形態においては、図17に示すようにSTIのソース領域側の下端においてインパクトイオン化率が比較例よりも低くなっていることがわかる。

【0073】

また本発明者は、図16および図17の各々のA-A線に沿う電界強度と、インパクトイオン化発生率とを調べた。その結果を図18および図19に示す。

【0074】

図18は図16および図17のA-A線に沿う電界強度を示し、図19は図16および図17のA-A線に沿うインパクトイオン化発生率を示している。図18および図19の結果から、本実施の形態においては比較例よりも電界強度およびインパクトイオン化発生率の双方が低くなっていることがわかる。特にSTIのソース領域側の下端付近において、本実施の形態の電界強度およびインパクトイオン化発生率が、比較例よりも低くなっていることがわかる。

【0075】

さらに本発明者は、本実施の形態と比較例との各々におけるオン抵抗 $R_{s\,p}$ とゲート電流 $I_{g\,s}$ との関係と、オフ耐圧 $BV_{o\,f\,f}$ とゲート電流 $I_{g\,s}$ との関係とについて調べた。その結果を図20および図21に示す。

【0076】

図20は本実施の形態と比較例との各々におけるオン抵抗 $R_{s\,p}$ とゲート電流 $I_{g\,s}$ との関係を示し、図21は本実施の形態と比較例との各々におけるオフ耐圧 $BV_{o\,f\,f}$ とゲート電流 $I_{g\,s}$ との関係を示している。図20および図21の結果から、本実施の形態においては比較例に比べて、オン抵抗 $R_{s\,p}$ が1~2%増加しているものの、オフ耐圧 $BV_{o\,f\,f}$ を維持したままゲート電流 $I_{g\,s}$ を低下できることがわかる。

【0077】

ここでゲート電流 $I_{g\,s}$ とは、半導体基板SUBとゲート電極GEとの間にゲート絶縁膜GIなどを介在して流れる電流のことである。このため、ゲート電流 $I_{g\,s}$ が小さいとは、ゲート電極GEに半導体基板SUBから注入されるキャリアの量が少ないと意味する。よって、ゲート電流 $I_{g\,s}$ が低減されるとの上記結果から、本実施の形態では比較例よりもゲート電極GE内へのホットキャリアの注入が抑制できていることがわかる。

【0078】

加えて本発明者は、本実施の形態と比較例との各々において、測定素子に対し一定のストレスを与えたときの半導体基板内の電位分布について調べた。その結果を図22および図23に示す。

【0079】

図22は比較例における半導体装置の等電位線を示し、図23は本実施の形態における半導体装置の等電位線を示している。このシミュレーションにおいては、オン耐圧80Vの素子に対し、ゲート電圧 $V_{g\,s}$ を-1.3Vとし、かつドレイン電圧 $V_{d\,s}$ を-80Vとして電位分布を観察した。

【0080】

図22および図23の結果から、比較例においてはSTIのソース領域側の下端において-10Vとなっているのに対し、本実施の形態においてはSTIのソース領域側の下端において-8Vとなっている。また本実施の形態においては、比較例よりもSTIのソース領域側の端部近傍において等電位線の間隔が広がっており、電界が緩和されていることがわかる。

【0081】

これらの結果から、本実施の形態においては、n型不純物領域NH(図4)が配置されたことによって、STI端部における電界が緩和され、それによりインパクトイオン化が抑えられたことでホットキャリアのゲート電極GEへの注入がさらに抑制されたと考えら

10

20

30

40

50

れる。

【0082】

以上より、本実施の形態においては図4に示すようにp型ドリフト領域DFTの下側であって凹部HLの真下領域にn型不純物領域NHが配置されている。このため、上記のとおりオフ耐圧BVoffを維持したままゲート電極GEへのホットキャリアの注入がさらに抑制でき、その結果、ゲート電流Igを抑制することができる。

【0083】

また本実施の形態において凹部HLの真下領域にのみn型不純物領域NHが配置されている場合には、ゲート電極GEへのホットキャリアの注入を抑制しつつ、RESURF(REDuced SURface Field)効果により高耐圧を得ることもできる。以下、そのことを説明する。

【0084】

図4の構成において、仮に凹部HLが分離絶縁膜SISに設けられておらず、かつn型不純物領域NHが分離溝TNCの真下領域の全体に配置されている場合について想定する。この場合、n型不純物領域NHが分離溝TNCの真下領域の全体に配置されているため、p<sup>-</sup>ドリフト領域DFTとn<sup>-</sup>ウエル領域HWLとの横方向の接合により得られるRESURF効果が得られなくなる。この結果、電界集中が生じやすくなり、耐圧が低下する。

【0085】

係る耐圧の低下を抑えるためには、p<sup>-</sup>ドリフト領域DFTのp型不純物濃度を高くする必要がある。しかし p<sup>-</sup>ドリフト領域DFTのp型不純物濃度を高くすると、STIの端部近傍での電界集中が促進される。これによりゲート電極GEへのホットキャリアの注入が促進される。

【0086】

これに対して本実施の形態では、凹部HLの真下領域にのみn型不純物領域NHが配置されている。このため p<sup>-</sup>ドリフト領域DFTとn<sup>-</sup>ウエル領域HWLとの横方向の接合長さを十分に確保することができる。これにより、RESURF効果によって高耐圧を得ることができる。

【0087】

つまり、空乏層がp<sup>-</sup>ドリフト領域DFTとn<sup>-</sup>ウエル領域HWLとのpn接合部から上下に拡がり、これにより電界分布が均一化され電界集中が緩和される結果、耐圧が向上する。

【0088】

また高耐圧を得るためにp<sup>-</sup>ドリフト領域DFTのp型不純物濃度を高くする必要がない。このため p<sup>-</sup>ドリフト領域DFTのp型不純物濃度を高くした場合に生じるホットキャリア注入促進も生じない。

【0089】

以上より、ゲート電極GEへのホットキャリアの注入を抑制しつつ、RESURF効果により高耐圧を得ることもできる。

【0090】

また本実施の形態においては、n型不純物領域NHは、分離溝TNCのソース領域SC側の端部TNCsから、分離溝TNCの長さLdの3分の1の寸法の範囲内に位置している。このような範囲内にn型不純物領域NHが位置していることにより、上述したRESURF効果による高耐圧を維持することができる。

【0091】

また仮に凹部HLのソース領域SC側の端部HLSと分離溝TNCのソース領域SC側の端部TNCsとの間の寸法Lsがゲート絶縁膜GIの膜厚未満である場合、その薄い分離絶縁膜SISの部分を通過してホットキャリアがゲート電極GEに注入されやすくなる。このため上記寸法Lsがゲート絶縁膜GIの膜厚以上であることにより、その薄い分離絶縁膜SISの部分を通じてゲート電極GEにホットキャリアが注入されることが抑制される。

10

20

30

40

50

## 【0092】

またn型不純物領域N Hのソース領域S C側の端部N H Sと分離溝T N Cのソース領域S C側の端部T N C Sとの間の上記ソース-ドレイン方向の寸法が上記分離溝T N Cの長さL dの3分の1以下である。これにより、n型不純物領域N Hによって、ゲート電極G Eへのホットキャリアの注入を十分に抑制することができる。

## 【0093】

また図6に示されるように、n型不純物領域N Hのドレイン領域D C側の端部N H Dは、上記位置P 1よりもソース領域S C側に位置している。これによりゲート電極G Eへのホットキャリアの注入が抑制されるとともに、上記のR E S U R F効果を得ることができる。

10

## 【0094】

また図4に示されるように、n型ウエル領域N W Lよりもn型不純物濃度の低いn<sup>+</sup>ウエル領域がp<sup>+</sup>ドリフト領域D F Tと横方向に沿って接続されてp n接合を構成している。これにより上記のR E S U R F効果を得ることができる。

## 【0095】

## (実施の形態2)

図24に示されるように、本実施の形態の構成は実施の形態1の構成と比較してp型不純物領域P H(第2不純物領域)が追加されている点において異なる。p型不純物領域P Hは、p<sup>-</sup>ドリフト領域D F Tよりも高いp型不純物濃度を有している。このp型不純物領域P Hは、n型不純物領域N Hの濃度ピークよりも低い濃度ピークを有していることが好ましい。

20

## 【0096】

p型不純物領域P Hは、凹部H Lの真下領域に配置されている。p型不純物領域P Hは、p<sup>-</sup>ドリフト領域D F T内に配置されていれば、分離絶縁膜S I Sに接していてもよく、また接していなくてもよい。p型不純物領域P Hは、n型不純物領域N Hと深さ方向に間隔をあけて配置されていることが好ましい。

## 【0097】

p型不純物領域P Hのドレイン領域D C側の端部P H Dは、図6で説明した位置P 1よりもソース領域S C側に位置している。p型不純物領域P Hのソース領域S C側の端部P H Sは、図6で説明した位置P 2よりもドレイン領域D C側に位置していることが好ましい。

30

## 【0098】

またp型不純物領域P Hは、凹部H Lの真下領域のみに配置されていることが好ましい。具体的にはp型不純物領域P Hは、平面視において図3で説明した領域R D B内に配置されており、この領域R D Bからはみださないことが好ましい。

## 【0099】

またp型不純物領域P Hのソース領域S C側の端部P H Sは、分離溝T N Cのソース領域S C側の端部T N C Sよりもドレイン領域D C側に位置している。またp型不純物領域P Hのソース領域S C側の端部P H Sは、p<sup>-</sup>ドリフト領域D F Tのソース側端部D F T Sよりもドレイン領域D C側に位置している。

40

## 【0100】

しかし図7に示すn型不純物領域N Hと同様に、p型不純物領域P Hのソース側端部P H Sは、分離溝T N Cのソース領域S C側の端部T N C Sよりもソース領域S C側に位置していてもよい。またp型不純物領域P Hのソース側端部P H Sは、p<sup>-</sup>ドリフト領域D F Tのソース領域S C側の端部D F T Sよりもソース領域S C側に位置していてもよい。

## 【0101】

またp型不純物領域P Hは、分離溝T N Cのソース領域S C側の端部T N C Sから、ドリフト領域D F Tの長さL dの3分の1の寸法の範囲内に位置している。

## 【0102】

具体的には、p型不純物領域P Hのドレイン領域D C側の端部P H Dと分離溝T N Cの

50

ソース領域 S C 側の端部 T N C S との間の上記ソース - ドレイン方向の寸法は、上記ドリフト領域 D F T の長さ L d の 3 分の 1 以下である。

【 0 1 0 3 】

また p 型不純物領域 P H のソース領域 S C 側の端部 P H S と分離溝 T N C のソース領域 S C 側の端部 T N C S との間の上記ソース - ドレイン方向の寸法は、上記ドリフト領域 D F T の長さ L d の 3 分の 1 以下である。

【 0 1 0 4 】

なお本実施の形態の上記以外の構成は、上述した実施の形態 1 の構成をほぼ同じであるため同一の要素については同一の符号を付し、その説明を繰り返さない。

【 0 1 0 5 】

次に、本実施の形態の半導体装置の製造方法について図 2 5 を用いて説明する。

本実施の形態の製造方法は、まず図 8 ~ 図 1 0 に示す実施の形態 1 の工程と同様の工程を経る。この後、本実施の形態においては図 2 5 に示されるように、絶縁膜 B I の貫通孔 T H を通じて n 型不純物および p 型不純物が半導体基板 S U B に注入される。これにより、n 型不純物領域 N H と p 型不純物領域 P H とが半導体基板 S U B に形成される。

【 0 1 0 6 】

p 型不純物領域 P H を形成するための p 型不純物のイオン注入条件は、たとえばエネルギーが数十 k e V で、ドーズ量が  $10^{11} \sim 10^{12} \text{ c m}^{-2}$  である。この p 型不純物のイオン注入は、注入イオンのノックオンを防ぐため、n 型不純物領域 N H を形成するための n 型不純物のイオン注入よりも先に行われることが好ましい。

【 0 1 0 7 】

この後、本実施の形態の製造方法は、図 1 2 ~ 図 1 5 に示す実施の形態 1 の工程と同様の工程を経る。これにより、図 2 4 に示される本実施の形態の半導体装置が製造される。

【 0 1 0 8 】

次に、本実施の形態の作用効果について説明する。

本発明者は、本実施の形態におけるオン抵抗 R s p およびゲート電流 I g の関係と、オフ耐圧 B V o f f およびゲート電流 I g の関係について調べた。その結果を図 2 6 および図 2 7 に示す。

【 0 1 0 9 】

図 2 6 は本実施の形態と実施の形態 1 と比較例との各々におけるオン抵抗 R s p とゲート電流 I g との関係を示している。また図 2 7 は本実施の形態と実施の形態 1 と比較例との各々におけるオフ耐圧 B V o f f とゲート電流 I g との関係を示している。図 2 6 および図 2 7 の結果から、本実施の形態においては比較例に比べてゲート電流 I g を低減できるとともに、実施の形態 1 に比べて、オン抵抗 R s p をさらに低減できることがわかる。

【 0 1 1 0 】

以上より、本実施の形態によれば、凹部 H L の真下に p 型不純物領域 P H が追加されたことにより、ゲート電流 I g を低減できるとともに、オン抵抗 R s p をさらに低減することができる。

【 0 1 1 1 】

また仮に p 型不純物領域 P H が n 型不純物領域 N H の濃度ピークよりも高い濃度ピークを有する場合、n 型不純物領域 N H による電界緩和の効果が p 型不純物領域 P H により相殺されるおそれがある。

【 0 1 1 2 】

本実施の形態においては、p 型不純物領域 P H は、n 型不純物領域 N H の濃度ピークよりも低い濃度ピークを有している。これにより n 型不純物領域 N H による電界緩和の効果が p 型不純物領域 P H により相殺されることが抑制される。

【 0 1 1 3 】

また p 型不純物領域 P H のドレイン領域 D C 側の端部 P H D は、凹部 H L の底部から分離溝 T N C の底部までの深さ方向の寸法 H 分だけ、凹部 H L からドレイン領域 D C 側へ離れた位置よりもソース領域 S C 側に位置している。これにより、ゲート電極 G E へのホツ

10

20

30

40

50

トキャリアの注入が抑制されるとともに、上記の R E S U R F 効果を得ることができる。

【0114】

(実施の形態3)

図28に示されるように、本実施の形態の半導体装置は、実施の形態1の構成と比較して、凹部H Lが複数個の凹部分H L Pを有している点と、n型不純物領域N Hが複数個のn型領域部分(第1領域部分)N H Pを有している点において異なっている。

【0115】

複数個の凹部分H L Pは、平面視において互いに間隔を隔てて並走するように配置されている。つまり、平面視において複数個の凹部分H L Pはいわゆる短冊状に形成されている。複数個の凹部分H L Pの各々の幅W Aは、複数個の凹部分H L Pのうち互いに隣り合う凹部分H L P間の距離W Bよりも大きい。

【0116】

また複数個のn型領域部分N H Pの各々は、互いに間隔を隔てて配置されている。複数個のn型領域部分N H Pの各々は、複数個の凹部分H L Pの各々の真下領域に配置されている。

【0117】

本実施の形態の上記以外の構成は、実施の形態1の構成とほぼ同じであるため、同一の要素については同一の符号を付し、その説明を繰り返さない。

【0118】

次に、本実施の形態の半導体装置の製造方法について図29～図33を用いて説明する。なお図29～図33においては2つの凹部分H L Pと2つのn型領域部分が示されているが、図24に示されるように3つの凹部分H L Pと3つのn型領域部分が設けられてもよい。

【0119】

本実施の形態の製造方法は、まず図8、図9に示す実施の形態1の工程と同様の工程を経る。この後、本実施の形態においては図29に示されるように、通常の写真製版技術により、フォトレジストパターンP R 2が形成される。このフォトレジストパターンP R 2は、絶縁膜B Iの一部表面を露出する開口を有する。このフォトレジストパターンP R 2をマスクとして絶縁膜B Iがエッチングされる。このエッチングの後、フォトレジストパターンP R 2がたとえばアッシングなどにより除去される。

【0120】

図30に示されるように、上記のエッチングにより絶縁膜B Iを貫通してp型ドリフト領域D F Tに達する複数の貫通孔部T H Pが絶縁膜B Iに形成される。この複数の貫通孔部T H Pを通じて半導体基板S U Bにn型の不純物が注入される。n型不純物のイオン注入の条件は、たとえば注入エネルギーが数百k e V～数M e Vで、ドーズ量が $10^{12} \sim 10^{13} \text{ cm}^{-2}$ である。このn型不純物の注入により、複数の貫通孔部T H Pの各々の真下領域であってp型ドリフト領域D F Tの下側に複数のn型領域部分N H Pが形成される。複数のn型領域部分N H Pによりn型不純物領域N Hが構成される。

【0121】

図31に示されるように、複数の貫通孔部T H Pの各々の内壁面を覆い、かつハードマスク層H Mおよび絶縁膜B Iの各上面を覆うように、たとえばシリコン酸化膜よりなる絶縁膜I Lが形成される。絶縁膜I Lは、たとえば貫通孔部T H Pの深さの1/3程度の膜厚で形成される。貫通孔部T H Pの内壁面を覆う絶縁膜I Lの上面により凹部分H L Pの内壁面が構成される。

【0122】

この後、ドープドポリシリコンよりなる導電膜G E 2が、複数の凹部分H L P内を埋め込むように、かつ絶縁膜I Lの上面上を覆うように形成される。導電膜G E 2は、たとえば数百n mの膜厚で形成される。この後、たとえばC M Pで絶縁膜I Lの表面が露出するまで導電膜G E 2が研磨される。

【0123】

10

20

30

40

50

図32に示されるように、上記のCMPにより複数の凹部分HLPの各々の内部にのみ導電膜GE2が残存される。この後、絶縁膜ILの一部およびハードマスク層HMがたとえばエッティングにより除去される。

【0124】

図33に示されるように、上記エッティング除去により導電膜GE1の表面が露出する。また上記エッティング除去により絶縁膜ILは貫通孔TH内にのみ残存される。この貫通孔IL内に残存する絶縁膜ILと絶縁膜BIとにより分離絶縁膜SISが形成される。

【0125】

半導体基板SUBの主表面MS上の全面に、たとえばドープドポリシリコンよりなる導電膜GE3が形成される。導電膜GE3は、たとえば数十nmの膜厚で形成される。この後、通常の写真製版技術およびエッティング技術により導電膜GE3、GE1がパターニングされる。これにより、導電膜GE1、GE2、GE3よりなるゲート電極GEが形成される。

【0126】

この後、本実施の形態の製造方法は、図15に示す実施の形態1の工程と同様の工程を経る。これにより、図28に示されるのと同等の構成を有する本実施の形態の半導体装置が製造される。

【0127】

次に、本実施の形態の作用効果について図34～図35に示す比較例と対比して説明する。

【0128】

比較例においては、図34に示されるように、幅の広い1つの凹部HLが形成される。この場合、導電膜GE2が形成され、図35に示されるように導電膜GE2がエッチバッカされると、導電膜GE2は凹部HLを埋め込むことができない。この場合、導電膜GE2は、凹部HLの側壁にのみ、サイドウォール形状で残る。

【0129】

これに対して本実施の形態においては、図28に示されるように凹部HLが複数の凹部分HLPを有している。このため、1つの凹部分HLPの幅WAを小さくしつつも、複数の凹部分HLP全体の幅(たとえば $3 \times WA + 2 \times WB$ )を大きく確保することができる。

【0130】

このためゲート電極GEへのホットキャリアの注入を抑制できながら、各凹部分HLPを導電膜GE2で埋め込むことが可能となる。

【0131】

また本実施の形態の製造方法においては、実施の形態1と比較して、フォトマスクを追加することなく複数の凹部分HLPを形成することができる。

【0132】

また凹部HLの幅Lt(図1参照)が大きくなると、電界が緩和されて寿命(TTF)が向上する(以下の論文参照)。このため寿命向上の観点からは凹部HLの幅が大きいことが好ましい。

【0133】

論文:H. Fujii et al., "A Recessed Gate LDMOSFET for Alleviating HCI Effects", Proceedings of the 2016 28th ISPSD, June 12-16, 2016, Prague, Czech Republic, pp.167-170

そこで本実施の形態では、複数の凹部分HLPの各々の幅WAは、複数の凹部分HLPのうちの互いに隣り合う凹部分HLP間の距離WBよりも大きく設定されている。これにより、複数の凹部分HLPの幅WAの合計を可能な限り大きく確保することができる、寿命が向上する。

【0134】

なお、図36に示されるように、実施の形態3の構成に、p型不純物領域PHが追加さ

10

20

30

40

50

れてもよい。p型不純物領域PHは、複数のp型領域部分PHPを有している。複数のp型領域部分PHPの各々は、複数の凹部分HLPの各々の真下領域に配置されている。

【0135】

この変形例は、図30に示す実施の形態3の製造工程に代えて、図37に示すようにn型不純物だけでなく、p型不純物も注入することにより製造される。これ以外の上記変形例の製造方法は、実施の形態3とほぼ同じであるため、その説明は繰り返さない。

【0136】

この変形例においては、複数のp型領域部分PHPを有するp型不純物領域PHが追加されることにより、実施の形態2と同様の作用効果を得ることができる。

【0137】

なお上記の実施の形態1～3においては、pLDMOSトランジスタについて説明したが、本開示は図38に示すようなnLDMOSトランジスタにも適用することができる。この場合においても上記と同様の作用効果を得ることができる。

【0138】

また上記においてはpLDMOSトランジスタおよびnLDMOSトランジスタについて説明した。しかし、本開示はpLDMIS (Laterally Diffused Metal Insulator Semiconductor)トランジスタまたはnLDMISトランジスタのようにゲート絶縁膜GIがシリコン酸化膜以外の材質のものにも同様に適用することができる。

【0139】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【符号の説明】

【0140】

ANA アナログ回路、BC ベース領域、BIL, IL 絶縁膜、BL n<sup>+</sup>埋め込み領域、BTR バイポーラトランジスタ、CH 半導体装置、CN, CN1, CN2, CN3 コンタクトホール、DC ドレイン領域、DFT p型ドリフト領域、DFTS, NHS, PHS, TNCS ソース側端部、HLD, NHD, PHD ドレイン側端部、DRI ドライバ回路、DTR 溝、EC エミッタ領域、GE ゲート電極、GE1, GE2, GE3 導電膜、GI ゲート絶縁膜、HL 凹部、HLP 凹部分、HM ハードマスク層、HWL ウエル領域、INC 配線層、IOC 入出力回路、IS 層間絶縁膜、LC ロジック回路、LNT nLDMOSトランジスタ、LPT pLDMOSトランジスタ、MS 主表面、NH n型不純物領域、NHP n型領域部分、NTR nMOSトランジスタ、NWL n型ウエル領域、P1, P2 位置、PC 電源回路、PDR プリドライバ回路、PH p型不純物領域、PHP p型領域部分、PL プラグ導電層、PR1, PR2 フォトレジスト、PTR pMOSトランジスタ、PWL p型ウエル領域、SB 基板領域、SC ソース領域、SIS 分離絶縁膜、SUB 半導体基板、SW 側壁絶縁膜、TH 貫通孔、THP 貫通孔部、TNC 分離溝、WC コンタクト領域。

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図26】

【図25】

【図27】

【図28】

【図30】

【図29】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

---

フロントページの続き

| (51)Int.Cl. |                   | F I    |            |

|-------------|-------------------|--------|------------|

| H 01 L      | 27/088 (2006.01)  | H 01 L | 27/088 B   |

| H 01 L      | 21/8248 (2006.01) | H 01 L | 27/088 C   |

| H 01 L      | 27/06 (2006.01)   | H 01 L | 27/06 101U |

| H 01 L      | 21/331 (2006.01)  | H 01 L | 29/72 P    |

| H 01 L      | 29/732 (2006.01)  |        |            |

(56)参考文献 特開2015-162581(JP, A)

特開2009-278100(JP, A)

特開2005-183633(JP, A)

特表2003-501837(JP, A)

国際公開第2014/061254(WO, A1)

米国特許出願公開第2015/0243777(US, A1)

米国特許出願公開第2009/0283825(US, A1)

中国特許出願公開第104882481(CN, A)

韓国公開特許第10-2015-0034234(KR, A)

## (58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 78

H 01 L 21 / 336

H 01 L 21 / 331

H 01 L 21 / 8234

H 01 L 21 / 8238

H 01 L 21 / 8248

H 01 L 27 / 06

H 01 L 27 / 088

H 01 L 27 / 092

H 01 L 29 / 732