(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-54192

(P2011-54192A)

(43) 公開日 平成23年3月17日(2011.3.17)

(51) Int.Cl.

**G06T 1/20** (2006.01)

**G06F 9/38** (2006.01)

**G06T 5/20** (2006.01)

F 1

G06T 1/20

G06F 9/38

G06T 5/20

370B

A

テーマコード(参考)

5B013

5B057

審査請求 有 請求項の数 10 O L (全 9 頁)

(21) 出願番号 特願2010-232722 (P2010-232722)

(22) 出願日 平成22年10月15日 (2010.10.15)

(62) 分割の表示 特願2006-509948 (P2006-509948)

の分割

原出願日 平成16年4月13日 (2004.4.13)

(31) 優先権主張番号 10/413,378

(32) 優先日 平成15年4月15日 (2003.4.15)

(33) 優先権主張国 米国(US)

(71) 出願人 500575824

ハネウェル・インターナショナル・インコ

ーポレーテッド

アメリカ合衆国ニュージャージー州079

62-2245, モーリスタウン, コロン

ビア・ロード 101, ピー・オー・ボッ

クス 2245

(74) 代理人 100140109

弁理士 小野 新次郎

(74) 代理人 100089705

弁理士 社本 一夫

(74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100080137

弁理士 千葉 昭男

最終頁に続く

(54) 【発明の名称】 画像分割システム及び方法

## (57) 【要約】

【課題】デジタル信号処理技術を改良するため、カメラから取り込んだ画像のデジタル信号処理を促進、改善する。着目した対象物と背景を区別するなどの画像分割を行うのに適している。

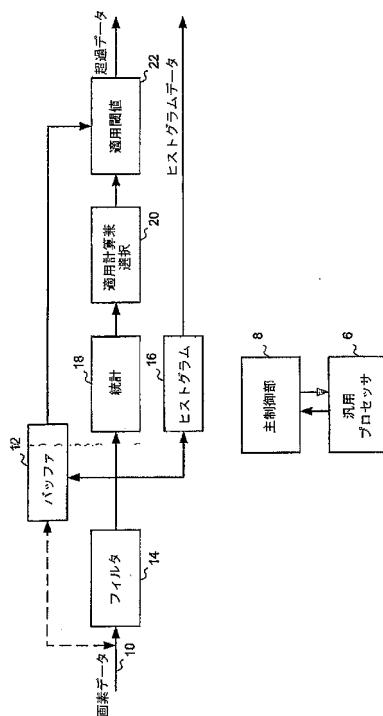

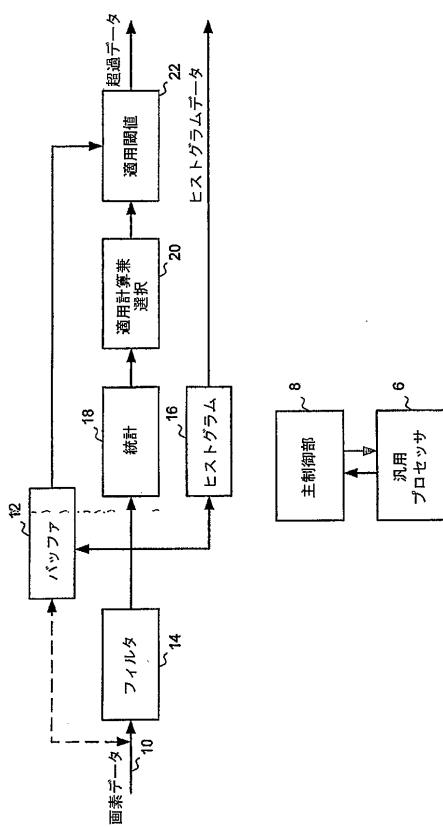

【解決手段】画像分割装置は、FPGAなどのデバイスで好適に集積化して実現され、画素データを記憶するバッファメモリ12と、バッファメモリと通信し係数がプログラム可能でデジタルフィルタ14と、バッファメモリと通信して画素データのヒストグラムを生成するヒストグラム生成モジュール16と、バッファメモリと通信して画素データに関する統計を作成する統計生成モジュール18と、複数の閾値のなかから1つを選択する閾値選択モジュール20と選択された閾値をバッファメモリに記憶されたデータに適用して選択された閾値より大きな超過データを生成する適用閾値モジュール22を備える。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

画素データを記憶可能なバッファメモリと、

前記バッファメモリと通信して画素データのヒストグラムを生成可能なヒストグラム生成モジュールと、

前記バッファメモリと通信して画素データに関する統計を生成可能な統計生成モジュールと、

複数の閾値のなかから 1 つを選択する閾値選択モジュールと前記選択された閾値を前記バッファメモリに記憶されたデータに適用する適用閾値モジュールと、

前記バッファメモリ、ヒストグラム生成モジュール、統計生成モジュール、閾値選択モジュール、及び適用閾値モジュールの少なくともひとつをレジスタを更新して前記バッファメモリ、ヒストグラム生成モジュール、統計生成モジュール、閾値選択モジュール、及び適用閾値モジュールの少なくともひとつを通るデータの再フローを生じさせることにより、前記バッファメモリ、ヒストグラム生成モジュール、統計生成モジュール、閾値選択モジュール、及び適用閾値モジュールをそれぞれ制御する制御モジュールと、を備え、

前記データの部分は、前記再フローのデータの前記部分に対して生成された前記統計に基づいて少なくとも 2 回、前記バッファメモリ、ヒストグラム生成モジュール、統計生成モジュール、閾値選択モジュール、及び適用閾値モジュールの少なくともひとつに渡され、

ヒストグラム、及び前記選択された閾値より大きな超過データが下流の汎用プロセッサに供給される、デジタル信号処理装置。

## 【請求項 2】

さらにフィルタを備える、請求項 1 に記載の装置。

## 【請求項 3】

前記フィルタは空間フィルタである、請求項 2 に記載の装置。

## 【請求項 4】

前記フィルタは係数がプログラム可能である、請求項 2 に記載の装置。

## 【請求項 5】

前記フィルタは平滑化フィルタとエッジ検出フィルタのうち少なくとも 1 つとして動作可能である、請求項 2 に記載の装置。

## 【請求項 6】

画素データを記憶し、

プログラム可能なフィルタ係数を制御、設定し、前記データのデジタルフィルタリングを少なくとも 1 回行うステップと、

前記データのヒストグラムを生成するステップと、

前記データに基づいて統計を生成するステップと、

複数の閾値の少なくとも 1 つは前記統計に基づいて算出される、複数の閾値のなかから 1 つを選択するステップと、

選択された閾値を前記データに適用するステップと、

前記ヒストグラムを出力するステップと、

前記選択された閾値より大きく、前記画素データから分割された画像を少なくとも部分的に表す超過データを出力するステップと、を備え、

プログラム可能なフィルタ係数を制御、設定し、前記データのデジタルフィルタリングを少なくとも 1 回行う前記ステップは、

前記統計に基づいて前記プログラム可能なフィルタ係数をリセットするステップと、

前記データの戻しをフィルタに再入力するステップと、

前記リセットされたプログラム可能なフィルタ係数により前記再入力データをフィルタリングするステップと、を含む、

画像分割を実行する方法。

## 【請求項 7】

10

20

30

40

50

さらに、画素データのフレーム毎に前記閾値のレベルを変更するステップを含む、請求項6に記載の方法。

【請求項8】

さらに、前記選択された閾値に付加されるオフセット値に基づいて超過データを計算するステップを含む、請求項6に記載の方法。

【請求項9】

2組の超過データが出力される、請求項8に記載の方法。

【請求項10】

さらに、汎用プロセッサから命令を受けるステップを含む、請求項6に記載の方法。

【発明の詳細な説明】

10

【技術分野】

【0001】

本発明は概してデジタル信号処理に関する。特に本発明は、フィールドプログラマブルゲートアレー(FPGA)や特定用途向け集積回路(ASIC)などの集積電子デバイスで好適に実現される、複数の機能ユニットまたは機能モジュールを使用して画像分割(イメージセグメント化)を行うシステム及び方法に関する。

【背景技術】

【0002】

デジタル信号処理(DSP)は多様な分野で利用されており、その1つに画像分割がある。画像分割は着目した対象物を背景や他の対象物と区別する機能である。例えば、画像分割は、特定の対象物、例えば、車両の自動操縦を行う際に路面の車線区分線を追跡、検知する画像処理の用途でよく使用される。自動操縦の場合、画像処理は高速であることが求められ、特に車両の比較的高速運転時にはそうである。

20

【0003】

また、自動操縦における画像処理の場合、雨天時や日の差す晴天時や夜間での運転など、様々な天候や環境に対応できることが望ましい。しかしながら、運転状況として考えられる広範囲の変化は、静止処理技術に依存する従来の画像分割処理にとって大きな問題であった。

【発明の開示】

【発明が解決しようとする課題】

30

【0004】

デジタル信号処理技術を改良するため、本発明はカメラから取り込んだ画像のデジタル信号処理を促進、改善するシステム及び方法に関する。本発明は、例えば着目した対象物と背景を区別するなどの画像分割を行うのに特に適している。

【課題を解決するための手段】

【0005】

本発明の好適な実施形態において、システムはフィールドプログラマブルゲートアレー(FPGA)で実現され、FPGAにより発明の個々の機能ユニットが実質的に制御されるとともに、機能ユニット間のデータフローが実質的に制御される。

40

【0006】

特に、本発明において、データは異なる時間に異なる機能ユニットに通すことができる、すなわち、データを数回実際に機能ユニットに通した後、さらに処理を行うためにFPGAから適宜、外部装置に最終的に出力することが可能である。本発明の利点の1つとして、同一の装置全体を使用して入力データに様々なアルゴリズムを適用することができる。さらに本発明によれば、例えば画像を平滑化し、または画像エッジを検出するためのフィルタリングなどで使用される係数の実時間プログラミングを実現することが可能になる。

【0007】

本発明の好適な実施形態において、入力画素データは、外部RAMなどで構成されるバッファとしてのメモリに記憶される。さらに、画素輝度の範囲や大きさを識別するために

50

入力画像データのヒストグラムが作成される。好適な実施形態において、ヒストグラムは1024ビンで実現され、各画素は16ビットワードで表現される。

【0008】

状況に応じ、バッファメモリからの画素データは、プログラムされたFPGAの動作様に従って、1あるいはそれ以上の異なる従来技術を使用してフィルタされる。本発明によれば、フィルタ係数を「大急ぎ」で変更できる利点がある、すなわち、フィルタ処理は入力データの種類に応じて変更可能である。

【0009】

画素データをメモリに記憶してからヒストグラムを生成（さらに可能であればフィルタ）した後、メモリの画像データ（またはフィルタされたもの）は、好適に統計生成モジュールに転送され、このモジュールで各画素輝度値に關し、平均や標準偏差など、一連の統計が作成される。この統計はこの後、閾値の算出で使用される。

10

【0010】

閾値計算では、複数の可能な方法（後に詳述する）の1つに従って、現データや所望の画像分割のレベル、種類に適した閾値が決定される。閾値（または閾値の組）が決定された後、閾値比較モジュールにより画像データのなかで閾値より大きな画素が決定される。好適には、閾値より大きな画素のみ値が維持され、他の画素は所定の輝度値、例えばゼロにリセットされる。これにより後続のデジタル信号処理でこれらの画素についてさらに処理を行う必要が無くなる。

20

【0011】

本発明の好適な実施形態において、実時間プログラム可能な制御レジスタにより閾値のレベルの微調整が可能である。すなわち、汎用プロセッサを介して主制御モジュールを制御することで、主制御モジュールからレジスタを更新することができ、それにより1以上のモジュール内の変数が設定され、任意のモジュールに關してデータフローや動作が制御可能になる。

30

【0012】

本発明をFPGAや特定用途向け集積回路（ASIC）で実現した場合、外部画像収集システムとのインターフェースが可能になるとともに、入力画像の処理により例えば追跡用として着目した対象物から背景を分離することが可能になる。また、後に詳述するように、複数の閾値がフレーム毎に実時間で変更可能な点で本発明は汎用性を提供するものである。さらに本発明によれば、フィルタ係数は好適にプログラム可能であることから複数の異なる態様で動作可能な空間フィルタリング能力が提供される。

30

【0013】

本発明の特徴及びそれに付随する効果は図面を参照してなされる以下の詳細な説明からさらに明らかになる。

【図面の簡単な説明】

【0014】

【図1】本発明に基づいたシステムの代表的な実施形態を示すブロック図である。

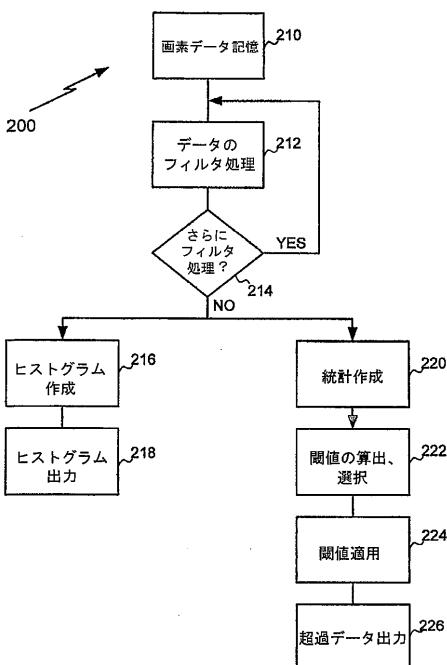

【図2】本発明の好適な実施形態に基づいた代表的な画像分割処理を示すフローチャートである。

40

【発明を実施するための形態】

【0015】

本発明の重要な側面として、データは1以上のモジュールに複数回通され、例えばカメラから取り込んだ入力画素データに異なるアルゴリズムを適用可能である。フィルタは、係数が実時間プログラム可能で、複数回通されることから、例えば平滑化やエッジ検出などの各種モードで使用可能である。図1に、本発明に基づいて入力画素データを処理する複数のモジュールを示す。主コントローラ8は1以上のレジスタ（図示せず）を備えている、データの経路選択を制御し、モジュールをイネーブルし、複数のモジュールに関する係数、その他の変数を設定、選択することにより、各モジュールを好適に制御する。図示していないが、主コントローラ8はその制御機能を果たすために後述する各モジュールに好

50

適に接続される。また、本発明のシステムに対し、典型的に汎用プロセッサ 6 が協働し、周知の方法で主コントローラ 8 と通信する。

【 0 0 1 6 】

図 1 において、1 回目のバスで、シリアルの画素データ 1 0 が図 1 のバッファ R A M 1 2 に記憶される。画素データ 1 0 は状況に応じてフィルタ 1 4 に通される。好適な実施形態において、フィルタ 1 4 は  $5 \times 5$  カーネルの空間フィルタで構成され、係数はプログラム可能である。フィルタ 1 4 は後で詳述する。

【 0 0 1 7 】

好適な実施形態において、バッファ R A M 1 2 は集合 F P G A デバイスにより直接実現されないが、その理由は、F P G A 内部に大量の画像データを記憶させようとすると F P G A リソースが制約され、F P G A の全体処理能力が損なわれるからである。また、画像データの F P G A 内部記憶は F P G A チップで処理可能な画像のサイズを制限することにもなる。中間の外部記憶能力（すなわち、バッファ 1 2）を設けることで F P G A チップは様々な画像サイズに対応可能になる。これより大きな ( $N \times N$ ) 画像を処理するには外部 R A M を付加するだけよい。

10

【 0 0 1 8 】

データがバッファ R A M 1 2 に記憶された後、ヒストグラムモジュール 1 6 はデータのヒストグラムを発生する。好適な実施形態において、ヒストグラムは 1 0 2 4 個の等間隔の bin で構成され、個々の画素はそれぞれの輝度 / カラーに応じて bin に割り振られる。輝度は例えば 1 6 ビットワードで表現されるが、他の大きさの変数により個々の画素を表現してもよい。

20

【 0 0 1 9 】

ヒストグラムの作成と同時に（または少なくとも極近い時間に）、データに関する統計が統計モジュール 1 8 で生成される。好適な実施形態では、少なくとも平均  $\mu$  と標準偏差が算出される。さらに、主コントローラ 8 との間で情報のやりとりをする汎用プロセッサ 6 から直接入力により、オフセット もこの段階で設定される。これらの値は以下説明する閾値の算出で使用される。

20

【 0 0 2 0 】

閾値の算出は閾値計算兼選択モジュール 2 0 と適用閾値モジュール 2 2 で実現するのが好ましい。本発明の好適な実施形態では、3 つの異なる画素分割閾値が使用可能である。第 1 の閾値は予め算出された値に設定される閾値であり、汎用プロセッサ 6 から供給される。

30

【 0 0 2 1 】

第 2 種と第 3 種の閾値は統計モジュール 1 8 から供給される現在の実時間統計に基づいて算出される。具体的には、次式により 1 画素の比較が得られる。

$$T = + \times \mu \quad (\text{平均、標準偏差、オフセット})$$

同様に、隣接 4 画素 ( $2 \times 2$  アレー) に関する閾値が次式により得られる。

【 0 0 2 2 】

$$T = 4 \times + \times \mu \quad (\text{平均、標準偏差、オフセット})$$

前記各閾値で示したように、本発明は閾値に関してオフセット が使用可能であることを好適にサポートする、すなわち、処理される画像フレーム毎に、閾値に対する超過画素を表すデータが 2 組得られる。

40

【 0 0 2 3 】

閾値が選択されると、適用閾値モジュール 2 2 はバッファ 1 2 から画像データを取り込み、選択された閾値を適用する。これにより得られた超過画素は好適に外部 R A M (図示せず) に書き込まれる。本発明の好適な実施形態において、閾値計算兼選択モジュール 2 0 は、処理中の画像データに係る個々の環境または性質に応じて閾値を微調整するために、レジスタを介して制御可能である。

【 0 0 2 4 】

前記のように、フィルタ 1 4 により画像の平滑化や画像エッジの検出が行われる。好適

50

な実施形態において、フィルタ14は、25個の係数がプログラム可能な $5 \times 5$ 画像マスクで構成される空間フィルタである。この種のフィルタは周知であり、詳細な説明は省略するが、加算器を備えた、25個の並列、パイプライン乗算器により、最適サイクルでフィルタの動作が可能である。フィルタは係数がプログラム可能であるため、平滑化フィルタリングや画像の不鮮明減少用の畳み込みフィルタリングなど、事実上任意の種類の空間フィルタ処理で使用可能である。好適には、固定小数点全精度演算フィルタにより、14または16ビットの画素サイズと16ビットの係数に必要な全精度に対応する。また、スループット遅延や演算中のオーバーフローを防止するために加算動作毎に別個の加算器が使用される。

## 【0025】

10

当業者には明らかなように、本発明に係る画像処理システムは対象物の追跡、検出に特に有効であり、車両の自動操縦システムなどにおいて重要な機能構成部品になる。自動操縦システムの場合、高速の入力画像を処理して車線区分線などの特徴的な対象物を抽出する必要があり、それにより車両をどの方向に操縦すべきかが決定可能になる。

## 【0026】

本発明に係る画像処理システムには、この種のシステムとインターフェースをとり、画像を処理し、背景を追跡のために着目した対象物から分離する能力がある。また、本発明によれば複数の閾値が提供され、統計の連続的作成や統計の閾値作成での使用に配慮して、フレーム毎に実時間で閾値を変更することができる。さらに、空間フィルタが設けられ、異なるフィルタ係数でプログラミングすることにより様々なモードのフィルタが実現される。以下はダイナミックな閾値算出が望ましい例である。

20

## 【0027】

閾値の変更： 着目した対象物がカメラに近づいたり、遠ざかったりする場合、その動きに応じて各画素のエネルギーが変化する。このため、システムは実時間ベースで閾値を調整する必要がある。このような場合に、背景の統計に基づいた閾値の実時間算出が行われる。

## 【0028】

下記はフィルタ選択の具体例であるが、典型的に、フィルタ選択は使用しているアプリケーションの関数である。下記に均一平滑フィルタの例を示す。

## 【0029】

30

## 【表1】

| 均一平滑フィルタ |      |      |      |      |

|----------|------|------|------|------|

| 0.04     | 0.04 | 0.04 | 0.04 | 0.04 |

| 0.04     | 0.04 | 0.04 | 0.04 | 0.04 |

| 0.04     | 0.04 | 0.04 | 0.04 | 0.04 |

| 0.04     | 0.04 | 0.04 | 0.04 | 0.04 |

| 0.04     | 0.04 | 0.04 | 0.04 | 0.04 |

## 【0030】

これまでの説明では、暗黙のうちに、フレーム毎に1回だけフィルタを動作させるとしてきたが、フィルタ14のデータ出力をバッファ12に戻した上でそのバッファデータをフィルタ14に再入力することにより、ヒストグラムや統計データの作成に先だって、フィルタ14を複数回使用することができる。したがって、フィルタは1つの画像分割処理において複数回使用可能である。例えば、エッジ検出の場合、2種類の異なるフィルタの係数を動作させて1つの結果を得ることが好ましい。全方向でエッジを強調するソーベル(Sobel)フィルタは好例である。これはカーネル係数を用いて2つの独立な畳み込み(空間フィルタリング)を行うことにより実現される。以下に使用される2種類のフィルタを示すが、最初は回転無しで後は90度回転させたものである。各カーネル動作の結果は組み合わされて最終結果が得られる。

40

## 【0031】

## 【表2】

ソーベルフィルタ(0度)

|      |       |       |       |      |

|------|-------|-------|-------|------|

| 0.00 | 0.00  | 0.00  | 0.00  | 0.00 |

| 0.00 | 1.00  | 2.00  | 1.00  | 0.00 |

| 0.00 | 0.00  | 0.00  | 0.00  | 0.00 |

| 0.00 | -1.00 | -2.00 | -1.00 | 0.00 |

| 0.00 | 0.00  | 0.00  | 0.00  | 0.00 |

ソーベルフィルタ(90度)

|      |      |      |       |      |

|------|------|------|-------|------|

| 0.00 | 0.00 | 0.00 | 0.00  | 0.00 |

| 0.00 | 1.00 | 0.00 | -1.00 | 0.00 |

| 0.00 | 2.00 | 0.00 | -2.00 | 0.00 |

| 0.00 | 1.00 | 0.00 | -1.00 | 0.00 |

| 0.00 | 0.00 | 0.00 | 0.00  | 0.00 |

## 【0032】

したがって、本発明によれば、図示のように複数の構成要素を組み込み、各構成要素がデータを操作する時間と態様を制御することにより、高速での画像処理が可能になり、フレーム毎の画像データ処理が求められる実時間アプリケーションに特に有効である。

## 【0033】

図2は本発明の好適な実施形態に基づいた代表的な画像分割処理を示すフローチャートである。この処理は参考符号200で示され、以下のステップからなる。ステップ210で画素データはバッファに好適に記憶される。次にステップ212で、バッファに記憶されたデータはフィルタされ、例えば画像の平滑化または画像のエッジ検出が行われる。次にステップ214で、さらにフィルタリングを行う必要があるか決定する。例えば、本発明によれば、フィルタ係数はプログラム変更可能であるため、フィルタを再使用して、しかも異なる態様でデータをフィルタすることができます。例えば、1回目のフィルタリングステップで画像を平滑化したのであれば、2回目のフィルタリングで画像のエッジを検出するように動作させることができます。さらにフィルタリングを行う必要がなければ、ステップ216でデータのヒストグラムを作成する。ステップ218で、ヒストグラムは本発明の装置と協働する汎用プロセッサに典型的に出力される。

## 【0034】

これと実質的に同時に、ステップ220で、バッファに記憶されたデータに関して一連の統計が作成される。この統計はバッファに当初記憶された原データあるいは後でバッファに再記憶されたフィルタ処理後のデータに基づいてなされる。統計の作成後、ステップ222で閾値を算出し、選択する。本発明によれば、閾値は作成したばかりの統計に基づいて得られ、あるいは汎用プロセッサから制御モジュールまたは制御機構のレジスタを介してプログラム設定される。閾値は、一旦選択されると、ステップ224でバッファのデータに適用される。バッファデータに閾値を適用した結果は「超過データ」と呼ばれるものであり、この超過データはヒストグラムとともに汎用プロセッサあるいはそれとは別個のDSP処理段に出力される。ヒストグラムデータは汎用プロセッサにおいて適宜使用される。

## 【0035】

当業者には明らかなように、本発明の場合、フィルタが柔軟に使用されるとともに様々な閾値が適用可能であることから、画像分割処理を実行する際に非常に効率がよい。具体的には、バッファ12との間で交わされるデータフローを制御してFPGAにデータを複数回通すことができ、それによって、画像処理に割り当てられるFPGAリソースを最大化するとともに、画素サイズの柔軟性を最大化することが可能になる。

## 【0036】

本発明の好適な実施形態に関する前記開示は例示と説明のためになされたものである。したがって包括的でなく、本発明は開示された形態に限定されない。前記開示内容に照ら

して、当業者には説明した実施形態から種々の変更、変形が明らかである。本発明の範囲は特許請求の範囲及びその均等物によってのみ限定されるものである。

【0037】

さらに、明細書において、本発明の実施の形態を説明する際に、本発明の方法／プロセスは特定のステップシーケンスとして示された。しかしながら、本方法／プロセスは、記載したステップの順序に依存しない範囲内で、記載のステップ順序には限定されないものである。当業者には明らかのように、他のステップ順序が可能である。したがって、明細書に記載したステップの順序は特許請求の範囲を限定しないものである。さらに、本発明の方法／プロセスに関する請求項は記載したステップの順序による性能に限定されるべきでなく、当業者には明らかのように、シーケンスは本発明の趣旨、範囲内で変更可能である。

【図1】

【図2】

---

フロントページの続き

(74)代理人 100096013

弁理士 富田 博行

(74)代理人 100107696

弁理士 西山 文俊

(72)発明者 ハケ, ジャマル

アメリカ合衆国フロリダ州 33626, タンパ, ロチェスター・ウェイ 10518

(72)発明者 プレヴィット, ジョン・ビー

アメリカ合衆国フロリダ州 33716, セント・ピータースバーグ, ノース・ビレッジ・ドライブ 885, ナンバー 202

(72)発明者 プラド, エドワード・アール

アメリカ合衆国フロリダ州 34685, パーム・ハーバー, サドルウッド・レーン 2778

(72)発明者 ウィルコックス, ミッセル・エス

アメリカ合衆国フロリダ州 33773, ラルゴ, ナインティファースト・ウェイ・ノース 12361

(72)発明者 パーカー, ジェイムズ・ディー

アメリカ合衆国フロリダ州 34689, ターポン・スプリングス, オスプレイ・コート 1003

F ターム(参考) 5B013 DD02

5B057 AA16 BA02 CA08 CA12 CA16 CB08 CB12 CB16 CC02 CE06

CH05 CH09 DA08 DB02 DB09 DC16