(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-128288

(P2006-128288A)

(43) 公開日 平成18年5月18日(2006.5.18)

| (51) Int.CI.                  | F 1        | テーマコード (参考) |

|-------------------------------|------------|-------------|

| <b>H01L 23/52</b> (2006.01)   | H01L 21/88 | R 4K030     |

| <b>H01L 21/3205</b> (2006.01) | C23C 16/18 | 4M104       |

| <b>C23C 16/18</b> (2006.01)   | C23C 16/50 | 5F033       |

| <b>C23C 16/50</b> (2006.01)   | H01L 21/28 | 301R        |

| <b>H01L 21/28</b> (2006.01)   |            |             |

審査請求 未請求 請求項の数 33 O L (全 22 頁)

|           |                              |            |                                                       |

|-----------|------------------------------|------------|-------------------------------------------------------|

| (21) 出願番号 | 特願2004-312497 (P2004-312497) | (71) 出願人   | 000219967<br>東京エレクトロン株式会社<br>東京都港区赤坂五丁目3番6号           |

| (22) 出願日  | 平成16年10月27日 (2004.10.27)     | (74) 代理人   | 100070150<br>弁理士 伊東 忠彦                                |

|           |                              | (72) 発明者   | 小島 康彦<br>東京都港区赤坂五丁目3番6号 TBS放送センター 東京エレクトロン株式会社内       |

|           |                              | (72) 発明者   | ▲吉▼井 直樹<br>東京都港区赤坂五丁目3番6号 TBS放送センター 東京エレクトロン株式会社内     |

|           |                              | F ターム (参考) | 4K030 AA11 BA01 BB12 CA04 DA02<br>EA12 FA01 LA01 LA12 |

最終頁に続く

(54) 【発明の名称】成膜方法、半導体装置の製造方法、半導体装置、プログラムおよび記録媒体

## (57) 【要約】

【課題】 半導体装置のCu拡散防止膜とCu配線との密着力を良好とし、半導体装置の信頼性を良好とする。

【解決手段】 被処理基板上にCu膜を成膜する成膜方法であって、前記被処理基板上に形成されたCu拡散防止膜上に密着膜を形成する第1の工程と、前記密着膜上にCu膜を成膜する第2の工程と、を有し、前記密着膜はPdを含むことを特徴とする成膜方法。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

被処理基板上に Cu 膜を成膜する成膜方法であって、

前記被処理基板上に形成された Cu 拡散防止膜上に密着膜を形成する第 1 の工程と、

前記密着膜上に前記 Cu 膜を成膜する第 2 の工程と、を有し、

前記密着膜は Pd を含むことを特徴とする成膜方法。

**【請求項 2】**

前記密着膜は、Cu を含むことを特徴とする請求項 1 記載の成膜方法。

**【請求項 3】**

前記 Cu 拡散防止膜は、前記被処理基板上に形成された絶縁膜を覆うように形成されて

いることを特徴とする請求項 1 または 2 記載の成膜方法。 10

**【請求項 4】**

前記絶縁膜にはパターン形状が形成されており、前記 Cu 拡散防止膜は当該パターン形

状にそって形成されていることを特徴とする請求項 3 記載の成膜方法。

**【請求項 5】**

前記密着膜は、PVD 法により成膜されることを特徴とする請求項 1 乃至 4 のうち、い

ずれか 1 項記載の成膜方法。

**【請求項 6】**

前記密着膜は、成膜ガスと還元ガスを用いた CVD 法により成膜されることを特徴とす

る請求項 1 乃至 4 のうち、いずれか 1 項記載の成膜方法。 20

**【請求項 7】**

前記成膜ガスは、Pd (hfac)<sub>2</sub>、(C<sub>5</sub>H<sub>5</sub>)Pd (allyl)、および Pd

(allyl)<sub>2</sub> のいずれかであることを特徴とする請求項 6 記載の成膜方法。

**【請求項 8】**

前記第 1 の工程は、

前記被処理基板上に成膜ガスを供給する成膜ガス工程と、

前記被処理基板上から当該成膜ガスを除去する成膜ガス除去工程と、

前記被処理基板上に還元ガスを供給する還元ガス工程と、

前記被処理基板上から当該還元ガスを除去する還元ガス除去工程と、を有することを特

徴とする請求項 1 乃至 4 のうち、いずれか 1 項記載の成膜方法。 30

**【請求項 9】**

前記成膜ガスは、Pd (hfac)<sub>2</sub>、(C<sub>5</sub>H<sub>5</sub>)Pd (allyl)、および Pd

(allyl)<sub>2</sub> のいずれかであることを特徴とする請求項 8 記載の成膜方法。

**【請求項 10】**

前記還元ガスは、プラズマ励起して用いられることを特徴とする請求項 8 または 9 記載

の成膜方法。

**【請求項 11】**

前記第 2 の工程は、

前記被処理基板上に Cu 成膜ガスを供給する Cu 成膜ガス工程と、

前記被処理基板上から当該 Cu 成膜ガスを除去する Cu 成膜ガス除去工程と、

前記被処理基板上に Cu 還元ガスを供給する Cu 還元ガス工程と、

前記被処理基板上から当該 Cu 還元ガスを除去する Cu 還元ガス除去工程と、を有すること

を特徴とする、請求項 1 乃至 10 のうち、いずれか 1 項記載の成膜方法。 40

**【請求項 12】**

前記 Cu 成膜ガスは、Cu (hfac)<sub>2</sub>、Cu (acac)<sub>2</sub>、Cu (dpm)<sub>2</sub>、Cu

(dibm)<sub>2</sub>、Cu (ibpm)<sub>2</sub>、Cu (edmd)<sub>2</sub>、Cu (hfac)TMV

S、および、Cu (hfac) COD よりなる群より選択されることを特徴とする請求項

11 記載の成膜方法。

**【請求項 13】**

前記 Cu 還元ガスは、プラズマ励起して用いられることを特徴とする請求項 11 または 50

12項記載の成膜方法。

【請求項 14】

Cu配線部を有する半導体装置の製造方法であって、

被処理基板上の絶縁層に形成されたパターン形状にそって形成されたCu拡散防止膜上

に、密着膜を形成する第1の工程と、

前記密着膜上に前記Cu配線部を形成する第2の工程と、を有し、

前記密着膜はPdを含むことを特徴とする半導体装置の製造方法。

【請求項 15】

前記密着膜は、Cuを含むことを特徴とする請求項14記載の半導体装置の製造方法。

【請求項 16】

前記密着膜は、PVD法により成膜されることを特徴とする請求項14または15記載

の半導体装置の製造方法。

【請求項 17】

前記密着膜は、成膜ガスと還元ガスを用いたCVD法により成膜されることを特徴とす

る請求項14または15記載の半導体装置の製造方法。

【請求項 18】

前記成膜ガスは、Pd(hfac)<sub>2</sub>、(C<sub>5</sub>H<sub>5</sub>)Pd(allyl)、およびPd

(allyl)<sub>2</sub>のいずれかであることを特徴とする請求項17記載の半導体装置の製造

方法。

【請求項 19】

前記第1の工程は、

前記被処理基板上に成膜ガスを供給する成膜ガス工程と、

前記被処理基板上から当該成膜ガスを除去する成膜ガス除去工程と、

前記被処理基板上に還元ガスを供給する還元ガス工程と、

前記被処理基板上から当該還元ガスを除去する還元ガス除去工程と、を有することを特

徴とする請求項14または15記載の半導体装置の製造方法。

【請求項 20】

前記成膜ガスは、Pd(hfac)<sub>2</sub>、(C<sub>5</sub>H<sub>5</sub>)Pd(allyl)、およびPd

(allyl)<sub>2</sub>のいずれかであることを特徴とする請求項19記載の半導体装置の製造

方法。

【請求項 21】

前記還元ガスは、プラズマ励起して用いられることを特徴とする請求項19または20記

載の半導体装置の製造方法。

【請求項 22】

前記第2の工程は、

前記被処理基板上にCu成膜ガスを供給するCu成膜ガス工程と、

前記被処理基板上から当該Cu成膜ガスを除去するCu成膜ガス除去工程と、

前記被処理基板上にCu還元ガスを供給するCu還元ガス工程と、

前記被処理基板上から当該Cu還元ガスを除去するCu還元ガス除去工程と、を有する

ことを特徴とする、請求項14乃至21のうち、いずれか1項記載の半導体装置の製造

方法。

【請求項 23】

前記Cu成膜ガスは、Cu(hfac)<sub>2</sub>、Cu(acac)<sub>2</sub>、Cu(dpm)<sub>2</sub>、Cu

(dibm)<sub>2</sub>、Cu(ibpm)<sub>2</sub>、Cu(edmd)<sub>2</sub>、Cu(hfac)TMV

S、および、Cu(hfac)CODよりなる群より選択されることを特徴とする請求項

22記載の半導体装置の製造方法。

【請求項 24】

前記Cu還元ガスは、プラズマ励起して用いられることを特徴とする請求項22または

23記載の半導体装置の製造方法。

【請求項 25】

10

20

30

40

50

被処理基板上に形成された絶縁層と、

前記絶縁層中に形成されたCu配線部と、

前記絶縁層と前記Cu配線部の間に形成されたCu拡散防止膜と、を有する半導体装置であって、

前記Cu配線部と前記Cu拡散防止膜の間にPdを含む密着膜を有することを特徴とする半導体装置。

**【請求項26】**

前記密着膜は、Cuを含むことを特徴とする請求項25記載の半導体装置。

**【請求項27】**

前記Cu拡散防止膜は、Ta、Ta<sub>N</sub>、TaCN<sub>x</sub>、W、WN、WCNx、TiN、TaSiN、およびTiSiNよりなる群より選択されるいづれかの材料を含むことを特徴とする請求項25または26記載の半導体装置。 10

**【請求項28】**

前記絶縁層は、シリコン酸化膜、フッ素添加シリコン酸化膜、SiOC膜、有機高分子膜、および多孔質膜のいづれかを含むことを特徴とする請求項25乃至27のうち、いづれか1項記載の半導体装置。

**【請求項29】**

被処理基板上に形成されたCu拡散防止膜とCu配線部との間に、Pdを含む密着膜を形成する、成膜装置による成膜方法をコンピュータに動作させるプログラムであって、

前記被処理基板上に成膜ガスを供給する成膜ガス工程と、

前記被処理基板上から当該成膜ガスを除去する成膜ガス除去工程と、

前記被処理基板上に還元ガスを供給する還元ガス工程と、

前記被処理基板上から当該還元ガスを除去する還元ガス除去工程と、を有することを特徴とするプログラム。 20

**【請求項30】**

前記成膜ガスは、Pd(hfac)<sub>2</sub>、(C<sub>5</sub>H<sub>5</sub>)Pd(allyl)、およびPd(allyl)<sub>2</sub>のいづれかであることを特徴とする請求項29記載のプログラム。

**【請求項31】**

前記還元ガスは、プラズマ励起して用いられることを特徴とする請求項29または30記載のプログラム。 30

**【請求項32】**

請求項29乃至31のうち、いづれか1項記載のプログラムを記憶した記録媒体。

**【請求項33】**

被処理基板上に形成されたCu拡散防止膜とCu配線部との間に、Pdを含む密着膜を形成する、成膜装置であって、

前記被処理基板上に成膜ガスを供給する成膜ガス工程と、

前記被処理基板上から当該成膜ガスを除去する成膜ガス除去工程と、

前記被処理基板上に還元ガスを供給する還元ガス工程と、

前記被処理基板上から当該還元ガスを除去する還元ガス除去工程と、を実行する制御装置を備えた成膜装置。 40

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、被処理基板上のCu拡散防止膜上にCu膜を形成する成膜方法と、これを用いた半導体装置の製造方法および半導体装置、また当該成膜方法を動作させるプログラム、および当該プログラムを記録した記憶媒体に関する。

**【背景技術】**

**【0002】**

近年、半導体装置の高性能化に伴い、半導体デバイスの高集積化が進んで微細化の要求が著しくなっており、配線ルールは0.1μm以下の領域へと開発が進んでいる。また、 50

配線材料は配線遅延の影響の少ない、抵抗値の低いCuが用いられている。

【0003】

そのため、Cu成膜技術と微細配線技術の組み合わせが、近年の微細化した多層配線技術の重要なキーテクノロジーとなっている。

【0004】

例えば、半導体装置などの配線に、Cu配線を用いる場合には、Cu配線の周囲に形成された絶縁層中にCuが拡散してしまう懸念があるため、Cu配線と絶縁層の間にCu拡散防止膜（またはバリア膜、下地膜などと呼ばれる場合もある）を形成することが一般的となっている。

【特許文献1】特開2004-193499号公報

10

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかし、この場合、Cu配線は、従来用いられてきたCu拡散防止膜、例えばTa膜やTaN膜などとの密着性が悪く、Cu配線とCu拡散防止膜の間で剥離が生じる場合があり、例えば半導体装置の信頼性の低下などの問題が生じていた。

【0006】

また、例えば、半導体装置の製造工程において、膜剥がれの他にも、特に熱工程後にCuの凝集が生じる場合があり、また、このように密着性が悪く、凝集が生じる状態で形成されたCu配線では、Cu配線中を流れる電流密度が高くなった場合に、電子の界面拡散に起因するエレクトロマイグレーションによる配線の劣化が生じ、またストレスマイグレーションによって配線劣化、または破損してしまう懸念が生じていた。

20

【0007】

このため、例えばCu拡散防止膜とCu配線との間にRuよりなる密着膜を形成する方法が試みられているが、Cu拡散防止膜とCu配線との間で充分な密着力を保持するには至っておらず、またCuの凝集性の改善も充分ではなく、実用レベルには達していない。

【0008】

そこで、本発明では上記の問題を解決した、新規で有用な成膜方法と、これを用いた半導体装置の製造方法および半導体装置、また当該成膜方法を動作させるプログラム、および当該プログラムを記録した記憶媒体を提供することを目的としている。

30

【0009】

本発明の具体的な課題は、Cu拡散防止膜とCu配線との密着力を良好とする成膜方法と、これを用いた半導体装置の製造方法および半導体装置、また当該成膜方法を動作させるプログラム、および当該プログラムを記録した記憶媒体を提供することである。

【課題を解決するための手段】

【0010】

本発明は上記の課題を解決するために、

請求項1に記載したように、

被処理基板上にCu膜を成膜する成膜方法であって、

前記被処理基板上に形成されたCu拡散防止膜上に密着膜を形成する第1の工程と、

40

前記密着膜上に前記Cu膜を成膜する第2の工程と、を有し、

前記密着膜はPdを含むことを特徴とする成膜方法により、また、

請求項2に記載したように、

前記密着膜は、Cuを含むことを特徴とする請求項1記載の成膜方法により、また、

請求項3に記載したように、

前記Cu拡散防止膜は、前記被処理基板上に形成された絶縁膜を覆うように形成されていることを特徴とする請求項1または2記載の成膜方法により、また、

請求項4に記載したように、

前記絶縁膜にはパターン形状が形成されており、前記Cu拡散防止膜は当該パターン形状にそって形成されていることを特徴とする請求項3記載の成膜方法により、また、

50

請求項 5 に記載したように、

前記密着膜は、 P V D 法により成膜されることを特徴とする請求項 1 乃至 4 のうち、 いずれか 1 項記載の成膜方法により、 また、

請求項 6 に記載したように、

前記密着膜は、 成膜ガスと還元ガスを用いた C V D 法により成膜されることを特徴とする請求項 1 乃至 4 のうち、 いずれか 1 項記載の成膜方法により、 また、

請求項 7 に記載したように、

前記成膜ガスは、 P d ( h f a c )<sub>2</sub> 、 ( C<sub>5</sub> H<sub>5</sub> ) P d ( a l l y l ) 、 および P d ( a l l y l )<sub>2</sub> のいずれかであることを特徴とする請求項 6 記載の成膜方法により、 また、

10

請求項 8 に記載したように、

前記第 1 の工程は、

前記被処理基板上に成膜ガスを供給する成膜ガス工程と、

前記被処理基板上から当該成膜ガスを除去する成膜ガス除去工程と、

前記被処理基板上に還元ガスを供給する還元ガス工程と、

前記被処理基板上から当該還元ガスを除去する還元ガス除去工程と、 を有することを特徴とする請求項 1 乃至 4 のうち、 いずれか 1 項記載の成膜方法により、 また、

請求項 9 に記載したように、

前記成膜ガスは、 P d ( h f a c )<sub>2</sub> 、 ( C<sub>5</sub> H<sub>5</sub> ) P d ( a l l y l ) 、 および P d ( a l l y l )<sub>2</sub> のいずれかであることを特徴とする請求項 8 記載の成膜方法により、 また、

20

請求項 10 に記載したように、

前記還元ガスは、 プラズマ励起して用いられることを特徴とする請求項 8 または 9 記載の成膜方法により、 また、

請求項 11 に記載したように、

前記第 2 の工程は、

前記被処理基板上に Cu 成膜ガスを供給する Cu 成膜ガス工程と、

前記被処理基板上から当該 Cu 成膜ガスを除去する Cu 成膜ガス除去工程と、

前記被処理基板上に Cu 還元ガスを供給する Cu 還元ガス工程と、

前記被処理基板上から当該 Cu 還元ガスを除去する Cu 還元ガス除去工程と、 を有することを特徴とする、 請求項 1 乃至 10 のうち、 いずれか 1 項記載の成膜方法により、 また、

30

請求項 12 に記載したように、

前記 Cu 成膜ガスは、 Cu ( h f a c )<sub>2</sub> 、 Cu ( a c a c )<sub>2</sub> 、 Cu ( d p m )<sub>2</sub> 、 Cu ( d i b m )<sub>2</sub> 、 Cu ( i b p m )<sub>2</sub> 、 Cu ( e d m d d )<sub>2</sub> 、 Cu ( h f a c ) T M V S 、 および、 Cu ( h f a c ) C O D よりなる群より選択されることを特徴とする請求項 11 記載の成膜方法により、 また、

請求項 13 に記載したように、

前記 Cu 還元ガスは、 プラズマ励起して用いられることを特徴とする請求項 11 または 12 記載の成膜方法により、 また、

40

請求項 14 に記載したように、

Cu 配線部を有する半導体装置の製造方法であって、

被処理基板上の絶縁層に形成されたパターン形状にそって形成された Cu 拡散防止膜上に、 密着膜を形成する第 1 の工程と、

前記密着膜上に前記 Cu 配線部を形成する第 2 の工程と、 を有し、

前記密着膜は P d を含むことを特徴とする半導体装置の製造方法により、 また、

請求項 15 に記載したように、

前記密着膜は、 Cu を含むことを特徴とする請求項 14 記載の半導体装置の製造方法により、 また、

請求項 16 に記載したように、

50

前記密着膜は、PVD法により成膜されることを特徴とする請求項14または15記載の半導体装置の製造方法により、また、

請求項17に記載したように、

前記密着膜は、成膜ガスと還元ガスを用いたCVD法により成膜されることを特徴とする請求項14または15記載の半導体装置の製造方法により、また、

請求項18に記載したように、

前記成膜ガスは、Pd(hfac)<sub>2</sub>、(C<sub>5</sub>H<sub>5</sub>)Pd(allyl)、およびPd(allyl)<sub>2</sub>のいずれかであることを特徴とする請求項17記載の半導体装置の製造方法により、また、

請求項19に記載したように、

前記第1の工程は、

前記被処理基板上に成膜ガスを供給する成膜ガス工程と、

前記被処理基板上から当該成膜ガスを除去する成膜ガス除去工程と、

前記被処理基板上に還元ガスを供給する還元ガス工程と、

前記被処理基板上から当該還元ガスを除去する還元ガス除去工程と、を有することを特徴とする請求項14または15記載の半導体装置の製造方法により、また、

請求項20に記載したように、

前記成膜ガスは、Pd(hfac)<sub>2</sub>、(C<sub>5</sub>H<sub>5</sub>)Pd(allyl)、およびPd(allyl)<sub>2</sub>のいずれかであることを特徴とする請求項19記載の半導体装置の製造方法により、また、

請求項21に記載したように、

前記還元ガスは、プラズマ励起して用いられることを特徴とする請求項19または20記載の半導体装置の製造方法により、また、

請求項22に記載したように、

前記第2の工程は、

前記被処理基板上にCu成膜ガスを供給するCu成膜ガス工程と、

前記被処理基板上から当該Cu成膜ガスを除去するCu成膜ガス除去工程と、

前記被処理基板上にCu還元ガスを供給するCu還元ガス工程と、

前記被処理基板上から当該Cu還元ガスを除去するCu還元ガス除去工程と、を有することを特徴とする、請求項14乃至21のうち、いずれか1項記載の半導体装置の製造方法により、また、

請求項23に記載したように、

前記Cu成膜ガスは、Cu(hfac)<sub>2</sub>、Cu(acac)<sub>2</sub>、Cu(dpm)<sub>2</sub>、Cu(dibm)<sub>2</sub>、Cu(ibpm)<sub>2</sub>、Cu(edmd)<sub>2</sub>、Cu(hfac)TMV<sub>S</sub>、および、Cu(hfac)CODよりなる群より選択されることを特徴とする請求項22記載の半導体装置の製造方法により、また、

請求項24に記載したように、

前記Cu還元ガスは、プラズマ励起して用いられることを特徴とする請求項22または23記載の半導体装置の製造方法により、また、

請求項25に記載したように、

被処理基板上に形成された絶縁層と、

前記絶縁層中に形成されたCu配線部と、

前記絶縁層と前記Cu配線部の間に形成されたCu拡散防止膜と、を有する半導体装置であって、

前記Cu配線部と前記Cu拡散防止膜の間にPdを含む密着膜を有することを特徴とする半導体装置により、また、

請求項26に記載したように、

前記密着膜は、Cuを含むことを特徴とする請求項25記載の半導体装置により、また、

請求項27に記載したように、

10

20

30

40

50

前記 Cu 拡散防止膜は、Ta、Ta<sub>N</sub>、TaCNx、W、WN、WCNx、TiN、TaSiN、およびTiSiNよりなる群より選択されるいづれかの材料を含むことを特徴とする請求項25または26記載の半導体装置により、また、

請求項28に記載したように、

前記絶縁層は、シリコン酸化膜、フッ素添加シリコン酸化膜、SiOC膜、有機高分子膜、および多孔質膜のいづれかを含むことを特徴とする請求項25乃至27のうち、いづれか1項記載の半導体装置により、また、

請求項29に記載したように、

被処理基板上に形成されたCu拡散防止膜とCu配線部との間に、Pdを含む密着膜を形成する、成膜装置による成膜方法をコンピュータに動作させるプログラムであって、

10

前記被処理基板上に成膜ガスを供給する成膜ガス工程と、

前記被処理基板上から当該成膜ガスを除去する成膜ガス除去工程と、

前記被処理基板上に還元ガスを供給する還元ガス工程と、

前記被処理基板上から当該還元ガスを除去する還元ガス除去工程と、を有することを特徴とするプログラムにより、また、

請求項30に記載したように、

前記成膜ガスは、Pd(hfac)<sub>2</sub>、(C<sub>5</sub>H<sub>5</sub>)Pd(allyl)、およびPd(allyl)<sub>2</sub>のいづれかであることを特徴とする請求項29記載のプログラムにより、また、

20

請求項31に記載したように、

前記還元ガスは、プラズマ励起して用いられることを特徴とする請求項29または30記載のプログラムにより、また、

請求項32に記載したように、

請求項29乃至31のうち、いづれか1項記載のプログラムを記憶した記録媒体により、また、

請求項33に記載したように、

被処理基板上に形成されたCu拡散防止膜とCu配線部との間に、Pdを含む密着膜を形成する、成膜装置であって、

前記被処理基板上に成膜ガスを供給する成膜ガス工程と、

前記被処理基板上から当該成膜ガスを除去する成膜ガス除去工程と、

30

前記被処理基板上に還元ガスを供給する還元ガス工程と、

前記被処理基板上から当該還元ガスを除去する還元ガス除去工程と、を実行する制御装置を備えた成膜装置により、解決する。

### 【発明の効果】

#### 【0011】

本発明によれば、半導体装置のCu拡散防止膜とCu配線との密着力を良好とすることが可能となり、半導体装置の信頼性を良好とすることが可能となる。

#### 【発明を実施するための最良の形態】

#### 【0012】

次に、本発明の実施の形態に関して図面に基づき、以下に説明する。

40

#### 【実施例1】

#### 【0013】

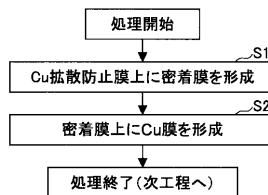

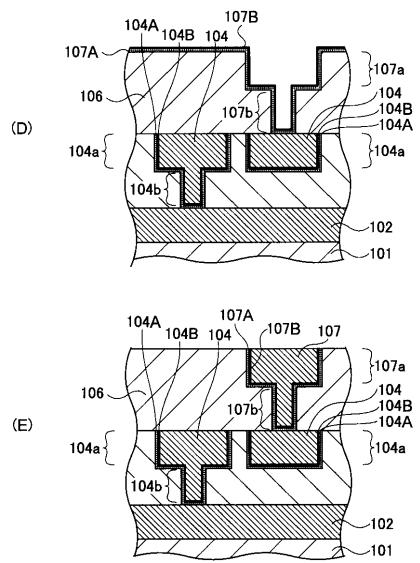

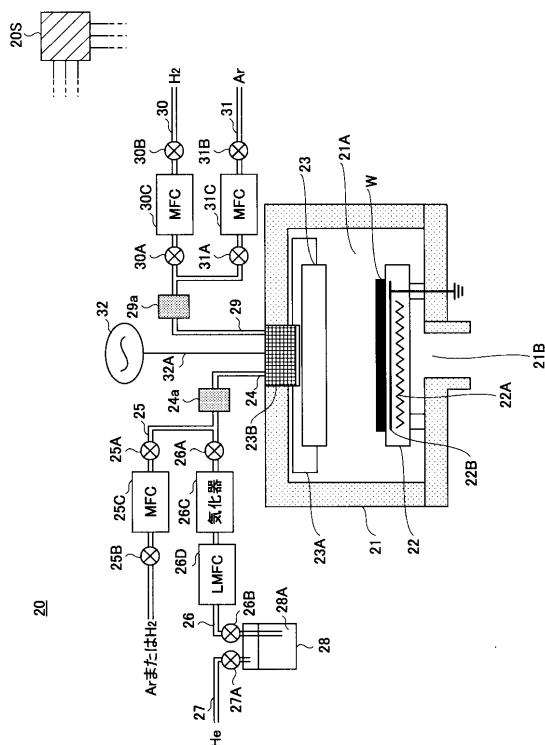

図1は、本発明の実施例1による成膜方法を示すフローチャートである。

#### 【0014】

図1を参照するに、まず、処理が開始されると、ステップ1(図中S1と表記、以下同様)において被処理基板上に形成された、Cu拡散防止膜上に、密着膜を形成する。例えば、当該Cu拡散防止膜は、被処理基板上に形成された絶縁層のパターニング形状にそって形成されている。当該密着膜は、Cu拡散防止膜と密着性が良好であって、さらに後の工程で形成される、Cu膜との密着性が良好である特徴を有している。

#### 【0015】

50

次に、ステップ2で、前記ステップ1で形成された密着膜上にCu膜を形成し、例えばCu配線を形成する。本ステップでCu膜を形成してCu配線を形成した後、必要に応じて、例えばCMP(化学機械研磨)工程や、さらにCMP工程後にさらに上層の配線構造を形成するなどの工程を実施して、例えば多層配線構造を有する半導体装置を形成する。

#### 【0016】

前記密着膜を構成する材料としては、Ruを用いる場合があったが、Cu拡散防止膜とCu膜との密着性を充分に改善するには至らず、またCuの凝集を充分に抑制することが困難となっていた。

#### 【0017】

そこで、本実施例による成膜方法では、密着膜にPdを含む膜を用いている。密着膜がPdを含むようにすると、おもに密着膜とCuの界面近傍において、活性な金属であるPdとCuとの合金化が促進し、その結果当該密着膜とCuの密着性が良好となると考えられる。また、密着膜に、特にPdを用いた場合には、他の材料を用いた場合に比べてより密着性が良好となることが本発明の発明者により、見出された。この場合、Cuの凝集が抑制され、エレクトロマイグレーション、ストレスマイグレーションが抑制されると考えられる。

#### 【0018】

また、本実施例による成膜方法を用いた場合、Cu拡散防止膜の表面がPdを含む密着膜で保護されるため、例えばCu配線を形成する前に被処理基板が酸素を含む雰囲気に曝された場合に、Cu拡散防止膜の酸化を防止することが可能となる。例えば、Cu拡散防止膜にTaを含む膜を用いた場合、Cu拡散防止膜が露出した状態で酸素を含む雰囲気に放置されるとTaは容易に酸化され、Cu拡散防止膜上には、Taの酸化物が形成されてしまう。Taの酸化物は、Cu膜との密着性が悪く、Cu膜を形成した場合に剥離の原因となってしまう懸念があり、またTaの酸化物が形成されることでCu拡散防止膜の比抵抗が増大する場合がある。

#### 【0019】

一方、Pdを含む密着膜は、例えばTaと比べると酸化されにくく、また、仮に酸化された場合でも、Pdの酸化物はTaの酸化物に比べて比抵抗が小さいため、密着膜を含むCu拡散防止膜の比抵抗の増大が抑制され、デバイス特性の劣化が抑制される効果を奏する。

#### 【0020】

次に、本実施例による成膜方法を用いて、半導体装置を製造する一例を以下に示す。

#### 【0021】

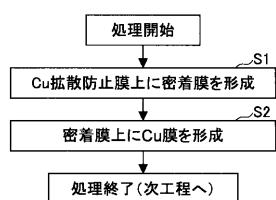

図2(A)～(C)、図3(D)～(E)は、図1に示した成膜方法を用いて半導体装置を製造する一例を、手順を追って示したものである。

#### 【0022】

まず、図2(A)を参照するに、シリコンからなる半導体基板(被処理基板)上に形成されたMOSトランジスタなどの素子(図示せず)を覆うように絶縁膜、例えばシリコン酸化膜101が形成されている。当該素子に電気的に接続されている、例えばタンゲステンからなる配線層(図示せず)と、これに接続された、例えばCuからなる配線層102が形成されている。

#### 【0023】

また、前記シリコン酸化膜101上には、配線層102を覆うように、第1の絶縁層103が形成されている。前記絶縁層103には、パターン形状である、例えば溝部104aおよびホール部104bが形成されている。前記溝部104aおよびホール部104bには、Cuにより形成された、トレンチ配線とビア配線からなる配線部104が形成され、これが前述の配線層102と電気的に接続された構成となっている。

#### 【0024】

また、前記第1の絶縁層103と前記配線部104の間には、当該第1の絶縁層103

の側には Cu 拡散防止膜 104A が、また前記配線部 104 の側には Pd を含む密着膜 104B が形成されている。前記 Cu 拡散防止膜 104A は、前記配線部 104 から前記第 1 の絶縁層 103 へ Cu が拡散するのを防止する機能を有する。さらに、前記配線部 104 および前記第 1 の絶縁層 103 の上を覆うように第 2 の絶縁層 106 が形成されている。本実施例では、前記第 2 の絶縁層 106 に、本発明による成膜方法を適用して、密着膜および Cu 膜を形成する方法を示す。なお、前記配線部 104 と前記密着膜 104B に関しても、以下に示す実施例に記載した方法で同様に形成することが可能である。

#### 【0025】

図 2 (B) に示す工程では、前記第 2 の絶縁層 106 に、パターン形状、例えば、溝部 107a およびホール部 107b を、例えばドライエッチング法などによって形成する。

10

#### 【0026】

次に図 2 (C) に示す工程において、前記溝部 107a および前記ホール部 107b の内壁面にそって前記第 2 の絶縁層 106 上、および前記配線部 104 の露出面に、Cu 拡散防止膜 107A の成膜を行う。前記 Cu 拡散防止膜 107A は、例えばこの場合 TaN 膜よりなり、例えばスパッタ法などの方法により、形成することが可能である。

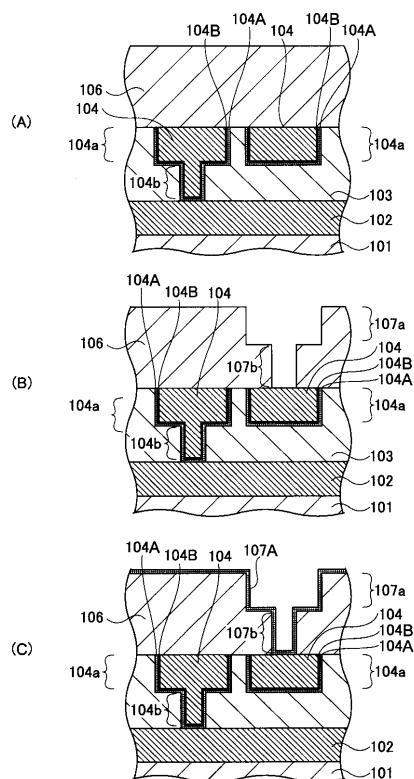

#### 【0027】

次に、図 3 (D) に示す工程において、前記溝部 107a および前記ホール部 107b の内壁面にそって、前記 Cu 拡散防止膜 107A 上に、例えばスパッタ法などの PVD 法により、Pd を含む密着膜 107B を形成する。また、当該密着膜 107B は、Pd に加えて、Cu を含むようによく、当該密着膜 107B が Pd と Cu とを含むと、さらに当該密着膜 107B と当該密着膜 107B 上に形成される後述する Cu 配線部との密着性が良好となる。

20

#### 【0028】

また、当該密着膜 107B は、様々な成膜方法で形成することが可能であり、PVD 法のほかに CVD 法、被処理基板上に複数のガスを交互に供給する方法（このような成膜方法を ALD 法、Atomic Layer Deposition 法と呼ぶ場合もある）などによって形成することが可能である。このような前記密着膜 107B を形成する装置や具体的な成膜方法の詳細に関しては図 4 以下で後述する。

#### 【0029】

次に図 3 (E) に示す工程において、Cu 膜を成膜し、前記溝部 107a および前記ホール部 107b を含む、前記密着膜 107B の上に、前記溝部 107a および前記ホール部 107b を埋設するようにして、Cu よりなる配線部 107 を形成する。また、当該配線部 107 は、様々な成膜方法で形成することが可能であり、PVD 法や CVD 法、被処理基板上に複数のガスを交互に供給する方法（ALD 法）、もしくは、メッキ法によって、またはこれらのいずれかの方法を組み合わせることによって形成することが可能である。

30

#### 【0030】

この場合、前記密着膜 107B 上に、まずシード層となる Cu 膜を形成し、次に当該シード層上に Cu 膜を埋設するようにして形成する方法がある。また、シード層を形成せずに Cu 膜を埋設するようにして形成する方法もある。

40

#### 【0031】

また、当該シード層を形成する方法としては、例えば PVD 法を用いることが可能であり、また CVD 法を用いた場合にはカバレッジが良好となり好適であり、また被処理基板上に複数のガスを交互に供給する方法（ALD 法）を用いた場合にはカバレッジがさらに良好となり、さらに好適である。また、当該シード層を形成した後に Cu 膜を埋設するように形成する方法としては、例えば、PVD 法、CVD 法、被処理基板上に複数のガスを交互に供給する方法（ALD 法）の他に、メッキ法を用いることも可能である。また、シード層を形成せずに、Cu 膜を埋設するようにして形成する方法を用いる場合、PVD 法、CVD 法、被処理基板上に複数のガスを交互に供給する方法（ALD 法）のいずれかの方法を用いることが可能である。

50

## 【0032】

従来は、Cu拡散防止膜とCu膜の密着性が悪いという問題があったが、本実施例では当該問題を解決し、Cuよりなる配線部の剥離の可能性が低く、信頼性の高い多層配線構造を形成することが可能となり、信頼性の高い半導体装置を形成することが可能となる。

## 【0033】

また、本工程の後に、さらに前記第2の絶縁層106の上部に第2+n(nは自然数)の絶縁層を形成し、それぞれの絶縁層に本発明による成膜方法を適用してCuよりなる配線部などを形成することが可能である。

## 【0034】

また、本実施例では、Cu拡散防止膜にはTaNからなる積層膜を用いているが、これに限定されるものではなく、様々なCu拡散防止膜を用いることが可能であり、例えば、Ta、Ta<sub>N</sub>、TaCN<sub>x</sub>、W、WN、WCNx、TiN、TaSiN、およびTiSiNよりなる群より選択されるいすれかの材料を含む膜や、またはこれらの積層膜などを組み合わせてCu拡散防止膜として用いることが可能である。これらのCu拡散防止膜を用いた場合に、本実施例によるPdを含む密着膜は、Cu配線部と当該Cu拡散防止膜の密着力を良好とする効果を奏する。

## 【0035】

また、前記第1の絶縁層103または前記第2の絶縁層106には、様々な材料を用いることが可能であり、例えば、シリコン酸化膜(SiO<sub>2</sub>膜)、フッ素添加シリコン酸化膜(SiOF膜)、SiCO膜、ポリマー膜などの有機高分子膜、またはこれらの膜を多孔質とした多孔質膜(ポーラス膜)などを用いることが可能である。

## 【0036】

次に、前記密着膜107Bを成膜する成膜装置の例について、図4～図5に基づき、説明する。

## 【0037】

図4は、本実施例による密着膜を成膜することが可能な成膜装置の一例である、CVD成膜装置10を模式的に示した図である。

## 【0038】

図4を参照するに、CVD成膜装置10は、例えば、上部が開口した、略円筒形の処理容器11と、当該処理容器11の開口部を塞ぐように、当該処理容器11上に設置された、例えば、いわゆるシャワーヘッド構造を有する供給部13を有している。

## 【0039】

前記処理容器11と前記供給部13によって画成される、前記処理容器11内部の空間である処理空間11Aの底部には、例えば半導体ウェハなどの被処理基板Wを保持する保持台12が設置されている。前記保持台12は、例えばヒータなどの加熱手段12Aを有し、被処理基板を加熱する構造となっている。

## 【0040】

前記処理容器11の底部には、排気口11Bに接続された、例えば真空ポンプなどの排気手段14が設置され、前記処理空間を排気することが可能に構成され、前記処理空間は、例えば、減圧状態となるように排気される。

## 【0041】

前記供給部13には、バルブ15Aが付された供給ライン15が接続され、さらに当該供給ライン15には、バルブ16Aが付され、成膜ガス源16Bに接続された成膜ガス供給ライン16と、バルブ17Aが付され、還元ガス源17Bに接続された還元ガスライン17とがそれぞれ接続されている。

## 【0042】

例えば、前記処理空間11Aに成膜ガスを供給する場合には、前記バルブ16A、15Aを開放して、前記成膜ガス源16Bから前記供給部13を介して成膜ガスを供給する。同様に、前記処理空間11Aに還元ガスを供給する場合には、前記バルブ17A、15Aを開放して、前記還元ガス源17Bから前記供給部13を介して還元ガスを供給する。

10

20

30

40

50

**【 0 0 4 3 】**

このようにして供給された成膜ガスと還元ガスが、加熱された被処理基板上で反応し、当該被処理基板上に密着膜を形成することが可能となる。

**【 0 0 4 4 】**

また、例えば、前記供給部 13 や前記保持台 12 には、高周波電力が印加されるようにしてもよい。

**【 0 0 4 5 】**

例えば、被処理基板上の Cu 拡散防止膜上に Pd を含む密着膜の一例として、例えば、

Pd 膜を形成する場合、前記成膜ガスとして、Pd (hfac)<sub>2</sub>、(C<sub>5</sub>H<sub>5</sub>)Pd (10

a11y1)、および Pd (a11y1)<sub>2</sub> のいずれか、また、例えば還元ガスとしては H<sub>2</sub> を用いることが可能である。また、CVD 成膜装置にて用いる成膜ガスは、常温・常圧では液体のものや固体のものを気化または昇華して用いることが可能であり、これらの成膜に係る原料をプリカーサと呼ぶ場合がある。

**【 0 0 4 6 】**

また、上記の成膜ガスと還元ガスを用いて形成された Pd 膜は、僅かな不純物（例えば僅かな有機物など）を含む場合もあるが、このような場合も含めて本実施例では Pd 膜と定義している。また、当該 Pd 膜に必要に応じて様々な添加物を添加して用いることも可能であるが、Cu 配線部との密着力を確保するためには、密着膜は Pd を主成分とすることが好ましい。

**【 0 0 4 7 】**

また、前記 CVD 成膜装置 10 の、成膜に係る動作は、図示を省略する記憶媒体とコンピュータを内蔵した制御装置 10S により、制御される。例えば、バルブ 15A, 16A, 17A などの開閉や、前記加熱手段 12A の温度制御などの動作などは、前記制御装置 10S によって制御される。

**【 0 0 4 8 】**

また、このような CVD 成膜装置は、例えば Cu 拡散防止膜や、Cu 膜を形成する場合にも用いることが可能である。

**【 0 0 4 9 】**

例えば、Cu 膜を形成する場合には、成膜ガスとして、Cu (hfac)<sub>2</sub>、Cu (aac)<sub>2</sub>、Cu (dpm)<sub>2</sub>、Cu (dibm)<sub>2</sub>、Cu (ibpm)<sub>2</sub>、Cu (edmd)<sub>2</sub>、Cu (hfac) TMVS、および、Cu (hfac) COD よりなる群より選択されるいずれかを用いることが可能である。例えば前記 CVD 装置 10 では、Cu 配線部を形成する場合に、シード層の形成や、シード層形成後の埋め込みに用いることが可能でありまたはシード層を形成する事無く埋め込みにより Cu 配線部を形成することもできる。

**【 0 0 5 0 】**

次に、図 5 には、本実施例による密着膜を成膜することが可能な成膜装置の一例である、ALD 成膜装置 20 を模式的に示す。

**【 0 0 5 1 】**

図 5 を参照するに、ALD 成膜装置 20 の概略は、内部に被処理基板 W を収納する処理容器 21 を有し、当該処理容器 21 内に形成される処理空間 21A の被処理基板上に、ガスライン 24 およびガスライン 29 を介して、それぞれ成膜ガスおよび還元ガスが供給される構造になっている。

**【 0 0 5 2 】**

前記処理空間 21A には、ガスライン 24 とガスライン 29 より、成膜ガスと還元ガスを交互に供給することで、被処理基板の反応表面への吸着を経由して原子層・分子層に近いレベルで成膜を行ない、これらの工程を繰り返し、いわゆる ALD 法により、被処理基板 W 上に所定の厚さの薄膜を形成することが可能となっている。このような ALD 法で形成された膜は、成膜温度が低温でありながら、不純物が少なく高品質な膜質が得られると同時に、微細パターンに成膜するにあたっては、良好なカバレッジ特性を得ることができ

10

20

30

40

50

る。

【0053】

次に、当該成膜装置20の詳細についてみると、前記処理容器21の内部には略円板状の基板保持台22が設置され、前記基板保持台22の中心には被処理基板である半導体被処理基板Wが載置される。前記基板保持台22には例えばヒータよりなる加熱手段22Aが内蔵されて前記被処理基板Wを所望の温度に加熱することが可能な構造となっている。

【0054】

前記基板処理容器21内の処理空間21Aは、排気口21Bに接続される、図示しない排気手段により真空排気され、前記処理空間21Aを減圧状態とすることが可能である。また、前記被処理基板Wは、前記処理容器21に設置された図示しないゲートバルブより前記処理容器21内に搬入もしくは搬出される。

【0055】

また、前記処理容器21内には、前記基板保持台22に対向するように、例えばニッケルやアルミニウムなどからなる略円筒状のシャワー・ヘッド部23が設置されており、前記シャワー・ヘッド部23の側壁面および当該シャワー・ヘッド部23と前記処理容器21の間には、例えば石英やSiN、AlNなどのセラミックなどからなるインシュレータ23Aが設けられている。

【0056】

また、前記シャワー・ヘッド部23上の、前記処理容器21の壁面には開口部が設けられて、絶縁体からなるインシュレータ23Bが設置されている。前記インシュレータ23Bには、高周波電源32に接続された導入線32Aが挿通され、前記導入線32Aは前記シャワー・ヘッド部23に接続されて、前記導入線32Aによって前記シャワー・ヘッド部23には高周波電源が印加される構造となっている。

【0057】

また、前記処理空間21Aに、成膜ガスを供給する前記ガスライン24と、前記処理空間21Aに、還元ガスを供給するガスライン29は、前記シャワー・ヘッド部23に接続され、成膜ガスと還元ガスは、当該シャワー・ヘッド部23を介して前記処理空間21Aに供給される構造になっている。また、前記ガスライン24およびガスライン29にはそれぞれ、インシュレータ24aおよび29aが挿入されており、ガスラインが高周波電力から隔離される構造になっている。

【0058】

また、前記ガスライン24には、当該ガスライン24に成膜ガスを供給するライン26と、当該ガスライン24に、例えばバージガスまたはキャリアガスなどを供給するガスライン25が接続されている。

【0059】

一方、前記ガスライン29には、当該ガスライン29に還元ガスを供給するガスライン30と、当該ガスライン29に、例えばバージガスなどを供給するガスライン31が接続されている。

【0060】

まず、前記ガスライン26についてみると、当該ガスライン26は、例えば、 $Pd(Hf_{0.8}C)_{2}$ などの、原料(プリカーサ)28Aが保持された原料容器28に接続されており、また前記ガスライン26には、例えば液体質量流量コントローラ26Dと、気化器26C、バルブ26A、バルブ26Bが設置されている。当該原料容器28には、バルブ27Aが付されたガスライン27が接続され、例えばHeなどの不活性ガスを前記原料容器28に導入し、原料28Aを前記ガスライン26側に押し出すことが可能になっている。前記ライン26に供給された、例えば液体よりなる原料は、前記液体質量流量コントローラ26Dによって流量が制御され、さらに前記気化器26Cによって気化され、成膜ガスとなる。

【0061】

また、前記ガスライン25には、質量流量コントローラ25Cと、バルブ25A、25B

10

20

30

40

50

B が付され、図示を省略する、例えば Ar などのガス供給源に接続されている。前記ガスライン 24 からは、前記ガスライン 25 から供給される Ar などのキャリアガスと共に、前記ガスライン 26 から供給される成膜ガスが、前記シャワーヘッド部 23 を介して前記処理空間 21A に供給される構造になっている。

#### 【0062】

一方、前記ガスライン 29 に接続された、前記ガスライン 30 には、図示を省略する、還元ガスである例えば H<sub>2</sub> ガスの供給源が接続され、質量流量コントローラ 30C と、バルブ 30A、30B が付されて、前記ガスライン 29 に供給される還元ガスの流量が制御される構造になっている。

#### 【0063】

また、前記ガスライン 29 にバージガスを供給するための前記ガスライン 31 には、バージガスである、例えば、Ar ガスの供給源が接続され、質量流量コントローラ 31C と、バルブ 31A、31B が付され、供給されるバージガスの流量が制御される構造になっている。

#### 【0064】

また、被処理基板上の Cu 拡散防止膜上に形成される密着膜の一例として、例えば、Pd 膜を形成する場合、前記成膜ガスとして、Pd(hfac)<sub>2</sub>、(C<sub>5</sub>H<sub>5</sub>)Pd(allyl)、および Pd(allyl)<sub>2</sub> のいずれか、また、例えば還元ガスとしては、H<sub>2</sub> を用いることが可能である。また、ALD 成膜装置にて用いる成膜ガスは、常温・常圧では液体のものや固体のものを気化または昇華して用いることが可能であり、これらの成膜に係る原料をプリカーサと呼ぶ場合がある。この場合、必要に応じてプリカーサを気化または昇華して用いればよい。

#### 【0065】

また、このような ALD 成膜装置は、例えば Cu 拡散防止膜や、Cu 膜を形成する場合にも用いることが可能である。

#### 【0066】

例えば、Cu 膜を形成する場合には、成膜ガスとして、Cu(hfac)<sub>2</sub>、Cu(acac)<sub>2</sub>、Cu(dpm)<sub>2</sub>、Cu(dibm)<sub>2</sub>、Cu(ibpm)<sub>2</sub>、Cu(edmd)<sub>2</sub>、Cu(hfac)TMVS、および、Cu(hfac)COD よりなる群より選択されるいずれかを用いることが可能である。例えば前記成膜装置 20 では、Cu 配線部を形成する場合に、シード層を形成することや、またはシード層を形成する事無く埋め込みにより Cu 配線部を形成することが可能である。

#### 【0067】

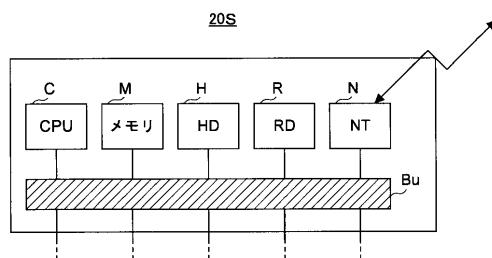

また、前記成膜装置 20 の、成膜に係る動作は、記憶媒体と、コンピュータ(CPU)を内蔵した制御装置 20S により、制御される。例えば、バルブ 25A、25B、26A、26B、27A、30A、30B、31A、31B の開閉や、前記加熱手段 22A の温度制御や前記高周波電源 32 の動作などは、前記制御装置 20S によって制御される。また、前記制御装置 20S の動作は記憶媒体に記憶されたプログラムにより行われる構造になっている。

#### 【0068】

図 6 は、前記制御装置 20S の構造を模式的に示した図である。図 6 を参照するに、前記制御装置 20S は、CPU(コンピュータ) C と、メモリ M、例えばハードディスクなどの記憶媒体 H、取り外し可能な記憶媒体である記憶媒体 R、およびネットワーク接続手段 N を有し、さらにこれらが接続されるバス Bu を有しており、当該バス Bu は、例えばバルブや加熱手段と接続される構造となっている。前記記憶媒体 H には、成膜装置を動作させるプログラムが記録されているが、当該プログラムは、例えば記憶媒体 R、またはネットワーク接続手段 NT を介して入力することも可能である。

#### 【0069】

例えば、前記 ALD 成膜装置 20 を用いて、密着膜や Cu 膜などの成膜を行う場合には、前記記憶媒体 H に記録されたプログラム(これをレシピと呼ぶ場合がある)によって前

10

20

30

40

50

記制御装置 20 S が A L D 成膜装置 20 を、以下に示すように動作させる。

【0070】

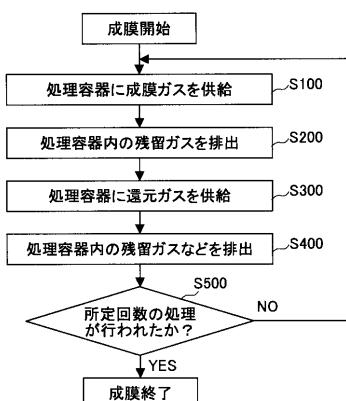

例えば、前記 A L D 成膜装置 20 によって、密着膜を形成する場合の、具体的な動作を示すフローチャートを、図 7 および図 8 に示す。

【0071】

まず、図 7 を参照するに、成膜処理が開始されると、ステップ 100 において、前記バルブ 25A, 25B, 26A, 26B, 27A が開放され、気化した前記原料 28A が、前記ガスライン 25 から供給される Ar と共に、前記ガスライン 24 を介して、前記処理空間 21A に供給される。

【0072】

本ステップにおいて、成膜ガスである、例えば  $Pd(hfac)_2$  が被処理基板上に供給されることで、被処理基板上に前記成膜ガスが吸着される。

【0073】

次に、ステップ 200 で、前記バルブ 25A, 25B, 26A, 26B, 27A を閉じて前記処理空間 21A への成膜ガスの供給を停止し、前記被処理基板上に吸着していない、未吸着で前記処理空間 21A に残留していた成膜ガスを、前記排気口 21B より前記処理容器 21A の外へと排出する。この場合、前記バルブ 25A, 25B、および前記バルブ 31A, 31B、を開放して、それぞれ前記ガスライン 24 およびガスライン 29 からバージガスとして Ar を導入して、前記処理空間 21A をバージしてもよい。この場合、速やかに残留した成膜ガスが処理空間より排出される。所定の時間のバージが終了後、前記バルブ 25A, 25B、および前記バルブ 31A, 31B を閉じる。

【0074】

次に、ステップ 300 において、前記バルブ 30A, 30B を開放し、前記質量流量コントローラ 30C で流量を制御することで、還元ガスである H<sub>2</sub> ガスが前記ガスライン 29 より前記処理空間 21A に供給され、被処理基板 W 上に吸着している前記成膜ガス ( $Pd(hfac)_2$ ) と反応し、例えば被処理基板上に形成された Cu 拡散防止膜上に Pd 膜が形成される。

【0075】

次に、ステップ 400 で、前記バルブ 30A, 30B を閉じて前記処理空間 21A への還元ガスの供給を停止し、前記被処理基板上の前記成膜ガスと反応していない前記処理空間 21A に残留していた還元ガスを、前記排気口 21B より前記処理容器 21A の外へと排出する。この場合、前記バルブ 25A, 25B、および前記バルブ 31A, 31B、を開放して、それぞれ前記ガスライン 24 およびガスライン 29 からバージガスとして Ar を導入して、前記処理空間 21A をバージしてもよい。この場合、速やかに残留した還元ガスや、または副生成物などが、処理空間より排出される。所定の時間のバージが終了後、前記バルブ 25A, 25B、および前記バルブ 31A, 31B を閉じる。

【0076】

次に、ステップ 500 においては、被処理基板上に必要な膜厚の薄膜を形成するために、必要に応じて成膜工程を再びステップ 100 に戻し、所望の膜厚となるまでステップ 100 ~ 400 からなる、いわゆる A L D 法による成膜工程である工程を繰り返した後に、成膜を終了する。

【0077】

このような A L D 法によって形成された膜は、膜中不純物が少なく膜質が良好であり、またパターン形状に成膜する場合のカバレッジが良好である特長を有している。

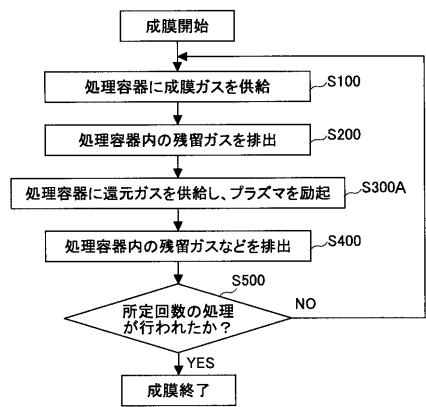

【0078】

また、上記の図 7 に示した成膜方法は、図 8 に示すように変更することも可能である。図 8 は、図 7 に示した成膜方法の変更例を示したフローチャートである。ただし図中、先に説明した部分には同一の参照符号を付し、説明を省略する。

【0079】

図 8 を参照するに、本図に示す成膜方法では、図 7 のステップ 300 に相当するステッ

10

20

30

40

50

300Aにおいて、ステップ300で行われる動作に加えてさらに、前記高周波電源32より前記シャワー・ヘッド部23に高周波電力を印加して、前記処理空間21Aにてプラズマ励起を行っている。この場合、前記処理空間のH<sub>2</sub>が解離されて、H<sup>+</sup>/H<sup>\*</sup>(水素イオンと水素ラジカル)となるため、被処理基板W上に吸着している前記成膜ガス(Pd(hfacc)<sub>2</sub>)との反応が促進され、効率よくPd膜を形成することが可能となる。このように、必要に応じて前記高周波電力32より高周波電力を印加し、処理空間にプラズマを励起することでガスが解離されるようにしてもよい。

#### 【0080】

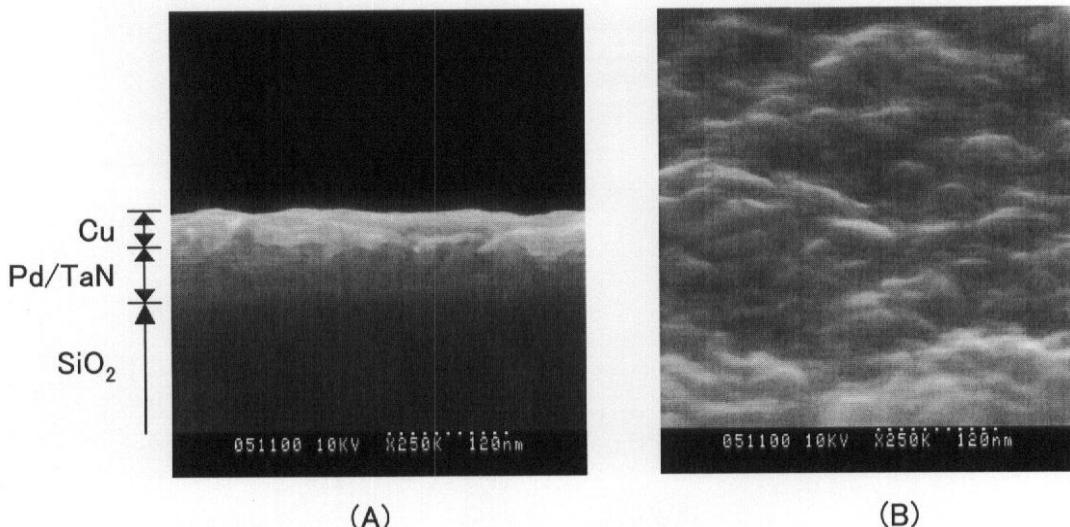

次に、本実施例による成膜方法を用いて、Cu拡散防止膜上にCu膜を形成した場合のSEM(走査型電子顕微鏡)写真を示す。

10

#### 【0081】

図9(A)は、シリコン酸化膜(SiO<sub>2</sub>膜)上にCu拡散防止膜であるTaN膜を形成し、当該TaN膜上に、本実施例による成膜方法を用いて、プリカーサにPd(hfacc)<sub>2</sub>を用いて、密着膜であるPd膜を形成し、当該密着膜上にCu膜を形成した場合の断面SEM写真であり、図9(B)は、図9(A)に示す構造を斜め方向(Cu膜側)からみたSEM写真である。

#### 【0082】

図9(A),(B)を参照するに、Cu拡散防止膜上に、剥がれや凝集が抑制されて、良好にCu膜が形成されている様子がわかる。

20

#### 【0083】

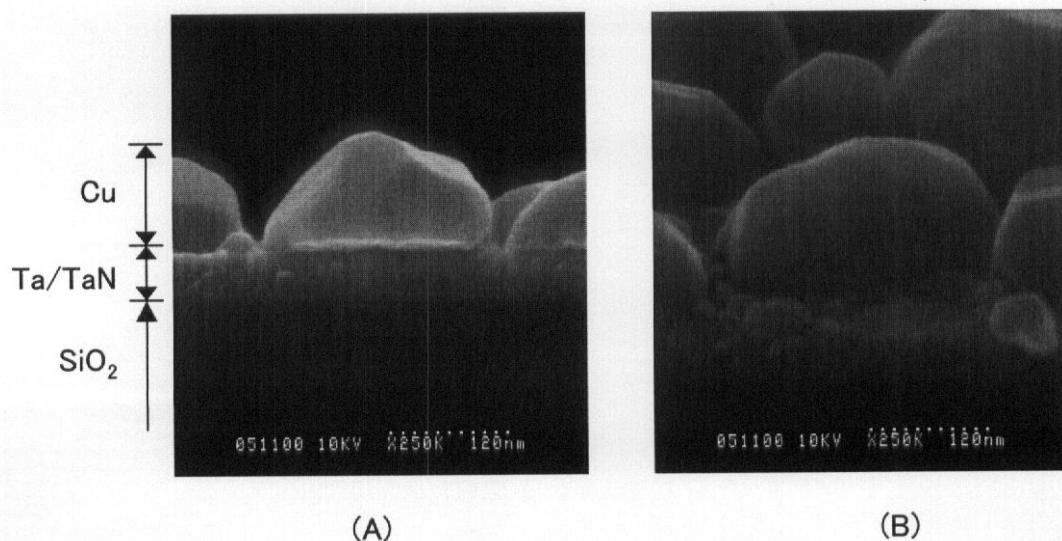

また、図10(A)はシリコン酸化膜上にCu拡散防止膜であるTa/TaN膜を形成し、当該Ta/TaN膜上に、Cu膜を形成した場合の、すなわち密着膜を形成しない場合の断面SEM写真であり、図10(B)は、図10(A)に示す構造を斜め方向(Cu膜側)からみたSEM写真である。

#### 【0084】

図10(A),(B)を参照するに、Cu拡散防止膜上に密着膜が形成されていない場合には、例えば当該SEM写真にみられるようにCuの凝集が生じる場合があり、またCu拡散防止膜とCu膜の密着性を確保することが困難であることがわかる。また、この場合には、エレクトロマイグレーション耐性に問題が生じる場合がある。

30

#### 【0085】

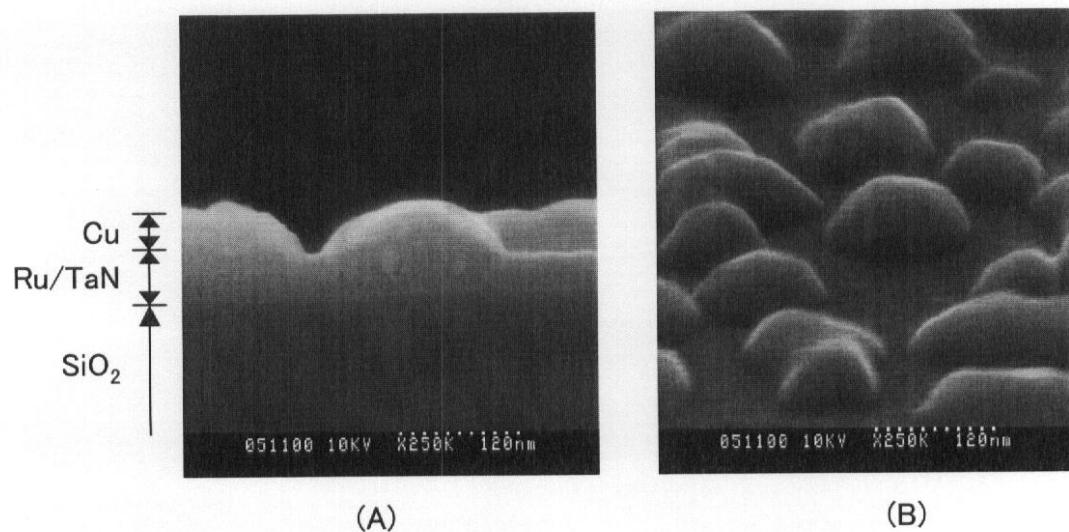

また、図11(A)は、シリコン酸化膜上にCu拡散防止膜であるTaN膜を形成し、当該TaN膜上に、Ru膜を形成し、当該Ru膜上にCu膜を形成した場合の断面SEM写真であり、図11(B)は、図11(A)に示す構造を斜め方向(Cu膜側)からみたSEM写真である。

#### 【0086】

図11(A),(B)を参照するに、Cu拡散防止膜上にRu膜が形成され、当該Ru膜上にCu膜が形成されている場合、密着膜が形成されていない場合にくらべてCuの凝集が改善しているもののその効果は充分ではなく、凝集により島状に形成されたCuが観察され、このような状態ではCu拡散防止膜とCu膜の密着性を確保することが困難であることが容易に推測できる。また、このように形成されたCu膜の場合、エレクトロマイグレーション耐性に問題が生じる可能性がある。

40

#### 【0087】

上記の図9(A),(B)、図10(A),(B)、および図11(A),(B)からわかるように、本実施例による成膜方法によってPdを含む密着膜を形成することにより、Cu拡散防止膜にCu膜を形成する場合のCuの凝集が抑制され、そのためにCu膜とCu拡散防止膜の密着性が良好となる効果を奏することがわかる。また、この場合、エレクトロマイグレーションやストレスマイグレーションに対する耐性も改善されると推察される。

#### 【0088】

以上、本発明を好ましい実施例について説明したが、本発明は上記の特定の実施例に限

50

定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

**【産業上の利用可能性】**

**【0089】**

本発明によれば、半導体装置のCu拡散防止膜とCu配線との密着力を良好とすることが可能となり、半導体装置の信頼性を良好とすることが可能となる。

**【図面の簡単な説明】**

**【0090】**

【図1】実施例1による成膜方法を示すフローチャート(その1)である。

【図2】(A)～(C)は、実施例1による半導体装置の製造方法を手順を追って示した図(その1)である。 10

【図3】(D)～(E)は、実施例1による半導体装置の製造方法を手順を追って示した図(その2)である。

【図4】実施例1による成膜方法を実施可能なCVD成膜装置の一例を示す図である。

【図5】実施例1による成膜方法を実施可能なALD成膜装置の一例を示す図である。

【図6】図5の装置に用いる制御装置の構成を模式的に示した図である。

【図7】図5の装置を用いて成膜を行う方法を示すフローチャート(その1)である。

【図8】図5の装置を用いて成膜を行う方法を示すフローチャート(その2)である。

【図9】(A),(B)は、Cu拡散防止膜上にCu膜を形成した状態を示すSEM写真(その1)である。 20

【図10】(A),(B)は、Cu拡散防止膜上にCu膜を形成した状態を示すSEM写真(その2)である。

【図11】(A),(B)は、Cu拡散防止膜上にCu膜を形成した状態を示すSEM写真(その3)である。

**【符号の説明】**

**【0091】**

10 CVD成膜装置

20 ALD成膜装置

11, 21 処理容器

12, 22 保持台

12A, 22A 加熱手段

13 供給部

13A ガス孔

23 シャワーヘッド部

23A, 23B, 24a, 29a インシュレータ

28 原料容器

28A 原料

32 高周波電源

10S, 20S 制御装置

H D 1, H D 2 記録媒体

15, 16, 17, 24, 25, 26, 27, 29, 30, 31 ライン

15A, 16A, 17A, 25A, 25B, 26A, 26B, 27A, 30A, 30B

, 31A, 31B バルブ

25C, 26D, 30C, 31C 質量流量コントローラ

26C 気化器

101 シリコン酸化膜

102 配線層層

103, 106 絶縁層

104, 107 配線部

104a, 107a 溝部

30

40

50

104b, 107b ホール部

104A, 107A Cu拡散防止膜

104B, 107B 密着膜

【図1】

【図2】

【図3】

【図4】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

F ターム(参考) 4M104 AA01 BB04 BB07 BB17 BB18 BB25 BB27 BB30 BB32 BB33

BB34 BB36 DD43 DD44 DD45 HH01 HH02 HH08

5F033 HH07 HH11 HH19 HH21 HH27 HH30 HH32 HH33 HH34 HH36

JJ07 JJ11 JJ19 JJ21 JJ27 JJ30 JJ32 JJ33 JJ34 JJ36

KK07 KK11 KK18 KK21 KK27 KK30 KK32 KK33 KK34 KK36

MM01 MM02 MM12 MM13 NN06 NN07 PP02 PP12 PP15 PP27

PP33 QQ09 QQ11 QQ37 RR01 RR04 RR11 RR21 RR29 XX05

XX06 XX13