(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4299370号

(P4299370)

(45) 発行日 平成21年7月22日(2009.7.22)

(24) 登録日 平成21年4月24日(2009.4.24)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 21/683 | (2006.01) |

| HO 2 N 13/00  | (2006.01) |

| B 23 Q 3/15   | (2006.01) |

| HO 1 L 21/68  | R         |

| HO 2 N 13/00  | D         |

| B 23 Q 3/15   | D         |

請求項の数 17 (全 15 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願平11-505689                 |

| (86) (22) 出願日 | 平成10年6月24日(1998.6.24)        |

| (65) 公表番号     | 特表2002-507326(P2002-507326A) |

| (43) 公表日      | 平成14年3月5日(2002.3.5)          |

| (86) 国際出願番号   | PCT/US1998/013159            |

| (87) 国際公開番号   | W01999/000889                |

| (87) 国際公開日    | 平成11年1月7日(1999.1.7)          |

| 審査請求日         | 平成17年6月24日(2005.6.24)        |

| (31) 優先権主張番号  | 08/883,068                   |

| (32) 優先日      | 平成9年6月27日(1997.6.27)         |

| (33) 優先権主張国   | 米国(US)                       |

|           |                                                                             |

|-----------|-----------------------------------------------------------------------------|

| (73) 特許権者 | ラム・リサーチ・コーポレーション<br>アメリカ合衆国 カリフォルニア州945<br>38 フリモント, クッシング・パークウ<br>エイ, 4650 |

| (74) 代理人  | 弁理士 五十嵐 孝雄                                                                  |

| (74) 代理人  | 弁理士 下出 隆史                                                                   |

| (74) 代理人  | 弁理士 市川 浩                                                                    |

| (74) 代理人  | 弁理士 加藤 光宏                                                                   |

最終頁に続く

(54) 【発明の名称】 双極静電チャックにおけるプラズマバイアス電圧のオフセット方法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

静電チャック電源の基準ノードの基準電圧を制御するよう構成された制御回路であって、該静電チャック電源が第1埋込導体と第2埋込導体とを有する双極静電チャックに基板をクランプするように構成され、該静電チャック電源が前記第1埋込導体に接続するよう構成された第1出力を有し、該第1出力が前記基準電圧を基準とする第1出力電圧を有し、前記第1出力電圧は、前記基準電圧に定電圧を足した値であり、該静電チャック電源が、該第2埋込導体に接続されるよう構成された第2出力をさらに有し、該第2出力が、前記基準電圧を基準とする第2出力電圧を有し、前記第2出力電圧は、前記基準電圧から前記定電圧を引いた値であり、前記第1出力電圧と前記第2出力電圧との差は、前記定電圧の2倍に等しく、

前記第1出力と前記第1埋込導体との間に直列接続された第1抵抗器と、

前記第1抵抗器における第1電圧降下を検出するため該第1抵抗器に接続された第1增幅器と、

前記第2出力と前記第2埋込導体との間に直列接続された第2抵抗器と、

前記第2抵抗器における第2電圧降下を検出するため該第2抵抗器に接続された第2增幅器と、

前記第1增幅器と前記第2增幅器との出力に接続され、制御信号を出力するための出力を有する差動增幅器であって、前記制御信号は、前記第1電圧降下と前記第2電圧降下との差に概ね比例すると共に、前記第1抵抗器における第1電流と前記第2抵抗器における第

10

20

2電流との差に概ね比例する、差動増幅器と、

前記基準ノードに接続された出力と前記差動増幅器の出力に接続された入力とを有し、前記制御信号に応じて、出力側において、前記第1電流と前記第2電流との前記差を概ね0に低減する前記基準電圧の値を生成する可変電圧電源とを備える制御回路。

【請求項2】

請求項1に記載の制御回路において、前記チャックは、 $10^6$  -cmから $10^{18}$  -cmの範囲の抵抗率を有する抵抗材料によって形成されている制御回路。

【請求項3】

その内部に配置されている第1埋込導体と第2埋込導体とを有する双極静電チャックに接続されるよう構成された電源であって、

可変基準電圧を有する基準ノードと、

前記第1埋込導体に接続されるよう構成され、前記基準ノードを基準とする第1出力電圧を有する第1出力であって、前記第1出力電圧は、前記基準電圧に定電圧を足した値である第1出力と、

前記第2埋込導体に接続されるよう構成され、前記基準ノードを基準とする第2出力電圧を有する第2出力であって、前記第2出力電圧は、前記基準電圧から前記定電圧を引いた値であり、前記第1出力電圧と前記第2出力電圧との差は、前記定電圧の2倍に等しい第2出力と、

前記第1出力の第1電流と前記第2出力の第2電流との電流差を検出するため該第1出力と該第2出力とに接続された制御回路であって、該電流差に概ね比例する制御電圧を、該制御回路の制御出力に出力する制御回路と、

前記制御電圧を受けるよう構成された供給回路であって、前記制御回路に応じて、前記基準電圧を前記基準ノードに出力して、前記電流差を概ね0に駆動する供給回路とを備える電源。

【請求項4】

請求項3に記載の電源において、前記制御回路はさらに、

前記第1出力と前記第1埋込導体との間の直列の第1抵抗器と、

前記第1抵抗器における第1電圧降下を検出するため該第1抵抗器に接続された第1増幅器と、

前記第2出力と前記第2埋込導体との間の直列の第2抵抗器と、

前記第2抵抗器における第2電圧降下を検出するため該第2抵抗器に接続された第2増幅器とを含む電源。

【請求項5】

請求項4に記載の電源において、前記制御回路はさらに、前記制御電圧を発生させるため前記第1増幅器と前記第2増幅器の出力に接続された差動増幅器を含む電源。

【請求項6】

請求項4に記載の電源であって、前記チャックは、 $10^6$  -cmから $10^{18}$  -cmの範囲の抵抗率を有する抵抗材料によって形成されている電源。

【請求項7】

プラズマ処理センターにおいて基板を第1埋込導体と第2埋込導体とを有するチャックにクランプする方法であって、

基準ノードと第1出力と第2出力とを有する第1電源を提供し、前記第1出力および第2出力は制御回路に接続され、前記第1出力は前記基準ノードを基準とする第1出力電圧を有し、前記第2出力は前記基準ノードを基準とする第2出力電圧を有し、

前記第1埋込導体を前記第1出力に接続し、

前記第2埋込導体を前記第2出力に接続し、

前記第1出力の第1電流と前記第2出力の第2電流との電流差を前記制御回路によって検出し、

前記制御回路から、前記電流差に概ね比例すると共に、第2電源から出力される電位レベルを制御する制御電圧を前記第2の電源に対して出力し、

10

20

30

40

50

前記第2電源は、ノードにおいて前記制御電圧を受け取り、受け取った前記制御電圧に応じて、前記基準ノードに前記電位レベルを出力することを備える方法。

【請求項8】

請求項7に記載の方法において、前記制御回路は、前記第1出力と前記第1埋込導体との間の直列の第1抵抗器と前記第2出力と前記第2埋込導体との間の直列の第2抵抗器とを含み、該制御回路はさらに前記第1抵抗器における電圧降下を検出するための第1増幅器と、前記第2抵抗器における電圧降下を検出するための第2増幅器とを含む方法。

【請求項9】

請求項8に記載の方法において、前記第1抵抗器と前記第2抵抗器の値が概ね等しい方法。

10

【請求項10】

請求項8に記載の方法において、前記第1抵抗器が $500\text{ k}\Omega$  + / - 1%の値を有し、前記第2抵抗器が $500\text{ k}\Omega$  + / - 1%の値を有する方法。

【請求項11】

請求項8に記載の方法において、前記制御回路はさらに、前記制御電圧を発生させるため前記第1増幅器の出力と前記第2増幅器の出力とに接続された差動増幅器を含む方法。

【請求項12】

請求項10に記載の方法において、前記チャックは $10^{10}\text{ -cm}$ から $10^{11}\text{ -cm}$ の範囲の抵抗率を有する材料にて形成される方法。

【請求項13】

静電チャック電源の基準ノードの基準電圧を制御するように構成された制御回路であって、該静電チャック電源は第1埋込導体と第2埋込導体を有する双極静電チャックに基板をクランプするように構成され、該静電チャック電源は該第1埋込導体に接続されるよう構成された第1出力を有し、該第1出力は該基準電圧を基準とする第1出力電圧を有し、該静電チャック電源はさらに該第2埋込導体に接続されるよう構成された第2出力を有し、該第2出力は該基準電圧を基準とする第2出力電圧を有し、

前記第1出力と前記第1埋込導体との間に直列接続された第1抵抗手段と、

前記第1抵抗手段における第1電圧降下を検出するため該第1抵抗手段に接続された第1検出手段と、

前記第2出力と前記第2埋込導体との間に直列の第2抵抗手段と、

20

前記第2抵抗手段における電圧降下を検出するため該第2抵抗手段に接続された第2検出手段と、

制御電圧を発生させるために前記第1検出手段と前記第2検出手段との出力に接続された差動増幅手段と、

前記差動増幅手段の出力に接続され、前記制御電圧に応じて、前記基準ノードに前記基準電圧を出力するよう構成された回路手段とを備える制御回路。

【請求項14】

請求項3に記載の電源において、前記供給回路は可変電圧電源を含む電源。

【請求項15】

請求項13に記載の制御回路において、前記第1抵抗手段は第1抵抗器であり、前記第2抵抗手段は第2抵抗器である制御回路。

30

【請求項16】

請求項13に記載の制御回路において、前記第1検出手段は第1増幅器であり、前記第2検出手段は第2増幅器である制御回路。

【請求項17】

請求項13に記載の制御回路において、前記回路手段は可変電圧電源である制御回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置と半導体製造用装置に関する。より詳細には、本発明は、プラズマ

40

50

処理チャンバにおいて半導体基板を双極静電チャックにクランプするための改良装置および方法に関する。

【背景技術】

【0002】

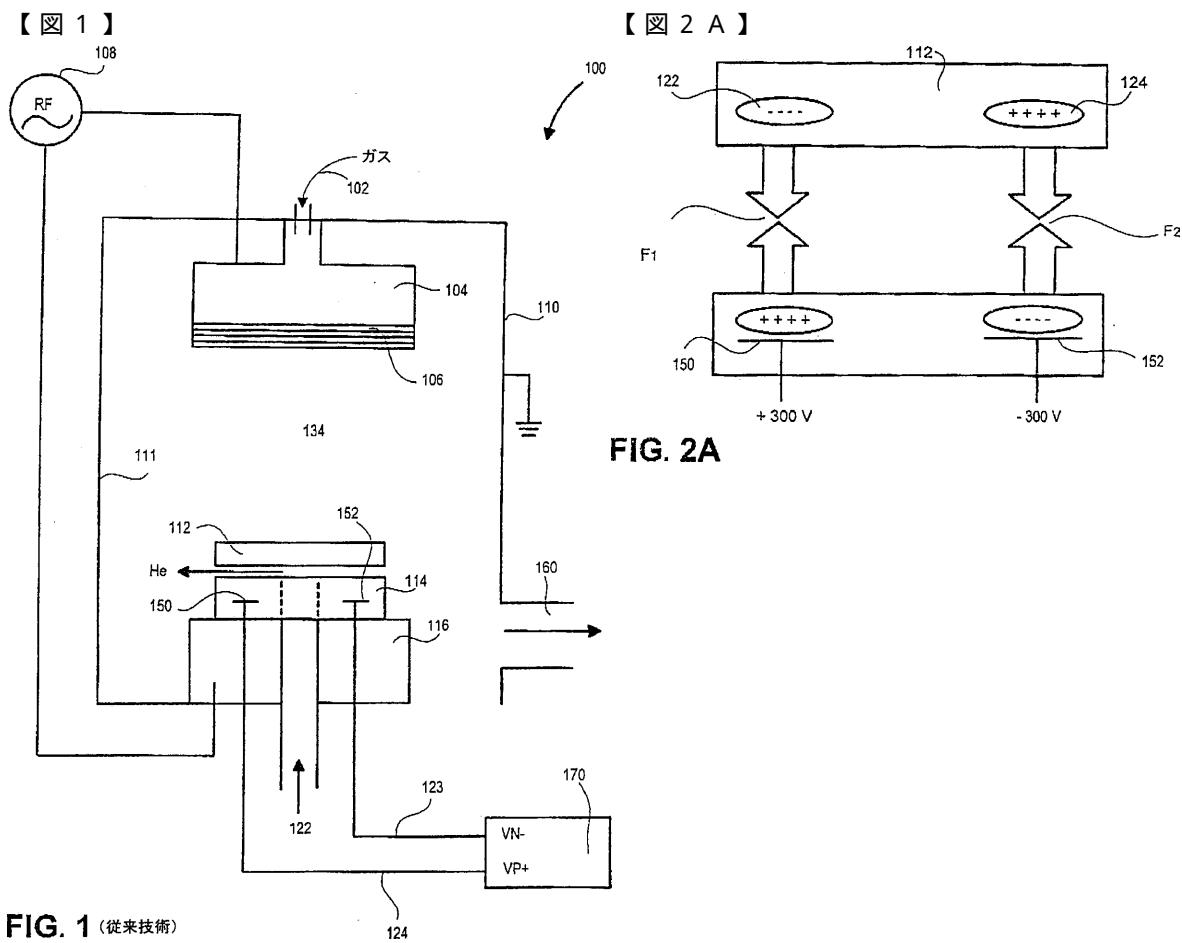

プラズマ処理システムにおける双極静電チャックの使用は、広く知られている。説明を容易にするため、双極静電チャックの使用に適したチャンバを表す基板処理チャンバの概略図を図1に示す。図1において、基板プラズマ処理システム100はプラズマ処理チャンバ110を含む。チャンバ110の内部にはRF発生器108によって励磁されるシャワヘッド型またはTCPコイルを表す電極104が配置されている。

【0003】

チャンバ110の上部には、ガス状原料物質（例えば、エッティングガス）が送り込まれるガスオリフィス102が電極104の上部へと延出するように設けられている。この実施例ではシャワヘッド型電極104は、半導体基板またはフラットパネルディスプレイなどを表す基板112上のRF誘導プラズマ領域134へとガス状原料物質を拡散させるための複数のバッフル106を含む。ガス状原料物質は、チャンバの壁に穿設されたポートから、または基板の下に配置されたガスリング装置から放出される。

【0004】

チャンバ110に挿入された基板112は、双極静電チャック114上に載置される。双極静電チャック114は、下部電極116と一体的に取付けられ、電気的に接続されている。したがって、双極静電チャック114と下部電極116のRF電位は同一となる。下部電極116は一般的にRF発生器108からRF出力を受けとる。電源170は、導線123により第1埋込板152に負バイアス電圧 $V_N$ を送るとともに、導線124により第2埋込板150に正バイアス $V_P$ を供給する。

【0005】

RF発生器108により供給されるRFエネルギーから電源170を保護するため、電源170とRF発生器108との間にRFフィルタ（従来型なので、簡略化のため図1では省略）を配設してもよい。同様にRF発生器108が、電源170から供給される直流電位レベルの影響を受けないよう、電源170とRF発生器108との間に直流阻止コンデンサ（従来型なので、簡略化のため図1では省略）を設けてもよい。

【0006】

下部電極116と静電チャック114の両者を貫通し、冷却剤ポート122が延在している。加圧された（一実施例では、例えば約5-10 Torr）ヘリウム冷却ガスが冷却材オリフィス122から導入される。ヘリウム冷却ガスは基板112の下面に衝突し、処理中に基板の温度を正確に調節するための熱伝導媒体として作用するので、均一かつ反復的な処理結果が得られる。プラズマ処理中にあっては、ポート160からガスを抜くことによりチャンバ110内の圧力は低く、例えば一実施例では約5から25 Torrに維持されることが望ましい。エッティングに適したチャンバ温度（例えば一実施例では約70°C）に維持するため、複数のヒータ（簡略化のため、図1では省略）を設けることができる。接地への電気経路を設けるため、通常、チャンバ110の壁111は接地されている。

【0007】

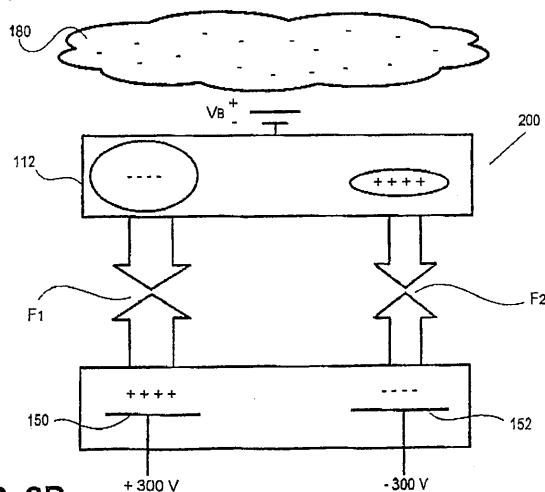

図2Aは図1の双極静電チャック114の断面を詳細に示す。名前が示すように双極静電チャック114は、2枚の埋込板、すなわち負帯電埋込板152と正帯電埋込板150とを有する。双極静電チャック114の両埋込板は図1の電源に接続されている。電源170がオンになると、埋込板150は電源170により共通の基準電位レベルに対して正にバイアスされる。電源170はまた、共通の基準電位レベルに対して埋込板152を負にバイアスする。埋込板150と152は固定位置にあるため、帯電埋込板により発生する静電界は、各埋込板の周囲領域に良好に画定される。

【0008】

p型の半導体ウエハの場合、基板112の孔は負バイアス埋込板152を直接被覆する基板領域へと移動する。この結果、埋込板152により静電チャック114に発生する電界

10

20

30

40

50

と電界強度が同じであると共に極性が逆の実効正電荷領域が形成される。結果的に、正バイアス埋込板 150 を直接被覆する基板 112 の領域に、実効負電荷領域が形成される。同様にして、n型半導体ウエハの場合も基板 112 内の電子は正の埋込板 150 を直接被覆する基板 112 の領域へと移動する。したがって、埋込板 150 により静電チャック 114 に発生する電界と電界強度は同じで極性が逆の実効負電荷領域が形成される。その結果、負バイアス埋込板 152 を直接被覆する基板 112 の領域に実効正電荷領域が形成される。

#### 【 0 0 0 9 】

当業者には周知のように、基板 112 と静電チャック 114 のバイアス板 150, 152 とに互いに逆の電荷を持つ領域が存在することにより、基板 112 と静電チャック 114 を結合させる誘導静電力が発生する。一例として図 2A には正帯電板 150 と基板 112 の負帯電領域 122 との間に静電力  $F_1$  が図示されている。図 2A には、負帯電板 152 と基板 112 の正帯電領域 124 との間に静電力  $F_2$  も図示されている。当業者にとって周知のように、力  $F_1$  の強さは、バイアス板 150 と帯電領域 122 との間の電位差に正比例する。同様に  $F_2$  の強さはバイアス板 152 と帯電領域 124 との電位差に正比例する。この例では静電力  $F_1$  と  $F_2$  は基板 112 を静電チャック 114 にクランプする作用を行う。

#### 【 0 0 1 0 】

一般的にプラズマ処理中は、加工物すなわち基板に印加されるクランプ力が平衡を保つ(すなわち静電力  $F_1$  と静電力  $F_2$  の強さは概ね等しい)ことが望ましい。

#### 【 0 0 1 1 】

しかし、チャンバ 110 に負帯電プラズマを導入すると、基板 112 はプラズマ誘導バイアス -  $V_B$  により静電チャックに対して負バイアスされる。一例として図 2B には静電クランプ力  $F_1$  と  $F_2$  への負帯電プラズマ 180 の影響が図示されている。基板 112 のプラズマ誘導バイアス -  $V_B$  により、基板 112 の誘導帯電領域 122 と 124 およびバイアス埋込板 150 と 152 (電源 170 により共通の接地に対して一定の電位に保持される)との間の相対的電圧電位低下がオフセットされる。静電力  $F_1$  と  $F_2$  は領域 122, 124 と板 150, 152 との間の相対的電位差に正比例するため、プラズマ誘導バイアス -  $V_B$  はクランプ力  $F_1$  を増大させ力  $F_2$  を減少させることによりクランプ力  $F_1$  と力  $F_2$  の平衡を崩す。

#### 【 0 0 1 2 】

この状態を説明するため、電源 170 が共通の基準電圧レベルに対して正電極 204 を +350V、負電極 206 を -350V にバイアスする場合を検討する。プラズマをオフにすると、基板の電位は共通の基準電圧レベルに対して 0V となり、双極チャック 114 の両極とこれらを被覆する基板領域との間の電位差はそれぞれ +350V と -350V となる。

#### 【 0 0 1 3 】

しかしプラズマの存在により基板 112 が負に帯電すると、基板と双極静電チャックの二極との間の電位差は非対称となる。例えば基板バイアス電圧はプラズマがオンになると -100V となる。この場合、正極と負バイアス基板の間の電位差は +450V (すなわち +350V - (-100V)) まで上昇する。しかし負極と負バイアス基板の間の電位差は -250V (すなわち -350V - (-100V)) までしか低下しない。電位差の低下により、負極とウエハ間の静電保持力が低下する。結果的に何らかの熱交換ガスが放出されて、温度調節および/または処理の変動は不適切なものとなる。場合によっては、基板を双極チャックに保持する静電力は、ヘリウム冷却圧力とチャンバ内の低圧との間の圧力差により基板に加えられる力に抗するのに不十分なほど弱くなることもあり、その結果、基板がチャックの表面から「突然離れてしまう」ことになる。

#### 【 0 0 1 4 】

さらに、プラズマ誘導負基板バイアスは、負バイアス基板と双極チャックの正極との間の電位差を過度に増加させることがある。電位差が極端に高いと、基板の下面とチャックの

10

20

30

40

50

上面の間にアーク（すなわちスパーク）を発生させたり過剰な電流をプラズマに出入りさせ、その結果、食孔跡損傷（ピットマークダメージ）を引き起こす。チャックの表面は時間とともに、熱交換ガスが正常にシールされた状態に維持するのが不可能となるほどの損傷を受ける。

【0015】

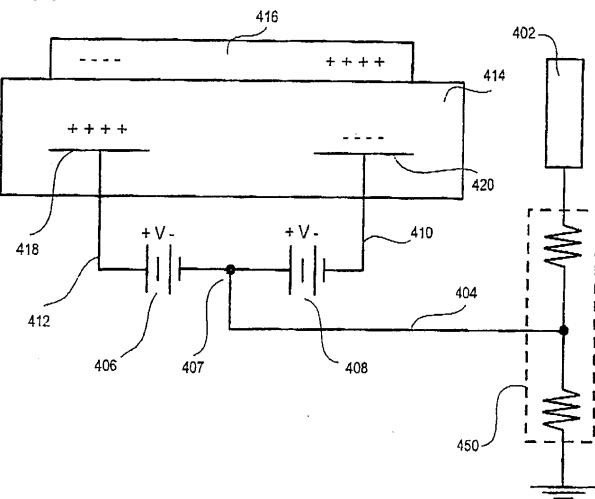

プラズマ誘導バイアスを補償するための先行技術による試みが、図3に示されている。静電チャック414は、負バイアス埋込板420と正バイアス板418とを含む。直流電源406と直流電源408は、基板416に反対かつ等しい帯電領域を形成するため可変接地基準ノード407に対して必要な電圧電位を板418と420にそれぞれ供給する。この反対かつ概ね等しい帯電領域は、必要なクランプ力を生み出す。ピックアップピン402は、ウエハ416で発生したプラズマ誘導バイアスを検出するようにチャンバ内に配置され、このようにして基準ノード407を変えるのに必要な入力を提供する。可変接地基準ノード407は、板418と420に印加される電位を適当に上下させることにより、誘導プラズマバイアスを補償するという効果を持つ。

10

【0016】

しかしピックアップピン402の使用には不都合な点が多い。その一つは、ピックアップピン402は基板416におけるプラズマ誘導バイアスを概算するのみという点にある。さらにこの概算は、ユーザによる制御が不可能な多くの要因に影響される。一例を挙げると、ピックアップピン402は、時間超過に伴って強力なプラズマイオンがピックアップピンの粒子を離脱させてチャンバ内のプラズマを汚染させるスパッタリングとして当該技術分野で周知のプラズマ誘導ダメージを受ける。このダメージは、望ましくない汚染を生じさせるだけでなく、定期的な校正と調整（すなわち、ピックアップピン420の電気的性質の変化を補償するための抵抗器ブリッジ450を設けること）に加えて、最終的には著しい稼働休止時間と生産高の損失をもたらす交換を必要とするのでピックアップピンの電気的性質を変えてしまうこともある。

20

【0017】

ピックアップピン402が位置する領域のプラズマと、基板416の表面に衝突するプラズマとが大きく異なっている場合、ピックアップピン402によっては基板416のプラズマ誘導バイアスを適切に補償することはできない。このピックアップピン402で見られるプラズマとウエハ416のプラズマとの違いは、例えば空間的变化（すなわちプラズマの密度／温度の径方向の分布）、不規則な幾何学形状によるプラズマ自体の不均一性といった要因による。実際、これらの要因のいずれか一つでも存在する場合、プラズマ誘導バイアス補償機構としてのピックアップピン402の使用は満足のいくものとならない。

30

【発明の開示】

【発明が解決しようとする課題】

【0018】

以上から見て、プラズマの存在下では特に、双極静電チャックへの基板のクランプを改良するための技術向上が望ましい。コスト削減および／または汚染低減のため、ピックアップピンおよび／または第2電源もしくは複雑な制御回路の使用を必要としないことが、改良技術にとって望ましい。

40

【課題を解決するための手段】

【0019】

一実施形態において本発明は、静電チャック電源の基準ノードの基準電圧を制御するよう構成された制御回路に関する。静電チャック電源は、基板を双極静電チャックにクランプするよう構成されている。静電チャックは、第1埋込導体と第2埋込導体とを有する。静電チャック電源は、第1埋込導体と接続されるよう構成された第1出力を有する。第1出力は、基準ノードの基準電圧を基準とする第1出力電圧を有する。静電チャック電源は、第2埋込導体と接続されるよう構成された第2出力をさらに有する。第2出力は、基準ノードの基準電圧を基準とする第2出力電圧を有する。

【0020】

50

制御回路は、第1出力に直列接続された第1抵抗器と、第1抵抗器における第1電圧降下を検出するため第1抵抗器に接続された第1増幅器と、第2出力に直列接続された第2抵抗器と、第2抵抗器における第2電圧降下を検出するため第2抵抗器に接続された第2増幅器とを含む。

#### 【0021】

別の実施形態では、第1埋込導体と第2埋込導体とを有する双極静電チャックと接続されるよう構成された電源が開示されている。電源は、基準ノードと、第1出力が基準ノードを基準とする第1出力電圧を有するよう、第1埋込導体と接続される構成の第1出力を含む。この電源は、第2埋込導体と接続されるよう構成された第2出力をさらに有し、第2出力は、基準ノードを基準とする第2出力電圧を有する。この電源は、第1出力と第2出力とに接続された制御回路をさらに含む。この制御回路は、第1出力の第1電流と第2出力の第2電流との電流差を検出する。この制御回路は、制御回路の制御出力において、基準ノードの電位レベルを制御するための制御電圧を出力する。制御電圧は、電流差に概ね比例する。

10

#### 【0022】

さらに別の実施形態では、プラズマ処理センターで基板を第1埋込導体と第2埋込導体とを有するチャックにクランプする方法が開示されている。この方法には以下の作業工程が含まれる。基準ノードと第1出力と第2出力を有し、前記第1出力および第2出力が制御回路に接続されている第1電源を提供する工程。この実施例では、第1埋込導体が第1出力に接続され第2埋込導体が第2出力に接続され、第1出力の第1電流と第2出力の第2電流との電流差が制御回路によって検出される。制御回路は、電流差に概ね比例すると共に、第2電源から出力される電位レベルを制御する制御電圧を第2の電源に対して出力し、第2電源は受け取った制御電圧に応じて、基準ノードに電位レベルを出力する。制御電圧は、電流差に概ね比例する。

20

#### 【0023】

また別の実施形態では、静電チャック電源の基準ノードの基準電圧を制御するよう構成された制御回路が開示されている。静電チャック電源は、第1埋込導体と第2埋込導体とを有する双極静電チャックに基板をクランプするように構成されている。静電チャック電源は、第1埋込導体に接続されよう構成された第1出力を有する。第1出力は、基準ノードの基準電圧を基準とする第1出力電圧を有する。静電チャック電源は、第2埋込導体に接続されるよう構成された第2出力をさらに有する。第2出力は、基準ノードの基準電圧を基準とする第2出力電圧を有する。制御回路は、第1出力に直列接続された第1抵抗手段を含む。第1抵抗手段での第1電圧降下を検出するため、第1検出手段が第1抵抗手段に接続されている。制御回路は、第2検出手段とともに第2出力に直列接続された第2抵抗手段をさらに含む。第2検出手段は、第2抵抗手段での第2電圧降下を検出するため、第2抵抗手段に接続されている。

30

#### 【0024】

添付図面の図において本発明は限定のためではなく例示のために図示されている。理解を容易にするため以下の図では、同様の参照番号は同様または類似の要素を示す。

#### 【発明を実施するための最良の形態】

40

#### 【0025】

添付図面に図示された、いくつかの好適な実施例について、本発明を詳細に説明する。以下の説明では、本発明の完全な理解を促すために特定の詳細事項が数多く記載されている。しかしながら、これら特定の詳細の一部または全てがない場合でも、本発明を実行できることは当業者にとって明らかであろう。他の例では、本発明が不必要に不明瞭となることを避けるため周知の処理工程については詳細に記されていない。

#### 【0026】

本発明は、自己バイアス電源の使用による、プラズマ処理チャンバ内の双極静電チャックにおけるプラズマ誘導バイアス電圧の補償に関する。本発明の一実施例では、電源は、プラズマ処理中に印加されるバイアス電圧の量を測定するため静電チャックの漏れ電流特性

50

を利用する。バイアス電圧は電源の正の導線と負の導線の間で漏れ電流をオフセットする。これにより、プラズマ誘導バイアス電圧を補償する接地基準のオフセット効果を最終的に有するフィードバックループへの入力が形成される。

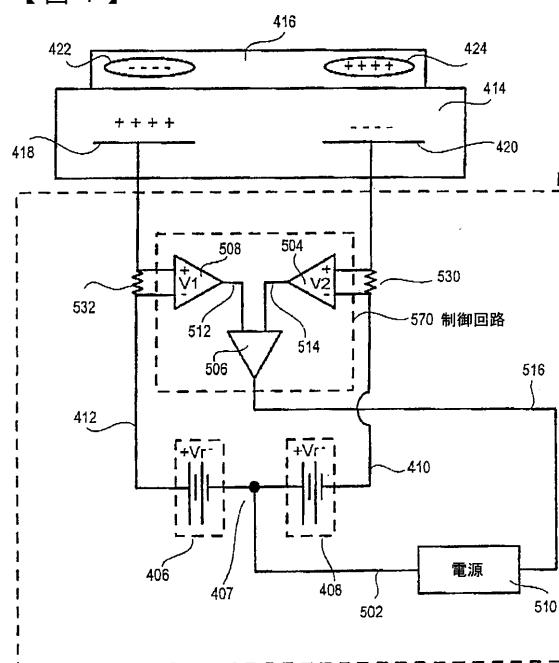

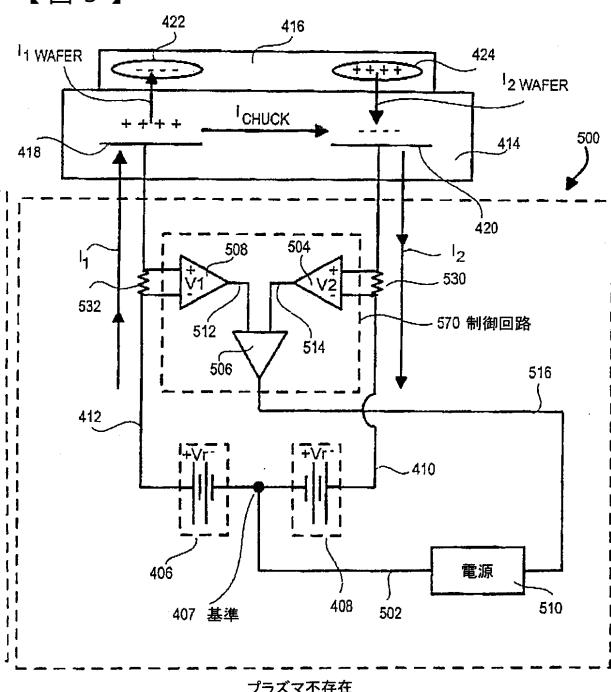

【0027】

図4は、本発明の一実施例にしたがって、双極静電チャック、例えば図4のチャック414の板に不均衡な電圧を供給するための自己バイアス静電チャック電源500を示す。図4の構成では、自己バイアス静電チャック電源500には、可変電圧電源510が含まれている。可変電圧電源510は、制御信号516（例えば0Vから5Vの直流信号）を入力として受信し、正または負の接地基準ノード407を出力端子502にて出力する。本実施例では、可変電圧電源510は、カリフォルニア州エル・ケイジョン（El Cajon）市所在のアメリカン・ハイ・ボルテージ社（American High Voltage, Inc.）のTC5電圧電源を表しているが、他の従来型電源（可変の有無を問わず）も使用され得る。

10

【0028】

可変電圧電源510の出力端子502は、接地基準ノード407により直流電源の陽極406と直流電源の陰極408とに接続されている。直流電源の陰極406は、自己バイアス静電チャック電源500の第1脚部412により静電チャック414の埋込板418に接続されている。この実施例では埋込板418と直流電源の陰極406とに、抵抗器532が直列接続されている。抵抗器532は絶縁増幅器508の入力ノードに並列接続され、抵抗器532における電圧降下 $V_1$ によって絶縁増幅器508の入力が決まることを望ましい。

20

【0029】

図4の実施例では、直流電源の陽極408は、自己バイアス静電チャック電源500の第2脚部410により、静電チャック414の埋込板420に接続される。この実施例では、埋込板420と直流電源408の陽極408とに抵抗器530が直列接続される。抵抗器530は絶縁増幅器504の入力ノードに並列接続され、抵抗器530における電圧降下 $V_2$ によって絶縁増幅器504の入力が形成されることが望ましい。

30

【0030】

この例では、絶縁増幅器504と絶縁増幅器508とは、カリフォルニア州サンタクララ市所在のアナログ・デバイシズ（Analog Devices）社製のAD202KY絶縁増幅器を表すが、他の従来型絶縁増幅器（可変の有無を問わず）を使用してもよい。抵抗器530と抵抗器532は、一例では約500k $\Omega$  +/- 1%の抵抗値を持つとよい。

【0031】

既述の実施例によれば、絶縁増幅器508の出力ノード512と絶縁増幅器504の出力ノード514は各々、差動増幅器506への一对の入力の一つを形成する。差動増幅器506は可変電源510への入力制御信号を形成する出力信号516を有する。このようにして、絶縁増幅器504, 508、さらに差動増幅器506を含む制御回路570が形成される。この例では差動増幅器506はカリフォルニア州サンタクララ市所在のアナログ・デバイシズ社製のOP490GP差動増幅器が使用されているが、他の従来型差動増幅器も使用可能である。

40

【0032】

上述の実施例では、抵抗器530, 532は固定式でも可変式でも、抵抗要素の任意の組合せでもよい。可変抵抗器の場合、ユーザは、制御回路570に固有の不均衡の補償、および/または、システム校正および/または操作中の誘導変化（例えば静電チャック414またはチャンバの電気的特性）の調整を行うことができる。

【0033】

上の実施例では、静電チャック414は抵抗材料で形成される。一例を挙げると、 $10^6$  -  $10^{18}$  -cmの範囲、より望ましくは $10^8$  -  $10^{14}$  -cmの範囲の抵抗率を持つ材料が望ましく、 $10^{10}$  -  $10^{11}$  -cmの範囲が好適である。基板416は、抵抗率が $10^{40}$  -cmのn型またはp型の半導体材料の形式をとる。抵抗材料が電位差にさらされると電流が流れることは、当該技術分野では周知である。オームの法則 $I=V/R$ （I:電流、

50

V : 抵抗 R における電位差 ( すなわち電圧降下 ) ) にしたがって、電流は高電位領域から低電位領域に流れる。図 5 において、抵抗 R は単一の抵抗器または複数の抵抗器群などの個別要素である。別の実施例では、R は埋込板 418 と埋込板 420 間の領域のような分散要素でもよい。一例を挙げると、埋込板 418、420 が基準ノード 407 に対してそれぞれ +V と -V にバイアスされると、電位差  $2V_R$  により漏れ電流  $I_{CHUCK}$  が板 418 から板 420 に流れる。漏れ電流  $I_{CHUCK}$  は板 418 と 420 に印加されたバイアスの差に概ね左右される。

#### 【 0034 】

作業時に半導体ウエハ 416 で表される加工物は、プラズマチャンバ 110 にプラズマを導入する前に静電チャック 414 上に載置される。ウエハ 416 を静電チャック 414 に取付け固定するため、直流電源 406 は基準ノード 407 に対して +V ボルトまで埋込板 418 にバイアスをかける。同時に直流電源 408 は、埋込板 420 にも基準ノード 407 に対して -V ボルトまでバイアスをかける。上述のように、バイアスをかけられた埋込板 418 により、ウエハ 416 の領域 422 には強度が等しく極性が逆の電界が誘導される。同様にバイアスをかけられた埋込板 420 により、ウエハ 416 の領域 424 には強度が等しく極性が逆の電界が誘導される。説明した実施例では、プラズマの不在下で、実効電荷が概ね等しい領域 422 と 424 が存在することにより、ウエハ 416 を静電チャック 414 にクランプする平衡状態の静電力が得られる。

#### 【 0035 】

図 5 も、クランプされた基板と静電チャック間に存在する漏れ電流を示す。図示のように、漏れ電流  $I_{1WAFER}$  は埋込板 418 からウエハ 416 の領域 422 に流れ、戻り電流  $I_{2WAFER}$  はウエハ 416 の領域 424 から埋込板 420 に流れます。

#### 【 0036 】

当業者には周知のように、電流  $I_1$ 、 $I_2$ 、 $I_{CHUCK}$ 、 $I_{1WAFER}$ 、 $I_{2WAFER}$  はキルヒホッフの法則により以下のように関連付けられる。

$$I_1 = I_{CHUCK} + I_{1WAFER}$$

$$I_2 = I_{CHUCK} + I_{2WAFER}$$

#### 【 0037 】

この実施例では、板 418 は静電チャック電源 500 の第 1 脚部 412 に接続されているので、第 1 電流  $I_1$  ( 上述のように  $I_{CHUCK}$  と  $I_{1WAFER}$  の合計に等しい ) が抵抗器 532 を流れます。同様に、板 420 は電源 500 の第 2 脚部 410 に接続されているので、第 2 電流  $I_2$  ( 上述のように  $I_{CHUCK}$  と  $I_{2WAFER}$  の合計に等しい ) が抵抗器 530 を流れます。

#### 【 0038 】

プラズマの不在下、ウエハ 416 には実効バイアスは誘導されない。したがって  $I_{1WAFER}$  は  $I_{2WAFER}$  に等しい ( ウエハ 416 へ流入する電流は、ウエハ 416 から出る電流と等しい )。上述のように  $I_1$  は  $I_2$  と等しいので、結果的に抵抗器 532 において  $I_1$  により発生される電圧  $V_1$  と、抵抗器 530 において  $I_2$  により発生される電圧  $V_2$  とは概ね等しくなる。電圧  $V_1$  と  $V_2$  によってそれぞれ絶縁増幅器 508 と 504 の入力が決まるので、絶縁増幅器 508、504 の出力 512、514 は概ね等しくなる。上述のように、差動増幅器 506 は電圧  $V_1$  と  $V_2$  の差 ( ゆえに  $I_1$  と  $I_2$  の差 ) に基づき作動し、可変電源 510 の入力制御信号を画定する出力 / 入力信号 516 を生成する。電圧  $V_1$  と  $V_2$  ( 同様に  $I_1$  と  $I_2$  ) が概ね等しい場合、出力 / 入力信号 516 は概ね 0V となる。出力 / 入力信号 516 が概ね 0V であると、可変電源 510 は基準ノード 407 をオフセットするためのバイアス電圧を生成しない。このようにプラズマが不在の状況では、制御回路 570 は初期休止状態となっている。

#### 【 0039 】

別の実施例では、プラズマが存在しないときであっても、漏れ電流  $I_1$  と  $I_2$  の初期の差をもたらす回路に固有の不均衡により、異なる初期均衡状態が生じる。この実施例では電源 510 により発生されたオフセット電圧は基準ノード 407 にバイアスをかけ、漏れ電流  $I_1$  と  $I_2$  に見られる初期の差を除去する。

10

20

30

40

50

## 【0040】

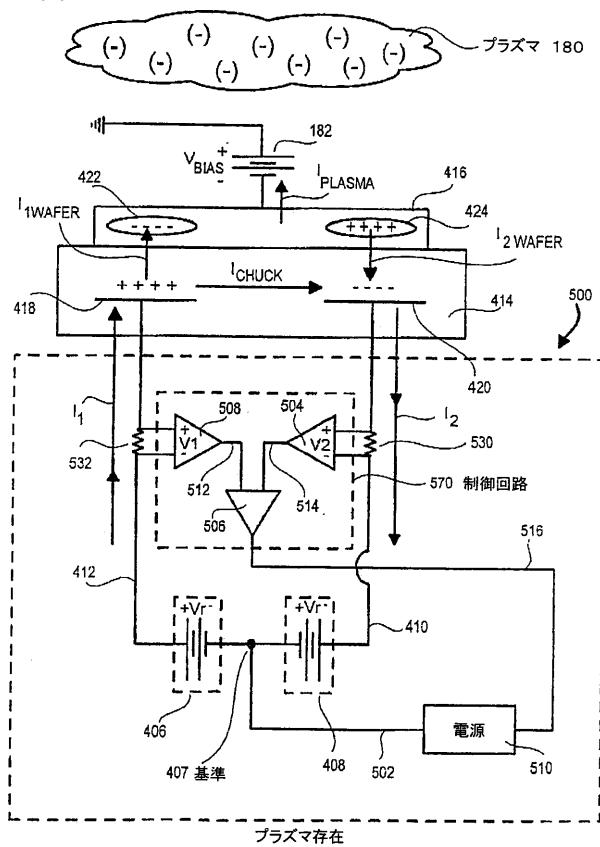

ウエハ416が静電チャック414にクランプされるとともに制御回路570が平衡である（すなわち $I_1$ が $I_2$ と概ね等しい）初期セットアップに続き、負帯電プラズマ180がプラズマチャンバ110に導入される。別の実施例では正帯電プラズマが導入される。図6は、負帯電プラズマ180の存在下、ウエハ416と静電チャック414に誘導される様々な漏れ電流を表している。上述の実施例ではプラズマ180は、陰極が接地され（すなわちチャンバの壁111に接続され）、陽極がウエハ416に接続された、固定バイアス電位源182（すなわちバッテリ）として表される。当業者にとって周知のように、プラズマ180により、基板416から接地までの電流 $I_{PLASMA}$ の電流経路が形成される。

## 【0041】

先に説明したように、プラズマ誘導バイアス $V_{BIAS}$ は、ウエハ416をチャック414に保持するための静電クランプ力に関して不均衡を生み出す。このクランプ力の不均衡は、埋込板418とウエハ416の領域422との電位差を増大させるとともに、埋込板420とウエハ416の領域424との電位差を減少させるプラズマ誘導バイアス $V_{BIAS}$ によるものである。

## 【0042】

漏れ電流 $I_{1WAFER}$ と $I_{2WAFER}$ も、埋込板とウエハ416の関連領域との電位差の変化に応じて変化する。上述の実施例では、負帯電プラズマ180は、埋込板418とウエハ416の領域422との電位差の増加により、ウエハ416への電流 $I_{1WAFER}$ を増加させる。同時に、ウエハ416から流出する電流 $I_{2WAFER}$ は、埋込板420とウエハ416の領域424との間の電位差の減少に伴い減少する。 $I_{1WAFER}$ と $I_{2WAFER}$ の正味の差が $I_{PLASMA}$ となる。この例では $I_{PLASMA}$ がプラズマ180に流入する。他の実施例では正帯電プラズマにより正反対の結果が得られる。（注：上記実施例において、約 $2V_R$ では、埋込板418と420の電位差は不变なので、漏れ電流 $I_{CHUCK}$ は基本的に不变となる。）

## 【0043】

一例を挙げると、図6のように、プラズマ180がチャンバ110に導入されると、ウエハ416に対してプラズマ誘導バイアス- $V_{BIAS}$ （正帯電プラズマの場合、プラズマ誘導バイアスは $+V_{BIAS}$ となる。）がかかる。プラズマ誘導バイアス- $V_{BIAS}$ は、埋込板418とウエハ416の領域422との電位差を $+V_R - (-V_{BIAS})$ または $V_R + V_{BIAS}$ まで上昇させる（埋込板418は基準ノード407に対して固定電位 $+V_R$ のままである）。ウエハ416の領域422と埋込板418との電位差が増加すると、ウエハ416に流入する漏れ電流 $I_{1WAFER}$ も同時に増加する。 $I_1 = I_{1WAFER} + I_{CHUCK}$ （キルヒホッフの法則）は変化しないので、プラズマ誘導バイアス $V_{BIAS}$ により $I_{1WAFER}$ が増加すると、比例した量だけ第1脚部の電流 $I_1$ が増加する。

## 【0044】

同様にして、埋込板420は基準ノードに対して固定電位 $-V_R$ に維持されるので、プラズマ誘導バイアス- $V_{BIAS}$ により、埋込板420とウエハ416の領域424との電位差が $-V_R - (-V_{BIAS})$ または $-V_R + V_{BIAS}$ まで減少する。このように電位差が減少すると、ウエハ416から流出する漏れ電流 $I_{2WAFER}$ が減少することになる。 $I_2 = I_{2WAFER} + I_{CHUCK}$ （キルヒホッフの法則）で $I_{CHUCK}$ は変化しないので、プラズマ誘導バイアス- $V_{BIAS}$ により $I_{2WAFER}$ が減少すると第2脚部の電流 $I_2$ が、その比例分だけ減少する。

## 【0045】

上述したように、 $I_{CHUCK}$ は基本的に不变状態が維持されており、 $I_1$ と $I_2$ の間の差 $I$ は、ウエハ416にプラズマ180の存在下で誘導される、オフセット電位の尺度となる。差 $I$ は制御回路570により構成されるフィードバックループの入力を画定する。制御回路570により画定されるフィードバックループは、 $I$ を概ねゼロまで減少させるよう設計されている（すなわち $I_1$ と $I_2$ は概ね等しい）。この実施例では、制御回路570は埋込板418と410に対して基準ノード407をオフセットすることにより $I$ を減少させる。このようにして埋込板418, 420とウエハ416の関連領域422, 424との間の電位差は、漏れ電流 $I_1$ と $I_2$ の間で観察される差に関連している。

10

20

30

40

50

## 【0046】

一例を挙げると、オームの法則から、 $I_1$ は抵抗器 532 における電圧降下  $V_1$  を引き起こし、 $I_2$  は抵抗器 530 における電圧降下  $V_2$  を引き起こす。 $V_1$  と  $V_2$  は、差動増幅器 506 への入力を画定する出力 512 と 514 をそれぞれ有する絶縁増幅器 508 と 504 への入力を画定する。上記の実施例によれば、差動増幅器 506 は  $V_1$  と  $V_2$  の差（上記のオームの法則によれば  $I_1$  と  $I_2$  に直接関係する）に比例する出力 / 制御信号 516 を発する。出力 / 制御信号 516 は基準ノード 407 により発生され基準ノードに印加される出力バイアス電圧を決定する。

## 【0047】

基準ノード 407 が何らかの変化を示すと、ノードに関連している埋込板 418 と 420 のバイアスが直接変化する。一例を挙げると、直接電源 406 が埋込板 418 に  $+V_R$  のバイアスを印加すると、基準ノード 407 は正バイアス  $+V_{ref}$  となり、次に板 418 の電位は  $+V_R - ( +V_{ref} )$  となる。同様にして直流電源 408 が埋込板 420 に  $-V_R$  のバイアスを印加すると、基準ノード 407 は  $+V_{ref}$  の正バイアスとなり、次に板 420 の電位は  $-V_R - V_{ref}$  となる。

10

## 【0048】

上記からも明らかなように、埋込板 418, 420 とウエハ 416 の関連領域 422, 424 との電位差は、静電チャック 414 内の影響漏れ電流  $I_{1WAFER}$  と  $I_{2WAFER}$  に影響を及ぼすことになる。 $I_{1WAFER}$  または  $I_{2WAFER}$  が何らかの変化を示すと、第1脚部の漏れ電流  $I_1$  と第2脚部の漏れ電流  $I_2$  に影響を及ぼし、フィードバックループを完成させる。

20

## 【0049】

上述した本発明の実施例は、信頼性がなく汚れる可能性のあるプローブピンを使用せずに、双極静電チャックへの不平衡電圧を補償するという目標を達成する。本発明の別の好適な局面によれば、基板からプラズマへに流入する電流を減少または除去して、アークの危険を減らし、放電時間を短くして処理能力を高め、基板を静電チャックに効果的にクランプするのに必要な電圧を下げる。

## 【0050】

本実施例のさらなる長所は、信頼性がなく汚染の可能性のあるプローブピンを使用することなく、双極静電チャックへの不平衡な電圧を補償できる能力を含むことにある。本実施例の別の長所によれば、基板からプラズマへ流れる電流を減らすまたは除去することが可能である。基板からプラズマへの電流を減らすことにより、または除去することにより、アークの危険を減らし、処理能力を高め（放電時間が短くなるため）、基板を基板に効果的にクランプするのに必要な電圧を下げることになる。

30

## 【0051】

また別の長所として、電源を他のシステムに合わせて容易に更新でき、工程の支障となり、設置のためにはチャンバの物理的構成に変更を加えねばならないような外部測定装置（プローブピンのような）が不要であることが挙げられる。いくつかの好適な実施例について本発明を説明したが、本発明の範囲に包含される代替物、置換物、均等物が存在する。例えば、実施例ではプラズマエッティング反応器について説明したが、本発明の自己バイアス双極 E S C チャック電源は、蒸着に用いられるものなど、他のプラズマ反応器でも使用できる。本発明の方法および装置を実行する他の方法も存在することに注意すべきである。したがって、以下に添付された特許請求の範囲は、本発明の真の趣旨と本発明の範囲とに含まれる代替物、置換物、均等物をすべて含むものとして解釈されるべきである。

40

## 【図面の簡単な説明】

## 【0052】

【図 1】説明を容易にするため一般的なプラズマ基板処理システムを示す。

【図 2 A】誘導電荷とその結果生じるクランプ力との分布を示す、双極静電チャックと基板との断面図である。

【図 2 B】誘導電荷とその結果生じる不均衡なクランプ力の分布に対する負帯電プラズマの影響を示す、図 2 A に示した双極静電チャックと基板の断面図である。

50

【図3】ウェハのプラズマ誘導バイアスを補償するためのピックアップピンの使用に基づく従来技術の回路を示す。

【図4】本発明の一実施例に従う双極静電チャックの板にプラズマ誘導バイアス補償電圧を供給するための自己バイアス静電チャック電源を示す。

【図5】本発明の一実施例に従うプラズマが不存在の場合における静電チャックにクランプされた基板における漏れ電流を示す。

【図6】本発明の一実施例に従うプラズマ導入後に自己バイアス電源に接続された静電チャックに載置された基板に存在する漏れ電流を示す。

【図 2B】

FIG. 2B

【図 3】

FIG. 3 (従来技術)

【図 4】

FIG. 4

【図 5】

プラズマ不存在

FIG. 5

【図6】

FIG.6

---

フロントページの続き

(72)発明者 ラムソン・アルバート・エム .

アメリカ合衆国 カリフォルニア州94539 フリモント, フォーチュナ・コモン, 623

(72)発明者 キャプレ・リック

アメリカ合衆国 カリフォルニア州94560 ニューアーク, ルビコン・アベニュー, 6248

(72)発明者 レンズ・エリック・エイチ .

アメリカ合衆国 カリフォルニア州95138 サン・ホセ, フォリグノ・ウェイ, 5960

(72)発明者 ブラウン・ローラ・エム .

アメリカ合衆国 カリフォルニア州94539 フリモント, モジャブ・コモン, 145

(72)発明者 マーシュ・リッキー

アメリカ合衆国 カリフォルニア州94583 サン・ラモン, ドス・リオス, 2778

審査官 植村 森平

(56)参考文献 特開平06-326176 (JP, A)

特表平02-503376 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/67 - 21/687

H02N 13/00

B23Q 3/15