JS006720649B2

# (12) United States Patent Huang

(10) Patent No.: US 6,720,649 B2 (45) Date of Patent: Apr. 13, 2004

| (54) | SEMICONDUCTOR PACKAGE WITH HEAT DISSIPATING STRUCTURE |                                                                                                              |  |

|------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| (75) | Inventor:                                             | Chien-Ping Huang, Hsinchu (TW)                                                                               |  |

| (73) | Assignee:                                             | Siliconware Precision Industries Co., Ltd. (TW)                                                              |  |

| (*)  | Notice:                                               | Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days. |  |

| (21) | Appl. No.: 10/211,430                                 |                                                                                                              |  |

| (22) | Filed:                                                | Aug. 2, 2002                                                                                                 |  |

| (65) | <b>Prior Publication Data</b>                         |                                                                                                              |  |

|      | US 2003/0107124 A1 Jun. 12, 2003                      |                                                                                                              |  |

Foreign Application Priority Data

(51) Int. Cl.<sup>7</sup> ...... H01L 23/10

**U.S. Cl.** ...... **257/706**; 707/718; 707/719;

(TW) ...... 90221335 U

707/778; 707/787; 707/796

257/718, 719, 691, 778, 787, 796

\* cited by examiner

Primary Examiner—Son L. Mai Assistant Examiner—Andy Huynh (74) Attorney, Agent, or Firm—Peter F. Corless; Steven M. Jensen; Edwards & Angell, LLP

### (57) ABSTRACT

A semiconductor package with a heat dissipating structure is provided. The heat dissipating structure includes a flat portion, and a plurality of support portions formed at edge corners of the flat portion for supporting the flat portion above a chip mounted on a substrate. The support portions are mounted at predetermined area on the substrate without interfering with arrangement of the chip and bonding wires that electrically connect the chip to the substrate. The support portions are arranged to form a space embraced by adjacent supports and the flat portion, so as to allow the bonding wires to pass through the space to reach area on the substrate outside coverage of the heat dissipating structure; besides, passive components or other electronic components can be mounted on the substrate at area within or outside the coverage of the heat dissipating structure, thereby improving flexibility in component arrangement in the semiconductor package.

# References Cited

(30)

(56)

#### U.S. PATENT DOCUMENTS

| 5,397,917 A | * 3/1995  | Ommen et al 257/698   |

|-------------|-----------|-----------------------|

| 5,468,910 A | * 11/1995 | Knapp et al 174/52.2  |

| 5,652,461 A | * 7/1997  | Ootsuki et al 257/675 |

## 15 Claims, 5 Drawing Sheets

FIG. 1 2B 2A

FIG. 2A

FIG. 2B

FIG. 3

FIG. 5 (PRIOR ART)

FIG. 6 (PRIOR ART)

1

# SEMICONDUCTOR PACKAGE WITH HEAT DISSIPATING STRUCTURE

#### FIELD OF THE INVENTION

The present invention relates to semiconductor packages, and more particularly, to a semiconductor package with a heat dissipating structure.

#### BACKGROUND OF THE INVENTION

Ball grid array (BGA) semiconductor packages are mainstream package products in the light of providing a sufficient amount of I/O (input/output) connections for use with semiconductor chips that incorporate high density of electronic elements and electronic circuits. As such a highly-integrated chip operates to consequently produce relatively more heat, it is thereby important to promptly remove the heat from the chip; otherwise, heat accumulation in the chip would undesirably damage electrical performances and reliability of package products. Moreover, for protecting internal components of the semiconductor package against external contamination, it usually forms an encapsulant that encapsulates the chip and other conductive elements such as bonding wires. The encapsulant is made of a resin material with poor thermal conductivity (coefficient of thermal conductivity around 0.8 w/m°K); therefore, the chip-generated heat would not be efficiently dissipated to the atmosphere through the encapsulant; this would thereby adversely affect performances and lifetime of the chip by virtue of heat 30

In response to the above heat-dissipation problem, there is adopted a heat dissipating structure in the BGA semiconductor package for facilitating dissipation of heat generated from the chip. However, this heat dissipating structure is embedded in the encapsulant, such that the chip-generated heat still needs to pass through the encapsulant for dissipation. Therefore, this structural arrangement cannot achieve satisfactory improvement in heat dissipating efficiency for the semiconductor package.

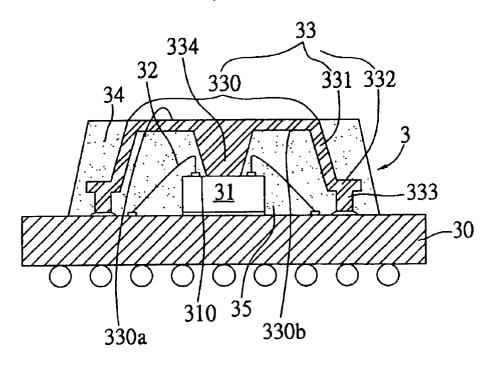

Accordingly, U.S. Pat. No. 5,977,626 discloses a semiconductor package with a heat dissipating structure being partly exposed to the atmosphere and also directly contacting with a chip. As shown in FIGS. 5 and 6, in this semiconductor package 3, a heat dissipating structure 33 is 45 provided on a substrate 30 above a chip 31 mounted on the substrate 30. The heat dissipating structure 33 comprises: a flat portion 330 having a top face 330a exposed to outside of an encapsulant 34 that encapsulates the chip 31 and bonding wires 32 that electrically connect the chip 31 to the 50 substrate 30; and a single encircled support portion 331 peripherally situated at the flat portion 330 and extending downwardly from a bottom surface 330b of the flat portion 330 to be attached to the substrate 30, wherein the flat portion 330 and the encircled support portion 331 integrate 55 to form a receiving space 35 where internal components such as the chip 31, bonding wires 32 and passive components (not shown) are placed. The encircled support portion 331 is integrally formed with a laterally-extending contact portion 332 at a bottom position thereof, and the contact portion 332 may be provided with a plurality of protruding portions 333 respectively extending downwardly to be attached to the substrate 30. Moreover, on the bottom surface 330b of the flat portion 330 there is formed a protrusion 334 extending to abut against an active surface 65 310 of the chip 31. This allows heat generated by the chip 31 during operation to be transmitted through the protrusion

2

**334** to the exposed top face **330***a* of the flat portion **330** by which the heat can be dissipated to the atmosphere, so as to provide excellent heat dissipating efficiency for the semiconductor package **3**.

However, the above semiconductor package 3 has significant drawbacks. In compliance with low profile packaging technology and high integration of chip development, substrates are preferred to be down-sized nearly to chip scale, and incorporated with sufficient conductive elements <sup>10</sup> such as bonding wires required for accommodating highlyintegrated chips with densely-arranged electronic elements or circuits. As a result, the above heat dissipating structure 33 is considered to occupy too much space on the substrate 30 in a manner that, the receiving space 35 embraced by the flat portion 330 and the single encircled support portion 331 with integrally-formed contact portion 332, makes all internal components of the semiconductor package 3 position restrictedly enclosed in the receiving space 35. Thereby, the bonding wires 32, passive components or other electronic components (not shown) can only be disposed on the substrate 30 at area within coverage of the heat dissipating structure 33 in the receiving space 35. This drawback makes the semiconductor package 3 with the heat dissipating structure 33 hardly applied for accommodating highlyintegrated chips that require a large amount of active and passive components as well as conductive elements to be comfortable situated on the substrate 30 for achieving desirable operational and electrical performances.

Further due to the heat dissipating structure 33 being located outside area for incorporating electronic components on the substrate 30, in another aspect, the substrate 30 may need to be increasingly sized in order to dispose a sufficient number of active and passive components as well as conductive elements on the substrate 30; this would make the substrate 30 considerably larger in size than the chip 31, thereby unfavorable to profile miniaturization.

#### SUMMARY OF THE INVENTION

An objective of the present invention is to provide a semiconductor package with a heat dissipating structure, wherein the heat dissipating structure is arranged in a manner not to interfere with layout of a chip, bonding wires or passive components mounted on the substrate, thereby improving flexibility in component arrangement in the semiconductor package.

Another objective of the invention is to provide a, semiconductor package with a heat dissipating structure, so as to reduce surface area of a substrate occupied by the heat dissipating structure, and thus to increase layout area on the substrate for accommodating bonding wires and passive components.

A further objective of the invention is to provide a semiconductor package with a heat dissipating structure, so as to improve heat dissipating efficiency of the semiconductor package.

To achieve the above and other objectives, the present invention proposes a semiconductor package with a heat dissipating structure, comprising: a substrate; at least a chip mounted on the substrate and electrically connected to the substrate via a plurality of bonding wires; a heat dissipating structure comprising a flat portion, and a plurality of support portions formed at edges of the flat portion for supporting the flat portion in position above the chip, wherein the support portions are mounted at predetermined area on the substrate to be free of interference with arrangement of the chip and the bonding wires, and the support portions are

arranged to form a space embraced by adjacent support portions and the flat portion, which space is dimensioned to accommodate the bonding wires and to allow the bonding wires to pass through the space to reach area on the substrate outside coverage of the heat dissipating structure; an encapsulant formed on the substrate for encapsulating the chip and the bonding wires; and a plurality of solder balls implanted on the substrate and exposed to outside of the encapsulant.

In the above package structure, the flat portion of the heat dissipating structure is elevated above the chip by the 10 support portions and forms a predetermined height difference with respect to the substrate, wherein the height difference is at least corresponding to height of wire loops of the bonding wires. Therefore, part of bond fingers where the bonding wires are bonded can be formed on the substrate at 15 area outside the coverage of the heat dissipating structure, allowing the corresponding bonding wires to pass through the space embraced by adjacent support portions and the flat portion and to reach the outside-coverage bond fingers. Besides, passive components or other electronic components 20 may also be desirably mounted on the substrate at area within or outside the coverage of the heat dissipating structure, thereby improving flexibility in component arrangement in the semiconductor package. Moreover, by the above structural arrangement, more flexibly-sized heat 25 dissipating structures or chips can be adopted in the semiconductor package as long as the support portions of the heat dissipating structure are mounted on the substrate at area without affecting the arrangement of the chip and the bonding wires. Furthermore, the heat dissipating structure with multiple individual support portions, instead of a conventional single encircled support portion (as shown in FIG. 6), can desirably reduce surface area of the substrate occupied by the heat dissipating structure, thereby increasing layout area on the substrate for accommodating the bonding wires, 35 passive components or other electronic components.

In another embodiment, the flat portion of the heat dissipating structure, having a top surface exposed to outside of the encapsulant and a bottom surface connected to the support portions, is formed with at least a peripherallysituated recess on the top surface and at least a protrusion on the bottom surface. During a molding process for forming the encapsulant by an encapsulating resin, when flowing to the peripherally-situated recess, the encapsulating resin would quickly absorb heat from an encapsulating mold and 45 slow down its flowing speed without flashing over the exposed top surface of the flat portion, thereby helping assure reliability of fabricated package products. Moreover, the protrusion formed on the flat portion extends toward the chip mounted on the substrate and shortens the distance 50 plurality of electric elements and electric circuits thereon, between the flat portion and the chip, by which heat generated from the chip can be efficiently transmitted to the heat dissipating structure for dissipation, such that heat dissipating efficiency of the semiconductor package is desirably improved.

## BRIEF DESCRIPTION OF THE DRAWINGS

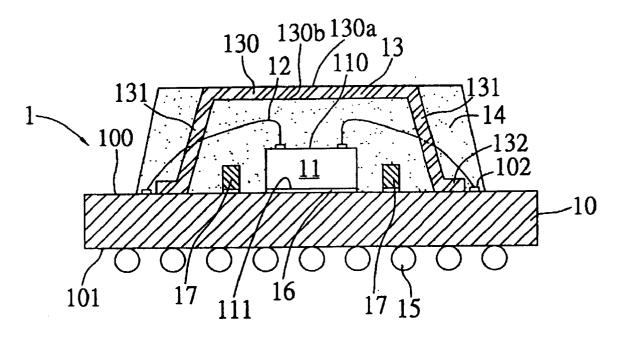

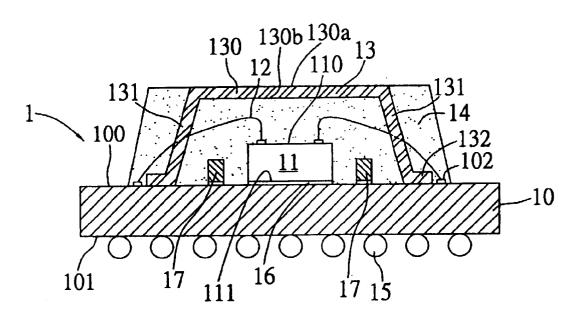

- FIG. 1 is a top perspective view of a semiconductor package according to a preferred embodiment of the present invention;

- FIG. 2A is a cross-sectional view of the semiconductor package shown in FIG. 1 taken along line 2A-2A;

- FIG. 2B is a cross-sectional view of the semiconductor package shown in FIG. 1 taken along line 2B—2B;

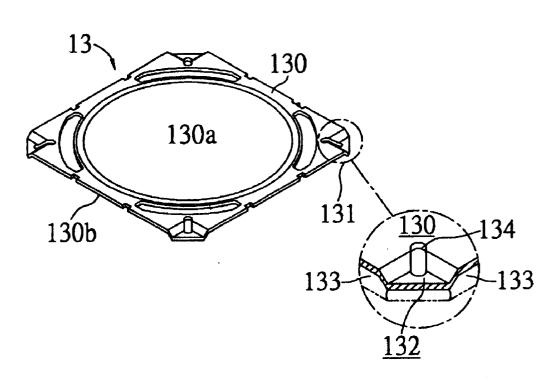

- dissipating structure used in the semiconductor package according to the invention;

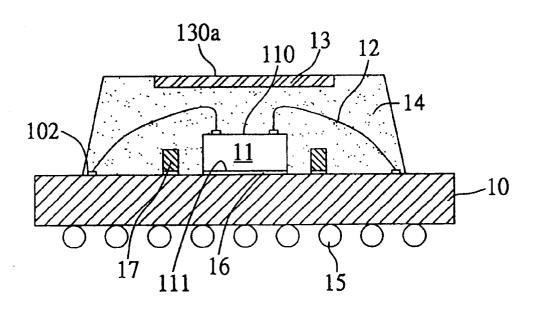

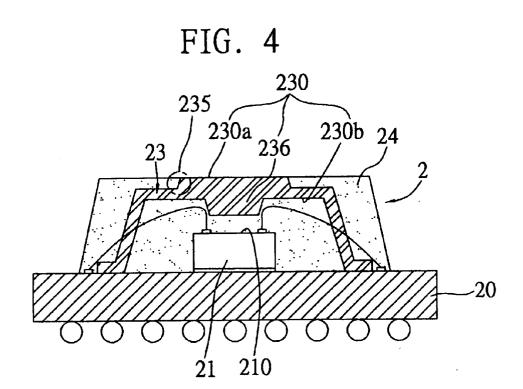

- FIG. 4 is a cross-sectional view of the semiconductor package according to another preferred embodiment of the invention;

- FIG. 5 (PRIOR ART) is a cross-sectional view of a semiconductor package according to U.S. Pat. No. 5,977, 626; and

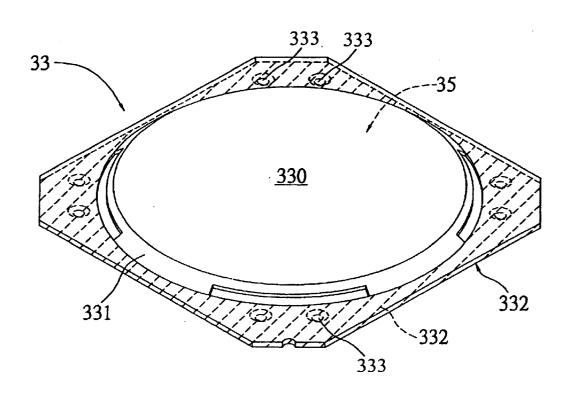

- FIG. 6 (PRIOR ART) is a top view of a heat dissipating structure used in the semiconductor package shown in FIG.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

FIGS. 1, 2A and 2B illustrate a semiconductor package 1 proposed in the present invention, wherein FIGS. 2A and 2B are cross-sectional views of the semiconductor package 1 shown in FIG. 1. As shown in the drawings, the semiconductor package 1 comprises: a substrate 10; a chip 11 mounted on the substrate 10; a plurality of bonding wires 12 for electrically connecting the chip 11 to the substrate 10; a heat sink 13 mounted on the substrate 10; a plurality of passive components 17 disposed on the substrate 10; an encapsulant 14 for encapsulating the chip 11, bonding wires 12, heat sink 13 and passive components 17; and a plurality of solder balls 15 implanted on the substrate 10 and exposed to outside of the encapsulant 14.

The substrate 10 has a top surface 100 and a bottom surface 101 opposed to the top surface 100, each surface being formed with predetermined conductive traces (not shown) thereon. A plurality of conventional vias (not shown) are formed through the substrate 10 for electrically interconnecting the conductive traces on the top and bottom surfaces 100, 101. The substrate 10 may be made of epoxy resin, polyimide resin, BT (bismaleimide triazine) resin, ceramic material, glass material, etc., and preferably BT

A plurality of bond fingers 102 are formed and associated with corresponding conductive traces on the top surface 100 of the substrate 10, so as to allow the bonding wires 12 to be bonded to the bond fingers 102 respectively. The passive components 17, such as inductor, capacitor, resister, etc., are mounted on the top surface 100 of the substrate 10 for modulating electrical performances in operation of the semiconductor package 1. The solder balls 15 are implanted on the bottom surface 101 of the substrate 10 at positions associated with corresponding conductive traces, and used to electrically connect the chip 11 to an external device such as a printed circuit board (PCB, not shown).

The chip 11 has an active surface 110 formed with a and a non-active surface 111 opposed to the active surface 110, wherein the non-active surface 111 is mounted on the top surface 100 of the substrate 10 by an adhesive 16 such as silver paste or a polyimide tape.

In accompany with reference to FIG. 3, the heat sink 13, a characteristic feature of the invention, is an embedded type of heat sink mounted on the top surface 100 of the substrate 10 at conductive-element-free area without interfering with arrangement of the bond fingers 102, bonding wires 12 and passive components 17. The heat sink 13 comprises a flat portion 130, and a plurality of support portions 131 for elevating the flat portion 130 in position above the chip 11. The flat portion 130 has a top surface 130a and a bottom surface 130b opposed to the top surface 130a, wherein the FIG. 3 is a top view and a local enlarged view of a heat 65 top surface 130a is exposed to outside of the encapsulant 14, and the bottom surface 130b is formed with the support portions 131. The support portions 131 are situated at edge

5

corners of the flat portion 130, and extend downwardly to be attached to the top surface 100 of the substrate 10. The flat portion 130 elevated by the support portions 131 is adapted to form a predetermined height difference with respect to the substrate 100 in a manner as to form a space 133 embraced by adjacent support portions 131 and the flat portion 130, wherein the space 133 is dimensioned to accommodate wire loops of the bonding wires 12 and the passive components 17 and to allow the bonding wires 12 to pass through the space 133 to reach area on the substrate 10 outside coverage of the heat sink 13. For example, bond fingers 102 formed on the substrate 10 can be situated at area outside the coverage of the heat sink 13, allowing the corresponding bonding wires 12 to be bonded to the outside-coverage bond fingers 102 in a manner shown in FIG. 2A; moreover, the passive components 17 or other electronic components can also be desirably disposed on the area of the substrate 10 outside the coverage of the heat sink 13; this thereby improves flexibility in component arrangement in the semiconductor package 1.

Each of the support portions 131 may be formed with a contact portion 132 at a position in contact with the substrate 10, wherein the contact portion 132 substantially extends laterally with respect to the substrate 10. The contact portion 132 may be flexibly shaped as, but not limited to, a rectangle, triangle, semicircle, etc. Each of the support portions 131 may be further formed with at least a hole 134 (as shown in FIG. 3) for allowing an encapsulating resin used for forming the encapsulant 14 to pass through the hole 134 during a molding process, so as to enhance bonding strength between the heat sink 13 and the fabricated encapsulant 14.

Moreover, by the above structural arrangement, more flexibly-sized heat sinks 13 or chips 11 can be adopted in the semiconductor package 1 as long as the support portions 131 of the heat sink 13 are mounted on the substrate 10 at area without affecting the arrangement of the chip 11 and the bonding wires 12. Furthermore, the heat sink 13 with multiple individual support portions 131, instead of a conventional single encircled support portion (as shown in FIG. 6), can desirably reduce surface area of the substrate 10 occupied by the heat sink 13, thereby increasing layout area on the substrate 10 for accommodating the bonding wires 12, passive components 17 or other electronic components.

FIG. 4 illustrates a semiconductor package 2 according to 45 another preferred embodiment of the invention. This semiconductor package 2 is substantially similar to the semiconductor package 1 described in the foregoing embodiment. A difference in the semiconductor package 2 is that, at least a peripherally-situated recess 235 is formed on a top surface 50 230a of a flat portion 230 of a heat sink 23. During a molding process for forming an encapsulant 24 by an encapsulating resin, when flowing to the peripherally situated recess 235, the encapsulating resin would quickly absorb heat from an encapsulating mold (not shown) and 55 reduce its flowing speed without flashing over the exposed top surface 230a. Moreover, at least a protrusion 236 may be formed on a bottom face 230b of the flat portion 230 and extends toward a chip 21 mounted on a substrate 20 and shortens the distance between the flat portion 230 and an 60 active surface 210 of the chip 21, by which heat generated from the chip 21 can be efficiently transmitted to the heat sink 23 for dissipation, such that heat dissipating efficiency of the semiconductor package 2 is desirably improved.

The present invention has been described using exem- 65 the flat portion. plary preferred embodiments. However, it is to be understood that the scope of the invention is not limited to the of the support

6

disclosed embodiments. On the contrary, it is intended to cover various modifications and similar arrangements. The scope of the claims, therefore, should be accorded the broadest interpretation so as to encompass all such modifications and similar arrangements.

What is claimed is:

- 1. A semiconductor package with a heat dissipating structure, comprising:

- a substrate;

- at least a chip mounted on the substrate and electrically connected to the substrate via a plurality of conductive elements;

- one or more passive components mounted on the substrate:

- the heat dissipating structure comprising a flat portion, and a plurality of support portions formed at edges of the flat portion for supporting the flat portion in position above the chip, wherein the support portions are mounted at a predetermined area on the substrate and free of interference with an arrangement of the chip, the passive components and the conductive elements, and the support portions are arranged to form a space between two adjacent support portions, the space being sufficiently dimensioned to accommodate the conductive elements and the passive components so as to allow the conductive elements to pass through the space to reach an area on the substrate outside coverage of the heat dissipating structure and such that the passive components are located within and/or outside the coverage of the heat dissipating structure; and

- an encapsulant formed on the substrate for encapsulating the chip and the conductive elements.

- 2. The semiconductor package of claim 1, further comprising:

- a plurality of solder balls implanted on the substrate and exposed to outside of the encapsulant.

- 3. The semiconductor package of claim 1, wherein the conductive elements are bonding wires, and a plurality of bond fingers are formed on the substrate for allowing the bonding wires to be bonded to the bond fingers.

- 4. The semiconductor package of claim 3, wherein the flat portion is elevated above the chip by the support portions and forms a predetermined height difference with respect to the substrate, allowing the height difference to be at least corresponding to height of wire loops of the bonding wires.

- 5. The semiconductor package of claim 4, wherein part of the bond fingers are situated on the substrate at area outside the coverage of the heat dissipating structure, allowing the corresponding bonding wires to pass through the space embraced by adjacent support portions and the flat portion and to reach the outside-coverage bond fingers.

- 6. The semiconductor package of claim 1, wherein the support portions are situated at edge corners of the flat portion.

- 7. The semiconductor package of claim 1, wherein the flat portion has a top surface exposed to outside of the encapsulant, and a bottom surface opposed to the top surface, the bottom surface being formed with the support portions.

- 8. The semiconductor package of claim 7, wherein at least a protrusion is formed on the bottom surface of the flat portion and extends toward the chip.

- 9. The semiconductor package of claim 7, wherein at least a peripherally-situated recess is formed on the top surface of the flat portion.

- 10. The semiconductor package of claim 1, wherein each of the support portions is formed with at least a hole for

7

allowing an encapsulating resin used for forming the encapsulant to pass through the hole.

- 11. The semiconductor package of claim 1, wherein each of the support portions is formed with a contact portion at a position in contact with the substrate.

- 12. The semiconductor package of claim 11, wherein the contact portion substantially extends laterally with respect to the substrate.

8

- 13. The semiconductor package of claim 11, wherein the contact portion is of a triangular shape.

- 14. The semiconductor package of claim 11, wherein the contact portion is of a rectangular shape.

- 15. The semiconductor package of claim 11, wherein the contact portion is of a semicircular shape.

\* \* \* \* \*