(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5130896号

(P5130896)

(45) 発行日 平成25年1月30日(2013.1.30)

(24) 登録日 平成24年11月16日(2012.11.16)

(51) Int.Cl.

F 1

H03K 17/16 (2006.01)

H03K 17/687 (2006.01)H03K 17/16

H03K 17/687L

A

請求項の数 2 (全 9 頁)

(21) 出願番号 特願2007-324500 (P2007-324500)

(22) 出願日 平成19年12月17日 (2007.12.17)

(65) 公開番号 特開2009-147784 (P2009-147784A)

(43) 公開日 平成21年7月2日 (2009.7.2)

審査請求日 平成22年12月15日 (2010.12.15)

(73) 特許権者 000003218

株式会社豊田自動織機

愛知県刈谷市豊田町2丁目1番地

(74) 代理人 100074099

弁理士 大菅 義之

(72) 発明者 松本 尚能

愛知県刈谷市豊田町2丁目1番地 株式会

社豊田自動織機内

審査官 栗栖 正和

最終頁に続く

(54) 【発明の名称】半導体素子の駆動回路

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体素子をスイッチング動作させる駆動信号を生成する駆動回路であって、駆動信号のオン期間及びオフ期間を決める信号を生成するICの出力がゲートに印加される第1のトランジスタと、

前記第1のトランジスタと継続接続され、前記ICの出力がツェナーダイオードを介してゲートに印加される第2のトランジスタとからなり、

前記第1及び第2のトランジスタはMOSトランジスタからなり、

前記第1のMOSトランジスタのドレインまたはソースにゲートが接続された第3のMOSトランジスタと、

前記第2のMOSトランジスタのドレインまたはソースに一端が接続され、他端が電源電圧に接続された第2の抵抗と、

前記第2の抵抗の一端に、ゲートが接続された第4のMOSトランジスタとを有し、

前記第1と第2のMOSトランジスタは第1の抵抗を介して継続接続され、

前記第3のMOSトランジスタのソースは第3の抵抗の一端に接続され、ドレインは前記第4のMOSトランジスタのドレインに接続され、

前記第3の抵抗の他端は前記電源電圧に接続され、

前記第4のMOSトランジスタのソースは第4の抵抗を介して接地され、

前記第1の抵抗の値は、前記第3の抵抗及び前記第4の抵抗の値に比べて大きな値である半導体素子の駆動回路。

10

20

## 【請求項 2】

前記第1のMOSトランジスタのゲートには、第1のダイオードと第1のツェナーダイオードが直列に接続され、

前記第2のMOSトランジスタのゲートには、第2のダイオードと第2のツェナーダイオードが直列に接続されている請求項1記載の半導体素子の駆動回路。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、半導体素子の駆動回路に関する。

## 【背景技術】

## 【0002】

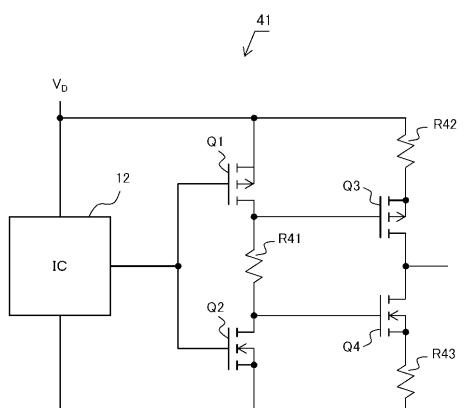

半導体素子をスイッチング動作させる駆動回路として、例えば、図5に示す駆動回路41が用いられる。

図5において、IC12は、駆動信号のオン期間、オフ期間を可変する信号を生成し、生成した信号をpチャネルMOSトランジスタQ1とnチャネルMOSトランジスタQ2のゲートに出力する。pチャネルMOSトランジスタQ1のドレインは、pチャネルMOSトランジスタQ3のゲートと抵抗R41の一端に接続されている。pチャネルMOSトランジスタQ1のソースには電源電圧V<sub>D</sub>が供給される。

## 【0003】

nチャネルMOSトランジスタQ2のドレインは、nチャネルMOSトランジスタQ4のゲートと抵抗R41の他端に接続され、ソースは接地されている。

pチャネルMOSトランジスタQ3とnチャネルMOSトランジスタQ4は継続接続され、pチャネルMOSトランジスタQ3のソースは抵抗R42を介して電源電圧V<sub>D</sub>に接続されている。そして、MOSトランジスタQ3とQ4の接続点の電圧が、図示しない制御対象のMOSトランジスタのゲートに出力されている。MOSトランジスタQ4のソースは抵抗R43を介して接地されている。

## 【0004】

図6は、IC12とMOSトランジスタQ1～Q4の動作波形を示す図である。

IC12の出力がローレベルからハイレベルに変化すると、MOSトランジスタQ1がオフ、MOSトランジスタQ2がオンに変化する。IC12の出力がローレベルのとき、MOSトランジスタQ3のゲートには電源電圧V<sub>D</sub>が印加されているので、MOSトランジスタQ1がオフ状態に変化しても、MOSトランジスタQ3のゲート電圧が正の一定値に上昇するまでの間、MOSトランジスタQ3はオフ状態を維持する。

## 【0005】

他方、MOSトランジスタQ4のゲートにはこれまで電源電圧V<sub>D</sub>が印加されていたので、MOSトランジスタQ2がオンとなっても、MOSトランジスタQ4のゲート電圧はすぐには所定電圧以下とならず、一定時間経過した後オフ状態となる。

## 【0006】

そのため、図6に示すようにMOSトランジスタQ3とQ4の両方がオンとなる期間が生じる。駆動回路41の出力電流を大きくするため、抵抗R42、R43は小さな値に設計されるので、MOSトランジスタQ3、Q4が同時にオンすると大きな貫通電流が流れしまう。

## 【0007】

また、電源起動時に電源電圧V<sub>D</sub>が一定値に達するまでの期間は、IC12の出力はローレベルであることが望ましいが、実際には、IC12が正常に動作する電圧に達するまでの間、IC12の出力は不定であり、IC12の電源端子に印加される電圧がハイレベルの信号としてそのまま出力されてしまうことがある。その結果、電源の起動時に、駆動回路41から半導体素子をオンにする信号が出力される可能性があった。

## 【0008】

特許文献1には、第2のスイッチング素子のオン動作に従属して電源電圧が得られる従

10

20

30

40

50

属的電源回路に接続したインバータにおいて、従属的電源回路の電圧が所定値以上に上昇するまで、第1のスイッチング素子のオン動作を禁止する回路を設けることが記載されている。

【特許文献1】特開平1-114374号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

本発明の課題は、駆動回路の電源電圧が所定値以上に上昇するまで駆動回路がオン動作しないこと、半導体素子をスイッチング動作させる駆動回路の出力段のトランジスタに貫通電流が流れないようにすることである。

10

【課題を解決するための手段】

【0010】

本発明は、半導体素子をスイッチング動作させる駆動信号を生成する駆動回路であって、駆動信号のオン期間及びオフ期間を決める信号を生成するICの出力がゲートに印加される第1のトランジスタと、前記第1のトランジスタと縦続接続され、前記ICの出力がツエナーダイオードを介してゲートに印加される第2のトランジスタとからなり、前記第1及び第2のトランジスタはMOSトランジスタからなり、前記第1のMOSトランジスタのドレインまたはソースにゲートが接続された第3のMOSトランジスタと、前記第2のMOSトランジスタのドレインまたはソースに一端が接続され、他端が電源電圧に接続された第2の抵抗と、前記第2の抵抗の一端に、ゲートが接続された第4のMOSトランジスタとを有する。

20

【0011】

この駆動回路によれば、駆動回路の電源電圧が所定値以上に上昇するまで駆動回路がオン動作しないようにできる。

また、このように構成することで、駆動回路の電源電圧が所定値以上に上昇するまで駆動回路がオン動作しないようにできる。

上記の駆動回路において、前記第1と第2のMOSトランジスタは第1の抵抗を介して縦続接続され、前記第3のMOSトランジスタのソースは第3の抵抗の一端に接続され、ドレインは前記第4のMOSトランジスタのドレインに接続され、前記第3の抵抗の他端は前記電源電圧に接続され、前記第4のMOSトランジスタのソースは第4の抵抗を介して接地され、前記第1の抵抗の値は、前記第3の抵抗及び前記第4の抵抗の値に比べて大きな値である。

30

【0012】

このように構成することで、第1の抵抗の値は、第3の抵抗、第4の抵抗の値に比べて大きな値にすることができる、第1のMOSトランジスタ、第2のMOSトランジスタに流れる貫通電流は動作上問題が無い値にできる。

上記の駆動回路において、前記第1のMOSトランジスタのゲートには、第1のダイオードと第1のツエナーダイオードが直列に接続され、前記第2のMOSトランジスタのゲートには、第2のダイオードと第2のツエナーダイオードが直列に接続されている。

40

【0013】

このように構成することで、駆動回路の電源電圧が所定値以上に上昇するまで駆動回路がオン動作しないようにできると共に、駆動回路の出力段のトランジスタが同時にオンするのを防止できる。

【発明の効果】

【0014】

本発明によれば、駆動回路の電源電圧が所定値以上に上昇するまで駆動回路がオン動作せず、かつ駆動回路の出力段のトランジスタが同時にオンするのを防止できる。

【発明を実施するための最良の形態】

【0015】

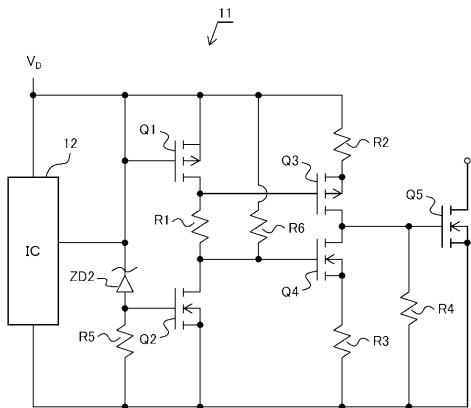

以下、本発明の好適な実施の形態について説明する。図1は、第1の実施の形態の駆動

50

回路 1 1 の回路図である。この第 1 の実施の形態は、駆動回路 1 1 の電源電圧が所定値以上に上昇するまで駆動回路 1 1 をオン動作させないためのものである。

【 0 0 1 6 】

駆動回路 1 1 は、半導体素子、例えばMOSトランジスタQ5をスイッチング動作させるための駆動信号を生成する回路である。IC12は、信号生成用の専用の半導体集積回路であり、駆動信号のオン期間及びオフ期間を決める信号を出力する。IC12の出力は、pチャネルMOSトランジスタQ1のゲートとツェナーダイオードZD2のカソードに印加されている。ツェナーダイオードZD2のアノードは、nチャネルMOSトランジスタQ2のゲートと、抵抗R5の一端に接続されており、抵抗R5の他端は接地（または共通電位、以下、接地として説明する）されている。

10

【 0 0 1 7 】

MOSトランジスタQ1のソースは電源電圧V<sub>D</sub>に接続され、ドレインはpチャネルMOSトランジスタQ3のゲートと、抵抗R1の一端に接続されている。MOSトランジスタQ2のドレインは、抵抗R1の他端と、nチャネルMOSトランジスタQ4のゲートに接続されている。MOSトランジスタQ4のゲートには抵抗R6が接続され、その抵抗R6の他端は電源電圧V<sub>D</sub>に接続されている。

【 0 0 1 8 】

MOSトランジスタQ3のソースは抵抗R2の一端に接続され、ドレインはnチャネルMOSトランジスタQ4のドレインに接続されている。抵抗R2の他端は電源電圧V<sub>D</sub>に接続されている。nチャネルMOSトランジスタQ4のソースは抵抗R3を介して接地されている。

20

【 0 0 1 9 】

MOSトランジスタQ3とMOSトランジスタQ4の接続点は、制御対象のnチャネルMOSトランジスタQ5のゲートと接続されており、MOSトランジスタQ3、Q4の出力電圧が駆動信号としてMOSトランジスタQ5のゲートに出力されている。MOSトランジスタQ5のゲートには抵抗R4が接続され、抵抗R4の他端は接地されている。

【 0 0 2 0 】

図1の駆動回路11は、IC12の出力がローレベルのとき、pチャネルMOSトランジスタQ1がオン、nチャネルMOSトランジスタQ2がオフ状態になる。

MOSトランジスタQ1がオン状態のとき、pチャネルMOSトランジスタQ3のゲートには電源電圧V<sub>D</sub>が印加されるので、MOSトランジスタQ3はオフ状態となる。MOSトランジスタQ2がオフ状態のとき、nチャネルMOSトランジスタQ4のゲートには、抵抗R6を介して電源電圧V<sub>D</sub>のが印加されるので、MOSトランジスタQ4はオン状態となる。

30

【 0 0 2 1 】

IC12の出力がローレベルからハイレベルに変化する過程で、出力電圧、つまりMOSトランジスタQ1のゲート電圧が一定電圧（MOSトランジスタQ1がオフとなる電圧）以上になると、MOSトランジスタQ1はオフ状態に変化する。このとき、IC12の出力電圧が、ツェナーダイオードZD2のツェナー電圧未満であれば、MOSトランジスタQ2はオフ状態を維持する。

40

【 0 0 2 2 】

すなわち、IC12の出力電圧がツェナーダイオードZD2のツェナー電圧未満のとき、MOSトランジスタQ2はオフ状態になる。

MOSトランジスタQ2がオフのとき、pチャネルMOSトランジスタQ3のゲートには、抵抗R6、R1を介して電源電圧V<sub>D</sub>が印加されるので、pチャネルMOSトランジスタQ3はオフ状態を維持する。

【 0 0 2 3 】

他方、MOSトランジスタQ4のゲートには抵抗R6を介して電源電圧V<sub>D</sub>が印加されるので、MOSトランジスタQ4はオン状態を維持する。これによりMOSトランジスタQ5をオフ状態にすることができます。

50

## 【0024】

すなわち、駆動回路11の電源電圧 $V_D$ が低く、IC12の出力電圧がツエナーダイオードZD2のツエナー電圧未満のときには、MOSトランジスタQ2をオフ状態、MOSトランジスタQ4をオン状態にできるので、駆動回路11から半導体素子をオン状態にする信号が出力されるのを防止することができる。

## 【0025】

上述した第1の実施の形態によれば、IC12の出力とMOSトランジスタQ2のゲートとの間にツエナーダイオードZD2を挿入し、MOSトランジスタQ4のゲートに抵抗R6を介して電源電圧 $V_D$ を印加することで、駆動回路11の電源電圧 $V_D$ が所定値以上となるまで、駆動回路11からMOSトランジスタQ5をオン状態にする信号が出力されないようにできる。

10

## 【0026】

なお、図1の回路において、MOSトランジスタQ2がオン状態（またはオフ状態）になる電圧を制限するための回路はツエナーダイオードを用いたものに限らず、他の構成の電圧制限回路を用いても良い。

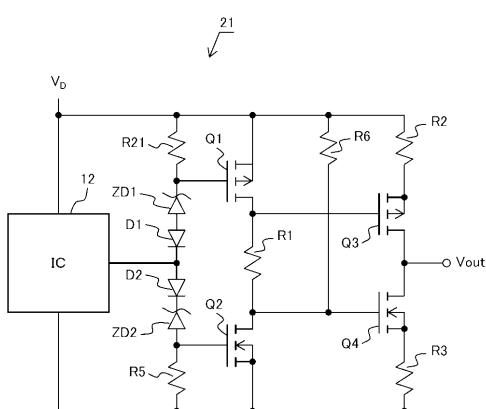

## 【0027】

次に、図2は、第2の実施の形態の駆動回路21の回路図である。この第2の実施の形態は、電源の起動時の駆動回路21の誤動作を防止するものであると共に、スイッチング時に駆動回路21の出力段のトランジスタが同時にオンするのを防止するものである。以下、図1と同じ要素には同じ符号を付けてそれらの説明は省略する。

20

## 【0028】

図2において、pチャネルMOSトランジスタQ1のゲートは抵抗R21を介して電源電圧 $V_D$ に接続され、さらにツエナーダイオードZD1とダイオードD1を介してIC12の出力に接続されている。ダイオードD1のカソードがIC12の出力に接続され、ツエナーダイオードZD1のカソードがゲートに接続されている。

## 【0029】

nチャネルMOSトランジスタQ2のゲートは、ツエナーダイオードZD2とダイオードD2を介してIC12の出力に接続され、さらに抵抗R5を介して接地されている。ダイオードD2のアノードがIC12の出力に接続され、ツエナーダイオードZD2のアノードがゲートに接続されている。

30

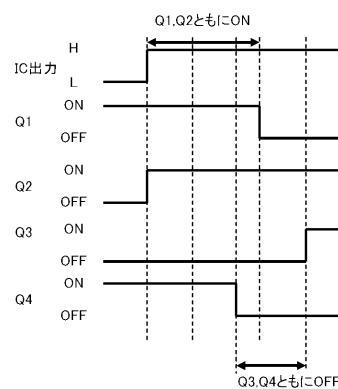

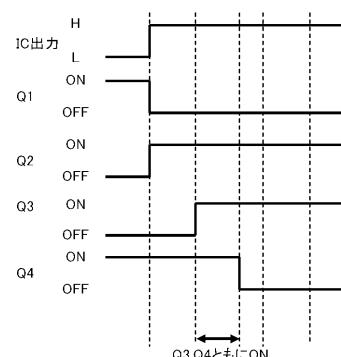

## 【0030】

上記の駆動回路21の動作を、図3の波形図を参照して説明する。IC12の出力がローレベルのときは、pチャネルMOSトランジスタQ1のゲートには、ツエナーダイオードZD1のツエナー電圧とダイオードD1の順方向電圧を加算した電圧が印加され、MOSトランジスタQ1はオン状態になっている。

## 【0031】

他方、MOSトランジスタQ2のゲートに印加される電圧は、IC12の出力がローレベルであることからほぼ0Vとなり、MOSトランジスタQ2はオフ状態になっている。

IC12の出力電圧がローレベルからハイレベルに変化し、その出力電圧がツエナーダイオードZD2のツエナー電圧以上となると、MOSトランジスタQ2はオン状態になる。

40

## 【0032】

一方、IC12の出力がハイレベルになっても、ダイオードD1によりIC12からMOSトランジスタQ1のゲートには電流は流入せず、電源電圧 $V_D$ から抵抗R21の経路で電流が流れるので、ゲート電圧が一定値（オフ電圧）に達するまでの一定時間MOSトランジスタQ1はオン状態を維持する。

## 【0033】

すなわち、図3に示すように、MOSトランジスタQ2は、IC12の出力がハイレベルに変化したとき直ぐにオン状態に変化するが、MOSトランジスタQ1はゲート電圧が一定値に達するまでの一定時間オン状態を維持する。従って、その間、MOSトランジス

50

タ  $Q_1$  と  $Q_2$  は同時にオン状態となる（図 3 の  $Q_1$ 、 $Q_2$  がともにオンの期間）。MOS トランジスタ  $Q_1$  と  $Q_2$  が同時にオン状態となることで、MOS トランジスタ  $Q_1$  と  $Q_2$  に貫通電流が流れるが、抵抗  $R_1$  の値は、出力段の抵抗  $R_2$ 、 $R_3$  の値に比べて大きな値に設計することができるので、トランジスタ  $Q_1$ 、 $Q_2$  に流れる貫通電流は動作上問題が無い値にできる。

#### 【0034】

MOS トランジスタ  $Q_1$  がオン状態のとき、MOS トランジスタ  $Q_3$  のゲートには電源電圧  $V_D$  が印加されるので、MOS トランジスタ  $Q_3$  はその間オフ状態を維持する。

MOS トランジスタ  $Q_2$  がオン状態に変化しても、MOS トランジスタ  $Q_4$  のゲート電圧が一定値以下になるまでMOS トランジスタ  $Q_4$  はオン状態を維持する（図 3 の  $Q_4$  がオン状態の期間）。

#### 【0035】

すなわち、図 3 の駆動回路 2-1 は、IC12 の出力がローレベルからハイレベルに変化してから一定期間、MOS トランジスタ  $Q_1$  と  $Q_2$  を同時にオン状態とすることで、その間MOS トランジスタ  $Q_3$  をオフ状態にすることができる。これにより、MOS トランジスタ  $Q_3$  と  $Q_4$  が同時にオンして貫通電流が流れるのを防止できる。

#### 【0036】

一定時間が経過してMOS トランジスタ  $Q_4$  のゲートの電荷が放出されてゲート電圧が一定値未満となると、MOS トランジスタ  $Q_4$  がオフ状態に変化する（図 3 の  $Q_4$  がオフに変化するタイミング）。その後、MOS トランジスタ  $Q_1$  のゲート電圧が一定値以上となり、MOS トランジスタ  $Q_1$  がオフ状態に変化すると（図 3 の  $Q_1$  がオフに変化するタイミング）、MOS トランジスタ  $Q_3$  のゲート電圧が次第に減少し、一定時間後にMOS トランジスタ  $Q_3$  がオン状態に変化する（図 3 の  $Q_3$  がオンに変化するタイミング）。このとき、MOS トランジスタ  $Q_3$  と  $Q_4$  の接続点の出力電圧  $V_{out}$  は正の電圧となり、半導体素子をオンさせる駆動信号が出力される。

#### 【0037】

次に、電源起動時の動作を説明する。電源の立ち上がり時にIC12 が誤動作してハイレベルの信号（例えば、その時の電源電圧  $V_D$  とほぼ等しい電圧値の信号）が出力されても、IC12 の出力電圧が、ツエナーダイオード ZD2 のツエナー電圧（ダイオード D2 の順方向電圧を含む）未満のときには、MOS トランジスタ  $Q_2$  はオフ状態を維持する。

#### 【0038】

MOS トランジスタ  $Q_2$  がオフ状態のとき、MOS トランジスタ  $Q_4$  のゲートには、抵抗  $R_6$  を介して電源電圧  $V_D$  が印加されるので、MOS トランジスタ  $Q_4$  はオン状態となる。

#### 【0039】

従って、駆動回路 2-1 の出力電圧  $V_{out}$  は接地電位となり、半導体素子（例えば、n チャネルMOS トランジスタ  $Q_5$ ）をオフ状態に保つことができる。これにより、電源起動時にIC12 の誤動作によりハイレベルの信号が出力される場合でも、駆動回路 2-1 の出力電圧  $V_{out}$  を接地電位にして、制御対象の半導体素子をオフ状態にすることができる。

#### 【0040】

上述した第 2 の実施の形態によれば、IC12 の出力が変化したときに、駆動回路 2-1 の出力段のMOS トランジスタ  $Q_3$ 、 $Q_4$  が同時にオンするのを防止できる。さらに、電源起動時にIC12 が誤動作して外部の半導体素子をオンにする信号（例えば、ハイレベルの信号）が出力されても、ツエナーダイオード ZD2 によりゲート電圧を制限することで、駆動回路 2-1 から半導体素子をオン状態にする信号が出力されるのを防止することができる。

#### 【0041】

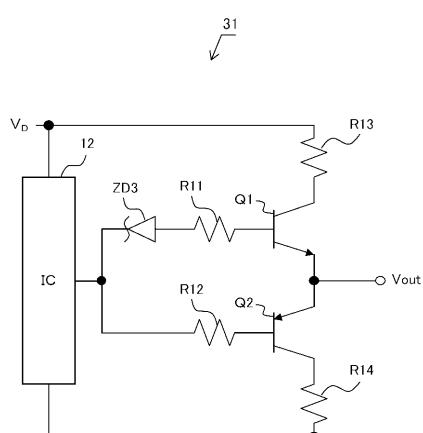

次に、図 4 は、第 3 の実施の形態の駆動回路 3-1 の回路図である。この第 3 の実施の形態は、駆動回路 3-1 をバイポーラトランジスタ  $Q_1$ 、 $Q_2$  で構成した例であり、トランジ

10

20

30

40

50

スタ Q 1、Q 2 が駆動回路 3 1 の出力段のトランジスタに該当する。

【0042】

I C 1 2 の出力は、ツェナーダイオード Z D 3 と抵抗 R 1 1 を介して、トランジスタ Q 1 のベースに入力している。また、I C 1 2 の出力は、抵抗 R 1 2 を介してトランジスタ Q 2 のベースに入力している。トランジスタ Q 1 のコレクタは抵抗 R 1 3 を介して電源電圧 V<sub>D</sub> に接続され、トランジスタ Q 1 のエミッタとトランジスタ Q 2 のエミッタが接続され、トランジスタ Q 2 のコレクタは接地（または基準電位）されている。トランジスタ Q 1 とトランジスタ Q 2 の接続点から、図示しない半導体素子を駆動する駆動電圧 V<sub>out</sub> が出力される。

【0043】

I C 1 2 の出力がローレベルのとき、トランジスタ Q 1 がオフ、トランジスタ Q 2 がオンとなっている。I C 1 2 の出力がローレベルからハイレベルに変化すると、トランジスタ Q 2 はオフ状態に変化するが、トランジスタ Q 1 は、I C 1 2 の出力電圧が、ツェナーダイオード Z D 3 のツェナー電圧以上で、かつトランジスタ Q 1 のオン電圧以上となるまでオフ状態を維持する。これにより、I C 1 2 の出力が変化するときに、駆動回路 3 1 の出力段のトランジスタ Q 1、Q 2 が同時にオンするのを防止できる。

【0044】

本発明は上述した実施の形態に限らず、例えば、以下のように構成しても良い。

駆動回路に使用するトランジスタはMOSトランジスタに限らず、バイポーラトランジスタ等の他の半導体素子でも良い。また、駆動回路は、縦続接続されたトランジスタが2段接続された回路に限らず、図4に示すような1段構成の回路、あるいは3段以上の回路であっても良い。

【図面の簡単な説明】

【0045】

【図1】第1の実施の形態の駆動回路の回路図である。

【図2】第2の実施の形態の駆動回路の回路図である。

【図3】第2の実施の形態の動作波形を示す図である。

【図4】第3の実施の形態の駆動回路の回路図である。

【図5】従来の駆動回路の回路図である。

【図6】従来の駆動回路の動作波形を示す図である。

【符号の説明】

【0046】

1 1、2 1、3 1、4 1 駆動回路

1 2 I C

Z D 1、Z D 2、Z D 3 ツェナーダイオード

Q 1 ~ Q 5 トランジスタ

10

20

30

【図1】

【図3】

【図2】

【図5】

【図6】

---

フロントページの続き

(56)参考文献 特開平01-305618(JP,A)

特開平05-003429(JP,A)

特開2007-088599(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 17/00 - 17/70