(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6224157号

(P6224157)

(45) 発行日 平成29年11月1日(2017.11.1)

(24) 登録日 平成29年10月13日(2017.10.13)

(51) Int.Cl.

F 1

|                     |                  |      |        |         |

|---------------------|------------------|------|--------|---------|

| <b>H01L 21/336</b>  | <b>(2006.01)</b> | H01L | 29/78  | 6 1 7 J |

| <b>H01L 29/786</b>  | <b>(2006.01)</b> | H01L | 29/78  | 6 1 8 B |

| <b>H01L 21/8234</b> | <b>(2006.01)</b> | H01L | 27/06  | 1 0 2 A |

| <b>H01L 27/06</b>   | <b>(2006.01)</b> | H01L | 27/088 | 3 3 1 E |

| <b>H01L 27/088</b>  | <b>(2006.01)</b> | H01L | 27/088 | E       |

請求項の数 6 (全 24 頁) 最終頁に続く

|              |                                                                  |

|--------------|------------------------------------------------------------------|

| (21) 出願番号    | 特願2016-80026 (P2016-80026)                                       |

| (22) 出願日     | 平成28年4月13日 (2016.4.13)                                           |

| (62) 分割の表示   | 特願2011-192413 (P2011-192413)<br>の分割<br>原出願日 平成23年9月5日 (2011.9.5) |

| (65) 公開番号    | 特開2016-131258 (P2016-131258A)                                    |

| (43) 公開日     | 平成28年7月21日 (2016.7.21)                                           |

| 審査請求日        | 平成28年4月14日 (2016.4.14)                                           |

| (31) 優先権主張番号 | 特願2010-197220 (P2010-197220)                                     |

| (32) 優先日     | 平成22年9月3日 (2010.9.3)                                             |

| (33) 優先権主張国  | 日本国 (JP)                                                         |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 竹村 保彦<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査官       | 岩本 勉                                           |

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

電界効果トランジスタを有する半導体回路を形成する工程と、

前記電界効果トランジスタのフローティング電極に電荷を帯電させる工程と、

前記帯電工程の後、前記半導体回路を遮光膜で覆う工程と、を有し、

前記電界効果トランジスタは、

半導体層と、

前記半導体層と接する領域を有する第1の導電層と、

前記半導体層と接する領域を有する第2の導電層と、

前記半導体層上方に設けられ、且つ前記半導体層と重なる領域を有する第3の導電層と

、を有し、

前記フローティング電極は、前記半導体層と前記第3の導電層との間に設けられ、

前記フローティング電極は、前記半導体層を横切るように設けられ、

前記帯電工程の後、前記フローティング電極に蓄積された電荷量は、変更されないことを特徴とする半導体装置の作製方法。

## 【請求項 2】

請求項1において、

前記半導体層は、インジウム及び亜鉛を含む酸化物を有し、

前記酸化物において、インジウム及び亜鉛の全金属元素に占める比率が、25%以上である酸化物を有することを特徴とする半導体装置の作製方法。

**【請求項 3】**

請求項 1 又は 2 において、

前記半導体層は、バンドギャップが 3 . 0 eV 以上 4 . 5 eV 以下である酸化物を有することを特徴とする半導体装置の作製方法。

**【請求項 4】**

請求項 1 乃至 3 のいずれか一において、

前記半導体層は、第 1 のドーピング領域と、第 2 のドーピング領域と、を有し、

前記半導体層において、前記第 1 のドーピング領域のキャリア濃度と、前記第 2 のドーピング領域のキャリア濃度とは、前記第 1 のドーピング領域及び前記第 2 のドーピング領域以外の領域のキャリア濃度よりも高く、

10

前記第 1 のドーピング領域は、前記第 1 の導電層と接する領域を有し、

前記第 2 のドーピング領域は、前記第 2 の導電層と接する領域を有することを特徴とする半導体装置の作製方法。

**【請求項 5】**

請求項 1 乃至 4 のいずれか一において、

前記帯電工程において、前記フローティング電極に蓄積させる電荷量は、前記半導体回路の特性のばらつきが低減するように、決定することを特徴とする半導体装置の作製方法。

**【請求項 6】**

請求項 1 乃至 5 のいずれか一において、

20

前記フローティング電極は、絶縁物で覆われた導体、又は、絶縁物で覆われた半導体を有することを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、電界効果トランジスタ (FET) 、FET を有する半導体回路、FET もしくは半導体回路を有する半導体装置に関する。

**【背景技術】****【0002】**

FET とは、半導体にソース、ドレインという領域を設け、それぞれに電極を設けて、電位を与え、絶縁膜（ゲート絶縁膜と呼ばれる）あるいはショットキーバリヤを介してゲートとよばれる電極より半導体に電界をかけ、半導体の状態を制御することにより、ソースとドレイン間に流れる電流を制御するものである。用いられる半導体としては、シリコンやゲルマニウム等の 14 族元素やガリウムヒ素、インジウムリン、窒化ガリウム、硫化亜鉛、カドミウムテルル等の化合物等が挙げられる。

30

**【0003】**

近年、酸化亜鉛や酸化インジウムガリウム亜鉛系化合物等の酸化物を半導体として用いた FET が報告された（特許文献 1 および特許文献 2）。これらの酸化物半導体を用いた FET では、比較的大きな移動度が得られると共に、それらの材料が 3 電子ボルト以上の大きなバンドギャップを有するために、酸化物半導体を用いた FET をディスプレーやパワーデバイス等に応用することが提案されている。

40

**【0004】**

例えば、バンドギャップが 3 電子ボルト以上ということは、可視光に対して透明であるので、ディスプレーとして用いた場合、FET 部分も光を透過でき、開口率が向上することが期待される。

**【0005】**

また、このような大きなバンドギャップという特徴は、パワーデバイスに用いられる炭化シリコンと同じなので、同様にパワーデバイスとなることが期待される。

**【0006】**

さらに、バンドギャップが大きいということは、熱励起キャリアが少ないことを意味する

50

。例えば、室温において、シリコンでは、バンドギャップが1.1電子ボルトであるので、熱励起キャリアは $10^{11} / \text{cm}^3$ 程度であるが、バンドギャップが3.2電子ボルトの半導体では、熱励起キャリアは $10^{-7} / \text{cm}^3$ 程度と計算される。

#### 【0007】

シリコンの場合、全く、不純物を含まないものを作っても、熱励起によるキャリアが上記のように存在するため、室温での抵抗率は、 $10^5 \text{ cm}$ 以上にできないが、バンドギャップが3.2電子ボルトの半導体では、理論的には、 $10^{20} \text{ cm}$ 以上の抵抗率が得られる。このような半導体でFETを作製し、オフ状態（ゲートの電位がソースの電位と同じ状態）における高い抵抗率を用いれば、電荷を半永久的に閉じこめることも可能となると期待される。

10

#### 【0008】

ところで、特に亜鉛もしくはインジウムを有する酸化物半導体においては、これまで、P型の導電性を示すものはほとんど報告されていない。そのため、シリコンのFETのようなPN接合を用いたものは報告されておらず、特許文献1および特許文献2にあるように、N型あるいはI型（本明細書では、キャリア濃度が $10^{12} / \text{cm}^3$ 以下の半導体をI型という）の酸化物半導体に導体電極等を接触させた導体半導体接合（学術書では、一般に金属半導体接合、Metal Insulator Junctionと言われるが、本明細書では、文言の解釈をより正確にするため、このように表現する）によって、ソース、ドレインを形成している。

20

#### 【先行技術文献】

#### 【特許文献】

#### 【0009】

【特許文献1】米国特許公開2005/0199879号公報

【特許文献2】米国特許公開2007/0194379号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

さて、導体半導体接合によって、ソース、ドレインを形成したFETでは、用いる半導体のキャリア濃度が大きいと、オフ状態でもソースとドレインの間に電流（オフ電流、本明細書では、オフ電流とは、ゲートの電位がソースの電位と同じか低い場合のソースとドレイン間に流れる電流のことを言う）が流れてしまう。そこで、半導体中のキャリア濃度を低減させて、I型とすることにより、オフ電流を低減することが望まれる。しかしながら、このような試みは、FETのチャネル長が短い場合や、半導体層やゲートと半導体層の間の絶縁膜が厚い場合には適用できないことが発明者の考察で明らかとなった。

30

#### 【0011】

一般に、導体半導体接合においては、導体の仕事関数と半導体の電子親和力（あるいはフェルミ準位）の関係によって、オーミック接合になったり、ショットキーバリヤ型接合になったりする。例えば、電子親和力が4.3電子ボルトの半導体に、仕事関数3.9電子ボルトの導体を接触させ、理想的な（界面に何らトラップ準位や化合物が形成されない状態の）導体半導体接合を形成したとすると、導体から半導体へ電子が流入する。

40

#### 【0012】

その場合、半導体では、導体と半導体の接合界面に近いほど電子の濃度が高く、電子濃度は、大雑把な計算では、導体半導体接合界面から数nmでは $10^{20} / \text{cm}^3$ 程度、数十nmでは $10^{18} / \text{cm}^3$ 程度、数百nmでは $10^{16} / \text{cm}^3$ 程度、数μmでも $10^{14} / \text{cm}^3$ 程度である。すなわち、半導体自体がI型であっても、導体との接触によって、キャリア濃度の高い領域ができてしまう。このようなキャリアの多い領域が導体半導体接合界面近傍にできることにより、導体半導体接合はオーミック接合となる。

#### 【0013】

一方、例えば、電子親和力が4.3電子ボルトの半導体に、仕事関数4.9電子ボルトの導体を接触させ、理想的な導体半導体接合を形成したとすると、半導体に存在する電子が

50

導体へ移動する。電子がなくなった領域では、当然のことながら、電子の濃度は極めて低くなる。電子が移動する半導体の領域の幅は、半導体の電子濃度に依存し、例えば、もともとの半導体の電子濃度が  $10^{18} / \text{cm}^3$  であれば、数十 nm 程度である。

#### 【0014】

そして、この部分の電子濃度が著しく低くなるため、バンド図においては、導体と半導体との接合界面において、バリヤができる。このようなバリヤを有する導体半導体接合をショットキーバリヤ型接合という。電子は、半導体から導体へは流れやすいが、導体から半導体へは、バリヤがあるため流れにくい。したがって、ショットキーバリヤ型接合では整流作用が観測される。

#### 【0015】

同様のことは、導体が直接、半導体に接していなくても起こる。例えば、半導体と導体との間に絶縁膜が存在する場合にも半導体の電子濃度は導体の影響を受ける。もちろん、その程度は、絶縁膜の厚さや誘電率により影響される。絶縁膜が厚くなるか、誘電率が低くなれば、導体の影響は小さくなる。

#### 【0016】

ソースと半導体あるいはドレインと半導体との接合は、電流が流れやすいことが好ましいので、特許文献 1 あるいは特許文献 2 にあるような FET においては、オーミック接合となるように導体材料が選択される。例えば、チタンや窒化チタン等である。電極と半導体との接合がオーミック接合であると、得られる FET の特性が安定し、良品率が高くなるというメリットもある。

#### 【0017】

また、ゲートの材料としては、半導体の電子を排除する作用を有する材料が選択される。例えば、タンゲステンや白金等の仕事関数の大きな材料である。このような材料を用いても、チャネル長（典型的には、ソース電極とドレイン電極の間隔） $L$  と実効的なゲート絶縁膜と半導体の厚さの和  $T$ （以下、典型的な厚さという）の比率  $L/T$  が 10 以上であれば、ゲートとソースの電位を等しくしたときのオフ電流（以下、ゼロ電流という）が  $1 \times 10^{-16} \text{ A}$  以下の FET を作製できる。ここで、 $T = (\text{ゲート絶縁膜の厚さ} \times \text{半導体の誘電率}) / \text{ゲート絶縁膜の誘電率} + \text{半導体の厚さ}$ 、で算出される。

#### 【0018】

すなわち、より  $L$  を大きく、 $T$  を薄くすると、よりゼロ電流の低い FET が得られる。しかしながら、デバイスの微細化を進めるに伴う缩小とともに、ゲート絶縁膜を過剰に薄くすると、トンネル電流によるリークが生じ、さらに、ゲート絶縁膜や半導体を過剰に薄くすることは技術的な困難を伴う。一方、パワーデバイスへの応用では、耐圧を高めるために、ゲート絶縁膜を厚くすることも求められる。

#### 【0019】

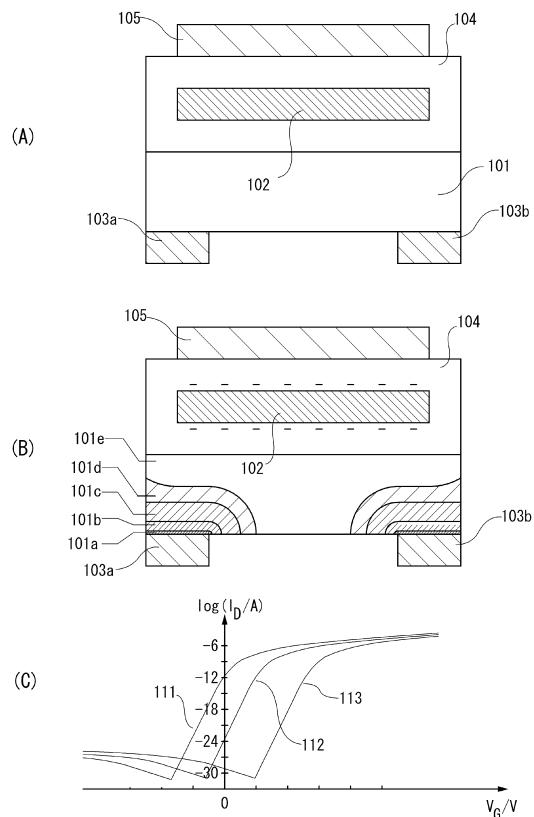

すると、比率  $L/T$  が低下し、特に比率  $L/T$  が 4 以下となると、ゼロ電流をシリコン半導体を用いた FET よりも低く保つことは不可能となる。その原因を図 2 を用いて説明する。図 2 (A) には導体半導体接合を有する典型的な FET の構造を示す。すなわち、半導体層 101 の一方の面にソース電極 103a とドレイン電極 103b を有する。また、半導体層 101 の他方の面にはゲート絶縁膜として機能する絶縁物 104 とゲート 105 を有する。

#### 【0020】

ソース電極 103a と半導体層 101、およびドレイン電極 103b と半導体層 101 との接合はオーミック接合となるように、導体が選択されており、また、ゲート 105 には半導体の電子親和力より仕事関数の大きな材料を用いることにより、ソース電極 103a やドレイン電極 103b から流入する電子を排除するようとする。

#### 【0021】

それぞれの作用は、ソース電極 103a やドレイン電極 103b やゲート 105 からの距離に依存すると考えられる。話を単純にするため、ソース電極 103a やドレイン電極 103b が半導体層 101 に電子を注入しようとする力と、ゲート 105 が半導体層 101

10

20

30

40

50

から電子を排除しようとする力を等しいものと考える。すなわち、半導体層 101 の中で双方から同じだけ離れた場所では、それぞれの力が拮抗して、電子濃度は、もともとあった値と等しくなるとする。

#### 【0022】

また、ソース電極 103a やドレイン電極 103b がゲート 105 より近い場所では、前者の作用が勝り、その地点では、電子濃度がより高くなる。逆に、前者より後者の方が近い場所では、後者の作用が勝り、その地点では、電子濃度がより低くなる。

#### 【0023】

ここで、距離について注意しておく。この場合の距離とは、空間的な距離ではなく、電磁気的な距離であるので、空間的な距離に誘電率をかけた値で比較する必要がある。

10

#### 【0024】

上記の前提に基づく、図 2 (A) の FET の半導体層 101 中の電子濃度の概念的な等濃度線を図 2 (B) に示す。ここでは、話を簡単にするために、絶縁物 104 の誘電率は半導体層 101 の誘電率と等しいものとする。また、ソース電極 103a、ドレイン電極 103b とゲート 105 の電位は等しくしてある。

#### 【0025】

ソース電極 103a やドレイン電極 103b と半導体層 101 との界面付近には電子濃度の高い領域 101a が存在する。そして、その次には、それよりも 1 術程度電子濃度の低い領域 101b、さらに、その外側には、さらに 1 術程度電子濃度の低い領域 101c が存在し、さらに、その外側には、さらに 1 術程度電子濃度の低い領域 101d が存在し、その、外側には、電子濃度がそれ未満の領域 101e が存在する。

20

#### 【0026】

注目すべきは、領域 101d が半導体層 101 のゲート 105 との反対側の面でつながっているということである。これは、その領域まではゲート 105 の力が及ばず、ソース電極 103a やドレイン電極 103b の力により電子が注入されたためである。

#### 【0027】

この図においては、比率 L / T は 2 弱である。ソース電極 103a とドレイン電極 103b の間の距離を 120 nm とすれば、半導体層 101 の厚さは 50 nm であり、領域 101a と領域 101b との間の等濃度線は、概ね、電子濃度が  $10^{20} / \text{cm}^3$  であり、領域 101d と領域 101e との間の等濃度線は、概ね、電子濃度が  $10^{17} / \text{cm}^3$  であることを示すと考えてよい。

30

#### 【0028】

また、ソース電極 103a とドレイン電極 103b の間の距離を 1.2 μm とすれば、半導体層 101 の厚さは 0.5 μm であり、領域 101a と領域 101b との間の等濃度線は、概ね、電子濃度が  $10^{18} / \text{cm}^3$  であり、領域 101d と領域 101e との間の等濃度線は、電子濃度が概ね、 $10^{15} / \text{cm}^3$  であることを示すと考えてよい。

#### 【0029】

電子濃度が  $10^{15} / \text{cm}^3$  という値は、十分に低い値のように思えるが、抵抗率で 1 k cm 程度である。図に示すように、半導体層の 3 分の 1 以上は、電子濃度が  $10^{15} / \text{cm}^3$  以上であるので、チャネル長とチャネル幅が同じ FET においては、抵抗は 10 M 程度であり、ソース電極 103a とドレイン電極 103b 間の電位差を 1 V とした場合ゼロ電流は 0.1 μA も流れれる。

40

#### 【0030】

つまり、ゼロ電流を小さくするには、このようなゲートの反対側の電子濃度が無視できない領域をなくすことが必要である。そのためには、半導体層 101 を薄くすることが考えられる。つまり、ゲート 105 の影響力が及ばない領域を減らすことである。図の場合では、厚さを 75 % とすればよい。例えば、半導体層 101 を半分の厚さにすれば、ゼロ電流は 10 万分の 1 まで下げることができる計算される。

#### 【0031】

しかしながら、例えば、ソース電極 103a とドレイン電極 103b の間の距離が 24 n

50

mというような極めて小さなデバイスにおいては、半導体層101の厚さを3.75nm以下、例えば、2.5nm以下としなければならず、そのような薄い半導体層101を均質に形成することには技術的な困難が伴う。

#### 【0032】

第2の方法は絶縁物104を薄くすることである。図の絶縁物104の厚さを6分の1以下とすれば、ゲート105の影響力を、半導体層101の裏面にまで及ぼすことができる。しかし、上記の例と同様に、ソース電極103aとドレイン電極103bの間の距離を24nmとすると、絶縁物104は0.8nm以下である必要がある。

#### 【0033】

酸化物半導体上においては、ゲート絶縁膜はスパッタ法やCVD法によって形成されている。これらの方法は、シリコンの熱酸化法のように、高性能な絶縁膜を均一の厚さで形成することは困難なので、やはり、現実的ではない。さらに、仮に熱酸化法による高品質な絶縁膜であったとしても、厚さが1nm以下のものでは、トンネル電流によるリーク電流が問題となる。

#### 【0034】

ソース電極とドレイン電極間の電流が極めて低くても、ソース電極とゲートあるいはドレイン電極とゲートの間でのリーク電流がそれ以上に大きければ、電荷を保持するという目的には使用できない。また、それ以外の目的で使用するにしても、リーク電流は消費電力の増大をもたらすので好ましくない。

#### 【0035】

FETのゲート電圧( $V_G$ )とドレイン電流( $I_D$ )の関係( $I_D - V_G$ 曲線)は、図2(C)に示すようなチャネル長依存性を示すことが計算から明らかとなる。図2(C)において、曲線114、曲線115、曲線116は、いずれも、チャネル長とチャネル幅が等しいFETの $I_D - V_G$ 曲線である。ここで、典型的な厚さTは一定としている。なお、図2(C)に示す曲線はFETの特性の変動をわかりやすく説明するためのもので、実測値ではない。

#### 【0036】

チャネル長とチャネル幅が等しい理想的なFETではオン電流が、チャネル長によって変化することはないが、しきい値やサブスレショールド特性値は変化することがある。このことは、通常のMOSFETでも短チャネル効果として知られている。導体半導体接合を有するFETでは、図2(C)のように、チャネル長によるしきい値やサブスレショールド特性値(S値)が変化する。

#### 【0037】

すなわち、曲線116は比較的チャネル長の大きなFETである。曲線115は、チャネル長がその1/10程度のものである。曲線114はチャネル長が曲線116の1/10程度のものである。このように、チャネル長が短くなるにしたがって、ゲートの電圧をソースと同じ0Vとしたときのドレイン電流(すなわち、ゼロ電流)が増加し、また、曲線の傾きが緩慢になる(S値が増加する)。

#### 【0038】

上記の考察は、ソース電極103aやドレイン電極103bが半導体層101に電子を注入しようとする力と、ゲート105が半導体層101から電子を排除しようとする力が等しいという前提であり、前者の力が後者よりも大きければ、より多くの電子がソース電極103aやドレイン電極103bから半導体層101に注入される。

#### 【0039】

本発明は、上記の問題に鑑みてなされたものである。本発明は導体半導体接合を有する新規の半導体装置、あるいは、新規のFET、あるいは新規の半導体装置の製造方法、あるいは新規のFETの製造方法の少なくともひとつを提供することを課題とする。

#### 【0040】

また、本発明は、上記に説明したように導体半導体接合を有するFETのサイズを変更することにより、FETのゼロ電流が増大してしまうことに対して有効な対策を提供するこ

10

20

30

40

50

とを課題の一つとする。特に、比率  $L / T$  が 4 以下、あるいは、 $L$  が 100 nm 未満の FETにおいて、ゼロ電流が実用的に十分な小ささとなるような新規の構造を提供することを課題の一つとする。本発明は上記の課題の少なくとも 1 つを解決する。

**【課題を解決するための手段】**

**【0041】**

以下、本発明の説明をおこなうが、本明細書で用いる用語について簡単に説明する。まず、FET のソースとドレインについては、本明細書においては、N チャネル型 FET においては、高い電位を与えられる方をドレイン、他方をソースとし、P チャネル型 FET においては、低い電位を与えられる方をドレイン、他方をソースとする。いずれの電位もおなじであれば、いずれか一方をソース、他方をドレインとする。また、ソース電極、ドレン電極という用語のかわりに第 1 の導体電極、第 2 の導体電極とも表現することがある。その場合は、電位の高低によって呼び名を変えない。10

**【0042】**

本発明の態様の一は、半導体層と、その一の面に接して設けられた第 1 および第 2 の導体電極と、半導体層のその面あるいは他の面に設けられたゲートとを有する FET において、半導体層とゲートとの間に、絶縁物に周囲を覆われた導体もしくは半導体よりなり、一定の電荷により帯電したフローティング電極を有し、フローティング電極は、半導体層を横切るように設けられ、かつ、FET には PN 接合が存在しないという構成を有する。

**【0043】**

本発明の態様の一は、半導体層と、その一の面に接して設けられた第 1 および第 2 の導体電極と、半導体層のその面あるいは他の面に設けられたゲートとを有する FET において、半導体層とゲートとの間に、絶縁物に周囲を覆われた導体もしくは半導体よりなり、一定の電荷により帯電したフローティング電極を有し、フローティング電極は、半導体層を横切るように設けられ、かつ、第 1 および第 2 の導体電極と半導体層との間には導体半導体接合が存在するという構成を有する。20

**【0044】**

上記において、FET を有する半導体装置は、フローティング電極を帯電させるための回路を有しないことが好ましい。また、上記において、フローティング電極に蓄積された電荷量は製造工程完了後は、使用者が変更できない設定となっていることが好ましい。

**【0045】**

本発明の態様の一は、半導体層と、その一の面に接して設けられた第 1 および第 2 の導体電極と、半導体層のその面あるいは他の面に設けられたゲートとを有し、半導体層とゲートとの間に、絶縁物に周囲を覆われた導体もしくは半導体よりなるフローティング電極を有し、フローティング電極は、半導体層を横切るように設けられた FET を有する半導体回路を作製する工程と、フローティング電極を帯電させる工程と、その後、遮光性の材料で半導体回路を覆う工程とを有する、半導体装置の作製方法である。30

**【0046】**

本発明の態様の一は、半導体層と、その一の面に接して設けられた第 1 および第 2 の導体電極と、半導体層のその面あるいは他の面に設けられたゲートとを有し、半導体層とゲートとの間に、絶縁物に周囲を覆われた導体もしくは半導体よりなるフローティング電極を有し、フローティング電極は、半導体層を横切るように設けられた FET を有する半導体回路を作製する工程と、その半導体回路に設けられたパッドを通して、外部より電圧を印加することにより、フローティング電極を帯電させる工程とを有する、半導体装置の作製方法である。40

**【0047】**

上記において、FET が N チャネル型の場合は、フローティング電極は、負に帯電し、FET が P チャネル型の場合は、フローティング電極は、正に帯電するようにするとよい。また、半導体層は、インジウム (In) の全金属元素に占める比率、亜鉛 (Zn) の全金属元素に占める比率、あるいは In と Zn の全金属元素に占める比率のいずれかが少なくとも 25 % 以上である酸化物としてもよい。また、半導体層は、バンドギャップが 3.050

eV以上4.5eV以下の酸化物としてもよい。また、半導体層は、硫化物等の16族化合物でもよい。

#### 【0048】

なお、本明細書で酸化物とは、その物質（化合物を含む）に含まれる窒素、酸素、フッ素、硫黄、セレン、塩素、臭素、テルル、ヨウ素の占める割合（モル比）が全体の25%以上で、かつ、以上の元素に対する酸素の割合（モル比）が70%以上のものをいう。

#### 【0049】

また、本明細書で金属元素とは、希ガス元素、水素、ホウ素、炭素、窒素、16族元素（酸素等）、17族元素（フッ素等）、珪素、燐、ゲルマニウム、砒素、アンチモン以外の全ての元素のことである。

10

#### 【0050】

さらに、本明細書において、ある（1つの）元素（あるいは金属元素）を主たる成分（あるいは金属成分）とする、とはその物質中に元素（あるいは金属元素）が複数ある中で、当該元素（あるいは金属元素）が元素（あるいは金属元素）全体の50%以上を占める場合を言う。また、n種の元素（あるいは金属元素）M<sub>1</sub>、M<sub>2</sub>、…、M<sub>n</sub>を主たる成分（あるいは金属成分）とするとは、元素（あるいは金属元素）M<sub>1</sub>、M<sub>2</sub>、…、M<sub>n</sub>のそれぞれの占める比率の総和が元素（あるいは金属元素）全体の{ (1 - 2<sup>-n</sup>) × 100 } [%]以上を占める場合をいう。

#### 【0051】

なお、本明細書において記載されている膜中の主たる成分でない元素の濃度は、特に断らない限り、二次イオン質量分析法により検出される濃度の最低値である。一般に、二次イオン質量分析法により、単層あるいは多層の膜の深さ方向の元素の濃度の分析をおこなうと、特に微量元素の場合、基板と膜あるいは膜と膜の界面では元素濃度が異常に高くなる傾向があるが、このような部分の濃度は正確な値ではない上、測定ごとのばらつきも大きい。

20

#### 【0052】

半導体層に酸化物半導体を用いる場合には、少なくともInあるいはZnを含むことが好み。特にInとZnを含むことが好み。また、該酸化物を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好み。また、スタビライザーとしてスズ(Sn)を有することが好み。また、スタビライザーとしてハフニウム(Hf)を有することが好み。また、スタビライザーとしてアルミニウム(Al)を有することが好み。

30

#### 【0053】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

#### 【0054】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物、三元系金属の酸化物であるIn-Ga-Zn系酸化物、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、四元系金属の酸化物であるIn-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸

40

50

化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物を用いることができる。

#### 【0055】

なお、ここで、例えば、In-Ga-Zn系酸化物とは、InとGaとZnを主たる金属成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

#### 【0056】

例えば、 $In : Ga : Zn = 1 : 1 : 1 (= 1/3 : 1/3 : 1/3)$ あるいは $In : Ga : Zn = 2 : 2 : 1 (= 2/5 : 2/5 : 1/5)$ の原子比のIn-Ga-Zn系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $In : Sn : Zn = 1 : 1 : 1 (= 1/3 : 1/3 : 1/3)$ 、 $In : Sn : Zn = 2 : 1 : 3 (= 1/3 : 1/6 : 1/2)$ あるいは $In : Sn : Zn = 2 : 1 : 5 (= 1/4 : 1/8 : 5/8)$ の原子比のIn-Sn-Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

10

#### 【0057】

しかし、これらに限られず、必要とする半導体特性（移動度、しきい値、ばらつき等）に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

#### 【0058】

例えば、In-Sn-Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In-Ga-Zn系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

20

#### 【0059】

なお、例えば、In、Ga、Znの原子数比が $In : Ga : Zn = a : b : c (a + b + c = 1)$ である酸化物の組成が、原子数比が $In : Ga : Zn = A : B : C (A + B + C = 1)$ の酸化物の組成の近傍であるとは、a、b、cが、

$(a - A)^2 + (b - B)^2 + (c - C)^2 \leq r^2$

を満たすことを言い、rは、例えば、0.05とすればよい。他の酸化物でも同様である。

#### 【0060】

30

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

#### 【0061】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるために、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

#### 【0062】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成する方が好ましく、具体的には、平均面粗さ( $R_a$ )が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。なお、 $R_a$ は、JIS B 0601で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものである。

40

#### 【0063】

また、上記において、半導体層がドーピングにより、キャリアを高濃度に有する第1のドーピング領域と第2のドーピング領域を有するように構成し、第1のドーピング領域は第1の導体電極に接し、第2のドーピング領域は第2の導体電極に接するようにしてもよい。第1および第2のドーピング領域におけるキャリア濃度は $1 \times 10^{18} / \text{cm}^3$ 以上1

50

$\times 10^{21} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{19} / \text{cm}^3$  以上  $1 \times 10^{20} / \text{cm}^3$  未満となるように設定すればよい。

#### 【0064】

上記において、第1および第2の導体電極の半導体層と接する部分の仕事関数は、半導体層の電子親和力と0.3電子ボルトの和（すなわち、電子親和力+0.3電子ボルト）よりも小さい、あるいは、第1および第2の導体電極と半導体層はオーミック接合であることが好ましい。また、第1の導体電極と第2の導体電極は同じ材料で構成される必要はない。

#### 【0065】

なお、第1の導体電極をソース電極、第2の導体電極をドレイン電極と読み替えてよいし、第1の導体電極をドレイン電極、第2の導体電極をソース電極と読み替えてよい。10

#### 【0066】

また、上記において、フローティング電極を構成する材料の仕事関数は、第1の導体電極の仕事関数もしくは第2の導体電極の仕事関数より0.6電子ボルト以上、大きいことが好ましい。あるいは、フローティング電極を構成する材料の仕事関数は、半導体層の電子親和力より0.6電子ボルト以上、大きいことが好ましい。

#### 【発明の効果】

#### 【0067】

上記の構成のいずれかを採用することにより、前記課題を解決できる。以下、図面を用いて本発明のFETの作用効果について説明する。以下で、使用する用語は、上記に使用した用語と基本的に同じものを用いる。したがって、それらの用語の示す材料には、上記で使用した各用語に適用される条件を適用すればよい。例えば、以下の説明でソース電極という説明があった場合には、その仕事関数としては上記の説明で示されたものを用いればよい。20

#### 【0068】

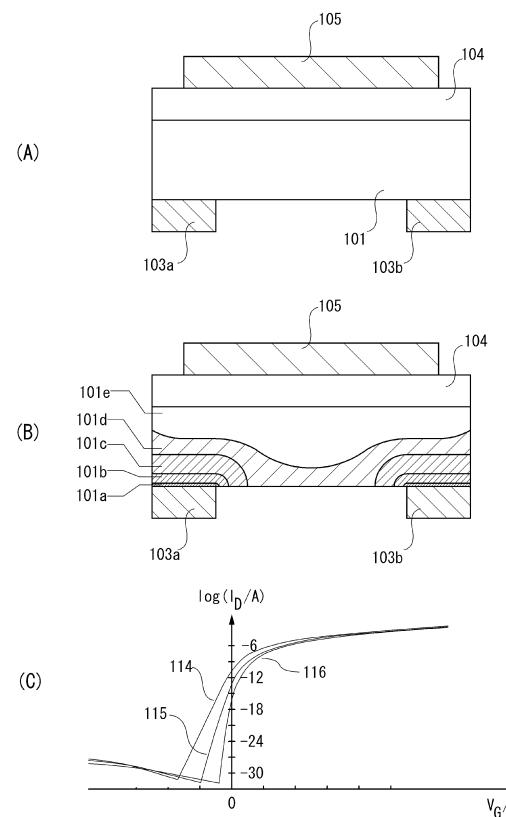

図1には本発明のFETの一例を示す。図1(A)のFETは半導体層101と、その一方の面にソース電極103aとドレイン電極103b、半導体層101の他方の面にゲート105を有する。さらに、半導体層101とゲート105の間に、絶縁物104で覆われたフローティング電極102を有する。

#### 【0069】

フローティング電極102は、外部の導体と接触していない状態（浮遊状態）であり、フローティング電極102に電荷が蓄積している場合は、極めて長期にわたって、その電荷を保持できる。フローティング電極102は、公知の書き換え可能ROM(EPROM)のフローティングゲートと同等のものである。ただし、図1に示すFETではフローティング電極102に電荷を蓄積する作業をおこなうのは、製造工程中だけである。30

#### 【0070】

フローティング電極102に電荷を蓄積するには、ゲート105とソース電極103aあるいはドレイン電極103bの一方、あるいは双方に十分に高い電圧を印加すればよい。また、その際、可視光を照射すると、より低い電圧でも電荷を蓄積できる。また、半導体層のバンドギャップよりエネルギーの大きな紫外光を照射しつつ、電圧を印加してもよい。40

#### 【0071】

FETがNチャネル型の場合には、フローティング電極102は負に帯電するようにし、Pチャネル型の場合には、フローティング電極102は正に帯電するようにする。

#### 【0072】

いずれにしても、製造後にフローティング電極102の電荷を消去することや、再度、電荷を蓄積する必要はないので、可視光や紫外光を再度、当てることや、高い電圧を印加する必要はない。したがって、FETに可視光や紫外光があたる構造や、高い電圧を発生させる回路をFETが含まれる半導体回路あるいは半導体装置に設ける必要はない。

#### 【0073】

例えば、紫外光を用いてフローティング電極 102 を帯電させた後、FET が含まれる半導体回路を遮光性のパッケージに封入してしまえばよい。とくに FET に光が当たらないようにすることが好ましい。そのことにより、フローティング電極 102 から電荷が漏洩することを防止でき、FET の特性を安定させることができる。

#### 【0074】

また、高い電圧を用いてフローティング電極 102 を帯電させるには、電圧を供給するための装置から半導体回路に設けられたパッドを通して、半導体回路中の FET に高い電圧を印加すればよい。さらに、フローティング電極 102 を帯電させた後、半導体回路を遮光性のパッケージに封入すればよい。

#### 【0075】

いずれにしても、フローティング電極 102 を帯電させる回数は限られており、また、紫外光を用いる場合には、過剰に高い電圧を用いないので、絶縁物 104 に与えられるダメージは極めて限定的であり、フローティング電極 102 に蓄積された電荷は長期にわたって保持される。

#### 【0076】

図 1 (B) は、FET が N チャネル型の場合を示している。図 1 (B) に示すように、フローティング電極 102 は負に帯電している。そのため、ソース電極 103a やドレイン電極 103b から半導体層 101 に流入した電子が影響を受け、図 2 (B) との比較から明らかのように、電子の濃度の高い領域は後退あるいは縮小する。

#### 【0077】

その結果、図 2 (B) では、半導体層 101 のゲート 105 の反対の面でつながっていた領域 101d が、図 1 (B) では途切れてしまい、ソース電極 103a とドレイン電極 103b との間の絶縁性が著しく向上する。すなわち、ゼロ電流を下げることができる。そのことは図 1 (C) に示す計算の結果からも明らかである。

#### 【0078】

図 1 (C) の曲線 111 は、フローティング電極 102 を帯電させない場合の  $I_D - V_G$  曲線であり、図 2 (C) の曲線 114 に相当するものである。 $V_G = 0 [V]$  でのドレイン電流（ゼロ電流）は  $1 \times 10^{-10} A$  程度である。しかしながら、フローティング電極 102 を適度に帯電させると、曲線 112 のようになり、ゼロ電流が  $1 \times 10^{-24} A$  まで低下する。

#### 【0079】

さらに、フローティング電極 102 を過剰に帯電させると、曲線 113 のようになり、ゼロ電流は  $1 \times 10^{-29} A$  程度で曲線 112 の場合より低下するが、しきい値が高くなり、十分なオン電流を得るためにゲートに大きな電圧を印加する必要が生じる。このようなことは半導体回路に過剰な負担を与えるので、特殊な目的以外には避けることが望ましい。なお、図 1 (C) に示す曲線は FET の特性の変動をわかりやすく説明するためのものであり、実測値ではない。

#### 【0080】

ゼロ電流は、FET の用途によって異なる。例えば、インバータ等の論理回路では、貫通電流による消費電力の低減のためには、 $1 \times 10^{-12} A$  以下であればよく、通常は、 $1 \times 10^{-15} A$  以下は必要とされない。一方、後述するような半永久的にデータを保存するメモリの用途であれば、 $1 \times 10^{-21} A$  以下、好ましくは、 $1 \times 10^{-24} A$  以下であることが求められる。

#### 【0081】

また、電荷を微調整することにより、複数の FET の特性をそろえることができる。上記の説明から明らかなように、導体半導体接合を有する FET では、半導体層の厚さ、ゲート絶縁膜の厚さ、チャネル長等の大きさによって、ゼロ電流やしきい値が変動する。そのような量を、すべての FET で等しくすることは困難であり、FET 間でばらつくことは避けられない。そのため FET のゼロ電流やしきい値がばらつくこととなる。

#### 【0082】

10

20

30

40

50

また、FETの特性のばらつきは、製造プロセスの条件等によっても変動する。例えば、半導体として酸化物半導体を用いる場合、多くはスパッタリング法で半導体層が形成されるが、用いるターゲットは同じでも、使い始め（新品）のときと長期間使用した後とで、形成される半導体層に微妙な差が生じことがある。

#### 【0083】

このような特性のばらつきは、個々のFETのフローティング電極102に蓄積する電荷の量を調整することで小さくできる。その結果、それまでであれば不良品となるFETを使用できるようになる。このことは特に集積度の高い半導体回路において効果が大である。すなわち、集積度の高い回路では、1つのFETが不良となった場合、それを代替する手段が限られるので、半導体回路全体が不良となることがある。すなわち、歩留まりの低下となる。上記の方法で、不良となるべきFETが救済されるのであれば、歩留まりは向上する。

#### 【0084】

上記の効果は、フローティング電極102の半導体層101から電子を排除する力がソース電極103aやドレイン電極103bが半導体層101に電子を注入する力より大きい場合に顕著である。このような力の大小は、仕事関数や電子親和力によって決定される。

#### 【0085】

具体的には、フローティング電極102の仕事関数が、ソース電極103aやドレイン電極103bの仕事関数より0.6電子ボルト以上大きいとよい。あるいは、フローティング電極102の仕事関数が、半導体層の電子親和力より0.6電子ボルト以上大きいとよい。

#### 【0086】

一般に、仕事関数の大きな材料を用いれば、フローティング電極102に蓄積する電荷量が少なくとも十分に低いゼロ電流が得られる。しかし、仕事関数の小さな材料であっても、フローティング電極102に蓄積する電荷量を大きくすれば十分に低いゼロ電流が得られるので、通常の使用では問題はない。ただし、仕事関数の大きな材料を用いると、蓄積された電荷が漏洩しにくいので、長期かつ高温での保存時にFETの特性を劣化させない効果がある。

#### 【0087】

また、フローティング電極102に用いる材料の仕事関数を、ゲート105あるいは半導体層101に用いる材料の仕事関数より大きくすると、フローティング電極102を帯電させる工程において、フローティング電極102をより効果的に帯電させることができる。

#### 【0088】

フローティング電極102を負に帯電させる場合、ゲート105に正の電圧を印加することにより、半導体層101の表面にできるチャネルから電子をフローティング電極102に移動させるのであるが、その際、一度、フローティング電極102に入った電子がゲート105に出てしまうこともある。

#### 【0089】

その際、フローティング電極102の材料の仕事関数が大きい場合には、絶縁物104の伝導帯がより高くなるため、フローティング電極102に入った電子がゲート105に出てしまう確率が低下する。そのため、効果的にフローティング電極102を帯電させることができる。

#### 【0090】

同様な効果は、フローティング電極102とゲート105の間の絶縁物104の厚さを、フローティング電極102と半導体層101の間のものより大きくすることでも得られる。ただし、その際にはゲート105と半導体層101との間の容量が低下するため、オン電流は減少する。

#### 【0091】

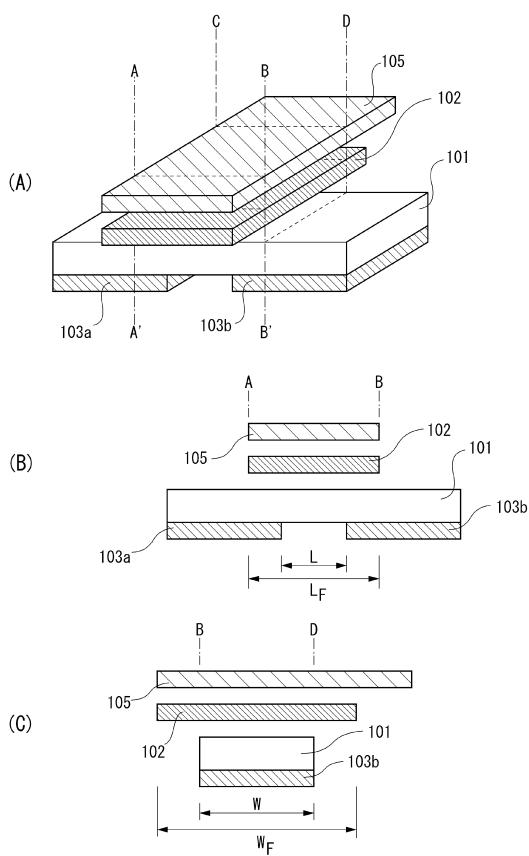

図3(A)は、図1(A)に示すFETを立体的に示すものである。また、図3(B)は

10

20

30

40

50

、図3(A)の線分A-A' と線分B-B' を含む面の断面図であり、図1(A)に相当する。また、図3(C)は、図3(A)の線分B-B' と線分D-D' (点D' は図3(A)では、FETの背後にあり表示できない)を含む面の断面図である。

#### 【0092】

図3(C)に示すように、フローティング電極102の長さ $W_F$  はFETのチャネル幅Wよりも大きく、半導体層101のチャネル幅方向の両端を覆うことが必要である。これに対し、図3(B)では、フローティング電極102の幅 $L_F$  がFETのチャネル長Lよりも大きく描かれているが、それに限定されない。例えば、フローティング電極102の幅 $L_F$  はFETのチャネル長Lよりも小さくてもよい。ただし、少なくとも、フローティング電極102の一端がソース電極103aとドレイン電極103bの間にあることが必要である。10

#### 【0093】

なお、本発明によって十分に低いゼロ電流を得るには、導体に接触しない状態での半導体層のキャリア濃度を $10^{12} / \text{cm}^3$  以下とすることが好ましい。なお、半導体層のキャリア濃度は導体に接すると、上記の説明のように、導体の近傍では導体からキャリアが注入されたり、導体にキャリアが吸収されたりして、本来のキャリア濃度を知ることは困難である。したがって、導体から十分に離れた(少なくとも $100 \mu\text{m}$ 以上離れた)部分での測定とすることが必要である。

#### 【0094】

上記に関連して、半導体層101が酸化物半導体である場合は、酸素欠損や水素濃度が小さい方が好ましい。酸素欠損や水素の混入はキャリアの源泉となるためである。また、水素を含有すると、FETの動作を不安定にする。水素濃度は $10^{18} / \text{cm}^3$  以下とすることが好ましい。20

#### 【0095】

上記の議論は導体半導体接合を有するFETに関するものであるが、キャリア濃度の濃度勾配を有するFETにおいても適応できる。特に、PN接合によってソースドレイン間の分離ができないFETにおいては本発明によってソースドレイン間の分離ができる。

#### 【0096】

導体と半導体との接合においては、上記の説明のように、仕事関数と電子親和力等によって導体から半導体に電子が供給されたり、半導体から導体に電子が吸収されたりする。同じことが高濃度のキャリアを有する領域と、低濃度のキャリアを有する領域で起こる。30

#### 【0097】

例えば、2つの領域、第1の領域と第2の領域があるとして、第1の領域は、電子濃度が $1 \times 10^{20} / \text{cm}^3$  で、第2の領域は、電子濃度が $1 \times 10^{12} / \text{cm}^3$  であるとする。その場合、第1の領域のフェルミ準位はバンド図では伝導帯の下端近辺に存在するのに對し、第2の領域のフェルミ準位はバンドギャップの中央付近に存在する。すなわち、第1の領域の電子の多くは、第2の領域の電子よりもポテンシャルが高い。

#### 【0098】

もし、第1の領域と第2の領域を接合すると、ポテンシャルの差により、第1の領域の電子は第2の領域に流入する。第1の領域の電子濃度が $1 \times 10^{20} / \text{cm}^3$  というような比較的、高濃度であれば、電子の供給は、導体と第2の領域が接した場合と同様と考えられ、第2の領域の相当、深い部分にまで電子が流入する。40

#### 【0099】

その程度は、第2の領域のフェルミ準位と第1の領域のフェルミ準位の差、すなわち、第2の領域の電子濃度と第1の領域の電子濃度の比率に依存し、第2の領域の電子濃度が低ければ、より深い部分にまで第1の領域から電子が注入される。いうまでもなく、このように注入された電子は、ゼロ電流を増加させる。

#### 【0100】

特に、シリコンの場合と、シリコンよりバンドギャップの大きな半導体の場合とを比較すると、後者の方が、第2の領域のより深い部分まで電子が注入される。これは、後者の方50

がバンドギャップが大きいため、第1の領域のフェルミ準位と第2の領域のフェルミ準位の差が大きいためである。

#### 【0101】

このような、高濃度のキャリアを有する領域からのキャリアの流入を防ぐには、上記のような帯電したフローティング電極によって流入する電子を排除し、半導体層中に電子濃度の極めて低い領域を形成すればよい。その原理は図1(B)に示されるものと同様である。

#### 【0102】

なお、上記の説明で、導体の仕事関数について議論した。もっとも簡単な仮定では、導体の仕事関数は半導体との界面で決定される値を用いればよいが、現実には界面は、化学的反応により半導体と導体の化合物が生成されたり、あるいは界面に電荷や異種元素がトラップされたりして複雑な物性を示すことが多い。10

#### 【0103】

また、例えば、半導体層と厚さが数nm以下の極めて薄い第1の導体層と、それに重なるある程度の厚みのある第2の導体層が積層している場合は、第1の導体層の仕事関数の影響度がかなり低下する。したがって、本発明を適用するに当たっては、界面から5nm離れた部分での各種材料の仕事関数が、本発明で好ましいとする条件を満たすように設計してもよい。

#### 【0104】

本発明は、キャリアとして、実質的に、電子あるいはホールの一方しか用いられない半導体材料(ドーピングによって導電型を制御できない半導体材料)において効果が顕著である。すなわち、電子あるいはホールの一方の移動度は、 $1 \text{ cm}^2 / \text{Vs}$ 以上であるのに対し、他方の移動度が $0.01 \text{ cm}^2 / \text{Vs}$ 以下であるとか、他方がキャリアとして存在しないとか、あるいは、他方の有効質量が自由電子の100倍以上であるとか、という場合において好ましい結果が得られる。20

#### 【図面の簡単な説明】

#### 【0105】

【図1】本発明のFETの一例および動作原理を示す図である。

【図2】従来のFETの例および動作を示す図である。

【図3】本発明のFETの例を示す図である。30

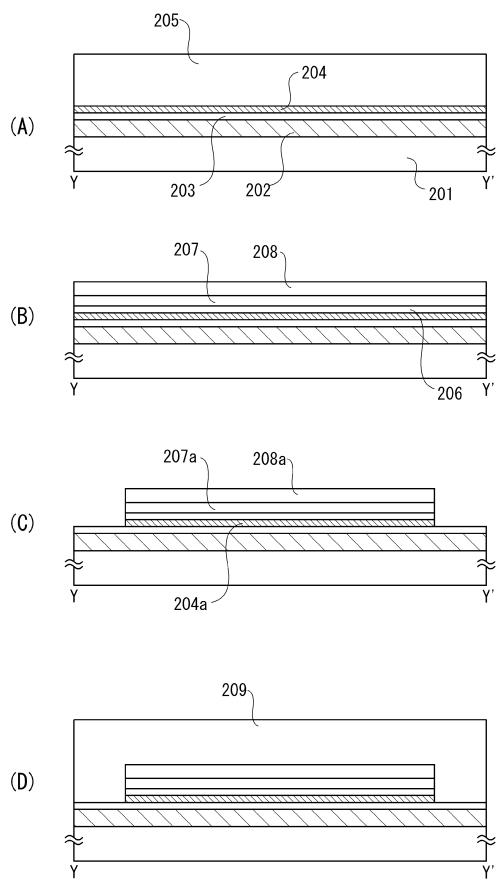

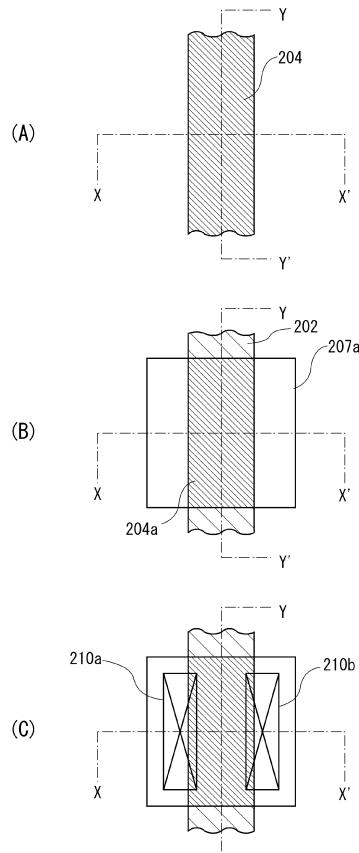

【図4】実施の形態1のFETの作製工程を示す図である。

【図5】実施の形態1のFETの作製工程を示す図である。

【図6】実施の形態1のFETの作製工程を示す図である。

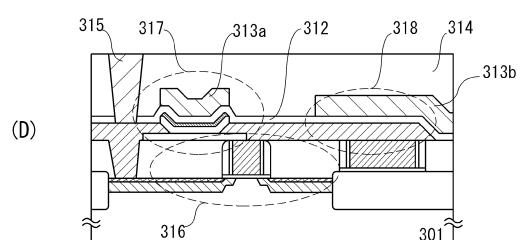

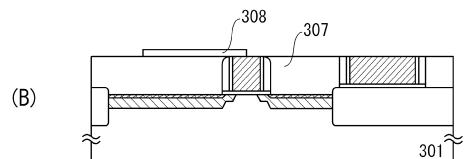

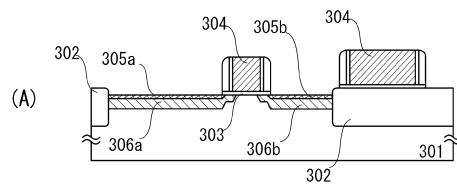

【図7】実施の形態2のFETを有する半導体装置の作製工程を示す図である。

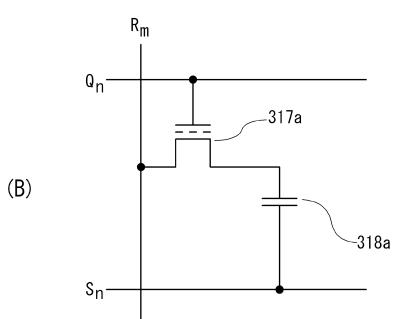

【図8】実施の形態2のFETを有する半導体装置の回路を示す図である。

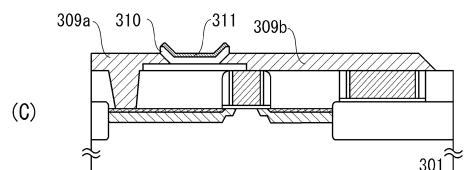

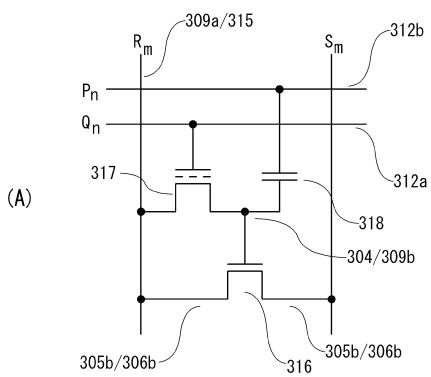

【図9】実施の形態3のFETを有する半導体装置の作製工程を示す図である。

#### 【発明を実施するための形態】

#### 【0106】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。ゆえに本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。40

#### 【0107】

また、以下の実施の形態のいずれかで開示された構造や条件等の項目は、他の実施の形態においても適宜、組み合わせることができる。なお、以下に説明する構成において、同様のものを指す符号は異なる図面間で共通の符号を用いて示し、同一部分又は同様な機能を有する部分の詳細な説明は省略することもある。

#### 【0108】

なお、本明細書で酸化物というのは、その物質(化合物を含む)に含まれる窒素、酸素、フッ素、硫黄、セレン、塩素、臭素、テルル、ヨウ素の占める割合(モル比)が全体の250

5 %以上で、かつ、以上の元素に対する酸素の割合(モル比)が70%以上のものをいう。

#### 【0109】

また、本明細書で金属元素とは、希ガス元素、水素、ホウ素、炭素、窒素、16族元素(酸素等)、17族元素(フッ素等)、シリコン、燐、ゲルマニウム、砒素、アンチモン以外の全ての元素のことである。

#### 【0110】

##### (実施の形態1)

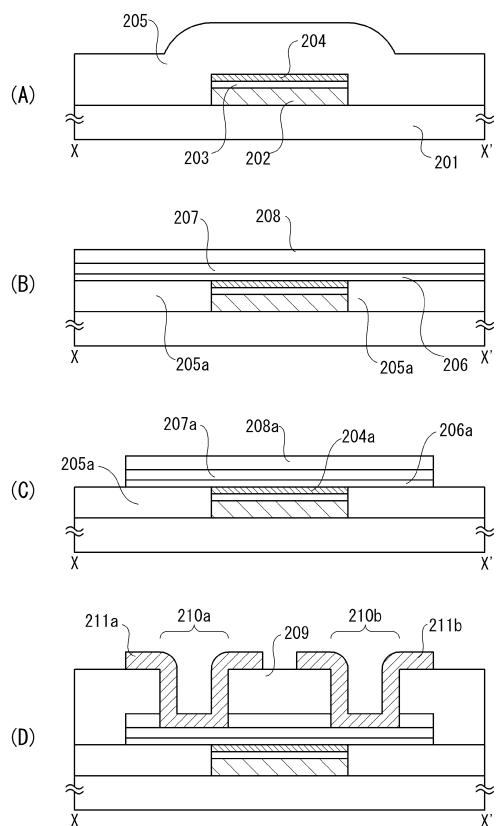

本実施の形態を図4乃至図6を用いて説明する。まず、基板201上に、導体膜と絶縁膜、導体膜を形成し、これを選択的にエッチングして、図4(A)に示すように、ゲート202、第1のゲート絶縁膜203、フローティング電極204を形成する。基板201としては、様々なものが用いられるが、その後の処理に耐えられる物性を有していることが必要である。また、その表面は絶縁性であることが好ましい。すなわち、基板201は絶縁体単独、あるいは絶縁体や導体や半導体の表面に絶縁層を形成したもの等であることことが好ましい。

10

#### 【0111】

絶縁体としては、各種ガラスやサファイヤ、石英、セラミックス等を用いることができる。導体としては、アルミニウム、銅、ステンレス鋼、銀等を用いることができる。半導体としては、シリコン、ゲルマニウム、炭化シリコン、窒化ガリウム等を用いることができる。本実施の形態では、基板201としてバリウム硼珪酸ガラスを用いる。

20

#### 【0112】

ゲート202の材料としては、各種の金属材料あるいは導電性酸化物等の導体を用いることができる。ゲート202はそのような材料単独で構成してもよいし、多層構造としてもよい。本実施の形態では、厚さ250nmのチタン/アルミニウム/チタンの3層構造の多層膜をスパッタリング法で形成したものを使う。

#### 【0113】

なお、従来は、ゲートの材料としては、仕事関数の大きいものを用いることがゼロ電流を低減する上で好ましかった。それは、仕事関数の大きい材料は、半導体層の電子を排除する力が強かったためであるが、本実施の形態ではフローティング電極204を帯電させて用いるため、ゲート202の仕事関数はほとんど影響しない。

30

#### 【0114】

仕事関数の高い材料は、高価であるとか、作製が困難であるとか、導電性がよくない等の問題があるものが多く、実用上の障害となるが、本実施の形態では、安価で作製も容易で、導電性も優れた材料を使用しても十分に低いゼロ電流が得られる。

#### 【0115】

第1のゲート絶縁膜203の材料としては、酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化ハフニウム、酸化ランタン、酸化イットリウム等を用いることができる。厚さは、その後の使用においてフローティング電極204から電荷が漏洩しない程度に厚いことが好ましい。本実施の形態では、第1のゲート絶縁膜203の材料として、CVD法により形成した厚さ30nm乃至100nmの酸化窒化シリコンを用いる。

40

#### 【0116】

フローティング電極204の材料としては、ゲート202と同様な各種導電性材料を用いることができる。一般に、仕事関数の大きな材料を用いることが好ましいが、それに限らない。なお、上述のとおり、仕事関数の大きな材料は導電性が十分でないものもあるが、フローティング電極204では限られた領域(具体的には、フローティング電極の一方の面から他方の面)を電子が移動するので、導電性はほとんど問題とならない。また、その厚さは5nm乃至100nm、好ましくは10nm乃至30nmとするよい。

#### 【0117】

さらに、図4(A)に示すように、ゲート202、第1のゲート絶縁膜203、フローティング電極204を覆って、厚い絶縁物205を形成する。絶縁物205は、段差被覆性

50

に優れた方法や材料で形成されることが好ましい。例えば、CVD法あるいはスピニコート法による酸化シリコン、窒化シリコン、酸化窒化シリコンなどを絶縁物205の材料として用いるとよい。また、その厚さは、少なくともゲート202、第1のゲート絶縁膜203、フローティング電極204の厚さの総和よりも大きいことが求められる。

#### 【0118】

図4(A)で断面が示されるFETを上方より見た様子を図6(A)に示す。図6では、絶縁物205は省略してある。図6(A)のX-X'の断面が図4(A)に示され、また、Y-Y'の断面が図5(A)に示される。

#### 【0119】

その後、例えば、化学的機械的研磨(CMP)法により、表面を平坦化させる。この研磨はフローティング電極204の表面が露出するまでおこなうとよい。なお、例えば、スピニコート法によって絶縁物205を形成した場合、既に、その表面が十分に平坦な平面であれば、CMP法を用いるまでもなく、通常のドライエッティング法で、フローティング電極204の表面が露出するまで絶縁物205をエッティングすればよい。かくして、ゲート202、第1のゲート絶縁膜203、フローティング電極204が絶縁物205aに埋め込まれた状態となる。

10

#### 【0120】

その後、図4(B)に示すように、第2のゲート絶縁膜206、半導体層207、保護絶縁層208を形成する。十分に平坦な平面上に形成するので、これらの成膜にはスパッタ法のような段差被覆性が十分でない方法を用いてもよい。また、これらの形成に際して、途中で基板201を大気中に触れされることなく、連続的におこなうことが求められる。これは、半導体層207が大気と接し、特に大気中の水蒸気が半導体層に吸収されることを防止する上で効果がある。

20

#### 【0121】

なお、第2のゲート絶縁膜206と保護絶縁層208は、第1のゲート絶縁膜203に用いられる材料を用いて形成すればよいが、その水素濃度が十分に低いことが望ましい。そのためには成膜時の雰囲気における水素および水素を含む化合物(水等)の濃度を十分に低くすることが好ましい。

#### 【0122】

第2のゲート絶縁膜206の厚さは、その後の工程において、フローティング電極204に電荷を蓄積するのに十分に薄く、かつ、その後の使用においてフローティング電極204から電荷が漏洩しない程度に厚いことが好ましい。本実施の形態では、第2のゲート絶縁膜206を厚さ10nm乃至20nmとする。

30

#### 【0123】

保護絶縁層208の厚さは、量産性に問題がない限り、厚い方が好ましい。かつ、保護絶縁層には過剰な酸素が存在することが好ましい。本実施の形態では、保護絶縁層208を厚さ50nm乃至100nmとする。

#### 【0124】

半導体層207の材料としてはInあるいはGaを有する酸化物半導体を用いる。酸化物半導体としては、上記以外にも各種のものが用いられる。本実施の形態では、InとGaとZnが等しく含まれる酸化物ターゲットを用いたスパッタリング法によって、厚さ5nm乃至20nmのIn-Ga-Zn系酸化物膜を形成する。半導体層207もその水素濃度が十分に低いことが望ましい。そのためには成膜時の雰囲気における水素および水素を含む化合物(水蒸気等)の濃度を十分に低くすることが好ましい。図5(B)には、図4(B)に相当する断面のFETのY-Y'の断面を示す。

40

#### 【0125】

その後、フローティング電極204、第2のゲート絶縁膜206、半導体層207、保護絶縁層208を選択的にエッティングする。エッティングの結果、それぞれ、形状が変化し、フローティング電極204a、第2のゲート絶縁膜206a、半導体層207a、保護絶縁層208aとなる。このときのFETの上面図を図6(B)に示す。また、X-X'の

50

断面を図4( C )に、Y-Y'の断面を図5( C )にそれぞれ示す。なお、図6では第1のゲート絶縁膜203、絶縁物205a、第2のゲート絶縁膜206aと保護絶縁層208aは省略してある。

#### 【0126】

このエッティングにより、半導体層207aの領域が確定するが、これは段階的におこなうことが好ましい。半導体層207aとする部分にはレジストマスクを形成し、エッティングされないようにする。最初に保護絶縁層208、半導体層207、第2のゲート絶縁膜206をエッティングする。このエッティングは連続的におこなってもよい。このエッティングにより、第2のゲート絶縁膜206a、半導体層207a、保護絶縁層208aが形成され、第2のゲート絶縁膜206aと保護絶縁層208aは、半導体層207aと、概略同一形状となる。また、フローティング電極204の一部と絶縁物205aの一部が露出する。

10

#### 【0127】

次に、フローティング電極204のエッティングをおこなう。このエッティングは、フローティング電極204が優先的にエッティングされる条件でおこなう。その結果、絶縁物205aはほとんどエッティングされない状態となる。このエッティングによりフローティング電極204がエッティングされ、半導体層207aの下にのみフローティング電極204aとして残る。

#### 【0128】

図6( B )から明らかなように、フローティング電極204aは半導体層207aの形状に合わせて、すなわち、自己整合的に形成され、半導体層207aのチャネル幅方向の長さと概略同じ長さを有し、チャネル幅方向の一端から他端までと重なる構造となる。このような構造は、特に微細化という点で効果が大きい。

20

#### 【0129】

上記のエッティング工程の後、もしくは、それ以前で半導体層207を形成後において適切な熱処理を1回あるいは複数回おこなうとよい。これは、半導体層207あるいは207a中の水素濃度や酸素欠損を低減させるためである。

#### 【0130】

その後、層間絶縁物209を形成する(図4( D )および図5( D )参照)。層間絶縁物209は、単層もしくは多層の絶縁物よりなり、スパッタ法、CVD法、スピンドル法等による酸化シリコン、窒化シリコン、酸化窒化シリコン等の無機絶縁物やポリイミド等の有機絶縁物を用いて形成することができる。

30

#### 【0131】

例えば、最初にスパッタ法により、水素濃度の極めて低い酸化シリコン膜を50nm乃至200nm形成し、その後、スピンドル法で厚さ500nm乃至1μmのポリイミド膜を形成してもよい。スピンドル法により形成すると、平坦な表面を有するので好ましい。

#### 【0132】

そして、図4( D )および図6( C )に示すように、層間絶縁物209にコンタクトホール210aおよび210bを形成する。なお、図6( C )には層間絶縁物209は示されていない。そして、金属等の導体膜を形成し、これを選択的にエッティングして、ソース電極211a、ドレイン電極211bとする。ソース電極211a、ドレイン電極211bに用いる材料としては、各種金属材料あるいは導電性酸化物等が挙げられる。以上で、フローティング電極204aを有するFETが完成する。

40

#### 【0133】

##### (実施の形態2)

本実施の形態では、シリコンによるFET上に別の半導体層を有し、かつ、フローティング電極を有するFETを形成する半導体回路の作製方法について図7( A )乃至( D )を用いて説明する。まず、公知のシリコンMOSFET作製技術により、シリコン基板301に、素子分離領域302を形成し、ゲート絶縁膜303、ゲート304、ソース306

50

a、およびドレイン306bを有するシリコンFETを形成する。ゲート304には、図に示すようなサイドウォールを設けてもよい。また、ゲート304は素子分離領域上にも延在する。さらに、ソース306a、およびドレイン306bの表面には、導電性を高めるためのシリサイド層305a、305bを設けてもよい(図7(A)参照)。

#### 【0134】

その後、絶縁物を形成し、その表面をCMP法で研磨することで、表面が平坦な絶縁物307を得る。CMP法はゲート304の表面が露出するまでおこなうとよい。さらに、酸化物半導体膜を形成し、これをエッチングして、必要な形状(例えば、島状)の酸化物半導体層308を形成する(図7(B)参照)。

#### 【0135】

そして、ソース306aに達するコンタクトホールを形成して、導体膜を堆積し、その表面を平坦化した後、選択的にエッチングすることで、第1の電極309a、第2の電極309bを形成する。さらに、絶縁膜と導体膜を堆積し、これをエッチングすることで、第1のゲート絶縁層310とフローティング電極311を形成する(図7(C)参照)。ここで、本実施の形態の第1のゲート絶縁層310は、実施の形態1の第2のゲート絶縁膜206aに相当することに注意が必要である。

10

#### 【0136】

その後、第2のゲート絶縁層312、導体膜を堆積し、導体膜を選択的にエッチングして、配線313aと配線313bを形成する。配線313aは酸化物半導体を半導体層とするFET317のゲートをも兼ねる。また、配線313bは第2の電極309bとの間で、第2のゲート絶縁層312を誘電体とする容量素子318を形成する(図7(D)参照)。

20

#### 【0137】

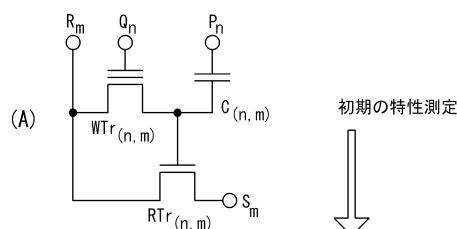

さらに、層間絶縁物314を形成し、これにコンタクトホールを形成し、第1の電極309aに達するコンタクトプラグ315を埋め込む。さらに、コンタクトプラグ315に接続する配線を設けてもよい。以上で、シリコンMOSFET316、酸化物半導体のFET317、容量素子318を有する半導体回路が形成される(図7(D)参照)。

#### 【0138】

上記のような半導体回路は図8(A)に示されるようなメモリ素子に用いることができる。このメモリ素子は、2つのFET316と317と1つの容量素子318よりなる。図に示されているのは第n行第m列のメモリ素子である。

30

#### 【0139】

メモリ素子にデータを書き込む際には書き込みワード線Q<sub>n</sub>の電位をハイとすることで、FET317をオンとし、その際にビット線R<sub>m</sub>にデータを与えると、データに応じた電荷がFET317を通過し、容量素子318に蓄積される。

#### 【0140】

メモリ素子からデータを読み出す際には、読み出しワード線P<sub>n</sub>の電位を適切な値とすることで、容量素子318に蓄積された電荷の量に応じて、FET316がオンとなったりオフとなったりするので、ビット線R<sub>m</sub>の電位とソース線S<sub>m</sub>の電位と比較することでデータを読み出せる。

40

#### 【0141】

このように、読み出しに際して、データが消滅することはない。そのためFET317のゼロ電流が十分に低ければ、半永久的にデータを保存することができる。ゼロ電流を十分に低くするには、フローティング電極311を負に帯電させる。このことにより、FET317のゼロ電流を $1 \times 10^{-21} A$ 以下、好ましくは $1 \times 10^{-24} A$ 以下とることができ、極めて長期にわたりデータを保持できる。

#### 【0142】

図8(A)に示すメモリ素子では、FET316によってデータを增幅して読み出すため、容量素子318の容量を、 $1 \times 10^{-16} F$ 以下、好ましくは $1 \times 10^{-17} F$ 以下とすることもでき、容量素子318の構造を単純にできること、およびその面積を縮小でき

50

るという特徴を有する。これらのことから、メモリ素子も小さくでき、高集積化が可能である。

#### 【0143】

一方で、そのような容量の小さな容量素子318を用いる場合には、FET317のゼロ電流が大きな場合には、データが瞬時に失われてしまう。上述のように、FET317のゼロ電流を $1 \times 10^{-2.1} A$ とすると、容量素子318の容量が $1 \times 10^{-1.6} F$ の場合には1日、 $1 \times 10^{-1.7} F$ の場合には3時間しかデータを保持できないが、ゼロ電流を $1 \times 10^{-2.4} A$ とすると、容量素子318の容量が $1 \times 10^{-1.6} F$ の場合には3年、 $1 \times 10^{-1.7} F$ の場合でも100余日、データを保持できる。さらに、ゼロ電流を $1 \times 10^{-2.6} A$ とすると、容量素子318の容量が $1 \times 10^{-1.7} F$ の場合でも31年もの長期にわたりデータを保持できる。10

#### 【0144】

一方、図7に示した作製工程を援用して、図8(B)に示すような、1つのFET317aと1つの容量素子318aよりなるDRAM型メモリ素子を形成してもよい。このメモリ素子では、容量素子318aの容量は、ノイズを防止する観点から $1 \times 10^{-1.5} F$ 以上が必要であり、そのために、スタック型の容量を用いるとよい。

#### 【0145】

データの書き込みはワード線 $Q_n$ にハイの信号を与えて、FET317aをオンにしたときに、ビット線 $R_m$ にデータを印加することにより容量素子318aに電荷を蓄積させておこない、読み出しへワード線 $Q_n$ にハイの信号を与えて、FET317aをオンにしたときに、容量素子318aよりビット線 $R_m$ に放出される電荷量を測定することによりおこなう。なお、ソース線 $S_n$ は通常は一定の電位に保持されるが、ビット線 $R_m$ あるいはワード線 $Q_n$ に同期する信号を与えてよい。20

#### 【0146】

当然のことながら、FET317aのゼロ電流が小さいほど、容量素子318aに長期に電荷を蓄積できるので、データを長期にわたり保持できる。例えば、容量素子318aの容量が $1 \times 10^{-1.5} F$ の場合には、FET317aのゼロ電流を $1 \times 10^{-2.1} A$ とすると11日、ゼロ電流を $1 \times 10^{-2.4} A$ 以下とすると31年間以上データを保持できる。後者の場合は実質的に半永久的にデータを保存することができる。

#### 【0147】

##### (実施の形態3)

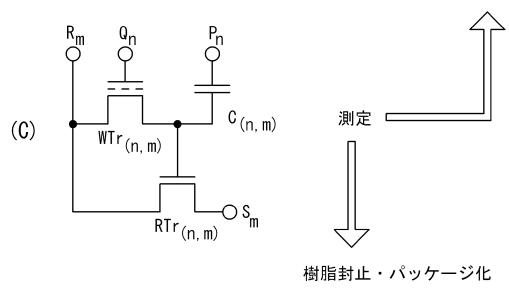

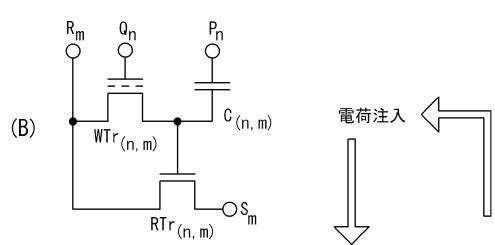

実施の形態1あるいは2ではFETの作製方法について説明したが、本実施の形態では、フローティング電極に電荷を蓄積する方法について図9を用いて説明する。本実施の形態では、図8(A)に示されるようなメモリ素子に電荷を蓄積する方法について説明する。なお、メモリ素子の $RTr(n, m)$ 、 $WTr(n, m)$ 、 $C(n, m)$ は、それぞれ、図8(A)のFET316、FET317、容量素子318に相当する。

#### 【0148】

##### <図9(A)>

まず、メモリ素子を含む半導体回路が完成したら、メモリ素子の初期特性を測定する。この段階では、 $WTr(n, m)$ のフローティング電極は帯電していない。ここで、メモリ素子として機能するかどうかを判定し、かつ、メモリ素子の特性を記録する。40

#### 【0149】

##### <図9(B)>

この段階では、 $WTr(n, m)$ のフローティング電極に電荷を蓄積する。 $WTr(n, m)$ のフローティング電極に蓄積する電荷の量は、 $WTr(n, m)$ のゲートとソース電極(あるいはドレイン電極)の電位差で制御できる。具体的には、書き込みワード線 $Q_n$ とビット線 $R_m$ との間の電位差を制御することで、メモリ素子の $WTr(n, m)$ のフローティング電極に蓄積される電荷を制御できる。先の測定結果をもとに、メモリ素子の $WTr(n, m)$ のフローティング電極に適切な量の電荷を蓄積する。なお、電荷の蓄積には十分な時間をかけておこなうことができ、そのため、蓄積される電荷量の誤差を十分に50

小さくできる。

**【0150】**

<図9(C)>

この段階で再度、メモリ素子の特性を測定する。ここで、必要な量のメモリ素子で十分な特性が得られていれば、半導体回路を樹脂等で封止し、パッケージ化する。しかしながら、必要な量のメモリ素子で十分な特性が得られていない場合には、この測定データを元に再度、フローティング電極に適切な量の電荷を蓄積する工程へ戻る。

**【0151】**

このようなサイクルを繰り返すことで、良品率の高い半導体回路および半導体装置（メモリ装置）を得ることができる。上記では、高い電圧を用いて電荷を蓄積したが、その際に用いる電圧は、外部の回路より供給すればよい。

10

**【0152】**

(実施の形態4)

上記実施の形態1乃至実施の形態3で示した半導体装置は、半導体メモリをはじめ、さまざまな電子機器に用いることができる。例えば、テレビジョン、パーソナルコンピュータ、携帯電話等の通信機器、電子手帳、携帯音楽プレーヤ等である。

**【符号の説明】**

**【0153】**

101 半導体層

20

102 フローティング電極

103 a ソース電極

103 b ドレイン電極

104 絶縁物

105 ゲート

111  $I_D - V_G$  曲線

112  $I_D - V_G$  曲線

113  $I_D - V_G$  曲線

114  $I_D - V_G$  曲線

115  $I_D - V_G$  曲線

116  $I_D - V_G$  曲線

30

201 基板

202 ゲート

203 第1のゲート絶縁膜

204 フローティング電極

204 a フローティング電極

205 絶縁物

205 a 絶縁物

206 第2のゲート絶縁膜

206 a 第2のゲート絶縁膜

207 半導体層

40

207 a 半導体層

208 保護絶縁層

208 a 保護絶縁層

209 層間絶縁物

210 a コンタクトホール

210 b コンタクトホール

211 a ソース電極

211 b ドレイン電極

301 基板

302 素子分離領域

50

|         |           |    |

|---------|-----------|----|

| 3 0 3   | ゲート絶縁膜    |    |

| 3 0 4   | ゲート       |    |

| 3 0 5 a | シリサイド層    |    |

| 3 0 5 b | シリサイド層    |    |

| 3 0 6 a | ソース       |    |

| 3 0 6 b | ドレイン      |    |

| 3 0 7   | 絶縁物       |    |

| 3 0 8   | 半導体層      |    |

| 3 0 9 a | 第1の電極     | 10 |

| 3 0 9 b | 第2の電極     |    |

| 3 1 0   | 第1のゲート絶縁層 |    |

| 3 1 1   | フローティング電極 |    |

| 3 1 2   | 第2のゲート絶縁層 |    |

| 3 1 3 a | 配線        |    |

| 3 1 3 b | 配線        |    |

| 3 1 4   | 層間絶縁物     |    |

| 3 1 5   | コンタクトプラグ  |    |

| 3 1 6   | FET       |    |

| 3 1 7   | FET       |    |

| 3 1 7 a | FET       | 20 |

| 3 1 8   | 容量素子      |    |

| 3 1 8 a | 容量素子      |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

樹脂封止・パッケージ化

---

フロントページの続き

| (51)Int.Cl.             | F I               |

|-------------------------|-------------------|

| H 01L 21/8242 (2006.01) | H 01L 27/088 H    |

| H 01L 27/108 (2006.01)  | H 01L 27/108 321  |

| H 01L 29/788 (2006.01)  | H 01L 27/108 671Z |

| H 01L 29/792 (2006.01)  | H 01L 29/78 371   |

| H 01L 27/115 (2017.01)  | H 01L 27/115      |

| H 01L 27/1156 (2017.01) | H 01L 27/1156     |

(56)参考文献 特開2012-074692(JP,A)

特開平06-085279(JP,A)

特開平08-139197(JP,A)

特開平03-214779(JP,A)

特開平08-023039(JP,A)

特開2009-253159(JP,A)

特開2007-250983(JP,A)

特開2010-186860(JP,A)

国際公開第2010/046997(WO,A1)

米国特許第05646428(US,A)

## (58)調査した分野(Int.Cl., DB名)

H 01L 29 / 786

H 01L 21 / 336

H 01L 27 / 06

H 01L 27 / 088

H 01L 27 / 108

H 01L 27 / 115

H 01L 27 / 1156