# **PCT**

# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

# INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification <sup>3</sup>:

A1

(11) International Publication Number: WO 81/01064

(43) International Publication Date: 16 April 1981 (16.04.81)

(21) International Application Number: PCT/GB80/00161

(22) International Filing Date: 9 October 1980 (09.10.80)

(31) Priority Application Number: 7935042

(32) Priority Date: 9 October 1979 (09.10.79)

(33) Priority Country: GB

(71) Applicant (for all designated States except US): BUR-ROUGHS CORPORATION [US/US]; Burroughs Place, Detroit, MI 48232 (US).

(72) Inventors; and

(75) Inventors/Applicants (for US only): ROBERTSON, Michael, Andrew [GB/GB]; 34/35 West Craigs Crescent, Edinburgh, (GB). WARREN, Robert, Geoffey [GB/GB]; 36 Dorchester Avenue, Kelvindale, Glasgow, (GB).

- (74) Agent: G. F. REDFERN & CO.; Marlborough Lodge, 14 Farncombe Road, Worthing, West Sussey, BN11 2BT (GB).

- (81) Designated States: BR, DE (European patent), FR (European patent), GB (European patent), JP, NL (European patent), US.

#### **Published**

With international search report

(54) Title: IMPROVEMENTS IN OR RELATING TO DATA COMMUNICATIONS

### (57) Abstract

A data communications controller for use intermediately between a data processor and a data communications link such as a modem driven landline, relieves the data processor of time consuming supervisory and data preparation tasks normally associated with the use of a data link by means of a block loadable transmit queue (24), an automatic CRC generator (26), an automatic time-fill generator (28) and parity generator (32), a block unloadable receive queue (44), an automatic character load translator (42), an automatic character monitor (40) and a received serial bit queue (34) in conjunction with a byte synchronising detector (36), the operation or non-operation of each of the above elements and, if operational, the manner of that operation being selectable by the data processor.

# FOR THE PURPOSES OF INFORMATION ONLY

$\label{lem:codes} \textbf{Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.}$

| AT | Austria                      | KP | Democratic People's Republic of Korea |

|----|------------------------------|----|---------------------------------------|

| ΑŬ | Australia                    | LI | Liechtenstein                         |

| BR | Brazil                       | LU | Luxembourg                            |

| CF | Central African Republic     | MC | Monaco                                |

| CG | Congo                        | MG | Madagascar                            |

| CH | Switzerland                  | MW | Malaŵi                                |

| CM | Cameroon                     | NL | Netherlands                           |

| DE | Germany, Federal Republic of | NO | Norway                                |

| DK | Denmark                      | RO | Romania                               |

| FI | Finland                      | SE | Sweden                                |

| FR | France                       | SN | Senegal                               |

| GA | Gabon                        | SU | Soviet Union                          |

| GB | United Kingdom               | TD | Chad                                  |

| HU | Hungary                      | TG | Togo                                  |

| JP | Japan                        | US | United States of America              |

|    |                              |    |                                       |

- 1 -

## "IMPROVEMENTS IN OR RELATING TO DATA COMMUNICATIONS"

The present invention relates to a communications controller for data storage and processing intermediately between a data-processing host and a data communications link, and it is an object of the present invention to provide a controller having flexibility of operation and requiring minimal host supervision.

It is well known in the art to provide data communications between mutually remote data processing systems via

modulated carrier landline links, radio links or direct wire connection, using any one of a plurality of well known codes and of well known protocols.

It is usual that a data link comprises a modulator/

demodulator (hereinafter referred to as a modem) at either end

15 each under the control of their respective host. The host

originating a message provides that message, pre-coded

and complete with error-checking characters, bit-by-bit to

the transmitting modem. The coding of the message, the

insertion of error-checking characters, and the servicing of

20 the modem once for every transmitted bit impose a taxing

burden on the host, taking up much operating time that would

more profitably be spent on other tasks and ruining the

continuity of the execution of other tasks by frequent

interruptions. In the extreme case, small or slow hosts

25 may possess insufficient processing capacity or speed of

execution to fulfil the various coding, error character

generation, and modem servicing requirements between successive demands by the modem for a fresh transmission bit, leading not only to a complete abandonment of alternative task execution but also to a failure in the data on the data link itself.

A host in receipt of a data communications message receives that message bit-by-bit from the modem and is subject to bit-by-bit interruption, decoding and error checking character verification requirements. The receiving host is thereby no better off than the transmitting host.

An additional disadvantage in current data communications methods is the large amount of manpower, time and memory space consuming software required to be written for each host, especially in those hosts which may be asked to communicate using a plurality of protocols and codes.

A host is rarely linked directly to a modem. An interface of some kind is usually provided therebetween.

Current interfaces are generally code and protocol specific.

As it is increasingly the case that a processor is expected to communicate with more than one remote system, and that different systems observe different protocols and codes, the number and consequent expense of the required plurality of interfaces increases.

In certain so-called synchronous modes of transmission

25 it is a requirement on the receiving host that it knows in

advance the beginning bits of each byte. It is a deficiency

15

20

25

in the current art that should that information be lost there is no means of recovery from that loss.

It is the current trend that a plurality of processors of small size and/or data terminals of limited processing capacity are provided together on one site, such as a factory, and are required to communicate not only with one another, but also with remote equipment at other sites such as a head office or another factory. It is generally the case that almost the entire operation of a supervisory processor is 10 required to be sacrificed in order to achieve this aim.

It is therefore desirable to provide means whereby a host may conduct data communications with any one of a plurality of remote or local systems under conditions of minimal processing requirements. It is further desirable that means be provided for automatic byte-synchronisation of synchronously received, plural-bit characters.

According to one aspect the present invention consists in a data communications controller, for use intermediately between a data processor and a data communications link, characterised by said controller being operable, in response to commands from said processor, to receive data characters from said processor, and to encode and supply supplementary characters to said data characters for serial transmission by said communications link in any selectable one out of a plurality of transmission modes and according to any selectable one out of a plurality of transmission protocols.

WO 81/01064 PCT/GB80/00161

According to another aspect, the present invention consists in a data communications controller, for use intermediately between a data processor and a data communications link, characterised by said controller being operable, in response to commands from said processor, to receive serial binary characters from said communications link, to decode said serial binary characters, to check the validity of and delete supplementary characters contained therein, and to present the result of said operations as received data to said processor.

5

10

20

25

According to another aspect, the present invention consists in a controller, for use intermediately between a data processor and a data communications link, comprising; a plural character data store for receiving a serial succession 15 of characters for transmission from said data processor, and for yielding up said stored characters, to said data link, in the same serial order as that of their receipt, and also comprising a monitor for monitoring the number of characters stored in said data store which have not yet been yielded up to said data link and for providing indication of said number to said data processor.

According to another aspect the present invention consists in a controller, for use intermediately between a data processor and a serial data link, comprising, a first-in first-out register for receiving a succession of binary digits, representative of a plurality of plural binary digit

25

characters, from said data link and operable to yield up said succession of binary digits to be coupled to said data processor.

According to another aspect, the present invention consists in a controller, for use intermediately between a data processor and a serial data link, comprising a first-in first-out register for receiving a succession of binary digits from said data link and operable to yield up said succession of binary digits to be coupled to said data processor, and a monitor for monitoring the output of said register and for 10 providing indication when a predetermined serial pattern of binary digits is presented at the output of said shift register.

According to another aspect the present invention consists in a controller, for use intermediately between a 15 data processor and a data communications link comprising a store for receiving and storing a plurality of plural binary digit data characters derived from said data communications link and operable to yield up for coupling to said data processor, said plurality of characters in the same serial 20 order as that of their receipt from said data link and a monitor for monitoring the number of characters in said store which have not yet been so yielded up and for providing indication of said number to said data processor.

According to another aspect, the present invention consists in a controller, for use intermediately between a

WO 81/01064 PCT/GB80/00161

6 -

data processor and a data link comprising a monitor for monitoring data characters received from said data link and for providing indication when any one out of a plurality of predetermined characters is so received.

5

According to another aspect the present invention consists in a controller, for use intermediately between a data processor and a data communication link comprising a translator for monitoring data characters received from said data link and for substituting, for coupling to said data 10 processor, a predetermined one out of a plurality of predetermined substitution characters whenever a corresponding one out of a corresponding plurality of predetermined data characters is so received.

According to another aspect the present invention 15 consists in a controller, for use intermediately between a data processor and a data communication link comprising a store for receiving and storing a serial plurality of mixed data characters for transmission by said data link and command characters not for transmission by said data link, operable to yield up said mixed characters in the same serial order as 20 that of their receipt, and a separator for separating said data characters from said command characters as they are yielded up by said store.

According to another aspect, the present invention consists in a controller, for use intermediately between a data processor and a data communications link comprising a

cyclic redundancy check generator for supplying cyclic redundancy check characters to the data, supplied by said processor to said controller for transmission.

According to another aspect, the present invention

5 consists in a controller, for use intermediately between a

data processor and a data communications link comprising a

cyclic redundancy character checker for checking and deleting

cyclic redundancy check characters received from said data

Link.

According to another aspect the present invention consists in any of the above aspects taken singly or in combination.

WO 81/01064 PCT/GB80/00161

In a preferred embodiment the controller comprises a first-in first-out serial transmission queue for accepting a burst of one or more parallel bit words from the processor, storing a plurality of said words and delivering up said words in the same serial order as that of their acceptance for 5 transmission purposes. The transmission queue preferably comprises a monitor for monitoring the state of fulness of the queue and for providing indication of said state of fulness to said processor. The transmission queue is preferably oper-10 able to store commands, intermixed randomly with said words, for execution by the controller as they are delivered up from the transmission queue, in which case the transmission queue preferably comprises a separator for separating commands from data for transmission.

The controller preferably comprises a cyclic redundancy check generator for calculating and adding cyclic redundancy check characters to data for transmission. The generator preferably operates on the parallel bit words emerging from the transmit queue. The polynomial used by the generator is 20 preferably selectable by the processor.

15

The controller preferably comprises a parallel-to-serial converter for converting parallel-bit data words for transmission into an equivalent serial data stream suitable for transmission over a data link. The operation of the parallel-25 to serial converter is preferably selectable, by the processor, as to word length.

WO 81/01064 PCT/GB80/00161

- 9 -

The controller preferably comprises a parity bit generator for adding parity bits to the succession of transmission data characters. The parity bit generator is preferably selectably operable, and when operational, selectable as to whether it inserts odd or even parity bits.

5

10

15

20

25

The controller preferably comprises a serial reception first-in first-out queue for accepting a plurality of serial bits, representative of received characters and for yielding them up, in the same serial order as that of their acceptance, to be coupled as received data to the processor. The serial reception queue preferably comprises a monitor for monitoring the contents of the queue and for providing indication to the processor when a predetermined plural-bit processor selected character is about to emerge therefrom. The serial reception queue also preferably comprises an indicator for indicating to the processor the state of fulness of the queue.

The controller preferably comprises a serial-toparallel converter for converting the serial bit stream of

characters from the data link into parallel words of processor

selectable length. The serial-to-parallel converter is

preferably responsive to the output of the monitor of the

receive serial queue to control the framing of its own output.

The controller preferably comprises a second CRC generator for checking and deleting cyclic redundancy check characters from the stream of received data from the data link, and for indicating to the processor when an error is detected.

The polynomial used by the second CRC generator is preferably processor selectable. The second CRC generator is preferably incorporated as all or part of the cyclic redundancy check generator for transmission characters.

The controller preferably comprises a search monitor for comparing incoming, received characters with a processor-selected list of predetermined characters and for providing indication when a match is found.

The controller preferably comprises a translator for changing any incoming received data word, if it matches with any member of a list of processor selected words, into a corresponding processor-selected substitution word.

The controller preferably comprises a receive first-in first-out queue for accepting and storing a plurality of

15 parallel binary digit words and for delivering up said words in the same serial order as that of their acceptance, in bursts of one or more successive words, to the processor, as received and processed data. The receive queue preferably comprises a monitor for indicating to the processor the state of fulness of the queue.

The controller is preferably coupled to the processor by a bus comprising a data bus for data and command characters and a control bus for indicating the nature of the character on the data bus.

The controller preferably comprises external equipment control means whereby the processor may send digital

WO 81/01064 PCT/GB80/00161

- 11 -

instructions to and receive digital feedback from external equipment, preferably an automatic dialling unit.

The controller is preferably implemented using plural LS1 integrated circuits, preferably three, in which case the integrated circuits are coupled together for character transfer therebetween and to the processor by the data bus already described. The control bus preferably is applied to only one of the integrated circuits, in which case that one integrated circuit controls access of the others to the data bus by supplying, to the others, a modified control bus under the control of that one integrated circuit.

5

10

15

20

25

The controller preferably comprises one or more processor selectable period timers which are operable to start their operation in response to a command from the processor and to indicate to the processor the termination of their individual timing operations.

The controller preferably comprises a processor selectable period data timer which starts its operation on receipt of each binary digit from the data link and indicates to the processor if another binary digit is not so received within the selected time.

The processor preferably controls the controller by preloading control characters into selectable control registers which are selectably readable by the processor.

The controller preferably signals indications and internal conditions back to the processor by controlling flag signals

WO 81/01064 PCT/GB80/00161

- 12 -

in one or more, processor readable status registers.

All signal processing elements are preferably testable by the processor.

The controller preferably operates at a processor selectable baud rate.

5

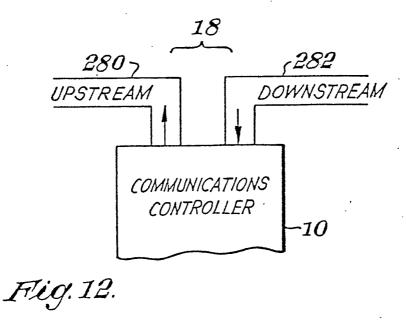

The output coupling of the controller preferably comprises two or more selectably controller usable buses any one of which can couple the controller to a data link or be used for communications with another controller.

The invention is further described, by way of an example, by the following description in conjunction with the appended drawings, in which:-

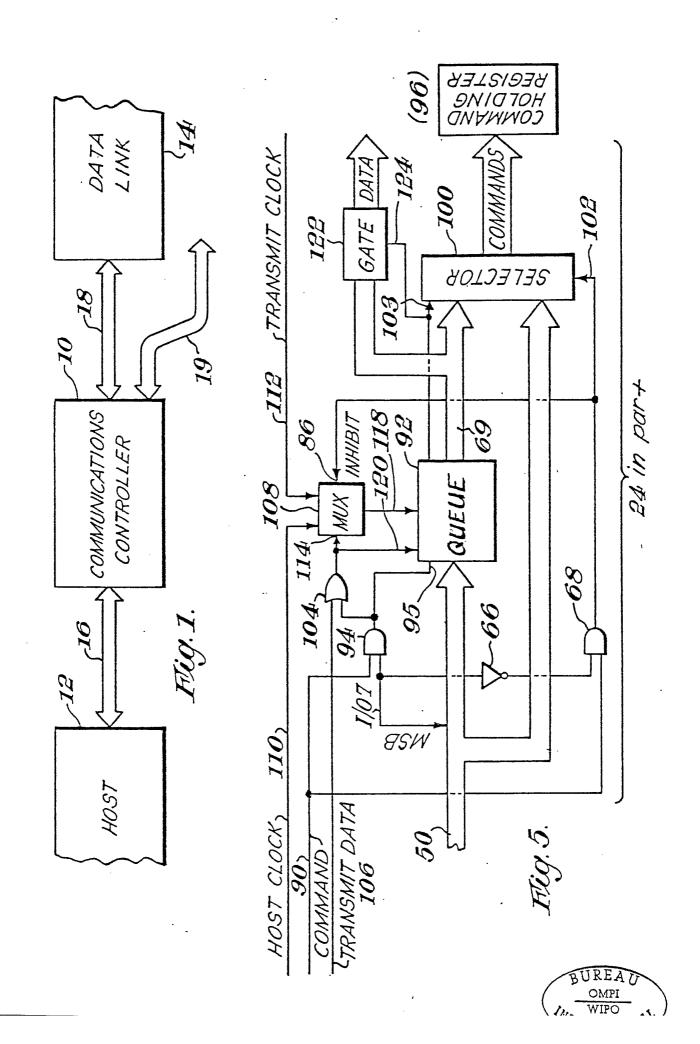

Figure 1 shows the data communications controller coupled intermediately between a host system and a data link;

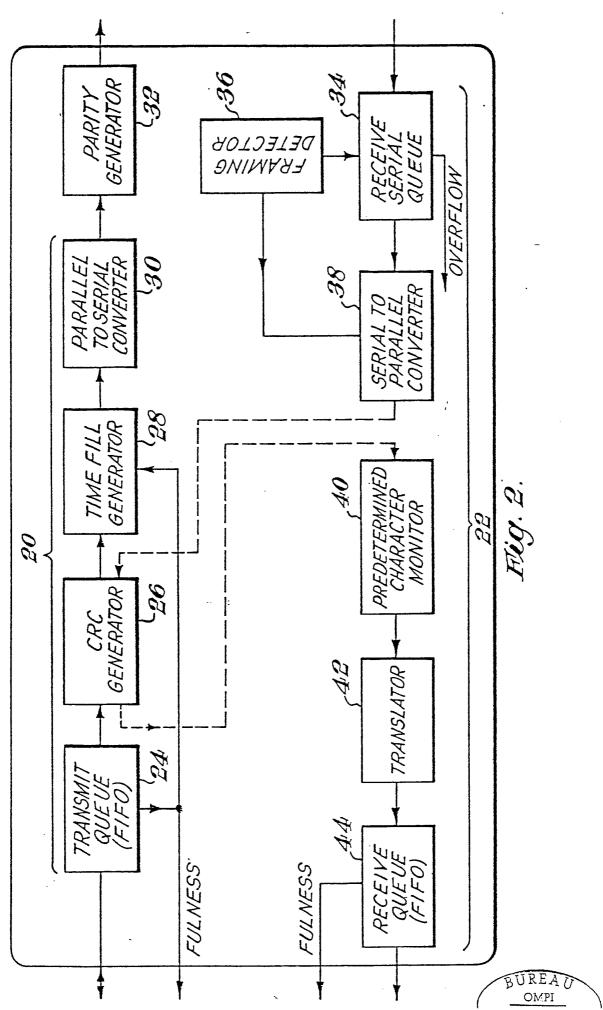

15 Figure 2 shows the principal data processing elements in the controller;

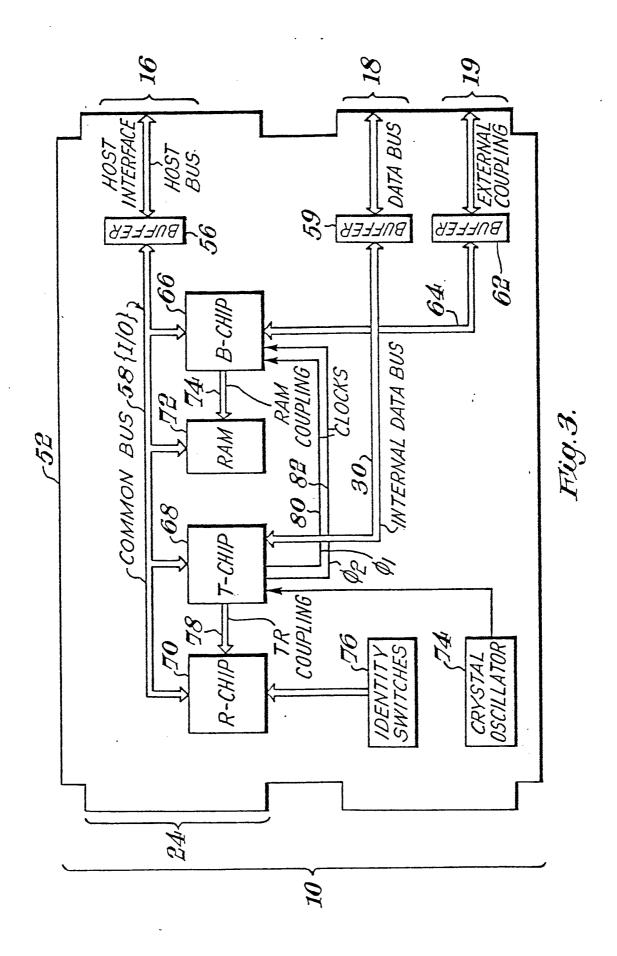

Figure 3 shows the physical implementations and element intercouplings of the controller;

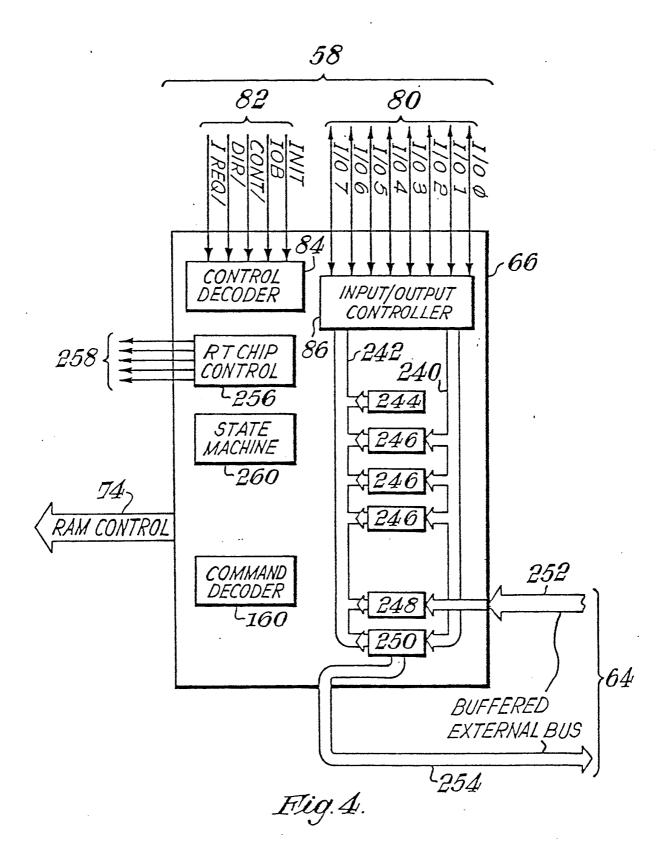

Figure 4 shows a schematic representation of the 20 control elements within the B-chip of figure 3;

Figure 5 shows a first part of the transmit queue of figure 2;

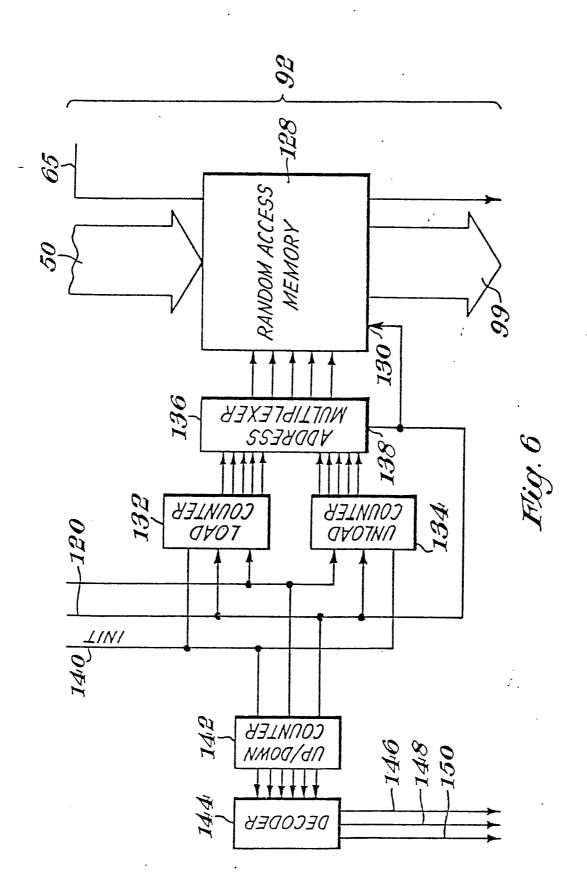

Figure 6 shows the serial queue of figure 5;

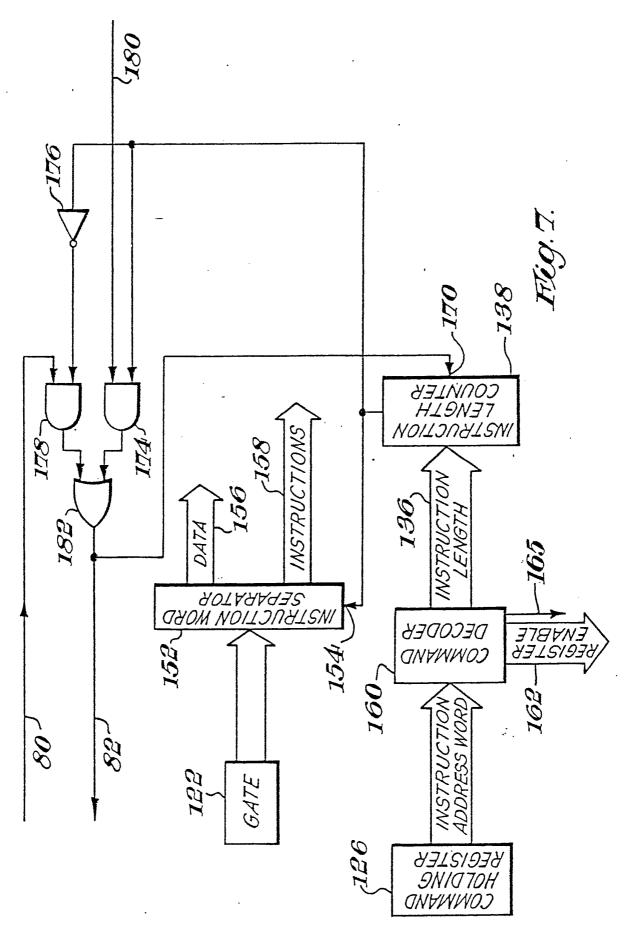

Figure 7 shows a second and final part of the transmit queue of figure 2;

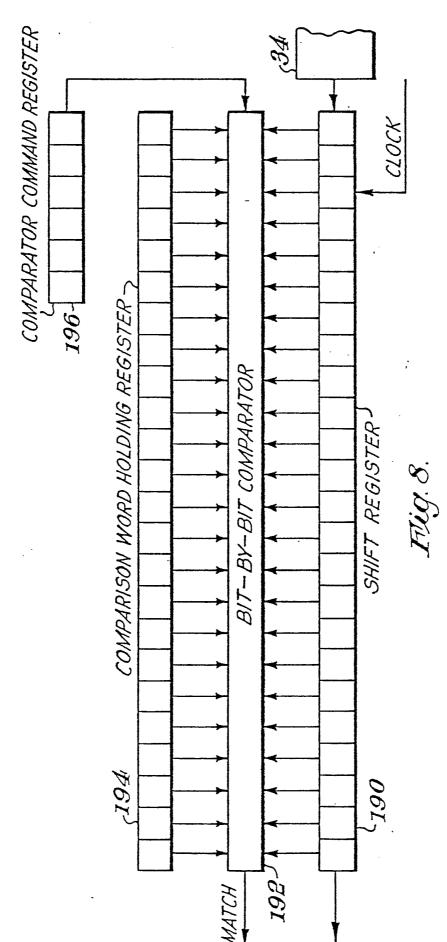

Figure 8 shows the framing monitor of figure 2;

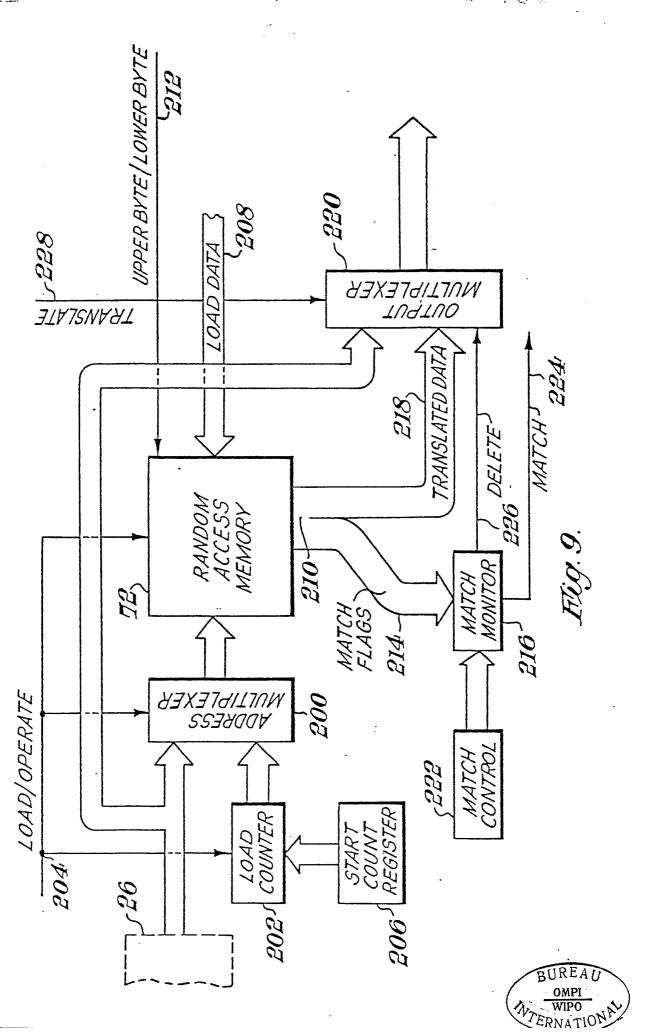

Figure 9 shows a combined implementation of the translator and predetermined character monitor of figure 2.

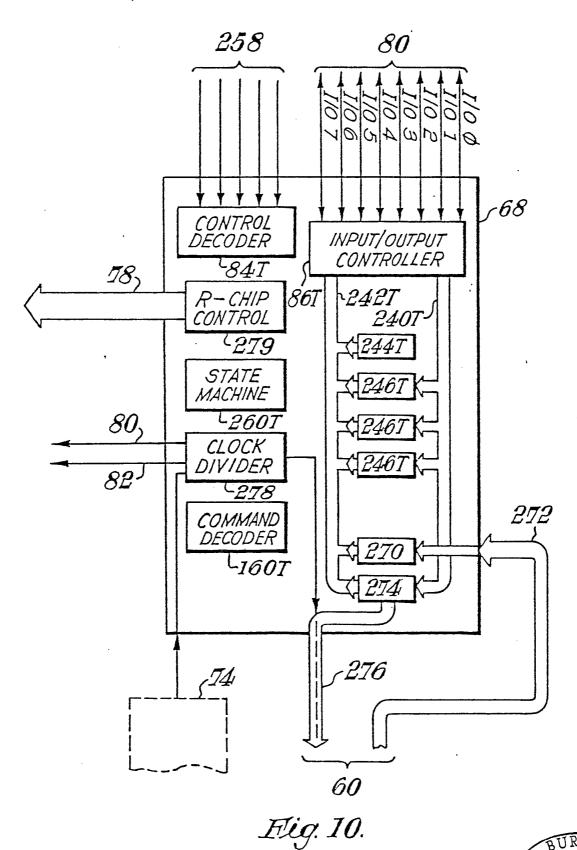

Figure 10 shows a schematic representation of the control elements within the T-chip of figure 3;

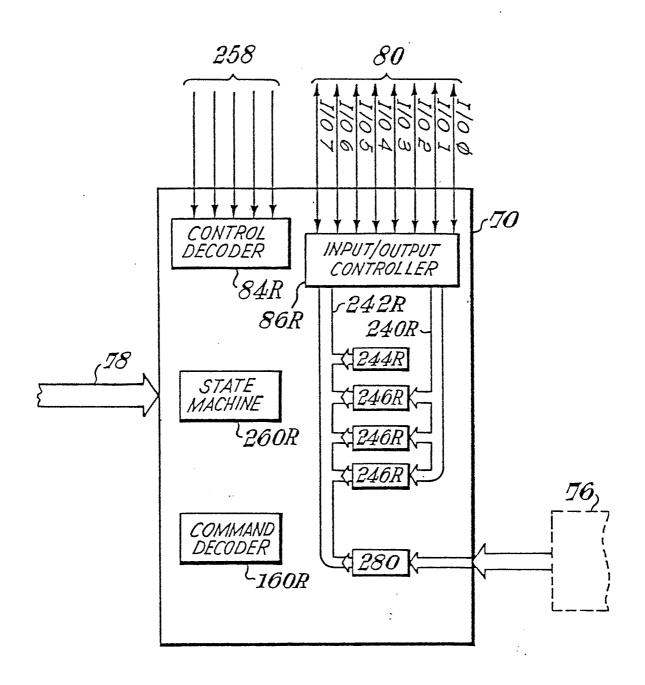

Figure 11 shows a schematic representation of the control elements within the R-chip of figure 3;

Figure 12 shows the dual nature of the data link bus of figure 1;

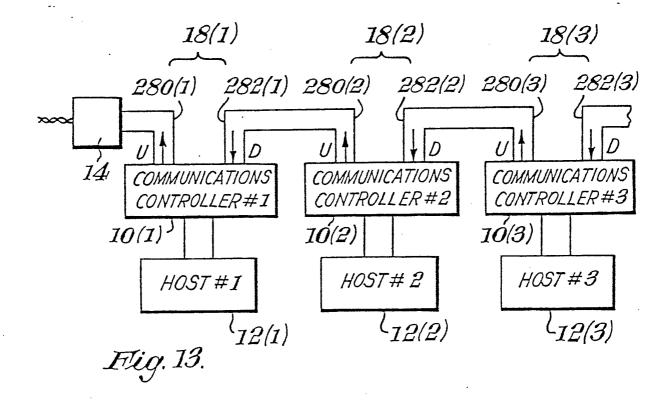

10 Figure 13 shows a plurality of controllers coupling a corresponding plurality of hosts to one another and to a common data link.

WO 81/01064 PCT/GB80/00161

- 14 -

Figure 1 shows the communications controller 10 coupled intermediately between a host system 12 and a data link 14. The host 12 is bidirectionally coupled to the controller 10 by the host bus 16. The controller 10 is bidirectionally coupled to the data link 14 by the data link bus 18.

5

10

15

25

The host 12 passes data to be transmitted by the data link 14, data processing instructions, for the controller 10 and reference characters for use by the controller 10 to the controller 10, in the form of a succession of parallel digital words. The controller 10 turns parallel data to be transmitted into serial data, having processed it according to instructions from the host 12. The processed serial data is then coupled to the data link 14 for sending to some remote data processing system. The controller 10 decodes any instructions from the host 12 which may be destined for the data link 14, and passes them thereto in a form suitable for the control of the link 14.

When the link 14 receives serial data characters from some remote data processor, the controller 10 receives the serial string of characters, processes them in accordance with earlier host 12 instructions, and presents them as a succession of parallel digital words, to the host 12 via the host bus 16. The controller 10 is operable to provide the host 12 with status information concerning the data link 14, to inform the host 12 and to take action when predetermined characters are received, and to automatically generate the

15

20

25

the protocol characters required when transmitting and eliminate such characters when receiving.

The host 12 may comprise any form of data processing equipment, but typically will be a digital computer. The data link 14 may comprise any form of remote data signalling device, such as a modem driven landline, a radio link, or even a direct-wire system.

The controller 10 accepts bursts of parallel transmission data words from the host 12 and controls the timing of 10 the transmission of their serial data equivalents to relieve the host 12 of the necessity of supervising the presentation of each word to the data link 14. Similarly, the controller 10 stores received serial data as a succession of parallel data words for subsequent presentation to the host 12 when the host 12 requests it, so relieving the host 12 of attending to the receipt of each individual character from the data link 14. In addition the controller 10 supplies error checking characters to transmitted data and checks these characters in received data. The controller 10 is also operable to translate received characters into an alternative, host-loaded code, is further operable to synchronise the framing of incoming serial data whose word boundaries are uncertain, and is yet further operable to buffer store incoming, received data as a serial string for later processing. In these, and other ways which will later become apparent, the controller 10 relieves the host 12 of time and program consuming tasks, allowing the

15

the host 12 to operate with improved time-utilisation efficiency. In addition, host systems 12 where memory size, data handling capacity or speed limitations would otherwise preclude their joining to a data link 14, may be so joined via the controller 10 by virtue of the simplification of host 12 task requirements which the controller 10 allows.

The controller 10 may also be linked to one or more host systems, via one or more controllers 10. A secondary, bidirectional external coupling 19 allows ancillary equipment to be controlled and monitored by the host 12.

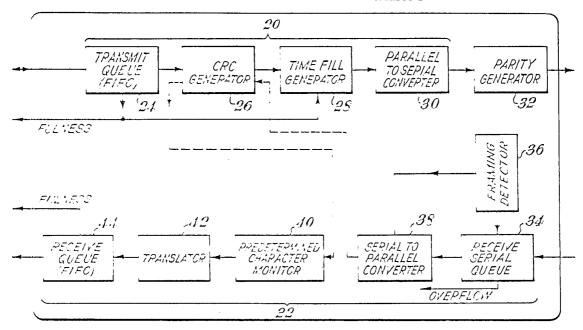

Figure 2 shows, in schematic form, a generalisation of the data flow through the communications controller 10.

The data flow may be divided into two paths, a first path 20 being for data characters, originating from the host 12 for transmission by the data link 14, and a second path 22 for characters, received from the data link 14 and destined for the host 12. Characters to and from the host 12 are in 8 bit parallel format. Characters sent to and received from the data link 14 are in serial form.

Data for transmission by the host 12, together with commands for the communications controller 10, is provided as input to the transmit queue 24. The transmit queue 24 is a 32 byte long first-in-first-out register, clocked by the host 12 for insertion of data and commands and for removal of commands, and at a rate conforming to the operational speed of the data link 14 for removal of data for transmission.

10

15

25

Data is separated from commands at the output of the transmit queue 24. Indication of the state of fullness of the transmit queue 24 is provided.

The output of the transmit queue 24 is provided as the input to a cyclic redundancy check generator 26 which is operable to divide the incoming stream of 8-bit parallel data characters by a selectable, predetermined, irreducible polynomial and to include the remainder resulting from that division as an additional character to be transmitted when commanded to do so. Having added the remainder, the generator 26 starts again dividing the following streams of data characters.

After the addition of the cyclic redundancy check remainders, the data for transmission is provided as an input to a time fill generator 28. The time fill generator 28, whenever no data characters are available for transmission, that is, when the transmit queue 24 is empty, is selectably operable to provide, as characters for transmission, a selectable repetition of one, or another, or combinations of two timefill data characters preloaded from the host 12 to ensure 20 continuity of transmission.

The timefill characters having been selectably added, the 8-bit parallel data characters pass as input to a parallelto-serial converter 30 which converts the 8-bit parallel data words to a selectable by 5-bits or by 8-bits serial data stream.

The output of the serial to parallel converter 30 is

coupled as a stream of binary digits for transmission to the data link 14, via a parity generator 32 which is selectably operable to provide selectably odd or even parity bits. The parity generator 32 need not operate on the serial data stream from the parallel-to-serial converter 30, but can equally well be included between the time-fill generator 28 and the converter 30 to operate on parallel words.

In the reception path 22, a serial stream of binary digits is received from the data link 14. The serial stream is provided as the input to a receive serial queue 34. The receive serial queue 34 is a 256-bit long first-in first-out register enabling the communications controller 10 to receive bursts of data from the data link 14. The queue 34 indicates to the host 12 if it is over-filled.

The output of the serial queue 34 is monitored by a framing detector 36. The framing detector 36, examines the next 24 bits about to emerge from the serial queue 34 and compares them selectably in whole or in part, with a predetermined pattern preloaded into the detector 36 by the host 12.

The preloaded pattern may be, for example, a time fill charact—

er. When a match is found the detector 36 provides output indicative thereof. Once a complete, pre-ordained character has been recognised by the detector 36 the communications controller 10 knows where bytes in the serial data from the data link 14 begin and end and which byte is which in the

serial succession of bytes.

Serial binary digits, emerging from the serial receive queue 34 are provided as input to a serial-to-parallel converter 38 which is operable to turn its serial input into selectably 5-bit or 8-bit parallel words, having reference to the indication provided by the framing detector 36.

The output of the serial-to-parallel converter 38 is coupled as an input to the CRC generator 26 also used in the transmit path 20. The CRC generator 26 works just as before, except this time, when commanded, it compares its calculated remainder with the incoming remainder word, discards the received remainder word, and signals an error condition to the host 12 if there is any difference therebetween.

The parallel characters, coming back from the CRC generator 26, are coupled as an input to a predetermined character monitor 40. The monitor 40 contains a list of predeter-15 mined characters, previously loaded therein by the host 12. The monitor 40 is selectably operable to compare the data word coming in from the CRC generator 26 with the characters in its list. If a match is found, the generator 40 is selectably 20 operable to discard that character, for example fill characters, or to signal to the host that some match has been found within the received data stream. As an example of the utility of such a feature, it may be that, on discovery of a certain match, the host 12 25 knows that the mode or rate of received data is to change and issues instructions to the communications controller 10

- 20 -

accordingly.

5

The output of the character monitor 40 is identical with its input (i.e. a serial stream of parallel bit received characters) and is provided as the input to a translator 42. translator 42 contains a predetermined search list, loaded beforehand from the host 12, of characters it is to look out for together with a corresponding predetermined list, also loaded from the host 12, of substitution characters. The translator 42 compares each character it receives from the 10 monitor 40 with the search list and, if a match is found, provides the corresponding character, from the substitution list, in its place. The translator 42 thus provides, as its output, its input character if no match is found in the search list, and a substituted character from the substitution list 15 if a match is found. The operation or non-operation of the translator 42 is selectable. When used, it allows code translation of some or all of the characters received from the monitor 40.

It is not necessary that the monitor 40 preceed the 20 translator 42. The reverse order may be adopted  $_{r}$  in which case the monitor 40 may react to a match which is a result of a character substitution by the translator 42.

The output of the translator 42 is coupled as an input to a receive queue 44, a 32-byte long first-in first-out 25 register for storing received and processed characters until the host 12 is ready to accept them. The receive queue 42

10

15

25

works in substantially the same manner as the transmit queue 24, with the exception that characters are loaded into the receive queue 44 at a rate consistent with the operation of the data link 14, and unloaded therefrom at a rate consistent with the operation of the host 12. The reverse of the rates pertaining in the transmit queue 24.

A receive parity checker, selectably operable to check and discard selectably odd or even parity bits in the received data, not shown in Figure 2, is included in the reception path 22 between the receive data queue 34 and the serial-to parallel converter 38. With simple modification to the serial-to-parallel converter 38, it might be included thereafter.

The elements so far described cover only the major features of the communications controller. Other features therein will become apparent from the following description.

Before progressing to a description of the individual elements of Figure 2, it is necessary to include a description of the overall structure of the communications controller 10 in that it affects the style of their implementation.

Figure 3 shows a schematic layout of the communications controller 10.

The controller 10 is built on a single circuit board 52. At one end of the board 52 edge connectors are provided for the host bus 16, the data link bus 18, and the external coupling 19. At the other end of the board 52 test points 54 are provided.

WO 81/01064 PCT/GB80/00161

- 22 -

The host bus 16 communicates bidirectionally with the controller 10 via the host bus buffer 56, which couples the host bus 16 to the common bus 58.

The data link bus 18 is bidirectionally coupled to the controller 10 via the data link buffer 59 which couples the data link bus 18 to the internal data bus 60.

5

20

The external coupling 19 is bidirectionally coupled to the controller 10 via the external coupling buffer 62 which couples the data coupling 19 to the internal data coupling 64.

The controller 10 comprises a byte-processing LSI integrated circuit 66, hereinafter called the B-chip, a transmission-controlling LSI integrated circuit 68, hereinafter called the T-chip, a reception controlling LSI integrated circuit 70, hereinafter called the R-chip, a random access memory 72, hereinafter called the RAM, a crystal oscillator clock generator 74, and identity switches 76 by means of which the controller 10 may be given a unique identity.

The common bus 56 communicates bidirectionally with the RAM 72, the B-chip 66, the T-chip 68 and the R-chip 70. The B-chip 66 communicates, for data retrieval purposes, with the RAM 72, via the RAM coupling 74.

The internal data coupling 64 is coupled, bidirectionally, to the B-chip 66. The internal data bus 60 is coupled, bidirectionally, to the T-chip 68. The output of the crystal oscillator 74 is coupled as an input to the T-chip 68. The digital word, representing the address of the controller 10,

- 23 -

which is selectable by means of the identity switches 46, is coupled as an input to the R-chip 70. The T-chip 68 is coupled to the R-chip 70, for passing signals thereto, by the T-R coupling 78.

5 The T-chip 68 processes the output of the crystal oscillator 74 to provide first and second clock signals on first and second clock couplings 80,82 for the control of the B-chip 66, and of the R-chip 68.

The R-chip 70, the T-chip 68, the RAM 72 and the B-chip 66 are operable not only to communicate with the host 12 via the common bus 58, but also with one another, not interfering with the host 12 because of the isolation therefrom offered by the host bus buffer 56.

The operations of the B-chip 66, the T-chip 68 and the

15 R-chip 70 are now described in general terms to be explained in

more detail thereafter.

The B-chip 66 contains the transmit queue 24, the CRC generator 26, the character monitor 40, the translator 42 and the receive queue 44..

20 As stated earlier, the B-chip 66 is a byte-processing unit. During data transmission it loads characters for transmission, together with associated commands, both received from the host 12, into the 32 byte first-in first-out queue 24, separates commands from data, and presents the data characters one-by-one to the T-chip 68 as the T-chip 68 requires.

The B-chip 66 indicates to the host 12 when the queue 24 of

transmission characters is empty, half empty or full so that the host 12 may supply further characters. The commands, separated from the data characters, are presented appropriately to itself (the B-chip 66), the T-chip 68 or the R-chip 70 as they appear at the end of the FIFO queue 24. During transmission the B-chip 66 computes the cyclic redundancy check character (CRC) for addition to the end of the string of transmission characters.

During data reception the B-chip 66 reads received 10 characters from the R-chip 70, as the R-chip 70 requires, together with any status characters. The B-chip 66 is operable to perform the code translation of received characters using the RAM 72 as a lookup table. The B-chip 66 is further operable to compare the received character, or the translated 15 character resulting from the code-translation performed thereon, with a list of characters stored in the RAM and, in response to a match is operable to provide indication to the host 12 of the discovery of a match, compute the CRC remainder and compare it with that received, 20 to load characters into the 32 byte long FIFO queue of received characters 44, to discard time-fill characters, to discard the received character, or where appropriate, to code translate. The B-chip 66 indicates to the host 12 when the 32 byte-long queue 44 of received characters is full, half full or empty so that the host 12 may regulate its demand for characters from the controller 10. Indication may also be given to the host 12 that a match has been found, that a character is the

20

25

first character following a predetermined FLAG character in certain received data formats, that a parity error has occurred in the received data, that the received data is not properly framed, that a predetermined termination character has been received, that an ABORT command has been received, an IDLE command has been received, or, in the event of signal loss, the reason for that loss.

The B-chip 66, as well as byte processing, is operable to receive a special command from the host 12 to lock out the reception of further commands,

indicate to the host 12 when timers have timed out in the T-chip 68 or the status of the data link 14 has changed, as sensed by the T-chip 68.

The T-chip 68 contains the parallel-to-serial converter 30, the parity generator 32, the time fill generator 28, and clock generation circuits.

The T-chip 68 is the transmission control element. It converts the parallel data transmission characters from the B-chip 66 into serial data for transmission according to a selectable 5-bit long or 8-bit long byte, and automatically inserts parity bits therein. The T-chip 68 can be selected to operate in a manner suitable for communication via an asynchronous data link 14, in which case the T-chip 68 automatically inserts start bits into the serial transmission data stream and also automatically inserts stop bits therein of a select-

able 1, 12 or 2 bit period duration. The T-chip 68 can also be selected to operate suitably for use with a synchronous data link 14, in which case the T-chip 68 automatically provides time fill characters (preloaded from the host 12) of, selectably, one or two character length, for transmission, when no data characters are available to be sent, and indicates to the B-chip 66 that a time fill character has been sent. The Tchip 68 can further be selected to operate suitably for use with a data link 12 using BDLC protocol, in which case the Tchip 38 automatically inserts a zero after each five successive 10 ones, automatically provides, for transmission, FLAG or ABORT characters in a time-fill situation, when it waits in an ABORT condition and indicated to the host 12 until released by the host 12.

The T-chip 68 is operable to delay the dropping of a 15 transmission enabling signal by a selectable 0, 2, 3 or 4 bitperiods so that the data link 14, turned off at the start of the delay, has time to go into receive mode.

It is the T-chip 68 that clocks data out to the data link 14 at the selected baud rate. The data may selectably 20 be converted, prior to sending to the data link 14, into zero complementing NRZI format.

On the T-chip 38 the output of the crystal oscillator 74 is divided by a selectable number to provide the baud rate clock, and by a predetermined number to provide a 1 KHz clock 25 for timing purposes. The 1 KHz clock is used by two general

purpose timers which may be programmed for timeout periods between 1 millisecond and 65.5 milliseconds.

5

15

Command signals for the data link 14 are stored in a register on the T-chip 38. Status signals from the data link 14 can be selectably masked by the T-chip 68 to cause interrupts to the host 12 when any status signal from the data link 14, changes, rises or falls. Those status signals from the data link 14 which are required by the R-chip 70 are routed thereto via the T-chip 68. The T-chip 68 can also manipulate 10 the data link 14 signals to provide concatenation, wrap around or monitoring facilities. When the controller 10 is receiving data, the T-chip 68, when reception is asynchronous or isosynchronous, generates the clock signal necessary for data reception. In addition, when the received data is in zero complementing NRZI format, the T-chip 68 is operable to convert it to NRZ.

The R-chip 70 contains the receive serial queue 34, the framing detector 36 and the serial-to parallel converter 38.

The R-chip 70 is the reception controlling element. Firstly, it loads received characters from the data link 14 in 20 the 256 bit long FIFO serial data queue 34, and converts them, as they are presented at the output of the queue, into selectable 5-bit or 8-bit parallel form. When reception is in asynchronous mode, the R-chip 40 detects and indicates framing errors. When reception is in synchronous mode, the R-chip 70 25 automatically byte synchronises on a predetermined character,

and detects and indicates individual or pairs of time-fill characters to be discarded by the B-chip 66. When reception is in BDLC mode, the R-chip 70 automatically byte-synchronises on the FLAG character, indicates the first character after the FLAG character, automatically deletes the zero following five consecutive received ones, indicates the first occurrence of the TERMINATION FLAG, indicates the occurrence of the ABORT condition, and indicates whether or not data characters are being received whenever requested to do so.

The R-chip 70 allows no new characters to enter the 256 bit serial, received data FIFO queue 34 when the carrier is lost, when the queue is full, or when an illegal signal has been received. The R-chip 70 indicates, to the host 12, the act of sealing and reason for sealing the queue.

A general purpose timer is provided on the R-chip having a selectable period and triggered by the received data characters. The timer is automatically re-armed by the R-chip 70 to measure inter-character gaps. Indication is provided if the preselected gap is exceeded.

The RAM 72 is incorporated into the working of the character monitor 40 and of the translator 42.

The RAM 72 is addressed and controlled by the B-chip 66. It is divided into two functions. Firstly, it holds 256 characters for comparison

25 against received characters from the data link 14. Secondly, it holds a 256 character lookup table for code translation of

25

received characters.

The identity switches 76 provide 4-bits towards the controller identity and a further 8-bits towards an optional terminal address when a read switch command is being executed.

The controller 10 is provided with lamp driving circuits for indicating to the system operator the act of transmitting data, the act of receiving data, and the presence of a carrier.

Figure 3 shows a schematic block diagram of the B-chip 66 with respect to data and control signal flow therethrough.

Data commands and signals are sent to and from the Bchip 66 via the common bus 58, which comprises an eight bit data bus 80 together with a line control bus 82. The data bus 80 is operable to transfer digital words, being received data, data for transmission, commands for the controller 10 or status 15 readout from the controller 10, to and from the host 12. control bus 82 is operable to signify the nature of the 8-bit word present on the data bus 80 to indicate to the controller 10 when the host 12 is performing some function, to which the 20 controller 10 must respond, and to indicate to the host 12 when the controller 10 requires attention therefrom. control bus 82 is able to signify whether the word on the data bus 80 is data to be transmitted, data which has been received, a status word from the controller 10, or a command to the controller 10.

The control bus 82 comprises 5 lines, an initialising

10

15

25

line INIT, for initialising the controller 10 whenever the signal thereon is logically true, a host action line 10B for signifying to the controller 10, whenever the signal thereon is logically true, that the host 12 is performing some function to which the controller 10 must respond, a request line I REQ/ by which the controller 10 signifies to the host 12, whenever the signal thereon is logically false, that host 12 response is required, and two data defining lines DIR/ and CONT/ which together, by their logical state, define whether the word on the data bus 80 is a command to the controller 10, received data, data for transmission, or status information read from registers within the controller 10.

The five lines of the control bus 82 are provided as input to a control decoder 84. The control decoder 84 provides one output for each of the conditions described above. Although the outputs of the decoder 84 are not shown coupled to other elements in the B-chip 66 it is to be understood that they are so coupled, in a manner which will become apparent.

The data bus 80 comprises eight lines I/0  $\emptyset$  to I/0 7 inclusively, which are coupled to the input/output controller 86.

The data bus 80 is in receipt of both data and commands from the host 12. Commands to the controller 10 are of two kinds. A first type of command, a direct command, is to be executed immediately. A second type of command, a

queued command, is to be executed at some later time after the transmission of a selected data word and before the transmission of another. All commands, queued or direct, are distinguished from other signals on the data bus 80 by the action of the control decoder 86 which, by observing which of 4 possible states the DIR/ and the CONT/ lines of the control bus 82 are in, provides indication when the signal is a command. Queued commands are distinguished from direct commands by the queued command possessing a "1" in the most significant bit position on the I/O 7 line, and direct commands possessing a "0" in that position. Having thus far described the constructions of the B-chip 66, attention is drawn, for the meantime, away from figure 4 to figure 5.

Figure 5 shows a first part of the transmit queue 24 of 15 figure 2, and in particular, how data and direct and indirect commands are separated from one another, and how data and commands are stored.

The control decoder 86 provides a command line 90 which is logically true if and only if the incoming word on the data 20 bus 80 is a command. The command bus 80 is provided as the input to a 32-byte 9-bit wide first-in first-out register 92.

A first and gate 94 receives the most significant bit from I/O 7 of the data bus, as a first input and the command line 90 from the decoder 86 as a second 25 input. If the most significant bit of the incoming word is a 1, and the command line 90 is true, then the incoming word is

WO 81/01064 PCT/GB80/00161

5

10

15

20

25

- 32 -

a queued command, and the first and gate 94 provides a logically true output which is provided as a ninth, parallel, binary digit on the flag input 95 of the queue 92 for storage, together with the word from the data bus 80, in the queue 92.

on I/O 7 is inverted by a first inverter 96, whose output is logically true if the most significant bit is a zero. The output of the first inverter is provided as a first input to a second and gate 98 and the command line 90 from the command decoder 86 is provided as a second input to the second and gate 98. The output of the second and gate 98 is logically true if the command line 90 carries a logically true signal and the most significant bit of the word on the data bus 80 is zero, the combination of these conditions signifying that the word on the data bus 80 is a direct command for immediate execution by the controller 10.

The output of 98 of the queue 92 is provided as a first input to a signal selector 100 and the data bus 80 is provided as a second input to the selector 100. When the signal on a control input 102 to the selector 100 is logically true, the selector 100 provides, as its output, the signals on the data bus 80. When the signal on the control input 102 is logically false and the input on a selection input 103 is logically true, the selector 100 provides, as its output, the first eight bits of the output of the

WO 81/01064

- 33 -

queue 92, ignoring the additional ninth bit provided at the input of the queue 92 by the first and gate 94.

As stated earlier, the queue 92 is a nine bit wide 32byte long FIFO. Data may be loaded into the queue 92 from 5 the host 12 and extracted under the clocking control of the Tchip 70. The queue 92 is to be loaded whenever the incoming character on the data bus 80 is a queued command or data for transmission. The output of the first and gate 94 is 10 provided as a first input to a first OR gate 104 and the transmit data line 106 from the control decoder:86 is provided as a second input to the first OR gate 104. Whenever the signal on the transmit data line 106 is logically true, it signifies that the word on the data bus 80 is to be 15 transmitted. Whenever the output of the first and gate 94 is logically true it signifies that the word on the data bus 80 is a queued command. The output of the first OR gate 104 being logically true thus signifies that the word on the data bus 80 is either a queued command or a character for trans-20 mission and should be loaded into the queue 92.

A clock multiplexer 108 receives, as a first input, a clock signal from the host 12 on the host clock line 110, and, as a second input, a transmit clock signal on the transmit clock line 112 from the T-chip 68. The clock multiplexer 108 is responsive to the signal on a control input 114, provided by the output of the first OR gate 104, such that, when the

WO 81/01064 PCT/GB80/00161

5

- 34 -

output of the first OR gate 104 is logically true, the clock multiplexer 108 provides, as output, the host clock on the host clock line 110, and when logically false provides, as output, the transmit clock on the transmit clock line 112. The multiplexer 168 is also responsive to an inhibit signal, on an inhibiting input 116, provided by the output of the secondand gate 98, such that, when the output of the second and gate 98 is true, that is, when the character on the data bus 80 is a direct command, the clock multiplexer 108 provides no output. The output of the multiplexer 108is coupled, as clock signal on queue 92. The multiplexer the clock input 88 of the 108 thus provides as output, the relevant clock signal for the operation of the queue 92 whenever the word on the data bus 80 is one that is to be loaded into or removed from the queue 92, 15 and inhibits the clock signal to the . queue 92 whenever the word on the data bus 80 is a direct command, which is not to be loaded into the queue 92.

The queue 92 is a first-in first-out register of a kind which allows independent loading and unloading thereof. 20 output of the first OR gate 104 is provided as a mode controlling signal on a control input 120. When the output of the first OR gate 104 is logically true, signifying that the incoming word on the data bus 80 is to be loaded, the loads the input word into the next vacant queue 92, 25 space behind data which has not yet been presented as output, and when the output of the first OR gate 104 is logically

WO 81/01064

5

**-** 35 **-**

false, the queue 92 presents, as output, that stored word which has been therein for the longest time. The operation and construction of the queue 92 is explained in greater detail at a later stage.

As described earlier, the 8-bit word, stored in the queue 92 from the data bus 80, is presented as a first input to the selector 100 and the signal on the data bus 80 is presented as a second input thereto. The extra, ninth bit, generated by the first and gate 94 in response to the incoming 10 word being a queued command and stored in parallel association in the queue with that word, is provided as: the selection signal on the selection input 103 of the signal selector 100. Thus, as earlier described, the signal selector 100 provides, as its output, any direct command as it is received, or 15 the character provided as output by the queue if it has associated therewith the ninth bit signifying that it is a queued command. In the event of a queued command and a direct command being simultaneously presented to the selector 100, the selector provides, as output, the direct command, the queued command being held over, at the output of the queue 92, 20 until the second and gate 98 by providing a logically false output, indicates that the direct command has been accepted.

The output of the queue 92 is also provided as the input to a data gate 122. The ninth bit associated with each 25 word retrieved from the output of the queue 92 is provided as a controlling input 124 to the data gate 122. Whenever the

PCT/GB80/00161

5

10

15

20

- 36 -

associated ninth bit is logically false, signifying that the word presented at the output of the queue 92 is a data word for transmission, the data gate 122 is opened, providing, as its output, the 8-bit word originally stored by the queue from the data bus 80 and subsequently provided as the output of the queue 92. Whenever the associated ninth bit is logically true, signifying that the word presented at the output of the queue 92 is a queued command, the data gate 122 is closed, providing no output.

In the above manner, queued data is separated from queued commands, and priority is given to direct commands. The exact implementation of such a separator

may be varied in detail without departing the fundamental aspects of its operation.

The output of the selector 100 being the 8-bit word, either as originally stored in and subsequently retrieved from the queue 92 or received directly from the data bus 80, and in either case being a command word, is passed on for intermedate storage in the command holding register 126. The output of the data gate 122, being the 8-bit data word for transmission, originally stored in and retrieved from the queue 92, is passed on for further processing by the B-chip 66 and subsequent transmission via the T-chip 68 and the data link 14.

25 Figure 5 shows, in schematic form, details of one possible method of construction of the queue 92.

A random access memory 128 is operable to receive and store up to 32 nine-bit words, each word being stored in a different selectable one out of 32, storage locations the particular location for each word being defined by a 5-bit address input word. The memory 128 is responsive to the signal on a read/write input 130 such that when the signal thereon is logically true the memory 128 accepts the word on the data bus 80 in parallel with the ninth bit from the output 65 of the first and gate 94 for storage in the location defined by the 5-bit address word, and when the signal on the read/write input 130 is logically false the memory 128 provides, as output, being the output of the queue 92, the word stored in the location defined by the 5-bit address word.

A 5-bit load counter 132, provides a 5-bit address, as output, for defining the location in the memory 128 where a word on the data bus 80 is to be stored. A 5-bit unload counter 134 provides, as output, a 5-bit address for defining the location in the memory 128 from which a word, stored in the memory 128, is to be retrieved and presented at the output 99 of the memory 128.

Both of the counters 132, 134 are rollover incrementing counters. The 5-bit address words, which are their outputs, are binary numbers which are incremented by 1 every time that counter 132, 134 receives a clock pulse. When each counter 132, 134 is in the state where its output is all ones, i.e. 11111, on receipt of the next pulse the output goes to all

- 38 -

zeros, i.e. 00000, and thereafter, on receipt of subsequent clock pulses, goes through 00001, 00010, 00011 etc., back to 11111. Each of the counters 132, 134 may be forcibly reset such that the output is 00000.

5

10

15

The output of the load counter 132 is provided as a first input to an address multiplexer 136. The output of the unload counter 134 is provided as a second input to the address multiplexer 136. The address multiplexer 136 is responsive to the logical state of the signal presented at a control input 138 thereof such that when the signal thereon is logically true, the multiplexer 136 provides, as its output, the output of the load counter 132, and when the signal thereon is logically false, the multiplexer 136 provides, as its output, the output of the unload counter 134. The output of the multiplexer 136 is provided as the address defining input to the memory 128.

The clock signal to each of the counters 132, 134 is provided via the clock input 118 to the queue 92. The signal to the read/write input 130 of the memory 128 and to the 20 control input 138 of the address multiplexer 136 is provided via the control input line 120 to the queue 92. The load counter 132 and the unload counter 134 are also in receipt of the signal on the control input 120 to the queue 92. When the signal on the transmit queue control input 120 is logically true, the load counter 132 is enabled such that its output is incrementable by clock pulses and the unload

10

counter 134 is frozen. When the signal on the transmit queue control input 120 is logically false the unload counter 134 is enabled such that its output is incrementable in response to clock pulses and the load counter 132 is frozen.

Both the load counter 132 and the unload counter 134 are in receipt of the initialising signal INIT on the initialising line 140, from the control bus 82 of figure 4 and in response to the signal thereon being logically true, both counters 132, 134 are together reset such that both have the output state 00000.

A bidirectional 6-bit monitor counter 142 is in receipt of the clock signal from the clock input 118 to the queue 92, the initialising signal INIT from the initialising line 140, and the control signal from the control input 120 to the queue 92. The output of the monitor counter 142 is a 6-bit binary number which is incremented by 1 on receipt of a clock pulse when the signal on the queue control input 120 is logically true, decremented by 1 on receipt of a clock pulse when the signal on the queue control input 120 is logically false, and reset to 000000, regardless of other conditions, when the signal on the initialising line 140 is logically true.

The output of the monitor counter 142 is provided as the input to a decoder 144. The decoder 144 provides a first, logically true, output signal on the "empty" line 146 when the monitor counter's 142 output is 000000, i.e. zero, a second, logically true output signal on the "half full" line 148 when

\_ 40 \_

the monitor counter's 142 output is 010000, i.e. sixteen, and a third, logically true output signal on the "full" line 120 when the monitor counter's 142 output is equal to or greater than 100000, i.e. 32.

At the beginning of operations of the communications controller 10 the host 12 initialises the controller 10 by sending out a logically true signal on the initialising line (INIT) 140. This resets the contents of all counters and registers in the controller 10 to zero.

5

25

In the case of the queue 92, this has the effect of 10 resetting the load counter 132, the unload counter 134 and the monitor counter 142 to zero. Thereafter whenever a character is to be loaded in the memory 128, the signal on the control input 120 to the queue 92 is made logically true by the action of the first OR gate 104 of figure 4, the memory 128 responds 15 by storing the character on the data bus 80, at the location designated by the output of the address multiplexer 136, which in this case, is the output of the load counter 132 and the load counter 132 and the monitor counter 142 are both increm-The load counter 132 thus points to the next address ented. 20 in the memory 128 for the storage of the next character to be presented on the data bus 80, and the monitor counter 142 records the storing of another character in the memory 128 by having its count increased by 1.

Whenever a character is to be unloaded from the memory

128, the signal on the control input 120 to the queue 92 is

made logically false by the action of the first OR gate 104 of figure 4. The address multiplexer 136, in response thereto, provides, as its output, the output of the unload counter 134, the unload counter 134 is enabled to be incremented by subsequent clock pulses, the load counter 132 is frozen, and the monitor counter 142 is enabled to be decremented by the next clock pulse.

In the event of the incoming word on the data bus 80 being a direct command, the clock multiplexer 108 of figure 4 is inhibited, by the action of the second and gate 98 of figure 4 from providing clock pulses on the clock input line 118 to the queue 92 and the unload counter 134 and the monitor counter 142 therefore remain unchanged. The same word will . therefore be accessed from the memory 128, if required, after 15 compliance with the direct command.

If no direct command is to be complied with, the word, stored in the location in the memory 128 determined by the output of the unload counter 134 is provided on the output 99 of the memory 128 and thereafter, the subsequent clock pulse 20 on the clock line 118 increments the monitor counter 142 by 1.

The action of the monitor counter 142 is seen to be to keep a running tally of the number of unretrieved words stored in the memory 128. Whenever a word is stored in the memory 128 the monitor counter 142 is incremented, and when-25 ever a word is retrieved from the memory 128 the monitor counter 142 is decremented. Since the monitor counter 142 is

- 42 -

initialised to zero, its output counter equals the difference between the number of words, inserted into over the number of words retrieved from the memory 128.

As stated earlier, the memory 128 holds up to 32 words. The "empty" line 146 from the decoder 144, when it goes logic-5 ally true, thus signifies that all words previously stored in the memory 128 have been retrieved therefrom. Similarly, a logically true signal on the "half full" line 148 signifies that there have been 16 more words deposited in the memory 128 than have been retrieved therefrom and the memory 128 is 10 consequently, half full. In a like manner, a logically true signal on the full line 150 signifies that all of the memory 128 is full of unretrieved characters, and no more may be placed therein. The empty line 146, the half full line 148 and 15 the full line 150 are coupled back to the host 12, as feedback indicative of the state of fulness of the transmit queue 24.

In use, the host 12 provides bursts of data and commands to the communications controller 10. The host 12

20 monitors the state of fullness of the transmit queue 24.

Whenever the queue 24 reaches a selectable state of emptiness, either half full or empty according to the preference of the operational routine of the host 12, the host 12 provides a stream of data and/or commands until, in the case of a response to half-emptiness of the queue 24, the queue 62 is full, or less than full, or in the case of a response to emptiness

of the queue 24, the queue 24 is selectably part full, half full or completely full. During the loading of data into the memory 128 the controlling clock is the host clock on the host clock line 110 of figure 5, and is very much faster than than the transmit clock on the transmit clock line 112 of figure 5, which is used to clock data at the slow rate required by the data link 14 of figure 1. The memory 128 is thus able to be replenished in a time which, in general, is less than one period of the signal on the transmit clock line 112 of figure 5, and the sending of a character by the data link 14 need not 10 be omitted. In addition, the host 12 is only required to service its data link 14, via the communications controller 10, after the sending of 16 or 32 characters or indeed, however many characters, up to 32, which the host 12 choses to load, by 15 the data link 14, thus leaving very long gaps during which the host 12 can attend to other data processing tasks.

Because the load counter 132 and the unload counter 134 are both rollover counters, as previously described, and the host 12 responds to predetermined levels of emptiness of the memory 128, the action of the queue 92 is to deposit new characters in locations in the memory 128 where they will be retrieved, in their serial order of deposition, immediately consecutively upon the retrieval of the last character already stored therein.

25 The mutual action of the load counter 132 and the unload counter 134 are best described by way of an example.

Imagine that all counters 132, 134, 136 are initially at zero. Imagine also that the host 12 elects to load the memory 128 with 21 characters at a time. In loading, the load counter 132 is incremented from 00000 to 10101, and the characters are stored in consecutive addresses 00000 to 10100 in the memory 128. The monitor counter 142 is also\_incremented from 00000 to 10101. When unloading, the unload counter 134 is incremented from 00000 to 10101, and characters are thereby retrieved from the memory 128 consecutively, in their order of loading, from consecutive addresses in the memory 128 00000 to 10100. Every time that a character is retrieved from the memory 128 the monitor counter 142 is decremented by 1. When the last character is retrieved from the memory 128, the monitor counter 142 stands at zero, and the decoder 144 15 signals to the host 12, via the empty line 146, that the transmit queue 24 is empty. Responding to this indication, the host 12 loads a further 21 characters.

The next 21 characters are loaded into locations in the memory 128 having addresses 10101 through to 11111, and there-20 after 00000 to 10001, since the load counter 132 "rolls over" from 11111 to 00000. The new characters overwrite locations in the memory 128 previously occupied by members of the first set of characters, but this does not matter as the first set of characters have already been retrieved and will not be 25 required again. In loading the characters the load counter 132 is incremented from 10101, the address in the memory

**-** 45 **-**

the controller 10.

· Commands to alter the state of the controller 10 consist of an instruction address word followed by one or more instruction words. The instruction address word specifies which of various registers is the destination of the following instructions word or words. Other commands tell the controller 10 to send back to the host 12 the contents of specified registers. The contents of the specified register will consist of one or more words. The host 12 provides a direct or 10 queued "read register" command to the controller 10, and, subsequently to that command being recognised by the controller 10, the host 12 expects the next subsequent one or more words, the exact number depending upon which register was specified, appearing on the data bus 80, to be the contents of the 15 specified register. At the same time, in order that the host 12 should be aware that the controller 10 is providing information, the controller 10 is required to indicate to the host 12, via the control bus 82, that it is providing data output. This last feature is most essential when dealing with queued 20 commands in that the host 12 has no way of knowing, in advance of the instant when the command will be recognised by the controller 10.

It is also essential, when unloading queued commands from the transmit register 24, that the instruction address word or words are unloaded quickly enough that the sending of the following data word is not interferred with. To this

- 46 -

128 of the first member of the second set of characters, to 10010, the address for the storage of the first character in any subsequent set of characters to be stored. In retrieving the second set of characters from the memory 128, the unload counter 134 is incremented from 10101, the address of the first character of the second set, to 10010, the address of the first character in any subsequent set, and, in so doing, controls the retrieval, in the same serial order as that of their deposition, of characters stored in memory locations 10101 through to 11111 and thereafter from 00000 to 10001. As before, the monitor counter 142 is incremented, by loading, from 00000 to 10101 and decremented by unloading back to 00000, which condition is relayed back to the host 12.

5

10

20

It is thus seen that the load counter 132 and the unload counter 134 "chase each other round" their respective counting loops to achieve the data deposition and retrieval action previously described.

The queuing of data for transmission together with queued commands is of utility to the operation efficiency of the host 12. It is often the case that the mode of operation of the communications controller 10 requires to be altered subsequently to the transmission of a specific data character. By being able to queue that command immediately following the last data character to be sent under the former set of instructions and immediately preceding the first data character to be sent under the new set of instructions, the host 12 is relieved of the necessity of intervening to alter the instructions to

15

end it is essential to provide a faster clock signal than the transmit clock signal to the queue 92 when an instruction has appeared at its output, so that it may be unloaded before the next request for a character by the data link 14.

In every case it is essential to know, upon recognition of the command, how many words following the instruction address word are in fact instruction words, or how many words are required to be sent back to the host 12.

Figure 6 shows a further and final part of the transmit

10 queue 24 of figure 2, and in particular shows one method of

implementing a circuit for achieving the above operations.

The data gate 122, previously shown in figure 5, passes its 8 bit parallel word output as an input to an instruction word separator 152. The separator 152 is responsive to the logical state of the signal on a selection input 154 thereof such that, when the signal is logically true it provides its input word on a data output bus 156, and when the signal is logically false, it provides its input word on an instruction output bus 158.

The command holding register 126, also previously shown in figure 5, provides, as its output, the command held therein, which output is coupled as the input to a command decoder 160. The command decoder 160 contains a predetermined list of all command codes. The command it receives is the instruct

25 ion address word. The instruction words themselves are indistinguishable, other than by their position behind the

- 48 -

instruction address word, from data for transmission, and therefore appear as an input to the separator 152.

5

10

The command decoder 160 examines its input and responds thereto by providing indication to the particular register specified by indicating whether data is to be deposited in or retrieved from that register, and by providing an output indicative of the number of instruction words that involves

The indication to the particular register specified is made via the register enabling bus 162. The register enabling bus 162 comprises a plurality of lines, one line going to each addressable register. The line to the specified register is made logically true and thus enables that register alone to either receive new contents or provide its current contents as an output to the host 12.

The indication as to whether data is to be deposited in or retrieved from the specified register is provided via the deposit/retrieve line 165 which goes to all addressable registers. When the signal thereon is logically true, the specified register prepares to receive new contents, and when logically false, the specified register provides a copy of its current contents to the host 12.

The indication of the number of instruction words which are to follow the instruction address word is provided on an 8-bit instruction length bus 166 which provides the input, as a binary number, to an instruction length counter 168. The binary number so presented is equal to the number of following

25

- 49 --

instruction words.

The instruction length counter 168 is in receipt of a clock signal on a clock input 170 thereof, and, when operational increments its count by 1 for each clock pulse. The length counter 168 is caused to become operational by the input it receives from the command decoder 160 becoming nonzero, and reverts to a non operational condition whenever its count once again becomes zero. The length counter 168 is re-armed by the presentation of another non-zero number from 10 the decoder 160.

The length counter 168 uses the incoming number from the decoder 160 as a count limit. Whenever its count equals the incoming number, it resets itself, back to zero, thus. becoming non operational. The length counter 168 thus remains 15 operational for a number of clock cycles equal to the number of instruction words following the instruction address word.

Whenever it is operational the instruction length counter 168 provides a controlling output which is logically false, and otherwise, logically true. The controlling output of the length counter 168 is coupled to the selection input 154 to the instruction word separator 152. Since the controlling output of the length counter 168 is logically false only while instruction words are being presented as the output of the gate 122, the selector 152 responds by providing the instruction words on the instruction output bus 158, and data words for transmission on the data output bus 156.

5

10

15

25

**-** 50 **-**

The controlling output of the length counter 168 is provided as a first input to a third and gate 174 and, via a second inverter 176, as the first input to a fourth and gate The third and gate 174 is provided, as a second input, with the clock used to clock characters for transmission via the data link 14, via the data link clock line 180. second and gate 178 is provided, as a second input, with the host clock signal from the host clock line 110, otherwise seen on figure 5. The output of the third and gate 174 is provided as a first input to a second OR gate 182 and the output of the fourth and gate 178 is provided as a second input to the second OR gate 182. The output of the second OR gate 182 is the transmission clock signal, provided on the transmission clock line 112 otherwise seen in figure 5. The output of the second OR gate 182 is provided as the clocking signal to the length counter 168.

Whenever an instruction address word is received by the command holding register 126, the length counter 168 is activated. Whenever the length counter 168 is activated, the clock signal provided at the output of the second OR gate 182, changes from that provided on the data link clock line 180 to the host clock line 110. The length counter 168 and the transmit queue 92 of figures 5 and 6 are therefore clocked at the higher rate of the host clock. The instruction words, following the instruction address word, are then stripped out of the queue 92 in a very short time. When all of the

instruction words have been so stripped, the length counter 168 becomes non-operational, and the queue 92 reverts to the data link clock ready to provide a character for transmission.

If the instruction address word is in the form of a direct command, the queue 92 will, as previously described, be 5 paralysed. The host clock signal is once again used to clock the counter 168 and the instruction words, following the instruction address word on the data bus 80 are inserted into their signified register at high speed. It should be noted that, in order to automatically maintain the paralysis of the 10 queue 92 during the receipt of instruction words following a direct command, it is necessary to provide the controlling output of the length counter 168, as a further output inhibiting input to the clock multiplexer 108 of figure 4. This must only occur during a direct command. The circuit for implementing this feature is not shown, but will be apparent to those skilled in the art.

Alternatively, the host 12 can maintain indication to the controller 10, via the control bus 82, that a direct command is being provided during the instruction words, so paralysing the queue 92.

It is to be appreciated that the circuit implementations shown in figures 5 to 7 may be variously changed, modified, or otherwise implemented without departing from the functionality attributed thereto.

It is to be appreciated that all data, as opposed to

PCT/GB80/00161 WO 81/01064

5

20

\_ - 52 -