(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7705366号**

**(P7705366)**

(45)発行日 令和7年7月9日(2025.7.9)

(24)登録日 令和7年7月1日(2025.7.1)

(51)国際特許分類

|         |                  |     |         |        |   |

|---------|------------------|-----|---------|--------|---|

| H 0 1 L | 21/203 (2006.01) | F I | H 0 1 L | 21/203 | S |

| C 2 3 C | 14/34 (2006.01)  |     | C 2 3 C | 14/34  | A |

| C 2 3 C | 14/08 (2006.01)  |     | C 2 3 C | 14/08  | K |

請求項の数 8 (全11頁)

|                   |                           |          |                                                                    |

|-------------------|---------------------------|----------|--------------------------------------------------------------------|

| (21)出願番号          | 特願2022-94923(P2022-94923) | (73)特許権者 | 522015294<br>ケイブイマテリアルズ株式会社<br>大韓民国慶尚北道龜尾市 3 工団 3 路 2 4<br>2       |

| (22)出願日           | 令和4年6月13日(2022.6.13)      | (74)代理人  | 100083806<br>弁理士 三好 秀和                                             |

| (65)公開番号          | 特開2023-3394(P2023-3394A)  | (74)代理人  | 100095500<br>弁理士 伊藤 正和                                             |

| (43)公開日           | 令和5年1月11日(2023.1.11)      | (74)代理人  | 100111235<br>弁理士 原 裕子                                              |

| 審査請求日             | 令和6年7月17日(2024.7.17)      | (74)代理人  | 100195257<br>弁理士 大渕 一志                                             |

| (31)優先権主張番号       | 10-2021-0081335           | (72)発明者  | カン シンヒュク<br>大韓民国 03907 ソウル マポーグ<br>サンガムサン 口 1 - ギル 24 サン<br>最終頁に続く |

| (32)優先日           | 令和3年6月23日(2021.6.23)      |          |                                                                    |

| (33)優先権主張国・地域又は機関 | 韓国(KR)                    |          |                                                                    |

(54)【発明の名称】 酸化物半導体スパッタリング用ターゲット及びこれを利用した薄膜トランジスターの製造方法

**(57)【特許請求の範囲】****【請求項1】**

薄膜トランジスターのアクティブ層を蒸着させるためのスパッタリング工程に使用されるスパッタリング用ターゲットであって、In、Sn、Ga、Zn及びOの組成を基盤とする物質を含み、

酸化ガリウム、酸化スズ、酸化亜鉛及び酸化インジウムを含み、(In + Sn + Ga + Zn)に対してInが60～80重量%、Snが0.5～8重量%、Gaが5～15重量%及びZnが10～30重量%である、酸化物半導体スパッタリング用ターゲット。

**【請求項2】**

(In + Sn + Ga + Zn)に対してInが65～75重量%、Snが1～5重量%、Gaが7～13重量%及びZnが10～20重量%である、請求項1に記載の酸化物半導体スパッタリング用ターゲット。

**【請求項3】**

Inに対するSnの重量比が0.03～0.15である、請求項1に記載の酸化物半導体スパッタリング用ターゲット。

**【請求項4】**

(In + Sn + Ga + Zn)に対してGaとZnの合計含量が20～40重量%である、請求項1に記載の酸化物半導体スパッタリング用ターゲット。

**【請求項5】**

(Ga + Zn)に対するGaの重量比が0.6以下である、請求項1に記載の酸化物半

導体スパッタリング用ターゲット。

**【請求項 6】**

請求項 1 乃至 請求項 5 のいずれか 1 項に記載の酸化物半導体スパッタリング用ターゲットを利用してアクティブ層を蒸着することを含む、薄膜トランジスターの製造方法。

**【請求項 7】**

請求項 1 乃至 請求項 5 のいずれか 1 項に記載の酸化物半導体スパッタリング用ターゲットを利用してアクティブ層を蒸着すること、及び

前記アクティブ層を蒸着した後に、前記アクティブ層を 200 ~ 400 で熱処理することを含む、薄膜トランジスターの製造方法。

**【請求項 8】**

液晶ディスプレイ装置、または有機発光ディスプレイ装置に備えられる薄膜トランジスターを製造する方法であって、

請求項 1 乃至 請求項 5 のいずれか 1 項に記載の酸化物半導体スパッタリング用ターゲットを利用してアクティブ層を蒸着することを含む、薄膜トランジスターの製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、酸化物半導体スパッタリング用ターゲット及びこれを利用した薄膜トランジスターの製造方法に関するものであり、より詳細には、高い電子移動度と素子駆動信頼性を有する薄膜を蒸着するための酸化物半導体スパッタリング用ターゲット及びこれを利用した薄膜トランジスターの製造方法に関するものである。

10

**【背景技術】**

**【0002】**

一般に、薄膜トランジスター (thin film transistor : TFT) は、S R A M や R O M にも応用されるが、主に能動行列型平板ディスプレイ (active matrix flat panel display) の画素 (pixel) スイッチング素子で使用される。例えば、液晶ディスプレイや有機電界発光ディスプレイのスイッチ素子や電流駆動素子で使用されている。ここで、スイッチング素子で使用される薄膜トランジスターは個別画素を独立的に制御するようにして各画素がそれぞれ他の電気信号を表現できるようにする役割をする。

20

**【0003】**

現在、液晶ディスプレイや有機発光ディスプレイは、シリコン系アクティブ層を有する薄膜トランジスターを主に使用している。しかし、ディスプレイに使用される非晶質シリコン (amorphous Si) の場合おおよそ  $0.5 \text{ cm}^2 / \text{V s}$  程度の低い電子移動度 (mobility) による低い動作速度と不安定 (instability) な特性のため大面積高解像度 / 高速駆動ディスプレイ具現に限界がある。そして、主に有機電界発光ディスプレイに使用される多結晶シリコン (poly-Si) の場合エキシマレーザー (excimer laser) を通じて結晶化させるため、電子移動度を含めた TFT 素子特性が非晶質シリコンより優秀な性能を示すが、大面積製造が不可能な短所がある。

30

**【0004】**

最近、これに対する解決策としてインジウムガリウムジンク酸化物系のアクティブ層を有する薄膜トランジスターがディスプレイ装置の駆動素子で一部適用もされているが、多結晶シリコンに比べ低い電子移動度によって次世代大面積 / 高解像度 / 高速駆動ディスプレイへの適用には限界がある実情である。

40

**【0005】**

また、移動度向上のためにインジウムの含量が高い酸化物系のアクティブ層も開発されているが、インジウム含量が高い場合後熱処理工程で発生可能な温度散布によって薄膜トランジスターの移動度などの特性差が発生することがある。これにより 8 世代級以上の大面積基板への適用に限界がある。

**【発明の概要】**

**【発明が解決しようとする課題】**

50

**【 0 0 0 6 】**

本発明は上述したところのような従来技術の問題点を解決するためになされたものであり、本発明の目的は、高い電子移動度と素子駆動信頼性を有して、また大面積製造時に高い均一度を有する薄膜を蒸着するための酸化物半導体スパッタリング用ターゲット、及びこれを利用した薄膜トランジスターの製造方法を提供することである。

**【課題を解決するための手段】****【 0 0 0 7 】**

このために、本発明の一側面は、薄膜、特に、薄膜トランジスターのアクティブ層を蒸着させるためのスパッタリング工程に使用されるターゲットであって、In、Sn、Ga、Zn及びOの組成を基盤とする物質を含む、酸化物半導体スパッタリング用ターゲットを提供する。

10

**【 0 0 0 8 】**

一実施形態では、酸化物半導体スパッタリング用ターゲットは、酸化インジウム、酸化スズ、酸化ガリウム及び酸化亜鉛を含み、(In + Sn + Ga + Zn)に対してInが60～80重量%、Snが0.5～8重量%、Gaが5～15重量%及びZnが10～30重量%の含量の割合で構成ができる。

**【 0 0 0 9 】**

一方、本発明の他の側面は、上記酸化物半導体スパッタリング用ターゲットを利用してアクティブ層を蒸着する、薄膜トランジスターの製造方法を提供する。このような薄膜トランジスターはディスプレイ装置、例えば、液晶ディスプレイ装置、有機発光ディスプレイ装置、電界発光を利用したディスプレイ装置などに使用することができる。

20

**【発明の効果】****【 0 0 1 0 】**

本発明によれば、In、Sn、Ga、Zn及びOの組成を基盤とする5成分系半導体物質でターゲットを形成し、これを通じて薄膜トランジスターのアクティブ層を蒸着させることで、従来のIn、Ga、Zn及びOの組成を基盤とする4成分系半導体物質で形成されたアクティブ層より高い電子移動度と素子駆動信頼性を示すことができ、後工程温度による特性差が少なくて薄膜トランジスター及びこれを備えるディスプレイ装置の性能を向上させることができ、大面積製造時に薄膜トランジスターの均一度向上で製造収率も向上させることができる。

30

**【図面の簡単な説明】****【 0 0 1 1 】**

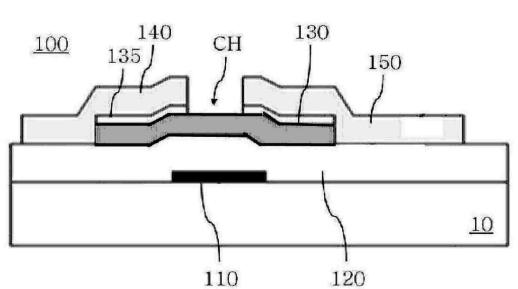

【図1】本発明の一実施例による薄膜トランジスターを示す断面図である。

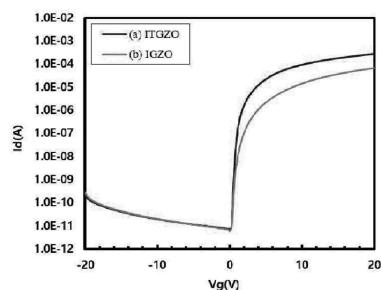

【図2】本発明の一実施例による薄膜トランジスターと従来技術による薄膜トランジスターのゲート電圧によるドレイン電流を示すグラフである。

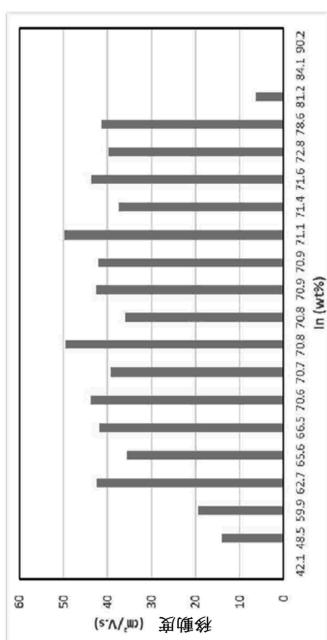

【図3】本発明において、ターゲットのインジウム含量によるTFT素子の電子移動度を示すグラフである。

【図4】図3の薄膜の特性を分類した結果を示す図面である。

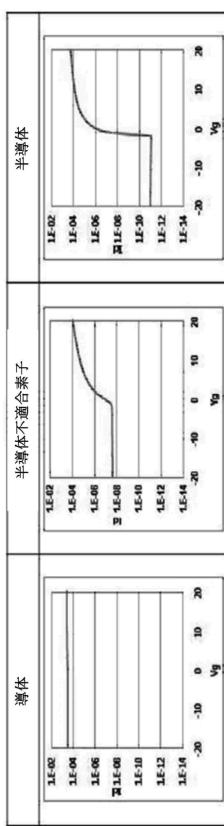

【図5】導体薄膜、半導体特性を示すことはあるが、その特性が劣悪で薄膜トランジスターのアクティブ層で使用されるには不適合な薄膜及び優秀な特性を示す半導体薄膜を有する薄膜トランジスターにおいて、VgによるIdの変化を示す図面である。

40

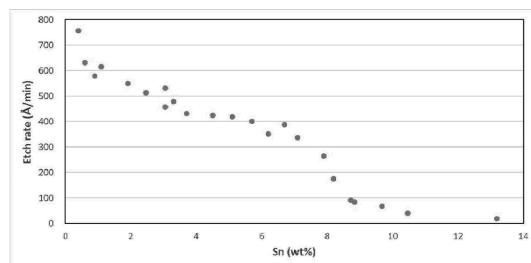

【図6】スズ含量による薄膜のエッチング速度を示すグラフである。

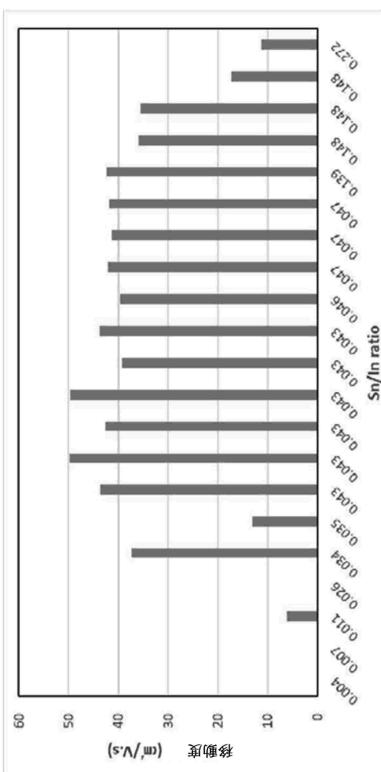

【図7】本発明において、ターゲットのインジウムに対するスズ含量によるTFT素子の電子移動度を示すグラフである。

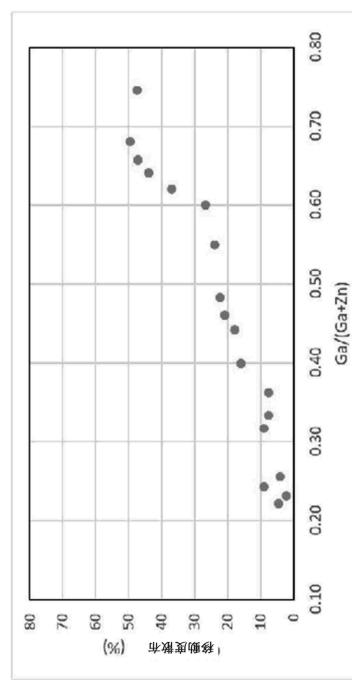

【図8】ガリウム及び亜鉛含量に対するガリウムの含量比によるTFT素子の温度による移動度散布を示すグラフである。

**【発明を実施するための形態】****【 0 0 1 2 】**

以下では添付された図面を参照して本発明の実施例による酸化物半導体スパッタリング用ターゲット、これを通じて蒸着されたアクティブ層を有する薄膜トランジスター及びこ

50

れを具備するディスプレイ装置について詳しく説明する。

**【0013】**

併せて、本発明を説明するにおいて、関連される公知機能あるいは構成に対する具体的な説明が本発明の要旨を必要に不明確にすることがあると判断された場合、その詳細な説明は略する。

**【0014】**

図1は、本発明の一実施例による薄膜トランジスターを示した断面図である。

**【0015】**

本発明の実施例による酸化物半導体スパッタリング用ターゲットは、図1に示したような薄膜トランジスター100のアクティブ層130を蒸着させるためのスパッタリング(sputtering)工程に使用されるターゲットである。ここで、スパッタリングプラズマ粒子をターゲットに速い速度で衝突させ、飛び出るターゲットの粒子をターゲットの向かい側にある基板上に蒸着させる方法である。10

**【0016】**

本発明の実施例で、このような酸化物半導体ターゲットはIn、Sn、Ga、Zn及びOの組成を基盤とする物質を含み、例えば、酸化ガリウム、酸化スズ、酸化亜鉛及び酸化インジウムを含むことができる。このとき、(In + Sn + Ga + Zn)に対してInが60～80重量%、Snが0.5～8重量%、Gaが5～15重量%及びZnが10～30重量%の含量の割合で含まれることができる。

**【0017】**

図1は、ボトムゲート構造の薄膜トランジスターを例示しているが、本発明が必ずこれに限定されるものではない。20

**【0018】**

例えば、本発明のスパッタリング用ターゲットはトップゲート構造の薄膜トランジスターなど多様な構造の薄膜トランジスターの薄膜蒸着に使用することができる。

**【0019】**

図2は、本発明の一実施例による薄膜トランジスターと従来技術による薄膜トランジスターのゲート電圧によるon currentを示すグラフである。

**【0020】**

このように、In、Sn、Ga、Zn及びOの組成を基盤とする物質で酸化物半導体ターゲットを形成し、これを使用してスパッタリング工程を通じて薄膜トランジスター100のアクティブ層130を蒸着させれば、図2に示したように、In、Sn、Ga、Zn及びOの組成を基盤とする物質を含む酸化物半導体ターゲットを通じてアクティブ層が蒸着された薄膜トランジスター(a)は従来のIn、Ga、Zn及びOの組成を基盤とする4成分系半導体物質で形成されたアクティブ層を有する薄膜トランジスター(b)と比べて、高電圧区間(Vg > Vth)ではおよそ10倍程度高いドレイン電流を示すによって高いon-off switching ratioを示して、スイッチング素子の主要特性であるsubthreshold swing(V/dec)が低いことによってより速くスイッチング可能であることを確認することができる。30

**【0021】**

図3は、本発明において、ターゲットのインジウム含量による薄膜トレンジストの電子移動度を示すグラフであり、図4は、図3の薄膜の特性を分類した結果を示す図面である。また、図5は、導体薄膜、半導体特性を示すことはあるが、その特性が劣悪で薄膜トランジスターのアクティブ層で使用されるには不適合な薄膜及び優秀な特性を示す半導体薄膜をアクティブ層で使用した薄膜トランジスターにおいて、VgによるIdの変化を示す図面である。

**【0022】**

図示されたように、Inが60重量%未満であるターゲットを利用して蒸着された薄膜は、半導体特性を示すことはあるが、電子移動度が低くて薄膜トランジスターのアクティブ層で使用されるには不適合である。また、Inが80重量%を超過したターゲットを利

10

20

30

40

50

用して蒸着された薄膜は、電子移動度が低いか、または導体特性を示して、薄膜トランジスターのアクティブ層で使用されることがない。反面、 $I_n$  が 60 ~ 80 重量 % であるターゲットを利用して蒸着された薄膜は、優秀な電子移動度を示す。これから、本発明のアクティブ層を成膜するためのターゲットの  $I_n$  の含量は 60 ~ 80 重量 % であるものが望ましいことが分かる。本発明の薄膜は望ましくは、少なくとも  $30 \text{ cm}^2 / \text{V} \cdot \text{s}$  の電子移動度値を有する。

#### 【0023】

アクティブ層が導体特性を示すと、薄膜トランジスターはゲート電圧に関係なく高いドレイン電流が測定されて threshold voltage(しきい電圧)を基準で on-off switching をする半導体素子特性具現をすることができない。

10

#### 【0024】

半導体で使用されるのに不適合な薄膜をアクティブ層で使用した薄膜トランジスターは、ゲート電圧によってドレイン電流の変化があるが、その差が大きくなくて、threshold voltage 以下のゲート電圧で高い漏洩電流が発生されてスイッチング素子として劣悪な性能を示す。一方、優秀な半導体特性を示す薄膜をアクティブ層で使用した薄膜トランジスターは、ゲート電圧によって大きい差のドレイン電流変化を伴うので、スイッチング素子として優秀な性能を示す。

#### 【0025】

図 6 は、本発明において、ターゲットのスズ含量による薄膜のエッティング速度を示す図面である。

20

#### 【0026】

図示されたように、( $I_n + S_n + Ga + Zn$ ) に対してターゲットのスズ含量が 8 重量 % 超過なら、それから成膜された薄膜のエッティング速度は急激に低下されることが分かる。

#### 【0027】

薄膜トランジスターはフォトリソグラフィ工法を利用して製作するようになるが、アクティブ層の場合蒸着後湿式エッティングを通じて一定な形状でのパターニングが必要である。このとき、湿式エッティングのためには一定な速度以上のエッティング速度を要求するようになって、望ましくは  $200 \text{ / min}$  以上のエッティング速度が要求される。

#### 【0028】

図 7 は、本発明において、ターゲットのインジウムに対するスズ含量比による TFT 素子の電子移動度を示すグラフである。

30

#### 【0029】

図示されたように、ターゲットのインジウムに対するスズ含量比(重量比)が 0.03 ~ 0.15 (インジウムの重量 : スズ重量 = 1 : 0.03 ~ 0.15) なら、それから成膜された薄膜は優秀な電子移動度を示す。これから、本発明のアクティブ層を成膜するためのターゲットのインジウムに対するスズ含量比が 0.03 ~ 0.15 であることが望ましいことが分かる。

#### 【0030】

図 8 は、本発明において、ターゲットのガリウム及び亜鉛含量に対するガリウムの含量比による TFT 素子の温度による移動度散布を示すグラフである。

40

#### 【0031】

図示されたように、ターゲットのガリウム及び亜鉛含量に対するガリウム含量比(重量比)が 0.6 以下ならば、それから成膜された薄膜は優秀な移動度散布を示す。これから、本発明のアクティブ層を成膜するためのターゲットのガリウム及び亜鉛含量に対するガリウム含量比が 0.6 以下であるものが望ましいことが分かる。

#### 【0032】

本発明で移動度散布は、アクティブ層を蒸着した後薄膜をそれぞれ 200 と 400 で熱処理して製作されたそれぞれの TFT 素子の移動度の差で、望ましくは 30 % 以下の移動度散布値を有する。

50

**【 0 0 3 3 】**

このような組成と含量比で構成されるターゲットは酸化ガリウム粉末、酸化スズ粉末、酸化亜鉛粉末及び酸化インジウム粉末を前記含量比に合うように混合した後乾式加圧成形(cold press)、スリップキャスティング(slip casting)、フィルタープレス(filter press)、静水圧成形(cold isostatic press)、ゲルキャスティング(gel casting)、強制沈降(centrifugal sedimentation)、自然沈降(gravimetric sedimentation)などの成形法を通じて成形した後、これに対する焼結を通じて製造されることができる。併せて、このように製造されたターゲットは、例えば、金属材で構成されるバックキングプレート(backing plate)と接合されて支持された状態でスパッタリング工程に使用されることができる。

**【 0 0 3 4 】**

一方、本発明の実施例による酸化物半導体ターゲットを使用して蒸着させたアクティブ層130を含む薄膜トランジスター100は液晶ディスプレイや有機発光ディスプレイのスイッチング素子や電流駆動素子で使用される。このような薄膜トランジスター100はゲート電極110、ゲート絶縁膜120、アクティブ層130、ソース電極140及びドレイン電極150を含んで形成される。

**【 0 0 3 5 】**

一方、基板10は薄膜トランジスター100のための熱力学的及び機械的要求事項を満足させることができる硝子、半導体ウェーバー(semiconductor wafer)、金属酸化物、セラミックス物質、プラスチックなどが使用されることがある。特に、基板10は硝子またはプラスチックであることが望ましいが、これだけに限定されるものではない。

**【 0 0 3 6 】**

ゲート電極110は基板10上に形成されるが、ディスプレイ装置に適用される場合、基板10上に第1方向、例えば、横方向に沿って配列されるゲートライン(図示せず)から分岐されて形成される。このようなゲート電極110には薄膜トランジスター100にオン／オフするための電圧が印加される。このために、ゲート電極110は金属、または金属酸化物のような伝導性物質で形成されることがある。例えば、ゲート電極110はPt、Ru、Au、Ag、Mo、Al、Wまたは、Cuのような金属、またはIZO(Indium Zinc Oxide)または、ITO(Indium Tin Oxide)のような金属、または伝導性酸化物で形成されることがある。すなわち、ゲート電極110は基板10上に前記の伝導性物質を薄膜で蒸着した後、これをパターニングして形成されるが、ゲートライン(図示せず)と一つの工程を通じて同時に形成される。

**【 0 0 3 7 】**

このようなゲート電極110は拡散防止膜(図示せず)及び拡散防止膜(図示せず)に蒸着された銅膜の構造でなされることができる。拡散防止膜(図示せず)は銅原子が基板10に拡散されることを防止し、銅の結合力及び電気的特性を向上させるためのものであり、チタン、タンタル、モリブデン、クロム、ニッケルまたは白金のうちで何れか一つを含んでなされることができる。

**【 0 0 3 8 】**

ゲート絶縁膜120は、通常的な半導体素子に使用される絶縁物質で形成されることがあるが、特に、シリコン酸化物またはシリコン窒化物で形成されることがある。例えば、ゲート絶縁膜120はSiO<sub>2</sub>またはSiO<sub>2</sub>より誘電率が高いHig h - K物質であるHfO<sub>2</sub>、Al<sub>2</sub>O<sub>3</sub>、Si<sub>3</sub>N<sub>4</sub>または、これらの混合物でなされることがある。

**【 0 0 3 9 】**

アクティブ層130はゲート電極110に相応されるゲート絶縁膜120上に形成されてチャンネル領域(CH)を具備する。

**【 0 0 4 0 】**

そして、本発明の実施例で、アクティブ層130は上述した本発明の実施例による酸化物半導体スパッタリング用ターゲット、すなわち、(In + Sn + Ga + Zn)に対してInが60～80重量%、Snが0.5～8重量%、Gaが5～15重量%及びZnが10～30重量%の含量割合で含むターゲットを利用したスパッタリング工程を通じてゲー

10

20

30

40

50

ト絶縁膜 120 上に蒸着され、パターニングされて形成される。

【0041】

このように、アクティブ層 130 が前記の組成及び含量比を有する薄膜で構成される従来の In、Ga、Zn 及び O の組成を基盤とする 4 成分系半導体物質で形成されたアクティブ層より高い電子移動度及び信頼性を示すことができて、これを含む薄膜トランジスター 100 の性能を向上させることができる。

【0042】

ソース電極 140 及びドレイン電極 150 は、アクティブ層 130 上に離隔配列される。このようなソース電極 140 及びドレイン電極 150 は金属など導電物質で構成されることができるし、ゲート電極 110 のように拡散防止膜(図示せず)及び拡散防止膜(図示せず)に蒸着された銅膜の構造でなされることができる。10

【0043】

ソース電極 140 は基板 10 上で、ゲートライン(図示せず)と直交する第 2 方向、例えば、縦方向に沿って配列されるデータライン(図示せず)と連結される。そして、ドレイン電極 150 は画素電極(図示せず)と連結される。

【0044】

一方、アクティブ層 130 とソース電極 140 及びドレイン電極 150 の間には不純物半導体層であるオームックコンタクト層 135 が形成されることがある。

【0045】

また、図 1 には示されないが、薄膜トランジスターは、ソース電極及びドレイン電極の上部に形成される保護層(図示せず)、などを含むことができる。保護層としては、SiO<sub>2</sub>、SiNx などの物質及びその外の酸化物が使用されることがある。20

【0046】

このような、本発明の実施例による薄膜トランジスター 100 は、各種ディスプレイ装置のスイッチング素子や電流駆動素子で使用される。例えば、図示しなかったが、薄膜トランジスター 100 がお互いに対向されるように向い合う上、下部基板と、その間に介されている液晶層及び下部基板の背面に配置されて前方に光を照射するバックライトを具備する液晶ディスプレイ装置(LCD)に使用される場合、薄膜トランジスター 100 は多数個のゲートラインとデータラインが配列された下部基板のうちでこれらラインが交差して定義される画素(pixel)領域に形成される。このとき、上部基板には画素領域に対応してカラーフィルターが具備される。そして、上部基板の上面には液晶ディスプレイ装置の光学的特性を補ってくれる光学フィルムが配置されることがある。30

【0047】

また、本発明の実施例による薄膜トランジスター 100 は、液晶ディスプレイ装置外にも有機発光ディスプレイ装置(OLED)にも使用されることがある。この場合、薄膜トランジスター 100 は多数個のゲートラインとデータラインが配列された下部基板のうちでこれらのラインが交差して定義される画素(pixel)領域に形成される。このとき、下部基板には有機発光素子が形成される。このような下部基板と上部基板が合着されて有機発光ディスプレイ装置の有機発光パネルを成すようになる。ここで、有機発光素子はアノード電極(anode electrode)とカソード電極(cathode electrode)そして、これらの間に位置する正孔輸送層(hole transporting layer)、発光層(emission layer)及び電子輸送層(electron transporting layer)を含む。このとき、正孔(hole)と電子(electron)をもう少し効率的に注入するために、アノード電極と正孔輸送層の間で正孔注入層(hole injection layer)が、そして、電子輸送層とカソード電極との間で電子注入層(electron injection layer)がそれぞれ含まれることができる。これによって、アノード電極から正孔注入層及び正孔輸送層を通じて発光層に注入された正孔と、カソード電極から電子注入層及び電子輸送層を通じて発光層に注入された電子がエキシトン(exciton)を形成するが、このエキシトンは正孔と電子との間のエネルギー・ギャップ(gap)に該当する光を発光するようになる。このとき、アノード電極は仕事関数(work function)が高くて透明な酸化インジウムスズ(indium-tin oxide : ITO)やインジウム酸化亜鉛(indium-zinc-oxide : IZO)のような物質

10

20

30

40

50

で、カソード電極は仕事関数が低くて化学的に安定なアルミニウム（A1）やカルシウム（Ca）、アルミニウム合金のような物質で構成されることができる。

【0048】

一方、有機発光ディスプレイ装置の上部基板上面にもこれの光学的特性を補ってくれる光学フィルムが配置されることができる。

【0049】

以上のように本発明はたとえ限定された実施例と図面によって説明されたが、本発明は前記の実施例に限定されるものではなくて、本発明が属する分野で通常の知識を有した者ならこのような記載から多様な修正及び変形が可能である。

【0050】

それで、本発明の範囲は説明された実施例に限って決まってはいけないし、添付の特許請求範囲だけではなく、特許請求範囲と均等なものなどによって決まらなければならない。

【符号の説明】

【0051】

100 薄膜トランジスター

110 ゲート電極

120 ゲート絶縁膜

130 アクティブ層

135 オーミックコンタクト層

140 ソース電極

150 ドレイン電極

10 基板

C H チャンネル領域

10

20

30

40

50

【図面】

【図 1】

【図 2】

10

【図 3】

【図 4】

| No. | In<br>(wt%) | 導体 | 半導体<br>不適合素子 | 半導体 |

|-----|-------------|----|--------------|-----|

| 1   | 42.1        |    | ○            |     |

| 2   | 48.5        |    | ○            |     |

| 3   | 59.9        |    | ○            |     |

| 4   | 62.7        |    |              | ○   |

| 5   | 65.6        |    |              | ○   |

| 6   | 66.5        |    |              | ○   |

| 7   | 70.6        |    |              | ○   |

| 8   | 70.7        |    |              | ○   |

| 9   | 70.8        |    |              | ○   |

| 10  | 70.8        |    |              | ○   |

| 11  | 70.9        |    |              | ○   |

| 12  | 70.9        |    |              | ○   |

| 13  | 71.1        |    |              | ○   |

| 14  | 71.4        |    |              | ○   |

| 15  | 71.6        |    |              | ○   |

| 16  | 72.8        |    |              | ○   |

| 17  | 78.6        |    |              | ○   |

| 18  | 81.2        |    | ○            |     |

| 19  | 84.1        | ○  |              |     |

| 20  | 90.2        | ○  |              |     |

20

30

40

50

【図 5】

【図 6】

10

【図 7】

【図 8】

20

20

30

40

50

---

フロントページの続き

ガム ワールドカップ パーク 4 ダンジ 403 - 1601

(72)発明者 ムン ジョンヒュン

大韓民国 43019 デグ ダルソン ガン ユガ ウブ テクノ デロ 195 106 - 1405

(72)発明者 オク カンミン

大韓民国 39164 キョンサンブク ド グミ - シ サンドン ミョン シンダン 3 - 口 16

ウミリン セントラル パーク 117 - 2506

審査官 河合 俊英

(56)参考文献 特開2010 - 118407 (JP, A)

特開2008 - 280216 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 21 / 203

H10D 30 / 67

C23C 14 / 34

C23C 14 / 08