(19) RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(à n'utiliser que pour les commandes de reproduction)

2 676 559

(21) N° d'enregistrement national :

91 05762

(51) Int Cl<sup>5</sup> : G 06 F 13/40

(12)

## DEMANDE DE BREVET D'INVENTION

A1

(22) Date de dépôt : 13.05.91.

(30) Priorité :

(43) Date de la mise à disposition du public de la demande : 20.11.92 Bulletin 92/47.

(56) Liste des documents cités dans le rapport de recherche : Se reporter à la fin du présent fascicule.

(60) Références à d'autres documents nationaux apparentés :

(71) Demandeur(s) : MATRA DEFENSE société anonyme — FR.

(72) Inventeur(s) : Léopold Louis.

(73) Titulaire(s) :

(74) Mandataire : Cabinet Plasseraud.

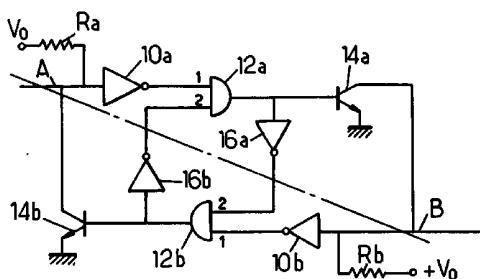

(54) Dispositif d'extension de bus bidirectionnel.

(57) Le dispositif comprend deux ensembles symétriques. Chaque ensemble comporte d'une part, disposés en série d'un bus vers l'autre, un amplificateur inverseur d'entrée (10a, 10b), une porte ET à deux entrées (12a, 12b) et un amplificateur inverseur de sortie (14a, 14b) et, d'autre part, un inverseur de validation (16a, 16b) dont l'entrée est reliée à la sortie de la porte ET et dont la sortie attaque la deuxième entrée de la porte ET de l'autre ensemble.

FR 2 676 559 - A1

**DISPOSITIF D'EXTENSION DE BUS BIDIRECTIONNEL**

La présente invention concerne un dispositif

5 d'extension de bus numérique bidirectionnel.

On connaît déjà des dispositifs électroniques

d'extension de bus constitués par un module ayant des

amplificateurs montés en tête-bêche et des circuits

permettant de valider l'amplificateur approprié et de

10 commander la direction de transfert d'information.

L'invention vise à fournir un dispositif d'exten-

sion permettant d'atteindre le même résultat que les

dispositifs classiques sans nécessiter de signaux de

contrôle.

15 Dans ce but, l'invention propose un dispositif

comprenant deux ensembles symétriques de circuits

électroniques, chaque ensemble comprenant :

- d'une part, disposés en série d'un bus vers

l'autre, un amplificateur inverseur d'entrée, une porte ET

20 à deux entrées et un amplificateur inverseur de sortie,

- et, d'autre part, un inverseur de validation dont

l'entrée est reliée à la sortie de la porte ET et dont la

sortie attaque la deuxième entrée de la porte ET de l'autre

ensemble.

25 Pour garantir un fonctionnement sûr, l'inverseur de

validation est avantageusement prévu pour avoir une

constante de temps de commutation vers l'état de blocage

inférieure à sa constante de temps de commutation vers

l'état de déblocage.

30 L'amplificateur inverseur de sortie peut être

constitué par un transistor monté en commutateur dont la

liaison émetteur-collecteur est montée entre le bus

respectif et une tension de référence. Cet amplificateur de

sortie peut également être constitué par un circuit à trois

35 états (niveau 1, niveau 0 et haute impédance) muni d'une

résistance de liaison avec une tension de référence égale à

la tension de repos du bus respectif.

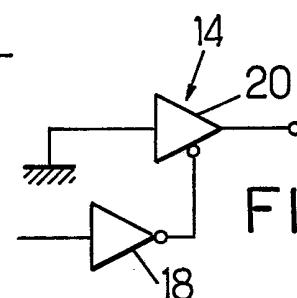

L'inverseur de validation est par exemple constitué par un amplificateur inverseur attaquant une des entrées d'une porte ET directement et l'autre entrée de la porte ET 5 par l'intermédiaire de circuits de retard, créant un retard au déblocage.

L'invention sera mieux comprise à la lecture d'un mode particulier de réalisation et de variantes donnés à titre d'exemple non limitatif. La description se réfère au 10 dessin qui l'accompagne, dans lequel :

- la figure 1 est un chemin synoptique d'un dispositif d'extension de bus porté à une tension positive prédéterminée V0 au repos,

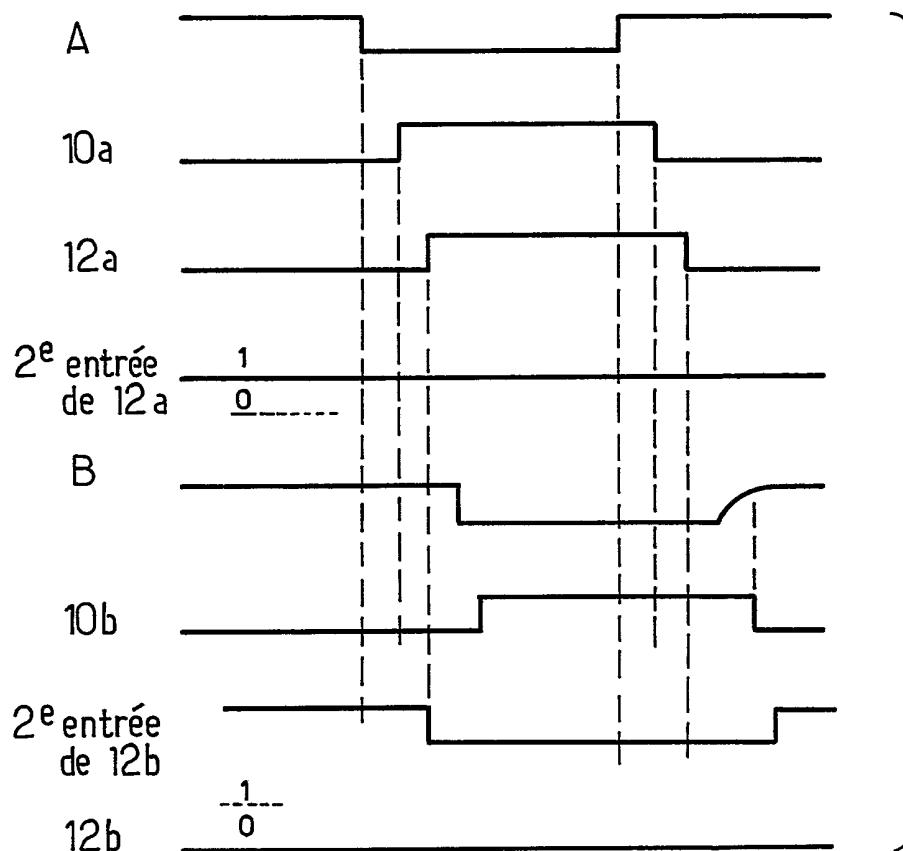

15 - la figure est un chronogramme montrant l'allure des signaux dans un dispositif du genre montré en figure 1,

- les figures 3 et 4 montrent schématiquement une constitution possible des amplificateurs de sortie et des inverseurs de validation appartenant au circuit de la 20 figure 1.

Le dispositif montré en figure 1 permet de relier un bus A à un bus d'extension B. On supposera dans ce qui suit que chaque bus est maintenu au repos à une tension V0 positive, par exemple de + 5 volts, par l'intermédiaire d'une résistance R, par exemple de 220 ohms ou 180 ohms, ce 25 type de bus ne constituant qu'un simple exemple. Le dispositif a une constitution symétrique par rapport à la ligne en traits mixtes de la figure 1. On peut le regarder comme comprenant deux ensembles électroniques, constitués de circuits identiques pour les deux ensembles, portant la 30 référence a dans un des ensembles et la référence b dans l'autre. Il suffit en conséquence de décrire un des deux ensembles.

L'ensemble de transmission du bus A vers le bus B 35 comporte, pour chaque ligne du bus, un ensemble ayant un amplificateur inverseur d'entrée 10a dont la sortie est reliée à une des entrées d'une porte logique ET 12a. La

sortie de la porte 12a est reliée à un amplificateur de sortie 14a dont les caractéristiques seront définies plus loin. La sortie de l'amplificateur inverseur 14a est reliée au bus B.

5 Le bouclage entre les deux ensembles est constitué, dans chaque sens, par un inverseur. L'inverseur 16a relie la sortie de la porte ET 12a à la seconde entrée de la porte ET 12b. Il est destiné à bloquer la porte 12b quand la porte 12a est passante.

10 Les divers composants sont cadencés par l'horloge commandant également le transfert d'informations sur les bus A et B.

15 Pour assurer un fonctionnement sûr du dispositif, chaque inverseur de validation 16a doit avoir une constante de temps de blocage de la porte qu'il attaque plus courte que la constante de temps de validation. La différence entre les constantes de temps doit être suffisante pour maintenir le blocage de la porte ET placée en aval suffisamment longtemps pour que l'amplificateur inverseur attaquant la porte ait eu le temps de commuter. Il faut cependant éviter une constante de temps excessive, qui réduirait la vitesse de fonctionnement du bus.

20 Dans la pratique, une constante de temps de 2 à 3 nano-secondes pour le blocage, de 5 à 10 nano-secondes pour la validation donne en général des résultats satisfaisants.

25 Le fonctionnement du dispositif est le suivant, dans le cas où les bus A et B ont le niveau logique 1 au repos, correspondant à une tension de + 5 volts. La sortie de l'amplificateur inverseur d'entrée 10a est alors au niveau 0 logique. Elle force la sortie de la porte ET 12a à 0, ce qui bloque l'amplificateur de sortie 14a et force à 1 la sortie de l'inverseur de validation 16a. Dans ce cas, la sortie de la porte ET 12b est à 0 du fait que le bus B est encore à 1, ce qui bloque l'amplificateur de sortie 14b et force la sortie de l'inverseur de validation 16b à 1, validant ainsi la porte 12a qui peut transférer le signal reçu sur sa première entrée.

Si le bus A passe au niveau logique 0, la sortie de l'amplificateur A1 (seconde ligne du chronogramme de la figure 2) passe au niveau 1, qui est appliqué à la première entrée de la porte 12a. L'autre entrée de la porte 12a étant encore au niveau 1, la sortie de la porte 12a passe au niveau 1 et commute l'amplificateur de sortie 14a : le bus B passe au niveau logique 0.

Entre-temps, l'entrée de l'inverseur de validation 16a étant passée à 1, la sortie de cet inverseur passe à 0, bloque la porte 12b et force la sortie de cette porte à 0. Etant donné que la sortie de la porte 12b était déjà à 0, il n'y a pas de changement d'état de cette porte.

La sortie de l'amplificateur inverseur d'entrée 10b passe au niveau 1, mais ce niveau n'est appliqué sur la première entrée de la porte ET 12b qu'alors que celle-ci est déjà bloquée par l'inverseur de validation 16a, à fonctionnement rapide dans le sens du blocage.

Si le bus A repasse à 1, la sortie de l'amplificateur inverseur 10a repasse à 0, force la sortie de la porte 12a à 0 et rebloque l'amplificateur 14a. Le bus B repasse à 1, avec une constante de temps de retard déterminée par la capacité répartie de ligne du bus B et par la valeur de la résistance de rappel Rb. La capacité des circuits d'entrée des circuits de charge du bus et les courants de sortie des circuits de charge du bus modifient également la constante, d'une valeur qui dépend du nombre de circuits de charge. Dans la pratique, la constante de temps de retard est en général d'environ 5 nano-secondes dans le cas d'un bus fonctionnant à une cadence d'horloge de 50 méga-hertz.

Cette constante de temps est compatible avec les valeurs habituelles de 5 à 10 nano-secondes de retard de fonctionnement de l'inverseur de validation 16 dans le sens du déblocage.

Le fonctionnement qui vient d'être décrit apparaît sur la figure 2, où chaque ligne indique la variation de niveau logique au point situé en aval de l'élément portant

la référence indiquée sur la ligne.

Les composants montrés en figure 1 peuvent avoir une constitution classique.

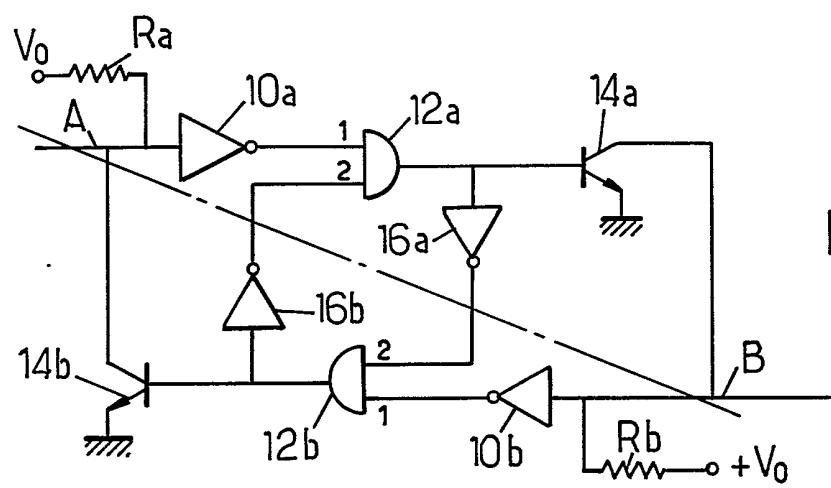

Chacun des amplificateurs inverseurs de sortie 14a

5 et 14b doit être choisi de façon que sa sortie puisse prendre uniquement les niveaux logiques 0 (tension de masse) et 1 (+ 5 volts). Cet amplificateur inverseur peut être constitué par un transistor dont l'émetteur est relié à la masse (figure 1). Il peut être constitué par un

10 circuit électronique à collecteur ouvert. Il peut être constitué par un circuit à trois états (niveaux logiques 1 et 0 à basse impédance et état à haute impédance). Il peut être constitué par un montage constitué d'un inverseur 18 de commande de commutation d'un amplificateur 20 (figure

15 3).

Chaque inverseur de validation 14a ou 14b peut également avoir diverses constitutions, permettant d'avoir deux constantes de temps différentes.

Il peut être constitué par un amplificateur inverseur à collecteur ouvert et résistance reliée à la source à + 5 volts pour ramener la sortie au niveau logique 1. Il peut être constitué par un circuit à trois états, encore avec résistance de rappel au niveau logique 1.

Il peut encore être constitué par un amplificateur inverseur 22 attaquant l'une des entrées d'une porte ET24 directement et l'autre entrée de la porte ET par l'intermédiaire d'éléments logiques en cascade 26 introduisant chacun un retard.

## REVENDICATIONS

1. Dispositif électronique d'extension de bus bidirectionnel, caractérisé en ce qu'il comprend deux ensembles symétriques de circuits électroniques, chaque ensemble comprenant :

- d'une part, disposés en série d'un bus vers l'autre, un amplificateur inverseur d'entrée (10a, 10b), une porte ET à deux entrées (12a, 12b) et un amplificateur inverseur de sortie (14a, 14b),

- et, d'autre part, un inverseur de validation (16a, 16b) dont l'entrée est reliée à la sortie de la porte ET et dont la sortie attaque la deuxième entrée de la porte ET de l'autre ensemble.

2. Dispositif selon la revendication 1, caractérisé en ce que l'inverseur de validation est prévu pour avoir une constante de temps de commutation vers l'état de blocage inférieure à sa constante de temps de commutation vers l'état de déblocage.

3. Dispositif selon la revendication 2, caractérisé en ce que les constantes de temps de blocage et de déblocage sont de 2 à 3 ns et de 5 à 10 ns, respectivement, pour une cadence de 50 MHz.

4. Dispositif selon la revendication 1, 2 ou 3, caractérisé en ce que l'amplificateur inverseur de sortie est constitué par un transistor monté en commutateur dont la liaison émetteur-collecteur est montée entre le bus respectif et une tension de référence, ou par un circuit à trois états muni d'une résistance de liaison avec une tension de référence égale à la tension de repos du bus.

5. Dispositif selon l'une quelconque des revendications 1 à 4, caractérisé en ce que l'inverseur de validation est constitué par un amplificateur inverseur (22) attaquant une des entrées d'une porte ET (24) directement et l'autre entrée de la porte ET par l'intermédiaire de circuits de retard (26).

6. Dispositif selon l'une quelconque des revendications 1 à 4, caractérisé en ce que l'inverseur de validation est constitué par un amplificateur inverseur à collecteur ouvert ou un circuit à trois états avec résistance de rappel au niveau de repos.

FIG.1.

FIG.3.

FIG.4.

FIG.2.

INSTITUT NATIONAL

de la

PROPRIETE INDUSTRIELLE

## RAPPORT DE RECHERCHE

établi sur la base des dernières revendications

déposées avant le commencement de la recherche

N° d'enregistrement

nationalFR 9105762

FA 461025

| DOCUMENTS CONSIDERES COMME PERTINENTS                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                              | Revendications concernées de la demande examinée |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Catégorie                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                              |                                                  |

| X                                                                                                                                                                                                                                                                                                                                            | US-A-4 154 978 (TU)<br>* colonne 1, ligne 12 - ligne 43 *<br>* colonne 4, ligne 56 - colonne 5, ligne 32 *<br>* colonne 7, ligne 35 - ligne 42 *<br>* colonne 7, ligne 59 - colonne 8, ligne 41 *<br>* colonne 9, ligne 5 - ligne 15 *<br>* figures 1,5,7 *  | 1-3,5-6<br>4                                     |

| X                                                                                                                                                                                                                                                                                                                                            | EDN ELECTRICAL DESIGN NEWS.<br>vol. 24, no. 2, Janvier 1979, NEWTON,<br>MASSACHUSETTS US<br>pages 106 - 108;<br>L.W. BERKBIGLER: 'Simplify mini or uC bus<br>extensions'<br>* page 106, colonne de droite - page 108,<br>colonne de droite *<br>* figure 2 * | 1-3,5                                            |

| A                                                                                                                                                                                                                                                                                                                                            | PATENT ABSTRACTS OF JAPAN<br>vol. 9, no. 318 (E-366)(2041) 13 Décembre 1985<br>& JP-A-60 152 153 ( SEIICHI MIYAZAKI ) 10 Août<br>1985<br>* abrégé *                                                                                                          | 4,6                                              |

| X                                                                                                                                                                                                                                                                                                                                            | PATENT ABSTRACTS OF JAPAN<br>vol. 9, no. 318 (E-366)(2041) 13 Décembre 1985<br>& JP-A-60 152 153 ( SEIICHI MIYAZAKI ) 10 Août<br>1985<br>* abrégé *                                                                                                          | 1                                                |

| A                                                                                                                                                                                                                                                                                                                                            | -----                                                                                                                                                                                                                                                        | 2-6                                              |

|                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                              | DOMAINES TECHNIQUES<br>RECHERCHES (Int. CL.5)    |

|                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                              | G06F<br>H04L                                     |

| Date d'achèvement de la recherche                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                              | Examinateur                                      |

| 18 DECEMBRE 1991                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                              | NGUYEN XUAN HIEP C.                              |

| CATEGORIE DES DOCUMENTS CITES                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                              |                                                  |

| X : particulièrement pertinent à lui seul<br>Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie<br>A : pertinent à l'encontre d'au moins une revendication ou arrière-plan technologique général<br>O : divulgation non-écrite<br>P : document intercalaire                                           |                                                                                                                                                                                                                                                              |                                                  |

| T : théorie ou principe à la base de l'invention<br>E : document de brevet bénéficiant d'une date antérieure à la date de dépôt et qui n'a été publié qu'à cette date de dépôt ou qu'à une date postérieure.<br>D : cité dans la demande<br>L : cité pour d'autres raisons<br>.....<br>& : membre de la même famille, document correspondant |                                                                                                                                                                                                                                                              |                                                  |