(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5121103号

(P5121103)

(45) 発行日 平成25年1月16日(2013.1.16)

(24) 登録日 平成24年11月2日(2012.11.2)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 21/336 | (2006.01) |

| HO 1 L 29/786 | (2006.01) |

| GO 2 F 1/1368 | (2006.01) |

| GO 9 F 9/30   | (2006.01) |

| HO 1 L 27/00  | (2006.01) |

| HO 1 L        | 29/78     |

| GO 2 F        | 1/1368    |

| GO 9 F        | 9/30      |

| HO 1 L        | 27/00     |

|               | 6 2 7 D   |

|               | 6 1 3 Z   |

|               | 3 3 8     |

|               | 3 0 1 B   |

請求項の数 11 (全 37 頁) 最終頁に続く

|              |                               |                 |           |

|--------------|-------------------------------|-----------------|-----------|

| (21) 出願番号    | 特願2001-276341 (P2001-276341)  | (73) 特許権者       | 000153878 |

| (22) 出願日     | 平成13年9月12日 (2001.9.12)        | 株式会社半導体エネルギー研究所 |           |

| (65) 公開番号    | 特開2002-164354 (P2002-164354A) | 神奈川県厚木市長谷398番地  |           |

| (43) 公開日     | 平成14年6月7日 (2002.6.7)          | (72) 発明者        | 石川 明      |

| 審査請求日        | 平成20年7月9日 (2008.7.9)          | 神奈川県厚木市長谷398番地  | 株式会社      |

| (31) 優先権主張番号 | 特願2000-280864 (P2000-280864)  | 半導体エネルギー研究所内    |           |

| (32) 優先日     | 平成12年9月14日 (2000.9.14)        | 審査官             | 綿引 隆      |

| (33) 優先権主張国  | 日本国 (JP)                      |                 |           |

| (31) 優先権主張番号 | 特願2000-280902 (P2000-280902)  |                 |           |

| (32) 優先日     | 平成12年9月14日 (2000.9.14)        |                 |           |

| (33) 優先権主張国  | 日本国 (JP)                      |                 |           |

最終頁に続く

(54) 【発明の名称】半導体装置、半導体装置の作製方法及び電気器具

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の基板上にエッティングストッパーとしての機能を有する第1の膜を形成し、前記第1の膜上に第1の絶縁膜を形成し、前記第1の絶縁膜上に半導体膜を形成し、前記半導体膜上にゲート絶縁膜を形成し、前記ゲート絶縁膜上にゲート電極を形成し、前記ゲート電極上に第2の絶縁膜を形成し、前記第2の絶縁膜及び前記ゲート絶縁膜に前記半導体膜に達する第1の開孔部を形成し、

前記第1の開孔部を介して前記半導体膜に接する第1の電極を形成し、

前記第1の電極上に第3の絶縁膜を形成し、

前記第1の基板に第2の基板を貼り合わせ、

前記第1の基板を研磨した後にエッティングすることにより、前記第1の基板を取り除き、

前記第1の膜を取り除き、

前記前記第1の絶縁膜に前記半導体膜に達する第2の開孔部を形成し、

前記第2の開孔部を介して前記半導体膜に接する第2の電極を形成することを特徴とする半導体装置の作製方法。

## 【請求項 2】

10

20

第1の基板上にエッティングストッパーとしての機能を有する第1の膜を形成し、

前記第1の膜上に第1の絶縁膜を形成し、

前記第1の絶縁膜上に半導体膜を形成し、

前記半導体膜上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上にゲート電極を形成し、

前記ゲート電極上に第2の絶縁膜を形成し、

前記第2の絶縁膜及び前記ゲート絶縁膜に前記半導体膜に達する第1の開孔部を形成し

、前記第2の絶縁膜及び前記ゲート絶縁膜に前記第1の膜に達する第3の開孔部を形成し

、前記第1の開孔部を介して前記半導体膜に接し、且つ前記第3の開孔部を介して前記第1の膜に接する第1の電極を形成し、

前記第1の電極上に第3の絶縁膜を形成し、

前記第1の基板に第2の基板を貼り合わせ、

前記第1の基板を研磨した後にエッティングすることにより、前記第1の基板を取り除き

、前記第1の膜を取り除き、

前記前記第1の絶縁膜に前記第3の開孔部に形成された前記第1の電極に達する第2の開孔部を形成し、

前記第2の開孔部を介して前記第3の開孔部に形成された前記第1の電極に接する第2の電極を形成することを特徴とする半導体装置の作製方法。

#### 【請求項3】

請求項1又は請求項2において、

前記第1の基板を研磨した後にエッティングすることにより、前記第1の基板を一部を残して取り除くことを特徴とする半導体装置の作製方法。

#### 【請求項4】

請求項1乃至3のいずれか一項において、

前記第2の基板は、接着材が塗布された領域と、粘着材が塗布された領域と、を有し、

前記第2の基板には、前記粘着材によって偏光フィルムが張り合わされていることを特徴とする半導体装置の作製方法。

#### 【請求項5】

請求項4において、

前記第2の電極を形成した後に、前記接着材が塗布された領域を切り離すように、前記半導体装置を切断することを特徴とする半導体装置の作製方法。

#### 【請求項6】

第1の薄膜デバイスと、

前記第1の薄膜デバイス上に形成された第2の薄膜デバイスと、

前記第2の薄膜デバイス上に形成された第3の薄膜デバイスと、を有し、

前記第1の薄膜デバイス、前記第2の薄膜デバイス及び前記第3の薄膜デバイスのそれぞれ、

第1の絶縁膜と、

前記第1の絶縁膜上に形成された第1の電極と、

前記第1の電極上に形成された第2の絶縁膜と、

前記第2の絶縁膜上に形成され、且つ前記第2の絶縁膜に形成された第1の開孔部を介して前記第1の電極と電気的に接続された第1の薄膜トランジスタ、及び前記第2の絶縁膜上に形成された第2の薄膜トランジスタと、

前記第1の薄膜トランジスタ及び前記第2の薄膜トランジスタ上に形成された第3の絶縁膜と、

前記第3の絶縁膜上に形成され、且つ前記第3の絶縁膜に形成された第2の開孔部を介して前記第2の薄膜トランジスタと電気的に接続された第2の電極と、

10

20

30

40

50

前記第3の絶縁膜及び前記第2の電極上に形成された第4の絶縁膜と、を有し、

前記第1の薄膜デバイスにおける前記第2の電極は、前記第2の薄膜デバイスにおける

前記第1の電極と電気的に接続され、

前記第2の薄膜デバイスにおける前記第2の電極は、前記第3の薄膜デバイスにおける

前記第1の電極と電気的に接続されることを特徴とする半導体装置。

#### 【請求項7】

請求項6において、

前記第1の薄膜デバイスにおける前記第2の電極と前記第2の薄膜デバイスにおける第

1の電極とは、前記第1の薄膜デバイスにおける前記第4の絶縁膜に形成された第3の開

孔部、及び前記第2の薄膜デバイスにおける前記第1の絶縁膜に設けられた第4の開孔部

に設けられた第1の導電性ペーストを介して電気的に接続されることを特徴とする半導体

装置。

10

#### 【請求項8】

請求項6又は請求項7において、

前記第2の薄膜デバイスにおける前記第2の電極と前記第3の薄膜デバイスにおける第

1の電極とは、前記第2の薄膜デバイスにおける前記第4の絶縁膜に形成された第5の開

孔部、及び前記第3の薄膜デバイスにおける前記第1の絶縁膜に設けられた第6の開孔部

に設けられた第2の導電性ペーストを介して電気的に接続されることを特徴とする半導体

装置。

20

#### 【請求項9】

請求項6乃至8のいずれか一において、

前記半導体装置はSOI構造の素子を用いた集積回路であることを特徴とする半導体裝

置。

20

#### 【請求項10】

請求項6乃至9のいずれか一に記載の半導体装置を表示部に用いた電気器具。

#### 【請求項11】

請求項10において、

前記電気器具は、ビデオカメラ、デジタルカメラ、プロジェクター、プロジェクション

TV、ヘッドマウントディスプレイ、ナビゲーションシステム、音響再生装置、ノート型

パソコンコンピュータ、ゲーム機器、携帯情報端末、モバイルコンピュータ、携帯電話

機、携帯型ゲーム機、電子書籍、または記録媒体を備えた画像再生装置であることを特徴

とする電気器具。

30

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

半導体装置の作製方法に関し、特に、薄くてフレキシブルな（可撓性を有する）半導体裝

置を作製する方法に関する。また、異なる層に絶縁膜を介して形成された配線間に生じる

寄生容量を低減する方法に関する。なお、本明細書において半導体装置とは、半導体特性

を利用することで機能する装置全般を指し、特に本発明は、絶縁体上に半導体層を形成した

SOI（Silicon On Insulator）構造の素子を用いた集積回路、

薄膜トランジスタ（TFT）を用いて構成されたアクティブマトリクス型液晶表示装置、

アクティブマトリクス型EL表示装置等に好適に適用できる。ここで、本明細書において

、薄膜デバイスとは、半導体薄膜を用いて構成した薄膜トランジスタ（TFT）および配

線、導電層、抵抗もしくは容量素子等のうち、少なくとも1つを含む電子デバイスのこと

を指す。

40

##### 【0002】

##### 【従来の技術】

半導体装置の一つとして、絶縁体上に半導体層を形成したSOI構造の素子を用いた集積

回路がある。半導体層が絶縁体上に形成されているため、寄生容量が少なく、高速動作が

可能である。

50

**【 0 0 0 3 】**

半導体装置の一つとして、アクティブマトリクス型液晶表示装置がある。アクティブマトリクス型液晶表示装置は、画素のスイッチング素子として用いられる薄膜トランジスタ（TFT）を形成した基板（TFT形成基板）と、対向電極を形成した基板（対向基板）とを貼り合わせ、間隙に液晶を注入した構造が主流である。このアクティブマトリクス型液晶表示装置は、ガラス等の透明基板上に形成されたTFTにより、液晶へ印加する電圧を1画素ごとに制御できるため、画像が鮮明であり、OA機器やTV等に広く用いられている。

**【 0 0 0 4 】**

また、半導体装置の一つとして、アクティブマトリクス型EL表示装置が知られている。

アクティブマトリクス型EL表示装置は、2枚の電極の間にEL材料を挟みこんだ構造をしており、電流を流して発光させる。複数個の画素トランジスタを用いて、EL材料に流す電流を一画素ごとに制御できるため、画像が鮮明である。

10

**【 0 0 0 5 】**

これらの半導体装置は、ますます微細化され集積度が向上されている。半導体装置の配線間に生じる寄生容量は、電気信号に伝播遅延を引き起こし、電気回路の高速動作や電気信号の正確な伝播を妨げる原因となっている。配線間に生じる寄生容量は、同じ層に形成された配線間に生じるものと、異なる層に絶縁膜を介して形成された配線間に生じるものとがある。

**【 0 0 0 6 】**

20

集積度が向上すると、同じ層に形成された配線間の距離は小さくなり、寄生容量が増える。同じ層に形成された配線間の寄生容量を減らすには、配線を異なる層に移動させればよい。つまり、多層配線化して同じ層の配線の集積度を下げる。そうすると、異なる層に絶縁膜を介して形成された配線間に生じる寄生容量を減らすことは、半導体装置全体の集積度の向上に寄与することになる。

**【 0 0 0 7 】**

そこで、異なる層に絶縁膜を介して形成された配線間に生じる寄生容量を低減するために、絶縁膜を厚くして配線間の距離を大きくとる、誘電率の低い絶縁膜を使う、等の方法がとられてきた。しかし、絶縁膜を厚くすると、配線間に導通をとるために絶縁膜にあける開孔部が開けにくくなるだけでなく、例えば、スパッタで形成する導電層が開孔部の内部において断線する、もしくは十分な膜厚が確保できないため、抵抗が大きくなる、等の問題が起こる場合がある。また、誘電率の低い絶縁膜は、耐熱性や透水性等の膜質に関する問題、エッチングによる寸法変化等の加工上の問題が生じる可能性がある。例えば、厚さ1μmのアクリルの場合、エッチング条件にもよるが、穴径が約1μm大きくなることもあり、半導体装置全体の集積度を向上する上で障害となる場合がある。

30

**【 0 0 0 8 】**

また、配線を形成する導電層の形成順序を変える方法もある。ここで、素子間の導通をとる配線を二層有する集積回路をトップゲート型トランジスタで構成する場合、成膜順に述べると、通常次のような構成になる。活性層、第一の絶縁膜（ゲート絶縁膜）、第一の導電層（ゲート電極）、第二の絶縁膜（第一層間絶縁膜）、第二の導電層（第一配線）、第三の絶縁膜（第二層間絶縁膜）、第三の導電層（第二配線）。

40

**【 0 0 0 9 】**

それを変えて、第一の導電層（第二配線）、第一の絶縁膜（下部絶縁膜）、活性層、第二の絶縁膜（ゲート絶縁膜）、第二の導電層（ゲート電極）、第三の絶縁膜（第一層間絶縁膜）、第三の導電層（第一配線）、と構成すると、第一配線と第二配線の間の距離が大きくなり、その間に形成される寄生容量を少なくすることができる。

**【 0 0 1 0 】**

この場合、第一配線と第二配線の距離は大きくなるが、例えば、活性層を介することで、開孔、導通の問題は回避できる。しかし、同じ第二配線でも、後者の場合、後で形成する活性層の成膜温度や注入した不純物の熱活性化温度に耐えられるものを使用しなければな

50

らず、前者の場合と後者の場合で必ずしも同じ材料を使うことができない。例えば、A1は抵抗率の低い配線材料としてよく用いられるが、耐熱性が低いので、後者の場合には使えない。

#### 【0011】

なお、本明細書中において「電極」とは「配線」の一部であり、説明の便宜上、「配線」と「電極」とを使い分けるが、「電極」という言葉に「配線」は常に含められているものとする。

#### 【0012】

##### 【発明が解決しようとする課題】

上記したような半導体装置は近年、携帯機器等に用いられ、薄型化、軽量化、フレキシビリティ（可撓性）が求められている。半導体装置の厚さの大部分は基板の厚さであり、薄型化、軽量化するには、基板を薄くすればよい。しかし、基板を薄くすれば、作製時に基板がそって写真製版工程でのトラブル原因になる他、基板搬送時に基板割れが起こりやすくなるなど、作製が困難である。そこで、透明なプラスチック基板等の上に半導体装置を作製できれば、軽くてフレキシブルな表示装置を作製できるが、プラスチック基板の耐熱性等の問題でまだ実現していない。

#### 【0013】

また、異なる層に絶縁膜を介して形成された配線間に生じる寄生容量を低減し、A1等、耐熱性が低くて使えなかった配線材料を使えるように、電気回路の高速動作や電気信号の正確な伝播を行えるようにする。

#### 【0014】

##### 【課題を解決するための手段】

そこで、本発明者は、作製時には十分な耐熱性、強度を持った基板上に薄膜デバイスを作製し、前記基板を取り除く方法を考えた。まず、第一の基板に薄膜デバイスを形成し、第二の基板に接着する。この状態で第一の基板と第二の基板の間に薄膜デバイスが存在する。そして、第二の基板に保持された状態で、薄膜デバイスを残して第一の基板を取り除き、第二の基板に保持された薄膜デバイスに到達する開孔部を設け、前記開孔部を介して前記薄膜デバイスに接するように導電層を形成するなど必要な加工を行ってから、第二の基板も取り除く。

#### 【0015】

さらに本発明においては、薄膜デバイスが形成されていない領域の一部に接着材を塗布することで、第一の基板と第二の基板を接着することを特徴としている。もしくは、薄膜デバイスが形成されていない領域の一部に接着材を塗布し、それ以外の部分は粘着材等を用いて仮止めしておく。こうすることによって、第二の基板は接着部分を切りはなす事によって、簡単に取り除くことができる。

#### 【0016】

前記作製方法を用いると、作製時には必ずどちらかの基板に保持されているが、最終的にはどちらの基板も剥離するので、第一の基板および第二の基板は厚くてもよく、十分な強度の基板が使える。それゆえ、基板がそったり、基板割れが生じたりすることが少なく、作製が容易である。

#### 【0017】

また、アクティブマトリクス型液晶表示装置、アクティブマトリクス型EL表示装置等、表示装置においては基板搬送時に基板裏面につくキズが表示品位を落とす原因となり、問題となっている。前記作製方法を用いると、作製時に支持していた基板を取り除くので、この問題も解決される。

#### 【0018】

さらに、前記作製方法を用いると、薄膜デバイスの表裏両面に出力電極を形成することができる。それらを重ね合わせると、3次元実装などの応用にも使える。

#### 【0019】

また他の発明は、活性層、第一の絶縁膜（ゲート絶縁膜）、第一の導電層（ゲート電極）

10

20

30

40

50

、第二の絶縁膜（第一層間絶縁膜）、第二の導電層（第一配線）、の順に形成した後、第二配線を活性層に対して第一配線と反対側に形成しようとするものである。つまり、第一の導電層（第二配線）、第一の絶縁膜（下部絶縁膜）、活性層、第二の絶縁膜（ゲート絶縁膜）、第二の導電層（ゲート電極）、第三の絶縁膜（第一層間絶縁膜）、第三の導電層（第一配線）、という構造を実現しようとするものである。なお、本明細書において、活性層とは、チャネル領域、ソース領域およびドレイン領域を含む半導体膜からなる層を指すこととする。

#### 【0020】

そうすると、第一配線と第二配線の間に形成される寄生容量を少なくでき、また、活性層を形成した後で配線を形成するので、耐熱性の低い材料でも配線として使うことが出来る。

10

。

#### 【0021】

このような構造を実現するために、本発明では基板を二枚使う。一枚目の基板上に薄膜デバイスを形成し、薄膜デバイスを形成した面と二枚目の基板を接着する。二枚目の基板に支持された状態で、機械研磨や化学研磨等を用いて、一枚目の基板を取り除く。一枚目の基板を取り除くと、薄膜デバイスの裏面が表に出てくるので、配線を形成する。このようにして、活性層の上下に配線を形成することができる。もちろん、一枚目の基板上にトランジスタを形成する場合、ボトムゲート型トランジスタの場合も、トップゲート型トランジスタの場合と同様に構成することができる。なお、本明細書において、ボトムゲート型薄膜トランジスタとは、図27に示すような、ゲート電極と配線との間に層に活性層が形成されている形状の薄膜トランジスタのことを指すこととする。

20

#### 【0022】

また、本発明の作製方法を用いれば、一枚目の基板上にトップゲート型トランジスタを形成し、その活性層の下側にのみ配線を形成することで、一枚目の基板を除去した後にボトムゲート型トランジスタとなるトランジスタを構成することができる。この場合、活性層の下側に形成した第一配線とゲート配線との寄生容量を低くすることができる。さらに、従来のボトムゲート型トランジスタではできなかったことだが、ゲート電極を用いてセルファーラインで不純物を打ち込むこともできる。

#### 【0023】

本発明は、第一の基板上に薄膜デバイスを形成する工程と、前記第一の基板の薄膜デバイスを形成した面と第二の基板とを接着する工程と、前記薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された薄膜デバイスに到達する開孔部を設ける工程と、前記薄膜デバイスと前記第二の基板の接着部分を取り除くように、前記第二の基板を切断し、前記第二の基板を取り除く工程と、を有することを特徴としている半導体装置の作製方法である。

30

#### 【0024】

また、本発明は、第一の基板上に薄膜デバイスを形成する工程と、前記第一の基板の薄膜デバイスを形成した面と第二の基板とを接着する工程と、前記薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された薄膜デバイスに到達する開孔部を設け、前記開孔部を介して前記薄膜デバイスに接する少なくとも一層の導電層を形成する工程と、前記薄膜デバイスと前記第二の基板の接着部分を取り除くように、前記第二の基板を切断し、前記第二の基板を取り除く工程と、を有することを特徴としている半導体装置の作製方法である。

40

#### 【0025】

また、本発明は、第一の基板上に薄膜デバイスを形成する工程と、少なくとも2種類以上の接着材を、前記薄膜デバイスが形成された領域と前記領域以外の領域で塗り分け、前記第一の基板の薄膜デバイスを形成した面と、第二の基板を接着する工程と、前記薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された薄膜デバイスに到達する開孔部を設ける工程と、前記接着材が塗られた領域を取り除き前記第二の基板を切断する工程と、を有することを特徴としている半導体装置の作製方法である。

50

## 【0026】

また、本発明は、第一の基板の一方の面上に薄膜デバイスを形成する工程と、少なくとも2種類以上の接着材を、前記薄膜デバイスが形成された領域と前記領域以外の領域で塗りわけ、前記第一の基板の薄膜デバイスを形成した面と、第二の基板を接着する工程と、前記薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された薄膜デバイスに到達する開孔部を形成し、前記開孔部を介して前記薄膜デバイスに接する少なくとも一層の導電層を形成する工程と、前記接着材が塗られた領域を取り除き、前記第二の基板を切断する工程と、を有することを特徴としている半導体装置の作製方法である。

## 【0027】

また、本発明は、第一の基板の一方の面上に第一の薄膜デバイスを形成する工程と、薄膜または第二の薄膜デバイスを第二の基板に部分的に接着する工程と、前記第一の基板の第一の薄膜デバイスを形成した面と、前記薄膜または第二の薄膜デバイスの第二の基板と接着した面とは反対側の面とを、接着する工程と、前記第一の薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された第一の薄膜デバイスに、開孔部を設ける工程と、前記薄膜または第二の薄膜デバイスと前記第二の基板の接着部分を取り除くように、前記第二の基板を切断し、前記薄膜または第二の薄膜デバイスを残して前記第二の基板のみを取り除く工程と、を有することを特徴としている半導体装置の作製方法である。

## 【0028】

また、本発明は、第一の基板の一方の面上に第一の薄膜デバイスを形成する工程と、薄膜または第二の薄膜デバイスを第二の基板に部分的に接着する工程と、前記第一の基板の第一の薄膜デバイスを形成した面と、前記薄膜または第二の薄膜デバイスの第二の基板と接着した面とは反対側の面とを、接着する工程と、前記第一の薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された第一の薄膜デバイスに、少なくとも一層の導電層を形成する工程と、前記薄膜または第二の薄膜デバイスと前記第二の基板の接着部分を取り除くように、前記第二の基板を切断し、前記薄膜または第二の薄膜デバイスを残して前記第二の基板のみを取り除く工程と、を有することを特徴としている半導体装置の作製方法である。

## 【0029】

また、本発明は、第一の基板の一方の面上に第一の薄膜デバイスを形成する工程と、少なくとも2種類以上の接着材を、前記薄膜デバイスが存在する場所と存在しない場所で塗り分けて、薄膜または第二の薄膜デバイスを第二の基板に接着する工程と、前記第一の基板の第一の薄膜デバイスを形成した面と、前記薄膜または第二の薄膜デバイスの第二の基板と接着した面とは反対側の面とを、接着する工程と、前記第一の薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された第一の薄膜デバイスに、開孔部を設ける工程と、前記薄膜または第二の薄膜デバイスと前記第二の基板の一部を取り除くように、前記第二の基板を切断し、前記薄膜または第二の薄膜デバイスを残して前記第二の基板のみを取り除く工程と、を有することを特徴としている半導体装置の作製方法である。

## 【0030】

また、本発明は、第一の基板の一方の面上に第一の薄膜デバイスを形成する工程と、少なくとも2種類以上の接着材を、前記薄膜デバイスが存在する場所と存在しない場所で塗り分けて、薄膜または第二の薄膜デバイスを第二の基板に接着する工程と、前記第一の基板の第一の薄膜デバイスを形成した面と、前記薄膜または第二の薄膜デバイスの第二の基板と接着した面とは反対側の面とを、接着する工程と、前記第一の薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された第一の薄膜デバイスに、少なくとも一層の導電層を形成する工程と、前記薄膜または第二の薄膜デバイスと前記第二の基板の一部を取り除くように、前記第二の基板を切断し、前記薄膜または第二の薄膜デバイスを残して前記第二の基板のみを取り除く工程と、を有することを特徴としている

10

20

30

40

50

半導体装置の作製方法である。

【0031】

また、本発明は、第一の基板の一方の面上に第一の薄膜デバイスを形成する工程と、薄膜または第二の薄膜デバイスを第二の基板に部分的に接着する工程と、前記第一の基板の第一の薄膜デバイスを形成した面と、前記薄膜または第二の薄膜デバイスの第二の基板と接着した面とは反対側の面とを、接着する工程と、前記薄膜または第二の薄膜デバイスと前記第二の基板の接着部分を取り除くように、前記第二の基板を切断し、前記薄膜または第二の薄膜デバイスを残して前記第二の基板のみを取り除く工程と、を有することを特徴としている半導体装置の作製方法である。

【0032】

10

また、本発明は、第一の基板の一方の面上に第一の薄膜デバイスを形成する工程と、少なくとも2種類以上の接着材を、前記薄膜デバイスが存在する場所と存在しない場所で塗り分けて、薄膜または第二の薄膜デバイスを第二の基板に接着する工程と、前記第一の基板の第一の薄膜デバイスを形成した面と、前記薄膜または第二の薄膜デバイスの第二の基板と接着した面とは反対側の面とを、接着する工程と、前記薄膜または第二の薄膜デバイスと前記第二の基板の一部を取り除くように、前記第二の基板を切断し、前記薄膜または第二の薄膜デバイスを残して前記第二の基板のみを取り除く工程と、を有することを特徴としている半導体装置の作製方法である。

【0033】

20

また、上記発明において、半導体装置とはアクティブマトリクス型液晶表示装置であることを特徴としている。

【0034】

また、上記発明において、半導体装置とはアクティブマトリクス型EL表示装置であることを特徴としている。

【0035】

また、本発明は上記記載の作製方法を用いて作製された半導体装置であることを特徴としている。

【0036】

30

また、本発明は、第一の基板の一方の面上に第一の薄膜デバイスを形成する工程と、薄膜または第二の薄膜デバイスを第二の基板に部分的に接着する工程と、前記第一の基板に形成した第一の薄膜デバイスと前記第二の基板に接着した薄膜または第二の薄膜デバイスの間に液晶を封入する工程と、前記第一の基板と前記第一の薄膜デバイスと前記第二の基板と前記薄膜または第二の薄膜デバイスの一部を取り除くように、前記第一の基板と前記第一の薄膜デバイスと前記第二の基板と前記薄膜または第二の薄膜デバイスを切断し、前記薄膜または第二の薄膜デバイスを残して前記第二の基板を取り除く工程と、を有することを特徴としている半導体装置の作製方法である。

【0037】

また、本発明は、第一の基板の一方の面上に第一の薄膜デバイスを形成する工程と、少なくとも2種類以上の接着材を、前記薄膜デバイスが存在する場所と存在しない場所で塗り分けて、薄膜または第二の薄膜デバイスを第二の基板に接着する工程と、前記第一の基板に形成した第一の薄膜デバイスと前記第二の基板に接着した薄膜または第二の薄膜デバイスの間に液晶を封入する工程と、前記第一の基板と前記第一の薄膜デバイスと前記第二の基板と前記薄膜または第二の薄膜デバイスの一部を取り除くように、前記第一の基板と前記第一の薄膜デバイスと前記第二の基板と前記薄膜または第二の薄膜デバイスを切断し、前記薄膜または第二の薄膜デバイスを残して前記第二の基板を取り除く工程と、を有することを特徴としている半導体装置の作製方法である。

【0038】

40

また、上記発明において、前記第二の基板を取り除く工程の前に、第二の薄膜または第三の薄膜デバイスを第三の基板に部分的に接着する工程と、前記第二の基板に接着した第一の薄膜デバイスと前記第三の基板に接着した第二の薄膜または第三の薄膜デバイスの間に

50

液晶を封入する工程と、前記第二の基板と前記第三の基板の一部を取り除くように、前記第二の基板と前記第三の基板を切断し、前記薄膜または第二の薄膜デバイスを残して前記第二の基板を取り除く工程と、前記第二の薄膜または第三の薄膜デバイスを残して前記第三の基板を取り除く工程と、を有することを特徴としている半導体装置の作製方法である。

#### 【 0 0 3 9 】

また、上記発明において、前記第二の基板を取り除く工程の前に、少なくとも 2 種類以上の接着材を、前記薄膜デバイスが存在する場所と存在しない場所で塗り分けて、第二の薄膜または第三の薄膜デバイスを第三の基板に接着する工程と、前記第二の基板に接着した第一の薄膜デバイスと前記第三の基板に接着した第二の薄膜または第三の薄膜デバイスの間に液晶を封入する工程と、前記第二の基板と前記第三の基板の一部を取り除くように、前記第二の基板と前記第三の基板を切断し、前記薄膜または第二の薄膜デバイスを残して前記第二の基板を取り除く工程と、前記第二の薄膜または第三の薄膜デバイスを残して前記第三の基板を取り除く工程と、を有することを特徴としている半導体装置の作製方法である。

10

#### 【 0 0 4 0 】

また、本発明は、第一の基板の一方の面上に薄膜デバイスを形成する工程と、偏光フィルムまたは偏光板を第二の基板に部分的に接着する工程と、前記第一の基板の薄膜デバイスを形成した面と、前記偏光フィルムまたは偏光板の第二の基板と接着した面とは反対側の面とを、接着する工程と、前記薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された薄膜デバイスに、開孔部を設ける工程と、前記偏光フィルムまたは偏光板と前記第二の基板の接着部分を取り除くように、前記第二の基板を切断し、前記偏光フィルムまたは偏光板を残して前記第二の基板のみを取り除く工程と、を有することを特徴としている半導体装置の作製方法である。

20

#### 【 0 0 4 1 】

また、本発明は、第一の基板の一方の面上に薄膜デバイスを形成する工程と、偏光フィルムまたは偏光板を第二の基板に部分的に接着する工程と、前記第一の基板の薄膜デバイスを形成した面と、前記偏光フィルムまたは偏光板の第二の基板と接着した面とは反対側の面とを、接着する工程と、前記薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された薄膜デバイスに、少なくとも一層の導電層を形成する工程と、前記偏光フィルムまたは偏光板と前記第二の基板の接着部分を取り除くように、前記第二の基板を切断し、前記偏光フィルムまたは偏光板を残して前記第二の基板のみを取り除く工程と、を有することを特徴としている半導体装置の作製方法である。

30

#### 【 0 0 4 2 】

また、本発明は、第一の基板の一方の面上に薄膜デバイスを形成する工程と、少なくとも 2 種類以上の接着材を、前記薄膜デバイスが存在する場所と存在しない場所で塗り分けて、偏光フィルムまたは偏光板を第二の基板に接着する工程と、前記第一の基板の薄膜デバイスを形成した面と、前記偏光フィルムまたは偏光板の第二の基板と接着した面とは反対側の面とを、接着する工程と、前記薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された薄膜デバイスに、開孔部を設ける工程と、前記偏光フィルムまたは偏光板と前記第二の基板の一部を取り除くように、前記第二の基板を切断し、前記偏光フィルムまたは偏光板を残して前記第二の基板のみを取り除く工程と、を有することを特徴としている半導体装置の作製方法である。

40

#### 【 0 0 4 3 】

また、本発明は、第一の基板の一方の面上に薄膜デバイスを形成する工程と、少なくとも 2 種類以上の接着材を、前記薄膜デバイスが存在する場所と存在しない場所で塗り分けて、偏光フィルムまたは偏光板を第二の基板に接着する工程と、前記第一の基板の薄膜デバイスを形成した面と、前記偏光フィルムまたは偏光板の第二の基板と接着した面とは反対側の面とを、接着する工程と、前記薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された薄膜デバイスに、少なくとも一層の導電層を形成する

50

工程と、前記偏光フィルムまたは偏光板と前記第二の基板の一部を取り除くように、前記第二の基板を切断し、前記偏光フィルムまたは偏光板を残して前記第二の基板のみを取り除く工程と、を有することを特徴としている半導体装置の作製方法である。

【0044】

また、上記発明において、前記第一の基板を取り除く工程において、前記第一の基板の一部を残し、液晶表示装置のスペーサーとして用いることを特徴としている。

【0045】

また、上記発明に記載された作製方法を用いて作製されたアクティブマトリクス型液晶表示装置であることを特徴としている。

【0046】

また、上記発明に記載された作製方法を用いて作製されたアクティブマトリクス型EL表示装置であることを特徴としている。

10

【0047】

また、本発明は、第一の基板の一方の面上に薄膜デバイスを形成する工程と、前記薄膜デバイス上に電極を形成する工程と、前記第一の基板の薄膜デバイスを形成した面と、第二の基板を部分的に接着する工程と、前記薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された薄膜デバイスに、開孔部を設ける工程と、前記薄膜デバイスと前記第二の基板の接着部分を取り除くように、前記第二の基板を切断し、前記第二の基板を取り除く工程と、前記複数の工程によって得られる薄膜デバイスを複数形成して重ね合わせ、前記薄膜デバイスの上下に形成された電極に導通をとる工程と、を有することを特徴としている半導体装置の作製方法である。

20

【0048】

また、本発明は、第一の基板の一方の面上に薄膜デバイスを形成する工程と、前記薄膜デバイス上に電極を形成する工程と、前記第一の基板の薄膜デバイスを形成した面と、第二の基板を部分的に接着する工程と、前記薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された薄膜デバイスに、開孔部を設け、少なくとも一層の導電層を形成して電極を形成する工程と、前記薄膜デバイスと前記第二の基板の接着部分を取り除くように、前記第二の基板を切断し、前記第二の基板を取り除く工程と、前記複数の工程によって得られる薄膜デバイスを複数形成して重ね合わせ、前記薄膜デバイスの上下に形成された電極に導通をとる工程と、を有することを特徴としている半導体装置の作製方法である。

30

【0049】

また、本発明は、第一の基板の一方の面上に薄膜デバイスを形成する工程と、前記薄膜デバイス上に電極を形成する工程と、少なくとも2種類以上の接着材を、前記薄膜デバイスが存在する場所と存在しない場所で塗り分けて、前記第一の基板の薄膜デバイスを形成した面と、第二の基板を接着する工程と、前記薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された薄膜デバイスに、開孔部を設ける工程と、前記薄膜デバイスと前記第二の基板の一部を取り除くように、前記第二の基板を切断し、前記第二の基板を取り除く工程と、前記複数の工程によって得られる薄膜デバイスを複数形成して重ね合わせ、前記薄膜デバイスの上下に形成された電極に導通をとる工程と、を有することを特徴としている半導体装置の作製方法である。

40

【0050】

また、本発明は、第一の基板の一方の面上に薄膜デバイスを形成する工程と、前記薄膜デバイス上に電極を形成する工程と、少なくとも2種類以上の接着材を、前記薄膜デバイスが存在する場所と存在しない場所で塗り分けて、前記第一の基板の薄膜デバイスを形成した面と、第二の基板を接着する工程と、前記薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された薄膜デバイスに、開孔部を設け、少なくとも一層の導電層を形成して電極を形成する工程と、前記薄膜デバイスと前記第二の基板の一部を取り除くように、前記第二の基板を切断し、前記第二の基板を取り除く工程と、前記複数の工程によって得られる薄膜デバイスを複数形成して重ね合わせ、前記薄膜デバイス

50

の上下に形成された電極に導通をとる工程と、を有することを特徴としている半導体装置の作製方法である。

【0051】

また、本発明は、第一の基板の一方の面上に第一の薄膜デバイスを形成する工程と、前記第一の薄膜デバイス上に電極を形成する工程と、開孔部を設けた薄膜または第二の薄膜デバイスを第二の基板に部分的に接着する工程、もしくは、薄膜または第二の薄膜デバイスを第二の基板に部分的に接着した後、前記薄膜または第二の薄膜デバイスに開孔部を設ける工程と、前記第一の基板の第一の薄膜デバイスを形成した面と、前記薄膜または第二の薄膜デバイスの第二の基板と接着した面とは反対側の面とを、接着する工程と、前記第一の薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された第一の薄膜デバイスに、開孔部を設ける工程と、前記薄膜または第二の薄膜デバイスと前記第二の基板の接着部分を取り除くように、前記第二の基板を切断し、前記薄膜または第二の薄膜デバイスを残して前記第二の基板のみを取り除く工程と、前記複数の工程によって得られる薄膜デバイスを複数形成して重ね合わせ、前記薄膜デバイスの上下に形成された電極に導通をとる工程と、を有することを特徴としている半導体装置の作製方法である。

10

【0052】

また、本発明は、第一の基板の一方の面上に第一の薄膜デバイスを形成する工程と、前記第一の薄膜デバイス上に電極を形成する工程と、開孔部を設けた薄膜または第二の薄膜デバイスを第二の基板に部分的に接着する工程、もしくは、薄膜または第二の薄膜デバイスを第二の基板に部分的に接着した後、前記薄膜または第二の薄膜デバイスに開孔部を設ける工程と、前記第一の基板の第一の薄膜デバイスを形成した面と、前記薄膜または第二の薄膜デバイスの第二の基板と接着した面とは反対側の面とを、接着する工程と、前記第一の薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された第一の薄膜デバイスに、開孔部を設け、少なくとも一層の導電層を形成して電極を形成する工程と、前記薄膜または第二の薄膜デバイスと前記第二の基板の接着部分を取り除くように、前記第二の基板を切断し、前記薄膜または第二の薄膜デバイスを残して前記第二の基板のみを取り除く工程と、前記複数の工程によって得られる薄膜デバイスを複数形成して重ね合わせ、前記薄膜デバイスの上下に形成された電極に導通をとる工程と、を有することを特徴としている半導体装置の作製方法である。

20

【0053】

また、本発明は、第一の基板の一方の面上に第一の薄膜デバイスを形成する工程と、前記第一の薄膜デバイス上に電極を形成する工程と、少なくとも2種類以上の接着材を、前記薄膜デバイスが存在する場所と存在しない場所で塗り分けて、開孔部を設けた薄膜または第二の薄膜デバイスを第二の基板に接着する工程、もしくは、少なくとも2種類以上の接着材を、前記薄膜デバイスが存在する場所と存在しない場所で塗り分けて、薄膜または第二の薄膜デバイスを第二の基板に接着した後、前記薄膜または第二の薄膜デバイスに開孔部を設ける工程と、前記第一の基板の第一の薄膜デバイスを形成した面と、前記薄膜または第二の薄膜デバイスの第二の基板と接着した面とは反対側の面とを、接着する工程と、前記第一の薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された第一の薄膜デバイスに、開孔部を設ける工程と、前記薄膜または第二の薄膜デバイスと前記第二の基板の一部を取り除くように、前記第二の基板を切断し、前記薄膜または第二の薄膜デバイスを残して前記第二の基板のみを取り除く工程と、前記複数の工程によって得られる薄膜デバイスを複数形成して重ね合わせ、前記薄膜デバイスの上下に形成された電極に導通をとる工程と、を有することを特徴としている半導体装置の作製方法である。

30

【0054】

また、本発明は、第一の基板の一方の面上に第一の薄膜デバイスを形成する工程と、前記第一の薄膜デバイス上に電極を形成する工程と、少なくとも2種類以上の接着材を、前記薄膜デバイスが存在する場所と存在しない場所で塗り分けて、開孔部を設けた薄膜または第二の薄膜デバイスを第二の基板に接着する工程、もしくは、少なくとも2種類以上の接着材を、前記薄膜デバイスが存在する場所と存在しない場所で塗り分けて、薄膜または第二の薄膜デバイスを第二の基板に接着した後、前記薄膜または第二の薄膜デバイスに開孔部を設ける工程と、前記第一の基板の第一の薄膜デバイスを形成した面と、前記薄膜または第二の薄膜デバイスの第二の基板と接着した面とは反対側の面とを、接着する工程と、前記第一の薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された第一の薄膜デバイスに、開孔部を設ける工程と、前記薄膜または第二の薄膜デバイスと前記第二の基板の一部を取り除くように、前記第二の基板を切断し、前記薄膜または第二の薄膜デバイスを残して前記第二の基板のみを取り除く工程と、前記複数の工程によって得られる薄膜デバイスを複数形成して重ね合わせ、前記薄膜デバイスの上下に形成された電極に導通をとる工程と、を有することを特徴としている半導体装置の作製方法である。

40

50

第二の薄膜デバイスを第二の基板に接着する工程、もしくは、少なくとも 2 種類以上の接着材を、前記薄膜デバイスが存在する場所と存在しない場所で塗り分けて、薄膜または第二の薄膜デバイスを第二の基板に接着した後、前記薄膜または第二の薄膜デバイスに開孔部を設ける工程と、前記第一の基板の第一の薄膜デバイスを形成した面と、前記薄膜または第二の薄膜デバイスの第二の基板と接着した面とは反対側の面とを、接着する工程と、前記第一の薄膜デバイスを残して、前記第一の基板を取り除く工程と、前記第二の基板に保持された第一の薄膜デバイスに、開孔部を設け、少なくとも一層の導電層を形成して電極を形成する工程と、前記薄膜または第二の薄膜デバイスと前記第二の基板の一部を取り除くように、前記第二の基板を切断し、前記薄膜または第二の薄膜デバイスを残して前記第二の基板のみを取り除く工程と、前記複数の工程によって得られる薄膜デバイスを複数形成して重ね合わせ、前記薄膜デバイスの上下に形成された電極に導通をとる工程と、を有することを特徴としている半導体装置の作製方法である。 10

【 0 0 5 5 】

また、上記発明において記載された作製方法を用いて作製された半導体装置であることを特徴としている。

【 0 0 5 6 】

また、本発明は、第一の基板上に薄膜デバイスを形成する工程と、前記第一の基板の薄膜デバイスを形成した面を第二の基板に接着する工程と、前記第一の基板を取り除く工程と、前記第二の基板に保持された薄膜デバイスに、開孔部を設ける工程と、を有することを特徴としている半導体装置の作製方法である。 20

【 0 0 5 7 】

また、本発明は、第一の基板上に薄膜デバイスを形成する工程と、前記第一の基板の薄膜デバイスを形成した面を第二の基板に接着する工程と、前記第一の基板を取り除く工程と、前記第二の基板に保持された薄膜デバイスに、少なくとも一層の導電層を形成する工程と、を有することを特徴としている半導体装置の作製方法である。

【 0 0 5 8 】

また、上記発明において記載された半導体装置とは自発光型表示装置であることを特徴としている。

【 0 0 5 9 】

また、上記発明において記載された半導体装置とは透過型表示装置であることを特徴としている。 30

【 0 0 6 0 】

また、上記発明において記載された半導体装置とは反射型表示装置であることを特徴としている。

【 0 0 6 1 】

また、上記発明において記載された半導体装置とはアクティブマトリクス型液晶表示装置であることを特徴としている。

【 0 0 6 2 】

また、上記発明において記載された半導体装置とはアクティブマトリクス型 E L 表示装置であることを特徴としている。 40

【 0 0 6 3 】

また、上記発明において記載された半導体装置とは S O I ( S e m i c o n d u c t o r O n I n s u l a t o r ) 構造の素子を用いた集積回路であることを特徴としている。

【 0 0 6 4 】

また、本発明は、絶縁体上に形成された半導体を活性層に用い、活性層の上下それぞれに、少なくとも一層の導電層を、耐熱温度が 550 度以下の材料を使って形成することを特徴としている薄膜トランジスタである。

【 0 0 6 5 】

また、本発明は、絶縁体上に形成された半導体を活性層に用い、前記活性層上にゲート絶

50

縁膜を有し、前記ゲート絶縁膜上にゲート電極を有し、前記ゲート電極をマスクに不純物の添加を行い、前記活性層に対して前記ゲート電極と反対側に、耐熱温度が550度以下の材料を使った配線を有することを特徴としている薄膜トランジスタである。

【0066】

また、上記発明において記載された薄膜トランジスタを有する集積回路であることを特徴としている。

【0067】

また、本発明は、一対の偏光フィルムと、画素電極と、活性層、前記活性層に接するゲート絶縁膜および前記ゲート絶縁膜に接するゲート電極からなるTFTと、

前記活性層に前記ゲート電極側から接続された配線と、対向電極と、前記一対の偏光フィルムの間に形成された前記画素電極と、前記対向電極との間の液晶と、封止材と、配向膜と、を含むことを特徴としている半導体装置である。 10

【0068】

また、本発明は、一対の偏光フィルムと、第1絶縁膜に接する活性層、前記活性層に接するゲート絶縁膜および前記ゲート絶縁膜に接するゲート電極からなる薄膜トランジスタと、前記ゲート電極に接する第3絶縁膜と、前記第3絶縁膜に接するパッシベーション膜と、前記第3絶縁膜および前記ゲート絶縁膜に形成された開孔部を介して各薄膜トランジスタを電気的に接続する配線と、前記活性層の前記ゲート電極が形成された面の反対側の面に形成された画素電極と、前記画素電極に接して形成された配向膜と、前記一対の偏光フィルムの一方の偏光フィルムに形成された対向電極と、前記一対の偏光フィルムの間に形成された前記画素電極と、前記対向電極との間の液晶と、前記第1絶縁膜と一方の偏光フィルムとの間に設けられた封止材と、を含むことを特徴としている半導体装置である。 20

【0069】

また、上記発明において、前記活性層は、前記画素電極と前記ゲート電極との間の層に形成されていることを特徴としている半導体装置である。

【0070】

【発明の実施の形態】

(実施の形態1)

本発明を用いたアクティブマトリクス型液晶表示装置の作製方法を、図1～3を用いて説明する。 30

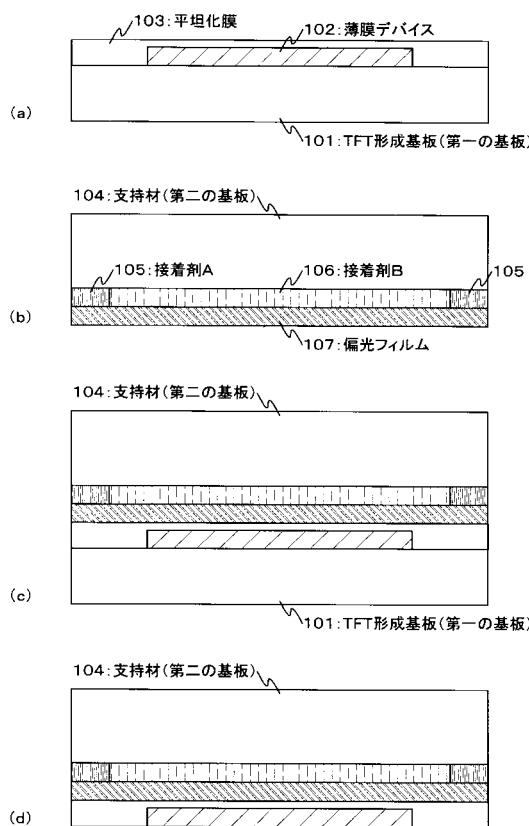

【0071】

まず、第一の基板としてTFT形成基板101上に薄膜デバイスを作製する(薄膜デバイス102となる)。平坦化膜103をつけて、第二の基板との接着面を平坦にしておくとよい(図1(a))。

【0072】

第二の基板として支持材104を用意し、偏光フィルム107を接着剤で貼り付けておく。なおここでは、2種類の接着剤を使い分けて接着する例を示す。接着剤A105は、後述するように第一の基板と第二の基板を貼り合わせた際に薄膜デバイス102の外側となる部分を接着し、接着剤B106は粘着材で支持材104を取り除くまでの間、偏光フィルムを仮止めする(図1(b))。 40

【0073】

もちろん、TFT形成基板101上の平坦化膜103上に偏光フィルムを貼り付けて、支持材104と接着してもよい。

【0074】

図1(c)で、薄膜デバイス102を介してTFT形成基板101上部に形成した平坦化基板103の縁辺と、支持材104の偏光フィルム107を貼り付けた面の縁辺とに接着材を塗布して、両方の基板を接着する。そして、バックグラインドやCMP等で第一の基板を取り除き、薄膜デバイス102を表面に出す(図1(d))。実際には、薄膜デバイス102の最下層に窒化膜等を用意しておき、研磨工程の最後にウエットエッティングを行い、そのストッパーとして用いるとよい。 50

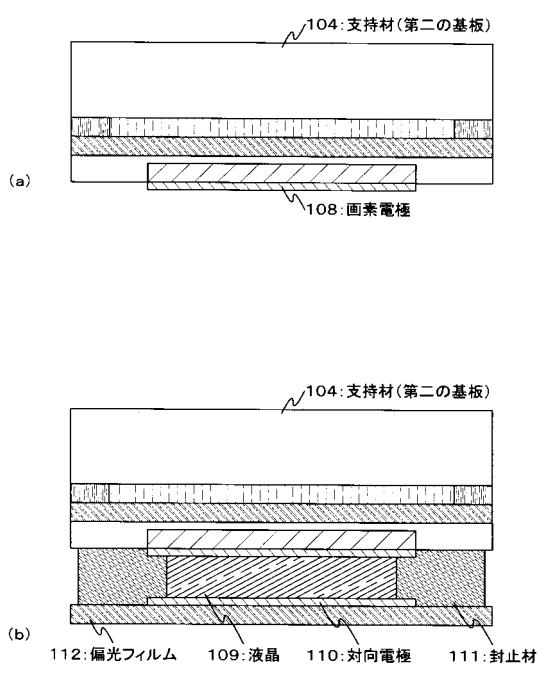

**【 0 0 7 5 】**

次に、支持材 104 に保持された薄膜デバイス 102 に、画素電極 108 を形成する（図 2（a））。偏光フィルム 112 に対向電極 110 をつけ、封止材 111 で液晶 109 を閉じこめる（図 2（b））。なお、偏光フィルムがたわむ場合は、もう一つ別の支持材を用意して、偏光フィルム 112 を支えてよい。

**【 0 0 7 6 】**

図 3（a）では、薄膜デバイス 102 の外側で接着剤 A105 を切り離せる場所で、基板を切断する。切断する事によって、接着剤 A105 が塗布された領域はなくなり、接着剤 B106 として粘着材が塗布された領域だけになるので（図 3（b））、支持材 104 を取り除く（図 3（c））。

10

**【 0 0 7 7 】**

このように、基板に固定した状態で作製し、最終的には基板を取り除くことによって、半導体装置にフレキシビリティ（可撓性）をもたせ、薄型化、軽量化することができる。なお、ここではアクティブマトリクス型液晶表示装置に関して示したので、基板を取り除いた後の表面には偏光フィルムが貼られているが、使用目的に応じて、表面保護のためのフィルム、支持材としてのフィルム等を自由に組み合わせて、使うことができる。

**【 0 0 7 8 】****（実施の形態 2 ）**

本発明の作製方法を、薄膜トランジスタ（TFT）を用いた半導体装置について簡単に説明する。ここでは、薄膜トランジスタ 1 個分と配線の断面図を利用して話を進めるが、もちろん複数のトランジスタを用いた集積回路にも適用できる。

20

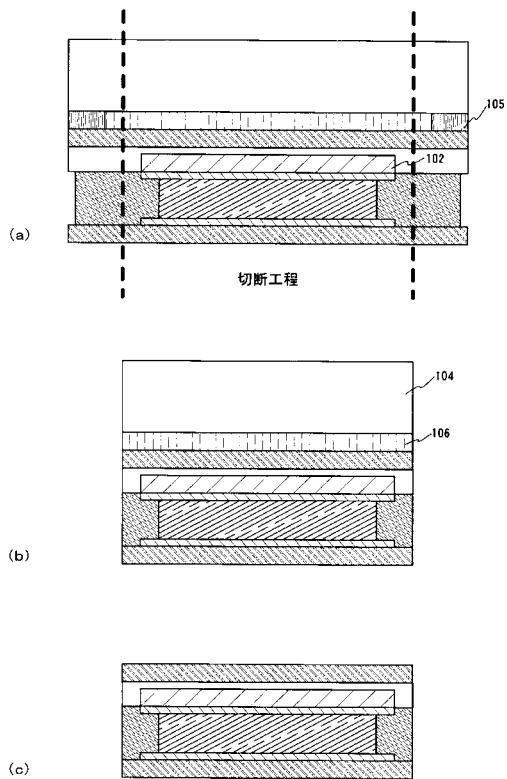

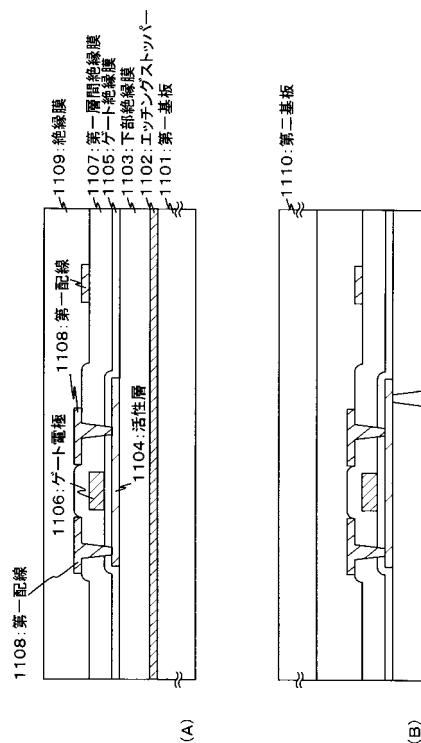

**【 0 0 7 9 】**

図 4（A）で、第一基板 1101 上に、後で第一基板 1101 を取り除く際に利用するエッティングストッパー 1102 を形成し、その上に下部絶縁膜 1103、シリコン等半導体からなる活性層 1104、ゲート絶縁膜 1105、ゲート電極 1106 を形成してトランジスタを構成する。第一層間絶縁膜 1107 を成膜し、活性層 1104 に到達する開孔部を形成し、開孔部を介して第一配線 1108 を形成する。第二層間絶縁膜 1109 を成膜する（図 4（A））。

**【 0 0 8 0 】**

第一基板 1101 上の薄膜デバイスを形成した面に第二基板 1110 を接着し、第一基板 1101 とエッティングストッパー 1102 を取り除き、活性層 1104 に到達する開孔部を形成する（図 4（B））。エッティングストッパー 1102 は必ずしも必要なものではないが、トランジスタの最下層に窒化膜等を用意しておき、最後にウエットエッティングを行って、そのストッパーとして用いるとよい。

30

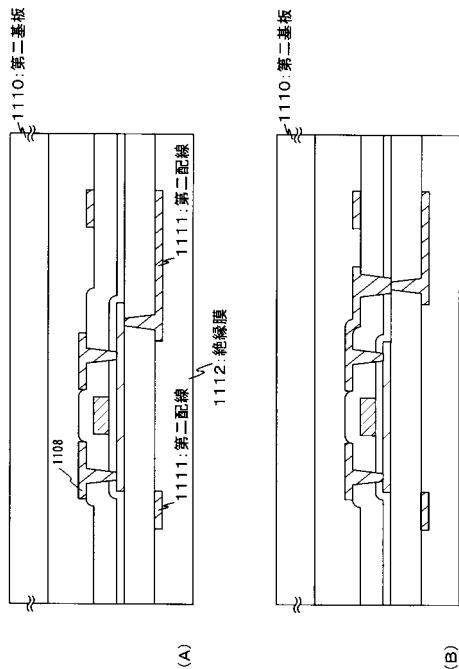

**【 0 0 8 1 】**

そして、開孔部を介して活性層に接する第二配線 1111 を形成して、絶縁膜 1112 を形成する（図 5（A））。今回は活性層を通して、第一配線 1108 と第二配線 1111 の導通をとったが、図 5（B）のように、アライメント精度分だけ大きめの開孔部を設け、直接つないでもよい。どちらにしても本発明の構造では、上下から開孔部を設けるので、導通をとりやすい。また、活性層を形成した後で配線を形成するので、耐熱性の低い配線でも使える。

40

**【 0 0 8 2 】**

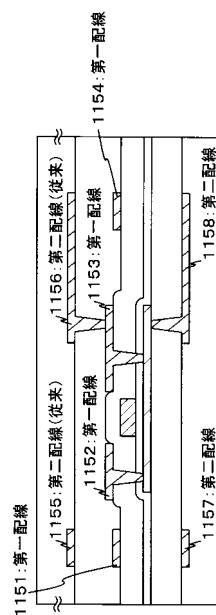

図 6 に活性層、ゲート絶縁膜、ゲート電極、第一層間絶縁膜、第一配線、第二層間絶縁膜、第二配線、の従来構造の配線も、比較のために、同時に図示する。なお、第一配線 1151、1154、第二配線 1155、1157 は、ここで図示されている薄膜トランジスタに電気的に接続されていない配線の断面である。

**【 0 0 8 3 】**

もし本発明の構造を用いていなければ、第二配線 1158 は 1156 の場所になり、第二配線 1156 は第一配線 1154 と近く、寄生容量も大きくなる。また第二配線 1157 は 1155 の場所、もしくは第一配線として 1151 に形成してもよい。この場合も第一

50

配線 1 1 5 2 との距離が近くなってしまう。

【0084】

つまり、第一配線と第二配線の距離は、従来構造では第二層間絶縁膜の厚さであり、本発明の作製方法では、下部絶縁膜と第一層間絶縁膜を合わせた厚さになる。もちろん、第二層間絶縁膜の厚さより、下部絶縁膜と第一層間絶縁膜を合わせた厚さの方が大きくなる。

【0085】

このように、本発明の作製方法を用いれば、配線間の絶縁膜を実質的に厚くとることができ、異なる層に形成された配線間に生じる寄生容量を低減できる。なお、従来のように、ただ絶縁膜を厚くするのでは、絶縁膜を通しての導通のとりやすさに問題があったが、本発明の作製方法では問題ない。また、活性層の下部に配線を設けた従来構造と同じ構造であるが、活性層を形成後に配線を形成するので、耐熱性の低い配線材料も使うことができ、耐熱性が低いがために使えなかった低抵抗な配線を使うこともできる。

【0086】

【実施例】

[実施例1]

ここでは、本発明の半導体装置の作製方法を、アクティブマトリクス型液晶表示装置に適用する例を示す。なお図では、接着剤を使い分ける位置、封止材の位置、基板を切断する位置等を説明するため、液晶表示装置の一画素のみの断面を示すが、もちろん、複数の画素を有する液晶表示装置、駆動回路を一体形成した液晶表示装置等にも、本発明は適用できる。

10

【0087】

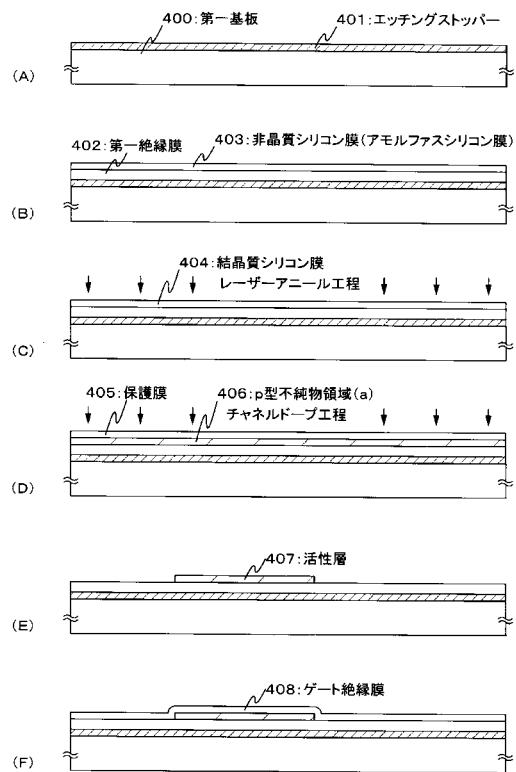

図7(A)において、第一基板400にはガラス基板や石英基板を使用することができる。その他にもシリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものを基板として用いてもよい。

【0088】

後で、第一基板400を取り除く時のために、エッティングストッパー401を形成する。エッティングストッパー401は、第一基板との選択比が十分なものを選ぶ。本実施例では、第一基板400に石英基板を使用し、エッティングストッパー401に窒化膜を10nm～1000nm(代表的には100～500nm)形成する。

20

【0089】

エッティングストッパー401上に第一絶縁膜402を、酸化シリコン膜で10～1000nm(代表的には300～500nm)の厚さに形成する。また、酸化窒化シリコン膜を用いてもよい。

30

【0090】

連続して、第一絶縁膜402上に、10～100nmの非晶質半導体膜(本実施例では非晶質シリコン膜(アモルファスシリコン膜)403)を公知の成膜法で形成する(図7(B))。なお、非晶質半導体膜としては、非晶質シリコン膜以外にも、非晶質シリコングルマニウム膜などの非晶質の化合物半導体膜を用いることもできる。

【0091】

そして、特開平7-130652号公報(USP5,643,826号に対応)に記載された技術に従って結晶構造を含む半導体膜(本実施例では結晶質シリコン膜404)を形成する。同公報記載の技術は、非晶質シリコン膜の結晶化に際して、結晶化を助長する触媒元素(ニッケル、コバルト、グルマニウム、錫、鉛、パラジウム、鉄、銅から選ばれた一種または複数の元素、代表的にはニッケル)を用いる結晶化手段である。

40

【0092】

具体的には、非晶質シリコン膜表面に触媒元素を保持させた状態で加熱処理を行い、非晶質シリコン膜を結晶質シリコン膜に変化させるものである。本実施例では同公報の実施例1に記載された技術を用いるが、実施例2に記載された技術を用いてもよい。なお、結晶質シリコン膜にはいわゆる単結晶シリコン膜も多結晶シリコン膜も含まれるが、本実施例で形成される結晶質シリコン膜は結晶粒界を有するシリコン膜である。

50

## 【0093】

非晶質シリコン膜は含有水素量にもよるが、好ましくは400～550で数時間加熱処理して脱水素処理を行い、含有水素量を5atomic%以下として結晶化の工程を行うことが望ましい。また、非晶質シリコン膜をスパッタ法や蒸着法などの他の作製法で形成してもよいが、膜中に含まれる酸素、窒素、などの不純物元素を十分に低減させておくことが望ましい。

## 【0094】

非晶質シリコン膜403に対して、公知の技術を使って結晶質シリコン膜（ポリシリコン膜または多結晶シリコン膜）404を形成する。本実施例では、非晶質シリコン膜403に対してレーザーから発する光（レーザー光）を照射して結晶質シリコン膜404を形成した（図7（C））。レーザーとしては、パルス発振型または連続発振型のエキシマレーザーを用いればよいが、連続発振型のアルゴンレーザーでもよい。または、Nd:YAGレーザーもしくはNd:YVOレーザーの第二高調波、第三高調波または第四高調波を用いてもよい。さらに、レーザー光のビーム形状は線状（長方形形状も含む）であっても矩形形状であってもかまわない。

10

## 【0095】

また、レーザー光のかわりにランプから発する光（ランプ光）を照射（以下、ランプアニールという）してもよい。ランプ光としては、ハロゲンランプ、赤外線ランプ等から発するランプ光を用いることができる。

20

## 【0096】

このようにレーザー光またはランプ光により熱処理（アニール）を施す工程を光アニール工程という。光アニール工程は短時間で高温熱処理が行えるため、ガラス基板等の耐熱性の低い基板を用いる場合にも効果的な熱処理工程を高いスループットで行うことができる。もちろん、目的はアニールであるので電熱炉を用いたファーネスアニール（熱アニールともいう）で代用することもできる。

20

## 【0097】

本実施例では、パルス発振型エキシマレーザー光を線状に加工してレーザーアニール工程を行う。レーザーアニール条件は、励起ガスとしてXeClガスを用い、処理温度を室温、パルス発振周波数を30Hzとし、レーザーエネルギー密度を250～500mJ/cm<sup>2</sup>（代表的には350～400mJ/cm<sup>2</sup>）とする。

30

## 【0098】

上記条件で行われるレーザーアニール工程は、熱結晶化後に残存した非晶質領域を完全に結晶化するとともに、既に結晶化された結晶質領域の欠陥等を低減する効果を有する。そのため、本工程は光アニールにより半導体膜の結晶性を改善する工程、または半導体膜の結晶化を助長する工程と呼ぶこともできる。このような効果はランプアニールの条件を最適化することによっても得ることが可能である。

## 【0099】

次に、結晶質シリコン膜404上に、後の不純物添加のために保護膜405を形成する（図7（D））。保護膜405は100～200nm（好ましくは130～170nm）の厚さの窒化酸化シリコン膜または酸化シリコン膜を用いる。この保護膜405は不純物添加時に結晶質シリコン膜404が直接プラズマにさらされないようにするために、微妙な温度制御を可能にするための意味がある。

40

## 【0100】

続いて、保護膜405を介してp型を付与する不純物元素（以下、p型不純物元素という）を添加する。p型不純物元素としては、代表的には周期表の13族に属する元素、典型的にはボロンまたはガリウムを用いることができる。この工程（チャネルドープ工程という）は、TFTしきい値電圧を制御するための工程である。なお、ここではジボラン（B<sub>2</sub>H<sub>6</sub>）を質量分離しないでプラズマ励起したイオンドープ法でボロンを添加した。もちろん、質量分離を行いうイオンインプランテーション法を用いてもよい。

## 【0101】

50

この工程により  $1 \times 10^{15} \sim 1 \times 10^{18}$  atoms/cm<sup>3</sup> (代表的には  $5 \times 10^{16} \sim 5 \times 10^{17}$  atoms/cm<sup>3</sup>) の濃度で、p型不純物元素 (本実施例ではボロン) を含む p型不純物領域 (a) 406 を形成する (図 7 (D))。

#### 【0102】

次に、保護膜 405 を除去した後、結晶質シリコン膜の不要な部分を除去して、島状の半導体膜 (以下、活性層という) 407 を形成する (図 7 (E))。

#### 【0103】

活性層 407 を覆って、ゲート絶縁膜 408 を形成する (図 7 (F))。ゲート絶縁膜 408 は、10 ~ 200 nm、好ましくは 50 ~ 150 nm の厚さに形成すればよい。本実施例では、プラズマ CVD 法で N<sub>2</sub>O と SiH<sub>4</sub> を原料とした窒化酸化シリコン膜を 80 nm 成膜する。

#### 【0104】

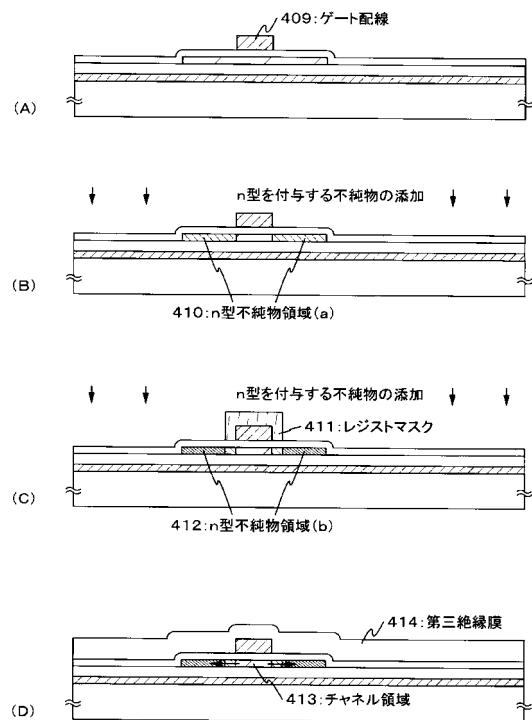

図示しないが、ゲート配線 409 として、厚さ 50 nm の窒化タンゲステン (WN) と、厚さ 350 nm のタンタル (Ta) との 2 層の積層膜を形成する (図 8 (A))。ゲート配線は单層の導電膜で形成してもよいが、必要に応じて 2 層、3 層といった積層膜とすることが好ましい。

#### 【0105】

なお、ゲート配線としては、タンタル (Ta)、チタン (Ti)、モリブデン (Mo)、タンゲステン (W)、クロム (Cr)、シリコン (Si) から選ばれた元素、または前記元素を組み合わせた合金膜 (代表的には、Mo-W 合金、Mo-Ta 合金) を用いることができる。

#### 【0106】

次に、ゲート配線 409 をマスクとして自己整合的に n 型不純物元素 (本実施例ではリン) を添加する (図 8 (B))。こうして形成された n 型不純物領域 (a) 410 には、前記のチャネルドープ工程で添加されたボロン濃度よりも 5 ~ 10 倍高い濃度 (代表的には  $1 \times 10^{16} \sim 5 \times 10^{18}$  atoms/cm<sup>3</sup>、典型的には  $3 \times 10^{17} \sim 3 \times 10^{18}$  atoms/cm<sup>3</sup>) でリンが添加されるように調整する。

#### 【0107】

レジストマスク 411 を形成し、n 型不純物元素 (本実施例ではリン) を添加して、高濃度にリンを含む n 型不純物領域 (b) 412 を形成する (図 8 (C))。ここでも、フォスフィン (PH<sub>3</sub>) を用いたイオンドープ法 (もちろん、イオンインプランテーション法でもよい) で行い、この領域のリンの濃度は  $1 \times 10^{20} \sim 1 \times 10^{21}$  atoms/cm<sup>3</sup> (代表的には  $2 \times 10^{20} \sim 5 \times 10^{20}$  atoms/cm<sup>3</sup>) とする。

#### 【0108】

また、n 型不純物領域 (b) 412 が形成された領域には、すでに前工程で添加されたリンまたはボロンが含まれるが、十分に高い濃度でリンが添加されることになるので、前工程で添加されたリンまたはボロンの影響は考えなくてよい。

#### 【0109】

レジストマスク 411 を除去した後、第三絶縁膜 414 を形成する (図 8 (D))。第三絶縁膜 414 としては、シリコンを含む絶縁膜、具体的には窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、またはそれらを組み合わせた積層膜で、膜厚は 600 nm ~ 1.5 μm とすればよい。本実施例では、プラズマ CVD 法で SiH<sub>4</sub>、N<sub>2</sub>O、NH<sub>3</sub> を原料ガスとし、1 μm 厚の窒化酸化シリコン膜 (但し窒素濃度が 25 ~ 50 atomic %) を用いる。

#### 【0110】

その後、それぞれの濃度で添加された n 型または p 型不純物元素を活性化するために熱処理工程を行う (図 8 (E))。この工程はファーネスアニール法、レーザーアニール法、またはラピッドサーマルアニール (RTA) 法で行うことができる。ここでは、ファーネスアニール法で活性化工程を行う。加熱処理は窒素雰囲気中において 300 ~ 650 °C、好ましくは 400 ~ 550 °C、ここでは 550 °C、4 時間の熱処理を行う。

10

20

30

40

50

**【0111】**

この時、本実施例において、非晶質シリコン膜の結晶化に用いた触媒元素（本実施例ではニッケル）が、矢印で示す方向に移動して、前記の図8（C）の工程で形成された高濃度にリンを含むn型不純物領域（b）412に捕獲（ゲッタリング）される。これは、リンによる金属元素のゲッタリング効果に起因する現象であり、この結果、チャネル領域413は前記触媒元素の濃度が $1 \times 10^{17}$ atoms/cm<sup>3</sup>以下（好ましくは $1 \times 10^{16}$ atoms/cm<sup>3</sup>以下）となる。

**【0112】**

また逆に触媒元素のゲッタリングサイトとなった領域（図8（C）の工程で形成されたn型不純物領域（b）412）は高濃度に触媒元素が偏析して、 $5 \times 10^{18}$ atoms/cm<sup>3</sup>以上（代表的には $1 \times 10^{19} \sim 5 \times 10^{20}$ atoms/cm<sup>3</sup>）の濃度で存在するようになる。

10

**【0113】**

さらに、3～100%の水素を含む雰囲気中で、300～450で1～12時間の熱処理を行い、活性層を水素化する工程を行う。この工程は熱的に励起された水素により、半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化（プラズマにより励起された水素を用いる）を行ってもよい。

**【0114】**

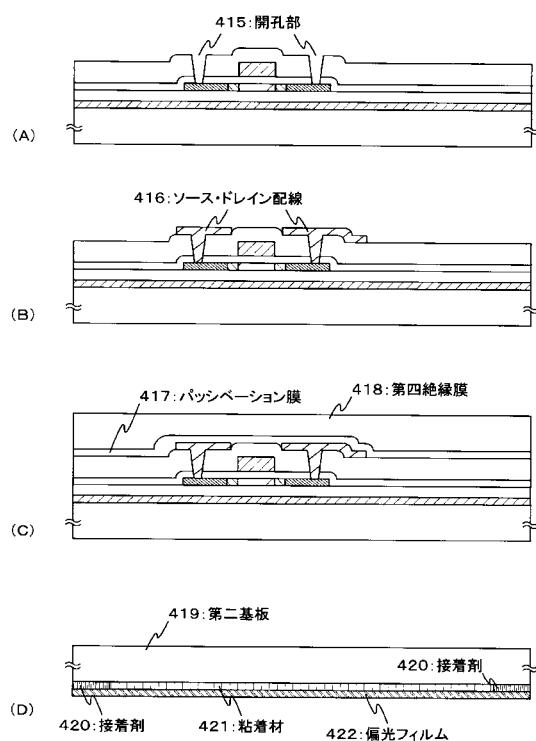

その後、TFTのソース・ドレイン領域に達する開孔部415（図9（A））、ソース・ドレイン配線416を形成する（図9（B））。また、図示していないが、本実施例ではこの配線は、Ti膜を100nm、Tiを含むアルミニウム膜を300nm、Ti膜150nmをスパッタ法で連続して形成した3層構造の積層膜である。

20

**【0115】**

次に、パッシベーション膜417として、窒化シリコン膜、酸化シリコン膜、または窒化酸化シリコン膜で50～500nm（代表的には200～300nm）の厚さで形成する（図9（C））。この時、本実施例では膜の形成に先立ってH<sub>2</sub>、NH<sub>3</sub>等水素を含むガスを用いてプラズマ処理を行い、成膜後に熱処理を行う。この前処理により励起された水素が第三絶縁膜414中に供給される。この状態で熱処理を行うことで、パッシベーション膜417の膜質を改善するとともに、第三絶縁膜414中に添加された水素が下方側に拡散するため、効果的に活性層を水素化することができる。

30

**【0116】**

また、パッシベーション膜417を形成した後に、さらに水素化工程を行ってもよい。例えば、3～100%の水素を含む雰囲気中で、300～450で1～12時間の熱処理を行うとよい。あるいはプラズマ水素化法を用いても同様の効果が得られる。

**【0117】**

その後、平坦化膜として有機樹脂からなる第四絶縁膜418を約1μmの厚さに形成する（図9（C））。有機樹脂としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB（ベンゾシクロブテン）等を使用することができる。有機樹脂膜を用いることの利点は、成膜方法が簡単である点や、比誘電率が低いので、寄生容量を低減できる点、平坦性に優れる点などが上げられる。なお上述した以外の有機樹脂膜や有機系SiO化合物などを用いることもできる。

40

ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300で焼成して形成する。

**【0118】**

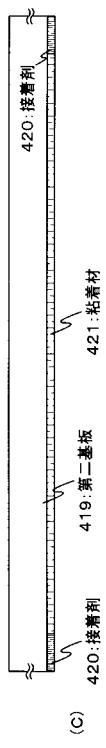

次に、第二基板419を用意し、第二基板419を第一基板400にあわせた時に、薄膜デバイスが形成されていない領域に接着材420を塗布し、それ以外の領域には、偏光フィルム422が動かないように粘着材421を塗布しておく（図9（D））。

**【0119】**

ここで、第二基板419としては、ガラス基板や石英基板、その他にもシリコン基板、金属基板またはステンレス基板等が使える。また、接着材420は、後で切り落とす部分（

50

薄膜デバイスが形成されていない領域)を接着するので、特に透明である必要もなく、耐熱性のあるものを選べばよい。例えば、一般に偏光フィルムの接着に用いられているポリビニルアルコール(PVA)系の接着材がある。粘着材421としては、耐熱性、透明性のよいものがよく、アクリル系、ウレタン系、シリコン系等の粘着材があげられる。

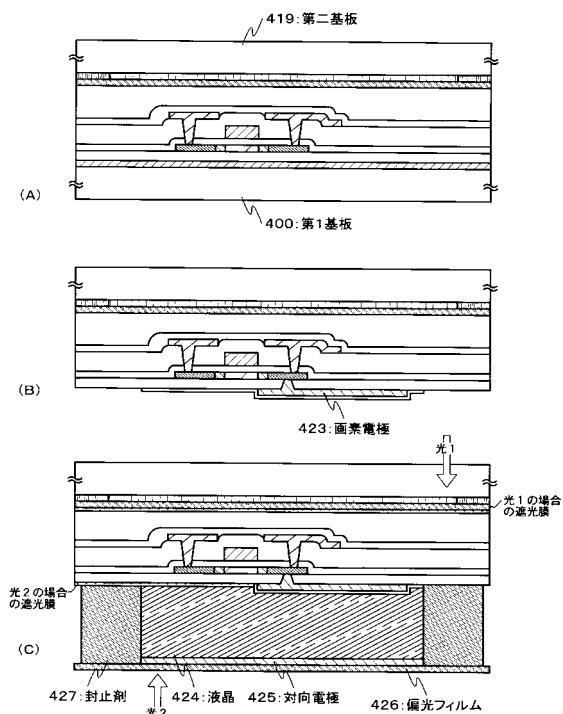

#### 【0120】

図10(A)で、第一基板400のTFTを形成した面と、第二基板419の偏光フィルムを貼り付けた面とを接着する。接着材には、透明で耐熱性のあるもの、例えば、ポリビニルアルコール(PVA)系の接着材を使えばよい。

#### 【0121】

そして、第二基板419に保持された状態で、第一基板400をバックグランドやCMP等を使って削り落とす(図10(B))。本実施例では、第一基板400に石英基板、エッティングストッパー401に窒化膜を使用しているので、最後はフッ酸を使ったウエットエッティングに切り替える。なお、ウエットエッティングの際にパターニングして第一基板400の一部を残し、液晶表示装置のスペーサーとして用いることもできる。また、本実施例では窒化膜でできたエッティングストッパー401も、その後ドライエッティングにより取り除いている。

#### 【0122】

次に、第一絶縁膜402に画素電極に導通をとるための開孔部を設け、画素電極423を形成する(図10(B))。画素電極423は、透過型液晶表示装置とする場合には透明導電膜を用い、反射型の液晶表示装置とする場合には金属膜を用いればよい。ここでは透過型の液晶表示装置とするために、酸化インジウム・スズ(ITO)膜を110nmの厚さにスパッタ法で形成する。

#### 【0123】

また、画素電極に導通をとるための方法としては、図9(A)でTFTのソース・ドレイン領域に達する開孔部415を開けるときに、活性層のない部分にエッティングストッパー401に達する開孔部を開けておき、図9(B)のソース・ドレイン配線416で導通をとる方法もある。この方法を用いると、活性層のない部分で導通をとるため、画素の開口率が落ちるもの、画素電極423を平坦なものにすることができます。

#### 【0124】

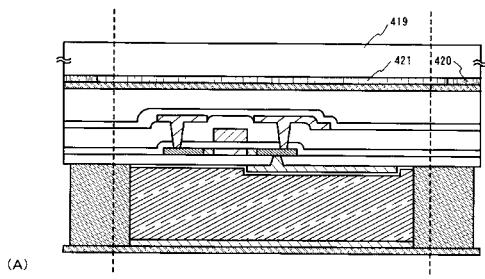

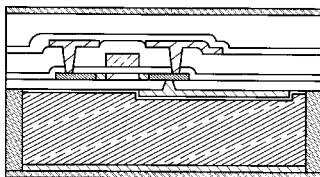

その後、図示していないが、ポリイミド膜を使って配向膜を形成し、ラビング処理を施して液晶分子がある一定のプレチルト角を持って配向するようにする。そして、偏光フィルム426に対向電極425を形成し、公知のセル組み工程によってシール材やスペーサ(共に図示せず)などを介して貼りあわせ、液晶424を封止材427を用いて封止する(図10(C))。なお、光の入射方向が、光1の場合には、偏光フィルム422上に遮光膜を形成することが好ましい。また、光の入射方向が光2の場合には、第1絶縁膜402の上または下に遮光膜となる膜を形成することが好ましい。液晶には公知の液晶材料を用いれば良い。なお、偏光フィルム426がたわむ場合は、第二基板419と同様の支持材をもう一つ用意してもよい。対向にある偏光フィルム426には、必要に応じてカラーフィルターや遮蔽膜を形成しても良い。

#### 【0125】

次に、図11(A)に示すように、接着剤420で接着された部分を切断する。後は、粘着材421で止められた部分だけになるので、第二基板419をはがし、薄く、軽量でフレキシブルなアクティブマトリクス型液晶表示装置が完成する(図11(B))。

#### 【0126】

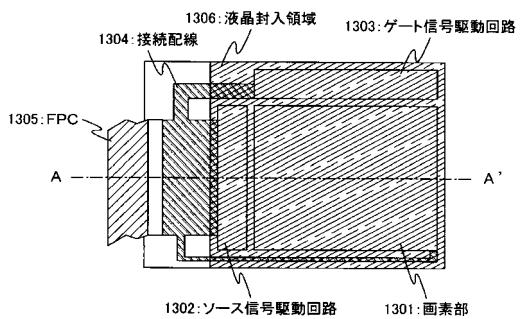

さらに図12に、駆動回路を一体形成した液晶表示装置を、本発明の作製方法を用いて作製した例を示す。図12は、第一基板上に、ソース信号駆動回路1302、ゲート信号駆動回路1303、画素部1301を構成するトランジスタを形成し、第二基板に接着した後、第一基板を取り除き、液晶を封入したもの(1306:液晶封入領域)を、液晶側から見た図である。

#### 【0127】

10

20

30

40

50

図12に示す液晶表示装置は、画素部1301と、ソース信号駆動回路1302、ゲート信号駆動回路1303とで構成される。画素部1301はnチャネル型TFTであり、周辺に設けられる駆動回路はCMOS回路を基本として構成されている。ソース信号駆動回路1302とゲート信号駆動回路1303は、接続配線1304を用いてFPC(フレキシブルプリントサーキット)1305に接続され、外部駆動回路から信号を受け取る。

#### 【0128】

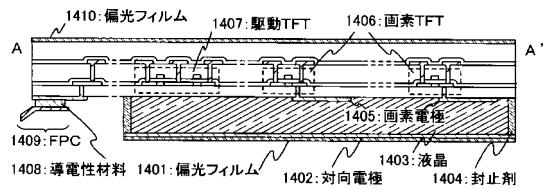

図13に、図12のA-A'で切断した断面図を示す。偏光フィルム1401、対向電極1402、封止剤1404、で囲まれた液晶1403が、画素TFT1406に接続された画素電極1405下にある。今回は、駆動TFT1407の下にも液晶1403があるが、寄生容量を減らしたい場合等には、画素電極1405下にのみ液晶1403を配置すればよい。駆動TFT1407には、導電性材料1408で接着されたFPC1409から信号が入力される。偏光フィルム1410を、液晶1403に対して、偏光フィルム1401と反対側に設けることで、透過型の表示装置として機能する。

#### 【0129】

##### [実施例2]

本実施例では、本発明を用いて形成した薄膜デバイスを重ね合わせ、3次元実装する例を図を用いて簡単に説明する。

#### 【0130】

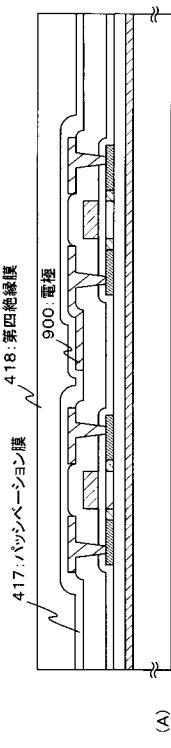

図9(C)まで、実施例1と同様であるので説明を省略する。図14(A)は、図9(A)とほぼ同じ状態であるが、ソース・ドレイン配線416を延長して電極900を形成している。なお、説明のためにトランジスタを2個表示し、実施例1と共通な部分は同じ符号を用いている。

#### 【0131】

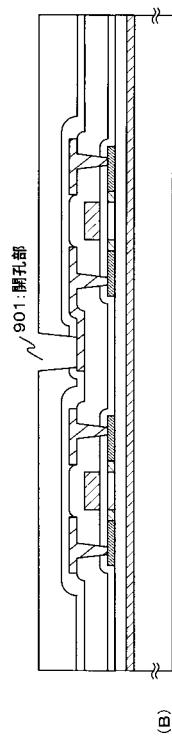

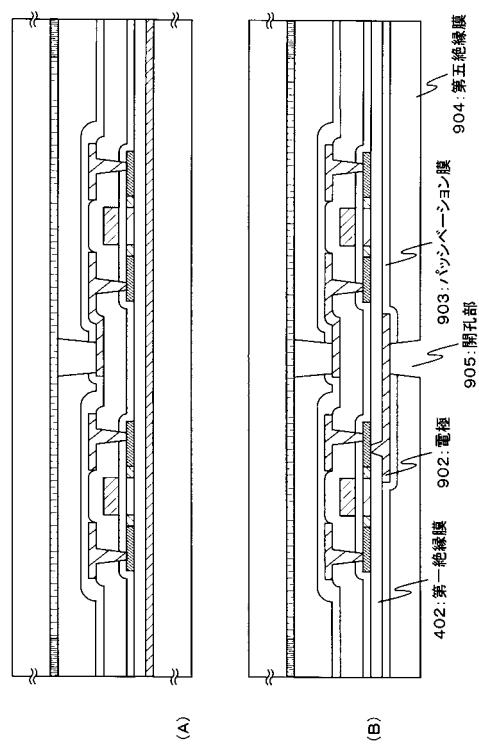

ここで、開孔部901を開け、電極900と導通がとれるようにしておく(図14(B))。第二基板419には、実施例1と同様に接着剤420と粘着材421を塗るが、偏光フィルムは必要ない(図14(C))。偏光フィルムは必要ないが、剛性保持のための薄い板材や保護フィルム等を使用してもよい。この場合、薄い板材や保護フィルムには、開孔部901に対応する位置にあらかじめ、開孔部を設けておく。図15(A)で、第一基板400の薄膜デバイスを形成した面と第二基板419を、接着剤420と粘着材421を使って接着する。

#### 【0132】

実施例1と同様、第一基板400とエッティングストッパー401を取り除く。第一絶縁膜402に開孔部を開け、電極(配線ともいう)902を形成する。電極902を覆って、パッシバーション膜903、第五絶縁膜904を形成し、電極902に導通がとれるよう開孔部905を設けておく。パッシバーション膜903は実施例1のパッシバーション膜417と同様、窒化シリコン膜、酸化シリコン膜、または窒化酸化シリコン膜で50~500nm(代表的には200~300nm)の厚さで形成すればよい。第五絶縁膜904は実施例1の第四絶縁膜418と同様、平坦化や保護膜の意味がある。ここまで工程で、図15(B)の状態になっている。

#### 【0133】

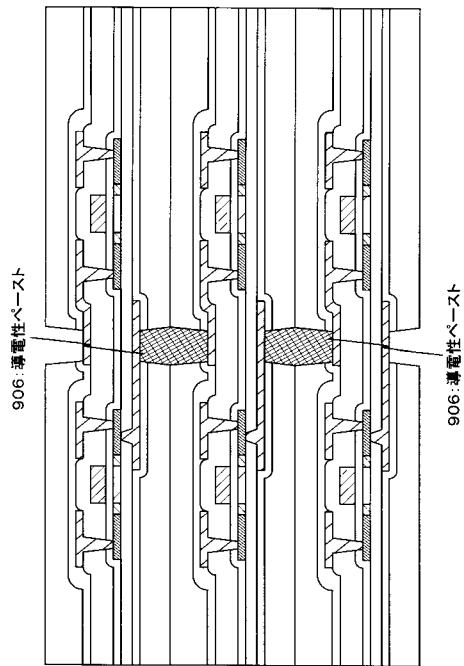

そして、実施例1と同じ方法で第二基板419を取り除く。ここまで工程でできる薄膜デバイスを複数作製し、導電性ペースト906で電極間に導通をとり、それらを接着剤で貼り合わせると、3次元実装された半導体装置ができあがる(図16)。近年、大容量化や小型化、軽量化が求められているメモリは、3次元実装の技術の実用化が注目されており、本発明を用いると、工程が複雑化することなく、簡便に3次元実装された半導体装置を実現することができる。なお図16では、貼り合わされた薄膜デバイスは、薄膜トランジスタのソース・ドレイン領域を介して導通をとっているように示されているが、配線同士の導通を直接とってもよい。

#### 【0134】

##### [実施例3]

10

20

30

40

50

本実施例では、絶縁体上に形成した半導体薄膜を活性層に用いた薄膜トランジスタ（TFT）を用いた半導体装置について説明する。なお図では、配線と活性層、配線と絶縁膜等の位置関係を説明するため、薄膜トランジスター個分と配線の断面を示すが、もちろん、複数の薄膜トランジスタを有する集積回路にも本発明は適用できる。

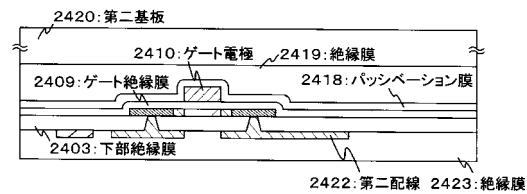

【0135】

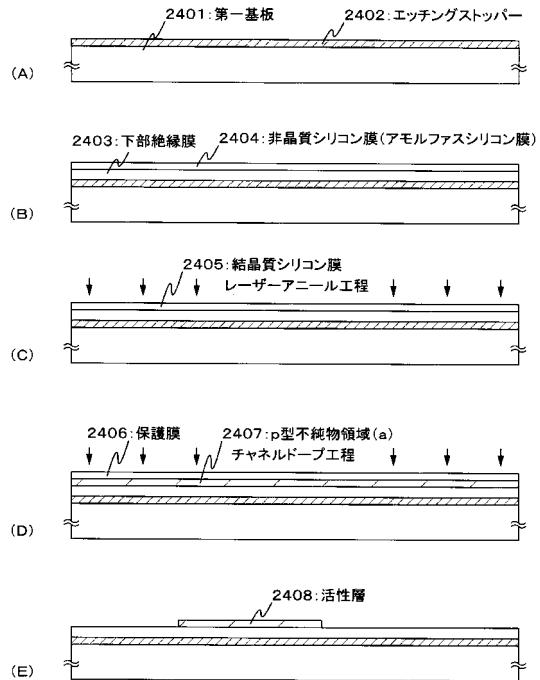

図17(A)において、第一基板2401にはガラス基板や石英基板を使用することができる。その他にもシリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものに基板として用いてもよい。

【0136】

後で、第一基板2401を取り除く時のために、エッチングストッパー2402を形成する。エッチングストッパー2402は、第一基板との選択比が十分なものを選ぶ。本実施例では、第一基板2401に石英基板を使用し、エッチングストッパー2402に窒化膜を10nm～1000nm(代表的には100～500nm)形成する。10

【0137】

エッチングストッパー2402上に下部絶縁膜2403を、酸化シリコン膜で10～1000nm(代表的には300～500nm)の厚さに形成する。また、酸化窒化シリコン膜を用いてもよい。

【0138】

連続して、下部絶縁膜2403上に、10～1000nmの非晶質半導体膜(本実施例では非晶質シリコン膜(アモルファスシリコン膜)2404)を公知の成膜法で形成する(図17(B))。なお、非晶質半導体膜としては、非晶質シリコン膜以外にも、非晶質シリコンゲルマニウム膜などの非晶質の化合物半導体膜を用いることもできる。20

【0139】

そして、特開平7-130652号公報(USP5,643,826号に対応)に記載された技術に従って結晶構造を含む半導体膜(本実施例では結晶質シリコン膜2405)を形成する。同公報記載の技術は、非晶質シリコン膜の結晶化に際して、結晶化を助長する触媒元素(ニッケル、コバルト、ゲルマニウム、錫、鉛、パラジウム、鉄、銅から選ばれた一種または複数の元素、代表的にはニッケル)を用いる結晶化手段である。

【0140】

具体的には、非晶質シリコン膜表面に触媒元素を保持させた状態で加熱処理を行い、非晶質シリコン膜を結晶質シリコン膜に変化させるものである。本実施例では同公報の実施例1に記載された技術を用いるが、実施例2に記載された技術を用いてもよい。なお、結晶質シリコン膜にはいわゆる単結晶シリコン膜も多結晶シリコン膜も含まれるが、本実施例で形成される結晶質シリコン膜は結晶粒界を有するシリコン膜である。30

【0141】

非晶質シリコン膜は含有水素量にもよるが、好ましくは400～550で数時間加熱処理して脱水素処理を行い、含有水素量を5atomic%以下として結晶化の工程を行うことが望ましい。また、非晶質シリコン膜をスパッタ法や蒸着法などの他の作製法で形成してもよいが、膜中に含まれる酸素、窒素、などの不純物元素を十分に低減させておくことが望ましい。40

【0142】

非晶質シリコン膜2404に対して、公知の技術を使って結晶質シリコン膜(ポリシリコン膜または多結晶シリコン膜)2405を形成する。本実施例では、非晶質シリコン膜2404に対してレーザーから発する光(レーザー光)を照射して結晶質シリコン膜2405を形成した(図17(C))。レーザーとしては、パルス発振型または連続発振型のエキシマレーザーを用いればよいが、連続発振型のアルゴンレーザーでもよい。または、Nd:YAGレーザーもしくはNd:YVO<sub>4</sub>レーザーの第二高調波、第三高調波または第四高調波を用いてもよい。さらに、レーザー光のビーム形状は線状(長方形状も含む)であっても矩形状であってもかまわない。

【0143】

50

また、レーザー光のかわりにランプから発する光（ランプ光）を照射（以下、ランプアニールという）してもよい。ランプ光としては、ハロゲンランプ、赤外線ランプ等から発するランプ光を用いることができる。

#### 【0144】

このようにレーザー光またはランプ光により熱処理（アニール）を施す工程を光アニール工程という。光アニール工程は短時間で高温熱処理が行えるため、ガラス基板等の耐熱性の低い基板を用いる場合にも効果的な熱処理工程を高いスループットで行うことができる。もちろん、目的はアニールであるので電熱炉を用いたファーネスアニール（熱アニールともいう）で代用することもできる。

#### 【0145】

本実施例では、パルス発振型エキシマレーザー光を線状に加工してレーザーアニール工程を行う。レーザーアニール条件は、励起ガスとしてXeClガスを用い、処理温度を室温、パルス発振周波数を30Hzとし、レーザーエネルギー密度を250～500mJ/cm<sup>2</sup>（代表的には350～400mJ/cm<sup>2</sup>）とする。

#### 【0146】

上記条件で行われるレーザーアニール工程は、熱結晶化後に残存した非晶質領域を完全に結晶化するとともに、既に結晶化された結晶質領域の欠陥等を低減する効果を有する。そのため、本工程は光アニールにより半導体膜の結晶性を改善する工程、または半導体膜の結晶化を助長する工程と呼ぶこともできる。このような効果はランプアニールの条件を最適化することによっても得ることが可能である。

#### 【0147】

次に、結晶質シリコン膜2405上に、後の不純物添加のために保護膜2406を形成する（図17（D））。保護膜2406は100～200nm（好ましくは130～170nm）の厚さの窒化酸化シリコン膜または酸化シリコン膜を用いる。この保護膜2406は不純物添加時に結晶質シリコン膜2405が直接プラズマにさらされないようにするために、微妙な温度制御を可能にするための意味がある。

#### 【0148】

続いて、保護膜2406を介してp型を付与する不純物元素（以下、p型不純物元素という）を添加する。p型不純物元素としては、代表的には周期表の13族に属する元素、典型的にはボロンまたはガリウムを用いることができる。この工程（チャネルドープ工程という）は、TFTしきい値電圧を制御するための工程である。なお、ここではジボラン（B<sub>2</sub>H<sub>6</sub>）を質量分離しないでプラズマ励起したイオンドープ法でボロンを添加した。もちろん、質量分離を行なうイオンインプランテーション法を用いてもよい。

#### 【0149】

この工程により $1 \times 10^{15} \sim 1 \times 10^{18}$ atoms/cm<sup>3</sup>（代表的には $5 \times 10^{16} \sim 5 \times 10^{17}$ atoms/cm<sup>3</sup>）の濃度で、p型不純物元素（本実施例ではボロン）を含むp型不純物領域（a）2407を形成する（図17（D））。

#### 【0150】

次に、保護膜2406を除去した後、結晶質シリコン膜の不要な部分を除去して、島状の半導体膜（以下、活性層という）2408を形成する（図17（E））。

#### 【0151】

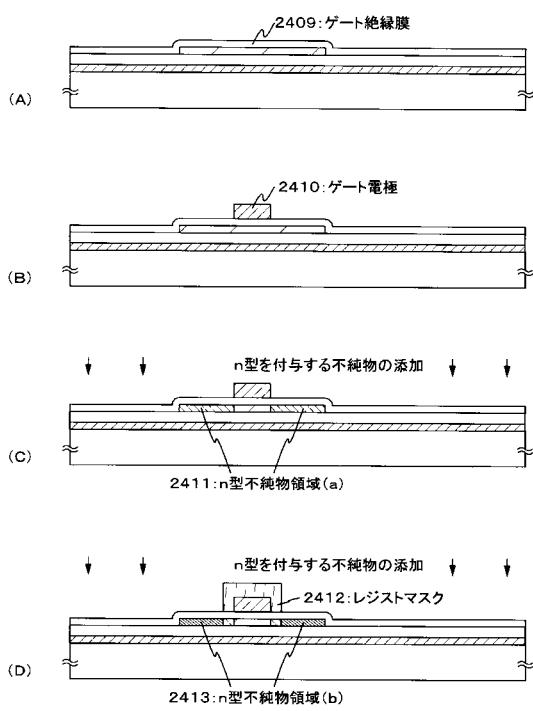

活性層2408を覆って、ゲート絶縁膜2409を形成する（図18（A））。ゲート絶縁膜2409は、10～200nm、好ましくは50～150nmの厚さに形成すればよい。本実施例では、プラズマCVD法でN<sub>2</sub>OとSiH<sub>4</sub>を原料とした窒化酸化シリコン膜を80nm成膜する。

#### 【0152】

図示しないが、ゲート電極2410として、厚さ50nmの窒化タンゲステン（WN）と、厚さ350nmのタンタル（Ta）との2層の積層膜を形成する（図18（B））。ゲート電極は単層の導電膜で形成してもよいが、必要に応じて2層、3層といった積層膜とすることが好ましい。

10

20

30

40

50

## 【0153】

なお、ゲート電極としては、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タンクステン(W)、クロム(Cr)、シリコン(Si)から選ばれた元素、または前記元素を組み合わせた合金膜(代表的には、Mo-W合金、Mo-Ta合金)を用いることができる。

## 【0154】

次に、ゲート電極2410をマスクとして自己整合的にn型不純物元素(本実施例ではリン)を添加する(図18(C))。こうして形成されたn型不純物領域(a)2411には、前記のチャネルドープ工程で添加されたボロン濃度よりも5~10倍高い濃度(代表的には $1 \times 10^{16} \sim 5 \times 10^{18}$ atoms/cm<sup>3</sup>、典型的には $3 \times 10^{17} \sim 3 \times 10^{18}$ atoms/cm<sup>3</sup>)でリンが添加されるように調整する。10

## 【0155】

レジストマスク2412を形成し、n型不純物元素(本実施例ではリン)を添加して、高濃度にリンを含むn型不純物領域(b)2413を形成する(図18(D))。ここでも、フォスフィン(PH<sub>3</sub>)を用いたイオンドープ法(もちろん、イオンインプランテーション法でもよい)で行い、この領域のリンの濃度は $1 \times 10^{20} \sim 1 \times 10^{21}$ atoms/cm<sup>3</sup>(代表的には $2 \times 10^{20} \sim 5 \times 10^{20}$ atoms/cm<sup>3</sup>)とする。

## 【0156】

また、n型不純物領域(b)2413が形成された領域には、すでに前工程で添加されたリンまたはボロンが含まれるが、十分に高い濃度でリンが添加されることになるので、前工程で添加されたリンまたはボロンの影響は考えなくてよい。20

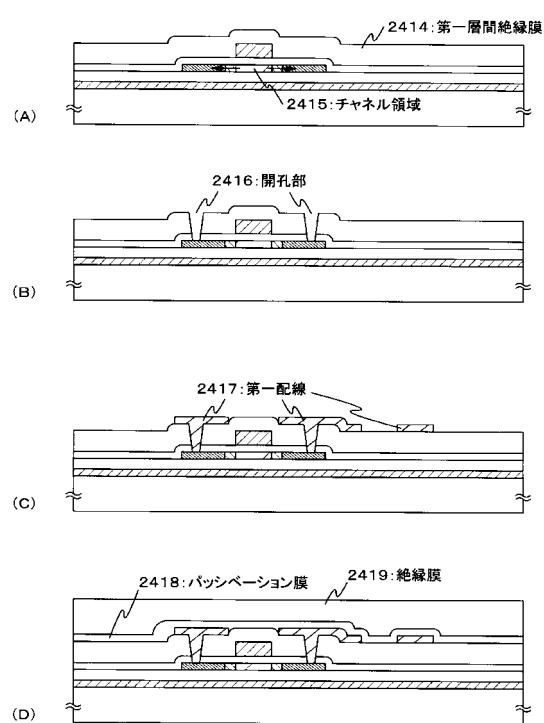

## 【0157】

レジストマスク2412を除去した後、第一層間絶縁膜2414を形成する(図19(A))。第一層間絶縁膜2414としては、シリコンを含む絶縁膜、具体的には窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、またはそれらを組み合わせた積層膜で、膜厚は600nm~1.5μmとすればよい。本実施例では、プラズマCVD法でSiH<sub>4</sub>、N<sub>2</sub>O、NH<sub>3</sub>を原料ガスとし、1μm厚の窒化酸化シリコン膜(但し窒素濃度が25~50atomic%)を用いる。

## 【0158】

その後、それぞれの濃度で添加されたn型またはp型不純物元素を活性化するために熱処理工程を行う(図19(A))。この工程はファーネスアニール法、レーザーアニール法、またはラピッドサーマルアニール(RTA)法で行うことができる。ここでは、ファーネスアニール法で活性化工程を行う。加熱処理は窒素雰囲気中において300~650、好ましくは400~550、ここでは550、4時間の熱処理を行う。30

## 【0159】

この時、本実施例において、非晶質シリコン膜の結晶化に用いた触媒元素(本実施例ではニッケル)が、矢印で示す方向に移動して、前記の図18(D)の工程で形成された高濃度にリンを含むn型不純物領域(b)2413に捕獲(ゲッタリング)される。これは、リンによる金属元素のゲッタリング効果に起因する現象であり、この結果、チャネル領域2415は前記触媒元素の濃度が $1 \times 10^{17}$ atoms/cm<sup>3</sup>以下(好ましくは $1 \times 10^{16}$ atoms/cm<sup>3</sup>以下)となる。40

## 【0160】

また逆に触媒元素のゲッタリングサイトとなった領域(図18(D))の工程で形成されたn型不純物領域(b)2413は高濃度に触媒元素が偏析して、 $5 \times 10^{18}$ atoms/cm<sup>3</sup>以上(代表的には $1 \times 10^{19} \sim 5 \times 10^{20}$ atoms/cm<sup>3</sup>)の濃度で存在するようになる。

## 【0161】

さらに、3~100%の水素を含む雰囲気中で、300~450で1~12時間の熱処理を行い、活性層を水素化する工程を行う。この工程は熱的に励起された水素により、半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ50

水素化（プラズマにより励起された水素を用いる）を行ってもよい。

**【0162】**

その後、TFTのソース・ドレイン領域に達する開孔部2416（図19（B））、第一配線2417を形成する（図19（C））。また、図示していないが、本実施例ではこの第一配線を、Ti膜を100nm、Tiを含むアルミニウム膜を300nm、Ti膜150nmをスパッタ法で連続して形成した3層構造の積層膜とする。

**【0163】**

次に、パッシベーション膜2418として、窒化シリコン膜、酸化シリコン膜、または窒化酸化シリコン膜で50～500nm（代表的には200～300nm）の厚さで形成する（図19（D））。この時、本実施例では膜の形成に先立ってH<sub>2</sub>、NH<sub>3</sub>等水素を含むガスを用いてプラズマ処理を行い、成膜後に熱処理を行う。この前処理により励起された水素が第一層間絶縁膜2414中に供給される。この状態で熱処理を行うことで、パッシベーション膜2418の膜質を改善するとともに、第一層間絶縁膜2414中に添加された水素が下方側に拡散するため、効果的に活性層を水素化することができる。10

**【0164】**

また、パッシベーション膜2418を形成した後に、さらに水素化工程を行ってもよい。例えば、3～100%の水素を含む雰囲気中で、300～450℃で1～12時間の熱処理を行うとよい。あるいはプラズマ水素化法を用いても同様の効果が得られる。

**【0165】**

その後、平坦化膜として有機樹脂からなる絶縁膜2419を約1μmの厚さに形成する（図19（D））。有機樹脂としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB（ベンゾシクロブテン）等を使用することができる。有機樹脂膜を用いることの利点は、成膜方法が簡単である点や、比誘電率が低いので、寄生容量を低減できる点、平坦性に優れる点などが上げられる。なお上述した以外の有機樹脂膜や有機系SiO化合物などを用いることもできる。ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300℃で焼成して形成する。20

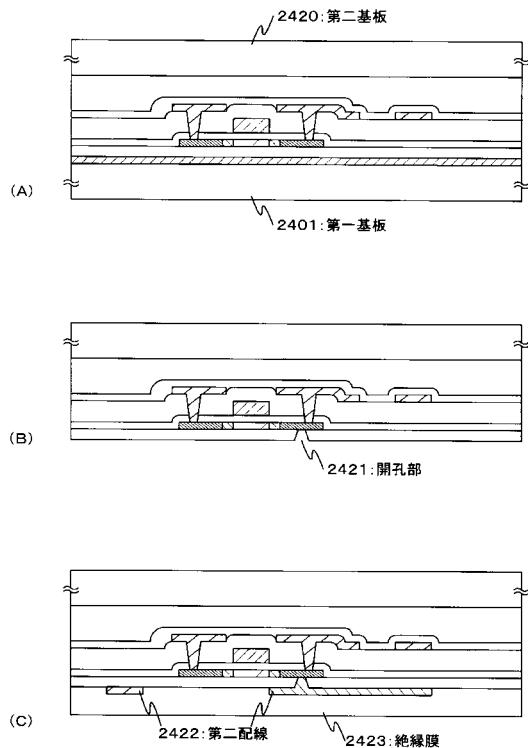

**【0166】**

次に、第二基板2420を用意し、第一基板2401の薄膜デバイスを形成した面と第二基板を接着する（図20（A））。ここで、第二基板2420としては、ガラス基板や石英基板、その他にもシリコン基板、金属基板またはステンレス基板等が使える。本実施例では、第二基板2420として石英基板を用いる。この場合、接着剤には、エポキシ系やシアノアクリレート系、または光線硬化型接着剤等が使える。30

**【0167】**

そして、第二基板2420に保持された状態で、第一基板2401をバックグラウンドやCMP（Chemical Mechanical Polishing）等を使って削り落とす（図20（B））。本実施例では、第一基板2401に石英基板、エッティングストッパー2402に窒化膜を使用しているので、適当な厚さまで削った後、フッ酸を使ったウエットエッティングに切り替える。また、本実施例では窒化膜でできたエッティングストッパー2402も、その後ドライエッティングにより取り除いている。40

**【0168】**

次に、下部絶縁膜2403に活性層2408に達する開孔部2421を設け（図20（B））、第二配線2422、絶縁膜2423を形成する（図20（C））。ここで、第二配線2422としては、すでに活性層2408の熱処理等が済んでいるので、耐熱性の低い配線材料でも使うことができる。第一配線2417と同様にアルミニウムを使ってもよいし、実施例4で示すように透過型液晶表示装置として使う場合には、酸化インジウム・スズ（ITO）を使ってもよい。

**【0169】**

このように、本発明の作製方法を用いれば、第一配線2417と第二配線2422との間の絶縁膜を厚くとることができ、寄生容量を低減できる。絶縁膜を通しての導通のとりやすさにも問題なく、また、耐熱性の低い配線材料も使うことができ、電気回路の高速動作や50

電気信号の正確な伝播に寄与することができる。

**【0170】**

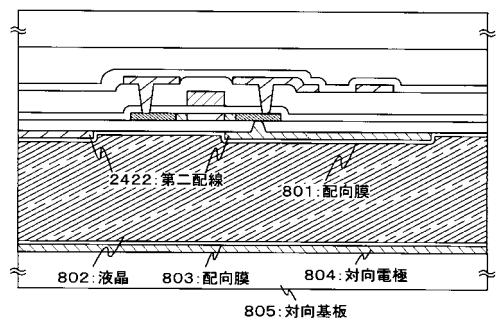

**[実施例4]**

本実施例では、実施例3で作製した半導体装置から、アクティブマトリクス型液晶表示装置を作製する工程を説明する。図21に示すように、図20(B)の状態の基板に対し、第二配線2422を形成する。第二配線2422は、透過型液晶表示装置とする場合には透明導電膜を用い、反射型の液晶表示装置とする場合には金属膜を用いればよい。ここでは透過型の液晶表示装置とするために、酸化インジウム・スズ(ITO)膜を110nmの厚さにスパッタ法で形成する。

**【0171】**

10

そして、配向膜801を形成する。本実施例では配向膜としてポリイミド膜を用いた。また、対向基板805には、透明導電膜で対向電極804を、そして配向膜803を形成する。なお、対向基板には必要に応じてカラーフィルターや遮蔽膜を形成しても良い。

**【0172】**

配向膜803を形成した後、ラビング処理を施して液晶分子がある一定のプレチルト角を持って配向するようにする。そして、画素部と駆動回路が形成されたアクティブマトリクス基板(実施例3で作製した半導体装置)と対向基板とを、公知のセル組み工程によってシール材やスペーサ(共に図示せず)などを介して貼りあわせる。その後、両基板の間に液晶802を注入し、封止剤(図示せず)によって完全に封止する。液晶には公知の液晶材料を用いれば良い。このようにして図21に示すアクティブマトリクス型液晶表示装置が完成する。

20

**【0173】**

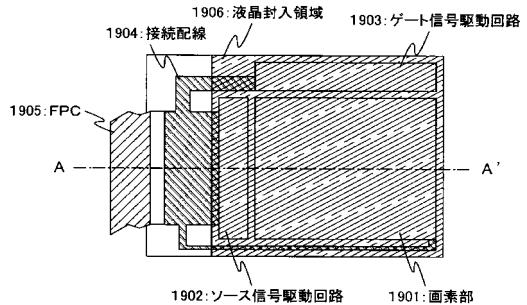

次に、このアクティブマトリクス型液晶表示装置を、駆動回路を一体形成した場合の全体構成を、図22に示す。尚、図23は、図22のA-A'で切断した断面図である。図22は、第一基板上に、ソース信号駆動回路1902、ゲート信号駆動回路1903、画素部1901を構成するトランジスタを形成し、第二基板に接着した後、第一基板を取り除き、液晶を封入したもの(1906:液晶封入領域)を、液晶側から見た図である。

**【0174】**

30

図22に示す液晶表示装置は、画素部1901と、ソース信号駆動回路1902、ゲート信号駆動回路1903とで構成される。画素部1901はnチャネル型TFTであり、周辺に設けられる駆動回路はCMOS回路を基本として構成されている。ソース信号駆動回路1902とゲート信号駆動回路1903は、接続配線1904を用いてFPC(フレキシブルプリントサーキット)1905に接続され、外部駆動回路から信号を受け取る。

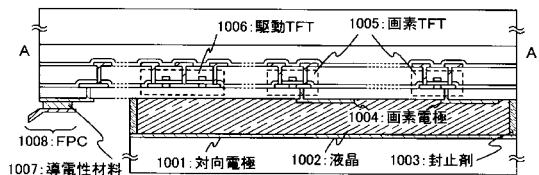

**【0175】**

図23は、対向電極1001、封止剤1003、で囲まれた液晶1002が、画素TFT1005に接続された画素電極1004の下にある。今回は、駆動TFT1006の下にも液晶1002があるが、寄生容量を減らしたい場合等には、画素電極1004下にのみ液晶1002を配置すればよい。駆動TFT1006には、導電性材料1007で接着されたFPC1008から信号が入力される。

**【0176】**

40

**[実施例5]**

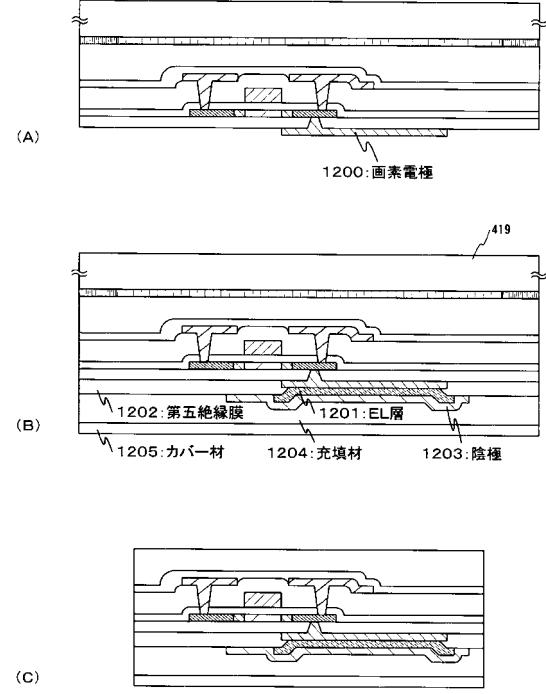

本発明の半導体装置の作製方法を、アクティブマトリクス型EL(エレクトロルミネンス)表示装置に適用する例を示す。

**【0177】**

実施例1の図10(B)まで同じであるが、偏光フィルム422は必要ない(図24(A))。画素電極1200としては、仕事関数の大きい透明導電膜が用いられる。透明導電膜としては、酸化インジウムと酸化スズとの化合物または酸化インジウムと酸化亜鉛との化合物を用いることができる。

**【0178】**

そして、画素電極1200の上(図では下)には第五絶縁膜1202が形成され、第五絶

50

縁膜 1202 は画素電極 1200 の上に開孔部が形成されている。この開孔部において、画素電極 1200 の上には E L 層 1201 が形成される。E L 層 1201 は公知の有機 E L 材料または無機 E L 材料を用いることができる。また、有機 E L 材料には低分子系(モノマー系)材料と高分子系(ポリマー系)材料があるがどちらを用いても良い。

#### 【0179】

E L 層 1201 の形成方法は公知の技術を用いれば良い。また、E L 層の構造は正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層を自由に組み合わせて積層構造または単層構造とすれば良い。

#### 【0180】

E L 層 1201 の上(図では下)には遮光性を有する導電膜(代表的にはアルミニウム、銅もしくは銀を主成分とする導電膜またはそれらと他の導電膜との積層膜)からなる陰極 1203 が形成される。また、陰極 1203 と E L 層 1201 の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、真空中で両者を連続成膜するか、E L 層 1201 を窒素または希ガス雰囲気で形成し、酸素や水分に触れさせないまま陰極 1203 を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスターツール方式)の成膜装置を用いることで上述のような成膜を可能とする。

#### 【0181】

以上のようにして、画素電極 1200、E L 層 1201 及び陰極 1203 からなる E L 素子が形成され、充填材 1204 により封入されている(図 24(B))。

#### 【0182】

カバー材 1205 としては、ガラス板、金属板(代表的にはステンレス板)、セラミックス板、F R P (Fiberglass Reinforced Plastics) 板、P V F (ポリビニルフルオライド) フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリルフィルムを用いることができる。また、アルミニウムホイルを P V F フィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる。

#### 【0183】

但し、E L 素子からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透明物質を用いる。

#### 【0184】

また、充填材 1204 としては紫外線硬化樹脂または熱硬化樹脂を用いることができ、P V C (ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、P V B (ポリビニルブチラル) または E V A (エチレンビニルアセテート) を用いることができる。この充填材 1204 の内部に吸湿性物質(好ましくは酸化バリウム)を設けておくと E L 素子の劣化を抑制できる。

#### 【0185】

また、充填材 1204 の中にスペーサを含有させてもよい。このとき、スペーサを酸化バリウムで形成すればスペーサ自体に吸湿性をもたせることが可能である。また、スペーサを設けた場合、スペーサからの圧力を緩和するバッファ層として陰極 1203 上に樹脂膜を設けることも有効である。

#### 【0186】

最後に、実施例 1 と同様に基板を切断して、第二基板 419 を取り除く。こうして、薄くて軽い、アクティブマトリクス型 E L 表示装置が作製できる(図 24(C))。

#### 【0187】

#### [実施例 6]

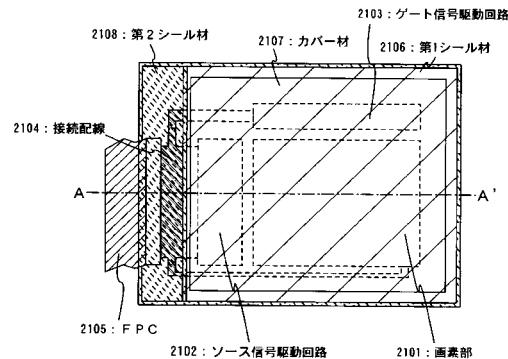

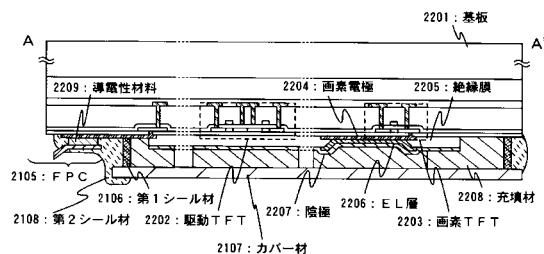

本実施例では、本発明を用いて E L (エレクトロルミネンス) 表示装置を作製した他の例について説明する。なお、図 25 は、第一基板上に、ソース信号駆動回路 2102、ゲート信号駆動回路 2103、画素部 2101 を構成するトランジスタを形成し、第二基板に接着した後、第一基板を取り除き、E L 層を形成したものを、E L 層側から見た図である。図 26 は、図 11 を A-A' で切断した断面図である。

10

20

30

40

50

**【0188】**

図25、26において、2201は基板、2101は画素部、2102はソース信号駆動回路、2103はゲート信号駆動回路であり、それぞれの駆動回路は接続配線2104を経てFPC(フレキシブルプリントサーキット)2105に至り、外部機器へと接続される。

**【0189】**

このとき、画素部2101、ソース信号駆動回路2102及びゲート信号駆動回路2103を囲むようにして第1シール材2106、カバー材2107、充填材2208及び第2シール材2108が設けられている。

**【0190】**

図26は、図25をA-A'で切断した断面図に相当し、基板2201の上にソース信号駆動回路2102に含まれる駆動TFT(但し、ここではnチャネル型TFTとpチャネル型TFTを図示している)2202及び画素部2101に含まれる画素TFT(但し、ここではEL素子への電流を制御するTFTを図示している)2203が形成されている。

**【0191】**

そして、画素電極2204は画素TFT2203のソース・ドレイン領域の一方と電気的に接続をとるように形成される。画素電極2204としては仕事関数の大きい透明導電膜が用いられる。透明導電膜としては、酸化インジウムと酸化スズとの化合物または酸化インジウムと酸化亜鉛との化合物を用いることができる。

**【0192】**

画素電極2204の上(図では下)には絶縁膜2205が形成され、絶縁膜2205は画素電極2204の上に開孔部が形成されている。この開孔部において、画素電極2204の上にはEL層2206が形成される。EL層2206は公知の有機EL材料または無機EL材料を用いることができる。また、有機EL材料には低分子系(モノマー系)材料と高分子系(ポリマー系)材料があるがどちらを用いても良い。

**【0193】**

EL層2206の形成方法は公知の技術を用いれば良い。また、EL層の構造は正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層を自由に組み合わせて積層構造または単層構造とすれば良い。

**【0194】**

EL層2206の上には遮光性を有する導電膜(代表的にはアルミニウム、銅もしくは銀を主成分とする導電膜またはそれらと他の導電膜との積層膜)からなる陰極2207が形成される。また、陰極2207とEL層2206の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、真空中で両者を連続成膜するか、EL層2206を窒素または希ガス雰囲気で形成し、酸素や水分に触れさせないまま陰極2207を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスターツール方式)の成膜装置を用いることで上述のような成膜を可能とする。

**【0195】**

以上のようにして、画素電極2204、EL層2206及び陰極2207からなるEL素子が形成される。このEL素子は、第1シール材2106及び第2シール材2108によって基板2201に貼り合わされたカバー材2107で囲まれ、充填材2208により封入されている。

**【0196】**

カバー材2107としては、ガラス板、金属板(代表的にはステンレス板)、セラミックス板、FRP(Fiberglass Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエスチルフィルムまたはアクリルフィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる。

**【0197】**

10

20

30

40

50

但し、EL素子からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透明物質を用いる。

#### 【0198】

また、充填材2208としては紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。この充填材2208の内部に吸湿性物質(好ましくは酸化バリウム)を設けておくとEL素子の劣化を抑制できる。

#### 【0199】

また、充填材2208の中にスペーサを含有させてもよい。このとき、スペーサを酸化バリウムで形成すればスペーサ自体に吸湿性をもたせることが可能である。また、スペーサを設けた場合、スペーサからの圧力を緩和するバッファ層として陰極2207上に樹脂膜を設けることも有効である。

#### 【0200】

また、接続配線2104は導電性材料2209を介してFPC2105に電気的に接続される。接続配線2104は画素部2101、ソース信号駆動回路2102及びゲート信号駆動回路2103に送られる信号をFPC2105に伝え、FPC2105により外部機器と電気的に接続される。

#### 【0201】

また、本実施例では第1シール材2106の露呈部及びFPC2105の一部を覆うように第2シール材2108を設け、EL素子を徹底的に外気から遮断する構造となっている。こうして図26の断面構造を有するEL表示装置となる。

#### 【0202】

##### [実施例7]

ここで、本発明の作製方法を用いて、ボトムゲート型薄膜トランジスタを形成する方法を簡単に説明する。図27に、そのトランジスタ1個分の断面図を示すが、作製方法は実施例3と基本的に同様である。なお、本明細書において、ボトムゲート型薄膜トランジスタとは、図27に示すような、ゲート電極と第二配線との間の層に活性層が形成されている(ゲート電極と配線とが、活性層の同一側には形成されていない)形状の薄膜トランジスタを指すこととする。

#### 【0203】

実施例1と同様に図18(C)では、ゲート電極2410をマスクとして、セルフアラインで活性層2408に不純物を添加する。第一配線2417は必要ないので、ゲート電極2410の上にはパッシベーション膜2418、絶縁膜2419を形成して平坦化する。その後、第二基板2420を接着して、第一基板2401を取り除き、第二配線2422(なお、本実施例では第一配線は存在しないが、実施例3とそろえるために第二配線と表記している)、絶縁膜2423を形成する。

#### 【0204】

このようにして、活性層に対して配線と反対側にゲート電極を持つボトムゲート型トランジスタが形成できるが、従来のボトムゲート型トランジスタとの違いは、セルフアラインで不純物を添加できるという点である。

#### 【0205】

##### [実施例8]

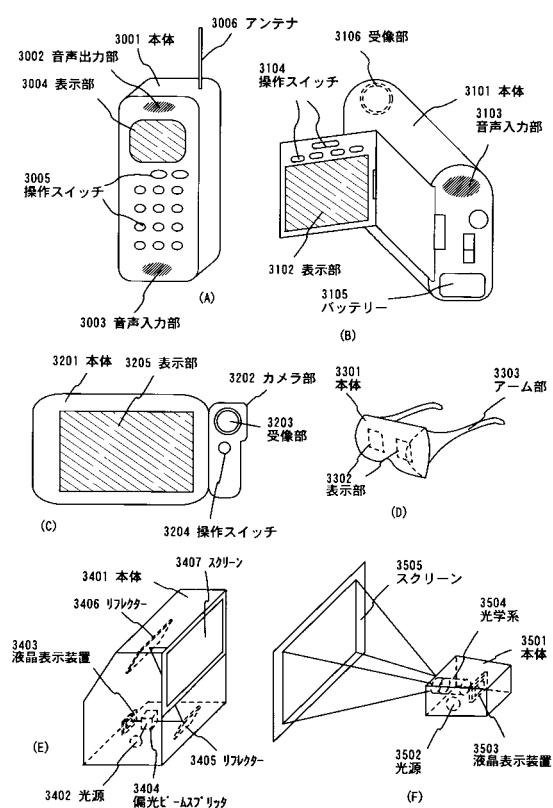

本発明のアクティブマトリクス型表示装置は電気器具の表示部として用いることができる。そのような電気器具としては、ビデオカメラ、デジタルカメラ、プロジェクター、プロジェクションTV、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置、ノート型パソコンコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置などが挙げられる。それら電気器具の具体例を図28に示す。

10

20

30

40

50

**【0206】**

図28(A)は携帯電話であり、本体3001、音声出力部3002、音声入力部3003、表示部3004、操作スイッチ3005、アンテナ3006で構成される。本発明のアクティブマトリクス型表示装置は表示部3004に用いることができる。

**【0207】**

図28(B)はビデオカメラであり、本体3101、表示部3102、音声入力部3103、操作スイッチ3104、バッテリー3105、受像部3106で構成される。本発明のアクティブマトリクス型表示装置は表示部3102に用いることができる。

**【0208】**

図28(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体3201、カメラ部3202、受像部3203、操作スイッチ3204、表示部3205で構成される。本発明のアクティブマトリクス型表示装置は表示部3205に用いることができる。10

**【0209】**

図28(D)はゴーグル型ディスプレイであり、本体3301、表示部3302、アーム部3303で構成される。本発明のアクティブマトリクス型表示装置は表示部3302に用いることができる。

**【0210】**

図28(E)はリアプロジェクター(プロジェクションTV)であり、本体3401、光源3402、液晶表示装置3403、偏光ビームスプリッタ3404、リフレクター3405、3406、スクリーン3407で構成される。本発明は液晶表示装置3403に用いることができる。20

**【0211】**

図28(F)はフロントプロジェクターであり、本体3501、光源3502、液晶表示装置3503、光学系3504、スクリーン3505で構成される。本発明は液晶表示装置3503に用いることができる。

**【0212】**

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電気器具に適用することができる。

**【0213】****【発明の効果】**

30

本発明は、半導体装置を薄型化、軽量化し、フレキシビリティを与えるものである。一般に基板を薄くすれば、半導体装置の作製工程が困難なものとなるが、本発明では、作製工程中のみ適當な支持材を用いて作製しやすくしている。本発明は、SOI構造の集積回路、アクティブマトリクス型液晶表示装置、アクティブマトリクス型EL表示装置など、絶縁体上に形成された半導体装置に適用可能である。

**【0214】**

また、本発明を用いれば、配線間の絶縁膜を厚くとることができ、異なる層に形成された配線間に生じる寄生容量を低減できる。さらに、従来構造において絶縁膜を厚く形成した時の、絶縁膜に開孔部を設けて導通をとる問題や、配線材料の耐熱性の問題を解決している。40

**【図面の簡単な説明】**

**【図1】** 本発明の実施の形態を示す図。

**【図2】** 本発明の実施の形態を示す図。

**【図3】** 本発明の実施の形態を示す図。

**【図4】** 本発明の実施の形態を示す図。

**【図5】** 本発明の実施の形態を示す図。

**【図6】** 本発明の実施の形態を示す図。

**【図7】** 本発明の実施の一例を示す図。

**【図8】** 本発明の実施の一例を示す図。

**【図9】** 本発明の実施の一例を示す図。

50

- 【図10】 本発明の実施の一例を示す図。

- 【図11】 本発明の実施の一例を示す図。

- 【図12】 本発明の実施の一例を示す図。

- 【図13】 本発明の実施の一例を示す図。

- 【図14】 本発明の実施の一例を示す図。

- 【図15】 本発明の実施の一例を示す図。

- 【図16】 本発明の実施の一例を示す図。

- 【図17】 本発明の実施の一例を示す図。

- 【図18】 本発明の実施の一例を示す図。

- 【図19】 本発明の実施の一例を示す図。

- 【図20】 本発明の実施の一例を示す図。

- 【図21】 本発明の実施の一例を示す図。

- 【図22】 本発明の実施の一例を示す図。

- 【図23】 本発明の実施の一例を示す図。

- 【図24】 本発明を用いて作製されたアクティブマトリクス型EL表示装置を示す図。

- 【図25】 本発明を用いて作製されたアクティブマトリクス型EL表示装置を示す図。

- 【図26】 本発明を用いて作製されたアクティブマトリクス型EL表示装置を示す図。

- 【図27】 本発明の実施の一例を示す図。

- 【図28】 電気器具の一例を示す図。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

(B)

【図12】

【図13】

【図14】

【図15】

(B)

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図27】

【図26】

【図28】

---

フロントページの続き

(51)Int.Cl. F I

H 01L 21/02 (2006.01) H 01L 27/12 B

H 01L 27/12 (2006.01)

(56)参考文献 特開平02-154232 (JP, A)

特開平10-209464 (JP, A)

特開平11-261001 (JP, A)

特開平10-223833 (JP, A)

特開平06-268183 (JP, A)

特表平09-509792 (JP, A)

特開平11-017107 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1368

G09F 9/30

H01L 21/02

H01L 21/336

H01L 27/00

H01L 27/12

H01L 29/786