(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4708914号 (P4708914)

(45) 発行日 平成23年6月22日(2011.6.22)

(24) 登録日 平成23年3月25日(2011.3.25)

(51) Int. Cl. F I

HO4L 9/08 (2006.01) HO4L 9/00

HO4L 9/14 (2006.01) HO4L 9/00

HO4L 9/00

請求項の数 4 (全 21 頁)

特願2005-235212 (P2005-235212) (21) 出願番号 (22) 出願日 平成17年8月15日 (2005.8.15) (62) 分割の表示 特願平8-39099の分割 原出願日 平成8年2月2日(1996.2.2) (65) 公開番号 特開2005-341625 (P2005-341625A) (43) 公開日 平成17年12月8日 (2005.12.8) 審査請求日 平成17年8月18日 (2005.8.18) 審判番号 不服2009-20619 (P2009-20619/J1) 審判請求日 平成21年10月26日 (2009.10.26)

(73) 特許権者 000002185

601B

601E

641

ソニー株式会社

東京都港区港南1丁目7番1号

|(74)代理人 100086841

弁理士 脇 篤夫

|(74)代理人 100114122

弁理士 鈴木 伸夫

||(72) 発明者 江成 正彦

東京都品川区北品川6丁目7番35号 ソ

二一株式会社内

合議体

審判長吉岡浩審判官石井茂和

最終頁に続く

(54) 【発明の名称】解読化方法

## (57)【特許請求の範囲】

# 【請求項1】

暗号化されたデータと、該データの種類を示す情報と<u>該データが暗号化されているか否かを示す情報と</u>を含む送信データを受信し、前記暗号化されたデータを解読するようにした解読化方法であって、

メモリ手段に一つの前記データの種類を示す情報に対して割り当てられている、互いに 異なる複数の鍵情報を書き込む書き込みステップと、

受信した前記送信データの中に含まれる<u>データの種類を示す情報とデータが暗号化されているか否かを示す</u>情報<u>と</u>により指示された鍵情報を、前記メモリ手段から読み出す読み出しステップと、

該読み出しステップで読み出された鍵情報に基づいて前記暗号化されたデータを解読する解読ステップとを含んでおり、

前記書き込みステップの実行期間と、前記読み出しステップの実行期間とが重なった場合であって、書き込みアドレスと読み出しアドレスとが一致している場合は、前記書き込みステップの実行を禁止するようにした

解読化方法。

### 【請求項2】

暗号化されたデータと、該データの種類を示す情報と<u>該データが暗号化されているか否かを示す情報と</u>を含む送信データを受信し、前記暗号化されたデータを解読するようにした解読化方法であって、

一つの前記データの種類を示す情報に対して割り当てられている、互いに異なる複数の鍵情報を記憶しているメモリ手段から、前記受信した送信データ中の<u>データの種類を示す情報とデータが暗号化されているか否かを示す情報による</u>指示データに基づいていずれかの鍵情報を読み出す読み出しステップと、

該読み出しステップで読み出された前記鍵情報に基づいて前記暗号化されたデータを解 読する解読ステップとからなり、

前記読み出しステップでは、前記指示データにより<u>前記データの種類を示す情報の</u>鍵テーブルを参照することにより、前記メモリ手段から読み出す鍵情報をサーチしており、前記指示データの<u>データの種類を示す情報</u>に該当する前記鍵情報を読み出すための鍵アドレスが、前記鍵テーブルに2つ以上存在する場合は、最も<u>小さい</u>鍵アドレスを選択する解読化方法。

【請求項3】

暗号化されたデータと、該データの種類を示す情報と<u>該データが暗号化されているか否かを示す情報と</u>を含む送信データを受信し、前記暗号化されたデータを解読するようにした解読化方法であって、

一つの前記データの種類を示す情報に対して割り当てられている、互いに異なる複数の鍵情報を記憶しているメモリ手段から、前記受信した送信データ中の<u>データの種類を示す情報とデータが暗号化されているか否かを示す情報による</u>指示データに基づいていずれかの鍵情報を読み出す読み出しステップと、

該読み出しステップで読み出された前記鍵情報に基づいて前記暗号化されたデータを解 読する解読ステップとからなり、

前記読み出しステップでは、前記指示データにより<u>前記データの種類を示す情報の鍵</u>テーブルを参照することにより、前記メモリ手段から読み出す鍵情報の鍵アドレスをサーチしており、前記指示データ<u>のデータの種類を示す情報</u>により参照される鍵アドレスが前記データの種類を示す情報の鍵テーブルに存在していない場合は、鍵アドレスのサーチを行わないようにした

解読化方法。

## 【請求項4】

暗号化されたデータと、該データの種類を示す情報と<u>該データが暗号化されているか否かを示す情報と</u>を含む送信データを受信し、前記暗号化されたデータを解読するようにした解読化方法であって、

初期設定を行う初期ステップと、

メモリ手段に一つの前記データの種類を示す情報に対して割り当てられている、互いに 異なる複数の鍵情報を書き込む書き込みステップと、

前記メモリ手段から、前記受信した送信データ中の<u>データの種類を示す情報とデータが</u>暗号化されているか否かを示す情報による指示データに基づいていずれかの鍵情報を読み出す読み出しステップと、

該読み出しステップで読み出された前記鍵情報に基づいて前記暗号化されたデータを解 読する解読ステップとからなり、

前記読み出しステップでは、前記指示データにより<u>データの種類を示す情報の</u>鍵テーブルを参照することにより、前記メモリ手段から読み出す鍵情報の鍵アドレスをサーチしており、初期化期間内においては、サーチした結果、該当する鍵アドレスがないように、前記初期ステップにおいて初期処理される

解読化方法。

【発明の詳細な説明】

# 【技術分野】

## [0001]

本発明は、暗号化されることによりスクランブルされた送信データを受けて、解読するようにした解読化方法に関する。

【背景技術】

10

20

30

40

#### [0002]

通信における情報を秘匿するために、送信情報を暗号化し、暗号化された送信情報を受信して解読することにより、元の情報を得るようにした暗号化・解読化方式が従来から知られている。このような暗号化・解読化方式としては、米国における標準方式であるDES(Data Encryption Standard)等の暗号アルゴリズムが知られている。

#### [0003]

ところで、暗号アルゴリズムには多種・多様なものがあり、より安全性・高速性に優れた方式が開発されている。この一例として、米国特許第4,982,429号明細書、米国特許第5,103,479号明細書、および特開平1-276189号公報等に記載されている暗号方式(MULTI2方式)が知られている。

また、国際標準化機構(ISO)においてもISO9979/0009として登録された暗号化方式や、ISO/IEC10116として登録された暗号化利用モードがある。 【 0 0 0 4 】

上記MULTI2方式の暗号化方式においては、入力データサイズが64ビット、出力データサイズが64ビットとされており、256ビットサイズのシステム鍵と64ビットのデータ鍵から、暗号化を行うために必要な256ビットサイズのワーク鍵が生成されている。さらに、暗号化段数は正の整数段とされている。

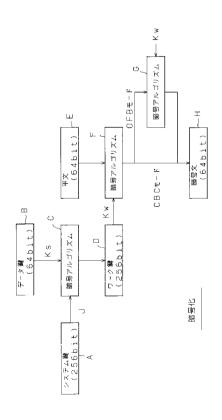

このMULTI2方式における暗号化アルゴリズムの概略構成を図17に示す。MULTI2方式は、図17に示すように64ビットのデータ鍵Ksに256ビットのシステム鍵Jを用いて暗号アルゴリズムの演算を施すことにより256ビットのワーク鍵Kwを生成する。この暗号アルゴリズムの演算は暗号アルゴリズム実行手段Cにより実行される。生成されたワーク鍵Kwは、暗号アルゴリズム実行手段Fに供給されて入力された64ビットの平文が暗号化される。なお、暗号アルゴリズム実行手段Cと暗号アルゴリズム実行手段Fとで実行される暗号アルゴリズムは、同一の暗号アルゴリズムである。

#### [0005]

このような暗号化がMULTI2方式の基本的な暗号化アルゴリズムであるが、これでは予め文字、あるいは単語が出現する頻度の分布を統計処理しておき、入手した暗号化文の文字列パターンの頻度分布とのマッチングを取ることにより、平文が推定されてしまうおそれがある。

そこで、暗号化された64ビットの暗号ブロックと、次に入力される64ビットの入力データとの排他的論理和を演算して暗号文を作成する手法がある。この手法を行って暗号化するモードをCBC(Cipher Block Chaining)モードとよんでいる。前記した暗号アルゴリズム実行手段Fにおいては、このようなCBCモードの暗号アルゴリズムが実行されている。

# [0006]

また、例えばパケット通信のように通信を行うデータの単位が予め決められている通信方式があるが、64ビットを1ブロックとするようなブロック暗号化方式では、1ブロックのビット数で割り切れないデータ単位が入力された場合に、データが余ってしまうようになる。そこで、その端数処理をOFB(Output Feedback)モードで処理するようにしている。

このOFBモードでは、データの端数部分が暗号アルゴリズム実行手段Gに供給され、 乱数を使用して暗号化される。この乱数は、ワーク鍵Kwを用いて暗号アルゴリズム実行 手段Gにより生成されている。これにより、64ビットを1ブロックとする暗号文を得る ことができるようになる。なお、CBCモードおよびOFBモードは暗号化利用モードと 呼ばれる。

# [0007]

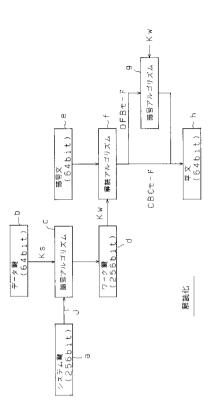

また、MULTI2方式における解読化アルゴリズムの概略構成を図18に示す。図18に示すように、64ビットのデータ鍵Ksに256ビットのシステム鍵Jを用いて暗号アルゴリズムの演算を施すことにより256ビットのワーク鍵Kwを生成する。この暗号アルゴリズムの演算は暗号アルゴリズム実行手段cにより実行される。生成されたワーク鍵Kw

10

20

30

40

は、解読アルゴリズム実行手段 f に供給されて入力された 6 4 ビットの暗号文が解読化される。

(4)

なお、OFBモードで暗号化されている暗号文は、暗号アルゴリズム実行手段gに供給され、ワーク鍵Kwを用いて暗号アルゴリズム実行手段gにより生成した乱数を使用することにより解読化される。これにより、1ブロック64ビットの暗号文を解読化して64ビットの平文を得ることができる。また、CBCモードとされている場合は、解読アルゴリズム実行手段fがCBCモードの解読アルゴリズムを実行するようにされる。

# [0008]

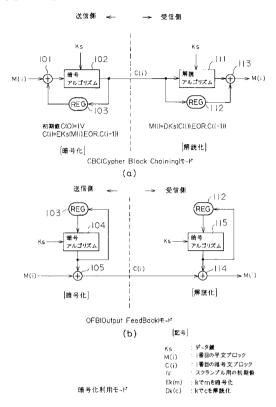

ここで、暗号化利用モードの説明を図19を参照しながら行うが、図19(a)にCBCモードの暗号化・解読化の概略構成を示し、図19(b)にOFBモードの暗号化・解読化の概略構成を示している。

CBCモードでは、図19(a)に示すように i 番目の平文ブロック M(i) は、排他的論理和回路101に入力され、レジスタ(REG)103により遅延された1ブロック前の暗号文ブロック C(i-1) との排他的論理和が演算される。演算されたデータは暗号アルゴリズム実行手段102において、データ鍵Ksに基づいて生成されたワーク鍵により暗号化される。この暗号化された i 番目の暗号文ブロック C(i) は、

C(i) = EKs(M(i) . EOR . C(i-1)) と表せる。ただし、EKs(m)はmをKsで暗号化することを意味しており、EORは排他的論理和の演算を行うことを示している。

# [0009]

そして、この暗号文ブロック C(i) は送信され、受信側において受信されることになる。受信された暗号文ブロック C(i) は、解読アルゴリズム実行手段 1 1 1 においてデータ鍵 K S に基づいて生成されたワーク鍵を用いて解読され、排他的論和回路 1 1 3 に供給される。この排他的論理和回路 1 1 3 にはレジスタ(R E G) 1 1 2 において遅延された、1 ブロック前の暗号文ブロック C(i-1) が入力されて、両者の排他的論和が演算される。この時、送信側と受信側のデータ鍵 K S は等しく、これにより、排他的論理和回路 1 1 3 から i 番目の平文ブロック M(i) が解読される。i 番目の平文ブロック M(i) は次のように表せる。

M(i) = DKs(C(i) . EOR.C(i-1))ただし、DKs(c)はKsでcを解読化することを示している。

## [0010]

また、OFBモード時では、i番目の平文ブロックM(i) は排他的論理和回路105に供給される。この排他的論理和回路105には、データ鍵Ksに基づいて生成されたワーク鍵により乱数化された暗号アルゴリズム実行手段104の出力が供給されている。なお、暗号アルゴリズム実行手段104の出力は、レジスタ103により1ブロック遅延されて暗号アルゴリズム実行手段104に戻されている。これにより、排他的論理和回路105からは乱数により暗号化された暗号文ブロックC(i)が出力される。

## [0011]

#### [0012]

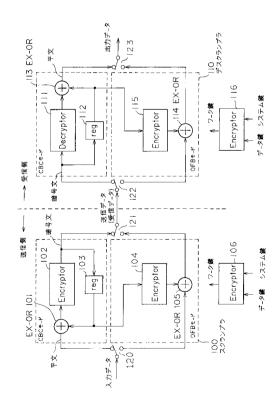

以上説明した暗号化利用モードを有する暗号化・解読化方式の概略構成を図20に示す

この図において、送信側にはスクランブラ100が備えられており、スクランブラ10

20

10

30

40

0により入力データがスクランブルされて送信されている。このスクランブルされた送信データは、空間等の伝送路を伝播されて受信側で受信される。受信側には、デスクランブ ラ110が備えられており、このデスクランプラ110によりスクランブルされた送信データがデスクランブルされて、元のデータに戻され出力されるようになる。

# [0013]

スクランブラ100は、入力された入力データ(平文)を暗号化する暗号アルゴリズム実行手段であるEncryptor 102と、レジスタ103と、排他的論理和回路(EX-OR)101からなるCBCモード暗号化部と、暗号アルゴリズム実行手段であるEncryptor 104と、排他的論理和回路(EX-OR)105からなるOFBモード暗号化部から構成されている。なお、データ鍵とシステム鍵からワーク鍵を生成するEncryptor 106もスクランブラ100内に備えられている。生成されたワーク鍵はEncryptor 102,104に供給される。

ところで、Encryptor 102、Encryptor 104、Encryptor 106は同一構成とされているので、1つのEncryptor により3つのEncryptor を兼用することができる。CBCモード暗号化部およびOFBモード暗号化部の動作は前述したとおりであるので、ここでは省略する。

## [0014]

また、デスクランブラ 1 1 0 は、入力された受信データ(暗号文)を解読化する解読アルゴリズム実行手段であるDecryptor 1 1 1 と、レジスタ 1 1 2 と、排他的論理和回路(E X - O R ) 1 1 3 からなる C B C モード解読化部と、暗号アルゴリズム実行手段であるEncryptor 1 1 5 と、排他的論理和回路(E X - O R ) 1 1 4 からなる O F B モード解読化部から構成されている。なお、データ鍵とシステム鍵からワーク鍵を生成するEncryptor 1 1 6 もデスクランブラ 1 1 0 内に備えられている。生成されたワーク鍵はDecryptor 1 1 1 と、Encryptor 1 1 5 に供給される。

なお、Encryptor 1 1 5、Encryptor 1 1 6 は同一構成とされているので、1つのEncryptor により2つのEncryptor を兼用することができる。また、CBCE-F解読化部およびOFBE-F解読化部の動作は前述したとおりであるので、ここでは省略する。

#### 【発明の開示】

【発明が解決しようとする課題】

# [0015]

ところで、上述したMULTI2方式のような高度な暗号化・解読化方式を、ソフトウェアで実現して使用する場合には、現在の演算手段の演算速度ではリアルタイム処理を行うことができない。すなわち、例えば衛星ディジタルテレビジョン放送等に適用した場合は、画像や音声を途切らせないでリアルタイム再生する必要があることから、受信側における解読化処理は高速な処理の可能なハードウェアで行わなければならないことになる。

しかしながら、受信側においてリアルタイムで全ての解読処理を完了することができる ハードウェアは、複雑な処理を行うことから大型なものになるという問題点があった。

## [0016]

そこで、本発明は高度な暗号化方式でスクランブルされたデータを、受信側においてリアルタイムで全ての解読処理を小型かつ安価なハードウェアを用いて完了することができる解読化方法を提供することを目的としている。

#### 【課題を解決するための手段】

# [0017]

上記目的を達成するために、本発明の解読化方法は、暗号化されたデータと、該データの種類を示す情報と<u>該データが暗号化されているか否かを示す情報と</u>を含む送信データを受信し、前記暗号化されたデータを解読するようにした解読化方法であって、メモリ手段に一つの前記データの種類を示す情報に対して割り当てられている、互いに異なる複数の鍵情報を書き込む書き込みステップと、受信した前記送信データの中に含まれる<u>データの種類を示す情報とデータが暗号化されているか否かを示す情報と</u>により指示された鍵情報を、前記メモリ手段から読み出す読み出しステップと、該読み出しステップで読み出され

10

20

30

40

た鍵情報に基づいて前記暗号化されたデータを解読する解読ステップとを含んでおり、前記書き込みステップの実行期間と、前記読み出しステップの実行期間とが重なった場合であって、書き込みアドレスと読み出しアドレスとが一致している場合は、前記書き込みステップの実行を禁止するようにしている。

#### [0018]

また、上記目的を達成するために、本発明の他の解読化方法は、前記複数の鍵情報を記憶しているメモリ手段から、入力データ中の指示データに基づいていずれかの鍵情報を読み出す読み出しステップと、該読み出しステップで読み出された前記鍵情報に基づいて前記入力データを解読する解読ステップとからなり、前記読み出しステップでは、前記指示データにより鍵テーブルを参照することにより、前記メモリ手段から読み出す鍵情報をサーチしており、前記指示データに該当する前記鍵情報を読み出すための鍵アドレスが、前記鍵テーブルに2つ以上存在する場合は、最も少ない鍵アドレスを選択するようにしている。

## [0019]

さらにまた、上記目的を達成するために、本発明のさらに他の解読化方法は、前記複数の鍵情報を記憶しているメモリ手段から、入力データ中の指示データに基づいていずれかの鍵情報を読み出す読み出しステップと、該読み出しステップで読み出された前記鍵情報に基づいて前記入力データを解読する解読ステップとからなり、前記読み出しステップでは、前記指示データによりテーブルを参照することにより、前記メモリ手段から読み出す鍵情報の鍵アドレスをサーチしており、前記指示データにより参照される鍵アドレスが前記テーブルに存在していない場合は、鍵アドレスのサーチを行わないようにしている。

## [0020]

さらにまた、上記目的を達成するために、本発明のさらに他の解読化方法は、初期設定を行う初期ステップと、メモリ手段に複数の鍵情報を書き込む書き込みステップと、前記メモリ手段から、入力データ中の指示データに基づいていずれかの鍵情報を読み出す読み出しステップと、該読み出しステップで読み出された前記鍵情報に基づいて前記入力データを解読する解読ステップとからなり、前記読み出しステップでは、前記指示データにより鍵テーブルを参照することにより、前記メモリ手段から読み出す鍵情報の鍵アドレスをサーチしており、初期化期間内においては、サーチした結果、該当する鍵アドレスがないように、前記初期ステップにおいて初期処理されるようにしている。

# [0021]

このような本発明の解読化方法によれば、解読処理を行うために必要な鍵情報が格納されているメモリ手段の読み出しおよび書き込み制御を適切に行うことができるため、メモリ制御を容易に行うことのできる解読化方法とすることができる。したがって、受信側においてリアルタイムで全ての解読処理を行うことのできる解読化方法とすることができる

また、このような解読化方法を実行する解読手段を備える電子機器においては、メモリ制御手段の構成を簡単化することができるので、電子機器を小型かつ安価に提供することができるようになる。

# 【発明の効果】

#### [0022]

本発明は以上のように構成されているので、解読処理を行うための鍵情報が格納されているメモリ手段の読み出しおよび書き込み制御を適切に行うことができ、メモリ制御を容易に行うことのできる解読化方法とすることができる。したがって、受信側においてリアルタイムで全ての解読処理を実行することのできる解読化方法とすることができる。

また、このような解読化方法を実行する解読手段を備える電子機器におけるメモリ制御手段の構成を小さくすることができるので、電子機器を小型かつ安価に提供することができるようになる。

# 【発明を実施するための最良の形態】

10

20

30

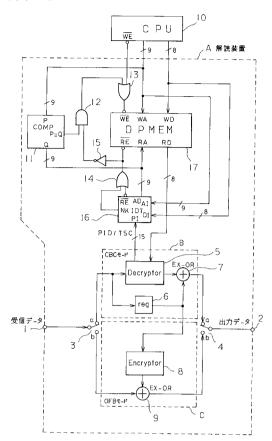

#### [0023]

本発明の解読化方法の実施の形態である解読装置の構成例を示すブロック図を図 1 に示す。

この図において、解読装置AはCBCモードの解読化部Bと、OFBモードの解読化部Cと、パケットID(PID)テーブルを備えるデータ鍵間接検索器(IDT)16と、入力データの暗号化に使用されたデータ鍵を解読化部B,Cに渡すデュアルポートメモリ(DPMEM)17と、DPMEM17の書き込みアドレスと読み出しアドレスとを比較する比較器(COMP)11から構成されている。

### [0024]

解読装置Aの端子1には受信データである暗号文データが入力され、この暗号文データは切換手段3に入力される。この時、CBCモードとされた場合は、切換手段3、および切換手段4が共に端子a側に切り換えられ、入力された暗号文データはCBCモード解読化部Bに供給されて解読化されて出力される。また、OFBモードとされた時は、切換手段3、および切換手段4は共に端子b側に切り換えられて、暗号文データはOFBモード解読化部C側に入力される。そして、入力された暗号文データは、OFBモード解読化部Cにおいて解読化されて平文データが出力される。

CBCモード解読化部B、およびOFBモード解読化部Cにおいて、入力された暗号文データは解読処理されて平文データとされるが、その解読化アルゴリズムは、前記図18に示す解読化アルゴリズムと同様である。なお、この場合解読処理に必要なデータ鍵はDPMEM17から供給される。

#### [0025]

また、端子1に入力される受信データのフォ・マットは、例えばISO/IEC13818として規定されているトランスポートストリーム(以下、TSと記す。)とされる。TSは188バイトのパケット構造とされており、通常4バイトのヘッダのあとに184バイトのペイロードが続くようにされている。さらに、伝送エラーに対するエラー訂正のためにパリティーを付加することから、16バイトのパリティ用のダミー期間が付加されて、これらの繰返しのストリームとされる。

#### [0026]

このTSのヘッダにはパケットが映像データで構成されているのか、音声データで構成されているのか、あるいは他のデータで構成されているのかを示すPID情報や、暗号化されているTSなのか否かを示すTSC(Transport Scrambling Control)フラグ等が含まれており、図示しない解析部においてヘッダを解析することにより、これらのパケットの属性が解釈されている。

この時、TSCにより暗号化されていないパケットと解釈された場合は、解読化処理を施すことなくTSを遅延部を通してそのまま出力するようにする。この遅延部の遅延時間は、解読装置Aが解読処理に要する時間と等しくされる。

# [0027]

また、1つのPIDに対しては、データ鍵Kse(Ks\_even )とデータ鍵Kso(Ks\_o dd)との2つが割り当てられている。これは、データ鍵が数秒ないし数十秒毎に更新されるため、更新に間に合うようにデータ鍵の書き替えを行う必要があること、および、解読処理時にはデータ鍵Kseとデータ鍵Ksoはその一方しか使用されず、使用されていないデータ鍵を更新可能として、そのデータ鍵を更新することができるからである。すなわち、データ鍵を更新する更新制御を容易に行うためである。

なお、前記解析部は図示しないが、例えばCBCモード解読化部Bに備えられており、 CBCモード解読化部Bから15ビットのデータサイズのPID/TSC情報がIDT1 6に送られている。

#### [0028]

IDT16においては、受けた13ビットサイズのPID情報を用いてPIDテーブルを参照し、PIDから読出されたアドレス情報と、2ビットサイズのTSC情報とを組み合わせてDPMEM17の読出アドレスRA(データサイズは9ビット)を生成している

10

20

30

40

。生成された読出アドレスRAは<u>AD</u>端子からDPMEM17のRA端子に供給され、この時にリードイネーブル(RE)信号がアクティブ状態になるよう制御して、読出アドレスRAに該当するデータ鍵をDPMEM17から読み出している。読み出されたデータ鍵は、入力されたTSの暗号化時に使用されたデータ鍵と等しく、端子RDから出力されてDecryptor 5に供給される。

Decryptor 5 は、供給されたデータ鍵と、システム毎に異なるシステム鍵からワーク鍵を生成して、生成されたワーク鍵に基づいて入力された暗号文データの解読処理を行う。 なお、システム鍵は予めCPU10から解読装置Aに渡されている。

## [0029]

また、CPU10は解読化部B,Cで必要とされる更新されるデータ鍵を、解読処理において必要になる前にDPMEM17に書き込むようにされており、書き込む場合には、ライトイネーブル(WE)をアクティブ状態とすると共に、9ビットのデータサイズの書込アドレス(WA)と、8ビットのデータサイズのデータ鍵の書込データ(WD)をDPMEM17に供給している。この場合、CPU10にはROMやRAMが備えられており、これらのメモリに解読装置Aに与えるデータが書き込まれている。

なお、DPMEM17にデータ鍵情報を書き込む時に、書込アドレスと同一の読出アドレスでIDT16がデータ鍵を読み出すようになった場合は、読み出されたデータが不定となることから、この時はDPMEM17への書き込みを禁止している。

#### [0030]

このために、比較器 1 1 とアンドゲート 1 2 、オアゲート 1 3 , 1 4 、インバータ 1 5 が設けられている。この動作を説明すると、IDT 1 6 から出力される読出アドレスRAと、CPU 1 0 から出力される書込アドレスWAとが比較器 1 1 のP端子およびQ端子にそれぞれ入力される。そして、P端子の入力データとQ端子の入力データとが一致(P=Q)した時に、比較器 1 1 からハイレベル信号が出力される。この時、反転REがローレベルでアクティブ状態になっていると、インバータ 1 5 からハイレベルが出力されるので、結局のところアンドゲート 1 2 からハイレベルが出力されることになる。このアンドゲート 1 2 の出力はオアゲート 1 3 に入力されて、オアゲート 1 3 の出力がハイレベルとされるので、反転WEは非アクティブ状態となり、DPMEM 1 7 への書き込みが禁止されることになる。

# [0031]

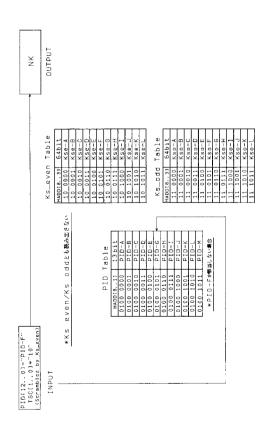

次に、CPU10から見た解読装置 AOUジスタのメモリ空間を図3に示すが、9ビットのデータサイズのアドレス(<math>HADD)の上位 6ビットが "000100 とされた 64 bit x10 エリアが、CBC1 モードの初期値テーブル(CBC1 Initial value table )に割り当てられている。この初期値テーブルに記憶される初期値は、電源投入時等に実行される初期処理時に、CBC1 モード解読化部 B1 に供給されてレジスタ 61 にセットされる。

また、アドレス(HADD)の上位 4 ビットが "0010 "とされた 2 5 6 bit  $\times$ 1のエリアが、システム鍵テーブル(SYSTEM\_Key table)に割り当てられている。このシステム鍵はシステム毎に異なるものとされるが、1つのシステムでは固定された鍵である。

# [0032]

さらに、アドレス(HADD)の上位 4 ビットが " 0 1 0 0 " とされた 1 3 bit  $\times$  1 2 のエリアが、 PIDテーブル (PID value table ) に割り当てられている。この PIDテーブルはパケット化されたデータ種類を示す情報であり、 1 チャンネルでは最大 1 2 種類とされデータ種類毎に異なる PIDとされる。

なお、システム鍵テーブルは所定のレジスタに、 P I D テーブルの情報は I D T 1 6 に 、初期処理時に C P U 1 0 から書き込まれる。

# [0033]

さらにまた、アドレス(HADD)の上位 2 ビットが " 1 0 " とされた 6 4 bit  $\times$  1 2 のエリアが、データ鍵 K s e テーブル (Ks\_even value table ) に割り当てられ、アドレス(HADD)の上位 2 ビットが " 1 1 " とされた 6 4 bit  $\times$  1 2 のエリアが、データ鍵 K s o テーブル (Ks\_odd value table) に割り当てられている。このデータ鍵 K s e テー

10

20

30

40

20

30

40

50

ブル、およびデータ鍵 K s o テーブルの情報は D P M E M 1 7 に書き込まれるが、数秒ないし数 1 0 秒の所定タイミング毎に、 C P U 1 0 により更新されている。

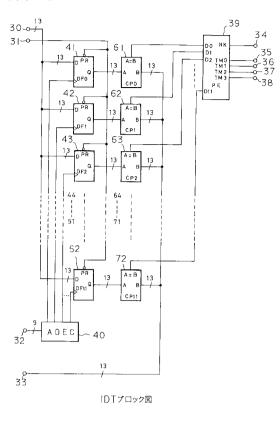

#### [0034]

次に、IDT16の詳細構成の一例を示すブロック図を図 2に示す。この図において、 41~52はそれぞれ 13ビット幅を有する 12個のフリップフロップ(DF0~DF11)であり、 61~72はそれぞれ 13ビット幅を有する 12個の比較器(CP0~CP11)である。また、 40はアドレスデコーダ(ADEC)であり、 9ビットのデータサイズのアドレス情報が入力されると、 12本の出力のうちの 1本だけに、 DF0~DF11のいずれかをアクティブにする出力が出される。 さらに、 39はプライオリティ・エンコーダ(PE)であり、 TSC情報と組み合わされるアドレス情報 TMP0~TMP3が出力される。

### [0035]

このIDT16において、端子30にはCPU10から出力された8ビットのデータサイズのPID情報が、13ビットのデータサイズに展開されて入力される。また、端子32にはCPU10から出力された9ビットのデータサイズのアドレス情報が入力され、ADEC40においてデコードされる。このデコード出力はストローブ信号としてDF0~DF11に入力され、DF0~DF11のうちのいずれか1つのみがラッチ可能とされる

この時、入力された13ビットのデータサイズのPID情報は、12個のDF0~DF11に共通に入力されており、ADEC40のデコード出力によりDF0~DF11が順次1つづつ選択されて、供給されているPID情報がラッチされる。このようにして、DF0~DF11によりPIDテーブルが構成されるようになる。

#### [0036]

また、端子33には13ビットのデータサイズのPID情報が入力され、比較器CP0~CP11のB入力端子に共通に入力される。このPID情報は、CBCモード解読化部Bにおいて、受信データであるパケットのヘッダから抽出されてIDT16に供給された15ビットのデータサイズのPID/TSC情報のうちの13ビットのデータサイズのPID情報である。

この場合、比較器 C P 0 ~ C P 1 1 には D F 0 ~ D F 1 1 よりの P I D 情報がそれぞれ A 端子に入力されており、端子 3 3 より入力された P I D 情報と一致する P I D 情報が A 端子に入力されている比較器から一致信号が出力される。従って、 P I D テーブルにある P I D 情報が端子 3 3 から入力されると、 C P 0 ~ C P 1 1 のいずれか 1 つから一致信号が出力される。

# [0037]

この  $CP0 \sim CP110$  論理表を図 4 に示すが、 $CP0 \sim CP110$  A 端子および B 端子にオール "1 "が入力されていない時は、一致した時(A=B)に "1 "信号が出力される。また、一致してない時は "0 "が出力される。

さらに、PE39の論理表を図5に示す。このPE39の論理表において、例えば、CP2から"1"信号が出力された時は、PE39からは"0010"の4ビット(TMP0~TMP3)のデータが出力される。このPE39では図5に示すように、D0が最も優先された入力とされ、D11が最下位の優先度の入力とされる。

ところで、DF0~DF11に設定されたPIDテーブルのPID情報と一致しないPID情報が入力されることがあるが、この場合にはPEにオール "0 "が入力されることになる。この時、PEのNK出力が "1 "となる。なお、NK出力が "1 "の時には、後述するデータ鍵の鍵テーブルを読みに行くことが禁止される。

#### [0038]

また、電源投入時等の初期処理時には端子31のレベルが "0 "となり、DF0~DF 11が全てプリセットされることから、DF0~DF11から "1 "が出力される。従って、この場合はCP0~CP11からオール "0 "が出力されることになり、上述のよう にデータ鍵の鍵テーブルを読みに行くことが禁止される。

なお、鍵テーブルを読みに行くことが禁止されている時は、鍵テーブルが使用されないので、この鍵テーブルにCPU10からデータ鍵を書き込むことができる。すなわち、データ鍵の初期設定をすることができる。また、端子31はパワーオンリセット端子であり、所定時間後にそのレベルは"1"に復帰する。

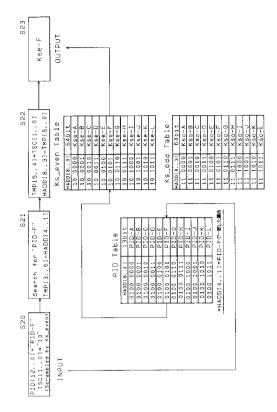

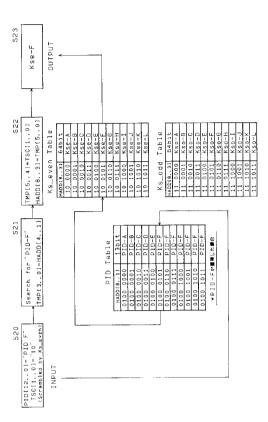

# [0039]

次に、受信データ中のPID情報とTSC情報により、データ鍵の鍵テーブルをサーチする動作を図6を参照しながら説明する。

図 6 に示すステップ S 2 0 にて、受信データのヘッダから 1 3 ビットのデータサイズの P I D 情報として "P I D - F "が、 2 ビットのデータサイズの T S C 情報として "1 0 "が入力されたとする。この "10"は、データ鍵 K s e でスクランブルされていることを示しているものとする。

次いで、ステップS21にてこのPID情報はCP0~CP11のA端子に入力されて、DF0~DF11に格納されているPID情報と比較される。この結果、CP5から "1 "信号が出力され、PE39のTEMP3~TEMP0の出力TMP[3..0]が、 "0101 "となる。すなわち、"PID-F"がサーチされる。この、PE39の出力である"0101 "は、アドレスHADDの第4ビットから第1ビットとされる。

### [0040]

次いで、ステップS22にてTSC情報TSC[1..0]の2ビット("10")が HADDの第5ビット,第6ビットとされて、6ビットサイズのアドレスHADD[8. .3]が生成される。したがって、アドレスHADD[8..3]は"100101"と なる。

そして、ステップ S 2 3 にて、生成された " 1 0 0 1 0 1 "のアドレスHADD [ 8 . . 3 ] により鍵テーブルを参照すると、Ks\_even Table から 6 4 ビット幅のデータ鍵 K s e - F が得られるようになる。そして、得られたデータ鍵 K s e - F に基づいて入力された暗号文の解読が解読装置 A で実行される。

このように、本発明の解読化方法では間接的にデータ鍵を検索する間接検索方法としているので、PID情報に対応する13ビット幅のテーブルを用意することなく、6ビット幅の鍵テーブルを用意すればよいのでメモリの容量を削減して小型化することができる。

# [0041]

なお、このように解読中では鍵テーブルのKs\_even Table ,Ks\_odd Table の一方しか使用されないため、使用していない鍵テーブルのデータ鍵を更新することができる。これは、前述したようにCPU10が実行するが、CPU10のタイミングと解読装置Aのタイミングとは非同期で動作するので、CPU10は非同期で更新するデータ鍵を書き込みに行く。

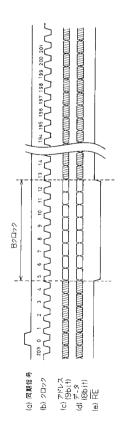

このため、鍵テーブルの格納されるデュアルポートメモリ17においては、前述したように書き込みと読み出しが同時に同一アドレスで行われる場合が生じるのである。この時のタイミング例を図9に示すが、図示するタイミングで8クロック幅の反転REが発生した場合には、この8クロック期間においては、前述したようにCPU10からの同一アドレスの書き込みが禁止される。

# [0042]

ところで、何らかの原因によりPIDテーブルに同一のPIDが格納されている場合が生じる。例えば、1チャンネル当り最大12種類のPID情報とされるが、12種類のPIDを必要としない場合はPIDテーブルには12種類のPIDを書き込む必要はなく、必要する種類のPIDだけを書き込むことになる。すると、書き込まれていないPIDの欄のデータが偶然PIDと同じデータになることがある。

このような場合には、誤ったデータ鍵を読み出して解読できなくなってしまう恐れがあるので、本発明においては次のようにしてこれを防止している。

## [0043]

図 7 に示すように P I D テーブルに複数の " P I D - F " がある場合は、その内のアド

10

20

30

40

20

30

40

50

レスHADDが小さい方を優先するようにしている。これは、アドレスHADDの小さい方からPIDテーブルに書き込みに行くので、アドレスHADDの大きい方が誤っている確率が高いからである。

これにより、 P I D 情報として " P I D - F "が入力されると、アドレスHADD[ 8 . . . 1 ]として " 0 1 0 0 0 1 0 1 "が得られるようになり、前述した処理と同様の処理が行われ、Ks\_even Table から 6 4 ビット幅のデータ鍵 K s e - F が得られるようになる

# [0044]

また、入力データのヘッダからのPID情報により、PIDテーブルを参照しても該当するPIDがない場合がある。例えば、図8に示すようにPID情報として"PID-F"が入力されても、PIDテーブル中には"PID-F"に該当するPIDがない。

このような場合には、鍵テーブルのKs\_even Table , Ks\_odd Table のいずれも読みに行くことなく、データ鍵を読み出さない。この場合は、入力データである T S はそのまま出力することになる。

### [0045]

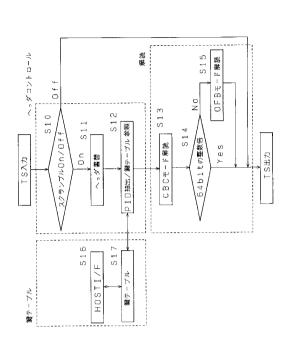

次に、図1に示す解読装置Aの解読フローを図10に示すが、トランスポートストリーム(TS)が入力されると、ステップS10にてスクランブルされているか否かが判定される。この判定はスクランブルされたことを示すヘッダ中のフラグが立っているか否かを検出することにより判定される。この場合、フラグが立っている場合はスクランブルonと判定されて、ステップS11に進み、ここで所望のフラグ等の書き換えが行われる。次いで、ステップS12にてヘッダからPID情報が抽出されて、鍵テーブルが参照される。この場合の鍵テーブルは、鍵テーブル処理のステップS16にてホストインターフェース処理が行われて、ステップS17にて書き込まれた鍵テーブルが参照される。

なお、ステップS12の処理は、前記図6に示す処理である。

#### [0046]

以上のステップ S 1 0 ないしステップ S 1 2 の処理がヘッダコントロール処理である。 なお、ステップ S 1 0 にてスクランブル o f f と判定された場合には、 T S はそのまま出力される。

次いで、ステップS13にてCBCモードの解読処理が行われ、ステップS14にて解読処理される暗号文が64ビットの整数倍か否かが判定される。暗号文に端数がありNoと判定された場合は、ステップS15にて端数部分についてOFBモードの解読処理が行われ、解読処理された平文が出力される。また、ステップS14にて64ビットの整数倍と判定された場合は、解読処理された64ビットの平文が出力されるようになる。

# [0047]

ところで、図10に示すような解読フローの実行は、前記図18に示す解読化アルゴリズムにより実行されている。図18に示す解読化アルゴリズムは前述したとおりであるのでここでは省略するが、解読化アルゴリズム中の解読アルゴリズムおよび暗号アルゴリズムを実行する構成の詳細を図11ないし図15を参照して説明する。

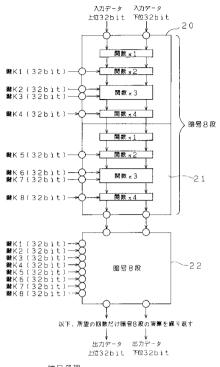

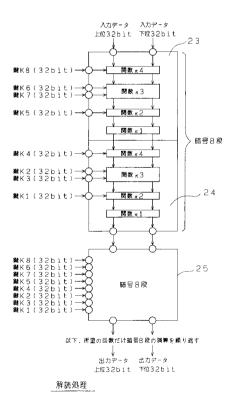

図11は暗号アルゴリズムを実行する暗号処理の構成を示す。図11において、64ビット幅の入力データは、上位32ビットのデータと下位の32ビットのデータに分割されて最初の暗号8段に入力される。この暗号8段は、関数の演算を行う4段の演算段が2回繰り返された構成とされる。そして、入力された上位32ビットのデータと下位の32ビットのデータに、演算段20の初段において関数 1の演算が施される。ついで、第2段において初段の出力に関数 2の演算が施される。この場合、第2段には32ビット幅のワーク鍵 K 1 が入力され、このワーク鍵 K 1 を用いて第2段の演算が行われている。

# [0048]

さらに、第3段において第2段の出力に関数 3の演算が施される。この場合、第3段には32ビット幅のワーク鍵 K2, K3が入力され、このワーク鍵 K2, K3を用いて演算が行われている。続いて、第4段において第3段の出力に関数 4の演算が施される。この場合、第4段には32ビット幅のワーク鍵 K4が入力され、このワーク鍵 K4を用い

て演算が行われている。

さらに残る4段の演算を行う演算段21において、演算段20からの出力に初段において関数 1の演算が施される。ついで、第2段において初段の出力に関数 2の演算が施される。この場合、第2段には32ビット幅のワーク鍵K5が入力され、このワーク鍵K5を用いて演算が行われている。

#### [0049]

さらに、第3段において第2段の出力に関数 3の演算が施される。この場合、第3段には32ビット幅のワーク鍵 K 6 , K 7 が入力され、このワーク鍵 K 6 , K 7 を用いて演算が行われている。続いて、第4段において第3段の出力に関数 4 の演算が施される。この場合、第4段には32ビット幅のワーク鍵 K 8 が入力され、このワーク鍵 K 8 を用いて演算が行われている。

このようにして暗号処理の行われた上位32ビット、下位32ビットの合計64ビット幅のデータは、さらに暗号8段22に入力される。この暗号8段22において、上述した暗号8段の演算と同様の演算が施されて、上位32ビット、下位32ビットの合計64ビット幅のランダム化された出力データが得られる。

#### [0050]

なお図示しているように、暗号 8 段の繰返し数は 2 回に限らず、所望の回数繰り返すことができる。この回数を多く繰り返すほど、出力データは高度にランダム化されて、暗号強度を強いものとすることができる。

なお、演算段の格段で行われている関数の演算は、一定の規則に従ってある文字を他の 文字に置き換える換字と、文字の順序を入れ替える転置を行う演算とされている。

#### [ 0 0 5 1 ]

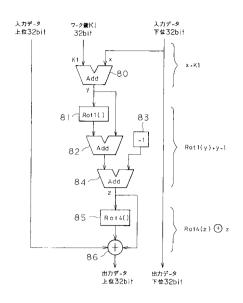

次に、解読アルゴリズムを実行する解読処理の構成を図12に示すが、前述した暗号処理と異なる点は、暗号処理の構成の出力側から逆に演算を行うようにしている点である。すなわち、暗号8段のうちの最初の4段の演算段23においては、上位32ビットと下位32ビットに分割された64ビット幅の暗号化されている入力データに、32ビット幅のワーク鍵 K 8 を用いて関数 4 の演算を施している。次いで、第2段目において、初段の出力データにワーク鍵 K 7 を用いて関数 3 の演算を施している。さらに、第3段目において、第2段の出力データにワーク鍵 K 6 , K 7 を用いて関数 2 の演算を施している。さらにまた第3段目において、第2段の出力データにワーク鍵 K 5 を用いて関数 2 の演算を施し、第4段目において、第3段の出力データに関数 1 の演算を施している。

# [0052]

このような 4 段の演算が、演算 2 4 においてワーク鍵 K 4 ~ K 1 を用いて同様に行われる。

さらに、上記した暗号 8 段の演算が縦続されている暗号 8 段 2 5 においても実行されて、解読化された上位 3 2 ビット、下位 3 2 ビットの計 6 4 ビット幅の出力データが得られるようになる。なお、暗号 8 段の繰り返し回数は、暗号処理において実行された暗号 8 段の繰返し回数と同じ回数とされる。

# [0053]

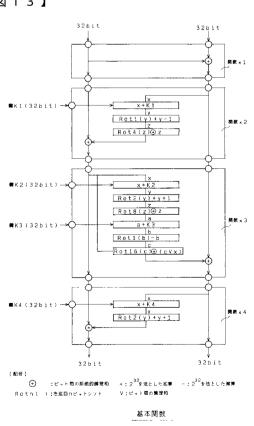

次に、演算段で行われている演算の詳細を暗号処理の演算段20を例に上げて図13を参照しながらに詳細に説明する。

初段の関数 1の演算では、入力された32ビットに分割された上位ビットは、演算されることなくそのまま出力され、上位ビットと下位ビットの排他的論理和が演算されて下位ビットとして出力される。

続く、第2段の関数 2の演算では、下位32ビットのデータ×にワーク鍵 K 1 が加算されて、x + K 1 がまず演算される。次いで、x + K 1をyとした時に、yを1ビット左巡回シフトし、その値にy - 1を加算してzを得る。次に、zを4ビット左巡回シフトし、その値とzとの排他的論理和を得る。この演算結果と、上位32ビットの排他的論理和が演算されて、演算された上位32ビットのデータが出力される。この場合、下位32ビットは入力されたデータが、演算されることなくそのまま出力される。

10

20

30

20

30

40

50

#### [0054]

また、第3段の関数 3の演算では、上位32ビットのデータ×にワーク鍵 K2 が加算されて、X+K2 がまず演算される。次いで、X+K2 を Y とした時に、Y を Y と Y と Y と Y と Y と Y を Y と Y と Y と Y と Y と Y と Y と Y と Y と Y の値と Y と Y と Y と Y と Y の Y と Y の Y と Y の Y と Y の Y と Y の Y と Y の Y と Y の Y と Y の Y と Y の Y と Y の Y と Y の Y と Y の Y と Y の Y と Y の Y と Y の Y と Y の Y と Y の Y と Y の Y と Y と Y と Y の Y と Y の Y と Y と Y と Y と Y と Y と Y と Y の Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と Y と

さらに、aにワーク鍵 K 3 が加算されて、a+ K 3 が演算される。次いで、a+ K 3 を b とした時に、 b を 1 ビット左巡回シフトし、その値に - b を加算して c を得る。次に、aと x のビット毎の論理和と、 c を 1 6 ビット左巡回シフトした値との排他的論理和を演算する。この演算結果と、下位 3 2 ビットのデータとの排他的論理和を演算して、演算された下位 3 2 ビットのデータを出力する。なお、上位 3 2 ビットのデータは、演算されることなくそのまま上位 3 2 ビットの出力データとなる。

[0055]

さらにまた、第4段の関数 4の演算では、下位32ビットのデータ×にワーク鍵K4が加算されて、x+K4がまず演算される。次いで、x+K4をyとした時に、yを2ビット左巡回シフトし、その値にy+1を加算する。この演算結果と、上位32ビットの排他的論理和が演算されて、演算された上位32ビットのデータが出力される。この場合、下位32ビットのデータは演算されることなく、そのまま下位32ビットのデータとして出力される。

[0056]

上記演算において、ワーク鍵 K 1 ~ K 4 をデータに加算することにより、文字を他の文字で置き換える換字処理が行われ、データを巡回シフトさせることにより文字の位置を入れ替える転置が行われる。このように、換字と転置のアルゴリズムを行うことにより平文が暗号文に暗号化される。

また、解読化する場合には、暗号化と逆の換字と転置のアルゴリズムを行うことにより元の平文に解読することができる。

[0057]

次に、上述した関数の演算を行う構成をさらに詳細に説明するが、関数 2の例を図 1 4に上げて説明するものとする。

図14において、第1加算器Add80において、下位32ビットの入力データ×と32ビットのワーク鍵K1とが加算され、加算データyが出力される。この加算データyは第1左巡回シフター81において1ビット左巡回シフトされると共に、第2加算器82において、第1左巡回シフター81の出力と加算される。この加算結果に第3加算器84において-1が加算されて、データzが演算される。このデータzは第2左巡回シフター85において4ビット左巡回シフトされると共に、排他的論理和回路86に供給される。この排他的論理和回路86には第2左巡回シフター85の出力データ、データz、上位32ビット入力データが入力され、3つのデータの排他的論理和が演算される。

この演算結果は、次段に入力される上位32ビット入力データとなる。また、下位32ビット入力データは、演算されることなく次段に入力される下位32ビット入力データとなる。

[0058]

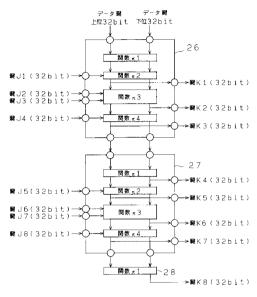

次に、64ビット幅のデータ鍵と256ビット幅のシステム鍵から256ビット幅のワーク鍵を生成する鍵スケジュール処理の構成を図15に示す。

鍵スケジュール処理は図15に示すように4段の演算段26,27が2段と、1段の演算段28が1段縦続接続された構成とされている。また、4段の演算段26,27においては、初段において関数 1の演算が行われ、2段目において関数 2の演算が行われ、3段目において関数 4の演算が行われている

[0059]

このような演算アルゴリズムは、前述した暗号処理のアルゴリズムと同じであるのでその説明は省略するが、鍵スケジュール処理においては、入力データが 6 4 ビットのデータ

鍵とされ、それぞれ32ビットのシステム鍵 J1~J8を用いて関数 1ないし関数 4の演算が行われて、それぞれ32ビットの8つのワーク鍵 K1~K8が生成されている。ただし、全体で9段の演算を行っており、最終段において関数 1の演算を行う点で、前述した暗号処理のアルゴリズムと相違している。

# [0060]

なお、演算段26の関数 2演算後の上位32ビット出力データがワーク鍵K1として出力され、関数 3演算後の下位32ビット出力データがワーク鍵K2として出力され、関数 4演算後の上位32ビット出力データがワーク鍵K3として出力されている。

さらに、演算段27の関数 1演算後の下位32ビット出力データがワーク鍵K4として出力され、関数 2演算後の上位32ビット出力データがワーク鍵K5として出力され、関数 3演算後の上位32ビット出力データがワーク鍵K6として出力され、関数 4演算後の上位32ビット出力データがワーク鍵K7として出力され、最終段28の関数 1演算後の下位32ビット出力データがワーク鍵K8として出力されている。

# [0061]

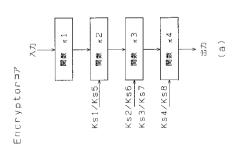

上述した、図11に示す暗号処理と図13に示す鍵スケジュール処理を参照すると、4段の演算段の構成、すなわち演算アルゴリズムは等しくされており、この4段の演算段の演算を繰り返し行うことにより、暗号処理あるいは鍵スケジュール処理を実行することができる。このことから、演算コアを図16(a)に示すように、関数 1の演算段、関数 2の演算段、関数 3の演算段、関数 4の演算段を縦続接続した構成とすれば、演算コアを繰返し実行することで、暗号処理あるいは鍵スケジュール処理を実行することができる。

なお、この演算コアは、図 2 0 に示すデータ鍵とシステム鍵からワーク鍵を生成すると共に、CBCモードおよびOFBモードで暗号処理を行っているEncryptor に相当し、Encryptor コアとされる。この場合、Encryptor コアにはデータ鍵 K s 1 ~ K s 4 とデータ鍵 K s 5 ~ K s 8 とが時分割で供給される。

## [0062]

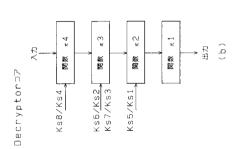

また、図12を参照すると、4段の演算段の構成、すなわち演算アルゴリズムは等しくされており、この4段の演算段の演算を繰り返し行うことにより、解読処理を実行することができる。このことから、解読演算コアを図16(b)に示すように、関数 4の演算段、関数 3の演算段、関数 2の演算段、関数 1の演算段を縦続接続した構成とすれば、解読演算コアを繰返し実行することで、解読処理を実行することができる。

なお、この解読演算コアは、図 2 0 に示す C B C モードおよび O F B モードの解読処理を行っているDecryptor に相当し、Decryptor コアとされる。この場合、Decryptor コアにはデータ鍵 K s 8 ~ K s 5 とデータ鍵 K s 4 ~ K s 1 とが時分割で供給される。

このように、Encryptor コアを繰返し実行することにより暗号処理および鍵スケジュールのアルゴリズムを実行することができ、Decryptor コアを繰返し実行することにより解読アルゴリズムを実行することができる。

## [0063]

以上、本発明の解読化方法を実行する解読装置の説明をしたが、本発明の電子機器は、このような解読装置を少なくとも備えているチューナーやテレビジョン装置等である。また、以上の説明では64ビットブロックの暗号文を64ビットのデータ鍵、および256ビットのシステム鍵を用いて64ビットブロックの平文を生成するものとして説明したが、本発明がこれらの数値に限定されるものではなく、任意の数値とすることができる

さらに、本発明は上述した転置および換字を繰り返すような暗号化・解読化方式に限定されるものではなく、他の暗号化・解読化方式にも適用することができる。

## 【図面の簡単な説明】

### [0064]

【図1】本発明の解読化方法の実施の形態である解読装置の構成例を示すブロック図である。

20

10

30

40

20

- 【図2】図1に示す解読装置におけるIDTの構成を示すブロック図である。

- 【図3】図1に示すCPUから見た解読装置におけるレジスタのメモリ空間を示す図表である。

- 【図4】図2に示すIDTの比較器CP0~CP11の論理表を示す図表である。

- 【図5】図2に示すIDTのPEの論理表を示す図表である。

- 【図 6 】図 1 に示す解読装置において、入力データのヘッダ中の情報から間接検索方法によりデータ鍵をサーチする方法を説明するための図である。

- 【図7】PIDテーブル中にPIDが重複している場合の動作を説明するための図である

- 【図8】PIDテーブル中に該当するPIDが存在しない場合の動作を説明するための図である。

- 【図9】図1に示す解読装置におけるDPMEMのリードタイミングの例を示す図である

- 【図10】図1に示す解読装置の解読フローを示すフローチャートである。

- 【図11】暗号処理の構成を示す図である。

- 【図12】解読処理の構成を示す図である。

- 【図13】暗号処理における基本関数の詳細を示す図である。

- 【図14】基本関数中の関数 2を演算するための詳細な構成を示す図である。

- 【図15】鍵スケジュール処理の構成を示す図である。

- 【図16】Encryptor コアとDecryptor コアの構成を示す図である。

- 【図17】従来の暗号化のアルゴリズムを示す図である。

- 【図18】従来の解読化のアルゴリズムを示す図である。

- 【図19】CBCモードとOFBモードの暗号化利用モードの構成を示す図である。

- 【図20】従来の暗号化・解読化方式の構成を示す図である。

## 【符号の説明】

# [0065]

1 受信データ、2 出力データ、3,4 切り換え手段、5 Decryptor、6 レジスタ、7,9,86 排他的論理和回路、8 Encryptor、10 CPU、11 比較器、12 アンドゲート、13,14 オアゲート、15 インバータ、16 IDT、17 DPMEM、20~28 演算段、39 PE、40 ADEC、41~52 フリッ 30 プフロップ、61~72 比較器、80,82,84 加算器、81,85 左巡回シフター

# 【図1】

# 【図2】

【図3】

| HADD(80]    | 内容                      | ピット数      |  |  |  |

|-------------|-------------------------|-----------|--|--|--|

| 0 0010 0××× | CBC Initial value table | 64bit× 1  |  |  |  |

| 0 010× ×××× | SYSTEM_Key table        | 256bit× 1 |  |  |  |

| 0 100× ×××× | PID value table         | 13bit×12  |  |  |  |

| 1 0××× ×××× | Ks_even value table     | 64bit×12  |  |  |  |

| 1 1××× ×××× | Ks odd value table      | 64hit×12  |  |  |  |

【図5】

# 【図4】

CP0~CP11の論理表

| 入力<br>A, B           | 出力<br>A = B |

|----------------------|-------------|

| A=B(AもBもall 11でないとき) | 1           |

| A=B(AもBもall'1'のとき)   | 0           |

| A < B                | 0           |

| A > B                | 0           |

| H H  | TMP1 TMP0 | 0 0 | 0 1 | 1 0 | 1 1 | 0 0 | 0 1 | 1 0 | 1 1 | 0 0 | 0 1 | 1 0 | 1 1 | , |

|------|-----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|

|      | TMP3 TMP2 | 0 0 | 0 0 | 0 0 | 0 0 | 0 1 | 0 1 | 1 0 | 0 1 | 1 0 | 1 0 | 1 0 | 1 0 | , |

| 7 73 | 00        | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | ( |

|      | 2 D1      | ×   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | < |

|      | 03 02     | ×   | ×   | × 1 | 1 0 | 0 0 | 0 0 | 0 0 | 0 0 | 0 0 | 0 0 | 0 0 | 0 0 |   |

|      | D4 C      | ×   | ×   | ×   | ×   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |   |

|      | 90        | ×   | ×   | ×   | ×   | ×   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | , |

|      | 90        | ×   | ×   | ×   | ×   | ×   | ×   | 1   | 0   | 0   | 0   | 0   | 0   |   |

|      | 10        | ×   | ×   | ×   | ×   | ×   | ×   | ×   |     | 0   | 0   | 0   | 0   | ( |

|      | 08        | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×   | -   | 0   | 0   | 0   | < |

|      | 0.0       | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×   | 1   | 0   | 0   | < |

|      | D10       | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×   | 1   | 0   | 4 |

|      | D11       | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×   | -   | ( |

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

暗号処理

【図12】

【図13】

(19)

Add : 32bit加算器 Rotn(): 左巡回nビットシフト + : ビット毎の排他的論理和

基本関数π2の回路構成例

鍵スケジュール処理

# 【図16】

# 【図17】

【図18】

【図19】

【図20】

# フロントページの続き

(56)参考文献 特開昭 6 1 - 1 7 7 0 4 6 ( J P , A ) 特開平 6 - 2 5 9 9 5 6 ( J P , A )

(58)調査した分野(Int.CI., DB名) H04L9/00