(12) NACH DEM VERTRAG ÜBER DIE INTERNATIONALE ZUSAMMENARBEIT AUF DEM GEBIET DES

PATENTWESENS (PCT) VERÖFFENTLICHTE INTERNATIONALE ANMELDUNG

(19) Weltorganisation für geistiges Eigentum

Internationales Büro

(43) Internationales Veröffentlichungsdatum

29. Dezember 2005 (29.12.2005)

PCT

(10) Internationale Veröffentlichungsnummer

**WO 2005/124854 A1**

(51) Internationale Patentklassifikation<sup>7</sup>: **H01L 21/768**

(21) Internationales Aktenzeichen: PCT/DE2005/001067

(22) Internationales Anmeldedatum:

15. Juni 2005 (15.06.2005)

(25) Einreichungssprache: Deutsch

(26) Veröffentlichungssprache: Deutsch

(30) Angaben zur Priorität:

10 2004 029 519.0 18. Juni 2004 (18.06.2004) DE

(71) Anmelder (für alle Bestimmungsstaaten mit Ausnahme von US): INFINEON TECHNOLOGIES AG [DE/DE]; St.-Martin-Str. 53, 81669 München (DE).

(72) Erfinder; und

(75) Erfinder/Anmelder (nur für US): ECKERT, Stefan [DE/DE]; Am Zollhaus 2A, 01108 Dresden (DE). GOLLER, Klaus [DE/DE]; Helmholtzstrasse 3B, 01069 Dresden (DE). WENDT, Hermann [DE/US]; 16 Creek Bend Road, Poughkeepsie, New York 12603 (US).

(74) Anwalt: DOKTER, Eric-Michael; Viering, Jentschura & Partner, Steinsdorfstr. 6, 80538 München (DE).

(81) Bestimmungsstaaten (soweit nicht anders angegeben, für jede verfügbare nationale Schutzrechtsart): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NG, NI, NO, NZ,

[Fortsetzung auf der nächsten Seite]

(54) Title: METHOD FOR PRODUCING A LAYER ARRANGEMENT

(54) Bezeichnung: VERFAHREN ZUM HERSTELLEN EINER SCHICHT-ANORDNUNG

(57) **Abstract:** The invention relates to a method for producing a layer arrangement, wherein an electrically conductive layer and a sacrificial layer are structured and formed, an electrically insulating layer is formed on said layers and is structured in such a manner that surface areas of the sacrificial layer are exposed. The exposed areas are removed and the thus exposed surface areas of the structured electrically conductive layer are covered with a structure which is made of an electrically conductive material.

(57) **Zusammenfassung:** Die Erfindung betrifft ein Verfahren zum Herstellen einer Schicht-Anordnung, bei dem eine strukturierte elektrisch leitfähige Schicht und eine Opferschicht gebildet werden, eine elektrisch isolierende Schicht darauf gebildet und derart strukturiert wird, dass Oberflächenbereiche der Opferschicht freigelegt werden, die freigelegten Bereiche entfernt werden und so freigelegte Oberflächenbereiche der strukturierten elektrisch leitfähigen Schicht mit einer Struktur aus elektrisch leitfähigem Material bedeckt werden.

WO 2005/124854 A1

OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

- (84) Bestimmungsstaaten** (*soweit nicht anders angegeben, für jede verfügbare regionale Schutzrechtsart*): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), eurasisches (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), europäisches (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, MC, NL,

**Veröffentlicht:**

— mit internationalem Recherchenbericht

*Zur Erklärung der Zweibuchstaben-Codes und der anderen Abkürzungen wird auf die Erklärungen ("Guidance Notes on Codes and Abbreviations") am Anfang jeder regulären Ausgabe der PCT-Gazette verwiesen.*

**Beschreibung****Verfahren zum Herstellen einer Schicht-Anordnung**

- 5 Die Erfindung betrifft ein Verfahren zum Herstellen einer Schicht-Anordnung.

Unter Verwendung von sogenannten Vias wird bei integrierten Schaltkreisen ein vertikaler elektrischer Kontakt zwischen 10 Leiterbahnen unterschiedlicher Metallisierungsebenen hergestellt. Vias, d.h. zu einer Substratoberfläche vertikal orientierte Gräben, werden häufig unter Verwendung eines Lithographie- und eines Plasmaätz-Verfahrens erzeugt und können dann mit elektrisch leitfähigem Material gefüllt 15 werden. Zwischen dem Material einer zu kontaktierenden Leiterbahn einer Metallisierungsebene und dem Material eines Vias kann eine Haft-, Barrieren- oder Keimschicht (Liner-Schicht) vorgesehen sein, mittels welcher ein Kontakt zwischen den beiden zu koppelnden Materialien vermittelt 20 werden kann bzw. ein unerwünschtes Diffundieren von Material der Via-Füllung in jenes der Leiterbahn (bzw. vice versa) vermieden werden kann.

Augrund prozessbedingter Schwankungen in der Justage von Ätz- 25 Masken für Vias können diese jedoch nicht optimal, sondern nur mit einem gewissen, beispielsweise lateralen Versatz strukturiert werden. Ein solcher Versatz liegt innerhalb der in Designregeln zum Gestalten eines integrierten Schaltkreises benannten Grenzen, ist aber für ein einzelnes 30 Via nicht exakt bestimmbar. Solche Schwankungen werden in den Designregeln zum Gestalten des integrierten Schaltkreises durch Vorschriften berücksichtigt, die beispielsweise für Vias größere als nominell erforderliche Kontaktflächen

definieren, um einen späteren Kontakt zwischen Leiterbahn und dem mit elektrisch leitfähigem Material gefüllten Via sicherzustellen.

- 5 Abgesehen von der Fläche des Vias selbst werden beim Layout größere Metallflächen berücksichtigt, auf denen die Vias landen, inklusive des beschriebenen Justierfehlers. Hierbei handelt es sich nicht um eine Prozessschwäche, sondern dies ist bedingt durch die Prozessierung. Für alle

- 10 Fertigungsschritte ist ein Toleranzbereich zu definieren, innerhalb dessen eine physikalische Größe zu liegen hat, um das zu fertigende mikroelektronische Bauteil korrekt ausliefern zu können.

- 15 Die größeren Flächen werden als "Landingpads" für Vias bezeichnet und sind in den Designregeln zum Bilden eines integrierten Schaltkreises zu berücksichtigen. Beispielsweise kann ein Via-Boden einen Durchmesser von 200nm haben. Ein solches Via ist zum Beispiel auf einer Fläche von 240nm x

- 20 240nm (Kantenlängen) zu positionieren. In diesem Fall wäre ein maximaler Versatz von 20nm pro Kante zulässig.

Die größeren Flächen führen zu einer lateralen Aufweitung der Metallbahnen in der Umgebung der Vias, wodurch das Routing im Design durchbrochen wird. Dies ist hinsichtlich der hohen Kosten von Chipfläche nachteilig, da dadurch der Platzbedarf eines integrierten Schaltkreises erhöht wird. Metallbahnen selbst können mit geringem Abstand voneinander prozessiert werden, allerdings benötigen die Vias eine Aufweitung der Metallbahn zum Bilden der Landingpads. Dieser Mehraufwand im Layout und der damit verbundene Verlust an Chipfläche ist angesichts des Bedarfs zunehmend höher integrierter ICs nachteilig.

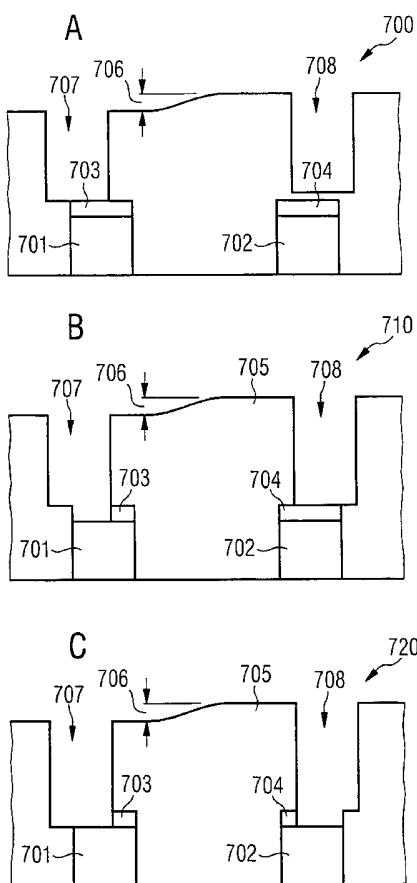

Bei zu erwartenden weiter schrumpfenden Dimensionen von integrierten Schaltkreisen bzw. von deren Komponenten wie Leiterbahnen können insbesondere die in Fig.1A bis Fig.1C 5 dargestellten Fälle auftreten.

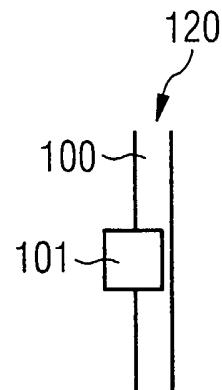

In **Fig.1A** ist eine Layout-Draufsicht 110 gezeigt, mit einer Leiterbahn 100, die mittels eines Vias 101 zu kontaktieren ist. Der Durchmesser des Vias 101 ist größer als die Breite 10 der Leiterbahn 100, so dass bei einem prozesstechnisch bedingtem lateralen Versatz zwischen den Schwerpunkten der Leiterbahn 100 und des Vias 101 immer noch eine Kontaktierung der Leiterbahn 100 durch das Via 101 gewährleistet ist.

15 Bei einer zweiten Layout-Draufsicht 120, die in **Fig.1B** gezeigt ist, sind der Durchmesser eines Vias 101 und einer Leiterbahn 100 gleich groß, allerdings ist das Via 101 aufgrund eines Kantenlagefehlers bei der Via-Belichtung teilweise neben der Leiterbahn 100 angeordnet, was zu einer 20 verschlechterten elektrischen Kontaktierung führen kann.

In einer dritten Layout-Draufsicht 130, die in **Fig.1C** gezeigt ist, ist wiederum eine Leiterbahn 100 und ein Via 101 gezeigt, wobei das Via 101 trotz einer lokalen 25 Bahnverbreiterung in Form eines Landingpads 102 neben der Leiterbahn 100 zu liegen kommt, bedingt durch die Justiertoleranz der Phototechnik beim Bilden des Vias 101.

30 Im Weiteren wird bezugnehmend auf Fig.2A bis Fig.2H ein Verfahren zum Herstellen einer Schicht-Anordnung gemäß dem Stand der Technik beschrieben, mit dem ein integrierter Schaltkreis gemäß der ersten Layout-Draufsicht 110 aus Fig.1A gebildet werden kann.

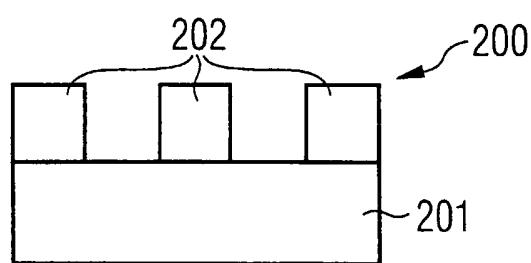

Um die in **Fig.2A** gezeigte Schichtenfolge 200 zu erhalten, wird auf einem Substrat (nicht gezeigt) eine Aluminium-Schicht 201 aufgebracht und je nach angestrebter

5 Strukturfeinheit zusätzlich eine ARC-Schicht ("anti reflective coating"). Auf der Aluminium-Schicht 201 wird nachfolgend Photoresist-Material gebildet, welches unter Verwendung eines Lithographie- und eines Ätz-Verfahrens zu einer Photoresist-Maske 202 strukturiert wird.

10

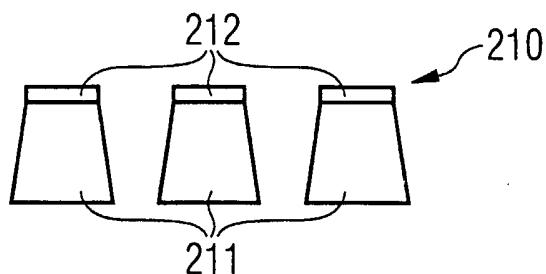

Um die in **Fig.2B** gezeigte Schichtenfolge 210 zu erhalten, wird ausgehend von der in Fig.2A gezeigten Schichtenfolge 200 unter Verwendung der Photoresist-Maske 202 die Aluminium-Schicht 201 derart strukturiert, dass Aluminium-Leiterbahnen

15 211 gebildet werden. Je nach angestrebter Strukturfeinheit kann zum Strukturieren der Aluminium-Leiterbahnen 211 eine Hartmaske eingesetzt werden. Der Photoresist 202 wird dann bereits nach der Strukturübertragung in die Hartmaske entfernt. Die Hartmaske ersetzt dann die Photoresist-Maske 202. Auf jeder der Aluminium-Leiterbahnen 211 ist ein nach 20 dem Ätzen verbliebener Photoresist-Rest 212 gezeigt, der mittels eines Stripping-Verfahrens nachfolgend entfernt wird.

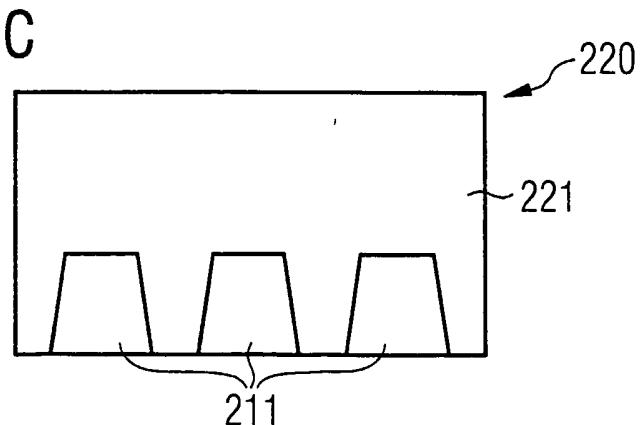

Um die in **Fig.2C** gezeigte Schichtenfolge 220 zu erhalten, 25 wird ausgehend von der in Fig.2B gezeigten Schichtenfolge 210 nach Entfernen des Photoresist-Rests 212 eine Siliziumoxid-Schicht 221 abgeschieden, welche die Aluminium-Leiterbahnen 211 bedeckt.

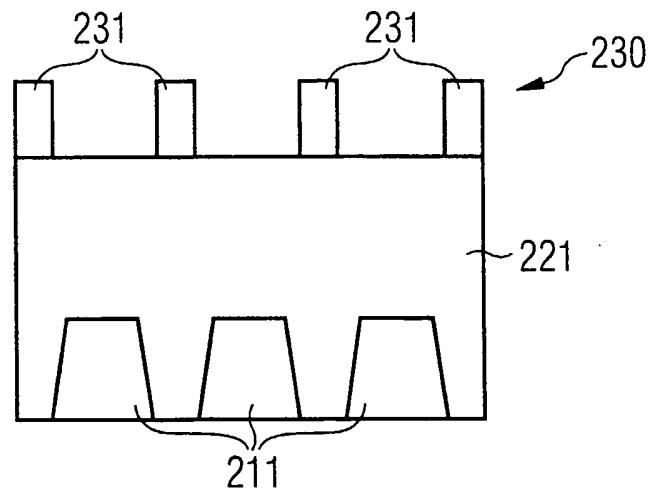

30 Um die in **Fig.2D** gezeigte Schichtenfolge 230 zu erhalten, wird Photoresist-Material auf der Schichtenfolge 220 abgeschieden und unter Verwendung eines Lithographie- und

eines Ätz-Verfahrens zum Bilden einer Photoresist-Maske 231 strukturiert.

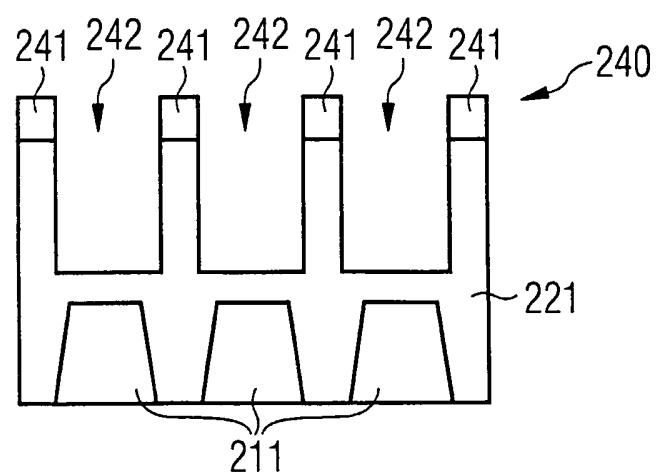

Um die in **Fig.2E** gezeigte Schichtenfolge 240 zu erhalten, 5 wird unter Verwendung der Photoresist-Maske 231 als Ätzmaske die Schichtenfolge 230 einem Ätz-Verfahren unterzogen, wodurch Material der Siliziumoxid-Schicht 221 entfernt wird und Gräben 242 gebildet werden. Es verbleiben Photoresist-Restbereiche 241 auf der Oberfläche der Schichtenfolge 240.

10

Die in **Fig.2F** gezeigte Schichtenfolge 250 wird erhalten, wenn ausgehend von der Schichtenfolge 240 das Verfahren zum Ätzen der Siliziumoxid-Schicht 221 fortgeführt wird. Zu einem bestimmten Verfahrenszeitpunkt während dieses Ätz-Verfahrens 15 ist die Tiefe der Gräben 242 derart groß, dass Oberflächenbereiche der Aluminium-Leiterbahnen 211 freigelegt werden. Die Schichtenfolge 250 gemäß diesem Verfahrenszustand ist in Fig.2F gezeigt, wo die Via-Ätzung bereits auf der strukturierten Metallbahn 211 angekommen ist.

20

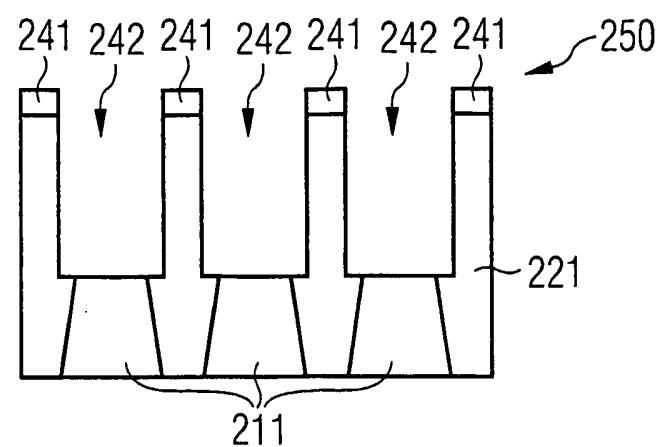

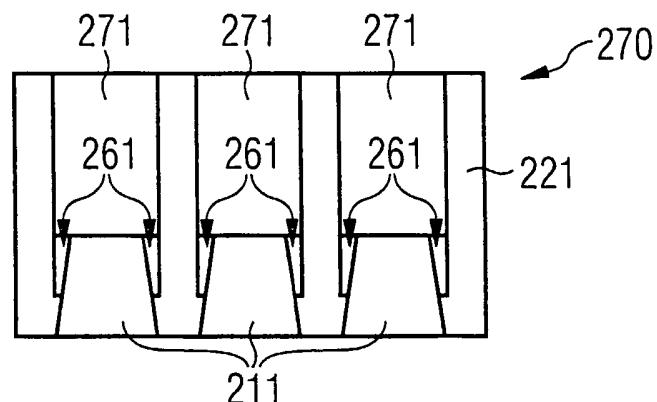

Um die in **Fig.2G** gezeigte Schichtenfolge 260 zu erhalten, wird das bezugnehmend auf Fig.2E und Fig.2F beschriebene Ätz-Verfahren fortgesetzt. Infolge von in der Praxis häufig auftretenden, prozesstechnisch bedingten Dickenunterschiede 25 der strukturierten Siliziumoxid-Schicht (als Inter Layer Dielectric, ILD) über einem Wafer als Substrat ist ein Überätzen ("Overetch") erforderlich, d.h. ein Ätzen tiefer als bis zu den Oberflächenbereichen der Leiterbahnen 221. Dieses Überätzen wird vorgenommen, um später die Vias auf dem 30 Wafer zuverlässig an Leiterbahnen 211 anschließen zu können. Die Dauer des Overetching beträgt typischerweise 10% bis 30% der gesamten Via-Ätzzeit. Das Ergebnis des Overetching-Verfahrens ist in der Schichtenfolge 260 gezeigt. Zwar sind

die Oberflächenbereiche der Leiterbahnen 211 sicher freigelegt, wodurch eine Kontaktierung mit Via-Material in einem nachfolgenden Verfahrensschritt ermöglicht wird, allerdings bilden sich aufgrund des Überätzens, wie in Fig.2G 5 gezeigt, enge Spalten 261 in Grenzbereichen zwischen Material der Siliziumoxid-Schicht 221 und den freigelegten Abschnitten der Leiterbahnen 211.

Als Ergebnis des Überätzens geht die Ätzung somit beidseitig 10 an den Metallbahnen 211 vorbei und erzeugt enge Spalten 261. Die Tiefe der Spalten 261 und damit deren Aspektverhältnis ist abhängig von der lokalen Dicke der dielektrischen Schicht 211 und kann über den Wafer hinweg variieren. Diese engen Spalten 261 sind Ursache vielfältiger Schwierigkeiten, die zu 15 gravierenden Zuverlässigkeitsproblemen führen. So ist eine Reinigung oder Entfernung von Polymer-Material in den engen Spalten 261 nur unvollständig oder gar nicht möglich. Dies führt zu Problemen bei einer nachfolgenden Linerabscheidung und/oder Metallauffüllung zum Bilden der Vias. Ferner gelingt 20 das Abscheiden von Haft-, Keim- oder Barriereschichten (Liner genannt) bei Auftreten von engen Spalten 261 nur unvollständig. Da ein solches Abscheiden in der Regel unter Verwendung auch physikalischer Verfahren erfolgt, spielt das lokal vorhandene Aspektverhältnis der engen Spalten 261 eine 25 wichtige Rolle. Je höher das Aspektverhältnis, umso kleiner ist die Kantenbedeckung mit der jeweiligen Schicht. Somit können bei der Metallauffüllung Hohlräume im Bereich der engen Spalten 261 entstehen, oder einzelne Vias werden gar nicht oder nur schlecht gefüllt. Dies führt zu einer 30 unzuverlässigen Kontaktierung zwischen Metallbahnen 211 und Vias.

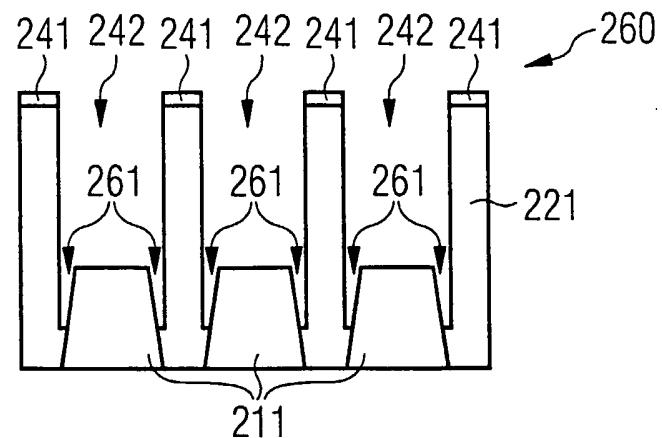

Um die in **Fig.2H** gezeigte Schicht-Anordnung 270 gemäß dem Stand der Technik zu erhalten, werden die Gräben 242 aus Fig.2G mit Wolfram-Material zum Bilden von Wolfram-Vias 271 aufgefüllt. Wie oben beschrieben ist bei diesem Auffüll-

5 Verfahren ein zuverlässiges Auffüllen der aufgrund des Überätzens gebildeten engen Spalten 261 mit lokal stark erhöhtem Aspektverhältnis nicht möglich. Dies führt zu Problemen hinsichtlich der Qualität der Schicht-Anordnung 270 hinsichtlich ihrer Verwendung als integrierter Schaltkreis.

10

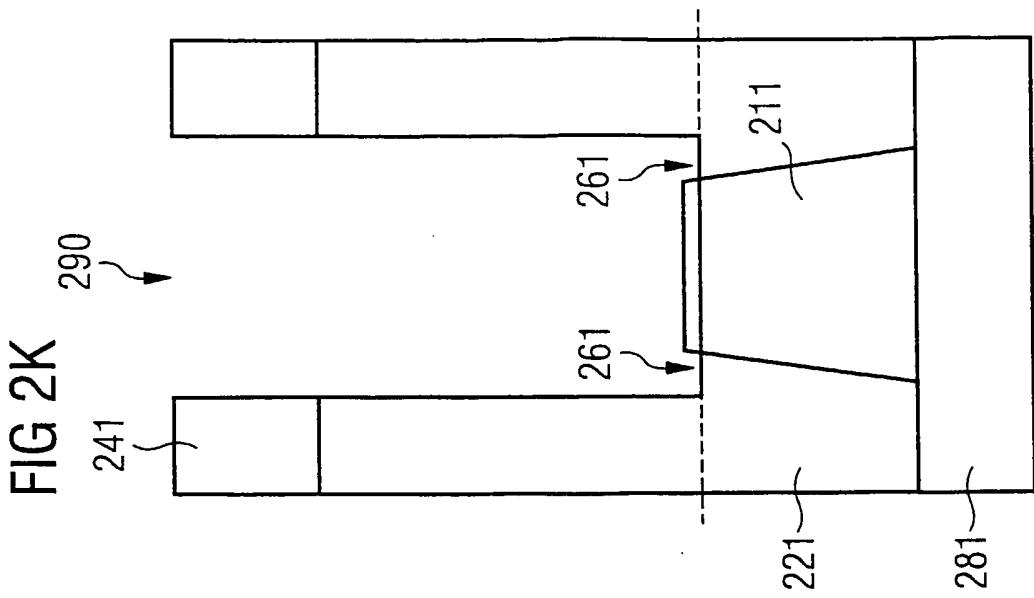

Im Weiteren wird bezugnehmend auf Fig.2I bis Fig.2K nochmals beschrieben, welche Prozesse zu dem Ausbilden der unerwünschten engen Spalten 261 führen, wenn das Verfahren zum Herstellen einer Schicht-Anordnung gemäß Fig.2A bis 15 Fig.2H durchgeführt wird.

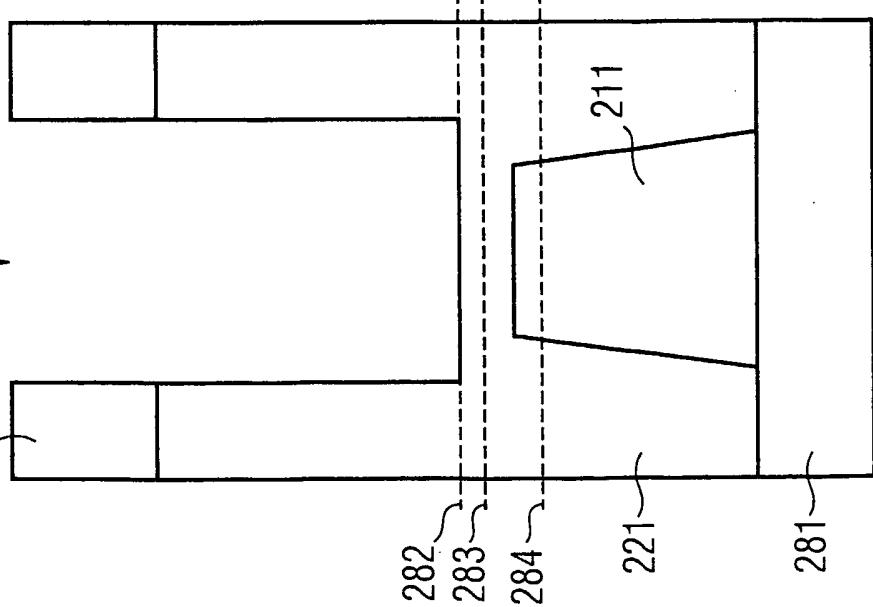

Die in **Fig.2I** dargestellte Schichtenfolge 280 zeigt einen Zustand während des Ätzens der Siliziumoxid-Schicht 221, bei dem die Ätzfront eine erste Ebene 282 erreicht hat.

20

Wie in **Fig.2J** gezeigt, wird eine Schichtenfolge 285 erhalten, wenn ausgehend von der Schichtenfolge 280 das Ätz-Verfahren zum Ätzen der ersten Siliziumoxid-Schicht 221 fortgesetzt wird. Die Ätzfront erstreckt sich dann bis zu einer zweiten 25 Ebene 283.

Da technologisch ein gewisses Überätzen zum Sicherstellen des Freilegens aller Oberflächen aller Aluminium-Leiterbahnen 211 erforderlich ist, tritt gemäß dem Stand der Technik der in 30 **Fig.2K** gezeigte Fall auf, bei dem in einer Schichtenfolge 290 die Ätzfront bis zu einer dritten Ebene 284 vorgedrungen ist, so dass an seitlichen Bereichen der freigelegten Aluminium-Leiterbahn 211 unerwünschte enge Spalten 261 auftreten.

Für die in Fig.1B und Fig.1C gezeigten Fälle ergibt sich ein ähnliches Bild wie für Fig.1A. Stets erfolgt eine tiefe Einätzung neben der Metallbahn, die dann zu den oben 5 beschriebenen Problemen führt.

In [1] wird ein Verfahren zur Erzeugung von Kontaktflächen auf einer Metallisierungsstruktur beschrieben, wobei auf Leiterbahnen, welche mit Resten einer Hartmasken-Schicht 10 versehen sind, eine dielektrische Schicht aufgebracht wird. Durch die dielektrische Schicht hindurch werden Kontaktlöcher geätzt mit Beenden des Ätzens bei Erreichen der Hartmasken-Schicht. Nachfolgend wird die Hartmasken-Schicht selektiv zur dielektrischen Schicht geätzt, so dass verhindert wird, dass 15 das Kontaktloch in den Zwischenraum zwischen benachbarten Leiterbahnen dringt, wodurch die Gefahr von Kurzschlüssen reduziert wird.

In [2] wird ein Verfahren zum konformen Aufbringen einer 20 Ätzstoppschicht auf eine strukturierte Metallisierungsebene mit einer Mehrzahl von Leiterbahnen beschrieben, wobei im Rahmen der Kontaktlochätzung das Kontaktloch so lange geätzt wird, bis unterhalb des Kontaktlochs alle Bereiche der Ätzstoppschicht freigelegt sind und somit auch die neben den 25 Leiterbahnen sich befindenden Oberflächen-Bereiche der Ätzstoppschicht.

Der Erfindung liegt insbesondere das Problem zugrunde, ein 30 Verfahren zum Herstellen einer Schicht-Anordnung bereitzustellen, bei dem eine verbesserte Kontaktierung zwischen unterschiedlichen elektrisch leitfähigen Strukturen ermöglicht ist.

Das Problem wird durch ein Verfahren zum Herstellen einer Schicht-Anordnung mit den Merkmalen gemäß dem unabhängigen Patentanspruch gelöst.

- 5 Bei dem erfindungsgemäßen Verfahren zum Herstellen einer Schicht-Anordnung wird eine elektrisch leitfähige Schicht auf einem Substrat gebildet und strukturiert und nachfolgend eine Opferschicht auf zumindest einem Teil der elektrisch leitfähigen Schicht gebildet. Eine elektrisch isolierende Schicht wird auf der elektrisch leitfähigen Schicht und auf der Opferschicht gebildet. Die elektrisch isolierende Schicht wird derart strukturiert, dass Oberflächenbereiche der Opferschicht freigelegt werden. Die freigelegten Bereiche der Opferschicht werden entfernt, womit Oberflächenbereiche der 15 elektrisch leitfähigen Schicht freigelegt werden. Schließlich werden die freigelegten Oberflächenbereiche der strukturierten elektrisch leitfähigen Schicht mit einer Struktur aus elektrisch leitfähigem Material bedeckt.

- 20 Eine Grundidee der Erfindung ist darin zu sehen, dass zwischen einer elektrisch leitfähigen Schicht, welche in einem strukturierten Zustand z.B. Leiterbahnen eines integrierten Schaltkreises bilden kann, und einer darauf abgeschiedenen elektrisch isolierenden Schicht als 25 Intermetalldielektrikum eine Opferschicht mit für deren Funktionalität frei wählbaren Eigenschaften vorgesehen wird, mittels welcher ein Überätzen zum Freilegen von Oberflächenbereichen der strukturierten elektrisch leitfähigen Schicht zum Kontaktieren derselben mit einer 30 Struktur aus elektrisch leitfähigem Material (z.B. Vias) verkürzt oder ganz vermieden werden kann.

Anschaulich hat die Opferschicht die Funktion, dass mit ihr die Ätzvorgänge zum Freilegen der Einzelbereiche der strukturierten elektrisch leitfähigen Schicht zeitlich/räumlich synchronisiert werden können. Bei einem

5 Ätzen der elektrisch isolierenden Schicht gemäß dem Stand der Technik tritt das Problem auf, dass die Dicke der elektrisch isolierenden Schicht häufig relativ groß und für unterschiedliche Einzelbereiche der strukturierten elektrisch leitfähigen Schicht unterschiedlich ist, was zum sicheren

10 Freilegen aller Einzelbereiche eine verlängerte Ätzzeit erfordert, die bei einem Teil der Einzelbereiche zu dem Bilden von unerwünschten engen Spalten führen kann (siehe Fig.2E bis Fig.2H). Dieses Problem ist erfindungsgemäß durch das Vorsehen der Opferschicht vermieden, da bei Einsatz der

15 Opferschicht als Ätzstopp-Schicht und/oder als ausreichend schnell ätzbare Schicht aufgrund der unterschiedlichen Materialien und somit Ätzraten der elektrisch isolierenden Schicht einerseits und der Opferschicht andererseits die Ätzfront oberhalb von allen Einzelbereichen zunächst bis zu

20 der Opferschicht vordringen kann. Hat die Ätzfront die Opferschicht auf den Einzelbereichen der strukturierten elektrisch leitfähigen Schicht erreicht, wird mit einem zusätzlichen Ätzverfahren die Opferschicht auf allen Einzelbereichen der strukturierten elektrisch leitfähigen

25 Schicht entfernt. Hierbei ist vorteilhaft, dass die Opferschicht hinsichtlich Materialwahl und/oder Dicke und/oder Ätzeigenschaften derart eingerichtet wird, dass bei dem Ätzen der Opferschicht die Ätzfront alle Einzelbereiche der strukturierten elektrisch leitfähigen Schicht annähernd

30 gleichzeitig erreicht, so dass ein Überätzen und ein daraus resultierendes Bilden unerwünschter enger Spalten vermieden wird. Dies ist insbesondere erreichbar, wenn bezogen auf vorgebbare Ätzparameter des eingesetzten Ätzverfahrens die

- Ätzrate zum Entfernen der Opferschicht größer eingestellt wird als für die elektrisch isolierende Schicht und/oder wenn die Dicke der Opferschicht ausreichend gering und/oder gleichmäßig vorgesehen wird. Dann ist die Dauer des Ätzens

- 5 der Opferschicht gering gehalten. Dieses Ätzen kann bei allen Einzelbereichen der Opferschicht im Wesentlichen gleichzeitig einsetzen, d.h. die Opferschicht kann anschaulich als Stoppschicht dienen.

- 10 Mit diesem sehr einfachen Verfahren unter Verwendung der Opferschicht ist bei mehreren Komponenten der strukturierten elektrisch leitfähigen Schicht (z.B. mehreren Leiterbahnen) sichergestellt, dass selbst bei lokal unterschiedlicher Schichtdicke der elektrisch isolierenden Schicht zunächst bei

- 15 allen Komponenten der strukturierten elektrisch leitfähigen Schicht das darüber gebildete elektrisch isolierende Material bis zur Oberfläche der Opferschicht entfernt wird. Somit kann ein ganz bestimmter Prozessierungs-Zwischenzustand infolge des Vorsehens der Opferschicht definiert werden, bei dem die

- 20 Ätzfront alle Oberflächenbereiche der Opferschicht erreicht hat. Die Opferschicht kann beispielsweise besonders dünn oder aus einem Material mit einer besonders hohen Ätzrate vorgesehen sein, so dass nach dem Erreichen der Opferschicht an allen Komponenten der strukturierten elektrisch

- 25 leitfähigen Schicht ein schnelles Entfernen der Stoppschicht ermöglicht ist. Aufgrund der schnellen Entfernbarkeit der Stoppschicht aufgrund ihrer geringen Dicke bzw. aufgrund ihrer Ätzbarkeit mit hoher Ätzrate kann das Überätzen, das gemäß dem Stand der Technik zur Qualitätssicherung

- 30 erforderlich war, erheblich verkürzt oder ganz vermieden werden.

12

Anders ausgedrückt erfolgt das Ätzen der elektrisch isolierenden Schicht und der Opferschicht zum Bilden von Gräben (die zum späteren Auffüllen mit Material einer Struktur aus elektrisch leitfähigem Material vorsehen sind,

5 z.B. als Vias) lateral selbstjustiert, so dass gemäß dem Stand der Technik auftretende Schwierigkeiten mit engen Spalten aufgrund eines zeitlich langen Überätzens vermieden sind.

- 10 Eine grundsätzliche Idee der Erfindung beruht auf dem optimiert vorsehbaren Material der Opferschicht, das so gewählt werden kann, dass die Opferschicht als Stoppschicht beim Ätzen dienen kann und dann besonders zügig und ohne starkes Überätzen entfernt werden kann. Somit ist ein

- 15 wichtiger Aspekt der Erfindung in dem Verwenden und der Kombination von unterschiedlichen Ätzverfahren und unterschiedlichen Materialien zu sehen, wobei das Verfahren durch die Wahl geeigneter Ätzparameter optimiert werden kann.

- 20 Auf dem zu kontaktierenden Material der strukturierten elektrisch leitfähigen Schicht ist somit eine geeignete Zusatz- oder Opferschicht vorhanden, die gemeinsam mit der Metallätzung zum Strukturieren der elektrisch leitfähigen Schicht strukturiert wird. Die Parameter der Ätzung zum

- 25 Freilegen von Oberflächenbereichen der strukturierten elektrisch leitfähigen Schicht (z.B. Via-Ätzung) können so eingestellt werden, dass die Opfer- oder Zusatzschicht deutlich schneller geätzt wird als das umgebende Material der elektrisch isolierenden Schicht ("inter layer dielectric").

- 30 Ausgehend von einem Zustand, bei dem die Via-Ätzfront gerade die Zusatzschicht erreicht hat, wird im weiteren Verlauf der Ätzung die Zusatzschicht schneller geätzt, so dass die Ätzfront in der elektrisch isolierenden Schicht zurückbleibt.

Hat die Ätzfront das zu kontaktierende Material der strukturierten elektrisch leitfähigen Schicht erreicht, so kann optional ein kurzes Überätztverfahren durchgeführt werden, so dass die in der dielektrischen Schicht vorhandene 5 Ätzstufe heruntergezogen wird. In günstigen Fällen schließt dann nach der Überätzung die Ätzfront mit der Metalloberfläche ab oder steht geringfügig höher. Selbst in ungünstigen Fällen, bei denen bei dem Überätztverfahren bis unter das Metallniveau geätzt wird, ist das Bilden von 10 unerwünschten engen Spalten gegenüber dem Stand der Technik auf jeden Fall deutlich verringert, so dass die Probleme bei der Abscheidung eines Liner-Materials oder dem Auffüllen der Vias, welche Probleme auf dem Vorhandensein von engen Spalten mit lokal erhöhtem Aspektverhältnis beruhen, deutlich 15 verringert sind.

Es sind bei dem Einsatz der erfundungsgemäßen Opferschicht insbesondere zwei Szenarien zu unterscheiden: Die Opferschicht kann als Ätz-Stoppschicht und/oder als schnell 20 ätzbare Schicht eingesetzt werden.

Bei Einsetzen der Opferschicht als Ätz-Stoppschicht wird zunächst oberhalb der strukturierten elektrisch leitfähigen Schicht und oberhalb der Opferschicht befindliches Material 25 der elektrisch isolierenden Schicht entfernt, wobei der Materialabtrag des Ätzverfahrens beim Erreichen der Opferschicht endet. Bei einem (unerwünschten, aber nicht immer vollständig vermeidbaren) lateralen Versatz der Ätzmaske, d.h. wenn die Ätzfront gegenüber den 30 Einzelstrukturen der Opferschicht leicht seitlich versetzt ist, kann es vorkommen, dass neben der Opferschicht befindliches Material der elektrisch isolierenden Schicht entfernt wird, das seitlich unterhalb der Oberfläche der

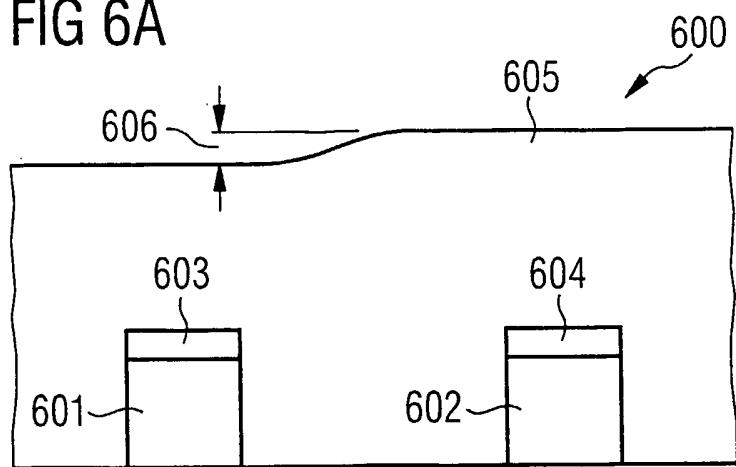

Opferschicht angeordnet ist. In diesem Szenario ist es vorteilhaft, wenn die Dicke der Opferschicht mindestens so groß gewählt wird wie ein Dickenrange (d.h. eine Schwankungsbreite der Dicke) der elektrisch isolierenden Schicht, da dann bei einem solchen lateralen Versatz kein unerwünschter enger Spalt erzeugt wird. Erreicht nämlich die Ätzfront an der dicksten Stelle der elektrisch isolierenden Schicht die Opferschicht, ist sie an der dünnsten Stelle der elektrisch isolierenden Schicht an der Opferschicht noch nicht vollständig vorbei (siehe Fig.6A, Fig.6B).

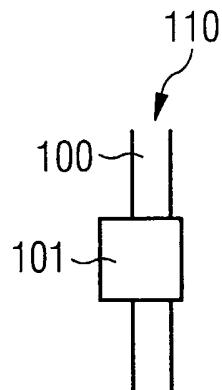

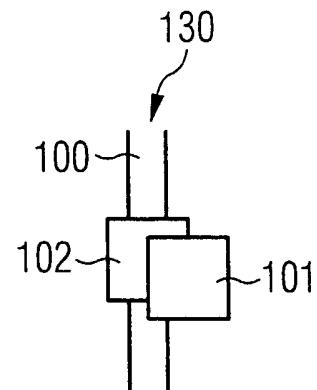

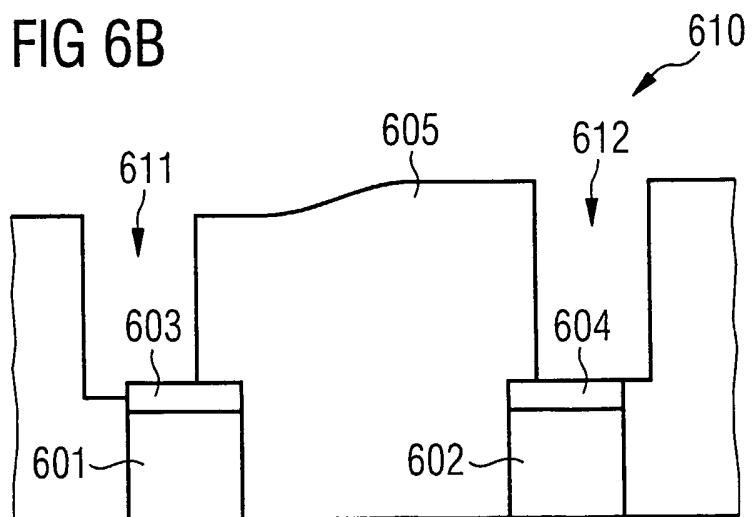

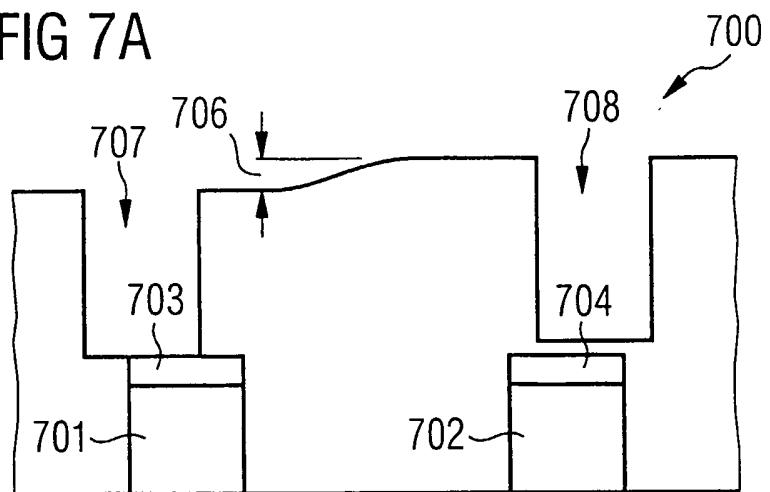

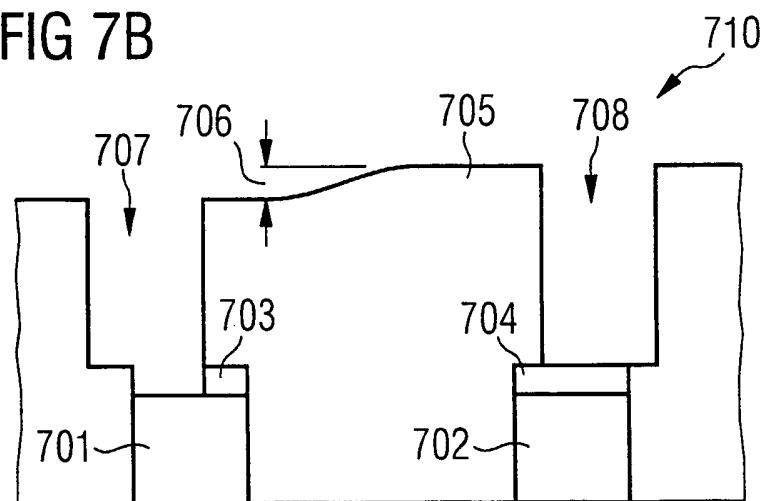

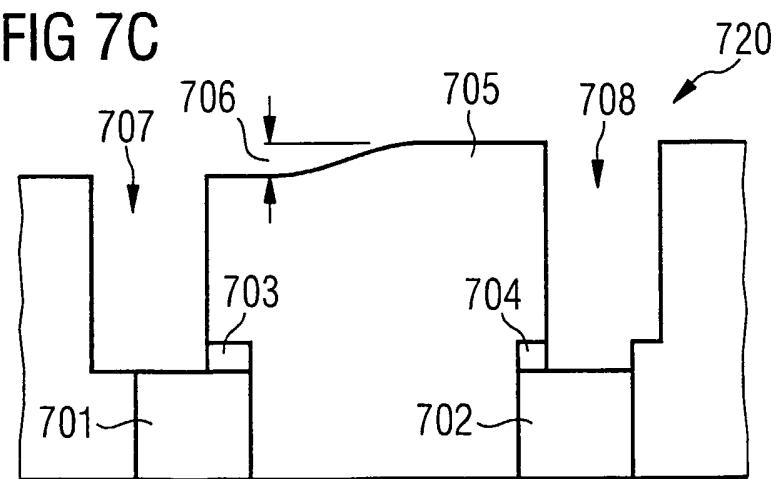

Bei Einsetzen der Opferschicht als schnell ätzbare Schicht kann die Opferschicht als eine Schicht vorgesehen sein, die gegenüber der elektrisch isolierenden Schicht eine wesentlich höhere Ätzrate aufweist. Auch in diesem Szenario ist es vorteilhaft, wenn insbesondere bei einem (unerwünschten, aber nicht immer vollständig vermeidbaren) lateralen Versatz der Ätzmaske, d.h. wenn die Ätzfront gegenüber den Einzelstrukturen der Opferschicht leicht seitlich versetzt ist, die Dicke der Opferschicht mindestens so groß gewählt wird wie ein Dickenrange (d.h. eine Schwankungsbreite der Dicke) der elektrisch isolierenden Schicht, da dann bei einem solchen lateralen Versatz kein unerwünschter enger Spalt erzeugt wird (siehe Fig.7A bis Fig.7C).

Bevorzugte Ausgestaltungen der Erfindung ergeben sich aus den abhängigen Ansprüchen.

Gemäß einer ersten bevorzugten Ausgestaltung des Verfahrens zum Herstellen einer Schicht-Anordnung wird zunächst die elektrisch leitfähige Schicht gebildet und wird die Opferschicht auf der elektrisch leitfähigen Schicht gebildet. Nachfolgend werden die elektrisch leitfähige Schicht und die

- Opferschicht gemeinsam strukturiert. Anschaulich werden gemäß dieser Ausgestaltung zunächst flächig die elektrisch leitfähige Schicht und auf deren freiliegender Oberfläche die Opferschicht gebildet. Danach werden die beiden übereinander angeordneten Schichten gemeinsam einem Lithographie- und einem Ätz-Verfahren unterzogen, so dass mit wenig Prozessschritten die strukturierten elektrisch leitfähigen Bereiche mit Material der Opferschicht bedeckt sind.

- 10 Gemäß einer zweiten bevorzugten Ausgestaltung des Verfahrens wird zunächst die elektrisch leitfähige Schicht gebildet und strukturiert. Nachfolgend wird die Opferschicht auf der elektrisch leitfähigen Schicht gebildet. In diesem Fall kann auch zwischen benachbarten Bereichen der strukturierten elektrisch leitfähigen Schicht Material der Opferschicht gebildet werden, was für den weiteren Ablauf der Prozessierung keinerlei Problem darstellt. Die Seitenwände der strukturierten Bereiche der elektrisch leitfähigen Schicht können bei der beschriebenen Prozessführung von 15 Material der Opferschicht frei bleiben.

- 20

Bei dem erfindungsgemäßen Verfahren kann die Opferschicht als Stoppschicht dienen. Gemäß dieser Ausgestaltung ist die Ätzfront beim Ätzen der elektrisch isolierenden Schicht beim Erreichen der Oberfläche der Opferschicht daran gehindert, 25 die Opferschicht zu entfernen, da diese bezogen auf die Ätzparameter zum Ätzen der elektrisch isolierenden Schicht (z.B. Ätzmittelzusammensetzung) daran gehindert ist, geätzt zu werden. Dadurch erreicht beim Fortsetzen des Ätzens mit 30 den Ätzparametern zum Ätzen der elektrisch isolierenden Schicht die Ätzfront sicher alle Oberflächenbereiche der strukturierten Opferschicht, ohne diese zunächst zu entfernen, d.h. die Opferschichtoberfläche stoppt diesen

16

Ätzprozess. Nach Modifizierung der Ätzparameter (z.B. Veränderung der Ätzmittelzusammensetzung) beginnt dann simultan das Entfernen aller gewünschten Bereiche der strukturierten Opferschicht.

5

Die Opferschicht kann mit einer höheren Rate entfernt werden als die elektrisch isolierende Schicht. Diese Ausgestaltung ermöglicht es, dass die Opferschicht mit einer höheren Ätzgeschwindigkeit oder Ätzrate, d.h. einem höheren

10 Materialabtrag pro Zeit, entfernt werden kann als die elektrisch isolierende Schicht. Wird z.B. die elektrisch isolierende Schicht aus Siliziumoxid-Material und die Opferschicht aus Siliziumnitrid- oder Siliziumoxinitrid-Material vorgesehen, so wird bei Verwendung einer Ätzung, bei 15 der Wasserstoff-, Sauerstoff- oder Kohlenmonoxid-Material als Ätzstoff zugesetzt wird oder deren Konzentration erhöht wird, ein Ätzen der Siliziumnitrid-Opferschicht wesentlich schneller erfolgen als ein Ätzen der elektrisch isolierenden Siliziumoxid-Schicht. Anschaulich kann bei Erhöhung 20 beispielsweise der Sauerstoff-Konzentration beim Ätzen die Ätzrate von Siliziumoxid sukzessive verringert werden, was bei einer Siliziumnitrid-Schicht nicht oder nur in wesentlich schwächerem Maße erfolgt. Dadurch kann mittels Auswählens der Materialkombination von elektrisch isolierender Schicht und 25 Opferschicht bzw. der Ätzparameter die Ätzgeschwindigkeit der unterschiedlichen Schichten genau eingestellt werden und das Bilden von engen Spalten stark verringert werden. Eine mangelhafte elektrische Kontaktierung zwischen Leiterbahnen und Vias aufgrund einer schlechten Auffüllung von engen 30 Spalten mit lokal hohem Aspektverhältnis ist somit erfindungsgemäß vermieden. Unerwünschte Hohlräume in der Schicht-Anordnung, Qualitätsprobleme und schlechte

elektrische Kontaktierungen sind bei der erfindungsgemäßen Schicht-Anordnung vermieden.

Die Opferschicht und die elektrisch isolierende Schicht

5 werden vorzugsweise unter Verwendung eines Ätz-Verfahrens entfernt, das derart eingerichtet ist, dass die Opferschicht mit einer höheren Ätzrate entfernt wird als die elektrisch isolierende Schicht.

10 Als Ätzmittel bei dem Ätz-Verfahren kann Tetrafluormethan ( $CF_4$ ), Trifluormethan ( $CHF_3$ ), Stickstoff ( $N_2$ ) und/oder Argon (Ar) verwendet werden.

Die Ätzrate kann eingestellt werden, indem bei dem Ätzmittel

15 die Konzentration von Sauerstoff ( $O_2$ ), Wasserstoff ( $H_2$ ) und/oder Kohlenmonoxid (CO) eingestellt wird oder indem die Temperatur des Wafers abgesenkt wird (bei niedriger Temperatur steigt die Nitrid-Ätzrate, bei höherer Temperatur sinkt die Oxid-Ätzrate leicht).

20 Alternativ oder zusätzlich zu dem Vorsehen von Opferschicht einerseits und elektrisch isolierender Schicht andererseits aus Material mit unterschiedlichen Ätzraten kann die Opferschicht eine geringere, vorzugsweise eine wesentlich geringere Dicke aufweisen als die elektrisch isolierende Schicht, vorzugsweise weniger als die Hälfte, weiter vorzugsweise weniger als ein Fünftel, noch weiter vorzugsweise weniger als ein Zehntel der Dicke der elektrisch isolierenden Schicht. Je dünner die Opferschicht vorgesehen

25 ist, desto schneller kann die Opferschicht entfernt werden, wodurch ein Unterätzen gering gehalten ist.

Zwischen der elektrisch leitfähigen Schicht und der Struktur aus elektrisch leitfähigem Material kann eine Liner-Schicht gebildet werden. Eine solche Liner-Schicht als Keim-, Haft- oder Barrièreschicht dient dazu, einen guten mechanischen und elektrischen Kontakt zwischen der strukturierten elektrisch leitfähigen Schicht (z.B. aus Aluminium) und der Struktur aus elektrisch leitfähigem Material (beispielsweise aus Wolfram) herzustellen. Auch kann mit einer Liner-Schicht vermieden werden, dass Material der strukturierten elektrisch leitfähigen Schicht in Material der Struktur aus elektrisch leitfähigem Material eindiffundiert oder vice versa.

Die Liner-Schicht kann nach dem Freilegen der Oberflächenbereiche der strukturierten elektrisch leitfähigen Schicht gebildet werden. Anschaulich kann gemäß dieser Ausgestaltung die Oberfläche eines Grabens der Schicht-Anordnung, welcher nach dem Freilegen der Oberflächenbereiche der strukturierten elektrisch leitfähigen Schicht gebildet ist, mit dem Liner-Material einer geringen Dicke von typischerweise 45nm bedeckt werden. Alternativ kann die Liner-Schicht zwischen dem Bilden der elektrisch leitfähigen Schicht und dem Bilden der Opferschicht erzeugt werden, so dass nach Entfernen der Opferschicht die elektrisch leitfähige Schicht bereits mit der Liner-Schicht bedeckt ist.

Das gemeinsame Strukturieren der elektrisch leitfähigen Schicht und der Opferschicht und/oder das Strukturieren der elektrisch isolierenden Schicht kann unter Verwendung eines Lithographie- und eines Ätz-Verfahrens durchgeführt werden.

Die elektrisch leitfähige Schicht und/oder die Opferschicht können unter Verwendung eines konformen Abscheideverfahrens gebildet werden, z.B. mittels eines CVD-Verfahrens ("Chemical

19

Vapour Deposition") oder eines ALD-Verfahrens ("Atomic Layer Deposition"). Mit dem Atomic-Layer-Deposition-Verfahren ist es möglich, eine Schicht einer sehr genau vorgebaren Dicke zu generieren, die bis auf die Genauigkeit einer Atomlage (d.h. 5 bis auf wenige Angstrom Genauigkeit) in sehr homogener Dicke auf einer Oberfläche abgeschieden werden kann. Das Bilden einer Opferschicht mit gleichmäßiger exakt vorgebbarer Dicke hat den Vorteil, dass deren Entfernung in einer räumlich konstanten Zeit möglich ist.

10

Die Schicht-Anordnung kann als integrierter Schaltkreis gebildet sein. Die Schicht-Anordnung kann auf und/oder in einem Halbleitermaterial (z.B. Silizium-Wafer oder Silizium-Chip) gebildet werden. Insbesondere kann die Schicht- 15 Anordnung in der Metallisierungsebene eines integrierten Schaltkreises gebildet werden ("end of the line").

Bei dem erfindungsgemäßen Verfahren kann ferner die elektrisch leitfähige Schicht zum Bilden von Leiterbahnen 20 strukturiert werden, und die Struktur aus elektrisch leitfähigem Material kann zum Bilden von Vias erzeugt werden.

Die elektrisch leitfähige Schicht und/oder die Struktur aus elektrisch leitfähigem Material kann aus Aluminium und/oder 25 Wolfram gebildet werden. Insbesondere ist Aluminium-Material für die elektrisch leitfähige Schicht als Leiterbahnen ein geeignetes Material. Für die Struktur aus elektrisch leitfähigem Material in einer Verwendung als Vias ist Wolfram-Material eine gute Wahl.

30

Die Opferschicht kann aus Siliziumnitrid und/oder aus Siliziumoxinitrid gebildet werden.

20

Die elektrisch isolierende Schicht kann aus Siliziumoxid gebildet werden.

Die Materialkombination einer stickstoffhaltigen Opferschicht und einer elektrisch isolierenden Schicht aus Siliziumoxid ist eine besonders günstige Kombination von Materialien, die bei geeignetem Ätzmittel zu einem schnellen Ätzen der Opferschicht und einem langsameren Ätzen der elektrisch isolierenden Schicht führt.

10

Die Liner-Schicht kann aus Titannitrid (TiN) gebildet werden.

Ein Ausführungsbeispiel der Erfindung ist in den Figuren dargestellt und wird im Weiteren näher erläutert.

15

Es zeigen:

Figuren 1A bis 1C Layout-Draufsichten gemäß dem Stand der Technik,

20

Figuren 2A bis 2K Schichtenfolgen zu unterschiedlichen Zeitpunkten während eines Verfahrens zum Herstellen einer Schicht-Anordnung gemäß dem Stand der Technik,

25 Figuren 3A bis 3H Schichtenfolgen zu unterschiedlichen Zeitpunkten während eines Verfahrens zum Herstellen einer Schicht-Anordnung gemäß einem ersten Ausführungsbeispiel der Erfindung,

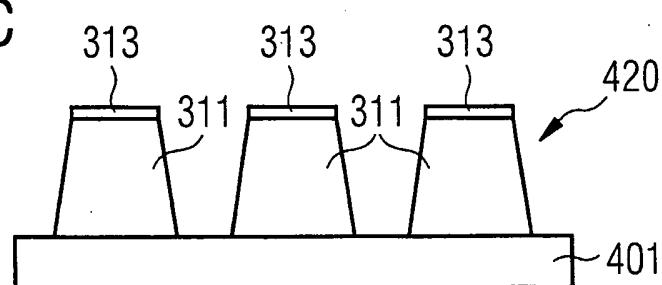

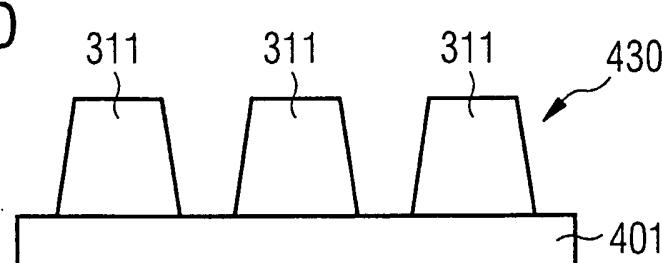

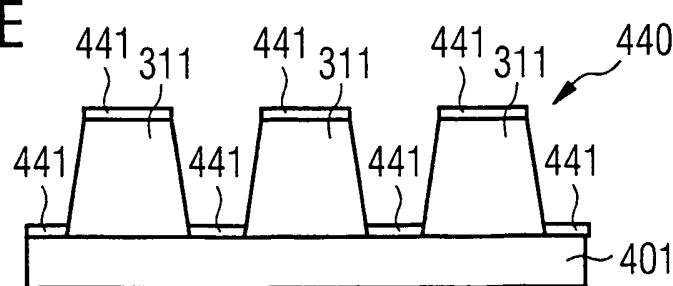

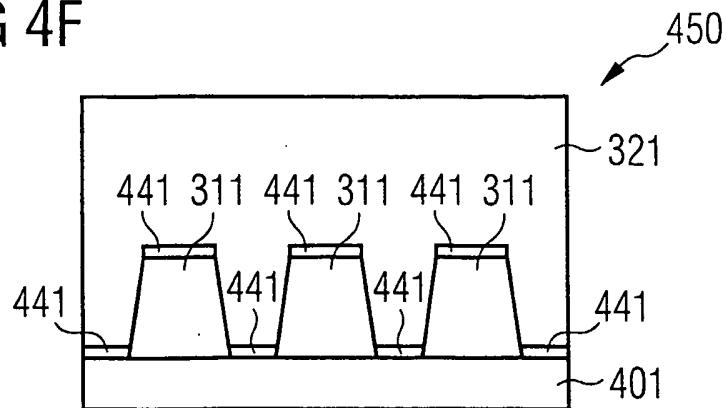

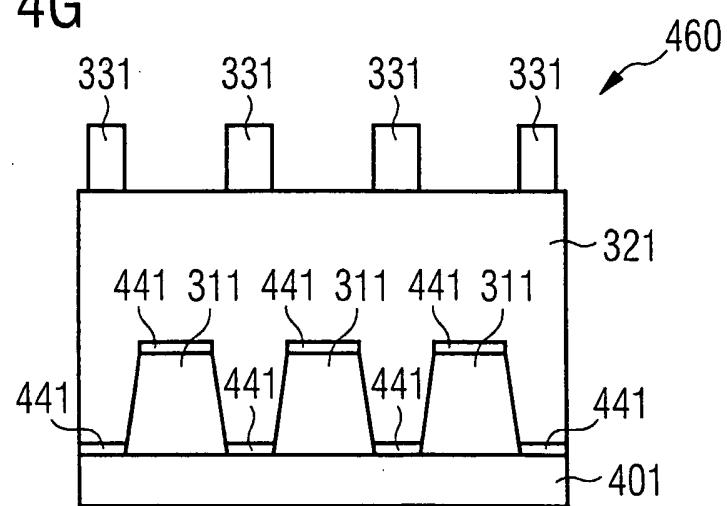

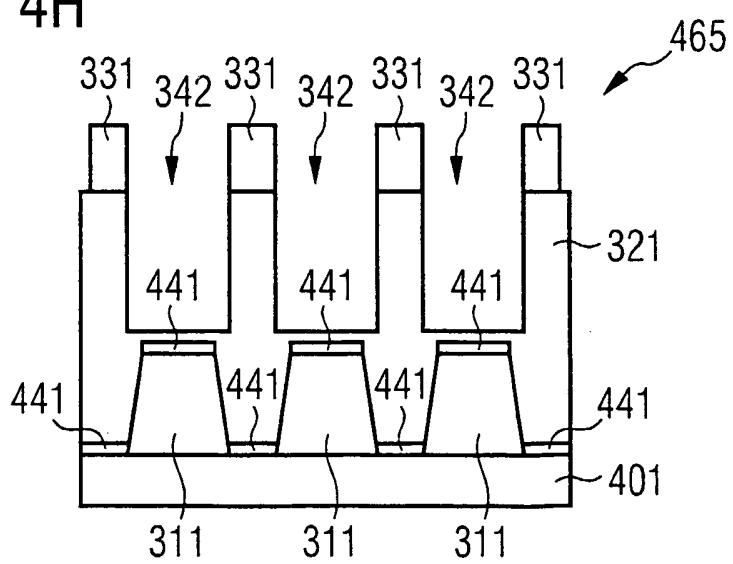

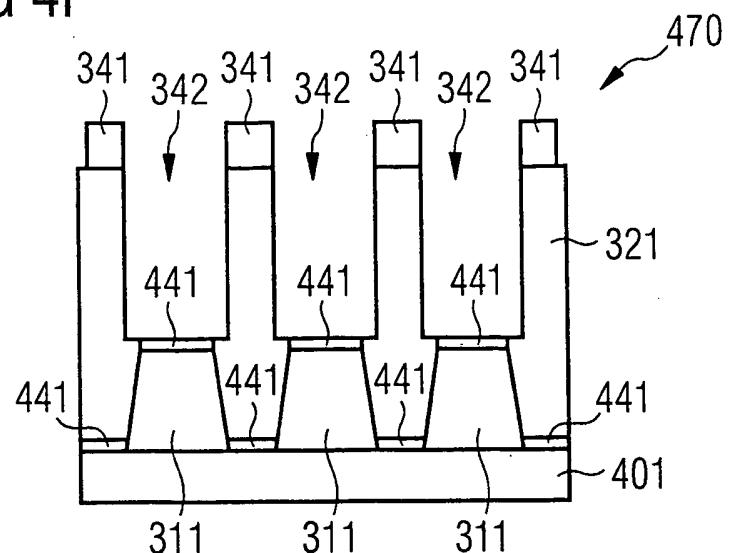

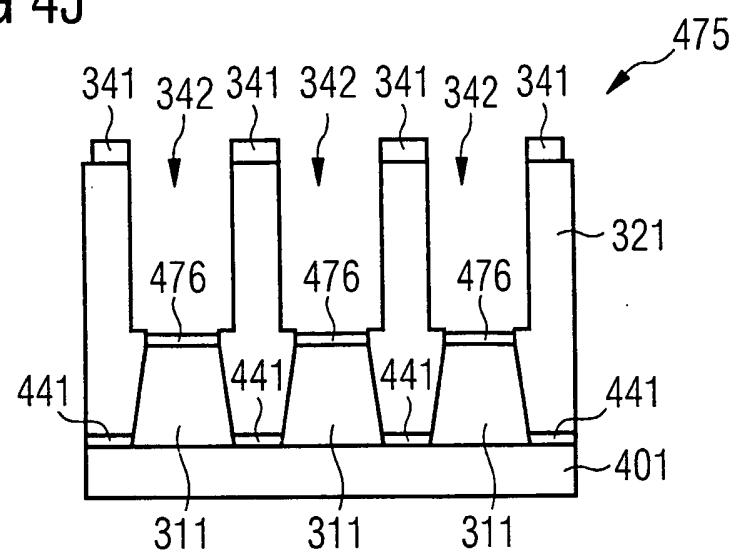

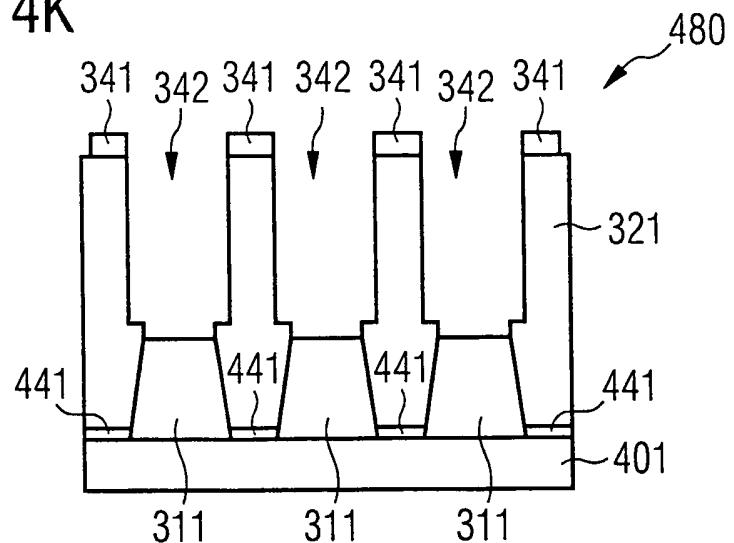

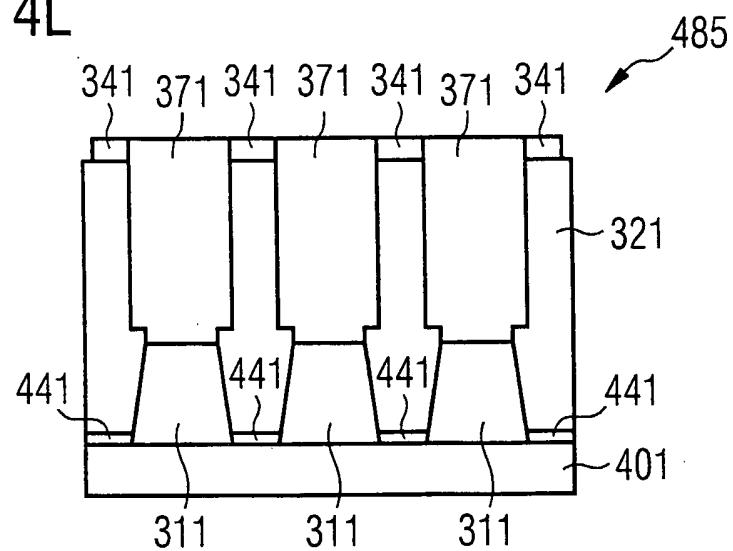

30 Figuren 4A bis 4L Schichtenfolgen zu unterschiedlichen Zeitpunkten während eines Verfahrens zum Herstellen einer Schicht-Anordnung gemäß einem zweiten Ausführungsbeispiel der Erfindung,

Figuren 5A bis 5C Schichtenfolgen zu unterschiedlichen Zeitpunkten während eines Verfahrens zum Herstellen einer Schicht-Anordnung gemäß der Erfindung,

5 Figuren 6A, 6B Schichtenfolgen zur Veranschaulichung des Einsatzes der erfindungsgemäßen Opferschicht als Ätz-Stoppschicht,

10 Figuren 7A bis 7C Schichtenfolgen zur Veranschaulichung des Einsatzes der erfindungsgemäßen Opferschicht als schnell ätzbare Schicht.

Gleiche oder ähnliche Komponenten in unterschiedlichen Figuren sind mit gleichen Bezugsziffern versehen.

15 Die Darstellungen in den Figuren sind schematisch und nicht maßstäblich.

20 Im Weiteren wird bezugnehmend auf Fig.3A bis Fig.3H ein Verfahren zum Herstellen einer Schicht-Anordnung gemäß einem ersten Ausführungsbeispiel der Erfindung beschrieben.

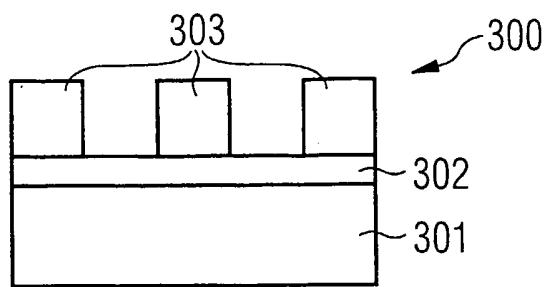

Um die in **Fig.3A** gezeigte Schichtenfolge 300 zu erhalten, wird eine Aluminium-Schicht 301 auf einem Silizium-Substrat 25 (nicht gezeigt) unter Verwendung eines konformen Abscheideverfahrens gebildet. Auf der Aluminium-Schicht 301 wird eine Siliziumnitrid-Opferschicht 302 unter Verwendung eines CVD-Verfahrens konform abgeschieden. Alternativ kann eine solche Opferschicht auch aus Siliziumoxinitrid-Material 30 gebildet werden. Auf der Siliziumnitrid-Opferschicht 302 wird Photoresist-Material gebildet und unter Verwendung eines Lithographie- und eines Ätz-Verfahrens zu einer Photoresist-Maske 303 strukturiert.

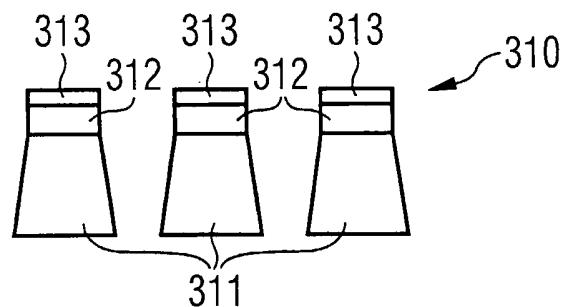

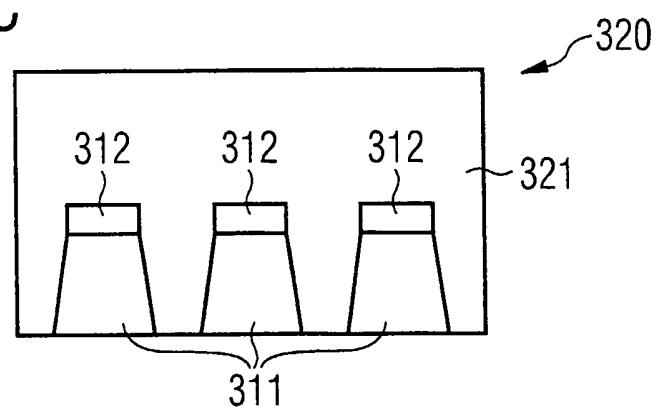

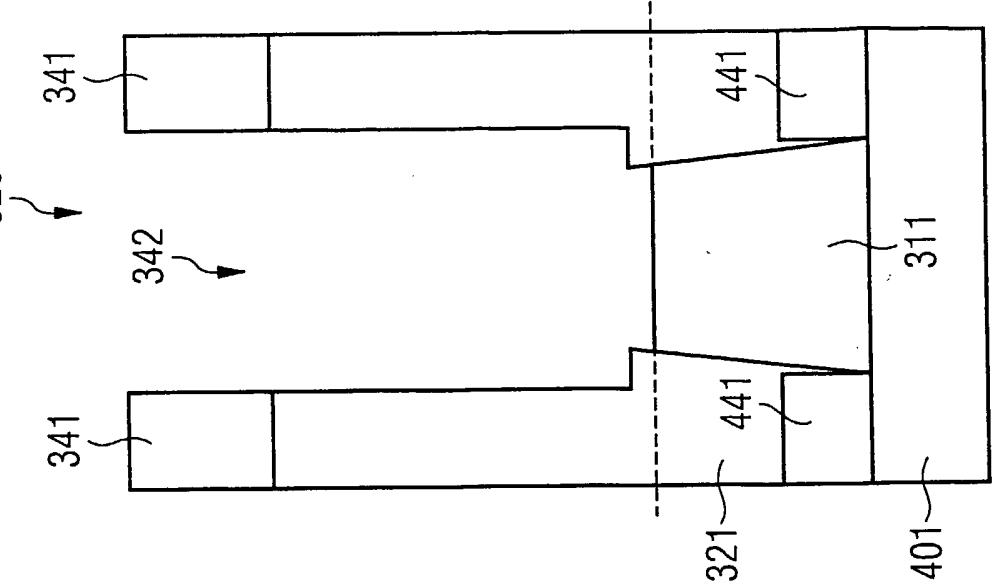

Um die in **Fig.3B** gezeigte Schichtenfolge 310 zu erhalten, werden ausgehend von der in Fig.3A gezeigten Schichtenfolge 300 die Aluminium-Schicht 301 und die Siliziumnitrid-Opferschicht 302 unter Verwendung eines Ätz-Verfahrens gemeinsam, d.h. in einem zusammengehörigen Verfahrensschritt, strukturiert. Dadurch werden Aluminium-Leiterbahnen 311 gebildet, wobei auf jeder Aluminium-Leiterbahn 311 eine von mehreren Opferschicht-Bereichen 312 angeordnet ist, bedeckt von einem Photoresist-Rest 313, der nach dem Ätz-Verfahren auf der Oberfläche der Schichtenfolge 310 verblieben ist. Der Photoresist-Rest 313 wird nachfolgend unter Verwendung eines Stripping-Verfahrens entfernt.

Um die in **Fig.3C** gezeigte Schichtenfolge 320 zu erhalten, wird nach dem Entfernen des Photoresist-Rests 313 eine Siliziumoxid-Schicht 321 auf der Schichtenfolge 310 unter Verwendung eines CVD-Verfahrens ("Chemical Vapour Deposition") gebildet.

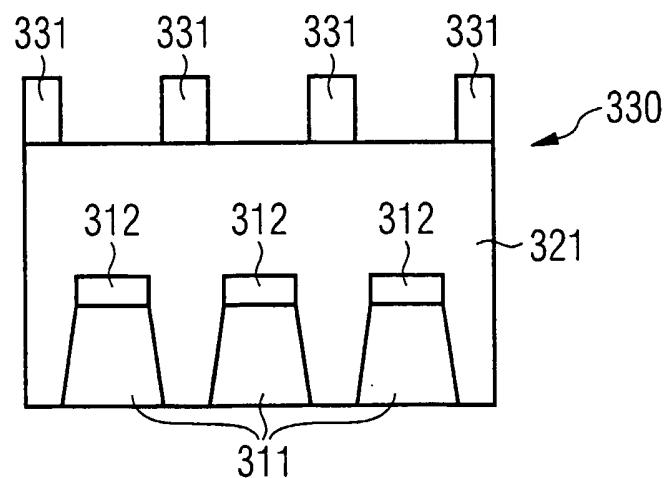

Um die in **Fig.3D** gezeigte Schichtenfolge 330 zu erhalten, wird auf der Schichtenfolge 320 eine Photoresist-Schicht gebildet und unter Verwendung eines Lithographie- und eines Ätz-Verfahrens zu einer Photoresist-Maske 331 strukturiert.

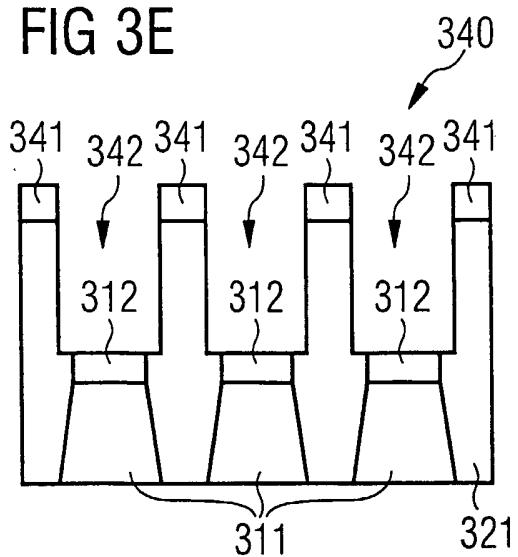

Um die in **Fig.3E** gezeigte Schichtenfolge 340 zu erhalten, wird die Schichtenfolge 330 einem derartigen Ätz-Verfahren unterzogen, dass unter Verwendung der Ätz-Maske 331 Material der Siliziumoxid-Schicht 321 entfernt wird, solange, bis die Ätz-Front die Oberfläche der Opferschicht-Bereiche 312 erreicht hat. Hierbei dienen die Opferschicht-Bereiche 312 als Stoppschicht des Ätz-Prozesses. Aufgrund dieses Ätz-Verfahrens werden in der Siliziumoxid-Schicht 321 Gräben 342 gebildet und Oberflächenbereiche der Opferschicht-Bereiche

312 freigelegt. Aufgrund der Funktionalität der Opferschicht-Bereiche 312 als Stoppschichten ist sichergestellt, dass auch bei lokal unterschiedlicher Dicke der Siliziumoxid-Schicht 321 in Bereichen unterschiedlicher Gräben 342 jeweils ein

5 Ätzen nur bis zur Oberfläche der dünnen Opferschicht-Bereiche 312 erfolgt. Es ist anzumerken, dass der Einsatz der erfindungsgemäßen Opferschicht als Ätzstoppschicht nur eine von mehreren Varianten ist. Gemäß einer anderen Variante kann alternativ oder ergänzend eine besonders hohe

10 Ätzgeschwindigkeit des Materials der Opferschicht ausgenutzt werden (siehe z.B. Fig.7A bis 7C).

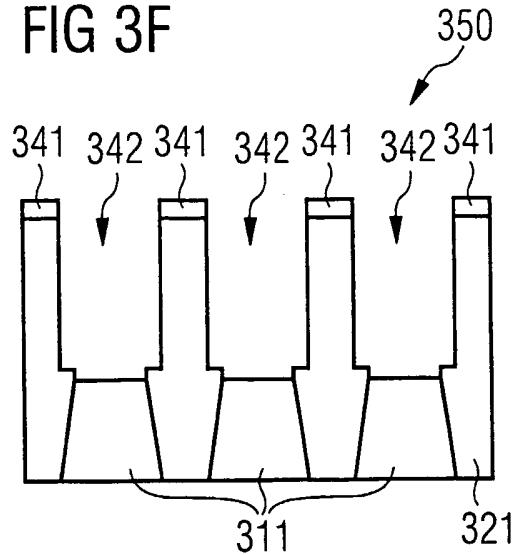

Um die in **Fig.3F** gezeigte Schichtenfolge 350 zu erhalten, werden unter Verwendung eines anderen Ätz-Verfahrens, welches

15 zum Ätzen des Materials der Opferschicht-Bereiche 312 eingerichtet ist, die Opferschicht-Bereiche 312 in allen Gräben 342 entfernt, wodurch Oberflächenbereiche der Aluminium-Leiterbahn 311 freigelegt werden. Das Material der Opferschicht-Bereiche 312 (Siliziumnitrid) hat solche

20 Materialeigenschaften, dass das Ätz-Verfahren dieses Material mit einer sehr hohen Ätzrate, d.h. sehr schnell entfernt. Ein Erhöhen des Verhältnisses der Ätzraten von Siliziumnitrid zu Siliziumoxid kann zum Beispiel mittels Zusetzens einer Sauerstoffkomponente zu dem Ätzmittel erfolgen. Ferner ist

25 die Dicke der Opferschicht-Bereiche 312 derart gering gewählt, dass in Kombination mit der erhöhten Ätzrate ein besonders schnelles Entfernen dieser Bereiche gewährleistet ist. Dies führt dazu, dass die Ätz-Front die Oberflächenbereiche der unterschiedlichen Leiterbahnen 311

30 annähernd gleichzeitig und nach kurzer Prozessierungszeit erreicht, wodurch ein langwieriges gemäß dem Stand der Technik erforderliches Unterätzen vermieden ist.

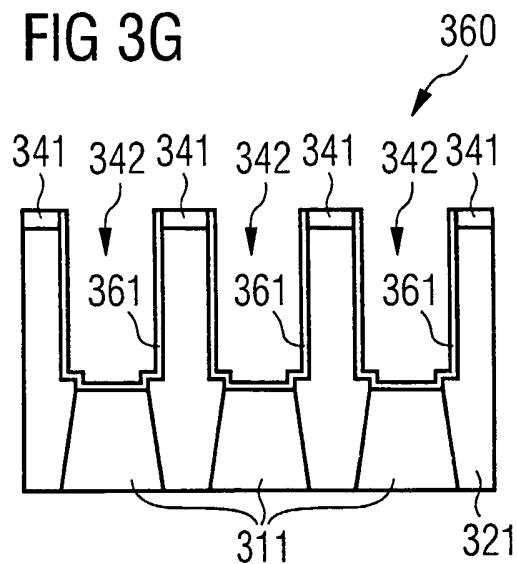

Um die in **Fig.3G** gezeigte Schichtenfolge 360 zu erhalten, wird das bezugnehmend auf Fig.3F beschriebene Ätz-Verfahren noch für eine geringe Zeit weitergeführt, d.h. möglicherweise ein geringfügiges Unterätzen in Kauf genommen, um

5 sicherzustellen, dass wirklich alle Oberflächenbereiche der Leiterbahnen 311 vollständig von zuvor darauf angeordnetem Material befreit sind. Wie in Fig.3G gezeigt, sind aufgrund der Kürze dieses optionalen Überätzverfahrens keine oder nur äußerst geringfügige enge Spalten (wie in Fig.2H mit

10 Bezugszeichen 261 gezeigt) auftreten. Ferner wird, um die in Fig.3G gezeigte Schichtenfolge 360 zu erhalten, unter Verwendung eines Abscheideverfahrens eine Liner-Schicht 361 aus Titannitrid-Material eine Dicke von ungefähr 45nm in jedem der Gräben 342 gebildet, womit insbesondere die

15 freiliegenden Oberflächenbereiche der Aluminium-Leiterbahn 311 mit dem Liner-Material als Barrierenschicht zum Koppeln der Aluminium-Leiterbahn 311 mit nachfolgend aufgebrachtem Wolfram-Material von Vias bedeckt sind.

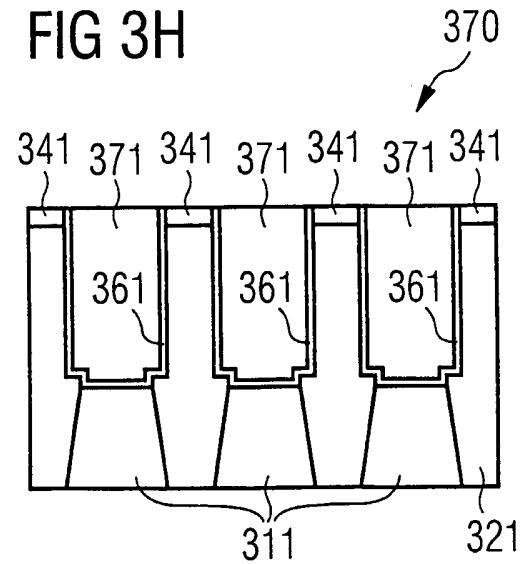

20 Um die in **Fig.3H** gezeigte Schicht-Anordnung 370 gemäß einem bevorzugten Ausführungsbeispiel der Erfindung zu erhalten, wird Wolfram-Material in die Gräben 342 eingefüllt, womit Wolfram-Vias 371 gebildet werden. Die Wolfram-Vias 371 sind mittels der Liner-Schicht 361 elektrisch und mechanisch gut

25 mit der Aluminium-Leiterbahn 311 gekoppelt. Aufgrund des Vermeidens von engen Spalten in Grenzbereichen zwischen seitlichen Abschnitten der Aluminium-Leiterbahn 311 und angrenzendem Material der Siliziumoxid-Schicht 321 sind elektrische Kopplungsprobleme zwischen Wolfram-Vias 371 und

30 Aluminium-Leiterbahn 311 sicher vermieden, wodurch eine Schicht-Anordnung 370 mit einer hohen Qualität und einer guten elektrischen Ankopplung ermöglicht ist.

Im Weiteren wird bezugnehmend auf Fig.4A bis Fig.4L ein Verfahren zum Herstellen einer Schicht-Anordnung gemäß einen zweiten Ausführungsbeispiel der Erfindung beschrieben.

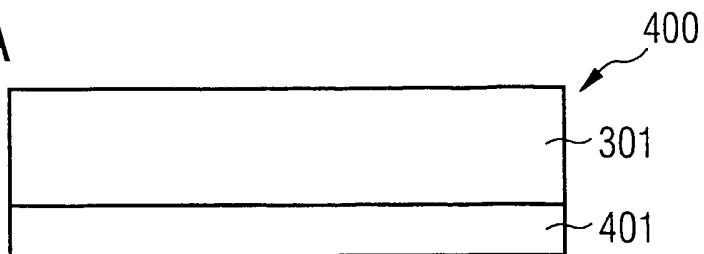

5 Um die in **Fig.4A** gezeigte Schichtenfolge 400 zu erhalten, wird auf einem Silizium-Substrat 401 eine Aluminium-Schicht 301 gebildet.

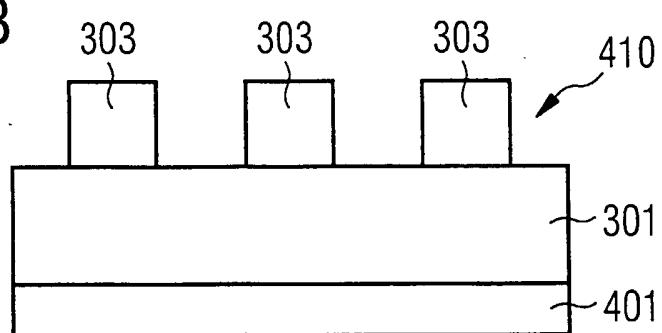

Um die in **Fig.4B** gezeigte Schichtenfolge 410 zu erhalten, 10 wird eine Photoresist-Maske 303 auf die Oberfläche der Schichtenfolge 400 aufgebracht.

Um die in **Fig.4C** gezeigte Schichtenfolge 420 zu erhalten, wird die Aluminium-Schicht 301 mittels der Photoresist-Maske 15 303 strukturiert, wodurch Aluminium-Leiterbahnen 311 gebildet werden. Auf der Oberfläche der Aluminium-Leiterbahnen 311 sind Photoresist-Reste 313 zu sehen.

Je nach angestrebter Strukturfeinheit kann zum Strukturieren 20 der Aluminium-Schicht 301 eine Hartmaske eingesetzt werden. Der Photoresist 303 wird dann bereits nach der Strukturübertragung in die Hartmaske entfernt. Die Hartmaske ersetzt dann die Photoresist-Maske 303.

25 Um die in **Fig.4D** gezeigte Schichtenfolge 430 zu erhalten, werden die Photoresist-Reste 313 (z.B. mittels eines Stripping-Verfahrens oder mittels eines Ätz-Verfahrens) entfernt.

30 Um die in **Fig.4E** gezeigte Schichtenfolge 440 zu erhalten, werden Opferschicht-Bereiche 441 auf der Schichtenfolge 430 gebildet, wodurch gemäß durch Fig.4E horizontale Oberflächenbereiche der Schichtenfolge 430 mit Opferschicht-

Bereichen 441 bedeckt werden. Die Opferschicht-Bereiche 441 können auch als Adjust-Liner bezeichnet werden.

Um die in **Fig.4F** gezeigte Schichtenfolge 450 zu erhalten,

- 5 wird eine Siliziumoxid-Schicht 321 als Interlayer-Dielektrikum (ILD) abgeschieden.

Um die in **Fig.4G** gezeigte Schichtenfolge 460 zu erhalten,

wird eine Photoresist-Maske 331 auf der Oberfläche der

- 10 Schichtenfolge 450 gebildet.

Um die in **Fig.4H** gezeigte Schichtenfolge 465 zu erhalten,

werden mittels Ätzens unter Verwendung der Photoresist-Maske 331 Gräben 342 in der Siliziumoxid-Schicht 321 gebildet.

- 15 Gemäß dem in Fig.4H gezeigten Zustand des Ätz-Verfahrens hat die Ätzfront die Oberfläche der Opferschicht-Bereiche 441 noch nicht erreicht.

Um die in **Fig.4I** gezeigte Schichtenfolge 470 zu erhalten,

- 20 wird das Ätzen der Siliziumoxid-Schicht 321 fortgesetzt, wobei gemäß Fig.4I die Ätzfront gerade die Oberfläche der Opferschicht-Bereiche 441 auf den oberen Endabschnitten der Aluminium-Leiterbahn 311 erreicht hat.

- 25 Um die in **Fig.4J** gezeigte Schichtenfolge 475 zu erhalten, werden die freigelegten Opferschicht-Bereiche 441 einem Ätz-Verfahren unterzogen, wobei die Ätzparameter derart eingestellt werden, dass die freigelegten Opferschicht-Bereiche 441 wesentlich schneller geätzt werden als das freiliegende Material der Siliziumoxid-Schicht 321. Dadurch wird die in Fig.4J gezeigte Schichtenfolge 475 erhalten, bei welcher aufgrund der unterschiedlichen Ätzgeschwindigkeiten zum Ätzen der Opferschicht-Bereiche 441 einerseits und zum

Ätzen der Siliziumoxid-Schicht 321 andererseits stufige Abschnitte an Übergangsbereichen zwischen dem Material 321 und den zurückzuätzenden Opferschicht-Bereichen 441 erhalten werden. Aufgrund des Ätzens der freigelegten Opferschicht-5 Bereiche 441 werden Opferschicht-Reste 476 generiert.

Um die in **Fig.4K** gezeigte Schichtenfolge 480 zu erhalten, wird das Ätz-Verfahren zum Ätzen der freigelegten Opferschicht-Bereiche 441 bzw. zum Ätzen der Opferschicht-10 Reste 476 fortgesetzt. Aufgrund der unterschiedlichen Ätzgeschwindigkeiten des Materials der Opferschicht einerseits und der Siliziumoxid-Schicht 321 andererseits werden an Kanten zwischen den Leiterbahnen 311 und der Siliziumoxid-Schicht 321 leicht stufige Abschnitte erhalten, 15 nicht hingegen die unerwünschten engen Spalten wie gemäß dem Stand der Technik.

Um die in Fig.4L gezeigte Schichtenfolge 485 zu erhalten, werden die Gräben 342 mit Wolfram-Material aufgefüllt, 20 wodurch Wolfram-Vias 371 gebildet werden.

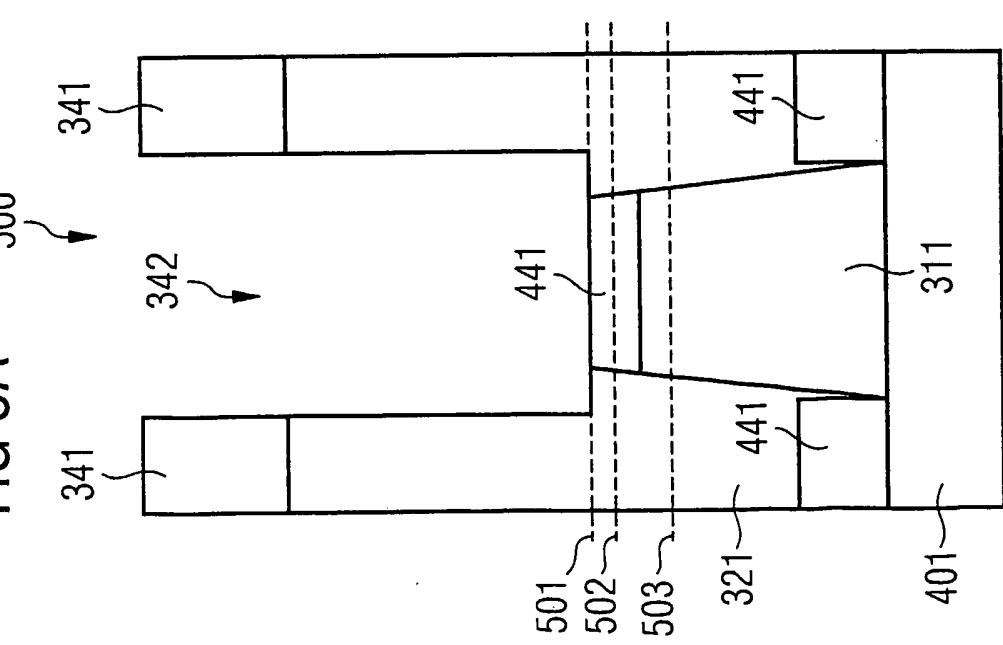

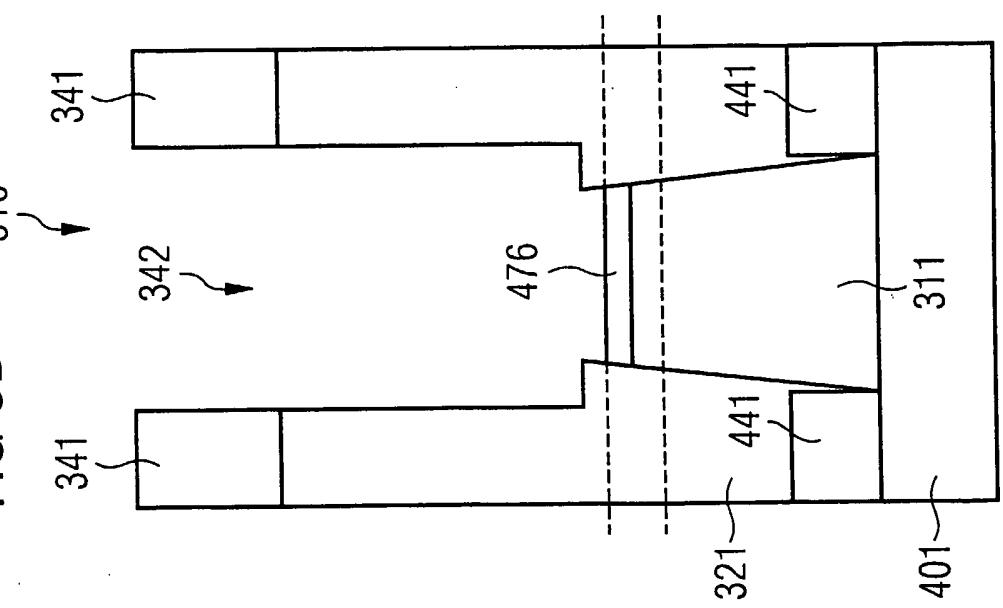

Im Weiteren werden nochmals bezugnehmend auf Fig.5A bis Fig.5C Detailansichten der Schichtenfolgen aus Fig.4I bis Fig.4K beschrieben, um das erfindungsgemäße Vermeiden von 25 engen Spalten nochmals zu erläutern. In den Schichtenfolgen 500 bis 520 aus Fig.5A bis Fig.5C sind eine erste Ebene 501, eine zweite Ebene 502 und eine dritte Ebene 503 der Ätzfront zum Ätzen der Opferschicht-Bereiche 441 gezeigt.

30 Die in **Fig.5A** gezeigte Schichtenfolge 500 entspricht im Wesentlichen der in Fig.4I gezeigten Schichtenfolge 470. Bei dem in Fig.5A gezeigten Zustand ist das Ätz-Verfahren soweit fortgeschritten, dass die Oberflächenbereiche der

Opferschicht-Bereiche 441 auf den Leiterbahnen 311 gerade freigelegt sind.

Wird das Ätz-Verfahren fortgesetzt, so wird die in **Fig.5B** 5 gezeigte Schichtenfolge 510 erhalten, welche im Wesentlichen der in Fig.4J gezeigten Schichtenfolge 475 entspricht. Bei Schichtenfolge 510 ist die Ätzfront hinsichtlich der Opferschicht-Bereiche 441 bis zu der zweiten Ebene 502 vorgedrungen, so dass nur noch Opferschicht-Reste 476 10 vorhanden sind. Da die Ätzparameter derart gewählt sind, dass das Material der Opferschicht-Bereiche 441 wesentlich schneller geätzt wird als das Material der Siliziumoxid-Schicht 321, bilden sich an Randabschnitten der Opferschicht-Reste 476 stufenartige Siliziumoxid-Strukturen, nicht 15 hingegen unerwünschte enge Spalten.

Bei einem weiteren Fortsetzen des Ätz-Verfahrens wird die in **Fig.5C** 20 gezeigte Schichtenfolge 520 erhalten, bei dem die Ätzfront bis an die dritte Ebene 503 vorgedrungen ist. Dieser Zustand entspricht im Wesentlichen der in Fig.4K gezeigten Schichtenfolge 480. In diesem Zustand sind die Oberflächen der Leiterbahnen 311 freigelegt, und das Material der Opferschicht-Bereiche 441 ist vollständig von den Oberflächen 25 der Leiterbahnen 311 entfernt. Material der Opferschicht-Bereiche 441 zwischen benachbarten Leiterbahnen verbleibt in der Schichtenfolge 520 und hat keinen negativen Einfluss auf die Prozessführung oder Funktionalität der Schichtenfolge 520.

30 Aufgrund der gewählten Ätzparameter sind, wie in Fig.5C gezeigt, die Oberflächenbereiche der Leiterbahnen 311 sicher freigelegt, wobei enge Spalten an den Grenzbereichen zwischen

den Leiterbahnen 311 und der elektrisch isolierenden Siliziumoxid-Schicht 321 vermieden sind.

Im Weiteren werden bezugnehmend auf Fig.6A, Fig.6B

5 Schichtenfolgen zur Veranschaulichung des Einsatzes der erfindungsgemäßen Opferschicht als Ätz-Stoppschicht beschrieben.

In **Fig.6A** ist eine Schichtenfolge 600 mit einer ersten

10 Aluminium-Leiterbahn 601 und mit einer zweiten Aluminium-Leiterbahn 602 gezeigt, wobei auf der ersten Aluminium-Leiterbahn 601 ein erster Opferschicht-Bereich 603 und auf der zweiten Aluminium-Leiterbahn 602 ein zweiter Opferschicht-Bereich 604 gebildet ist. Komponenten 601 bis

15 604 sind von einer Siliziumoxid-Schicht 605 bedeckt, deren Dicke nicht vollständig homogen ist, sondern die einen Dickenrange 606 aufweist.

In **Fig.6B** ist eine Schichtenfolge 610 gezeigt, bei der unter

20 Verwendung eines Ätzverfahrens ein erster Graben 611 zum Freilegen des ersten Opferschicht-Bereichs 603 und ein zweiter Graben 612 zum Freilegen des zweiten Opferschicht-Bereichs 604 gebildet ist. Aufgrund des Dickenranges 606 und eines unerwünschten lateralen Ätzmasken-Versatzes hat die

25 Ätzfront seitlich des ersten Opferschicht-Bereichs 603 Material der in diesem Bereich dünnen Siliziumoxid-Schicht 605 entfernt, wohingegen die Ätzfront seitlich des zweiten Opferschicht-Bereichs 604 kein Material der in diesem Bereich dicken Siliziumoxid-Schicht 605 entfernt hat, sondern dort

30 gerade erst die Oberfläche des zweiten Opferschicht-Bereichs 604 erreicht hat.

30

Bei Einsetzen der Opferschicht-Bereiche 603, 604 als Ätz-Stoppschicht wird somit zunächst oberhalb der Aluminium-Leiterbahnen 601, 602 und oberhalb der Opferschicht-Bereiche 603, 604 befindliches Material der Siliziumoxid-Schicht 605 entfernt, wobei der Materialabtrag des Ätzverfahrens beim Erreichen der Opferschicht-Bereiche 603, 604 endet. Bei dem (unerwünschten, aber nicht immer vollständig vermeidbaren) lateralen Versatz der Ätzmaske, d.h. da die Ätzfront gegenüber den Opferschicht-Bereichen 603, 604 leicht seitlich versetzt ist, kann es vorkommen, dass neben den Opferschicht-Bereichen 603, 604 befindliches Material der Siliziumoxid-Schicht 605 entfernt wird, das gemäß Fig.6B seitlich unterhalb der Oberfläche des Opferschicht-Bereichs 603 angeordnet ist. In diesem Szenario ist es vorteilhaft, wenn die Dicke der Opferschicht-Bereiche 603, 604 mindestens so groß gewählt wird wie der Dickenrange 606 (d.h. eine Schwankungsbreite der Dicke) der Siliziumoxid-Schicht 605, da dann bei einem solchen lateralen Versatz kein unerwünschter enger Spalt erzeugt wird. Erreicht nämlich die Ätzfront an der dicksten Stelle der Siliziumoxid-Schicht 605 (d.h. oberhalb des zweiten Opferschicht-Bereichs 604) die Opferschicht, ist sie an der dünnsten Stelle der Siliziumoxid-Schicht 605 an dem ersten Opferschicht-Bereich 603 noch nicht vollständig vorbei.

25

Im Weiteren werden bezugnehmend auf Fig.7A bis Fig.7C Schichtenfolgen zur Veranschaulichung des Einsatzes der erfindungsgemäßen Opferschicht als schnell ätzbare Schicht beschrieben.

30

In **Fig.7A** ist eine Schichtenfolge 700 mit einer ersten Aluminium-Leiterbahn 701 und mit einer zweiten Aluminium-Leiterbahn 702 gezeigt, wobei auf der ersten Aluminium-

Leiterbahn 701 ein erster Opferschicht-Bereich 703 und auf der zweiten Aluminium-Leiterbahn 702 ein zweiter

Opferschicht-Bereich 704 gebildet ist. Komponenten 701 bis 704 sind von einer Siliziumoxid-Schicht 705 bedeckt, deren

5 Dicke nicht vollständig homogen ist, sondern die einen Dickenrange 706 aufweist.

Bei der Schichtenfolge 700 ist unter Verwendung eines

Ätzverfahrens ein erster Graben 707 zum Freilegen des ersten Opferschicht-Bereichs 703 und ein zweiter Graben 708 geätzt,

10 der aufgrund des Dickenranges 706 und der großen Dicke der Siliziumoxid-Schicht 705 in diesem Bereich noch nicht so tief ist, dass der zweite Opferschicht-Bereich 704 bereits freigelegt wäre. Anders ausgedrückt hat bei der Schichtenfolge 700 die Ätzfront die Opferschicht gerade an 15 der dünnsten Stelle der Siliziumoxid-Schicht 705, d.h. an dem ersten Opferschicht-Bereich 703 erreicht.

In **Fig.7B** ist eine Schichtenfolge 710 zu einem späteren Zeitpunkt während der Prozessierung gezeigt. Gemäß Fig.7B hat 20 die Ätzfront den zweiten Opferschicht-Bereich 704 erreicht. Aufgrund der hohen Ätzrate des Materials der Opferschicht ist ein freiliegender Abschnitt des ersten Opferschicht-Bereichs 703 bereits vollständig entfernt. Seitlich davon ist aufgrund der wesentlich geringeren Ätzrate der Siliziumoxid-Schicht 25 705 kein störender enger Spalt erzeugt.

In **Fig.7C** ist eine Schichtenfolge 720 zu einem noch späteren Zeitpunkt während der Prozessierung gezeigt. Gemäß Fig.7C hat die Ätzfront auch einen freiliegenden Abschnitt des zweiten 30 Opferschicht-Bereichs 704 entfernt, nahe welchem Bereich die Siliziumoxid-Schicht 705 die größte Dicke aufweist. Aufgrund der hohen Ätzrate des Materials der Opferschicht und der wesentlich geringeren Ätzrate der Siliziumoxid-Schicht 705 sind keine störenden engen Spalten erzeugt. Dies gilt

32

insbesondere dann, wenn die vertikale Dicke der Opferschicht-Bereiche 703, 704 mindestens so groß ist wie der Dickenrange 706.

33

In diesem Dokument sind folgende Veröffentlichungen zitiert:

[1] DE 101 40 468 A1

5 [2] US 5 451 543 A

## Bezugszeichenliste

- 100 Leiterbahn

- 101 Via

- 102 Landingpad

- 110 erste Layout-Draufsicht

- 120 zweite Layout-Draufsicht

- 130 dritte Layout-Draufsicht

- 200 Schichtenfolge

- 201 Aluminium-Schicht

- 202 Photoresist-Maske

- 210 Schichtenfolge

- 211 Aluminium-Leiterbahnen

- 212 Photoresist-Rest

- 220 Schichtenfolge

- 221 Siliziumoxid-Schicht

- 230 Schichtenfolge

- 231 Photoresist-Maske

- 240 Schichtenfolge

- 241 Photoresist-Rest

- 242 Gräben

- 250 Schichtenfolge

- 260 Schichtenfolge

- 261 enge Spalten

- 270 Schicht-Anordnung

- 271 Wolfram-Via

- 280 Schichtenfolge

- 281 Substrat

- 282 erste Ebene

- 283 zweite Ebene

- 284 dritte Ebene

- 285 Schichtenfolge

- 290 Schichtenfolge

- 300 Schichtenfolge

- 301 Aluminium-Schicht

302 Siliziumnitrid-Opferschicht

303 Photoresist-Maske

310 Schichtenfolge

311 Aluminium-Leiterbahnen

312 Opferschicht-Bereiche

313 Photoresist-Rest

320 Schichtenfolge

321 Siliziumoxid-Schicht

330 Schichtenfolge

331 Photoresist-Maske

340 Schichtenfolge

341 Photoresist-Rest

342 Gräben

350 Schichtenfolge

360 Schichtenfolge

361 Liner-Schicht

370 Schicht-Anordnung

371 Wolfram-Vias

400 Schichtenfolge

401 Silizium-Substrat

410 Schichtenfolge

420 Schichtenfolge

430 Schichtenfolge

431 Photoresist-Maske

440 Schichtenfolge

441 Opferschicht-Bereiche

450 Schichtenfolge

460 Schichtenfolge

465 Schichtenfolge

470 Schichtenfolge

475 Schichtenfolge

476 Opferschicht-Reste

480 Schichtenfolge

500 Schichtenfolge

501 erste Ebene

502 zweite Ebene

503 dritte Ebene

510 Schichtenfolge

520 Schichtenfolge

600 Schichtenfolge

601 erste Aluminium-Leiterbahn

602 zweite Aluminium-Leiterbahn

603 erster Opferschicht-Bereich

604 zweiter Opferschicht-Bereich

605 Siliziumoxid-Schicht

606 Dickenrange

610 Schichtenfolge

611 erster Graben

612 zweiter Graben

700 Schichtenfolge

701 erste Aluminium-Leiterbahn

702 zweite Aluminium-Leiterbahn

703 erster Opferschicht-Bereich

704 zweiter Opferschicht-Bereich

705 Siliziumoxid-Schicht

706 Dickenrange

707 erster Graben

708 zweiter Graben

710 Schichtenfolge

720 Schichtenfolge

**Patentansprüche:**

1. Verfahren zum Herstellen einer Schicht-Anordnung,

bei dem

- 5     • zunächst eine elektrisch leitfähige Schicht auf einem

Substrat gebildet und strukturiert wird;

- nachfolgend eine Opferschicht auf zumindest einem Teil

der strukturierten elektrisch leitfähigen Schicht

gebildet wird;

- 10    • eine elektrisch isolierende Schicht auf der elektrisch

leitfähigen Schicht und auf der Opferschicht gebildet

wird;

- die elektrisch isolierende Schicht derart strukturiert

wird, dass Oberflächenbereiche der Opferschicht

15    freigelegt werden, wobei das Entfernen der elektrisch

isolierenden Schicht gestoppt wird, wenn die Oberfläche

der Opferschicht-Bereiche auf den oberen Endabschnitten

der elektrisch leitfähigen Schicht gerade erreicht ist;

- die freigelegten Bereiche der Opferschicht entfernt

20    werden, womit Oberflächenbereiche der elektrisch

leitfähigen Schicht freigelegt werden;

- die freigelegten Oberflächenbereiche der strukturierten

elektrisch leitfähigen Schicht mit einer Struktur aus

elektrisch leitfähigem Material bedeckt werden.

- 25    2. Verfahren zum Herstellen einer Schicht-Anordnung nach

Anspruch 1,

wobei die Opferschicht als Stoppschicht dient.

- 30    3. Verfahren zum Herstellen einer Schicht-Anordnung nach

einem der Ansprüche 1 oder 2,

bei dem die Opferschicht mit einer höheren Rate entfernt wird

als die elektrisch isolierende Schicht.

- 35    4. Verfahren zum Herstellen einer Schicht-Anordnung nach

einem der Ansprüche 1 bis 3,

bei dem die Opferschicht und die elektrisch isolierende

Schicht unter Verwendung eines Ätz-Verfahrens entfernt werden, das derart eingerichtet ist, dass die Opferschicht mit einer höheren Ätzrate entfernt wird als die elektrisch isolierende Schicht.

5

5. Verfahren zum Herstellen einer Schicht-Anordnung nach Anspruch 4,

bei dem als Ätzmittel bei dem Ätz-Verfahren

- Tetrafluormethan;

- Trifluormethan;

- Stickstoff; und/oder

- Argon

verwendet wird.

15 6. Verfahren zum Herstellen einer Schicht-Anordnung nach Anspruch 4 oder 5,

bei dem die Ätzrate eingestellt wird, indem bei dem Ätzmittel die Konzentration von

- Sauerstoff;

- Wasserstoff; und/oder

- Kohlenmonoxid

eingestellt wird.

7. Verfahren zum Herstellen einer Schicht-Anordnung nach 25 einem der Ansprüche 1 bis 6,

bei dem die Opferschicht mit einer wesentlich geringeren Dicke vorgesehen wird als die elektrisch isolierende Schicht.

8. Verfahren zum Herstellen einer Schicht-Anordnung nach 30 einem der Ansprüche 1 bis 7,

bei dem zwischen der elektrisch leitfähigen Schicht und der Struktur aus elektrisch leitfähigem Material eine Liner-Schicht gebildet wird.

35 9. Verfahren zum Herstellen einer Schicht-Anordnung nach Anspruch 8,

bei dem die Liner-Schicht nach dem Freilegen der

Oberflächenbereiche der strukturierten elektrisch leitfähigen Schicht gebildet wird.

10. Verfahren zum Herstellen einer Schicht-Anordnung nach

5 einem der Ansprüche 1 bis 9,

bei dem das Strukturieren der elektrisch leitfähigen Schicht und/oder das Strukturieren der elektrisch isolierenden Schicht unter Verwendung eines Lithographie- und eines Ätz-Verfahrens durchgeführt wird.

10

11. Verfahren zum Herstellen einer Schicht-Anordnung nach

einem der Ansprüche 1 bis 10,

bei dem die elektrisch leitfähige Schicht und/oder die

Opferschicht unter Verwendung eines konformen

15 Abscheideverfahrens gebildet werden.

12. Verfahren zum Herstellen einer Schicht-Anordnung nach

einem der Ansprüche 1 bis 11,

bei dem die Schicht-Anordnung als integrierter Schaltkreis

20 gebildet wird.

13. Verfahren zum Herstellen einer Schicht-Anordnung nach

einem der Ansprüche 1 bis 12,

bei dem

25 • die elektrisch leitfähige Schicht zum Bilden von Leiterbahnen strukturiert wird; und

• mittels der Struktur aus elektrisch leitfähigem Material Vias gebildet werden.

30 14. Verfahren zum Herstellen einer Schicht-Anordnung nach

einem der Ansprüche 1 bis 13,

bei dem die elektrisch leitfähige Schicht und/oder die

Struktur aus elektrisch leitfähigem Material aus

• Aluminium; und/oder

35 • Wolfram

gebildet wird/werden.

15. Verfahren zum Herstellen einer Schicht-Anordnung nach einem der Ansprüche 1 bis 14,

bei dem die Opferschicht aus

• Siliziumnitrid; und/oder

5 • Siliziumoxinitrid

gebildet wird.

16. Verfahren zum Herstellen einer Schicht-Anordnung nach einem der Ansprüche 1 bis 15,

10 bei dem die elektrisch isolierende Schicht aus Siliziumoxid gebildet wird.

17. Verfahren zum Herstellen einer Schicht-Anordnung nach einem der Ansprüche 8 bis 16,

15 bei dem die Liner-Schicht aus Titannitrid gebildet wird.

## Stand der Technik

FIG 1A

FIG 1B

FIG 1C

## Stand der Technik

FIG 2A

FIG 2B

FIG 2C

Stand der Technik

FIG 2D

FIG 2E

FIG 2F

Stand der Technik

FIG 2G

FIG 2H

Stand der Technik

FIG 2I

280

241

FIG 2J

285

241

FIG 2K

290

241

FIG 3A

FIG 3B

FIG 3C

FIG 3D

FIG 3E

FIG 3F

FIG 3G

FIG 3H

FIG 4A

FIG 4B

FIG 4C

FIG 4D

FIG 4E

FIG 4F

FIG 4G

FIG 4H

FIG 4I

FIG 4J

FIG 4K

FIG 4L

FIG 5A

FIG 5B

FIG 5C

FIG 6A

FIG 6B

FIG 7A

FIG 7B

FIG 7C

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/DE2005/001067A. CLASSIFICATION OF SUBJECT MATTER

IPC 7 H01L21/768

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC 7 H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages                                                | Relevant to claim No. |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X          | DE 101 40 468 A1 (INFINEON TECHNOLOGIES AG) 13 March 2003 (2003-03-13)<br>cited in the application<br>the whole document<br>----- | 1-17                  |

| X          | US 5 451 543 A (WOO ET AL) 19 September 1995 (1995-09-19)<br>cited in the application<br>the whole document<br>-----              | 1-4, 7,<br>10-16      |

| X          | US 5 920 793 A (MIZUSHIMA ET AL) 6 July 1999 (1999-07-06)<br>the whole document<br>-----                                          | 1-4, 6, 7,<br>10-16   |

| A          | US 2003/201121 A1 (JENG PEI-REN) 30 October 2003 (2003-10-30)<br>the whole document<br>-----                                      | 1-17                  |

|            |                                                                                                                                   | -/-                   |

Further documents are listed in the continuation of box C. Patent family members are listed in annex.

## ° Special categories of cited documents :

- °A° document defining the general state of the art which is not considered to be of particular relevance

- °E° earlier document but published on or after the international filing date

- °L° document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- °O° document referring to an oral disclosure, use, exhibition or other means

- °P° document published prior to the international filing date but later than the priority date claimed

- °T° later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- °X° document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- °Y° document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- °&° document member of the same patent family

Date of the actual completion of the international search

26 September 2005

Date of mailing of the international search report

05/10/2005

Name and mailing address of the ISA

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl

Fax: (+31-70) 340-3016

Authorized officer

Ploner, G

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/DE2005/001067

## C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages        | Relevant to claim No. |

|------------|-------------------------------------------------------------------------------------------|-----------------------|

| A          | US 5 700 737 A (YU ET AL)<br>23 December 1997 (1997-12-23)<br>the whole document<br>----- | 1-17                  |

| A          | US 6 015 751 A (LIU ET AL)<br>18 January 2000 (2000-01-18)<br>the whole document<br>----- | 1-17                  |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International Application No

PCT/DE2005/001067

| Patent document cited in search report | Publication date | Patent family member(s) | Publication date |

|----------------------------------------|------------------|-------------------------|------------------|

| DE 10140468                            | A1 13-03-2003    | US 2003036227 A1        | 20-02-2003       |

| US 5451543                             | A 19-09-1995     | NONE                    |                  |

| US 5920793                             | A 06-07-1999     | JP 9129732 A            | 16-05-1997       |

| US 2003201121                          | A1 30-10-2003    | NONE                    |                  |

| US 5700737                             | A 23-12-1997     | NONE                    |                  |

| US 6015751                             | A 18-01-2000     | NONE                    |                  |

# INTERNATIONALER RECHERCHENBERICHT

Internationales Aktenzeichen

PCT/DE2005/001067

A. KLASIFIZIERUNG DES ANMELDUNGSGEGENSTANDES

IPK 7 H01L21/768

Nach der Internationalen Patentklassifikation (IPK) oder nach der nationalen Klassifikation und der IPK

B. RECHERCHIERTE GEBIETE

Recherchierte Mindestprüfstoff (Klassifikationssystem und Klassifikationssymbole)

IPK 7 H01L

Recherchierte aber nicht zum Mindestprüfstoff gehörende Veröffentlichungen, soweit diese unter die recherchierten Gebiete fallen

Während der internationalen Recherche konsultierte elektronische Datenbank (Name der Datenbank und evtl. verwendete Suchbegriffe)

EPO-Internal, WPI Data

C. ALS WESENTLICH ANGESEHENE UNTERLAGEN

| Kategorie* | Bezeichnung der Veröffentlichung, soweit erforderlich unter Angabe der in Betracht kommenden Teile                                | Betr. Anspruch Nr.  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------|

| X          | DE 101 40 468 A1 (INFINEON TECHNOLOGIES AG) 13. März 2003 (2003-03-13)<br>in der Anmeldung erwähnt<br>das ganze Dokument<br>----- | 1-17                |

| X          | US 5 451 543 A (WOO ET AL) 19. September 1995 (1995-09-19)<br>in der Anmeldung erwähnt<br>das ganze Dokument<br>-----             | 1-4, 7,<br>10-16    |

| X          | US 5 920 793 A (MIZUSHIMA ET AL) 6. Juli 1999 (1999-07-06)<br>das ganze Dokument<br>-----                                         | 1-4, 6, 7,<br>10-16 |

| A          | US 2003/201121 A1 (JENG PEI-REN) 30. Oktober 2003 (2003-10-30)<br>das ganze Dokument<br>-----<br>-/-                              | 1-17                |

Weitere Veröffentlichungen sind der Fortsetzung von Feld C zu entnehmen

Siehe Anhang Patentfamilie

\* Besondere Kategorien von angegebenen Veröffentlichungen :

\*A\* Veröffentlichung, die den allgemeinen Stand der Technik definiert, aber nicht als besonders bedeutsam anzusehen ist

\*E\* älteres Dokument, das jedoch erst am oder nach dem internationalen Anmeldedatum veröffentlicht worden ist

\*L\* Veröffentlichung, die geeignet ist, einen Prioritätsanspruch zweifelhaft erscheinen zu lassen, oder durch die das Veröffentlichungsdatum einer anderen im Recherchenbericht genannten Veröffentlichung belegt werden soll oder die aus einem anderen besonderen Grund angegeben ist (wie ausgeführt)

\*O\* Veröffentlichung, die sich auf eine mündliche Offenbarung, eine Benutzung, eine Ausstellung oder andere Maßnahmen bezieht

\*P\* Veröffentlichung, die vor dem internationalen Anmeldedatum, aber nach dem beanspruchten Prioritätsdatum veröffentlicht worden ist

\*T\* Spätere Veröffentlichung, die nach dem internationalen Anmeldedatum oder dem Prioritätsdatum veröffentlicht worden ist und mit der Anmeldung nicht kollidiert, sondern nur zum Verständnis des der Erfindung zugrundeliegenden Prinzips oder der ihr zugrundeliegenden Theorie angegeben ist

\*X\* Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung kann allein aufgrund dieser Veröffentlichung nicht als neu oder auf erforderlicher Tätigkeit beruhend betrachtet werden

\*Y\* Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung kann nicht als auf erforderlicher Tätigkeit beruhend betrachtet werden, wenn die Veröffentlichung mit einer oder mehreren anderen Veröffentlichungen dieser Kategorie in Verbindung gebracht wird und diese Verbindung für einen Fachmann nahelegend ist

\*&\* Veröffentlichung, die Mitglied derselben Patentfamilie ist

Datum des Abschlusses der internationalen Recherche

Absendedatum des internationalen Recherchenberichts

26. September 2005

05/10/2005

Name und Postanschrift der Internationalen Recherchenbehörde

Europäisches Patentamt, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

Fax: (+31-70) 340-3016

Bevollmächtigter Bediensteter

Ploner, G

## INTERNATIONALER RECHERCHENBERICHT

Internationales Aktenzeichen

PCT/DE2005/001067

## C.(Fortsetzung) ALS WESENTLICH ANGESEHENE UNTERLAGEN

| Kategorie° | Bezeichnung der Veröffentlichung, soweit erforderlich unter Angabe der in Betracht kommenden Teile | Betr. Anspruch Nr. |

|------------|----------------------------------------------------------------------------------------------------|--------------------|

| A          | US 5 700 737 A (YU ET AL)<br>23. Dezember 1997 (1997-12-23)<br>das ganze Dokument<br>-----         | 1-17               |

| A          | US 6 015 751 A (LIU ET AL)<br>18. Januar 2000 (2000-01-18)<br>das ganze Dokument<br>-----          | 1-17               |

**INTERNATIONALER RECHERCHENBERICHT**

Angaben zu Veröffentlichungen, die zur selben Patentfamilie gehören

Internationales Aktenzeichen

PCT/DE2005/001067

| Im Recherchenbericht angeführtes Patentdokument |    | Datum der Veröffentlichung |    | Mitglied(er) der Patentfamilie |    | Datum der Veröffentlichung |

|-------------------------------------------------|----|----------------------------|----|--------------------------------|----|----------------------------|

| DE 10140468                                     | A1 | 13-03-2003                 | US | 2003036227                     | A1 | 20-02-2003                 |

| US 5451543                                      | A  | 19-09-1995                 |    | KEINE                          |    |                            |

| US 5920793                                      | A  | 06-07-1999                 | JP | 9129732                        | A  | 16-05-1997                 |

| US 2003201121                                   | A1 | 30-10-2003                 |    | KEINE                          |    |                            |

| US 5700737                                      | A  | 23-12-1997                 |    | KEINE                          |    |                            |

| US 6015751                                      | A  | 18-01-2000                 |    | KEINE                          |    |                            |