(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3848374号

(P3848374)

(45) 発行日 平成18年11月22日(2006.11.22)

(24) 登録日 平成18年9月1日(2006.9.1)

(51) Int.C1.

F 1

|                      |                  |               |         |

|----------------------|------------------|---------------|---------|

| <b>G 1 1 C 16/02</b> | <b>(2006.01)</b> | G 1 1 C 17/00 | 6 1 2 B |

| <b>G 1 1 C 16/06</b> | <b>(2006.01)</b> | G 1 1 C 17/00 | 6 1 2 E |

|                      |                  | G 1 1 C 17/00 | 6 3 5   |

請求項の数 20 (全 18 頁)

|               |                        |

|---------------|------------------------|

| (21) 出願番号     | 特願平9-542260            |

| (86) (22) 出願日 | 平成8年5月22日(1996.5.22)   |

| (65) 公表番号     | 特表平11-509955           |

| (43) 公表日      | 平成11年8月31日(1999.8.31)  |

| (86) 国際出願番号   | PCT/US1996/007490      |

| (87) 国際公開番号   | W01997/044791          |

| (87) 国際公開日    | 平成9年11月27日(1997.11.27) |

| 審査請求日         | 平成15年5月7日(2003.5.7)    |

|           |                                                            |

|-----------|------------------------------------------------------------|

| (73) 特許権者 | マクロニクス インターナショナル カンパニー リミテッド<br>台湾 シン チュ クリエイション ロード サード 3 |

| (74) 代理人  | 弁理士 中村 稔                                                   |

| (74) 代理人  | 弁理士 大塚 文昭                                                  |

| (74) 代理人  | 弁理士 宍戸 嘉一                                                  |

| (74) 代理人  | 弁理士 竹内 英人                                                  |

| (74) 代理人  | 弁理士 今城 俊夫                                                  |

最終頁に続く

(54) 【発明の名称】フローティングゲートメモリの集積回路

## (57) 【特許請求の範囲】

## 【請求項 1】

フラッシュメモリの集積回路であって、

複数の行と列に配列されたフラッシュメモリセルのセットを有し、前記セルは、セルが制御ゲート端子に与えられた読み取り電位に応答して導通しない高いスレッショルド状態、及び前記制御ゲート端子に与えられた読み取り電位に応答して導通する低いスレッショルド状態を有し、

前記セットにおけるセルのそれぞれの列のドレイン端子に結合された複数のドレインラインと、

前記セットにおけるセルのそれぞれの列のソース端子に結合されたソースラインと、

前記複数のドレインライン、ソースライン及びワードラインに結合され、高いスレッショルド状態における前記セットのセルを並列に低いスレッショルド状態にセットするための制御回路と、

を備え、

前記制御回路は、電源回路を含み、トンネリングによって、セットにおけるセルのスレッショルドを低下するために、第1の電圧シーケンスを供給し、前記第1の電圧シーケンスは、負の電位を前記複数のワードラインに与え、第1の正の電位を前記複数のソースラインに与え、その後前記セルのスレッショルドをテストし、もし、全てのセルが前記低いスレッショルド状態になら、もし、前記第1の電圧シーケンスが試行した回数M(ここで、Mは1に等しいか、それより大きい)が再試行の限界に等しくないなら、前記第1の電圧

10

20

シーケンスを再試行し、全ての前記セルが前記低いスレッショルド状態になるまでテストし、且つ、

もし、前記第1の電圧シーケンスの再試行の回数Mの後、前記セルのいずれもが前記低いスレッショルド状態にないならば、トンネリングによって、セットにおける前記セルのスレッショルドを低下するために、第2の電圧シーケンスを供給し、前記第2の電圧シーケンスは、負の電位を前記複数のワードラインに与え、第2の正の電位を前記複数のソースラインに与え、その後、前記セルのスレッショルドをテストし、もし、全てのセルが前記低いスレッショルド状態にないならば、前記第2の電圧シーケンスを再試行し、全てのセルが前記低いスレッショルド状態になるまで、或いは少なくとも再試行の回数が実行されるまでテストし、

前記第1と第2の電圧シーケンスは、前記トンネリングの電流に加えて、バンド・ツー・バンドのトンネリング電流を誘起し、前記バンド・ツー・バンドのトンネリング電流は、前記第1或いは第2の電圧シーケンスを受信するセルのスレッショルドに逆関連されたターンオン・スレッショルド・ソース電位によって特徴づけられ、前記第1の正の電位は、前記高いスレッショルド状態にある高いスレッショルドセルに対するターンオン・スレッショルド・ソース電位に近いか、それ以上のレベルに、及び前記高いスレッショルド状態にある低いスレッショルドセルに対する前記ターンオン・スレッショルド・ソース電位より小さいレベルにセットされ、且つ、前記第2の正の電位は、前記高いスレッショルド状態にある低いスレッショルドセルに対する前記ターンオン・スレッショルド・ソース電位に近いか、それ以上のレベルにセットされ、その結果、バンド・ツー・バンドのトンネリング電流は、前記高いスレッショルド状態にある高いスレッショルドセルの存在で、前記第1の電圧シーケンスにおいて制御され、且つ、前記高いスレッショルド状態にある前記高いスレッショルドセルは、前記第2の電圧シーケンス前のスレッショルドにおいてピーク電流消費を制限するように低下されることを特徴とするフラッシュメモリの集積回路。

#### 【請求項2】

前記第1の正の電位は5ボルトより小さく、前記第2の電位は7ボルトより小さいことを特徴とする請求項1に記載のフラッシュメモリの集積回路。

#### 【請求項3】

前記第1の電圧シーケンスにおける前記負の電位は、-6ボルトより小さいことを特徴とする請求項2に記載のフラッシュメモリの集積回路。

#### 【請求項4】

前記第1の電圧シーケンス及び第2の電圧シーケンスにおける前記負の電位は、-6ボルトより小さいことを特徴とする請求項2に記載のフラッシュメモリの集積回路。

#### 【請求項5】

前記第1の正の電位は4ボルトと5ボルトの間にあり、前記第2の正の電位は5ボルトと6ボルトの間にあることを特徴とする請求項1に記載のフラッシュメモリの集積回路。

#### 【請求項6】

前記第1の電圧シーケンス及び第2の電圧シーケンスにおける前記負の電位は、-7ボルトより小さいことを特徴とする請求項5に記載のフラッシュメモリの集積回路。

#### 【請求項7】

前記セルのセットは、250,000より多くのセルを有することを特徴とする請求項1に記載のフラッシュメモリの集積回路。

#### 【請求項8】

前記セルのセットは、4,000,000より多くのセルを有することを特徴とする請求項1に記載のフラッシュメモリの集積回路。

#### 【請求項9】

前記制御回路は、前記複数のドレンラインを前記第1と第2の電圧シーケンスにおけるオープン回路状態にセットすることを特徴とする請求項1に記載のフラッシュメモリの集積回路。

#### 【請求項10】

10

20

30

40

50

入力信号に応答して消去されるべきアレイのセクターを示す複数のセクターフラッグと、前記複数のセクターフラッグ、及び複数のセクターにおける前記複数のドレインライン、ソースライン及びワードラインに結合された第2の制御回路と、を備え、

前記第1と第2の電圧シーケンスは、スレッショルド電圧の消去ベリファイ電圧より低く低下されたスレッショルドを有する幾つかのセルを生じ、前記複数のソースラインと前記複数のドレインラインを横切って修復時間期間の間、前記複数のセクターフラッグによって示された選択されたセクターに修復パルスを供給するために電源回路を有し、一方、前記複数のワードライン上の電圧を消去ベリファイ電圧より下のレベルにセットすることを特徴とする請求項1に記載のフラッシュメモリの集積回路。

**【請求項11】**

複数の行と列に配列されたフラッシュメモリセルのアレイを有し、前記セルは、セルがセルの制御ゲート端子に与えられた読み取り電位に応答して導通しない高いスレッショルド状態、及びセルが前記制御ゲート端子に与えられた読み取り電位に応答して導通する低いスレッショルド状態を有し、前記アレイは、セルのそれぞれの列のドレイン端子に結合された複数のドレインライン、セルのそれぞれの列のソース端子に結合された複数のソースライン、セルのそれぞれの列のソース端子に結合された複数のワードラインを有するフラッシュメモリの集積回路において、前記高いスレッショルド状態にあるアレイにおけるセルを並列に前記低いスレッショルド状態にセットする方法であって、

トンネリングによって、前記アレイにおけるセルのスレッショルドを低下するために第1の電圧シーケンスを供給し、前記第1の電圧シーケンスは、負の電圧を前記複数のワードラインに与え、及び第1の正の電位を前記複数のソースラインに与え、その後、前記セルのスレッショルドをテストし、もし、全てのセルが前記低いスレッショルド状態にないならば、且つ、もし、前記第1の電圧シーケンスが試行した回数M（ここで、Mは1に等しいか、それより大きい）が再試行の限界に等しくないなら、前記第1の電圧シーケンスを再試行し、全てのセルが前記低いスレッショルド状態になるまでテストし、

もし、前記第1の電圧シーケンスの再試行の回数Mの後、前記セルのいずれもが前記低いスレッショルド状態にないならば、トンネリングによって、アレイにおける前記セルのスレッショルドを低下するために、第2の電圧シーケンスを供給し、前記第2の電圧シーケンスは、負の電位を前記複数のワードラインに与え、第2の正の電位を前記複数のソースラインに与え、その後前記セルのスレッショルドをテストし、もし、全てのセルが前記低いスレッショルド状態にないならば、前記第2の電圧シーケンスを再試行し、全てのセルが前記低いスレッショルド状態になるまで、或いは少なくとも再試行の回数が実行されるまでテストし、

前記第1と第2の電圧シーケンスは、前記トンネリングの電流に加えて、バンド・ツー・バンドのトンネリング電流を誘起し、前記バンド・ツー・バンドのトンネリング電流は、前記第1或いは第2の電圧シーケンスを受信するセルのスレッショルドに逆関連されたターンオン・スレッショルド・ソース電位によって特徴づけられ、前記第1の正の電位は、前記高いスレッショルド状態にある高いスレッショルドセルに対して前記ターンオン・スレッショルド・ソース電位に近いか、それ以上のレベルに、且つ、前記高いスレッショルド状態にある低いスレッショルドセルに対するターンオン・スレッショルド・ソース電位より小さいレベルにセットされ、且つ、前記第2の正の電位は、前記高いスレッショルド状態にある低いスレッショルドセルに対する前記ターンオン・スレッショルド・ソース電位に近いか、それ以上のレベルにセットされ、その結果、バンド・ツー・バンドのトンネリング電流は、前記高いスレッショルド状態にある高いスレッショルドセルの存在で、前記第1の電圧シーケンスにおいて制御され、且つ、前記高いスレッショルド状態にある前記高いスレッショルドセルは、前記第2の電圧シーケンス前のスレッショルドにおいてピーク電流消費を制限するように低下されることを特徴とする方法。

**【請求項12】**

前記第1の正の電位は5ボルトより小さく、前記第2の電気は7ボルトより小さいことを特徴とする請求項11に記載の方法。

**【請求項 1 3】**

前記第 1 の電圧シーケンスにおける前記負の電位は、 - 6 ボルトより小さいことを特徴とする請求項 1 2 に記載の方法。

**【請求項 1 4】**

前記第 1 の電圧シーケンス及び第 2 の電圧シーケンスにおける前記負の電位は、 - 6 ボルトより小さいことを特徴とする請求項 1 2 に記載の方法。

**【請求項 1 5】**

前記第 1 の正の電位は 4 ボルトと 5 ボルトの間にあり、前記第 2 の正の電位は 5 ボルトと 6 ボルトの間にあることを特徴とする請求項 1 1 に記載の方法。

**【請求項 1 6】**

10

前記第 1 の電圧シーケンス及び第 2 の電圧シーケンスにおける前記負の電位は、 - 7 ボルトより小さいことを特徴とする請求項 1 5 に記載の方法。

**【請求項 1 7】**

前記セルのアレイは、 250,000 より多くのセルを有することを特徴とする請求項 1 1 に記載の方法。

**【請求項 1 8】**

前記セルのセットは、 4,000,000 より多くのセルを有することを特徴とする請求項 1 1 に記載の方法。

**【請求項 1 9】**

20

前記第 1 と第 2 の電圧シーケンスにおいて前記複数のドレインラインをオープン回路状態にセットすることを特徴とする請求項 1 1 に記載の方法。

**【請求項 2 0】**

前記第 1 と第 2 の電圧シーケンスは、スレッショルド電圧の消去ベリファイ電圧より低く低下されたスレッショルドを有する幾つかのセルを生じ、前記複数のソースラインと前記複数のドレインラインを横切って修復時間期間の間、修復パルスをアレイに供給し、一方、前記複数のワードライン上の電圧を消去ベリファイ電圧より下のレベルにセットすることを特徴とする請求項 1 1 に記載の方法。

**【発明の詳細な説明】****発明の背景****発明の技術分野**

30

本発明は、例えばフラッシュメモリのようなフローティングゲートメモリに関し、特に減少したピーク電流消費を伴うフローティングゲートメモリセルのアレイを消去するための方法および回路に関する。

**関連技術の説明**

集積回路技術に基づく不揮発性メモリは、広い分野で用いられている。不揮発性メモリの幾つかのポピュラーなものは、電気的に消去することができます、プログラム可能なフローティングゲートメモリのトランジスタのアレイに基づいている。

一つの共通アプローチにおけるフローティングゲートメモリトランジスタのメモリアレイをプログラムする作用は、負電荷がフローティングゲートに蓄積し、メモリセルのターンオンスレッショルドが高いスレッショルド状態に増加するようにする、アドレスされたセルのフローティングゲートを電子で注入することを含む。従って、プログラムされたとき、セルはターンオンせず、従って、制御ゲートに与えられた読み取り電位でアドレスされたとき、それらは非導通のままである。負に帯電されたフローティングゲートを有するセルを消去する作用は、スレッショルドを低下するようにフローティングゲートから電子を除去することを含む。読み取り電位で制御ゲートヘアドレスされたとき、セルは低いスレッショルドで導通状態にターンオンするであろう。反対極性のアレイに対して、プログラムすることは、アドレスされたセルのフローティングゲートから電子を選択的に除去することを含む。

フラッシュメモリデバイスにおける消去プロセスの間、消去電位が並列に、全体のアレイか、或いはアレイの大部分に与えられる。従って、消去手順中に用いられた電源は、並列

40

50

に大量のセルにおける消去プロセスのために必要な電流を扱うことができなければならぬ。消去プロセスにおける主な電流は、電子がフローティングゲートからフローティングゲートメモリセルのソースへ駆動される、所謂フォウラー - ノードハイム (Fowler-Nordheim:F-N) のトンネル電流である。消去手順中の他の電流源は、バンド - ツー - バンドのトンネリング(band-to-band tunneling)として知られている。バンド - ツー - バンドのトンネリングは基板へ電流を生じ、またフローティングゲートの方向に注入された望ましくないホールの形態で電流を生じる。これらの望ましくないホールの大部分は、シリコンの表面から約 15 - 30 離れた領域にとどまる。何故なら、セルのスレッショルド電圧は、フローティングゲート(例えば、電子)における電荷、及びフローティングゲートとシリコン表面(例えば、トラップされたホール)間の領域における電荷の合計に基づかれ、そしてこれらのホールは容易にデトラップ(de-trap)し、電荷の合計を変化し、セルの信頼性が減少される。例えば、Ajika他による "A Five Volts Only 16M Bit Flash EEPROM Cell With a Simple Stacked Gate Structure", IEDM 1990, pages 115-118、及びWann他による "Suppressing Flash EEPROM Erase Leakage with Negative Gate Bias and LDD Erase Junction", Symposium on VLSI Technology 1993, pages 81-82を参照されたい。Wann他に記載されているように、消去プロセス中の負のゲート電位の使用によって、低い電源電圧の使用を可能にする。低い電源電圧はアバランシェ破壊を抑制し、セルの耐久性と信頼性を増す。しかし、望ましくないバンド - ツー - バンドのトンネル電流は、Wann他における与えられた消去速度に対して減少されない。Wann他によると、バンド - ツウ - バンドのトンネリングを更に抑制するためには、消去速度が犠牲にされる。

バンド - ツー - バンドのトンネル電流は、消去されるセルのスレッショルドに関連している。従って、高いスレッショルド状態が全て同じスレッショルドを有しないので、問題はフラッシュメモリデバイスに起きる。従って、高いスレッショルド状態の多くのセルは、他のものより高いスレッショルドレベルを有するであろう。例えば、あるセルは 8 ボルトのスレッショルドを有するが、一方他のものは 6 ボルトのスレッショルドを有する。高いスレッショルドのセル(例えば、8 ボルトに近い)に生じたバンド - ツー - バンドのトンネル電流は、低いスレッショルドのセル(例えば、6 ボルトに近い)におけるよりも大きい。従って、高いスレッショルドのセルは、消去プロセス中に著しいバンド - ツー - バンドのトンネル電流を形成する。フラッシュ消去手順は、並列に全アレイのセクタを消去することを含むので、著しいピーク電流が生じ得る。これは、電源のコストを増加し、フラッシュメモリデバイス用に用いられる利用可能な電源の範囲を制限する。

従来のシステムは、高電流でのバイアスを減少する電流リミターとして、抵抗が電源とソース端子間に直列に配置されて、具現化され、それによりバンド - ツー - バンドのトンネル電流を減少する。しかし、この手法は初期の消去パルス中にピーク電流をうまく制御できなかった。

従って、消去プロセス中に発生されるピーク電流を制御する一方で、フラッシュメモリデバイスの著しい消去速度を維持することができる技術を提供することが必要である。

#### 発明の概要

本発明は、プロセス中に生じる予期されたバンド - ツー - バンドのトンネル電流にしたがって、消去中にソース電位の選択によるフラッシュメモリデバイスのための、消去プロセス中に生じるピーク電流に実質的な減少を与える。プロセスの始めの間に、低いソース電位が選択され、そしてそれはバンド - ツー - バンドのトンネル電流を抑制する一方で、著しい F - N トンネル電流を生じるのに充分高く、そして消去プロセスの第 2 の部分の間、デバイスとともに用いられる電源のピーク電流要求を越えることなく、アレイの消去を確実にする高いソース電位が用いられる。

従って、本発明は行と列に配列されたフローティングゲートのメモリセルのセットに基づいたフローティングゲートメモリの集積回路として特徴づけられる。これらのセルは、セルがセルの制御ゲート端子に与えられた読み取り電位に応答して導通しない高いスレッショルド状態、及びセルが制御ゲート端子に与えられた読み取り電位に応答して導通する低いスレッショルド状態を有する。高いスレッショルド状態にあるセルは、読み取り電位よ

り上のスレッショルドの分布を有する。例えば、5 ボルトの読み取り電位の場合、高いスレッショルド状態にあるセルのスレッショルドの範囲は約 6 ボルトから約 8 ボルトまで変化することができる。フローティングゲートのメモリセルのセットは、そのセットにおけるセルの列のドレイン端子に結合された複数のドレインライン、そのセットにおけるそれぞれの列のソース端子に結合された複数のソースライン、およびセルのそれぞれの行の制御ゲート端子に結合された複数のワードラインを有する。制御回路はそれぞれ複数のドレインライン、ソースライン及びワードラインに結合され、高いスレッショルド状態にあるセルのセットにおけるセルを低いスレッショルド状態に並列にセットする。制御回路は、第 1 の電圧シーケンスを供給する電源回路を含んでいて、Fowler-Nordheim のトンネリングによってセットにおけるセルのスレッショルドを低くする。第 1 の電圧シーケンスは負の電位を複数のワードラインへ与え、第 1 の正の電位を複数のソースラインへ与えることを含み、一方ドレインラインはオープン回路状態にある。これは、セルのスレッショルドを低くする。次に、セットにおけるセルのスレッショルドは、それらが首尾よく消去されたかどうかを決定するためにテストされる。もし、全てのセルが低いスレッショルド状態にないならば、第 1 の電圧シーケンスおよびテストは、全てのセルが低いスレッショルド状態になるまで再試行されるか、再試行の数 M が実行されるまで再試行される。第 1 の電圧シーケンスの数 M の再試行後に、セルの何れかが低いスレッショルド状態にないならば、電源回路は、Fowler-Nordheim のトンネリングによってセットにおけるセルのスレッショルドを低くするために第 2 の電圧シーケンスを供給する。第 2 の電圧シーケンスは負の電位を複数のワードラインへ与え、第 2 の正の電位を複数のソースラインへ与えること、およびその後セルのスレッショルドをテストすることを含む。もし、全てのセルが低いスレッショルド状態にないならば、第 2 の電圧シーケンスが、全てのセルが低いスレッショルド状態にあるか、再試行の最大数が実行されるまで再試行される。

10

上述のように、第 1 と第 2 の電圧シーケンスは Fowler-Nordheim のトンネル電流に加えてバンド - ツー - バンドのトンネル電流を誘起する。バンド - ツー - バンドのトンネル電流は電圧シーケンスを受けるセルのスレッショルドに逆に関係したターンオンスレッショルドソース電位によって特徴づけられる。即ちターンオンスレッショルドソース電位は、低いスレッショルドを有するセルに対してよりも高いスレッショルドを有するセルに対して低い。本発明によれば、第 1 の電圧シーケンスに用いられる第 1 の電位は、高いスレッショルド状態にある高いスレッショルドセルに対するターンオンスレッショルドソース電位近く或いはそれ以上であるが、高いスレッショルド状態にある低いスレッショルドセルに対するターンオンスレッショルドソース電位以下のレベルにセットされる。第 2 の電圧シーケンスに用いられる第 2 の正の電位は、高いスレッショルド状態にある低いクレッショルドセルに対するターンオンスレッショルドソース電位近く或いはそれ以上のレベルにセットされる。このようにして、バンド - ツー - バンドのトンネル電流は高いスレッショルドセルの存在において第 1 の電圧シーケンスで制御され、第 2 の電圧シーケンスが加えられる前に、高いスレッショルドセルのスレッショルドが低下される。これは消去プロセスの速度が平衡釣合って減少することなく、消去プロセスに用いられるピーク電流の消費を制限する。この技術は、セクター化されたアレイシステムにも適用され、そのシステムにおいて、並列に消去されるべきアレイのセクタは、セクタ消去フラッグによって識別される。この実施の形態において、セットされたセクタ消去フラッグを有するセクタのみが第 1 と第 2 の電圧シーケンスに従う。

20

更に、本発明は、消去されたセルに与えられる“ソフトプログラム”的修復パルス (repair pulse) を含むように拡張することができる。第 1 と第 2 の電圧シーケンスは低いスレッショルド状態に対するスレッショルド電圧の選択された制限以下に低下されたスレッショルドを有する幾つかのセルを生じる。この実施の形態において、電源回路は、セルのソースとドレインを横切って修復時間間隔の間選択されたセクタへ修復パルスを供給するが、一方、スレッショルド電圧の選択された制限以下に選択されたセルのワードライン上に電圧をセットする。この修復パルスは、消去されたセルのスレッショルドを正常化し、アレイの信頼性を向上するという効果を有する。

30

40

50

本発明の他の特徴によると、第1と第2の電圧シーケンスのために用いられる制御回路は、複数のドレインラインを第1と第2の電圧シーケンス中にオープン回路状態にセットする。本発明の他の特徴によると、第1と第2の電圧シーケンス中にワードラインに与えられた負の電位は、負の6ボルトより小さい、例えば約-7.8ボルトである。第1の電圧シーケンス中にソースに与えられた正の電位は、5ボルト以下、好ましくは4ボルトと5ボルトの間、例えば4.5ボルトである。第2の電圧シーケンス中に与えられた正の電位は、5ボルトと6ボルトの間、例えば5.5ボルトである。

本発明は、消去プロセス中に発生されたピーク電流を制御するために、上述のように第1と第2の電圧シーケンスを行うための方法に対しても特徴がある。

従って、本発明は、初期の消去間隔の間電荷の量は比較的高く、バンド-ツー-バンドのトンネル電流が高いので、消去プロセスの初期部分の間低いソースバイアスを与えることに基づかれる。電荷の量が初期の消去期間に減少された後、回路は、消去効率を改善するために、高いソースバイアスをフラッシュメモリに与える。従って、消去期間の間にロードする電流は、システムと共に用いられる電源に対してピーク電流の問題を生じない。本発明の他の特徴および利点は図面、詳細な説明および請求項を精査すれば、理解されるであろう。

#### 【図面の簡単な説明】

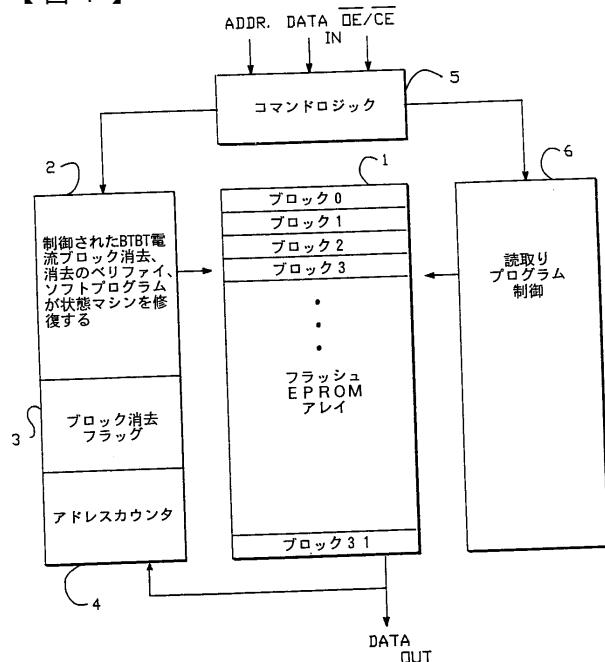

図1は、本発明によるフラッシュメモリの集積回路の概要を示すブロック図である。

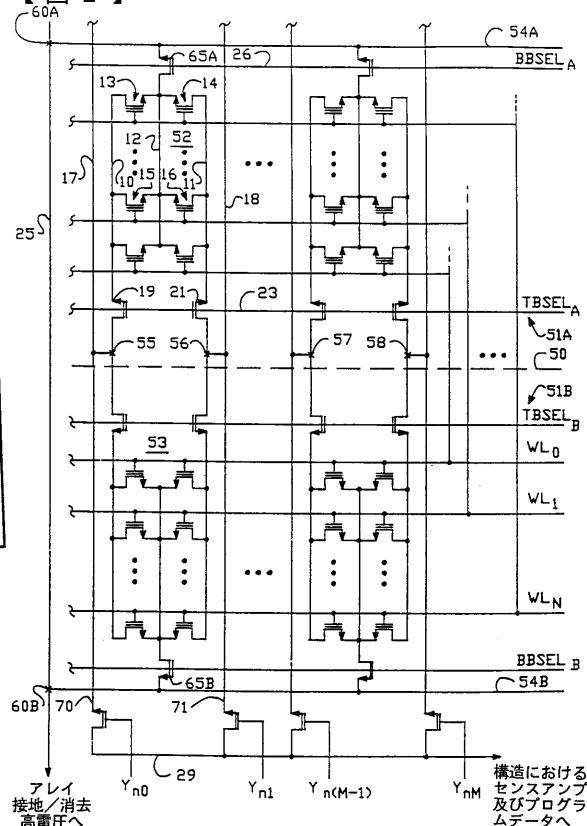

図2は、図1のフローティングゲートのメモリセルのための区分化されたアレイアーキテクチャを示す回路図である。

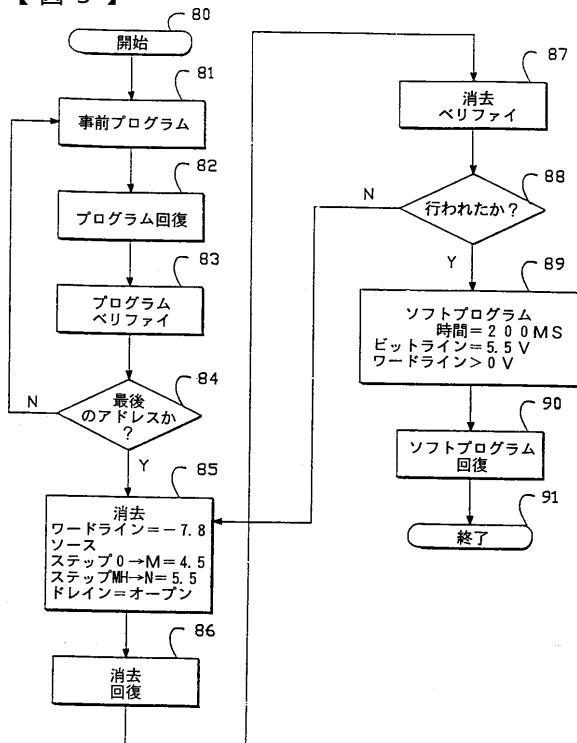

図3は、制御されたバンド-ツー-バンドのトンネル電流を有する、図1の状態マシンによって実行された概略フローチャートである。

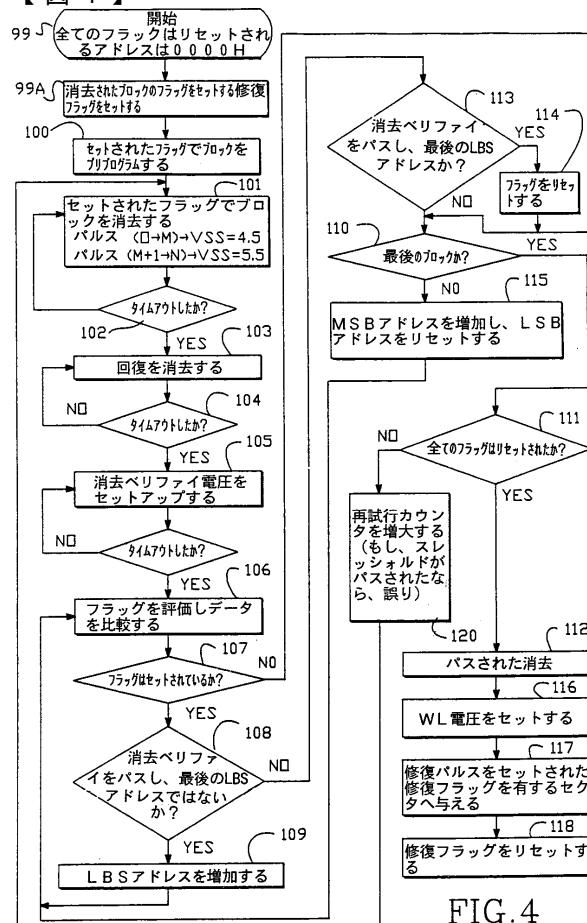

図4は、本発明のセクタ消去および修復プロセスを示すより詳細なフローチャートである。

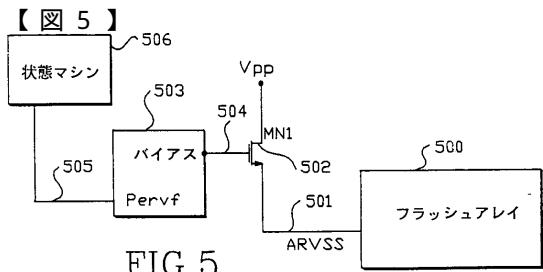

図5は、本発明による消去プロセスの間にソース電圧を制御するために用いられる回路を示す簡略化されたブロック図である。

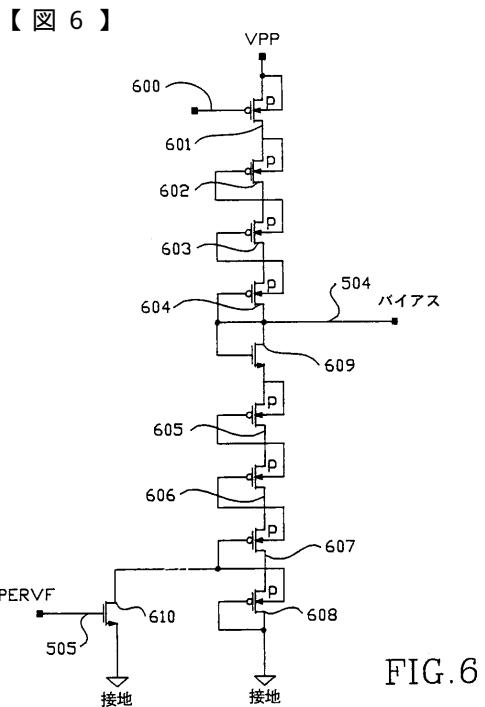

図6は、図5のBIAS信号を発生するために用いられる電圧分割器の回路図である。

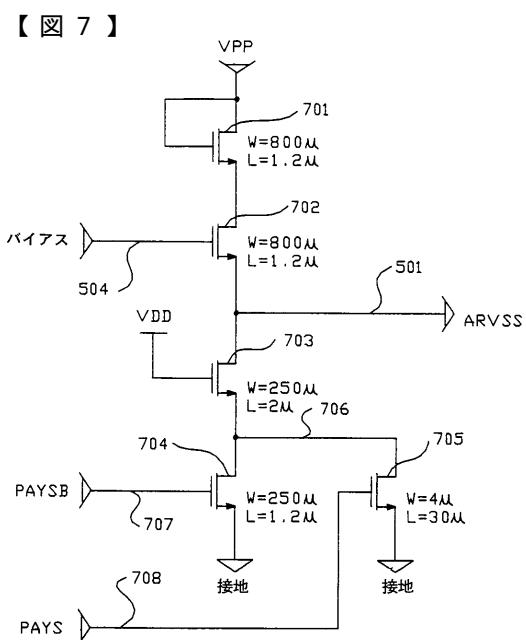

図7は、図5のシステムに用いられるソース電源回路の回路図である。

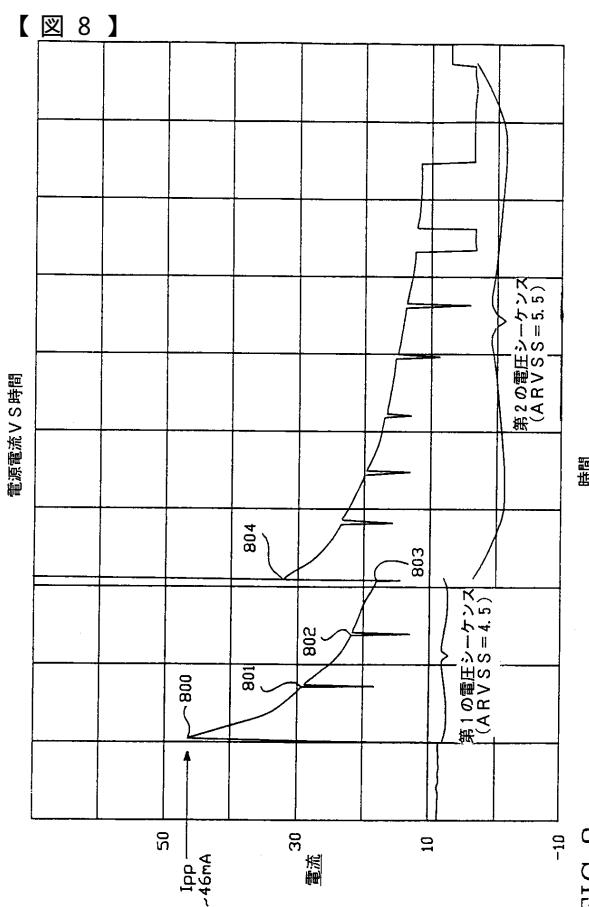

図8は、本発明によるピーク電流発生におけるセービングを示すグラフである。

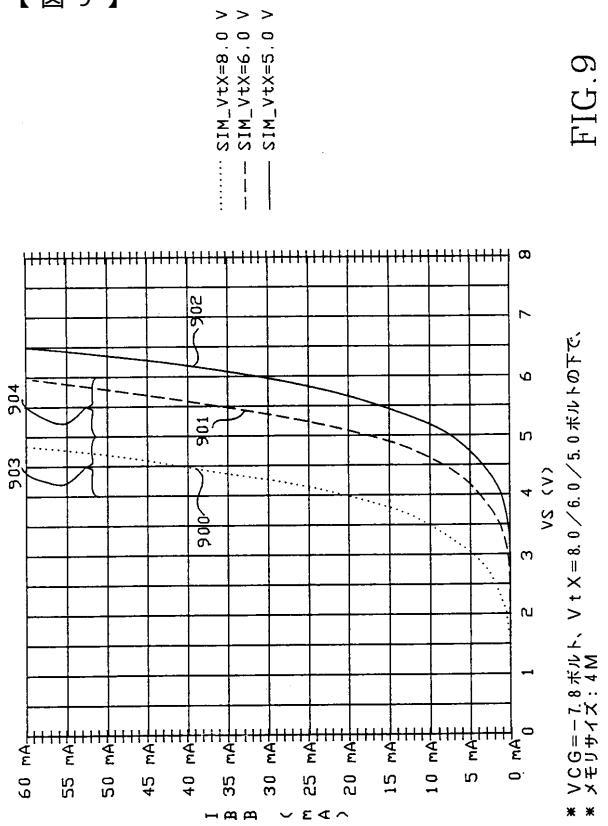

図9は、バンド-ツー-バンドのトンネル電流のターンオンソース電位を示すグラフである。

#### 発明の詳細な説明

本発明の好適な実施形態の詳細な説明は図面を参照してなされる。本発明による、ブロックに配列されたフローティングゲートのメモリセルの改善された消去シーケンスは、バンド-ツー-バンドのトンネル電流を制御することによって減少されたピーク電流を生じる。

図1は、本発明を組み込んだ4メガバイトのフローティングゲートメモリの集積回路の基本構造を示す。この回路は、複数のブロック（図面においては32ブロック）に分割されたメモリアレイ1を有する。メモリアレイのセグメント化が可能なアーキテクチャが本発明の消去シーケンスをセルブロックにそれぞれ適用することを可能にし、従って、ブロック毎の消去を可能にする。アレイアーキテクチャは、図2を参照して以下に詳細に記載される。

図1を参照すると、読み取りおよびプログラム制御回路6、およびブロック消去／消去のペリファイ／修復回路2がアレイ1に結合されている。ブロック消去／消去のペリファイ／修復回路2は消去フラッグ3に結合され、バンド-ツー-バンドのトンネル電流を制御するために回路を有する。メモリセル、ブロックまたは消去／消去のペリファイ／修復シーケンスのための全アレイを介してインクリメントするためのアドレスカウンター4が含まれる。

チップは、アドレス、データおよび出力イネーブル信号およびチップイネーブル信号のような他の制御ラインと結合されるコマンドロジック5を含む。このコマンドロジック5は

10

20

30

40

50

、読み取りとプログラム制御ロジック 6、およびブロック消去／消去のベリファイ／修復回路 2 に対して動作モードをセットするために入力を翻訳する。

コマンドロジック 5 は、セル、ブロックまたはアレイ消去のための本発明の追加のコマンドを有する、標準のフローティングゲートメモリの集積回路、例えばAdvanced Micro Devices, Inc. of Sunnyvale, Californiaによって製造されたAm28F020フラッシュメモリのチップにおいて行われるように具現化されることができる。コマンドロジック 5 によって発せられたコマンドに応答して、組み込まれた消去動作は、消去／消去のベリファイ／修復回路 2 における状態マシンによって実行される。ホスト C P U または別の方法で、ユーザーは、動作の好適なモードを示すためにアドレスおよびデータ信号をコマンドロジック 5 へ供給する。消去／消去のベリファイ／修復回路 2 によって実行されるモードは、アレイ 1 における全てのブロックが消去されるチップの消去モード、およびアレイ 1 における選択されたブロックが消去されるブロックの消去モードを含む。ユーザー入力に応答して、消去されるべきブロックは、チップに記憶されたブロックまたはセクター消去フラッグ 3 によって識別される。10

図 2 は、本発明が具現化され、ここに参照によって取り込まれた 1995 年 3 月 21 日に発行された Non-Volatile Memory Cell and Array Architecture の米国特許第 5,399,891 号のように、フローティングゲートのメモリ回路のドレイン - ソース - ドレイン形状におけるセグメント化が可能なアレイアーキテクチャの詳細を示す。他のアレイのアーキテクチャも同様に用いることができる。

回路は埋設された拡散導体によって具現化された第 1 のローカルビットライン 10 と第 2 のローカルビットライン 11 を含む。また、埋設された拡散によって具現化されたローカル仮想接地ライン 12 が含まれる。複数のフローティングゲートトランジスタはローカルビットライン 10, 11 およびローカル仮想接地ライン 12 に結合されたドレインとソースを有する。20

トランジスタ 13 の第 1 の列のドレインは第 1 のローカルビットライン 10 に結合され、トランジスタの第 2 の列のドレイン 14 は第 2 のローカルビットライン 11 に結合される。各ワードライン（例えば、W L<sub>1</sub>）が第 1 のローカルビットライン 10 におけるトランジスタ（例えば、トランジスタ 15）および第 2 のローカルビットライン 11 におけるトランジスタ（例えば、トランジスタ 16）のゲートに結合される場合、フローティングゲートトランジスタのゲートは、ワードライン W L<sub>0</sub> - W L<sub>N</sub> へ結合される。トランジスタ 15 と 16 は、共有されたソース拡散を有する 2 つのトランジスタセルと考えることができる。30

フローティングゲートをチャージする作用は、フローティングゲートのメモリセルのためのプログラムステップと呼ばれる。これはゲートとソース間の大きな正の電圧、例えば 1.2 ボルト、およびドレインとソース間の正の電圧、例えば 6 ボルトを確立することによって熱い電子の注入をとおしてバイトごとを基準にして達成される。

フローティングゲートをディスチャージする作用は、フローティングゲートのメモリセルのための消去ステップと呼ばれる。これはフローティングゲートとソース間（ソース消去）、或いはフローティングゲートと基板間（チャネル消去）の F - N (Fowler-Nordheim) トンネルメカニズムをとおして達成される。ソース消去は、正のバイアスをソースへ、例えば 7 ボルトより小さな電圧を印加することによって達成されるが、一方ゲートは負に、例えば - 6 ボルトより小さくバイアスされる。本発明によると、ソース電位は、以下に詳しく述べるように、第 1 の幾つかの消去試行の間特定の低い値（例えば、4.5 ボルト）および残りの消去試行の間、特定の高い値（例えば、5.5 ボルト）に設定される。40

セルの個々のブロックは選択された信号、即ち、上部のブロック選択信号 T B S E L<sub>A</sub> と T B S E L<sub>B</sub>、および下部のブロック選択信号 B B S E L<sub>A</sub> と B B S E L<sub>B</sub> によって制御される。

図 2 を参照すると、第 1 のグローバルビットライン 17 と第 2 のグローバルビットライン 18 は各ドレイン - ソース - ドレインのブロックと関連される。第 1 のグローバルビットライン 17 は、金属からの拡散コンタクト 55 をとおして上部のブロック選択トランジス50

タ 1 9 のソースに結合される。同様に、第 2 のグローバルビットライン 1 7 は、金属からの拡散コンタクト 5 6 をとおして上部のブロック選択トランジスタ 2 1 のソースに結合される。上部のブロック選択トランジスタ 1 9 , 2 1 のドレインは第 1 と第 2 のローカルビットライン 1 0 と 1 1 にそれぞれ結合される。従って、上部のブロックセクタートランジスタ 1 9 , 2 1 のゲートはライン 2 3 上の上部のブロック選択信号 T B S E L<sub>A</sub> によって制御される。

同様な方法で、下部のブロック選択トランジスタ 6 5 A のゲートは、ライン 2 6 を横切って下部のブロック選択信号 B B S E L<sub>A</sub> によって制御される。ローカル仮想接地ライン 1 2 は、下部のブロック選択トランジスタ 6 5 A を介して導体 5 4 A を横切って仮想接地端子に結合される。下部のブロック選択トランジスタ 6 5 A のドレインは、ローカル仮想接地ライン 1 2 に結合される。下部のブロック選択トランジスタ 6 5 A のソースは導体 5 4 A に結合される。このアーキテクチャにおいて、導体 5 4 A は、アレイを介して水平に移された位置でメタルから拡散へのコンタクト 6 0 A に伸びる埋設された拡散導体であり、コンタクトを垂直な金属仮想接地バス 2 5 に与える。

構造体におけるセンスアンプとプログラムデータに対して、データライン 2 9 は、それぞれの列選択トランジスタ 7 0 , 7 1 にアレイを介して垂直に伸びるグローバルビットライン 1 7 と 1 8 に結合される。従って、列選択トランジスタ 7 0 のソースはグローバルビットライン 1 7 に結合され、列選択トランジスタ 7 0 のゲートは列デコード信号 Y<sub>n0</sub> に結合され、そして列選択トランジスタ 7 0 のドレインはデータライン導体 2 9 に結合される。

図 1 に示されるように、フローティングゲートメモリセルのブロックは、大きな集積回路内の 2 つのサブアレイを示す図 2 に示された複数のサブアレイにセットされる。これらのサブアレイは点線 5 0 に沿って一般に分割され、ライン 5 0 より上のサブアレイ 5 1 A とライン 5 0 より下のサブアレイ 5 1 B を含む。セルの第 1 のグループ 5 2 は、与えられたビットライン対（例えば、1 7 , 1 8 ）に沿ってセルの第 2 グループ 5 3 と共にミラーメージに配列される。一つがビットライン対へ進むに従って、メモリのサブアレイは仮想接地導体 5 4 A , 5 4 B (埋設された拡散) および金属から金属への拡散コンタクト 5 5 , 5 6 , 5 7 , 5 8 を共有するように、フリップされる。仮想接地導体 5 4 A , 5 4 B は、金属から拡散へのコンタクト 6 0 A , 6 0 B をとおして垂直な仮想接地金属ライン 2 5 までアレイを横切って水平に伸びる。サブアレイは、隣接するサブアレイが金属の仮想接地ライン 2 5 を共有するように、金属の仮想接地ライン 2 5 の反対側で繰り返す。金属の仮想接地ライン 2 5 は、アレイの接地と消去の高電圧回路に結合される。従って、サブアレイのレイアウトは、グローバルビットラインに対する 2 つのトランジスタセルの列当たり 2 つの金属コンタクトピッチおよび金属の接地ライン 2 5 に対する 1 つの金属コンタクトピッチを必要とする。

ソフトプログラムの間、やや高い電圧でワードラインを駆動することは、高い電流がソフトプログラムされているセクターに発生される可能性を作る。この電流は、セルのソース側における電流制限器回路によって制限される。図 2 を参照すると、下部のブロック選択トランジスタ 6 5 B または 6 5 A が電流制限器として動作する。そのソース側のこのトランジスタは、動作モードに依存するゼロ電圧または正の電圧をサポートする発生器であるアレイの接地電源に接続される。従って、下部のブロック選択トランジスタ 6 5 A , 6 5 B は、ソフトプログラム中に電流制限器としても働くセクターデコードトランジスタである。他の電流制限機構、例えば電流ミラー回路も同様に用いることができる。

図 2 の回路によって与えられたセクターデコード能力は、ソースを接地している間約 5 . 5 ボルトをローカルドレインラインへ与えることによって、ドレンを乱す型のソフトプログラムパルスをアレイの選択されたセグメントのみへ与える回路が具現化されるようとする。

また、ビットラインまたはドレイン端子を接地している間、ソフトプログラムされるデバイスのソース端子を介して、他のシステムは約 5 . 5 ボルト或いは回路パラメータに依存してそれ以上のソフトプログラムパルスを与えるであろう。同じセグメントごとのデコーディング、およびワードライン駆動装置をこのソース乱れ手法に利用することができる。

10

20

30

40

50

図3を参照すると、本発明のピーク電流を制限するためのステップを含む、チップまたはブロック消去プロセスの全体のフローチャートが示されている。消去動作（ステップ80）を開始した後、オンチップ状態マシン、ホストCPUまたはコマンドロジック5（ステップ81）を介して他の方法により、消去用のチップまたは選択されたブロックに対して事前プログラミング(pre-programming)が開始される。ステップ82で、事前プログラミング後に電圧が定まる、即ち安定するようにするプログラム回復期間が生じる。ステップ83でプログラムのベリファイプロセスが生じる。それからシステムは、チップまたはブロックにおける最後のアドレスが事前プログラムされる（ステップ84）か否かを知るためにチェックする。もし、そうでなければ、事前プログラミングステップにおいて開始するプロセスは、チップまたはブロックにおける全てのセルが事前プログラムされるまで繰り返される。

事前プログラミングの後、ステップ85で消去動作が実行され、消去電圧が定まるようになる消去回復期間86が続く。次に、消去ベリファイ動作87が行われる。その後、システムは消去プロセスがステップ88で完了するか否かを知るためにチェックする。もし、完了しないなら、それは完了するまで消去動作を行ってステップ85へ戻る。

本発明によると、ステップ85で与えられた消去パルスは、ワードラインを負の電位、例えば-7.8ボルトにセットし、ドレインをオープン回路状態（フローティング）にセットし、且つソース電位を正の電位にセットするステップを含む。第1のM試行の間、ソース電位は約4.5ボルトにセットされる。残りの試行の間、ソース電位は約5.5ボルトにセットされる。本発明の1つの好適な実施形態において、Mは3である。2つの消去電位シーケンスの4.5ボルトと5.5ボルトのソース電位は、アレイにおけるフローティングゲートメモリのバンド-ツー-バンドのトンネル電流に対して、ターンオンソース電位に従って選択される。約4.5ボルトでの第1のソース電位は、高いスレッショルド状態にある高いスレッショルドを有するセルのみがバンド-ツー-バンドのトンネル電流に合うレベルにセットされ、一方、高いスレッショルド状態にある低いスレッショルドを有するセルは、著しいバンド-ツー-バンドのトンネル電流を受けないであろう。この例における約5.5ボルトの高いソース電位は、アレイの低いスレッショルドセルが著しいバンド-ツー-バンドのトンネル電流に合うようにセットされる。しかし、約5.5ボルトの第2のソース電位は、アレイの大部分のセルが消去パルスの第1のM試行の間第1電位シーケンスの適用によって、スレッショルドが減少される。本発明による使用のための好適なバンド-ツー-バンドのトンネル電流のターンオンソース電位の決定は、図9を参考して以下に詳細に説明される。

消去シーケンスがステップ88で完了すると、ステップ89におけるソフトプログラムは、ソフトプログラムパルスが消去動作の全チップまたはブロックサブジェクトにおける全てのセルに与えられる。ソフトプログラム回復はステップ90において生じる。プロセスはステップ91で終了する。

図4は、図1のセクター消去フラッグ3およびアドレスカウンター4を用いて制御回路2によって一般に実行される組み込まれた消去および修復プロセスに対するアルゴリズムを含む、本発明の1つの実施形態を示す。

組み込まれた消去アルゴリズムに従って、消去動作は消去されるべきアレイのセクターを指示する1つ、或いはそれ以上のフラッグの設定を伴って、ステップ99において開始する。チップ消去に対して、全てのフラッグがセットされ、アドレスカウンターはアドレスゼロに初期化される。もし、セクターの消去動作が実行されるべきであれば、選択されたセクターに対するフラッグのみがセットされる。本発明のこの実施形態によると、修復フラッグもセットされ、各々のセクター消去フラッグのための1つ、ソフトプログラム修復パルス（ステップ99A）を受けるためにセクターを識別する。次に、事前プログラム動作は選択されたセクター上で実行される（ステップ100）。

次のステップにおいて、セットされたフラッグを有する全てのセクターは消去される（ステップ101）。消去ステップは消去パルスをセットされたフラッグを有するセクターに与えるステップを含み、並列にアレイの選択されたセクターを消去するステップを生じる

10

20

30

40

50

。消去パルスの第 1 の M 試行の間、ソース電位は、第 1 の低い電圧、この例においては例えば 4 . 5 ボルトにセットされる。消去パルスの残りの試行の間、ソース電位は高い値、この例では約 5 . 5 ボルトにセットされる。消去動作の間、仮想接地ライン 25 のソース電圧は、例えば B B S E L トランジスタによって選択されないセクターから分離される。B B S E L は、セクターフラッグがセットされると、アレイソース電圧を通過するために高い電圧で駆動され、またセクターフラッグがリセットされると、ゼロ電圧で駆動される。これによりセクター化された消去動作が可能になる。選択されたセクターの全設定は、上記のように付勢電圧を与えることによって消去され、下部ブロックの選択トランジスタの制御下でセグメント化される。

次に、タイマーは消去のタイムアウト状態を待つ（ステップ 102）。タイムアウト状態の後、消去回復フェーズに入る（ステップ 103）。再び、この回復フェーズはステップ 104 において指示されるように、時間がきめられる。10

消去回復後、消去ベリファイ電圧はセットアップされる（ブロック 105）。この動作は、“ERASE AND PROGRAM VERIFICATION CIRCUIT FOR NON-VOLATILE MEMORY”と題する米国特許第 5,463,586 号に詳細に記載されている。

次のステップは、セットフラッグを有するセクター内の各位置においてフラッグを評価し、データをテストすることである（ブロック 106）。このルーチンはフラッグがセットされるたか否かを決定することを含む（ブロック 107）。もし、セットされているなら、ルーチンは最下位のビットカウンターの消去ベリファイバスおよびオーバーフローに対して、先ずチェックする。もし、バスが検出され、カウンターがセクターの終わりにないならば、最下位のビットアドレスは増加される（ブロック 109）。この点において、アルゴリズムはブロック 106 ヘループバックする。20

フラッグがブロック 107 においてセットされないなら、アルゴリズムは最後のセクターがテストされたか否かを決定するためにテストする場合、アルゴリズムはブロック 110 ヘループする。最後のセクターがブロック 110 でテストされたならば、アルゴリズムは全てのフラッグがリセットされたか否かをテストする場合、アルゴリズムはブロック 111 へ進む。もし、全てがリセットされているか、ルーチンの始めにリセット状態にあるならば、アルゴリズムは消去が行われたことを示す（ブロック 112）。もし、全てのフラッグがリセットされていないならば、アルゴリズムは、ブロック 120 へプランチし、試行カウンターを増加する。もし、試行カウンターがオーバーフローする（例えば、1024 に達する）なら、エラー信号が出される。オーバーフローが生じないなら、アルゴリズムはブロック 101 ヘループバックして、セットフラッグを有するセクターを再び消去する。30

もし、ブロック 108 で、セルが消去ベリファイをバスしなかったか、あるいはバスするが、セクターの最後の LSB であるなら、アルゴリズムはブロック 113 へプランチする。ブロック 113 において、アルゴリズムは、再び消去ベリファイバスおよびセクターの終わりに対してテストする。もし、セルがセクターの終わりにあり、バスするなら、セクターに対する消去フラッグがリセットされる（ブロック 114）。もし、セルがセクターの終わりになく、セクターに対する消去フラッグはこの時点でリセットされないなら、MSB アドレスは増加されて次のセクターへ行き、LSB アドレスはリセットされる（ブロック 115）。その点で、アルゴリズムはブロック 106 ヘループバックして、消去ベリファイのためのセットされたフラッグを有する他のセクターを介してループする。40

消去ベリファイの後、ソフトプログラムの修復パルスはセットされた修復フラッグを有するセクターに加えられる。従って、ワードライン電圧は、接地あるいはそれより上、好ましくは約 0 . 3 ボルト（ステップ 116）であるが、その程度に初期的にセットされる。この実施の形態において、修復パルスが約 200 ms 間セットされた修復フラッグを有するセクターへのビットラインに与えられる間、ワードライン電圧が維持される（ステップ 117）。最後に、修復フラッグは、修復ベリファイの動作なくリセットされる（ステップ 118）。修復パルスの間、選択されたセクターの上部ブロックの選択トランジスタは、修復フラッグに応答してイネーブルされ、その結果、5 . 5 ボルトの修復電圧が埋設さ50

れたドレインラインに加えられて、選択されたセクター（セクター消去の場合）または全体のチップ（チップ消去の場合）に存在するこれらの過消去(over-erased)セルを修復する。消去パルスは、チャネル長さおよび他のセルパラメーター、修復パルス長、および他のファクターに依存して、例えば、約3.5ボルトから約10.0ボルトまでの範囲に及ぶ。

図5～図8は、本発明による2つの消去電圧シーケンスを具現化するために用いられる回路図におけるロジックを与える。図5にデバイスの簡略化された図面が示されている。このデバイスは、トランジスタ502のソースにライン501上のソース電圧電位ARVS Sを受け取るフラッシュアレイ500を有する。トランジスタ502のドレインは高いプログラミング電位 $V_{pp}$ （例えば、50mAで12ボルト±5%）に接続される。トランジスタ502のゲートは、バイアス回路503によって発生される、ライン504上のBIA S電圧に接続される。このバイアス回路503は、組み込まれた消去アルゴリズムを制御するデバイス上の状態マシンによって発生される、ライン505上の制御信号PERVFによって制御される。上述のように、消去パルスの第1のM試行の間、ライン505上の制御信号PERVFは、高いロジック電位、約5ボルトにセットされる。再試行M+1からNの間、制御信号PERVFは、低いロジック電位、0ボルトにセットされる。通常、本発明によるとパラメーターMは1から5の範囲にあり、パラメーターNは約1024である。勿論、整数MとNは本発明の特定の実現化の必要性に適合されることができる。

図6は、図5の回路503によって、ライン504上にBIA S信号を発生するための電圧分割回路の一例を示す。図6の回路は、状態マシンからライン505上の入力PERVF信号として受信し、ライン504上にBIA S信号を発生する。BIA S回路への第2の入力はライン600上に供給される。この信号はBIA S回路をイネーブルして、消去パルスの間0ボルトであり、消去パルスが発生されない場合、高電位（例えば、12ボルト）である。図6の実施形態によるBIA S回路は、pチャネルトランジスタ601-608を含む。またnチャネルトランジスタ609-610もこの回路に含まれる。pチャネルトランジスタ601-604は、BIA S信号が発生されるノード504とプログラミング電位 $V_{pp}$ 間に直列に接続される。トランジスタ601のゲートはライン600上の制御信号に結合される。トランジスタ602-604のゲートはそれらのそれぞれのドレインに結合される。また、回路におけるpチャネルトランジスタの各々のウエルはそのソースに結合される。

nチャネルトランジスタ609は、ノード504に結合されたそのドレインとpチャネルトランジスタ605のソースに結合されたそのソースを有する。トランジスタ609のゲートは、ノード504に結合される。pチャネルトランジスタ605-608はトランジスタ609のソースと接地間に直列に結合される。pチャネルトランジスタ605-608の各々のゲートは、それぞれのドレインに結合される。pチャネルトランジスタ605-608の各々のソースは、トランジスタが形成されるウエルに結合される。nチャネルトランジスタ610はpチャネルトランジスタ607のゲートに結合されたそのドレインと接地に接続されたそのソースを有する。トランジスタ610のゲートは、制御信号PERVFを受信する。動作において、制御信号PERVFは、パルス1からMの間5ボルトであり、残りのパルスの間は0ボルトである。 $V_{pp}$ は約12ボルトに等しく、BIA S電位は、この例では第1の消去パルスシーケンスの間約5.95ボルトである。残りの消去パルスシーケンスの間、BIA S電位は約6.8ボルトである。

ライン504上のBIA S信号は図7の回路によって用いられ、ライン501上にアレイのソース電圧ARVSSを発生する。ソース電位を発生する、図7の回路はnチャネルトランジスタ701, 702, 703, 704および705を有する。nチャネルトランジスタ701はプログラミング電位 $V_{pp}$ に結合されたそのドレインとゲート、およびnチャネルトランジスタ702のドレインに結合されたそのソースを有する。トランジスタ702のゲートは、ライン504上のBIA S信号を受信するために結合される。トランジスタ702のソースはソース電圧電位ARVSSが与えられるノード501に結合される。トランジスタ703はノード501に結合されたそのドレイン、 $V_{dd}$ 電位（5ボルト±1

10

20

30

40

50

0 %)に結合されたそのゲートおよびノード706に結合されたそのソースを有する。トランジスタ704は、ノード706に結合されたそのドレインと接地に接続されたそのソースを有する。トランジスタ704のゲートは、ライン707上で制御信号PAYSBに結合される。トランジスタ705はノード706に結合されたそのドレインと接地に接続されたそのソースを有する。トランジスタ705のゲートは、ライン708上の制御信号PAYSに結合される。

図7に示された例示の回路において、トランジスタ701と702は、各々800μmの幅と1.2μmの長さである。トランジスタ703と704はそれぞれ250μmの幅である。トランジスタ703は2μmの長さである。トランジスタ704は1.2μmの長さである。トランジスタ705は4μmの幅で30μmの長さである。トランジスタ705は、消去プロセスの間ノード501を高いフローティングを妨げる弱い漏洩バスを与える。動作において、消去パルスの第1のセットに対して信号PAYSBは0に等しく、信号BIASは約5.97ボルトに等しい。これは約4.5ボルトのソース電位ARVSSを生じる。消去パルスの残りの、或いは第2のセットの間、制御信号PAYSBは0ボルトであり、制御信号PAYSはロジック1である。消去パルスの第2のセットの間、BIAS信号は約5.5ボルトのライン501上にソース電位を生じる約6.8ボルトである。消去シーケンスの間の他の時間では、信号PAYSBはロジック1であり、信号PAYSはロジック0であり、そしてBIAS信号は0ボルトである。これは約0ボルトのソース電位を生じる。

従って、本発明によると、組み込まれた消去プロセスは、第1のM消去パルスが第1の電位にセットされたソース電位を有する第1の電圧シーケンス、および残りの消去パルスが第2の電位にセットされたソース電位を有する第2の電圧シーケンスを含む。消去シーケンスの初期の部分の間に合うバンド-ツー-バンドのトンネル電流の量を制御するために、第1の電位は第2の電位より小さく、それにより、プロセスによって発生されたピーク電流を定格の電源レベル以下のレベルに制御する。例えば約50ミリアンペアの定格最大電流を伴う、12ボルト±5%の標準の $V_{PP}$ 電源である。従って、ピーク電流は12.6ボルト電源で50ミリアンペアをこえないように、消去プロセスの間に発生された電流を制御することが必要である。しかし、消去プロセスはできる限り進める必要がある。従って、初期の消去パルスは、消去速度を犠牲にすることなく、電源の利用可能なピーク電流容量をできる限り多く利用すべきである。

図8は、本発明による1つの例示システムにおけるプロセスの結果を示す。図8の例、即ち図1と図2のアーキテクチャを有する4メガビットのフラッシュメモリデバイスが本発明の組み込まれた消去アルゴリズムを用いて消去される。ここで、第1の3つの消去パルスは4.5ボルトのソース電位を用い、残りのパルスは5.5ボルトのソース電位を用いた。図示されるように、第1の消去パルスの間、点800におけるピーク電流 $I_{PP}$ は約46ミリアンペアである。第1の消去パルスの間、電流は点801に急速に低下する。点801の後で、ベリファイシーケンスが実行される。第2の消去パルスの終わりで、電流は点802において20ミリアンペアより僅かに大きい。第3の消去パルスの終わりで、電流は点803において約18ミリアンペアである。この点で、約5.5ボルトのソース電位を伴って第2の電圧シーケンスが開始する。従って、第4のパルスの始めにおけるピーク電流は点804において約33ミリアンペアである。電流は各々の続く消去パルスに対して低いレベルに下降する。消去速度は、電源に対して50ミリアンペアのピーク電流を越えることなく第4の消去パルスの間4.5ボルトから5.5ボルトまでソース電位を増加することによって著しく増加される。更に、消去プロセスの速度は、初期の消去パルスの間電源の最大電流駆動能力を用いる消去パルスを与えることによって維持され、残りのパルスの間消去電界を最小にする。

本発明による消去アルゴリズムの電圧シーケンスにおいて用いられるソース電位の選択は図9を参照して理解される。図9は-7.8ボルトの制御ゲート電位およびオープン回路状態におかれたドレインを有する4メガビットアレイに対する、シミュレートしたバンド-ツー-バンドのトンネル電流のグラフである。このグラフは、8ボルトのセルのスレッ

10

20

30

40

50

ショルド電圧でシミュレートされたアレイに対する第1のトレース 900 を示す。アレイにおけるセルのスレッショルト電圧が 6 ボルトの場合の第2のトレース 901 および電圧のスレッショルドが 5 ボルトの場合第3のトレース 902 を示す。本発明によると、消去アルゴリズムの第1の電圧シーケンスの間に選択されたソース電位は、高いスレッショルド、例えば約 8 ボルトを有するセルのバンド - ツー - バンドのトンネル電流に対するターンオンスレッショルドに近い。高いスレッショルド状態における高いスレッショルドセルのみが著しいバンド - ツー - バンドのトンネル電流を発生し、一方、アレイにおける低いスレッショルドセルは、間隔 903 において 4 ボルトから 5 ボルトの範囲にあるソース電位を伴って、著しいバンド - ツー - バンドのトンネル電流を発生しない。従って、組み込まれた消去アルゴリズムの間ソースにおける第1の電圧は間隔 903 において選択される。

10 消去アルゴリズムの第2の電圧シーケンスに用いられるソース電圧は、高いスレッショルド状態、例えば 6 ボルトのスレッショルドにおける低いスレッショルドを有するセルに対するターンオン電位の近くに選択される。従って、消去アルゴリズムの第2の電圧シーケンスに用いられる第2の電位は 5 ボルトと 6 ボルトの間の間隔 904 内に入る。従って、4.5 ボルトと 5.5 ボルトの電圧レベルが本発明のこの実施の形態による組み込まれた消去アルゴリズムの第1と第2のシーケンスに対して選択された。

20 従って、本発明による組み込まれた消去シーケンスは、バンド - ツー - バンドのトンネル電流のターンオンスレッショルドのソース電位が間隔 904 まで増加される前に、高いスレッショルドセルが低いレベルの高いスレッショルド状態に駆動される。このようにして、初期のパルスに対する消去プロセスにおいて消費されるピーク電流は、消去速度においてカウンターの平衡減少なく、著しく減少される。何故ならば、増加されたFowler-Nordheimのトンネル電流がバンド - ツー - バンドのトンネル電流において不合理に増加することなく得られる場合、第2の電圧シーケンスがソース電位を領域 904 へ増加することを含むからである。

30 結論として、本発明は大きなスケールのフラッシュメモリデバイスにおいて、組み込まれた消去アルゴリズムに対する高いプログラミング電位  $V_{pp}$  の電源ピーク電流要求を減少する。技術は高いピーク電流を防ぐために、第1の消去電圧シーケンスにおける消去パルスの間に生じるバンド - ツー - バンドのトンネル電流の量を制御することを含む。ここに述べたように、セクターのフラッギング機構やソフトプログラムパルスの使用のような、消去の間妨げる技術と結合されると、本発明は高い信頼性のあるフラッシュメモリデバイスと制御されたピーク電流を提供する。

本発明の好適な実施形態の以上の説明は概要を説明するためになされた。本発明を開示された正確な形状に限定することを意図しない。多くの変形や変更がなされることとはこの分野のいわゆる当業者には明らかであろう。本発明の範囲は以下の請求項およびその均等物によって定められるべきである。

【図1】

FIG.1

【図2】

FIG.2

【図3】

FIG.3

【図4】

FIG.4

FIG.7

FIG.8

【図9】

FIG.9

---

フロントページの続き

(74)代理人

弁理士 小川 信夫

(74)代理人

弁理士 村社 厚夫

(72)発明者 シアウ ツエン ヒューエイ

台湾 シン チュ カウンティー シン プ チュン チェン ロード 595

(72)発明者 ワン レイ リン

アメリカ合衆国 カリフォルニア州 94539 フリーモント ウィチトー ドライヴ 709

(72)発明者 リウ ユーアン チャン

台湾 ミヤオ リ シティー チャン クン リ ヤオ ピン ストリート #14

(72)発明者 ヒュン チュン シウン

台湾 シン チュ ユニヴァーシティー ロード レーン 81 アーレイ 3 - #5 - 4エフ

(72)発明者 チュアン ワイトン

台湾 タイチョン セクション 4 レーン 11 - 5 - 10 - エフ12

(72)発明者 チェン ハン スン

台湾 ケールン アイ チュー ロード 29

(72)発明者 ショーン フューチア

台湾 シン チュ サイエンス ベースド インダストリアル パーク ウォーターフロント ロード I - 2 - 3エフ

審査官 高野 芳徳

(56)参考文献 特開平07-235190(JP,A)

特開平06-037285(JP,A)

特開平07-326196(JP,A)

特開平07-312093(JP,A)

特開平07-073685(JP,A)

特開平05-182479(JP,A)

特開平08-055487(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 16/00 - 16/34