(11) **Número de Publicação:** PT 101296 B

(51) **Classificação Internacional:** (Ed. 6 )

G06F017/60 A H03K019/00 B

G06F159:00 Z

(12) **FASCÍCULO DE PATENTE DE INVENÇÃO**

|                                                          |                                                                                       |

|----------------------------------------------------------|---------------------------------------------------------------------------------------|

| (22) <b>Data de depósito:</b> 1993.06.30                 | (73) <b>Titular(es):</b><br>HELEDER DA SILVA<br>R. DAS MURTAS Nº 7, 1º-DTº 2735 CACÉM |

| (30) <b>Prioridade:</b>                                  |                                                                                       |

| (43) <b>Data de publicação do pedido:</b><br>1994.12.30  | (72) <b>Inventor(es):</b>                                                             |

| (45) <b>Data e BPI da concessão:</b><br>11/98 1998.11.03 | (74) <b>Mandatário(s):</b>                                                            |

(54) **Epígrafe:** CIRCUITO LÓGICO DIGITAL PARA UM TRAÇADOR VISUAL DO GRÁFICO DO PARTOGRAMA USADO NAS MATERNIDADES

(57) **Resumo:**

CIRCUITO LÓGICO DIGITAL PARA UM TRAÇADOR ELECTRÓNICO VISUAL DO GRÁFICO DO PARTOGRAMA USADO NAS MATERNIDADES

101296

*W. J.*

65811

1

## DESCRIÇÃO

5

CIRCUITO LÓGICO DIGITAL PARA UM TRAÇADOR ELECTRÓNICO

VISUAL DO GRÁFICO DO PARTOGRAMA USADO NAS MATERNIDADES

10

## SUMÁRIO DA INVENÇÃO

15

20

25

A invenção refere-se a um circuito lógico digital para um traçador electrónico, visual, do gráfico do partograma usado nas maternidades. Numa mulher grávida em perspectiva de parto recém chegada à maternidade, os obstetras medem a intervalos regulares a dilatação do colo do útero e através de um gráfico padrão analisam se o parto da parturiente é normal e, caso não seja, procuram uma alternativa que pode ser, por exemplo, uma cesariana. Com o intuito de eliminar o trabalho de rotina provocado pela constante análise da dilatação do colo do útero e a grande atenção que esta análise exige da parte do obstetra, concebeu-se um dispositivo (traçador) no qual, através de teclas, são introduzidos os dados necessários ao traçado do gráfico do partograma. O resultado do processamento destes dados é visualizado numa matriz de diodos emissores de luz (LED'S). Esta matriz tem uma zona de cor verde-

partos sem risco de cor de laranja- partos com perspectivas de risco e de cor vermelha- partos com risco.

## DESCRIÇÃO DAS FIGURAS

30

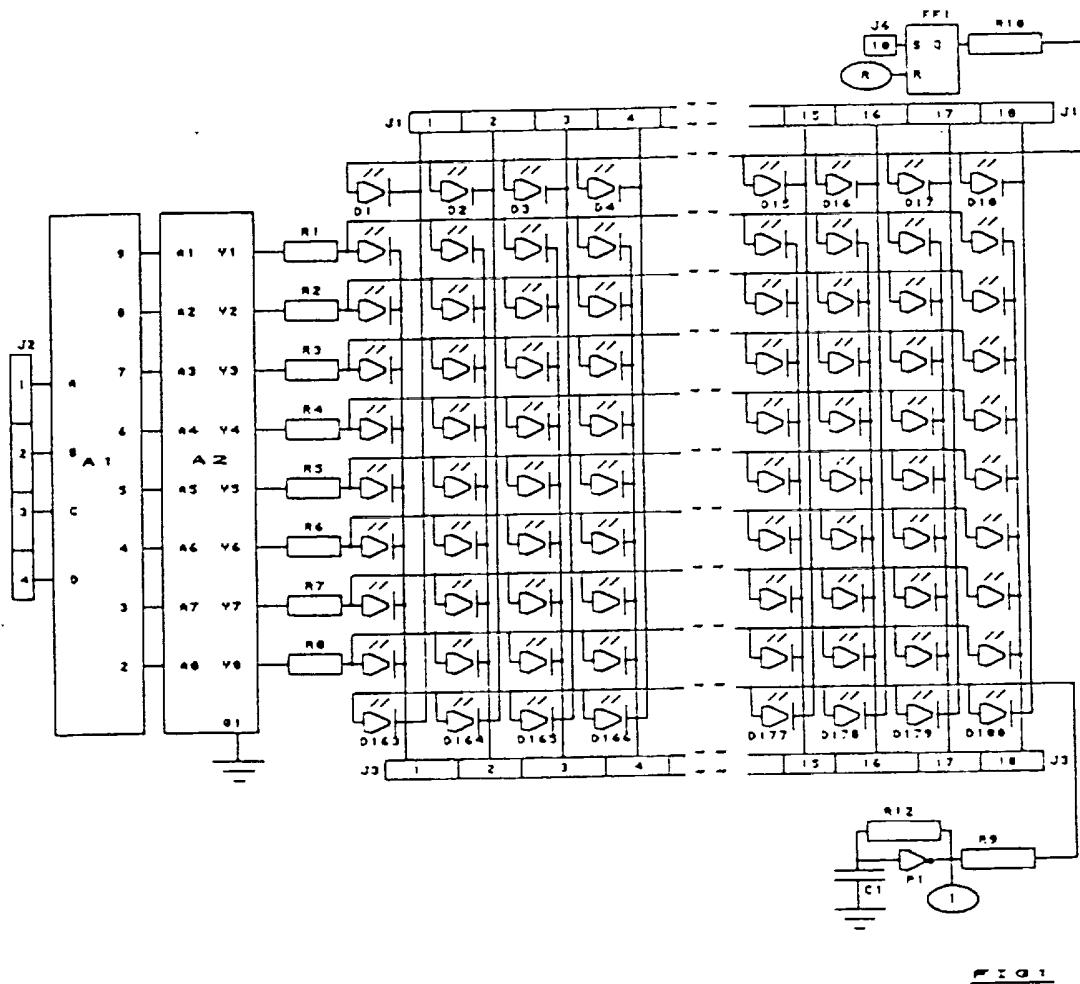

FIGURA 1- Mostra a matriz de diodos emissores de luz (LED'S) onde são visualizados todos os dados introduzidos e processados comandados pelo descodificador BCD-Decimal com as saídas complementadas pelas memórias tampão (Buffers) A2, e reduzida a corrente pelas resistências de R1 a R8. A fila inferior da matriz indica em que célula da memória serão endereçados os dados referentes à dilatação do colo do útero e aos planos. O circuito

1 Bi- estável (Flip-Flop) memoriza a pressão da tecla S1

pelo facto do descodificador A1 ter permanentemente na

sua saída 1 (Decimal).

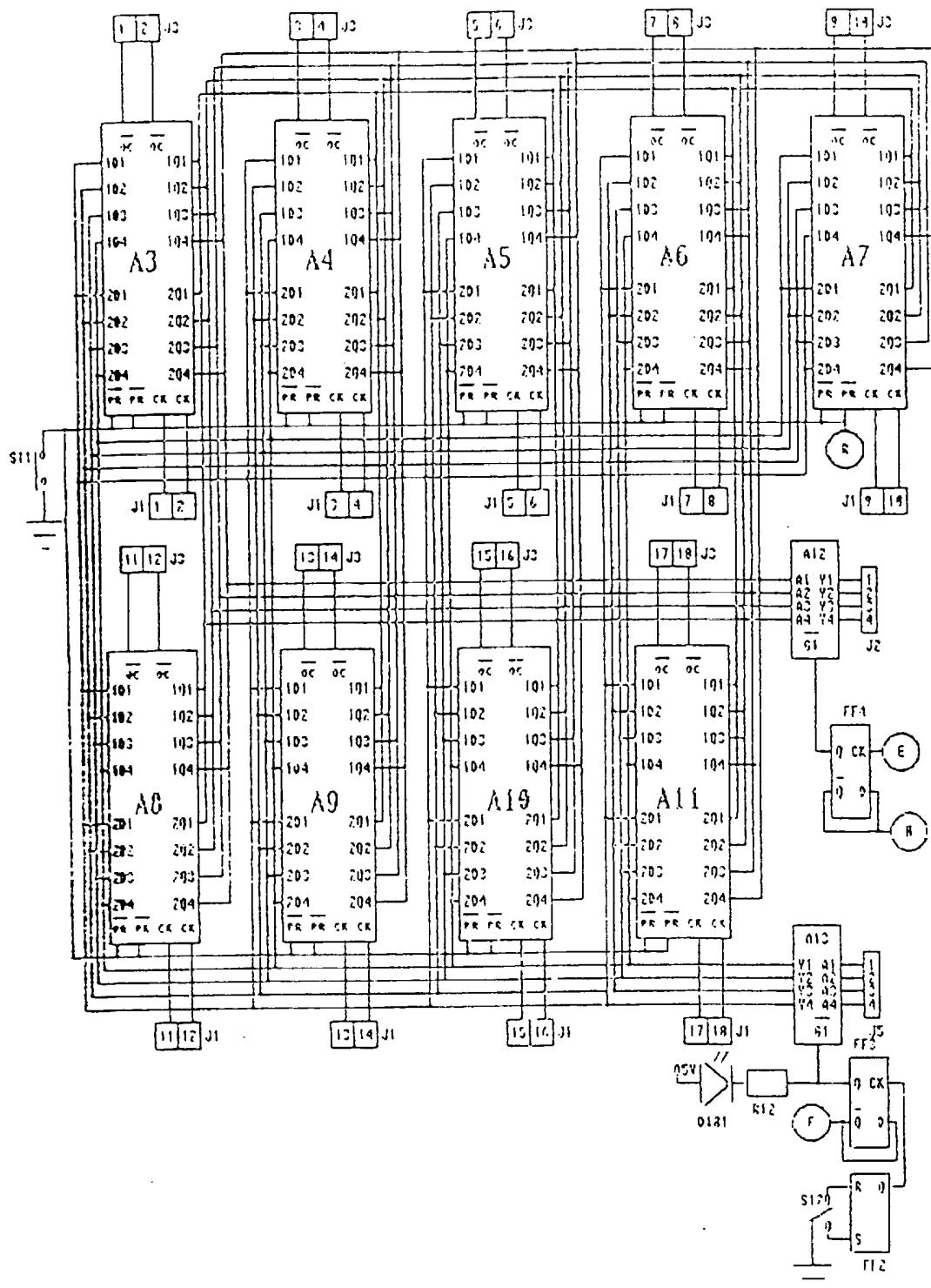

5 Figura 2 - Mostra a associação de circuitos Bi- estáveis

(Flip-Flop) do tipo D de A3 a A11 de modo a armazenar

e apresentar os dados introduzidos no teclado.

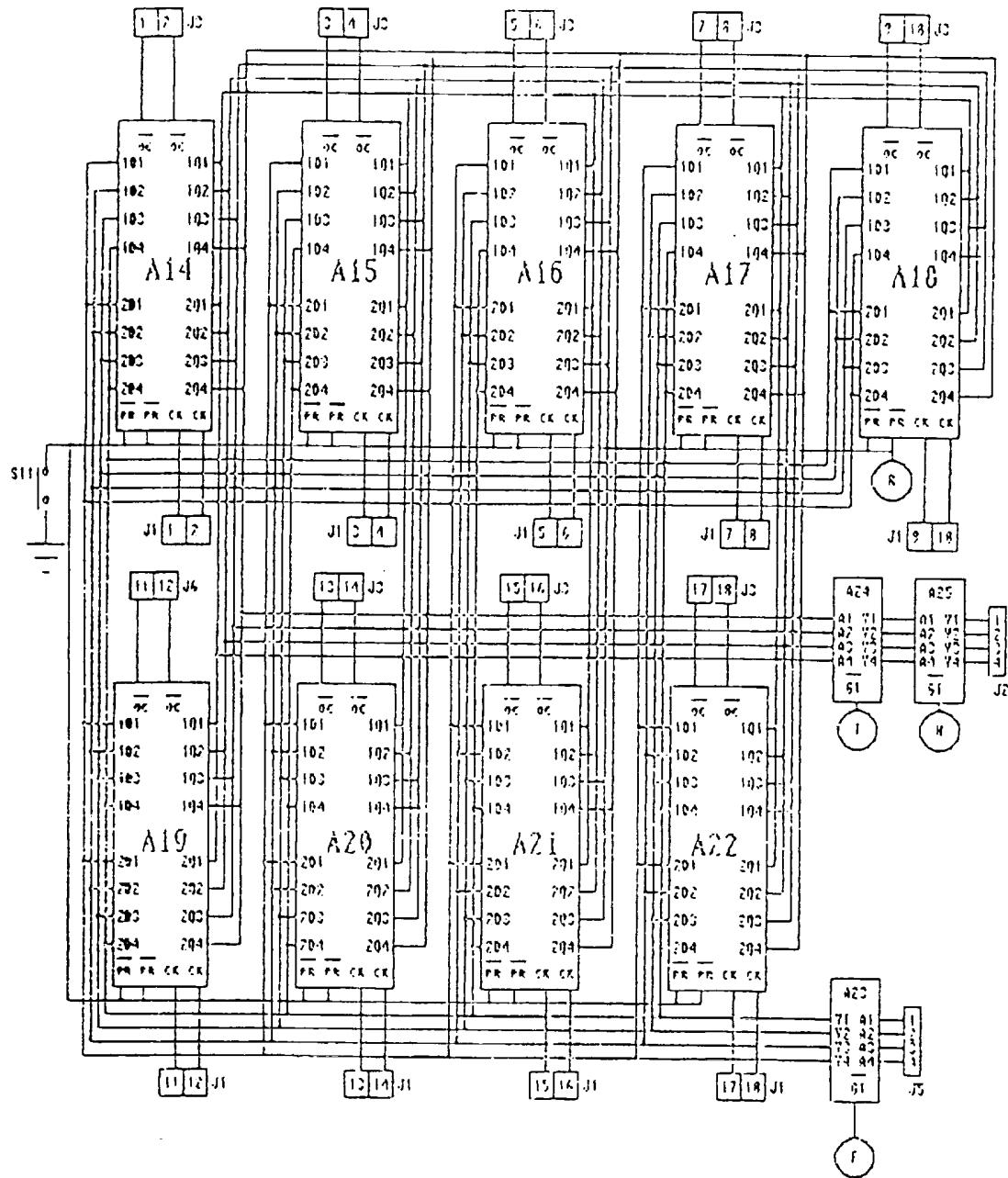

10 Figura 3 - Também mostra uma associação como a Figura 2,

embora o controlo da amostragem dos dados que estão

armazenados e dos que virão a estar sejam controlados

de uma forma complementar, utilizando para o efeito

os circuitos de A14 a A22.

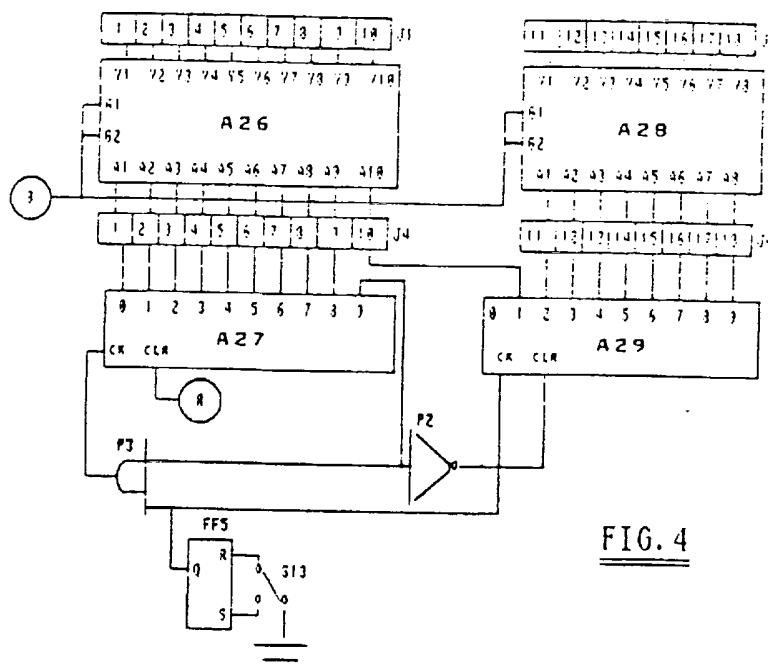

15 Figura 4 - Mostra a tecla S13 que em conjunto com o circuito

Bi- estável (Flip-Flop) FF5 produz impulsos bem

definidos para os contadores/descodificadores BCD-

Decimal A27 e A29 através das portas P2 e P3 que

permitem seleccionar as células de endereço. Temos

ainda nesta figura as memórias tampão (Buffers) A26 e

20 A28 que ao interromperem a transferência de dados

contidos nas saídas dos contadores/descodificadores

BCD-Decimal A27 e A29, na entrada de controlo da junção

B, permitem, por estarem conectados através da junção

J1 aos circuitos A3 a A11 e de A14 a A22, a memorização

25 dos dados contidos na saída do codificador Decimal-BCD

A30 na célula onde os circuitos A27 e A29 tiverem o

estado lógico zero.

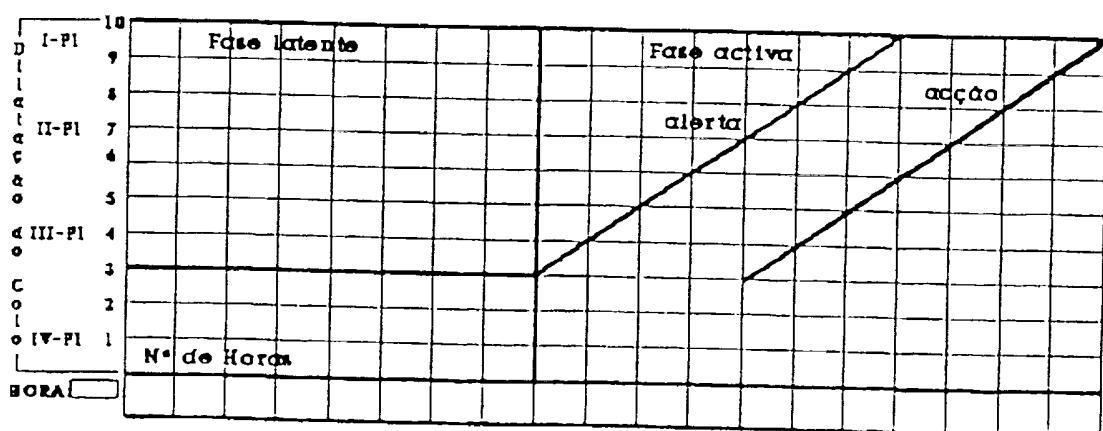

30 Figura 5 - Apresenta-se nesta figura o gráfico do partograma

onde os partos ocorridos acima da fase latente e da

fase activa são normais iluminando-se para o efeito os

diodos emissores de luz (LED'S) verdes correspondentes

35 a cada rectângulo, os partos ocorridos na zona de ação

tendem a provocar riscos iluminando-se assim os diodos

emissores de luz (LED'S) alaranjados correspondentes a

cada rectângulo, e abaixo da zona de ação iluminam-se

os diodos emissores de luz (LED'S) vermelhos que

*65811*

65811

demonstram a existência de perigo.

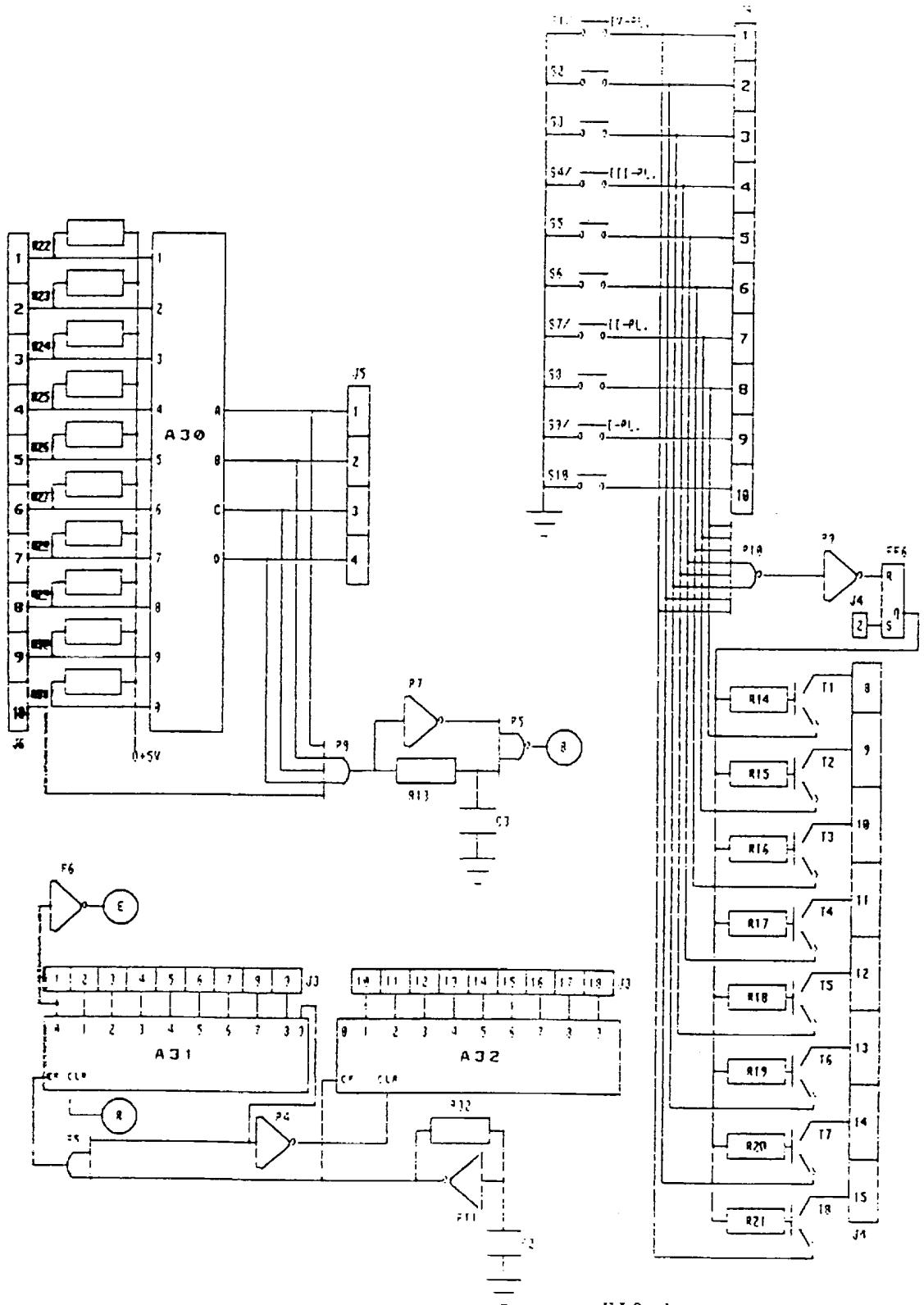

Figura 6- Mostra o teclado de S1 a S10 que através da junção J6 liga ao codificador Decimal-BCD A30 e este através da junção J2 endereça os dados aos circuitos Bi-estáveis (Flip-Flop's) de A3 a A11 e de A14 a A22 que são circuitos utilizados para a memorização da dilatação do colo do útero e dos planos respectivamente.

Temos ainda os transistores de T1 a T8 controlados pelo circuito Bi-estável (Flip-Flop) FF6 e P10 que em funcionamento conjunto fazem a transferência da prioridade de endereço da célula compreendida entre A3 e A11 para a recta padrão do partograma.

Nesta mesma figura existem os contadores/codificadores BCD-Decimal A31 e A32 que, auxiliados pelas portas P4 e P5, geram uma sequência de estado lógico 1 nas suas saídas com uma frequência de 1 KHz, o que permite uma multiplexagem na matriz dos dados memorizados em A3 a A11 e A14 a A22, sendo a junção J3 a intermediária da operação.

#### DESCRIÇÃO DA INVENÇÃO

Os obstetras que utilizam o método gráfico do partograma para analisar a evolução de um parto necessitam, em função do gráfico de partograma, conhecer:

- Dilatação do colo do útero.

- Planos (altura da descida da apresentação).

- Tempo de permanência da parturiente na maternidade em perspectiva de parto.

Para evitar as anotações escritas na forma como até agora o diagrama tem sido utilizado, o dispositivo da invenção possue uma matriz de diódos emissores de luz (LED'S) de D1

1 a D180 onde será visualizado todo o processamento dos

dados introduzidos segundo o método do partograma.

5 Os dados:

- Dilatação do colo do útero,

- Planos

10 São introduzidos utilizando as teclas de S1 a S10 que servem ao mesmo tempo para a introdução dos referidos dados e para memorizar os planos, bastando para isso premir a tecla S12, iluminando-se assim o diodo emissor de luz (LED) D181 que está conectado à saída Q do contador binário FF3, limitada a sua corrente pela resistência R12.

15 Os dados introduzidos no teclado de 10 teclas são codificados para BCD pelo codificador Decimal-BCD A30 que recebe dados decimais do teclado através da junção J6. As resistências de R22 a R31 garantem o nível lógico um nas entradas do codificador enquanto não for premida nenhuma tecla, tendo em conta que o comum das referidas resistências estão ligadas a + 5 Volts. As saídas do codificador A30 estão ligadas às entradas D dos circuitos Bi-estáveis (Flip-Flop's) de A3 a A11 e de A14 a A22 através das memórias tampão (Buffers) A13 e A24 respectivamente, sendo estas duas controladas pelo contador binário FF3 que com as suas saídas complementares seleccionam o endereço dos dados.

30 Uma vez premida uma das teclas de S1 a S10, a porta AND P8 identifica a tecla premida e nesse momento a saída da referida porta transita do estado lógico um para zero, atrasado o impulso pela montagem constituída por P7, P5, R13 e C3. A saída da porta NAND P5 produz um impulso com um atraso em relação ao tempo de pressão da tecla e este

1 impulso através da ligação 3 liga às entradas de controlo

das memórias tampão (Buffers) A26 e A28 as quais controlam

a transferência dos dados contidos no codificador A30,

cuja transferência tem prioridade, para a célula que tiver

5 a saída dos circuitos A27 e A29 em estado lógico zero, que

é a ordem de tempo de permanência da parturiente na

maternidade em perspectiva de parto, tempo este que é

introduzido sequencialmente pela tecla S13.

10 Para que os dados introduzidos (dilatação do colo do

útero) na segunda medição, caso ultrapassem ou sejam iguais

a 3 cm, sejam transferidos para a recta padrão do

partograma, a porta P10 detecta a pressão de uma das

15 referidas teclas de S1 a S8 e, complementada pela porta NOT

P9, ataca a entrada R do circuito bi-estável (Flip-Flop)

FF6 que, se for a segunda medição identificada pela

entrada S da ligação 2 da junção J4, o transistor

correspondente, de T1 a T8, à tecla premida dará

20 prioridade à transferência de dados para a recta padrão

utilizando a junção J4 com os pontos de ligação de 8 a 15.

O deslocamento gerado pelos circuitos integrados A31 e

25 A32, transmitidos através da junção J3, distribuem a sua

geração com uma frequência de 1 Khz à matriz de diodos

emissores de luz (LED'S) de D1 a D180, e também para os

controles de saída dos circuitos bi-estáveis (FLIP-FLOP)

de A3 a A11 e de A14 a A22, possibilitando uma multiplexagem

30 dos dados na matriz e na apresentação dos dados memorizados

e processados pelos circuitos atrás referidos.

Para existir uma diferença na matriz entre os dados

memorizados referentes à dilatação do colo e dos planos, as

35 memórias tampão (Buffers) A24 têm a sua entrada de controlo

ligada ao oscilador de muito baixa frequência através da

65811

1 Junção I, o que permite uma intermitência na apresentação dos

dados dos planos pelo facto da sua apresentação ser

interrompida por uma frequência de 2 Hertz.

5

Lisboa. 30 JUN. 1993

Por, HELDER DA SILVA

SCD MANGOSA 1993

ESTABELECIMENTO DE INVESTIGAÇÕES

DE POLÍCIA NACIONAL

10

15

20

25

30

35

## REIVINDICAÇÕES

1º - Circuito lógico digital para um traçador electrónico visual do gráfico do partograma usado nas maternidades, em que a partir das medições feitas pelo obstetra da dilatação do colo do útero da parturiente em intervalos regulares e dos planos feitos para o nascimento, se traça um gráfico que permite avaliar do risco envolvido no parto, caracterizado por os dados (dilatação e planos) serem introduzidos através das teclas S1 a S10, e a memorização dos dados ser feita premindo a tecla S12, sendo esses dados codificados pelo codificador BCD (A30), estando as saídas deste codificador ligadas às entradas D dos circuitos bi-estáveis (flip-flop's) de A3 a A11 e de A14 a A22, através de memórias tampão (Buffers) A13 e A24 respectivamente, sendo estas duas controladas pelo contador binário FF3 que com as suas saídas complementares seleccionam o endereço dos dados, e também por possuir circuitos integrados A31 e A32 e uma matriz de diodos emissores de luz (LED'S), tendo esta matriz uma zona de cor verde para partos sem risco, laranja para partos com perspectiva de risco e, vermelha para partos de risco.

2ª - Circuito Lógico Digital de acordo com a primeira reivindicação caracterizado por possuir um circuito bi-estável (flip-flop) FF1 que recebe através da junção J6 impulsos de tecla S10 para introduzir os 10 cm., tendo em conta que o descodificador A1 tem permanentemente na saída o algarismo zero no último estágio de contagem e desse modo impossibilita a marcação de uma décima tecla.

3ª - Circuito Lógico Digital de acordo com a reivindicação anterior caracterizado por possuir um oscilador constituído por uma resistência R9, um condensador C1 e uma porta disparador (SCHMITT-TRIGGER) P1 que dá impulsos com uma frequência de dois Herts para sinalizar de uma forma intermitente para que célula da memória, correspondente ao tempo de permanência da parturiente na maternidade em perspectiva de parto, estão a ser endereçados os dados referentes á dilatação do colo e os planos, utilizando para a memorização os circuitos integrados contendo circuitos bi-estáveis (flip-flop's) de A3 a A11, para a dilatação do colo, e de A14 a A22, para os planos.

4<sup>a</sup> - Circuito Lógico Digital de acordo com a 3<sup>a</sup> reivindicação caracterizado por possuir memórias tampão (Buffers) A13 que, pressionando a tecla S12, seleccionam a entrada de dados para os circuitos de A3 a A11, cuja selecção é visualizada no diodo emissor de luz (LED) D181 que recebe tensão da saída Q do circuito bi-estável (flip-flop) FF3 e limita a corrente pela resistência R12.

5<sup>a</sup> - Circuito Lógico Digital de acordo com reivindicação anterior caracterizado por possuir um circuito bi-estável (flip-flop) FF4 que recebe impulsos da conecção E dá prioridade ao acesso alternado das saídas do circuito de A3 a A11 e de A14 a A22 para o descodificador BCD-Decimal que alimenta a matriz.

6<sup>a</sup> - Circuito Lógico Digital de acordo com a 5<sup>a</sup> reivindicação caracterizado por possuir um registo de deslocamento accionado pelos circuitos integrados A27, A29, P2 e P3, estes dois últimos funcionando em conjunto permitem o funcionamento alternado dos circuitos A27 e A29.

7<sup>a</sup> - Circuito Lógico Digital de acordo com a 6<sup>a</sup> reivindicação caracterizado por possuir memórias tampão (Buffers) A26 e A28 que recebem impulsos através da ligação B após a pressão de uma das teclas de S1 a S10 e que pelo facto das saídas dos circuitos A27 e A29 serem de colector aberto e os circuitos de A3 a A11 e de A14 a A22 serem disparados no flanco ascendente, recebem um impulso de relógio na saída de A26 e A28, permitindo assim a memorização dos dados contidos na saída do descodificador decimal BCD A30.

8<sup>a</sup> - Circuito Lógico Digital de acordo com a reivindicação anterior caracterizado por possuir uma porta NAND P10 que detecta a pressão de uma tecla referente à dilatação do colo, superior ou igual a 3cm., e, uma vez invertida a sua saída com a porta P9 que activa a entrada R do circuito bi-estável (flip-flop) e a FF6 que detecta se é ou não a segunda medição do colo, e caso sejam reconhecidas as duas condições citadas anteriormente e pelo facto de a saída Q do circuito bi-estável (flip-flop) FF6 estar ligada ao comum das resistências de polarização dos transistores de T1 a T8, há uma transferência dos dados referentes à tecla premida num determinado tempo (matriz) para a recta padrão do partograma (Método de transferência do partograma).

9<sup>a</sup> - Circuito Lógico Digital de acordo com reivindicação anterior caracterizado por possuir dois contadores/descodificadores BCD-Decimal A31 e A32, montados de maneira especial, de modo a fazerem o papel de registo de deslocamento, visto que a porta P4 impossibilita o circuito A32 de funcionar sem que a última saída de A31 transite para o estado lógico zero.

Lisboa, 2 de Outubro de 1998.

**HELDER DA SILVA.**

A handwritten signature in black ink, appearing to read "Helder da Silva".

QJ JUL 1993

W

F I G 1

20 JUN 1993

FIG2

3C 054 1993

W

F163

30 JUN 1993

FIG. 4

FIG. 5

FIG. 6