(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5490371号

(P5490371)

(45) 発行日 平成26年5月14日(2014.5.14)

(24) 登録日 平成26年3月7日(2014.3.7)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 27/12  | (2006.01) |

| HO 1 L 21/02  | (2006.01) |

| HO 1 L 21/265 | (2006.01) |

| HO 1 L 21/20  | (2006.01) |

| HO 1 L 21/336 | (2006.01) |

| HO 1 L        | 27/12     |

| HO 1 L        | 21/265    |

| HO 1 L        | 21/20     |

| HO 1 L        | 29/78     |

|               | 6 2 7 D   |

請求項の数 10 (全 35 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2008-109208 (P2008-109208)  |

| (22) 出願日     | 平成20年4月18日 (2008.4.18)        |

| (65) 公開番号    | 特開2008-288578 (P2008-288578A) |

| (43) 公開日     | 平成20年11月27日 (2008.11.27)      |

| 審査請求日        | 平成23年4月7日 (2011.4.7)          |

| (31) 優先権主張番号 | 特願2007-112239 (P2007-112239)  |

| (32) 優先日     | 平成19年4月20日 (2007.4.20)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 神保 安弘<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 小路 博信<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 大沼 英人<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

支持基板上に剥離層を形成し、該剥離層上に絶縁層を形成し、前記絶縁層上に可撓性を有し且つ絶縁表面を有する第1の基板を設ける第1の工程と、

一の原子から成る複数の質量の異なるイオン又は複数の原子から成る質量の異なるイオノンを単結晶半導体基板に照射して、該単結晶半導体基板の表面から所定の深さの領域に脆弱領域を形成した後、前記単結晶半導体基板の表面の平坦性を保たせつつ熱処理を行い、前記脆弱領域を脆弱にする第2の工程と、

前記第1の工程及び前記第2の工程の後、前記単結晶半導体基板の表面、または、前記可撓性を有し且つ絶縁表面を有する第1の基板の表面を活性化してから、前記単結晶半導体基板と、前記可撓性を有し且つ絶縁表面を有する第1の基板とを接合し、前記支持基板上に単結晶半導体層を残存させたまま前記単結晶半導体基板を剥離する第3の工程と、

前記第3の工程の後、前記単結晶半導体層を用いた半導体素子を有する素子層を形成する第4の工程と、

前記素子層上に可撓性を有し且つ絶縁表面を有する第2の基板を設ける第5の工程と、

前記第5の工程の後、前記素子層から前記支持基板を前記剥離層で分離する第6の工程と、

を有することを特徴とする半導体装置の作製方法。

## 【請求項 2】

支持基板上に剥離層を形成し、該剥離層上に絶縁層を形成し、前記絶縁層上に可撓性を

10

20

有し且つ絶縁表面を有する第1の基板を設ける第1の工程と、

一の原子から成る複数の質量の異なるイオン又は複数の原子から成る質量の異なるイオノンを単結晶半導体基板に照射して、該単結晶半導体基板の表面から所定の深さの領域に脆弱領域を形成し、

前記単結晶半導体基板上有機シランガスを用いて化学気相成長法により酸化珪素層を形成し、

前記酸化珪素層の表面の平坦性を保たせつつ熱処理を行い、前記脆弱領域を脆弱にする第2の工程と、

前記第1の工程及び前記第2の工程の後、前記酸化珪素層の表面、または、前記可撓性を有し且つ絶縁表面を有する第1の基板の表面を活性化してから、前記単結晶半導体基板と前記可撓性を有し且つ絶縁表面を有する第1の基板とを、前記酸化珪素層を挟んで重ね合わせて接合し、

前記支持基板上に単結晶半導体層を残存させたまま前記単結晶半導体基板を剥離する第3の工程と、

前記第3の工程の後、前記単結晶半導体層を用いた半導体素子を有する素子層を形成する第4の工程と、

前記素子層上に可撓性を有し且つ絶縁表面を有する第2の基板を設ける第5の工程と、

前記第5の工程の後、前記素子層から前記支持基板を前記剥離層で分離する第6の工程と、

を有することを特徴とする半導体装置の作製方法。

#### 【請求項3】

請求項1または2において、

前記単結晶半導体基板または前記酸化珪素層の表面の平坦性を保たせつつ熱処理を行う方法は、前記単結晶半導体基板または前記酸化珪素層の表面に圧着部材を重ね合わせた状態で加熱を行うことを特徴とする半導体装置の作製方法。

#### 【請求項4】

請求項1または2において、

前記単結晶半導体基板または前記酸化珪素層の表面の平坦性を保たせつつ熱処理を行う方法は、前記単結晶半導体基板または前記酸化珪素層の表面にキャップ層を形成した状態で加熱を行うことを特徴とする半導体装置の作製方法。

#### 【請求項5】

請求項2において、

前記有機シランガスとして、珪酸エチル、テトラメチルシラン、テトラメチルシクロテトラシロキサン、オクタメチルシクロテトラシロキサン、ヘキサメチルジシラザン、トリエトキシシラン、トリスジメチルアミノシラから選ばれた一種を用いることを特徴とする半導体装置の作製方法。

#### 【請求項6】

請求項2において、

前記単結晶半導体基板上有機シランガスを用いて化学気相成長法により酸化珪素層を形成する温度が350以下であることを特徴とする半導体装置の作製方法。

#### 【請求項7】

請求項1乃至6のいずれか一項において、

前記熱処理は、前記脆弱領域が分離する温度未満であり、且つ前記脆弱領域が脆弱となる温度で行われることを特徴とする半導体装置の作製方法。

#### 【請求項8】

請求項1乃至6のいずれか一項において、

前記熱処理が250以上400未満の温度で行われることを特徴とする半導体装置の作製方法。

#### 【請求項9】

請求項1乃至8のいずれか一項において、

10

20

30

40

50

前記単結晶半導体基板の表面に、前記一の原子から成る複数の質量の異なるイオン又は複数の原子から成る質量の異なるイオンを照射する前に、窒素含有絶縁層を形成することを特徴とする半導体装置の作製方法。

**【請求項 10】**

請求項 9において、

前記窒素含有絶縁層が、窒化珪素層、窒化酸化珪素層若しくは酸化窒化珪素層から選ばれた一の層又は複数の層を積層して形成することを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

10

本発明は、SOI (Silicon on Insulator) 基板及びそれにより製造される半導体装置、並びにそれらの作製方法に関する。特に貼り合わせ SOI 技術に関するものであって、可撓性を有し且つ絶縁表面を有する基板に、単結晶若しくは多結晶の半導体層を接合させた SOI 基板及びそれにより製造される半導体装置、並びにそれらの作製方法に関する。

**【背景技術】**

**【0002】**

20

単結晶半導体のインゴットを薄くスライスして作製されるシリコンウェハーに代わり、絶縁表面に薄い単結晶半導体層を設けたシリコン・オン・インシュレータと呼ばれる単結晶半導体基板 (SOI 基板) を使った集積回路が開発されている。SOI 基板を用いて集積回路を形成するトランジスタを設けることによって、トランジスタのドレインと基板間ににおける寄生容量を低減し、半導体集積回路の性能を向上させることができるので、SOI 基板は注目を集めている。

**【0003】**

SOI 基板を製造する方法としては、水素イオン注入剥離法が知られている（例えば、特許文献 1 参照）。水素イオン注入剥離法は、シリコンウェハーに水素イオンを注入することによって表面から所定の深さに微小気泡層を形成し、水素イオン注入面を別のシリコンウェハーと重ね合わせ、熱処理を行って該微小気泡層を劈開面として剥離することで、別のシリコンウェハーに薄いシリコン層 (SOI 層) を接合する。SOI 層を剥離するための熱処理に加え、酸化性雰囲気下での熱処理により SOI 層に酸化層を形成し、その後に該酸化層を除去し、次に 1000 乃至 1300 の還元性雰囲気下で熱処理を行って接合強度を高め、SOI 層の表面のダメージ層の改善をする必要があるとされている。

30

**【0004】**

SOI 基板を用いた半導体装置の一例として、本出願人によるものが知られている（特許文献 2 参照）。この場合にも、SOI 層において応力に起因するトラップ準位や欠陥を除去するために 1050 乃至 1150 の熱処理が必要であることが開示されている。

**【特許文献 1】米国特許第 6372609 号**

**【特許文献 2】特開 2000-12864 号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

40

**【0005】**

従来の SOI 基板の製造方法では、SOI 層との接合強度を強固なものとし、SOI 層の表面のダメージ層の改善をするために 1000 以上の高温で熱処理をする必要があった。そのため、液晶パネルの製造に用いられるガラス基板、耐熱温度が 700 程度の基板や、さらに耐熱温度の低いプラスチックに SOI 層を形成することができなかった。仮に水素イオン注入剥離法で SOI 層をガラス基板上に設けたとしても、接合強度を高めるための高温の熱処理を適用することができないために、SOI 層の接合強度が弱いといった問題がある。

**【0006】**

また、可撓性基板は、厚さが薄く撓みやすいため固定されにくく、取り扱いが困難である

50

ため、可撓性を有する基板を用いた半導体装置の歩留まりが低いという問題がある。

#### 【0007】

このような問題点に鑑み、ガラス基板やプラスチックなど可撓性を有する基板を用いた場合にも、実用に耐えうるSOI層を備えたSOI基板を歩留まり高く作製する方法を提供することを目的の一とする。また、そのようなSOI基板を用いた薄型の半導体装置を歩留まり高く作製する方法を提供することを目的の一とする。

#### 【課題を解決するための手段】

#### 【0008】

可撓性を有し且つ絶縁表面を有する基板に、単結晶半導体基板を接合しSOI基板を作製するに際し、接合面の一方若しくは双方を活性化した後、可撓性を有し且つ絶縁表面を有する基板と、単結晶半導体基板とを圧着する。例えば、可撓性を有し且つ絶縁表面を有する基板、または単結晶半導体基板の少なくとも一方の接合面に、原子ビーム若しくはイオンビームを照射する。または、プラズマ照射若しくはラジカル処理を行う。また、可撓性を有し且つ絶縁表面を有する基板、または単結晶半導体基板の少なくとも一方の接合面を、酸素プラズマによる処理や、オゾン水洗浄により、親水化してもよい。このような表面処理により250以上400未満の温度であっても異種材料間の接合を行うことが容易となる。

10

#### 【0009】

また、可撓性を有し且つ絶縁表面を有する基板に、単結晶半導体基板を接合するに際し、接合を行う面の一方若しくは双方に、有機シランを原材料として形成した酸化珪素層を用いる。有機シランガスとしては、珪酸エチル(TEOS)、テトラメチルシラン(化学式Si(CH<sub>3</sub>)<sub>4</sub>)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン、トリスジメチルアミノシラン等のシリコン含有化合物が適用される。すなわち、可撓性を有し且つ絶縁表面を有する基板に単結晶半導体層(SOI層)を接合する構造を有するSOI基板において、接合を形成する面の一方若しくは双方に、平滑面を形成し活性化された表面を有する酸化珪素層を接合面として設ける。

20

#### 【0010】

可撓性を有し且つ絶縁表面を有する基板に接合されるSOI層は、単結晶半導体基板に形成された脆弱領域にて分離・剥離することにより得られる。脆弱領域は、ソースガスとして水素、ヘリウム若しくはフッ素に代表されるハロゲンのガスを用い、プラズマ励起して生成される加速されたイオンを単結晶半導体基板に照射することで形成される。この場合、一の原子から成る複数の質量の異なるイオン又は複数の原子から成る質量の異なるイオンを照射することが好ましい。水素イオンを照射する場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>イオンを含ませると共に、H<sub>3</sub><sup>+</sup>イオンの割合を高めておくことが好ましい。また、ヘリウムをイオン化して照射する場合は、質量分離を行わないイオンドーピングであっても、実質的にHe<sup>+</sup>イオンのみをドーピングすることができる。なお実質的とは、大気成分の元素もイオン化されてわずかにドーピングされることを指している。

30

#### 【0011】

また、可撓性を有し且つ絶縁表面を有する基板に接合されるSOI層は、単結晶半導体基板に形成された脆弱領域にて分離するためには、可撓性を有し且つ絶縁表面を有する基板と単結晶半導体基板を接合する前に、単結晶半導体基板を加熱処理して脆弱領域を脆弱にする。この場合、イオンが気体となって脆弱領域から脱離するのを防ぐため、単結晶半導体基板の表面に圧着部材で圧力を加えながら加熱処理する。または、単結晶半導体基板に絶縁層を形成して加熱処理を行う。

40

#### 【発明の効果】

#### 【0012】

単結晶半導体基板から剥離した単結晶半導体層とベースとなる基板とを接合する前に、単結晶半導体基板を加熱し、加速されたイオンを単結晶半導体基板に照射し単結晶半導体基板の一部を脆弱にした脆弱領域を形成することにより、耐熱性の低い可撓性基板と単結晶

50

半導体基板を接合し、S O I 基板を作製することができる。本構成によれば、プラスチック基板等の耐熱温度が低い基板であっても、接合力が強固な接合部によって基板と接合されたS O I 層を有するS O I 基板を歩留まり高く得ることができる。また、当該S O I 基板を用いた半導体装置を作製することができる。

**【発明を実施するための最良の形態】**

**【0013】**

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態及び実施例の記載内容に限定して解釈されるものではない。

10

**【0014】**

**(実施の形態1)**

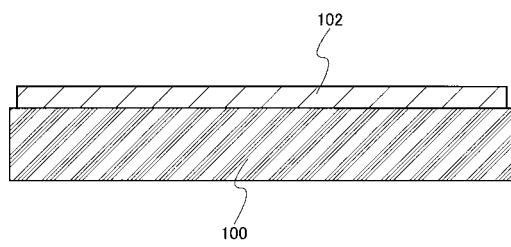

本発明に係るS O I 基板の構成を図1に示す。図1においてベース基板100は、S O I 基板において、S O I 層を設ける基板のことであり、可撓性を有し且つ絶縁表面を有する基板であり、代表的には可撓性を有する絶縁基板、表面に絶縁層が形成された可撓性を有する金属基板等である。可撓性を有する絶縁基板としては、P E T (ポリエチレンテレフタレート)、P E N (ポリエチレンナフタレート)、P E S (ポリエーテルスルホン)、ポリプロピレン、ポリプロピレンサルファイド、ポリカーボネート、ポリエーテルイミド、ポリフェニレンサルファイド、ポリフェニレンオキサイド、ポリサルファン、ポリフタルアミド等からなるプラスチック基板、または繊維質な材料からなる紙がある。

20

**【0015】**

また、可撓性を有する絶縁基板として、プリプレグを用いることで、後に作製されるS O I 基板や半導体装置の点圧、線圧による破壊を防ぐことが可能である。プリプレグの代表例としては、ポリビニルアルコール系繊維、ポリエステル系繊維、ポリアミド系繊維、ポリエチレン系繊維、アラミド系繊維、ポリパラフェニレンベンゾビスオキサゾール繊維、ガラス繊維、または炭素繊維等の繊維体に、エポキシ樹脂、不飽和ポリエステル樹脂、ポリイミド樹脂、フッ素樹脂等のマトリックス樹脂を有機溶剤で希釈した組成物を含浸させた後、乾燥して有機溶剤を揮発させてマトリックス樹脂を半硬化させたものである。

**【0016】**

また、可撓性を有する絶縁基板としては、アルミニノシリケートガラス、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板を用いることができる。

30

**【0017】**

表面に絶縁層が形成された可撓性を有する金属基板としては、酸化珪素層、窒化珪素層、酸化窒化珪素層、窒化アルミニウム層、酸化アルミニウム層等の絶縁層が形成された金属フィルムまたは金属シート等がある。なお、絶縁層は上記羅列した絶縁層に限定されず、適宜適用することができる。

**【0018】**

S O I 層102は単結晶半導体層であり、代表的には単結晶シリコンが適用される。また、水素イオン注入剥離法によって多結晶半導体基板から剥離可能であるシリコンや、水素イオン注入剥離法によって単結晶半導体基板若しくは多結晶半導体基板から剥離可能であるゲルマニウムも適用することができる。その他にも、シリコンゲルマニウム、ガリウムヒ素、インジウムリンなどの化合物半導体による結晶性半導体基板を適用することもできる。

40

**【0019】**

なお、本実施の形態及び実施の形態2以降においては、S O I 層102として代表例として単結晶半導体層を用いて示すが、単結晶半導体基板の代わりに、多結晶半導体基板を用いた場合は、S O I 層102は多結晶半導体層となる。また、単結晶半導体基板の代わりに、結晶性半導体基板を用いた場合は、S O I 層102は結晶性半導体層となる。

**【0020】**

50

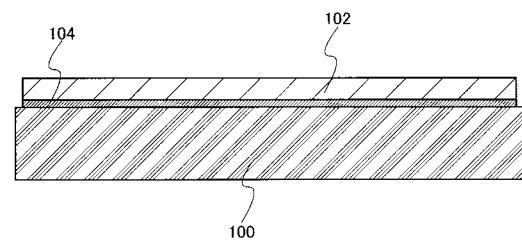

また、図2に示すように、上記ベース基板100とSOI層102の間には、平滑であり活性化された表面を有する接合層（接合界面に形成される層）104を設けててもよい。図2は、SOI層102の表面に、平滑であり活性化された表面を有する接合層104を形成し、ベース基板100及び平滑であり活性化された表面を有する接合層104を接合し作製したSOI基板である。なお、ベース基板100の表面に、平滑であり活性化された表面を有する接合層104を形成し、平滑であり活性化された表面を有する接合層104及びSOI層102を接合しSOI基板を作製してもよい。

#### 【0021】

接合層104としては、酸化珪素層が適している。特に有機シランガスを用いて化学気相成長法により作製される酸化珪素層が好ましい。有機シランガスとしては、硅酸エチル、テトラメチルシラン、テトラメチルシクロテトラシロキサン、オクタメチルシクロテトラシロキサン、ヘキサメチルジシラザン、トリエトキシシラン、トリスジメチルアミノシラン等のシリコン含有化合物を用いることができる。また、接合層104として単結晶半導体基板を高温で加熱処理して形成した熱酸化層や、ケミカルオキサイドを適用することもできる。ケミカルオキサイドは、例えばオゾン含有水でSOI層となる単結晶半導体基板表面を処理することで形成することができる。ケミカルオキサイドは単結晶半導体基板の表面の平坦性を反映して形成されるので好ましい。

10

#### 【0022】

上記平滑であり活性化された表面を有する接合層104は、1nm乃至600nm、好ましくは5nm乃至500nm、更に好ましくは5nm乃至200nmの厚さで設けられる。この厚さであれば、被形成表面（接合を形成する面）の表面荒れを平滑化すると共に、当該層の成長表面の平滑性を確保することが可能である。また、接合層104を設けることによって、接合するベース基板とSOI層との熱歪みを緩和することができる。可撓性を有し絶縁表面を有する基板を用いたベース基板100にSOI層102を接合するに際し、ベース基板100の接合面またはSOI層102の接合面の一方若しくは双方に、酸化珪素層、好ましくは熱酸化層、単結晶半導体基板の表面をオゾン水で処理して形成した酸化珪素層、または有機シランを原材料として形成した酸化珪素層でなる接合層104を設けることで、ベース基板100及びSOI層102を強固に接合することができる。

20

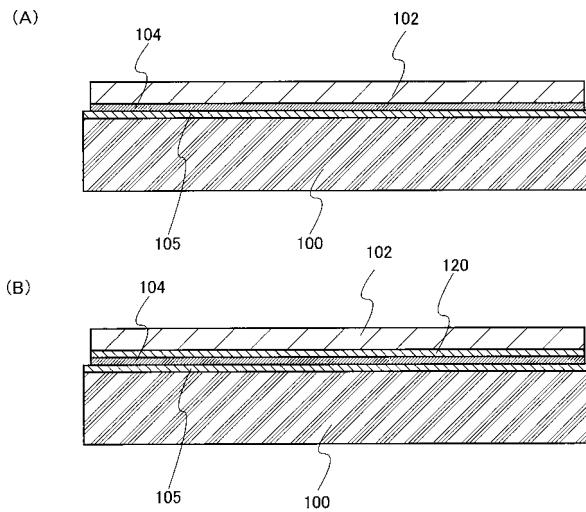

#### 【0023】

図3及び図4は、ベース基板100及びSOI層102の間に少なくともバリア層105及び接合層104を設けた構成を示す。SOI層102をベース基板100に接合した場合に、バリア層105を設けることによって、ベース基板100として用いられる可撓性を有する絶縁基板、可撓性を有する金属基板、絶縁表面を有し可撓性を有する基板から、アルカリ金属若しくはアルカリ土類金属のような可動イオン等の不純物が拡散し、SOI層102が汚染されることを防ぐことができる。バリア層105としては、窒素含有絶縁層が好ましく、代表的には窒化珪素層、窒化酸化珪素層、酸化窒化珪素層、窒化アルミニウム層、窒化酸化アルミニウム層、若しくは酸化窒化アルミニウム層から選ばれた一の層又は複数の層を積層して形成する。例えば、SOI層102側から酸化窒化珪素層、窒化酸化珪素層を積層してバリア層120とすることができる。また、バリア層105としては、エッティングレートの遅い緻密な層を用いることで、さらにバリア機能を高めることができ、エッティングレートの遅い緻密な層としては、上記窒素含有絶縁層、酸化珪素層、酸化窒化珪素層、窒化酸化珪素層、窒化アルミニウム層等を形成することができる。

30

#### 【0024】

なお、ここで酸化窒化珪素層とは、その組成として、窒素よりも酸素の含有量が多いものであって、ラザフォード後方散乱法（RBS：Rutherford Backscattering Spectrometry）及び水素前方散乱法（HFS：Hydrogen Forward Scattering）を用いて測定した場合に、濃度範囲として酸素50～70原子%、窒素が0.5～15原子%、Siが25～35原子%、水素が0.1～10原子%の範囲で含まれるものという。また、窒化酸化珪素層とは、その組成として、酸素よりも窒素の含有量が多いものであって、RBS及びHFSを用いて測定し

40

50

た場合に、濃度範囲として酸素が5～30原子%、窒素が20～55原子%、Siが25～35原子%、水素が10～30原子%の範囲で含まれるものという。但し、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を100原子%としたとき、窒素、酸素、Si及び水素の含有比率が上記の範囲内に含まれるものとする。

#### 【0025】

図3(A)は本発明に係るSOI基板の別の構成である。図3(A)は、接合層104とベース基板100の間にバリア層105を設けた構成を示す。ここでは、ベース基板100にバリア層105を設け、SOI層102表面に接合層104を設け、バリア層105及び接合層104を接合した構成を示す。なお、この代わりに、ベース基板100に接合層104を設け、SOI層102表面にバリア層105を設け、バリア層105及び接合層104を接合した構成とすることができます。さらには、ベース基板100またはSOI層102の一方の表面にバリア層105及び接合層104を順に積層し、ベース基板100またはSOI層102の他方の表面と接合層104を接合した構成とすることができます。

#### 【0026】

図3(B)は、ベース基板100とSOI層102との間に、接合層104及び複数のバリア層105、120を設けた構成を示す。ここでは、ベース基板100にバリア層105、120を設け、SOI層102表面にバリア層120及び接合層104を順に積層し、バリア層105及び接合層104を接合した構成を示す。なお、この代わりに、ベース基板100にバリア層105及び接合層104を順に積層し、SOI層102表面にバリア層120を設け、バリア層120及び接合層104を接合した構成とすることができます。

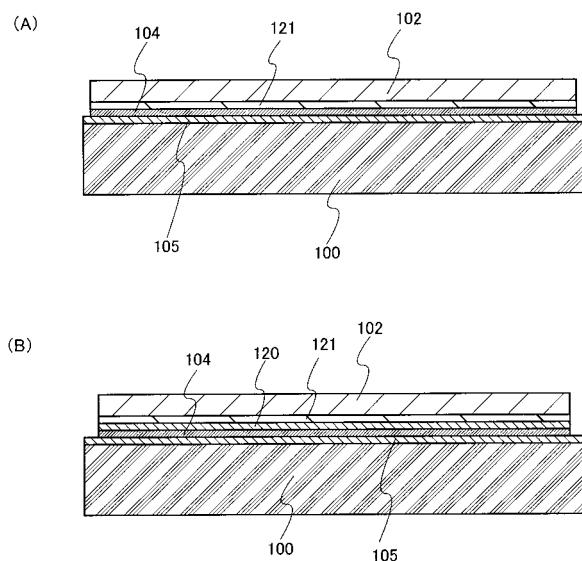

#### 【0027】

図4は、少なくともベース基板100及びSOI層102の間に、バリア層105及び接合層104と共に、絶縁層121を設けた構成を示す。絶縁層121は、SOI層102及び接合層104の間や、接合層104及びバリア層105の間や、ベース基板100及びバリア層105の間に設けることができる。

#### 【0028】

図4(A)は、ベース基板100及びSOI層102の間に、接合層104、バリア層105、及び絶縁層121を設けた構成を示す。ここでは、ベース基板100にバリア層105を設け、SOI層102表面に絶縁層121及び接合層104を順に積層し、バリア層105及び接合層104を接合した構成を示す。なお、この代わりに、ベース基板100にバリア層105及び接合層104を順に積層し、SOI層102表面に絶縁層121を設け、接合層104及び絶縁層121を接合した構成とすることができます。

#### 【0029】

図4(B)は、図4(A)において、ベース基板100表面上のほかに、SOI層102上にもバリア層120を設けた構成を示す。ここでは、ベース基板100にバリア層105を形成し、SOI層102表面に絶縁層121、バリア層120、及び接合層104を順に積層し、バリア層105及び接合層104を接合した構成を示す。なお、この代わりに、ベース基板100にバリア層105及び接合層104を順に積層し、SOI層102表面に絶縁層121及びバリア層120を順に積層し、接合層104及びバリア層120を接合した構成とすることができます。

#### 【0030】

絶縁層121は単結晶半導体基板を高温で加熱処理して形成した熱酸化層が好ましい。また、接合層104と同様に有機シランガスを用いて化学気相成長法により堆積した酸化珪素層を用いても良い。また、絶縁層121としてケミカルオキサイドを適用することもできる。ケミカルオキサイドは、例えばオゾン含有水でSOI層となる単結晶半導体基板表面を処理することで形成することができる。ケミカルオキサイドは単結晶半導体基板の表面の形状を反映して形成されるため、単結晶半導体基板が平坦であるとケミカルオキサイドも平坦になるので好ましい。

**【0031】**

本実施の形態で示すSOI基板は、可撓性を有する基板上にSOI層が接合されているため、可撓性を有する。また、薄型である。

**【0032】****(実施の形態2)**

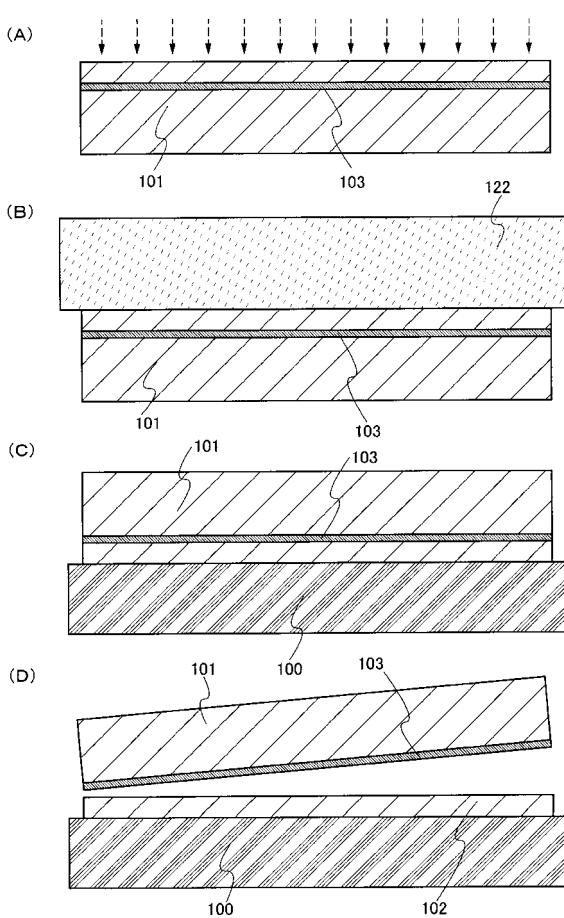

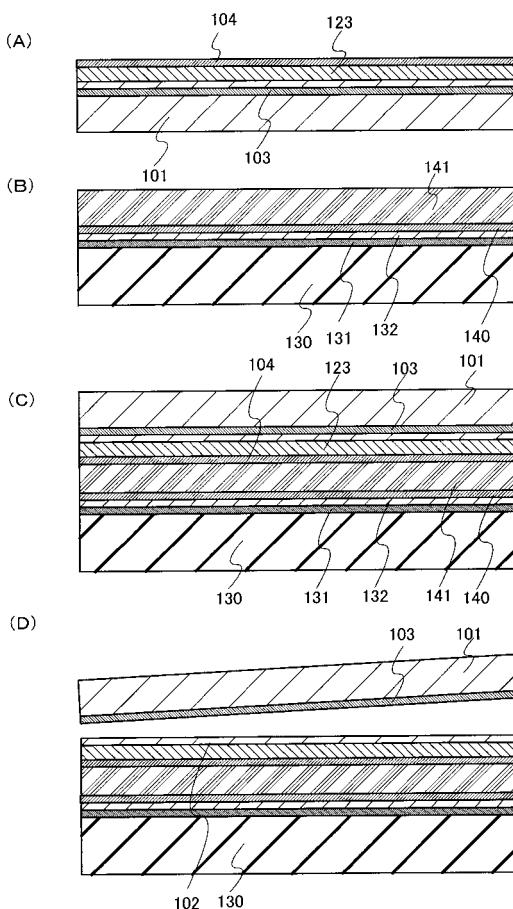

実施の形態1に示すSOI基板の製造方法について図5乃至図8を参照して説明する。

**【0033】**

図5(A)に示す単結晶半導体基板101は清浄化されており、その表面から電界で加速されたイオンを単結晶半導体基板に照射し、単結晶半導体基板の所定の深さに当該イオンの元素を含ませ、イオンドーピング層(具体的には、加速されたイオンの元素を含む脆弱な層のこと)であり、例えば、水素、ヘリウム若しくはフッ素に代表されるハロゲンを含む領域をいう。以下、脆弱領域103という)を形成する。加速されたイオンの照射はベース基板に転置するSOI層の厚さを考慮して行われる。当該SOI層は、5nm乃至500nm、好ましくは10nm乃至200nm、更に好ましくは10nm乃至100nm、更に好ましくは10nm乃至50nmの厚さとする。単結晶半導体基板101にイオンを照射する際の加速電圧はこのような厚さを考慮して設定する。なお、剥離(分離)後にSOI層の表面を研磨または溶融して平坦化するため、剥離(分離)直後のSOI層の厚さは50nm乃至500nmとしておくことが好ましい。

10

**【0034】**

脆弱領域103は、ソースガスとして水素、ヘリウム若しくはフッ素に代表されるハロゲンのガスを用い、プラズマ励起して生成される加速されたイオンを単結晶半導体基板に照射することで形成される。この場合、一の原子から成る複数の質量の異なるイオン又は複数の原子から成る質量の異なるイオンを照射することが好ましい。このようなイオンの照射方法としては、イオンドーピング法、イオン注入法等がある。加速された水素イオンを単結晶半導体基板に照射する場合には、 $H^+$ 、 $H_2^+$ 、 $H_3^+$ イオンを含ませると共に、 $H_3^+$ イオンの割合を高めておくことが好ましい。 $H_3^+$ イオンの割合を高めておくと導入効率を高めることができ、照射時間を短縮することができる。このように $H^+$ 、 $H_2^+$ イオンよりも $H_3^+$ イオンの割合を高くしてイオンを照射すると、 $H_3^+$ イオンの割合を高めないでイオンを照射する場合と比べてより単結晶半導体基板101に水素イオンを多く含ませる構成とすることで、少ないイオンの照射量で、後に行われる脆弱領域103での剥離(分離)を容易に行うことができる。

20

**【0035】**

単結晶半導体基板101に加速されたイオンを照射する場合、単結晶半導体基板の表面に、イオンを高い濃度で照射する必要があり、このため単結晶半導体基板101の表面が粗くなってしまう場合がある。そのため加速されたイオンが照射される面に、酸化珪素層、窒化珪素層、若しくは窒化酸化珪素層などにより単結晶半導体基板101に対する保護層を50nm乃至200nmの厚さで設けておくことで、イオンが照射される面がダメージを受け、平坦性が損なわれるのを防ぐことができるため好ましい。

30

**【0036】**

なお、本明細書においてイオンドーピング法とは、原料ガスから生成されるイオン化したガスを質量分離せず、そのまま電界で加速して対象物に照射し、イオン化したガスの元素を対象物に含ませる方式を指す。イオンドーピング装置を用いると、大面積基板であっても高効率に高ドーズのイオンドーピングを行うことができる。

40

**【0037】**

また、イオンドーピングの加速電圧は、20kV以上100kV以下、好ましくは20kV以上70kV以下とし、ドーズは、 $1 \times 10^{16}$  ions/cm<sup>2</sup>以上 $4 \times 10^{16}$  ions/cm<sup>2</sup>以下 $1 \times 10^{16}$  ions/cm<sup>2</sup>以上 $2.5 \times 10^{16}$  ions/cm<sup>2</sup>以下とすればよい。本実施の形態では、加速電圧80kVで、ドーズを $2 \times 10^{16}$  ions/cm<sup>2</sup>としてイオンドーピングを行う。

**【0038】**

50

次に、図5(B)に示すように、単結晶半導体基板101の表面に圧着部材122を設け、単結晶半導体基板101及び圧着部材122を密着させ加熱し、即ち加熱処理及び加圧処理を行うことで、後の工程で脆弱領域103を劈開面として単結晶半導体基板101をベース基板100から剥離(分離)することを容易とする。なお、ここでの劈開面とは、単結晶半導体基板が分離する領域のことをいい、以下、劈開面を分離領域と示す。加熱処理の温度は、脆弱領域103が分離する温度未満であり、且つ脆弱領域103が脆弱となる温度であることが好ましい。例えば、250以上、好ましくは300以上、400

未満、好ましくは350未満の熱処理を行うことにより、脆弱領域103に形成された微小な空洞の体積変化が起こるが、単結晶半導体基板表面には圧着部材122が設けられているため、単結晶半導体基板の表面は平坦性を保つことができる。この結果、脆弱領域103の微小な空洞の体積変化により、脆弱領域103に歪みが生じ、脆弱領域に沿って脆弱化することが可能となる。加圧処理においては、ベース基板100及び単結晶半導体基板101の耐圧性を考慮して接合面に垂直な方向に圧力が加わるように行う。

#### 【0039】

図5(C)に示すように、ベース基板100と単結晶半導体基板101とを密接させ、この両者を接合させる態様を示す。接合を行う面は、十分に清浄化しておく。そして、ベース基板100及び単結晶半導体基板101を加圧しながら密着させることにより、ベース基板100及び単結晶半導体基板101が接合する。この接合はファン・デル・ワールス力が作用しており、ベース基板100と単結晶半導体基板101とを圧接することで、水素結合によってファン・デル・ワールス力による接合よりも強固な接合を行うことが可能である。

#### 【0040】

良好な接合を行うために、接合を形成する面を活性化することが好ましい。例えば、接合を行う面に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオニンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行う。また、可撓性を有し且つ絶縁表面を有する基板、または単結晶半導体層の少なくとも一方の接合面を、酸素プラズマによる処理や、オゾン水洗浄により、親水化してもよい。このような表面処理により、後の加熱処理の温度が250以上400未満であっても異種材料間の接合強度を向上させることが容易となる。

#### 【0041】

なお、ベース基板100及び単結晶半導体基板101の接合の前に行った加熱処理の代わりに、ベース基板100及び単結晶半導体基板101を接合した後、ベース基板100または単結晶半導体基板101からレーザビームを単結晶半導体基板に照射し、脆弱領域103を加熱してもよい。なお、単結晶半導体基板101側からレーザビームを照射する場合は、赤外光のレーザビームを用いる。この結果、脆弱領域が形成され、当該脆弱領域を分離領域として単結晶半導体基板101をベース基板100から剥離(分離)することができる。

#### 【0042】

図5(D)に示すように、ベース基板100と単結晶半導体基板101を貼り合わせた後、脆弱領域103を分離領域として単結晶半導体基板101をベース基板100から剥離(分離)することで、SOI基板を得ることができる。単結晶半導体基板101の表面はベース基板100と接合しているので、ベース基板100上には単結晶半導体基板101と同じ結晶性を有するSOI層102が残存することとなる。

#### 【0043】

脆弱領域103を分離領域として単結晶半導体基板101をベース基板100から剥離(分離)する前に、剥離(分離)を容易に行うためにきっかけをつくることが好ましい。具体的には、脆弱領域103及びSOI層102の密着性を選択的(部分的)に低下させる前処理を行うことで、剥離(分離)不良が少くなり、さらに歩留まりも向上する。代表的には、ベース基板100または単結晶半導体基板101から脆弱領域103にレーザビ

10

20

30

40

50

ームまたはダイサーで溝を形成する例がある。

**【0044】**

また、単結晶半導体基板101をベース基板100から剥離(分離)する際、ベース基板100または単結晶半導体基板101の少なくとも一方の表面に、光または熱により剥離可能な粘着シートを設け、ベース基板100または単結晶半導体基板101の一方を固定し、他方を引き剥がすことで、さらに剥離(分離)が容易となる。このとき、ベース基板100または単結晶半導体基板101の他方に支持部材を設けることで引き剥がし工程が容易となる。

**【0045】**

なお、剥離(分離)により得られるSOI層は、その表面を平坦化するため、化学的機械的研磨(Chemical Mechanical Polishing: CMP)を行うことが好ましい。また、CMP等の物理的研磨手段を用いず、SOI層の表面にレーザビームを照射して平坦化を行ってもよい。なお、レーザビームを照射する際は、酸素濃度が10ppm以下の窒素雰囲気下で行なうことが好ましい。これは、酸素雰囲気下でレーザビームの照射を行うとSOI層表面が荒れる恐れがあるからである。また、得られたSOI層の薄層化を目的として、CMP等を行ってもよい。

10

**【0046】**

また、図5(B)に示す単結晶半導体基板101の表面に圧着部材122を設ける前に、単結晶半導体基板101表面に接合層104を形成してもよい。また、図5(B)に示す単結晶半導体基板101の表面に圧着部材122を設け、単結晶半導体基板101及び圧着部材122を密着させ加熱した後、単結晶半導体基板101表面に接合層104を形成してもよい。その後、図5(C)に示すように、接合層104及びベース基板100を密接させることで、容易にこの両者を接合させることができる。

20

**【0047】**

本実施の形態により、耐熱性の低い可撓性基板と単結晶半導体基板を接合し、SOI基板を作製することができる。本構成によれば、プラスチック基板等の耐熱温度が低い基板であっても、接合力が強固な接合部によって基板と接合されたSOI層を有するSOI基板を歩留まり高く得ることができる。また、可撓性を有し、薄型であるSOI基板を作製することができる。

**【0048】**

30

(実施の形態3)

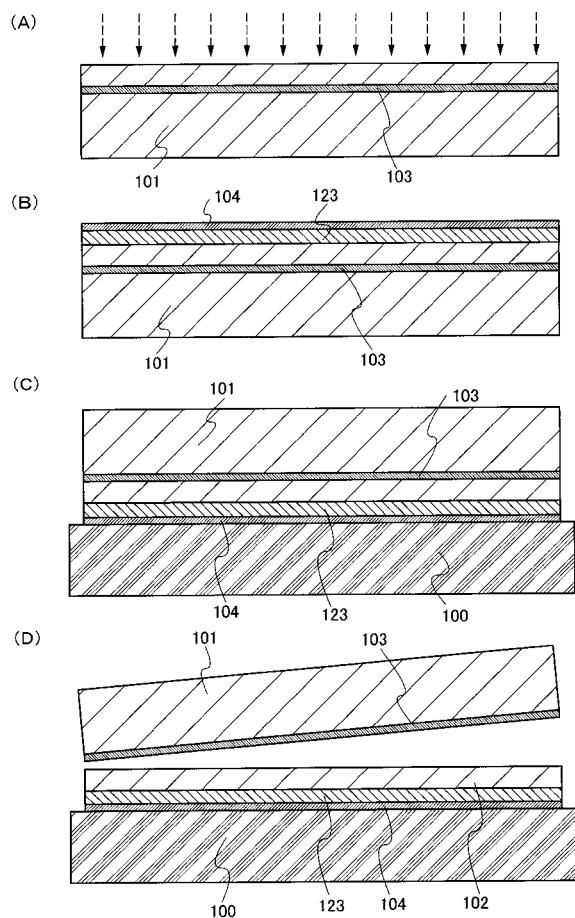

次に、上記実施の形態とは異なるSOI基板の作製方法について、図6を用いて示す。図6では、接合層を用いてベース基板100及び単結晶半導体基板101を接合する形態を示す。また、圧着部材を用いず、ベース基板100及び単結晶半導体基板101を接合する形態を示す。

**【0049】**

図5(A)と同様に、図6(A)に示すように、清浄化された単結晶半導体基板101の表面から電界で加速されたイオンを照射して単結晶半導体基板の所定の深さに当該イオンの元素を含ませ、脆弱領域103を形成する。

**【0050】**

40

次に、図6(B)に示すように、単結晶半導体基板101に少なくともキャップ層123及び接合層104を形成する。ここでは、単結晶半導体基板101の表面にキャップ層123を形成し、キャップ層123上に接合層104を形成する。

**【0051】**

ここでは、接合層104またはキャップ層123の少なくとも一方の厚さが厚い方が好ましい。後の工程で加熱処理を行うことで、脆弱領域103に形成された微小な空洞の体積変化が起こるが、単結晶半導体基板表面にはキャップ層123が設けられており、単結晶半導体基板の表面は平坦性を保つことができるため、その上に設けられる接合層104の平坦性をも保つことができる。この結果、脆弱領域103の微小な空洞の体積変化により、脆弱領域103に歪みが生じ、脆弱領域に沿って脆弱化することが可能となる。特に、

50

キャップ層 123 の厚さを厚くすることで、加熱処理の際、単結晶半導体基板 101 の表面に対して垂直方向に力が加わるため単結晶半導体基板の照射面の平坦性を保つつ、脆弱領域を形成する効果がある。

#### 【0052】

キャップ層 123 としては、窒素含有絶縁層や酸化珪素層の単層や積層とすることができます。なお、キャップ層 123 の一部または全部を窒素含有絶縁層で形成することで、キャップ層 123 はバリア層としても機能するため好ましい。

#### 【0053】

次に、加熱して、脆弱領域 103 の微小な空洞の体積を変化させる。この結果、後の工程で脆弱領域を分離領域として単結晶半導体基板 101 をベース基板 100 から剥離（分離）することを容易とする。加熱処理の温度は、脆弱領域 103 が剥離（分離）する温度未満であり、且つ脆弱領域 103 が形成される温度以上であることが好ましい。例えば、250 以上、好ましくは 300 以上、400 未満、好ましくは 350 未満の熱処理が好ましい。10

#### 【0054】

図 6 (C) は、キャップ層 123 及び接合層 104 が形成された単結晶半導体基板 101 の接合層 104 とベース基板 100 を密着させて接合する工程を示している。単結晶半導体基板 101 上の接合層 104 とベース基板 100 を密着させることにより接合する。

#### 【0055】

良好な接合を行うために、接合層 104 またはベース基板 100 の少なくとも一方の表面を活性化しておいても良い。例えば、接合を行う面に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行う。また、ベース基板 100、または接合層 104 の少なくとも一方の接合面を、酸素プラズマによる処理や、オゾン水洗浄により、親水化してもよい。このような表面処理により 400 未満の温度であっても異種材料間の接合を行うことが容易となる。20

#### 【0056】

その後、図 6 (D) で示すように単結晶半導体基板 101 を剥離（分離）することで、SOI 基板を得ることができる。なお、剥離（分離）により得られる SOI 層は、その表面を平坦化することが好ましい。また、得られた SOI 層の薄層化を目的として、CMP 等を行ってもよい。また、脆弱領域 103 を分離領域として単結晶半導体基板 101 をベース基板 100 から剥離（分離）する前に、剥離（分離）を容易に行うためにきっかけをつくってもよい。さらには、単結晶半導体基板 101 をベース基板 100 から剥離（分離）する際、ベース基板 100 または単結晶半導体基板 101 の少なくとも一方の表面に光または熱により剥離可能な粘着シートを設け、ベース基板 100 または単結晶半導体基板 101 の一方を固定し、他方を引き剥がすことで、さらに剥離（分離）が容易となる。このとき、ベース基板 100 または単結晶半導体基板 101 の他方に支持部材を設けることで引き剥がし工程が容易となる。30

#### 【0057】

なお、ベース基板 100 及び単結晶半導体基板 101 の接合の前に行った加熱処理の代わりに、ベース基板 100 及び単結晶半導体基板 101 を接合した後、ベース基板 100 または単結晶半導体基板 101 からレーザビームを単結晶半導体基板に照射し、脆弱領域 103 を加熱してもよい。なお、単結晶半導体基板 101 側からレーザビームを照射する場合は、単結晶半導体基板が吸収する波長のレーザビーム、代表的には赤外光のレーザビームを用いる。この結果、脆弱領域を分離領域として単結晶半導体基板 101 をベース基板 100 から剥離（分離）することができる。40

#### 【0058】

本実施の形態により、耐熱性の低い可撓性基板と単結晶半導体基板を接合し、SOI 基板を作製することができる。本構成によれば、プラスチック基板等の耐熱温度が低い基板で50

あっても、接合力が強固な接合部によって基板と接合された S O I 層を有する S O I 基板を歩留まり高く得ることができる。また、可撓性を有し、薄型である S O I 基板を作製することができる。

#### 【 0 0 5 9 】

##### ( 実施の形態 4 )

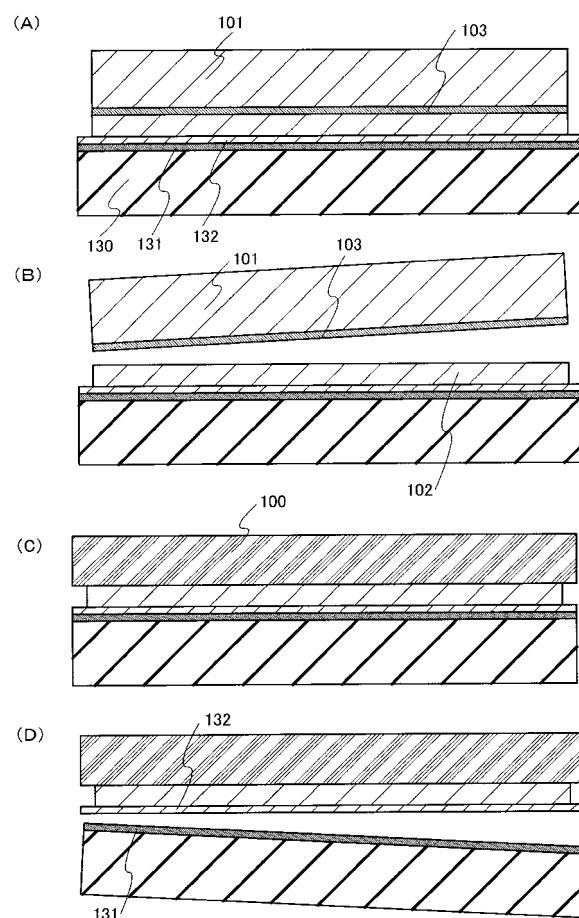

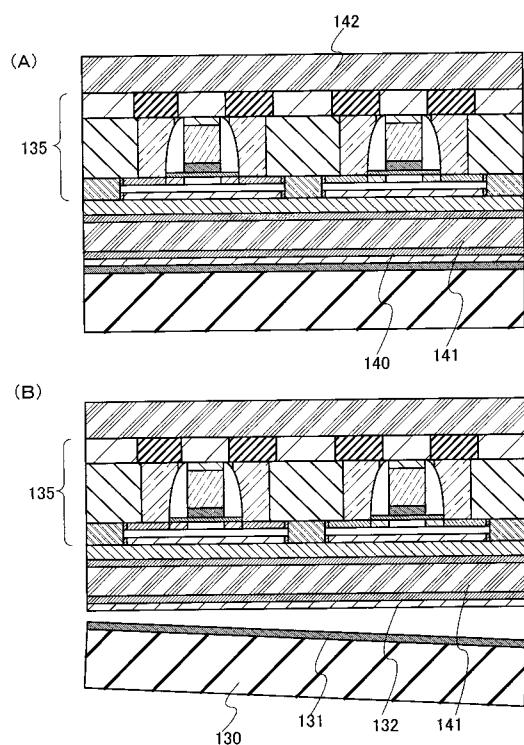

次に、上記実施の形態とは異なる S O I 基板の作製方法について、図 7 を用いて示す。ここでは、支持基板上に剥離層を形成し、剥離層上に S O I 層を形成し、 S O I 層上にベース基板を貼り付けた後、支持基板からベース基板を剥離して、 S O I 基板を作製する。

#### 【 0 0 6 0 】

図 7 ( A ) に示すように、支持基板 130 上に剥離層 131 を形成し、剥離層 131 上に絶縁層 132 を形成する。ここでは、支持基板 130 としては、剥離層を形成するための基板であり、脆弱領域に亀裂を生じさせる加熱処理温度（代表的には、 400 乃至 600 ）に耐えうる耐熱性を有する基板が好ましく、代表的には、ガラス基板、石英基板、セラミック基板、金属基板、シリコンウエハー等を用いることができる。

#### 【 0 0 6 1 】

剥離層 131 としては、スパッタリング法やプラズマ C V D 法、塗布法、印刷法等により、タンゲステン、モリブデン、チタン、タンタル、ニオブ、ニッケル、コバルト、ジルコニアム、亜鉛、ルテニウム、ロジウム、パラジウム、オスミウム、イリジウム、及び珪素の中から選択された元素、又は元素を主成分とする合金材料、又は元素を主成分とする化合物材料からなる層を、単層または複数の層を積層させて形成する。剥離層 131 として珪素を含む層を形成する場合、珪素を含む層の結晶構造は、非晶質、微結晶、多結晶のいずれの場合でもよい。ここでは、塗布法は、溶液を被処理物上に吐出させて形成する方法であり、例えばスピンドルコーティング法や液滴吐出法を含む。また、液滴吐出法とは微粒子を含む組成物の液滴を微細な孔から吐出して所定の形状のパターンを形成する方法である。

#### 【 0 0 6 2 】

剥離層 131 が单層構造の場合、好ましくは、タンゲステン、モリブデン、又はタンゲステンとモリブデンの混合物を含む層を形成する。又は、タンゲステンの酸化物若しくは酸化窒化物を含む層、モリブデンの酸化物若しくは酸化窒化物を含む層、又はタンゲステンとモリブデンの混合物の酸化物若しくは酸化窒化物を含む層を形成する。なお、タンゲステンとモリブデンの混合物とは、例えば、タンゲステンとモリブデンの合金に相当する。

#### 【 0 0 6 3 】

剥離層 131 が積層構造の場合、好ましくは、1 層目として金属層を形成し、2 層目として金属酸化物層を形成する。代表的には、1 層目としてタンゲステン、モリブデン、又はタンゲステンとモリブデンの混合物を含む層を形成し、2 層目として、タンゲステン、モリブデン、又はタンゲステンとモリブデンの混合物の酸化物、タンゲステン、モリブデン、又はタンゲステンとモリブデンの混合物の窒化物、タンゲステン、モリブデン、又はタンゲステンとモリブデンの混合物の酸化窒化物、又はタンゲステン、モリブデン、又はタンゲステンとモリブデンの混合物の窒化酸化物を含む層を形成する。

#### 【 0 0 6 4 】

剥離層 131 として、1 層目として金属層、2 層目として金属酸化物層の積層構造を形成する場合、金属層、例えばタンゲステンを含む層を形成し、その上層に酸化物で形成される絶縁層 132 、例えば酸化珪素層を形成することで、タンゲステンを含む層と絶縁層との界面に、金属酸化物層、例えばタンゲステンの酸化物を含む層が形成されることを活用してもよい。さらには、金属層の表面を、熱酸化処理、酸素プラズマ処理、オゾン水等の酸化力の強い溶液での処理等を行って金属酸化物層を形成してもよい。

#### 【 0 0 6 5 】

さらには、剥離層 131 として、1 層目として金属層、2 層目として金属窒化物層、金属酸化窒化物層を形成してもよい。代表的には、1 層目としてタンゲステンを含む層を形成

10

20

30

40

50

した後、2層目として、窒化タンゲステン層、酸化窒化タンゲステン層を形成すればよい。

#### 【0066】

絶縁層132としては、スパッタリング法やプラズマCVD法、塗布法、印刷法等により、無機化合物を用いて単層又は多層で形成する。無機化合物の代表例としては、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素等がある。なお、下地層として機能する絶縁層132に、窒化珪素、窒化酸化珪素、酸化窒化珪素等を用いることにより、外部から後に形成される素子層へ水分や、酸素等の気体が侵入することを防止することができる。

#### 【0067】

さらには、絶縁層132を積層構造としても良い。例えば、無機化合物を用いて積層してもよく、代表的には、酸化珪素、窒化酸化珪素、窒化珪素、または酸化窒化珪素の2つ以上を積層して形成しても良い。

#### 【0068】

次に、実施の形態2または3に示す工程により脆弱化された脆弱領域103を有する単結晶半導体基板101と、絶縁層132とを密着させて接合する。

#### 【0069】

良好な接合を行うために、絶縁層132または単結晶半導体基板101の少なくとも一方の表面を活性化しておいても良い。例えば、接合を行う面に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行う。また、絶縁層132、または単結晶半導体基板の少なくとも一方の接合面を、酸素プラズマによる処理や、オゾン水洗浄により、親水化してもよい。このような表面処理により250以上400未満の温度であっても異種材料間の接合を行なうことが容易となる。

#### 【0070】

図7(B)に示すように、加熱処理、さらには加圧処理を行うことで、脆弱領域103を分離領域として単結晶半導体基板101を支持基板130から剥離(分離)する。加熱処理の温度は、支持基板130の耐熱温度以下であることが好ましい。例えば、400乃至600の熱処理を行うことにより、脆弱領域103に形成された微小な空洞の体積変化が起こり、脆弱領域103に沿って分離することが可能となる。

#### 【0071】

このとき、加熱処理の代わりに、単結晶半導体基板101からレーザビームを照射して、脆弱領域103に形成された微小な空洞の体積変化を行っても良い。レーザビームとしては、単結晶半導体基板を透過し、脆弱領域103に含まれる元素に吸収される波長を用いることが好ましく、代表的には赤外光を用いることができる。

#### 【0072】

単結晶半導体基板を剥離(分離)した後、SOI層の表面を平坦化することが好ましい。また、得られたSOI層の薄層化を目的として、CMP等を行ってもよい。また、脆弱領域103を分離領域として単結晶半導体基板101を支持基板130から剥離(分離)する前に、剥離(分離)を容易に行なうためにきっかけをつくってもよい。さらには、単結晶半導体基板101を支持基板130から剥離(分離)する際、支持基板130または単結晶半導体基板101の少なくとも一方の表面に、光または熱により剥離可能な粘着シートを設け、支持基板130または単結晶半導体基板101の一方を固定し、他方を引き剥がすことで、さらに剥離(分離)が容易となる。このとき、支持基板130または単結晶半導体基板101の他方に支持部材を設けることで引き剥がし工程が容易となる。

#### 【0073】

次に、図7(C)に示すように、SOI層102にベース基板100を熱圧着することにより、SOI層102にベース基板100を固着させることができる。また、SOI層102に接着材(図示しない)を用いてベース基板100を固着することができる。また、実施の形態2に示すように、SOI層102とベース基板100を密着させて、接合して

10

20

30

40

50

もよい。

**【0074】**

次に、図7(D)に示すように、支持基板130からSOI層102が固着されたベース基板100を物理的手段により剥離する。物理的手段とは、力学的手段または機械的手段を指し、何らかの力学的エネルギー(機械的エネルギー)を変化させる手段をしており、その手段は、代表的には機械的な力を加えること(例えば人間の手や把持具で引き剥がす処理や、ローラーを回転させながら分離する処理)である。このとき、ベース基板100または支持基板130の少なくとも一方の表面に、光または熱により剥離可能な粘着シートを設けると、さらに剥離が容易となる。

**【0075】**

また、剥離層131及び絶縁層132の界面に液体を浸透させて支持基板130からベース基板100を剥離してもよい。

**【0076】**

ここでは、剥離層131及び絶縁層132の界面、剥離層131、または支持基板130及び剥離層131の界面のいずれかで剥離が生じ、支持基板130から素子層を剥離することができる。

**【0077】**

なお、上記剥離工程の前に、剥離を容易に行うために、剥離層131にきっかけをつくってもよい。さらには、単結晶半導体基板101を支持基板130から剥離する際、支持基板130または単結晶半導体基板101の少なくとも一方の表面に、光または熱により剥離可能な粘着シートを設け、ベース基板100または支持基板130の一方を固定し、他方を引き剥がすことで、さらに剥離が容易となる。このとき、支持基板130または単結晶半導体基板101の他方に支持部材を設けることで引き剥がし工程が容易となる。

**【0078】**

この後、SOI層102表面に接合される絶縁層132を除去してもよい。以上の工程により、SOI基板を作製することができる。本形態によれば、脆弱領域が形成された単結晶半導体基板を加熱してSOI層を剥離した後、当該SOI層にベース基板を固着する。また、ハンドリングのしやすい支持基板上に一旦SOI層を保持した後、当該SOI層にベース基板を固着し、支持基板からSOI層を剥離する。このため、耐熱性の低いベース基板上にSOI層が設けられたSOI基板を歩留まり高く作製することができる。

**【0079】**

本実施の形態により、耐熱性の低い可撓性基板と単結晶半導体基板を接合し、SOI基板を作製することができる。本構成によれば、プラスチック基板等の耐熱温度が低い基板であっても、接着力が強固な接合部によって基板と接合されたSOI層を有するSOI基板を歩留まり高く得ることができる。また、支持基板は可撓性を有する基板と比較して扱いやすいため、作製工程におけるハンドリングがしやすく、歩留まりを高めることができる。また、可撓性を有し、薄型であるSOI基板を作製することができる。

**【0080】**

(実施の形態5)

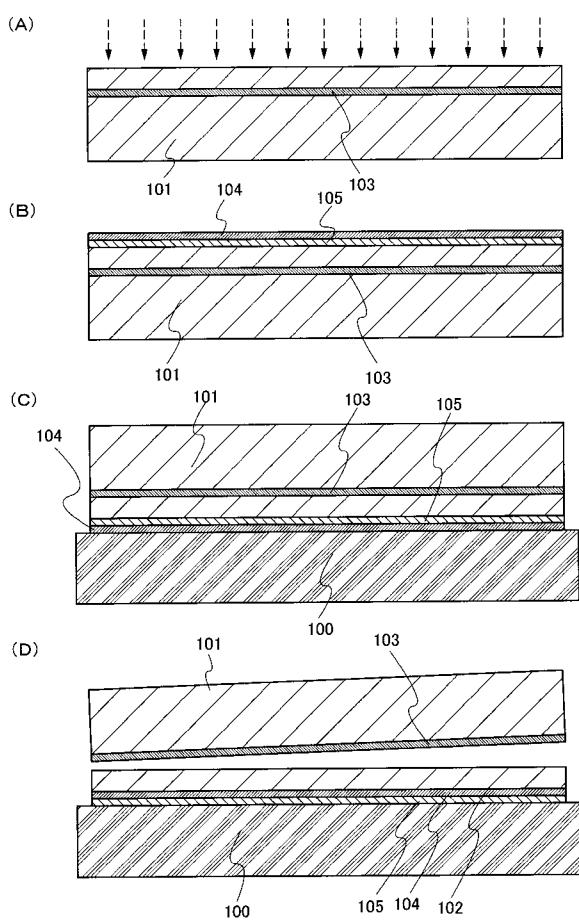

次に、上記実施の形態とは異なるSOI基板の作製方法について、図8を用いて示す。ここでは、ベース基板100として、耐熱温度が700℃以下であるベース基板100を用いてSOI基板を作製する。

**【0081】**

図5(A)と同様に、図8(A)に示すように、清浄化された単結晶半導体基板101に電界で加速されたイオンを照射し単結晶半導体基板の所定の深さに含ませ、脆弱領域103を形成する。

**【0082】**

次に、図8(B)に示すように、単結晶半導体基板101に少なくとも接合層104を形成する。ここでは、単結晶半導体基板101の表面にバリア層105を形成し、バリア層105上に接合層104を形成する。

10

20

30

40

50

**【 0 0 8 3 】**

バリア層 105 としては、少なくとも窒素含有絶縁層を含むことが好ましい。窒化含有絶縁層は、代表的には窒化珪素層、窒化酸化珪素層、酸化窒化珪素層、窒化アルミニウム層、窒化酸化アルミニウム層、若しくは酸化窒化アルミニウム層から選ばれた一又は複数の層を積層して形成する。例えば、単結晶半導体基板 101 側から酸化窒化珪素層、窒化酸化珪素層を積層してバリア層 105 とすることができます。バリア層 105 は、プラズマ CVD 法、スパッタリング法等を用いて形成することができる。

**【 0 0 8 4 】**

図 8 (C) は、単結晶半導体基板 101 の接合層 104 とベース基板 100 とを密着させて接合を行う工程を示している。単結晶半導体基板 101 上の接合層 104 とベース基板 100 を密着させることで接合する。ここでは、ベース基板 100 の耐熱温度が 700 以下であることが好ましく、代表的には、可撓性を有するガラス基板、可撓性を有し且つ絶縁層を有する金属フィルム等を用いることができる。このような耐熱性を有することで、脆弱領域 103 に沿って分離することが可能とするための加熱処理を行うことができる。

10

**【 0 0 8 5 】**

良好な接合を行うために、ベース基板 100 または接合層 104 の少なくとも一方の表面を活性化しておいても良い。例えば、接合を行う面に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行う。また、可撓性を有し且つ絶縁表面を有する基板、または単結晶半導体基板の少なくとも一方の接合面を、酸素プラズマによる処理や、オゾン水洗浄により、親水化してもよい。このような表面処理により 250 以上 400 未満の温度であっても異種材料間の接合を行うことが容易となる。

20

**【 0 0 8 6 】**

その後、加熱処理、さらには加圧処理を行うことで、図 8 (D) で示すように、脆弱領域 103 を分離領域として単結晶半導体基板 101 をベース基板 100 から剥離(分離)することができる。加熱処理の温度は、ベース基板 100 の耐熱温度以下であることが好ましい。例えば、400 乃至 600 の熱処理を行うことにより、脆弱領域 103 に形成された微小な空洞の体積変化が起こり、脆弱領域 103 に沿って分離することが可能となる。加圧処理においては、ベース基板 100 及び単結晶半導体基板 101 の耐圧性を考慮して、接合面に垂直な方向に圧力が加わるように行う。

30

**【 0 0 8 7 】**

このとき、加熱処理の代わりに、単結晶半導体基板 101 からレーザビームを照射して、脆弱領域 103 に形成された微小な空洞の体積変化を行っても良い。レーザビームとしては、単結晶半導体基板を透過し、脆弱領域 103 に含まれる元素に吸収される波長を用いることが好ましく、代表的には赤外光を用いることができる。

**【 0 0 8 8 】**

また、加熱処理の代わりに、ベース基板 100 及び単結晶半導体基板 101 を接合した後、ベース基板 100 からレーザビームを単結晶半導体基板に照射し、脆弱領域 103 を加熱してもよい。この結果、脆弱領域を分離領域として単結晶半導体基板 101 をベース基板 100 から剥離(分離)することができる。

40

**【 0 0 8 9 】**

なお、剥離(分離)により得られる SOI 層は、その表面を平坦化することが好ましい。また、得られた SOI 層の薄層化を目的として、CMP 等を行ってもよい。また、脆弱領域 103 を分離領域として単結晶半導体基板 101 をベース基板 100 から剥離(分離)する前に、剥離(分離)を容易に行うためにきっかけをつくってもよい。さらには、単結晶半導体基板 101 をベース基板 100 から剥離(分離)する際、ベース基板 100 または単結晶半導体基板 101 の少なくとも一方の表面上に光または熱により剥離可能な粘着シートを設け、ベース基板 100 または単結晶半導体基板 101 の一方を固定し、他方を引

50

き剥がすことで、さらに剥離（分離）が容易となる。このとき、ベース基板 100 または単結晶半導体基板 101 の他方に支持部材を設けることで引き剥がし工程が容易となる。

#### 【0090】

このように、本形態によれば、ガラス基板等の耐熱温度が 700 以下のベース基板 100 であっても、ベース基板との接合部の接合力が強固な SOI 層 102 を得ることができる。ベース基板 100 として、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスの如き無アルカリガラスと呼ばれる電子工業用に使われる各種ガラス基板を適用することが可能となる。すなわち、一辺が 1 メートルを超える基板上に単結晶半導体層を形成することができる。このような大面積基板を使って液晶ディスプレイのような表示装置のみならず、半導体集積回路を製造することができる。

10

#### 【0091】

また、本実施の形態の半導体装置は、可撓性を有し且つ絶縁表面を有する支持基板に接合された単結晶半導体層によって集積回路が形成することで、処理速度の高速化、及び低消費電力化を図った半導体装置を作製することができる。また、可撓性を有し、薄型である半導体装置を作製することができる。

#### 【0092】

##### (実施の形態 6)

次に、上記実施の形態 1 乃至 5 に示す SOI 基板を用いた半導体装置について図 9 と図 10 を参照して説明する。ここでは、図 6 及び図 8 に示すように、接合層 104 を用いて単結晶半導体基板とベース基板を接合した SOI 基板を用いて半導体装置を作製した形態を示すが、図 5 及び図 7 に示すように、接合層を用いず単結晶半導体基板及びベース基板を接合した SOI 基板を用いることができる。また、SOI 基板のベース基板に支持基板を貼り付けてもいい。また、SOI 基板を保持する保持部材によって SOI 基板を保持することで、撓みやすい可撓性基板でも歩留まり高く半導体装置を作製することができる。保持部材としては、ローラー、把持具等がある。

20

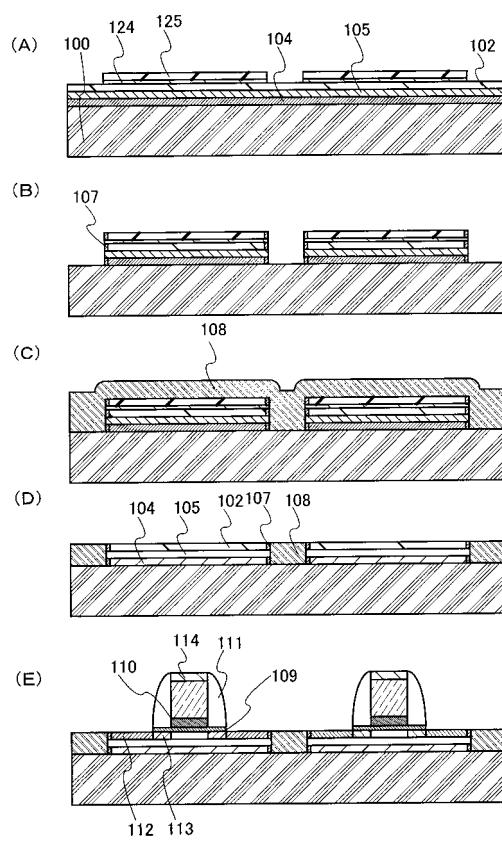

#### 【0093】

図 9 (A)において、ベース基板 100 に接合層 104 及びバリア層 105 を介して SOI 層 102 が設けられている。SOI 層 102 上には、素子形成領域に合わせて窒化珪素層 124、酸化珪素層 125 を形成する。酸化珪素層 125 は、素子分離のために SOI 層 102 をエッチングするときのハードマスクとして用いる。窒化珪素層 124 はエッチングストッパーとして用いる。

30

#### 【0094】

SOI 層 102 の厚さは 5 nm 乃至 500 nm、好ましくは 10 nm 乃至 200 nm とする。SOI 層 102 の厚さは、図 5 で説明した脆弱領域 103 の深さを制御することにより適宜設定できる。SOI 層 102 にはしきい値電圧を制御するために、硼素、アルミニウム、ガリウムなどの p 型不純物を添加する。例えば、p 型不純物として硼素を  $5 \times 10^{16} \text{ cm}^{-3}$  以上  $1 \times 10^{18} \text{ cm}^{-3}$  以下の濃度で添加すれば良い。

#### 【0095】

図 9 (B) は、酸化珪素層 125 をマスクとして SOI 層 102、接合層 104 をエッチングする工程である。次に、SOI 層 102 及び接合層 104 の露出した端面に対してプラズマ処理を行うことにより窒化する。この窒化処理により、少なくとも SOI 層 102 の周辺端部には窒化珪素層 107 が形成される。窒化珪素層 107 は絶縁性であり、SOI 層 102 の端面でのリーク電流が流れるのを防止する効果がある。また、耐酸化作用があるので、SOI 層 102 とバリア層 105 との間に、端面から酸化層が成長してバーズピークが形成されるのを防ぐことができる。

40

#### 【0096】

図 9 (C) は、素子分離絶縁層 108 を堆積する工程である。素子分離絶縁層 108 には、TEOS を用いて化学気相成長法で堆積した酸化珪素膜を用いる。素子分離絶縁層 108 は SOI 層 102 が埋め込まれるように厚く堆積する。

#### 【0097】

50

図9(D)は窒化珪素層124が露出するまで素子分離絶縁層108を除去する工程を示している。この除去工程は、ドライエッティングによって行うこともできるし、化学的機械研磨処理によって行っても良い。窒化珪素層124はエッティングストッパーとなる。素子分離絶縁層108はSOI層102の間に埋め込まれるように残存する。窒化珪素層124はその後除去する。

#### 【0098】

図9(E)において、SOI層102が露出した後、ゲート絶縁層109、ゲート電極110、サイドウォール絶縁層111を形成し、第1不純物領域112、第2不純物領域113を形成する。絶縁層114は窒化珪素層で形成し、ゲート電極110をエッティングするときのハードマスクとして用いる。

10

#### 【0099】

図10(A)において、層間絶縁層115を形成する。層間絶縁層115はBPSG(Boron Phosphorus Silicon Glass)層を形成してリフローにより平坦化させる。また、TEOSを用いて酸化珪素層を形成し化学的機械研磨処理によって平坦化しても良い。平坦化処理においてゲート電極110上の絶縁層114はエッティングストッパーとして機能する。層間絶縁層115にはコンタクトホール116を形成する。コンタクトホール116は、サイドウォール絶縁層111を利用してセルファーラインコンタクトの構成となっている。

#### 【0100】

その後、図10(B)で示すように、六フッ化タンゲステンを用い、CVD法でコンタクトプラグ117を形成する。さらに絶縁層118を形成し、コンタクトプラグ117に合わせて開口を形成して配線119を設ける。配線119はアルミニウム若しくはアルミニウム合金で形成し、上層と下層にはバリアメタルとしてモリブデン、クロム、チタンなどの金属層を形成する。

20

#### 【0101】

ここでは、SOI層102から絶縁層118及び配線119までの積層体を素子層135と示す。

#### 【0102】

この後、素子層135に複数の半導体装置が含まれる場合、素子層135及びベース基板100を分断して、複数の半導体装置を切り出してもよい。このような工程により、複数の半導体装置を作製することができる。

30

#### 【0103】

このように、ベース基板100に接合されたSOI層102を用いて半導体素子、代表的には電界効果トランジスタを作製することができる。本形態に係るSOI層102は、結晶方位が一定の単結晶半導体であるため、均一で高性能な電界効果トランジスタを得ることができる。すなわち、閾値電圧や移動度などトランジスタ特性として重要な特性値の不均一性を抑制し、高移動化などの高性能化を達成することができる。さらには、ベース基板100及びSOI層102の間にバリア層105が設けられているため、ベース基板からの不純物がSOI層に侵入することを防ぐことが可能であるため、素子層に形成されるトランジスタの特性ばらつきを抑えることができる。また、可撓性を有し、薄型である半導体装置を作製することができる。

40

#### 【0104】

##### (実施の形態7)

次に、上記実施の形態1乃至5に示すSOI基板を用いた半導体装置の作製方法について図11及び図12を参照して説明する。ここでは、図6及び図8に示すように、接合層104を用いて単結晶半導体基板とベース基板を接合したSOI基板を用いて半導体装置を作製した形態を示すが、図5及び図7に示すように、接合層を用いず単結晶半導体基板及びベース基板を接合したSOI基板を用いることができる。また、SOI基板のベース基板に支持基板を貼り付けてもいい。また、SOI基板を保持する保持部材によってSOI基板を保持することで、撓みやすい可撓性基板でも歩留まり高く半導体装置を作製するこ

50

とができる。保持部材としては、ローラー、把持具等がある。

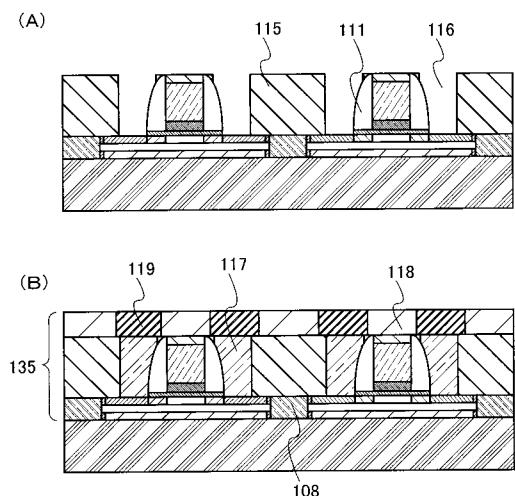

**【0105】**

図6(A)と同様に、図11(A)に示すように、単結晶半導体基板101にその表面から電界で加速されたイオンを照射し単結晶半導体基板の所定の深さに含ませ、脆弱領域103を形成する。次に、単結晶半導体基板101の表面にキャップ層123及び接合層104を順に積層する。この後、加熱して脆弱領域103をさらに脆弱化する。また、キャップ層123の代わりに、実施の形態2に示すように、接合層104に圧着部材を設けた後、加熱して、脆弱領域103をさらに脆弱化してもよい。

**【0106】**

図11(B)は、支持基板130上に形成された絶縁層132と単結晶半導体基板101の接合層104の表面とを密接させ、この両者を接合させる態様を示す。

10

**【0107】**

支持基板130上に剥離層131を形成し、剥離層131上に絶縁層132を形成する。次に、支持基板130上に形成される絶縁層132と単結晶半導体基板101表面に形成される接合層104を密着させ、絶縁層132及び接合層104を接合する。この接合はファン・デル・ワールス力が作用しており、支持基板130と単結晶半導体基板101とを圧接することで水素結合により強固な接合を行うことが可能である。

**【0108】**

さらに、良好な接合を行うために、表面を活性化しておいても良い。例えば、接合を行う面に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行う。このような表面処理により250以上400未満の温度であっても異種材料間の接合を行うことが容易となる。

20

**【0109】**

図11(C)において、支持基板130と単結晶半導体基板101を貼り合わせた後、単結晶半導体基板101を400乃至600で加熱処理し、脆弱領域103に亀裂を生じさせ、脆弱領域103を分離領域として単結晶半導体基板101を支持基板130から剥離(分離)する。接合層104は支持基板130と接合しているので、支持基板130上には単結晶半導体基板101と同じ結晶性を有するSOI層102が残存することとなる。

30

**【0110】**

なお、上記加熱処理の代わりに、支持基板130及び単結晶半導体基板101を接合した後、支持基板130からレーザビームを単結晶半導体基板に照射し、脆弱領域103を加熱してもよい。この結果、脆弱領域を分離領域として単結晶半導体基板101を支持基板130から剥離(分離)することができる。

**【0111】**

この後、SOI層102の表面を平坦化することが好ましい。平坦化方法としては、CMPを用いることができる。または、SOI層102の表面にレーザビームを照射し、表面を溶融して平坦化することができる。

40

**【0112】**

次に、図9及び図10の工程を経て、SOI層102を用いてトランジスタを含む素子層135を形成する。次に、素子層135上にベース基板136を設ける。ベース基板136及び素子層135を熱圧着することにより、素子層135にベース基板136を固定させることができる。また、素子層135に接着材(図示しない)を用いてベース基板136を固定することができる。(図11(D)参照)。ベース基板136としては、上記ベース基板100の代表例に列挙したものを使用することができる。

**【0113】**

この後、後の剥離工程を容易に行うために、ベース基板136から、素子層135及び剥離層131にレーザビームを照射して、溝を形成してもよい。溝を形成するために照射す

50

るレーザビームとしては、剥離層 131、または素子層 135 を構成する層のいずれかが吸収する波長を有するレーザビームが好ましく、代表的には、紫外領域、可視領域、又は赤外領域のレーザビームを適宜選択して照射する。

#### 【 0 1 1 4 】

次に、図 12 (A) に示すように、支持基板 130 から素子層 135 を物理的手段により剥離する。または、剥離層 131 及び絶縁層 132 の界面に液体を浸透させて支持基板 130 から素子層 135 を剥離する。

#### 【 0 1 1 5 】

ここでは、剥離層 131 及び絶縁層 132 の界面、剥離層 131、または支持基板 130 及び剥離層 131 の界面のいずれかで剥離が生じ、支持基板 130 から素子層 135 を剥離することができる。10

#### 【 0 1 1 6 】

なお、素子層 135 及びベース基板 136 を支持基板 130 から剥離する際、支持基板 130 またはベース基板 136 の少なくとも一方の表面に光または熱により剥離可能な粘着シートを設け、支持基板 130 またはベース基板 136 の一方を固定し、他方を引き剥がすことによって、さらに剥離が容易となる。このとき、支持基板 130 またはベース基板 136 の他方に支持部材を設けることで引き剥がし工程が容易となる。

#### 【 0 1 1 7 】

次に、図 12 (B) に示すように、絶縁層 132 に可撓性基板 137 を固着させる。可撓性基板 137 の材料及び固着方法はベース基板 136 と同様のものを適用することができる。20

#### 【 0 1 1 8 】

この後、素子層 135 に複数の半導体装置が含まれる場合、素子層 135、ベース基板 136 及び可撓性基板 137 を分断して、複数の半導体装置を切り出してもよい。このような工程により、複数の半導体装置を作製することができる。

#### 【 0 1 1 9 】

このように、支持基板 130 に接合された SOI 層 102 を用いた電界効果トランジスタを含む素子層を作製した後、当該素子層を用いて、可撓性を有し且つ薄型である半導体装置を作製することができる。本形態に係る SOI 層 102 は、結晶方位が一定の単結晶半導体であるため、均一で高性能な電界効果トランジスタを得ることができる。すなわち、閾値電圧や移動度などトランジスタ特性として重要な特性値の不均一性を抑制し、高移動化などの高性能化を達成することができる。さらには、ベース基板 136 及び SOI 層 102 の間にバリア層 105 が設けられているため、ベース基板からの不純物が SOI 層に侵入することを防ぐことが可能であるため、素子層に形成されるトランジスタの特性ばらつきを抑えることができる。30

#### 【 0 1 2 0 】

また、支持基板上に接合した SOI 層を用いて電界効果トランジスタを形成した後、支持基板から電界効果トランジスタを有する素子層を剥離して、可撓性を有し薄型の半導体装置を作製する。このため、作製工程における支持基板の取り扱いが容易になり、歩留まりを高めることができる。40

#### 【 0 1 2 1 】

##### ( 実施の形態 8 )

上記実施の形態 1 乃至 5 に示す SOI 基板を用いた半導体装置について図 13 及び図 14 を参照して説明する。ここでは、図 6 及び図 8 に示すように、接合層 104 を用いて単結晶半導体基板とベース基板を接合した SOI 基板を用いて半導体装置を作製した形態を示すが、図 5 及び図 7 に示すように、接合層を用いず単結晶半導体基板及びベース基板を接合した SOI 基板を用いることができる。また、SOI 基板のベース基板側に支持基板を貼り付けてもいい。また、SOI 基板を保持する保持部材によって SOI 基板を保持することで、撓みやすい可撓性基板でも歩留まり高く半導体装置を作製することができる。保持部材としては、ローラー、把持具等がある。50

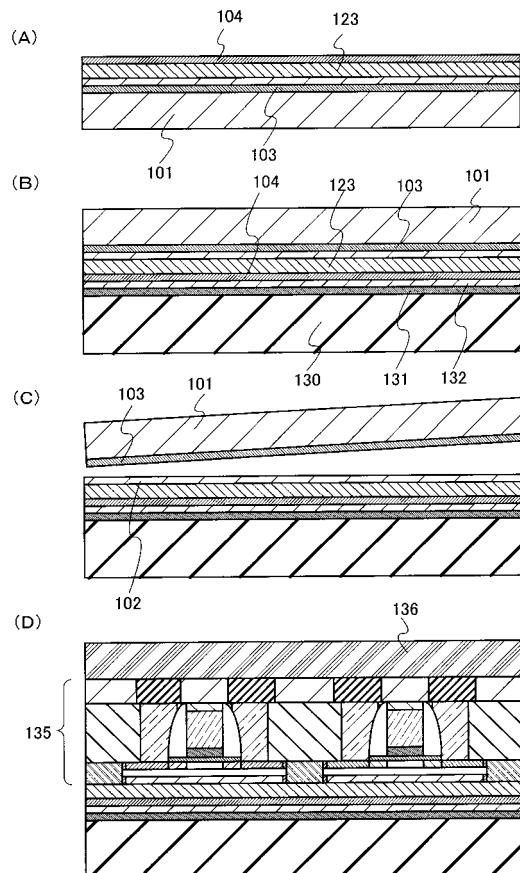

**【 0 1 2 2 】**

図6(A)と同様に、図13(A)に示すように、単結晶半導体基板101にその表面から電界で加速されたイオンを照射し単結晶半導体基板の所定の深さに含ませ、脆弱領域103を形成する。次に、単結晶半導体基板101の表面にキャップ層123及び接合層104を順に積層する。次に、単結晶半導体基板101を250以上、好ましくは300以上、400未満、好ましくは350未満で加熱処理し、脆弱領域103をさらに脆弱にする。ここでは、単結晶半導体基板101表面にキャップ層123が形成されるため、単結晶半導体基板101の表面及び接合層104の表面の平坦を保ちながら、脆弱領域103をさらに脆弱にすることができる。

**【 0 1 2 3 】**

10

図13(B)に示すように、支持基板130上に剥離層131を形成し、剥離層131上に絶縁層132を形成する。また、可撓性基板141に接合層140を形成する。次に、絶縁層132と可撓性基板141上に形成された接合層140とを密着させ、この両者を接合し、支持基板130と可撓性基板141を貼り合わせる。

**【 0 1 2 4 】**

次に、図13(C)に示すように、可撓性基板141と、単結晶半導体基板101に形成された接合層104を密着させ、この両者を接合し、可撓性基板141と単結晶半導体基板101を貼り合わせる。

**【 0 1 2 5 】**

20

良好な接合を行うために、表面を活性化しておいても良い。例えば、接合を行う面に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行う。また、可撓性を有し且つ絶縁表面を有する基板、または単結晶半導体基板の少なくとも一方の接合面を、酸素プラズマによる処理や、オゾン水洗浄により、親水化してもよい。このような表面処理により250以上400未満の温度であっても異種材料間の接合を行うことが容易となる。

**【 0 1 2 6 】**

図13(D)において、脆弱領域103を分離領域として単結晶半導体基板101を支持基板130及び可撓性基板141から剥離(分離)する。接合層104は支持基板130と接合しているので、支持基板130上には単結晶半導体基板101と同じ結晶性を有するSOI層102が残存することとなる。

30

**【 0 1 2 7 】**

なお、可撓性基板141及び単結晶半導体基板101の接合の前に行なった加熱処理の代わりに、可撓性基板141及び単結晶半導体基板101を接合した後、単結晶半導体基板101からレーザビームを単結晶半導体基板に照射し、脆弱領域103を加熱してもよい。この結果、脆弱領域を分離領域として単結晶半導体基板101を可撓性基板141から剥離(分離)することができる。

**【 0 1 2 8 】**

40

この後、SOI層102の表面を平坦化することが好ましい。平坦化方法としては、CMPを用いることができる。または、SOI層102の表面にレーザビームを照射し、表面を溶融して平坦化することができる。

**【 0 1 2 9 】**

また、脆弱領域103を分離領域として単結晶半導体基板101を支持基板130から剥離(分離)する前に、剥離(分離)を容易に行なうためにきっかけをつくってもよい。さらには、単結晶半導体基板101を支持基板130から剥離(分離)する際、支持基板130または単結晶半導体基板101の少なくとも一方の表面に光または熱により剥離可能な粘着シートを設け、支持基板130または単結晶半導体基板101の一方を固定し、他方を引き剥がすことで、さらに剥離(分離)が容易となる。このとき、支持基板130または単結晶半導体基板101の他方に支持部材を設けることで引き剥がし工程が容易となる

50

。

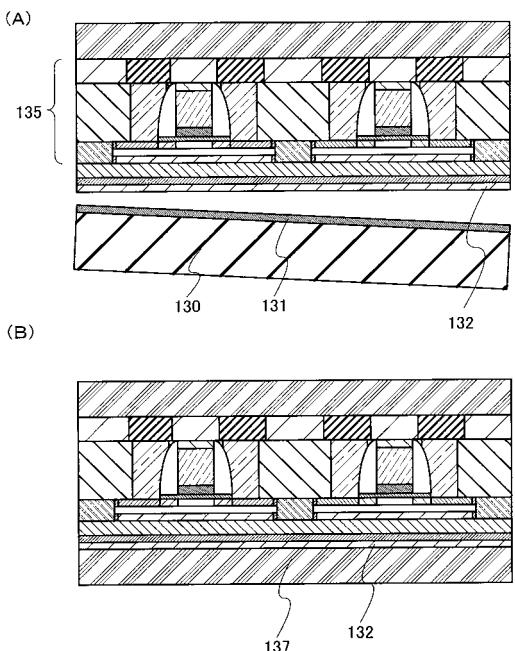

### 【 0 1 3 0 】

次に、図9及び図10の工程を経て、SOI層102を用いてトランジスタを含む素子層135を形成する。次に、素子層135上に可撓性基板142を設ける。可撓性基板142及び素子層135を熱圧着することにより、素子層135に可撓性基板142を固着させることができる。また、素子層135に接着材(図示しない)を用いて可撓性基板142を固着することができる。(図14(A)参照)。可撓性基板142としては、上記ベース基板100の代表例に列挙したものを使用することができる。

### 【 0 1 3 1 】

次に、図14(B)に示すように、支持基板130から可撓性基板141、素子層135及び可撓性基板142の積層体を物理的手段により剥離する。または、剥離層131及び絶縁層132の界面に液体を浸透させて支持基板130から、可撓性基板141、142、及び素子層135の積層体を剥離する。

10

### 【 0 1 3 2 】

ここでは、剥離層131及び絶縁層132の界面、剥離層131、または支持基板130及び剥離層131の界面のいずれかで剥離が生じ、支持基板130から素子層135を剥離することができる。

### 【 0 1 3 3 】

なお、剥離層131において支持基板130から素子層135及び可撓性基板142を剥離する前に、剥離を容易に行うためにきっかけをつくってもよい。さらには、素子層135及び可撓性基板142を支持基板130から剥離する際、支持基板130または可撓性基板142の少なくとも一方の表面に光または熱により剥離可能な粘着シートを設け、支持基板130または可撓性基板142の一方を固定し、他方を引き剥がすことで、さらに剥離が容易となる。このとき、支持基板130または可撓性基板142の他方に支持部材を設けることで引き剥がし工程が容易となる。

20

### 【 0 1 3 4 】

この後、素子層135に複数の半導体装置が含まれる場合、素子層135及び可撓性基板141、142を分断して、複数の半導体装置を切り出してもよい。このような工程により、複数の半導体装置を作製することができる。

### 【 0 1 3 5 】

30

また、支持基板上に接合したSOI層を用いて電界効果トランジスタを形成した後、支持基板から電界効果を有する素子層を剥離して、可撓性を有し薄型の半導体装置を作製する。このため、作製工程におけるハンドリングがしやすく、歩留まりを高めることができる。

### 【 0 1 3 6 】

このように、可撓性基板141に接合されたSOI層102を用いて電界効果トランジスタを作製することができる。本形態に係るSOI層102は、結晶方位が一定の単結晶半導体であるため、均一で高性能な電界効果トランジスタを得ることができる。すなわち、閾値電圧や移動度などトランジスタ特性として重要な特性値の不均一性を抑制し、高移動化などの高性能化を達成することができる。さらには、ベース基板100及びSOI層102の間にバリア層105が設けられているため、ベース基板からの不純物がSOI層に侵入することを防ぐことが可能であるため、素子層に形成されるトランジスタの特性ばらつきを抑えることができる。また、可撓性を有し、薄型である半導体装置を作製することができる。

40

### 【 0 1 3 7 】

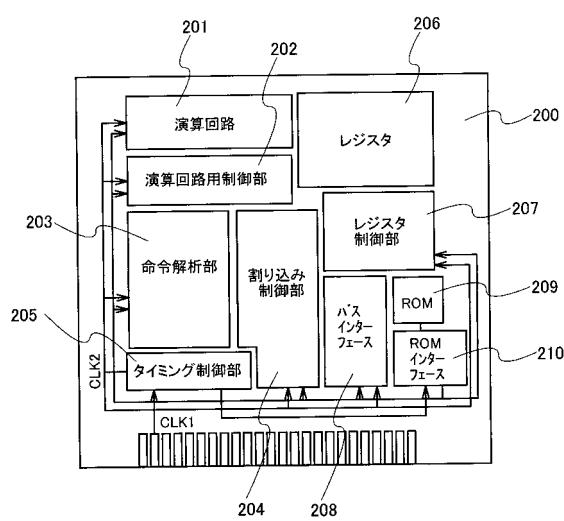

#### (実施の形態9)

図15は、実施の形態6乃至8に示す半導体装置の一例として、実施の形態1乃至5に示すSOI基板を用いて製造されるマイクロプロセッサの構成を示す。このマイクロプロセッサ200は、演算回路201(Arithmetic logic unit。ALUともいう。)、演算回路制御部202(ALU Controller)、命令解析部2

50

03 (Instruction Decoder)、割り込み制御部204 (Interrupt Controller)、タイミング制御部205 (Timing Controller)、レジスタ206 (Register)、レジスタ制御部207 (Register Controller)、バスインターフェース208 (Bus I/F)、読み出し専用メモリ209 (ROM)、及びメモリインターフェース210 (ROM I/F)を有している。

#### 【0138】

バスインターフェース208を介してマイクロプロセッサ200に入力された命令は、命令解析部203に入力され、デコードされた後、演算回路制御部202、割り込み制御部204、レジスタ制御部207、タイミング制御部205に入力される。演算回路制御部202、割り込み制御部204、レジスタ制御部207、タイミング制御部205は、デコードされた命令に基づき各種制御を行う。具体的に演算回路制御部202は、演算回路201の動作を制御するための信号を生成する。また、割り込み制御部204は、マイクロプロセッサ200のプログラム実行中に、外部の入出力装置や周辺回路からの割り込み要求を、その優先度やマスク状態から判断して処理する。レジスタ制御部207は、レジスタ206のアドレスを生成し、マイクロプロセッサ200の状態に応じてレジスタ206の読み出しや書き込みを行う。タイミング制御部205は、演算回路201、演算回路制御部202、命令解析部203、割り込み制御部204、レジスタ制御部207の動作のタイミングを制御する信号を生成する。例えばタイミング制御部205は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、クロック信号CLK2を上記各種回路に供給する。なお、図15に示すマイクロプロセッサ200は、その構成を簡略化して示した一例にすぎず、実際にはその用途によって多種多様な構成を備えることができる。

10

20

#### 【0139】

このようなマイクロプロセッサ200は、可撓性を有し且つ絶縁表面を有する基板上に接合された結晶方位が一定の単結晶半導体層(SOI層)によって集積回路が形成されているので、処理速度の高速化のみならず低消費電力化を図ることができる。

#### 【0140】

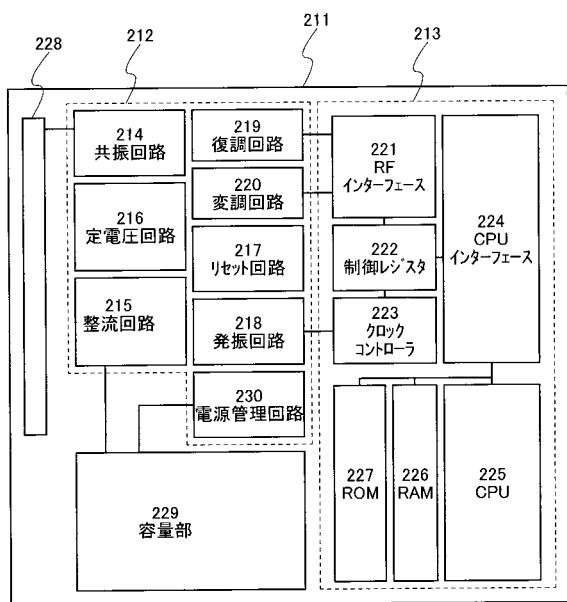

##### (実施の形態10)

次に、実施の形態6乃至8に示す半導体装置の一例として、非接触でデータの送受信を行うことのできる演算機能を備えた半導体装置として、実施の形態1乃至5に示すSOI基板により得られるRFCPUの構成について、図16を参照して説明する。図16は無線通信により外部装置と信号の送受信を行って動作するコンピュータ(以下、「RFCPU」という)の一例を示す。RFCPU211は、アナログ回路部212とデジタル回路部213を有している。アナログ回路部212として、共振容量を有する共振回路214、整流回路215、定電圧回路216、リセット回路217、発振回路218、復調回路219、変調回路220、電源管理回路230を有している。デジタル回路部213は、RFインターフェース221、制御レジスタ222、クロックコントローラ223、インターフェース224(CPUインターフェース)、中央処理ユニット225(CPU)、ランダムアクセスメモリ226(RAM)、読み出し専用メモリ227(ROM)を有している。

30

40

#### 【0141】

このような構成のRFCPU211の動作は概略以下の通りである。アンテナ228が受信した信号を元に共振回路214により誘導起電力が生じる。誘導起電力は、整流回路215を経て容量部229に充電される。この容量部229はセラミックコンデンサーや電気二重層コンデンサーなどのキャパシタで形成されていることが好ましい。容量部229はRFCPU211と一体形成されている必要はなく、別部品としてRFCPU211を構成する絶縁表面を有する基板に取り付けられていれば良い。

#### 【0142】

リセット回路217は、デジタル回路部213をリセットし初期化する信号を生成する。

50

例えば、電源電圧の上昇に遅延して立ち上がる信号をリセット信号として生成する。発振回路 218 は、定電圧回路 216 により生成される制御信号に応じて、クロック信号の周波数とデューティー比を変更する。ローパスフィルタで形成される復調回路 219 は、例えば振幅変調（ASK）方式の受信信号の振幅の変動を二値化する。変調回路 220 は、振幅変調（ASK）方式の送信信号の振幅を変動させて送信する。変調回路 220 は、共振回路 214 の共振点を変化させることで通信信号の振幅を変化させている。クロックコントローラ 223 は、電源電圧又は中央処理ユニット 225 における消費電流に応じてクロック信号の周波数とデューティー比を変更するための制御信号を生成している。電源電圧の監視は電源管理回路 230 が行っている。

## 【0143】

10

アンテナ 228 から RF CPU 211 に入力された信号は復調回路 219 で復調された後、RF インターフェース 221 で制御コマンドやデータなどに分解される。制御コマンドは制御レジスタ 222 に格納される。制御コマンドには、読み出し専用メモリ 227 に記憶されているデータの読み出し、ランダムアクセスメモリ 226 へのデータの書き込み、中央処理ユニット 225 への演算命令などが含まれている。中央処理ユニット 225 は、インターフェース 224 を介して読み出し専用メモリ 227、ランダムアクセスメモリ 226、制御レジスタ 222 にアクセスする。インターフェース 224 は、中央処理ユニット 225 が要求するアドレスより、読み出し専用メモリ 227、ランダムアクセスメモリ 226、制御レジスタ 222 のいずれかに対するアクセス信号を生成する機能を有している。

20

## 【0144】

中央処理ユニット 225 の演算方式は、読み出し専用メモリ 227 に OS（オペレーティングシステム）を記憶させておき、起動とともにプログラムを読み出し実行する方式を採用することができる。また、専用回路で演算回路を構成して、演算処理をハードウェア的に処理する方式を採用することもできる。ハードウェアとソフトウェアを併用する方式では、専用の演算回路で一部の処理を行い、残りの演算をプログラムを使って中央処理ユニット 225 が実行する方式を適用することができる。

## 【0145】

30

このような RF CPU 211 は、可撓性を有し且つ絶縁表面を有する基板に接合された結晶方位が一定の単結晶半導体層（SOI 層）によって集積回路が形成されているので、処理速度の高速化のみならず低消費電力化を図ることができる。それにより、電力を供給する容量部 229 を小型化しても長時間の動作を保証することができる。

## 【0146】

（実施の形態 11）

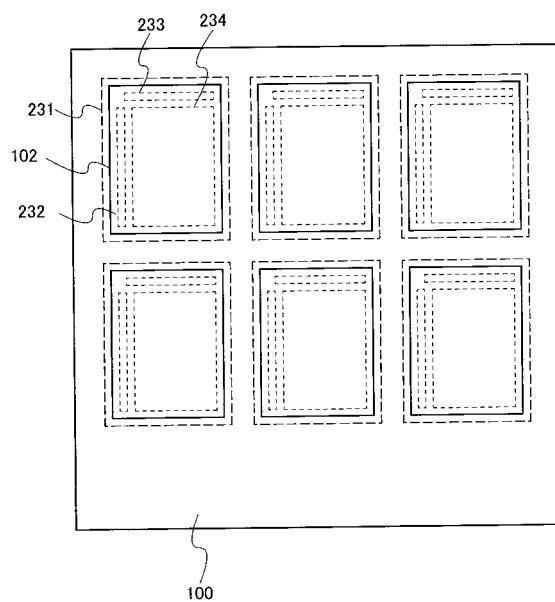

次に、実施の形態 6 乃至 8 に示す半導体装置の一例として、実施の形態 1 乃至 5 に示す SOI 基板により得られる表示パネルの構成について図 17 を用いて示す。

## 【0147】

40

実施の形態 1 乃至 5 で例示する SOI 層 102 は、表示パネルを製造する大型の可撓性基板に接合することもできる。図 17 はベース基板 100 として、可撓性を有し且つ絶縁表面を有する大面積基板に SOI 層 102 を接合する場合を示す。可撓性を有し且つ絶縁表面を有する大面積基板からは複数の表示パネルを切り出しが、SOI 層 102 は、表示パネル 231 の形成領域に合わせて接合することが好ましい。単結晶半導体基板に比べて、可撓性を有し且つ絶縁表面を有する大面積基板は面積が大きいので、SOI 層 102 は図 17 のように分割して配置することが好ましい。表示パネル 231 には、走査線駆動回路領域 232、信号線駆動回路領域 233、画素形成領域 234 があり、これらの領域が含まれるように SOI 層 102 をベース基板 100（可撓性を有し且つ絶縁表面を有する大面積基板）に接合する。

## 【0148】

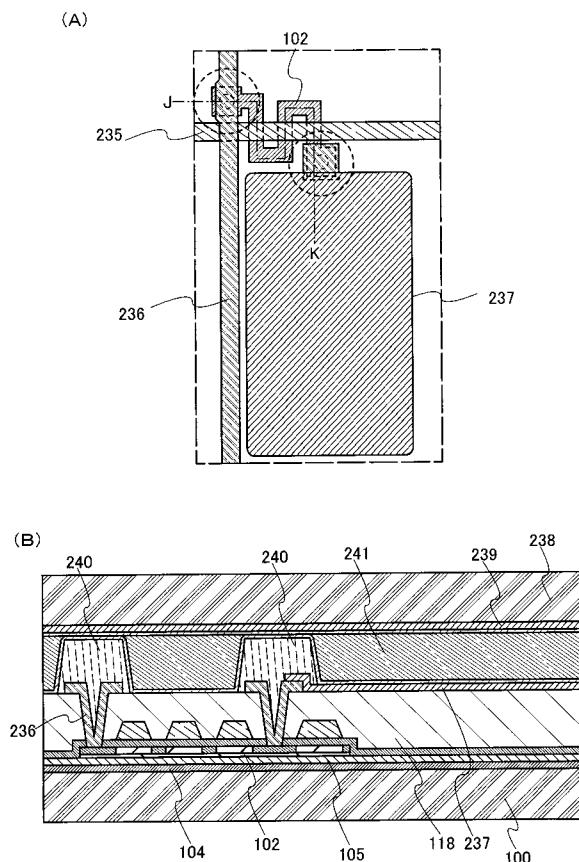

図 18 は SOI 層 102 により画素トランジスタが形成される表示パネルの画素の一例を示す。図 18 (A) は画素の平面図を示す。画素においては、SOI 層上において交差す

50

るゲート配線 235 及びソース配線 236 が形成される。また、SOI層には、ソース配線 236 及びドレイン電極 242 が接続し、ドレイン電極 242 に画素電極 237 が接続する。図 18 (A) に示す J - K 切断線に対応する断面図が図 18 (B) に示されている。

#### 【0149】

図 18 (B) において、ベース基板 100 にはバリア層 105 として窒化珪素層と酸化珪素層が積層されている。SOI層 102 は接合層 104 によって、可撓性を有し且つ絶縁表面を有するベース基板 100 と接合している。絶縁層 118 上に画素電極 237 が設けられている。SOI層 102 とソース配線 236 を接続するコンタクトホールにはそこを埋めるように柱状スペーサ 240 が設けられている。対向基板 238 には対向電極 239 が形成され、柱状スペーサ 240 によって形成される空隙に液晶層 241 が形成されている。

10

#### 【0150】

このように、表示パネルを製造する可撓性を有し且つ絶縁表面を有する大面積基板に SOI 層を形成し、当該 SOI 層を用いたトランジスタを形成することが可能である。SOI 層で形成されるトランジスタは、アモルファスシリコントランジスタよりも電流駆動能力など全ての動作特性が優れているので、トランジスタのサイズを小型化することができる。それにより、表示パネルにおける画素部の開口率を向上させることができる。また、図 15 説明したようなマイクロプロセッサも形成することができるので、表示パネル内にコンピュータの機能を搭載することもできる。また非接触でデータの入出力を可能としたディスプレイを作製することもできる。

20

#### 【0151】

##### (実施の形態 12)

以下において、本発明の特徴の一であるイオンの照射方法について考察する。

#### 【0152】

本発明では、水素 (H) に由来するイオン (以下「水素イオン種」と呼ぶ) を単結晶半導体基板に対して照射している。より具体的には、水素ガス又は水素を組成に含むガスを原材料として用い、水素プラズマを発生させ、該水素プラズマ中の水素イオン種を単結晶半導体基板に対して照射している。

30

#### 【0153】

##### (水素プラズマ中のイオン)

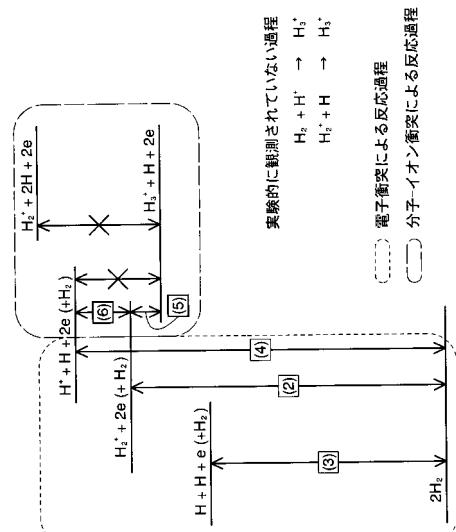

上記のような水素プラズマ中には、 $H^+$ 、 $H_2^+$ 、 $H_3^+$ といった水素イオン種が存在する。ここで、各水素イオン種の反応過程 (生成過程、消滅過程) について、以下に反応式を列挙する。

40

#### 【0154】

図 19 に、上記の反応の一部を模式的に表したエネルギーダイアグラムを示す。なお、図 19 に示すエネルギーダイアグラムは模式図に過ぎず、反応に係るエネルギーの関係を厳密に規定するものではない点に留意されたい。

#### 【0155】

##### ( $H_3^+$ の生成過程)

上記のように、 $H_3^+$  は、主として反応式 (5) により表される反応過程により生成さ

50

れる。一方で、反応式(5)と競合する反応として、反応式(6)により表される反応過程が存在する。 $H_3^+$ が増加するためには、少なくとも、反応式(5)の反応が、反応式(6)の反応より多く起こる必要がある(なお、 $H_3^+$ が減少する反応としては他にも(7)、(8)、(9)が存在するため、(5)の反応が(6)の反応より多いからといって、必ずしも $H_3^+$ が増加するとは限らない。)。反対に、反応式(5)の反応が、反応式(6)の反応より少ない場合には、プラズマ中における $H_3^+$ の割合は減少する。

#### 【0156】

上記反応式における右辺(最右辺)の生成物の増加量は、反応式の左辺(最左辺)で示す原料の密度や、その反応に係る速度係数などに依存している。ここで、 $H_2^+$ の運動エネルギーが約11eVより小さい場合には(5)の反応が主要となり(すなわち、反応式(5)に係る速度係数が、反応式(6)に係る速度係数と比較して十分に大きくなり)、 $H_2^+$ の運動エネルギーが約11eVより大きい場合には(6)の反応が主要となることが実験的に確認されている。10

#### 【0157】

荷電粒子は電場から力を受けて運動エネルギーを得る。該運動エネルギーは、電場によるポテンシャルエネルギーの減少量に対応している。例えば、ある荷電粒子が他の粒子と衝突するまでの間に得る運動エネルギーは、その間に通過した電位差分のポテンシャルエネルギーに等しい。つまり、電場中において、他の粒子と衝突することなく長い距離を移動できる状況では、そうではない状況と比較して、荷電粒子の運動エネルギー(の平均)は大きくなる傾向にある。このような、荷電粒子に係る運動エネルギーの増大傾向は、粒子の平均自由行程が大きい状況、すなわち、圧力が低い状況で生じ得る。20

#### 【0158】

また、平均自由行程が小さくとも、その間に大きな運動エネルギーを得ることができる状況であれば、荷電粒子の運動エネルギーは大きくなる。すなわち、平均自由行程が小さくとも、電位差が大きい状況であれば、荷電粒子の持つ運動エネルギーは大きくなると言える。

#### 【0159】

これを $H_2^+$ に適用してみる。プラズマの生成に係るチャンバー内のように電場の存在を前提とすれば、該チャンバー内の圧力が低い状況では $H_2^+$ の運動エネルギーは大きくなり、該チャンバー内の圧力が高い状況では $H_2^+$ の運動エネルギーは小さくなる。つまり、チャンバー内の圧力が低い状況では(6)の反応が主要となるため、 $H_3^+$ は減少する傾向となり、チャンバー内の圧力が高い状況では(5)の反応が主要となるため、 $H_3^+$ は増加する傾向となる。また、プラズマ生成領域における電場(又は電界)が強い状況、すなわち、ある二点間の電位差が大きい状況では $H_2^+$ の運動エネルギーは大きくなり、反対の状況では、 $H_2^+$ の運動エネルギーは小さくなる。つまり、電場が強い状況では(6)の反応が主要となるため $H_3^+$ は減少する傾向となり、電場が弱い状況では(5)の反応が主要となるため、 $H_3^+$ は増加する傾向となる。30

#### 【0160】

##### (イオン源による差異)

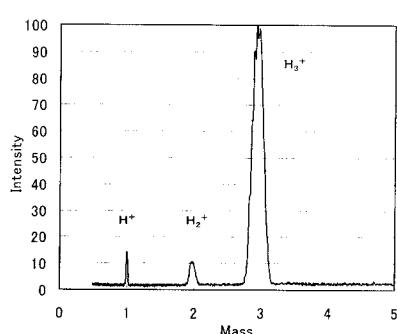

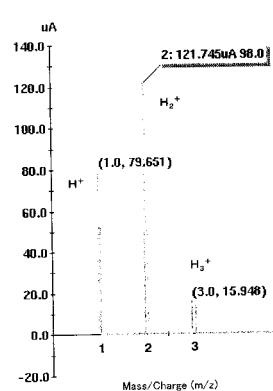

ここで、イオン種の割合(特に $H_3^+$ の割合)が異なる例を示す。図20は、100%水素ガス(イオン源の圧力:  $4.7 \times 10^{-2}$  Pa)から生成されるイオンの質量分析結果を示すグラフである。なお、上記質量分析は、イオン源から引き出されたイオンを測定することにより行った。横軸はイオンの質量である。スペクトル中、質量1、2、3のピークは、それぞれ、 $H^+$ 、 $H_2^+$ 、 $H_3^+$ に対応する。縦軸は、スペクトルの強度であり、イオンの数に対応する。図20では、質量が異なるイオンの数量を、質量3のイオンを100とした場合の相対比で表している。図20から、上記イオン源により生成されるイオンの割合は、 $H^+ : H_2^+ : H_3^+ = 1 : 1 : 8$ 程度となることが分かる。なお、このような割合のイオンは、プラズマを生成するプラズマソース部(イオン源)と、当該プラズマからイオンビームを引き出すための引出電極などから構成されるイオンドーピング装置によっても得ることが出来る。40

## 【0161】

図21は、図20とは異なるイオン源を用いた場合であって、イオン源の圧力がおおよそ $3 \times 10^{-3}$ Paの時に、PH<sub>3</sub>から生成したイオンの質量分析結果を示すグラフである。上記質量分析結果は、水素イオン種に着目したものである。また、質量分析は、イオン源から引き出されたイオンを測定することにより行った。図20と同様、横軸はイオンの質量を示し、質量1、2、3のピークは、それぞれH<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>に対応する。縦軸はイオンの数量に対応するスペクトルの強度である。図21から、プラズマ中のイオンの割合はH<sup>+</sup> : H<sub>2</sub><sup>+</sup> : H<sub>3</sub><sup>+</sup> = 37 : 56 : 7程度であることが分かる。なお、図21はソースガスがPH<sub>3</sub>の場合のデータであるが、ソースガスとして100%水素ガスを用いたときも、水素イオン種の割合は同程度になる。

10

## 【0162】

図21のデータを得たイオン源の場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>及びH<sub>3</sub><sup>+</sup>のうち、H<sub>3</sub><sup>+</sup>が7%程度しか生成されていない。他方、図20のデータを得たイオン源の場合には、H<sub>3</sub><sup>+</sup>の割合を50%以上（上記の条件では80%程度）とすることが可能である。これは、上記考察において明らかになったチャンバー内の圧力及び電場に起因するものと考えられる。

## 【0163】

(H<sub>3</sub><sup>+</sup>の照射メカニズム)

図20のような複数のイオン種を含むプラズマを生成し、生成されたイオン種を質量分離しないで単結晶半導体基板に照射する場合、単結晶半導体基板の表面には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>の各イオンが照射される。イオンの照射からイオン導入領域形成にかけてのメカニズムを再現するために、以下の5種類のモデルを考える。

20

1. 照射されるイオン種がH<sup>+</sup>で、照射後もH<sup>+</sup>(H)である場合

2. 照射されるイオン種がH<sub>2</sub><sup>+</sup>で、照射後もH<sub>2</sub><sup>+</sup>(H<sub>2</sub>)のままである場合

3. 照射されるイオン種がH<sub>2</sub><sup>+</sup>で、照射後に2個のH(H<sup>+</sup>)に分裂する場合

4. 照射されるイオン種がH<sub>3</sub><sup>+</sup>で、照射後もH<sub>3</sub><sup>+</sup>(H<sub>3</sub>)のままである場合

5. 照射されるイオン種がH<sub>3</sub><sup>+</sup>で、照射後に3個のH(H<sup>+</sup>)に分裂する場合

## 【0164】

## (シミュレーション結果と実測値との比較)

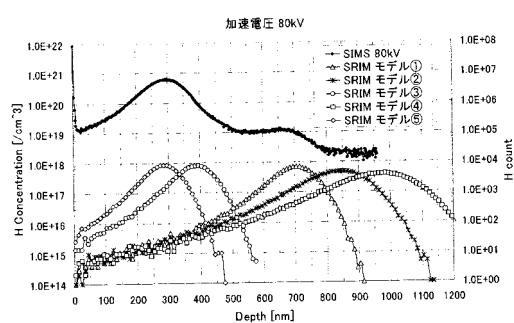

上記のモデルを基にして、水素イオン種をSi基板に照射する場合のシミュレーションを行った。シミュレーション用のソフトウェアとしては、SRIM(the Stopping and Range of Ions in Matter:モンテカルロ法によるイオン導入過程のシミュレーションソフトウェア、TRIM(the Transport of Ions in Matter)の改良版)を用いている。なお、計算の関係上、モデル2ではH<sub>2</sub><sup>+</sup>を質量2倍のH<sup>+</sup>に置き換えて計算した。また、モデル4ではH<sub>3</sub><sup>+</sup>を質量3倍のH<sup>+</sup>に置き換えて計算した。さらに、モデル3ではH<sub>2</sub><sup>+</sup>を運動エネルギー1/2のH<sup>+</sup>に置き換え、モデル5ではH<sub>3</sub><sup>+</sup>を運動エネルギー1/3のH<sup>+</sup>に置き換えて計算を行った。

30

## 【0165】

なお、SRIMは非晶質構造を対象とするソフトウェアではあるが、高エネルギー、高ドーズの条件で水素イオン種を照射する場合には、SRIMを適用可能である。水素イオン種とSi原子の衝突により、Si基板の結晶構造が非単結晶構造に変化するためである。

40

## 【0166】

図22に、モデル1乃至モデル5を用いて水素イオン種を照射した場合(H換算で10万個照射時)の計算結果を示す。また、図20の水素イオン種を照射したSi基板中の水素濃度(SIMS(Secondary Ion Mass Spectroscopy)のデータ)をあわせて示す。モデル1乃至モデル5を用いて行った計算の結果については、縦軸を水素原子の数で表しており(右軸)、SIMSデータについては、縦軸を水素原子の濃度で表している(左軸)。横軸はSi基板表面からの深さである。実測値である

50

SIMSデータと、計算結果とを比較した場合、モデル2及びモデル4は明らかにSIMSデータのピークから外れており、また、SIMSデータ中にはモデル3に対応するピークも見られない。このことから、モデル2乃至モデル4の寄与は、相対的に小さいことが分かる。イオンの運動エネルギーがk eV台であるのに対して、H-Hの結合エネルギーは数eV程度に過ぎないことを考えれば、モデル2及びモデル4の寄与が小さいのは、Si元素との衝突により、大部分のH<sub>2</sub><sup>+</sup>やH<sub>3</sub><sup>+</sup>が、H<sup>+</sup>やHに分離しているためと思われる。

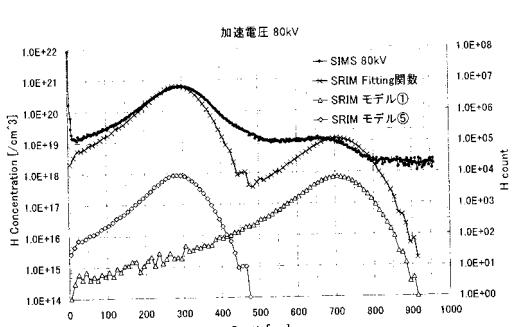

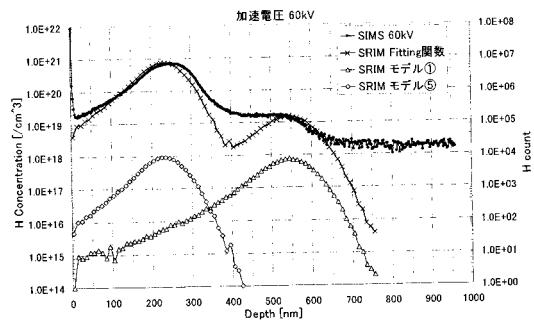

#### 【0167】

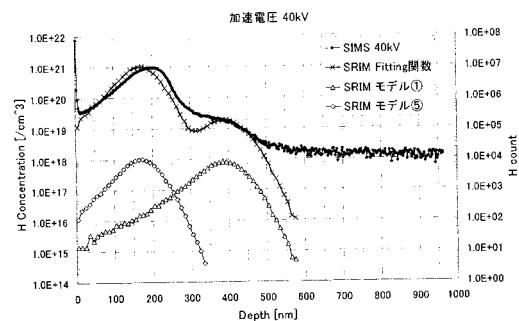

以上より、モデル2乃至モデル4については、以下では考慮しない。図23乃至図25に、モデル1及びモデル5を用いて水素イオン種を照射した場合（H換算で10万個照射時）の計算結果を示す。また、図20の水素イオン種を照射したSi基板中の水素濃度（SIMSデータ）及び、上記シミュレーション結果をSIMSデータにフィッティングさせたもの（以下フィッティング関数と呼ぶ）を合わせて示す。ここで、図23は加速電圧を80kVとした場合を示し、図24は加速電圧を60kVとした場合を示し、図25は加速電圧を40kVとした場合を示している。なお、モデル1及びモデル5を用いて行った計算の結果については、縦軸を水素原子の数で表しており（右軸）、SIMSデータ及びフィッティング関数については、縦軸を水素原子の濃度で表している（左軸）。横軸はSi基板表面からの深さである。

#### 【0168】

フィッティング関数はモデル1及びモデル5を考慮して以下の計算式により求めることとした。なお、計算式中、X、Yはフィッティングに係るパラメータであり、Vは体積である。

##### [フィッティング関数]

$$= X / V \times [\text{モデル1のデータ}] + Y / V \times [\text{モデル5のデータ}]$$

#### 【0169】

現実に照射されるイオン種の割合（H<sup>+</sup> : H<sub>2</sub><sup>+</sup> : H<sub>3</sub><sup>+</sup> = 1 : 1 : 8程度）を考えればH<sub>2</sub><sup>+</sup>の寄与（すなわち、モデル3）についても考慮すべきであるが、以下に示す理由により、ここでは除外して考えた。

- ・モデル3に示される照射過程により導入される水素は、モデル5の照射過程と比較して僅かであるため、除外して考えても大きな影響はない（SIMSデータにおいても、ピークが現れていない）。

- ・モデル5とピーク位置の近いモデル3は、モデル5において生じるチャネリング（結晶の格子構造に起因する元素の移動）により隠れてしまう可能性が高い。すなわち、モデル3のフィッティングパラメータを見積もるのは困難である。これは、本シミュレーションが非晶質Siを前提としており、結晶性に起因する影響を考慮していないことによるものである。

#### 【0170】

図26に、上記のフィッティングパラメータをまとめる。いずれの加速電圧においても、導入されるHの数の比は、[モデル1] : [モデル5] = 1 : 4.2 ~ 1 : 4.5程度（モデル1におけるHの数を1とした場合、モデル5におけるHの数は4.2以上4.5以下程度）であり、照射されるイオン種の数の比は、[H<sup>+</sup>（モデル1）] : [H<sub>3</sub><sup>+</sup>（モデル5）] = 1 : 1.4 ~ 1 : 1.5程度（モデル1におけるH<sup>+</sup>の数を1とした場合、モデル5におけるH<sub>3</sub><sup>+</sup>の数は1.4以上1.5以下程度）である。モデル3を考慮していないことや非晶質Siと仮定して計算していることなどを考えれば、実際の照射に係るイオン種の比（H<sup>+</sup> : H<sub>2</sub><sup>+</sup> : H<sub>3</sub><sup>+</sup> = 1 : 1 : 8程度）に近い値が得られていると言える。

#### 【0171】

##### (H<sub>3</sub><sup>+</sup>を用いる効果)

図20に示すようなH<sub>3</sub><sup>+</sup>の割合を高めた水素イオン種を基板に照射することで、H<sub>3</sub><sup>+</sup>に起因する複数のメリットを享受することができる。例えば、H<sub>3</sub><sup>+</sup>はH<sup>+</sup>やHなどに分離して基板内に導入されるため、主にH<sup>+</sup>やH<sub>2</sub><sup>+</sup>を照射する場合と比較して、イオン

10

20

30

40

50

の導入効率を向上させることができる。これにより、S O I 基板の生産性向上を図ることができる。また、同様に、 $H_3^+$  が分離した後の $H^+$  や H の運動エネルギーは小さくなる傾向にあるから、薄い半導体層の製造に向いている。

### 【 0 1 7 2 】

なお、本明細書では、 $H_3^+$  を効率的に照射するために、図 20 に示すような水素イオン種を照射可能なイオンドーピング装置を用いる方法について説明している。イオンドーピング装置は廉価で、大面積処理に優れているため、このようなイオンドーピング装置を用いて $H_3^+$  を照射することで、半導体特性の向上、大面積化、低コスト化、生産性向上などの顕著な効果を得ることができる。一方で、 $H_3^+$  の照射を第一に考えるのであれば、イオンドーピング装置を用いることに限定して解釈する必要はない。

10

### 【 図面の簡単な説明 】

#### 【 0 1 7 3 】

【 図 1 】 S O I 基板の構成を示す断面図である。

【 図 2 】 S O I 基板の構成を示す断面図である。

【 図 3 】 S O I 基板の構成を示す断面図である。

【 図 4 】 S O I 基板の構成を示す断面図である。

【 図 5 】 S O I 基板の製造方法を説明する断面図である。

【 図 6 】 S O I 基板の製造方法を説明する断面図である。

【 図 7 】 S O I 基板の製造方法を説明する断面図である。

【 図 8 】 S O I 基板の製造方法を説明する断面図である。

20

【 図 9 】 S O I 基板を用いた半導体装置の製造方法を説明する断面図である。

【 図 1 0 】 S O I 基板を用いた半導体装置の製造方法を説明する断面図である。

【 図 1 1 】 S O I 基板を用いた半導体装置の製造方法を説明する断面図である。

【 図 1 2 】 S O I 基板を用いた半導体装置の製造方法を説明する断面図である。

【 図 1 3 】 S O I 基板を用いた半導体装置の製造方法を説明する断面図である。

【 図 1 4 】 S O I 基板を用いた半導体装置の製造方法を説明する断面図である。

【 図 1 5 】 S O I 基板により得られるマイクロプロセッサの構成を示すブロック図である。

。

【 図 1 6 】 S O I 基板により得られる R F C P U の構成を示すブロック図である。

【 図 1 7 】 表示パネル製造用のマザーガラスに S O I 層を接合する場合を例示する平面図である。

30

【 図 1 8 】 S O I 層により画素トランジスタが構成されている表示パネルの一例を示す図である。

【 図 1 9 】 水素イオン種のエネルギーダイアグラムについて示す図である。

【 図 2 0 】 イオンの質量分析結果を示す図である。

【 図 2 1 】 イオンの質量分析結果を示す図である。

【 図 2 2 】 加速電圧を 8 0 k V とした場合の水素元素の深さ方向のプロファイル（実測値及び計算値）を示す図である。

【 図 2 3 】 加速電圧を 8 0 k V とした場合の水素元素の深さ方向のプロファイル（実測値、計算値、及びフィッティング関数）を示す図である。

40

【 図 2 4 】 加速電圧を 6 0 k V とした場合の水素元素の深さ方向のプロファイル（実測値、計算値、及びフィッティング関数）を示す図である。

【 図 2 5 】 加速電圧を 4 0 k V とした場合の水素元素の深さ方向のプロファイル（実測値、計算値、及びフィッティング関数）を示す図である。

【 図 2 6 】 フィッティングパラメータの比（水素元素比及び水素イオン種比）をまとめた図である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【 図 7 】

【 図 8 】

【 9 】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図22】

【図21】

【図23】

【図24】

【図26】

| 加速電圧  | 水素元素(H)比(X:Y) | 水素イオン種比(X:Y/3) |

|-------|---------------|----------------|

| 80 kV | 1 : 44.1      | 1 : 14.7       |

| 60 kV | 1 : 42.5      | 1 : 14.2       |

| 40 kV | 1 : 43.5      | 1 : 14.5       |

【図25】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/786 (2006.01)

審査官 右田 勝則

(56)参考文献 特開2000-349266 (JP, A)

特開2000-331899 (JP, A)

特開2004-179649 (JP, A)

特開2000-077287 (JP, A)

特開2002-170942 (JP, A)

特開2004-134675 (JP, A)

特開2004-165679 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/02

H 01 L 21/20

H 01 L 21/265

H 01 L 21/336

H 01 L 27/12

H 01 L 29/786