**(19) 대한민국특허청(KR)**

**(12) 특허공보(B1)**

(51) Int. Cl.<sup>3</sup>

H04N 5/52

(45) 공고일자 1982년06월04일

(11) 공고번호 특 1982-0001002

|            |                                                                   |           |

|------------|-------------------------------------------------------------------|-----------|

| (21) 출원번호  | 특 1979-0002825                                                    | (65) 공개번호 |

| (22) 출원일자  | 1979년08월18일                                                       | (43) 공개일자 |

| (30) 우선권주장 | 934, 834 1978년08월18일 미국(US)                                       |           |

| (71) 출원인   | 알 · 씨 · 에이 · 코퍼레이션 에드워드 제이 · 노오턴<br>미합중국, 10020 뉴욕, 뉴욕, 록펠러프라자 30 |           |

| (72) 발명자   | 에드워드 콜레이 폭스                                                       |           |

| (74) 대리인   | 미합중국, 08512 뉴저지, 크랜부리, 알 · 디 · 1 스틸레 드라이브 4<br>이병호, 김성기           |           |

**심사관 : 백승남 (책자공보 제693호)**

**(54) 피이크 검파기 회로**

**요약**

내용 없음.

**대표도**

**도1**

**형세서**

[발명의 명칭]

피이크 검파기 회로

[도면의 간단한 설명]

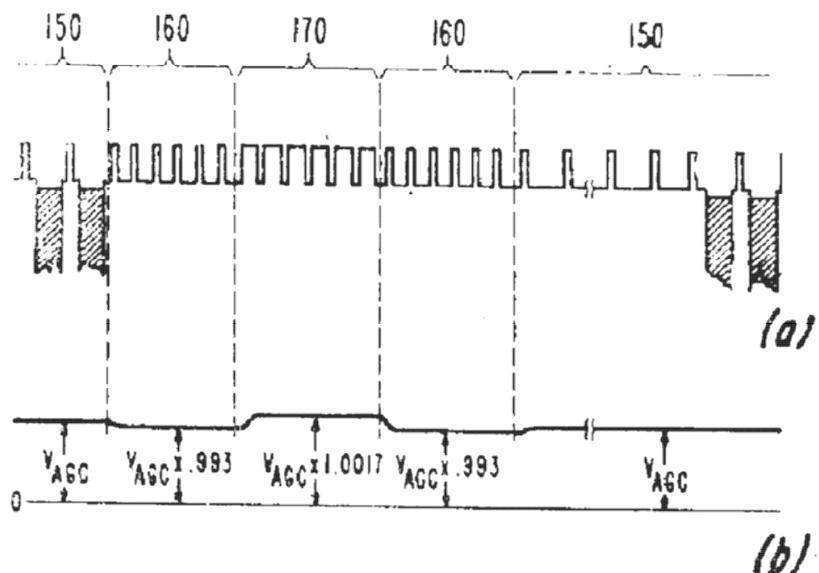

제1a도는 전형적인 합성비데오 신호를 도시한 도면.

제1b도는 제1a도의 동기펄스들의 폭의 함수로 변하는 AGC 제어전압을 도시한 도면.

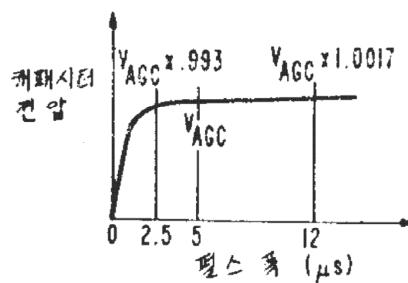

제2도는 동기펄스폭의 함수로 피이크 검파 캐패시터의 전압변화를 도시한 도면.

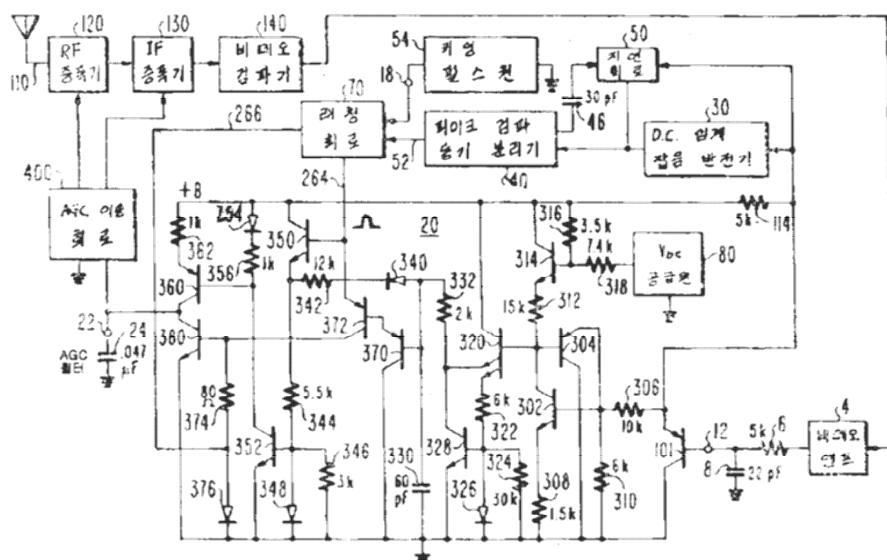

제3도는 본 발명의 원리에 따라서 구성된 피이크 검사 AGC 시스템의 양호한 실시예를 도시한 개략적인 계통도.

[발명의 상세한 설명]

본 발명은 충전정류기의 임피던스가 저레벨로 제한되는 충전정류기와 캐패시터를 포함하고 있고 텔레비전 수신기 내에 자동이득제어전압을 나타나게 하는데 사용되는 피이크(peak) 검파기에 관한 것이다.

통상적으로 자동이득제어(AGC)회로는 수신기의 무선주파수(RF) 증폭단과 중간주파수(IF) 증폭단에 인가하기에 적당한 제어전압을 유도하기 위해서 텔레비전 수신기내에 사용된다. 제어전압은 일정한 피이크 진폭을 검파한 텔레비전 신호를 갖추기 위해서 검파된 비데오 신호의 동기신호 성분들의 레벨에 따라서 이 단들의 이득을 반대로 변화시킨다.

통상적으로 텔레비전 수신기에서는, 합성비데오 신호의 동기신호 성분들의 피이크 레벨을 샘플링하고 신호 레벨의 변화에 응답하여 제어전압을 조정하므로서 AGC 제어전압을 유도한다. 피이크 검파기는 동기펄스들을 샘플하는데 이용되지만, 임펄스 잡음에 매우 민감하기 때문에, 수평편향 시스템에 의해 생긴 비교적 짧은 수평귀선(궤환) 펄스들 동안에만 AGC 회로를 켜이트 온(on)시키거나 키이(key)한다.

피이크 검파기는 충전회로에 의해 키잉(keying) 기간동안 비데오 신호의 피이크 레벨을 향하여 충전되는 캐패시터를 포함한다. 이 캐패시터는 지수(指數)비로 신호피이크로 충전된다. 이 캐패시터가 처음에 방전되면, 이 캐패시터는 충전회로로부터의 전류흐름에 의해 처음으로 충전된다. 이 캐패시터가 신호피이크를 향해 충전되면 충전회로에 의해 공급된 전류가 감소하므로 피이크 검파기의 충전시정수가 증가하게 된다. 이 증가하는 충전시정수는 충전정류가 감소하고 충전정류의 출력임피던스가 증가하는 것에 기인한다. 2.5μs 등화펄스와 같은 짧은 기간의 신호가 샘플되면, 증가하는 충전시정수는 캐패시터가 피이크 신호레벨 이하의 레벨로 충전하게 한다. 그러므로 피이크 검파기는, 모든 펄스들의 신호 레벨들이 동일하지만, 키잉기간동안 5μs 수평동기펄스들이나 27μs 수직동기펄스들을 샘플하는 것에 기인한 레벨보다는 등화펄스들을 샘플할 때의 저신호 레벨을 감지한다. 감지된 신호레벨내의 이 차이는 피이크 검파된 신호 레벨이 단 하나의 펄스진폭 대신에 동기펄스폭과 진폭의 함수로 되게 한다. AGC 시스템은 등화펄스 기간동안 RF와 IF 증폭기의 이득을 약간 증가시키고 수직동기기간동안 이득을 감소시키면서 시스템 이득내

의 변동이 수직주사비로 되게 하는 검파된 신호레벨내의 변화에 대응한다. 이 변동들은 AGC 시스템 루우프내에 저주파수 공진을 야기시켜서 수직동기 및 영상 룰(roll)이 손실되게 한다.

본 발명의 양호한 실시예에 따르면, 피아크 검파기 회로는 진폭변화 신호의 최대 편차를 검파하기 위해서 갖추어져 있다. 이 회로는 충전 임피던스에 직렬로 결합된 캐패시터를 포함하고 있고 진폭변화 신호의 최대편차에 응답하기에 적당한 시정수를 갖고 있는 회로를 포함한다. 반도체 장치는 진폭변화 신호를 수신하기 위한 입력단자와 진폭변화 신호의 최대편차를 향해 캐패시터를 충전하기 위해 충전 임피던스에 결합된 출력단자를 갖고 있다. 이 반도체 장치는 여기를 통하여 흐르는 전류가 감소하는 것을 증가시키는 임피던스를 나타낸다. 제어 가능한 전류 감소는 반도체 장치의 입력단자에서의 진폭변화 신호에 응답하고, 여기를 통하여 흐르는 캐패시터 충전전류에 보상되는 캐패시터의 충전동안 반도체 장치를 통하여 전류성분을 흐르게 하기 위해서 반도체 장치의 출력단자에 결합된다. 보상전류 성분은 충전 임피던스보다 작은 값 이상의 캐패시터의 충전동안 반도체 장치에 의해 나타난 임피던스의 증가를 미연에 방지시키기에 충분한 크기로 되어 있다. 제어 가능한 전류감소는 반도체 장치가 캐패시터를 충전하지 않을 때 전류가 도통되지 않게 한다.

피아크 검파기는 합성비데오 신호의 동기신호성분의 피아크 검파하도록 자동이득제어로에 사용될 수 있다.

이하 도면을 참조하여 본 발명을 더욱 상세하게 기술하겠다.

간략화한 형태에서, 신호의 피아크값을 샘플하고 측적하는 피아크 검파기는 반도체 다이오드 접합과 캐패시터를 포함한다. 이 신호는 다이오드의 애노드전극에 결합되고, p-n 접합에 의해 정류되며, 캐소드 전극에 접속된 캐패시터 양단에 인가된다. 신호가 피아크 레벨로 증가하면, 다이오드는 신호전류를 캐패시터로 도통시키고, 다이오드 접합양단의 전압강하보다 작은 신호의 피아크 레벨로 충전시킨다. 신호가 저레벨로 감소되면, 충전된 캐패시터는 피아크신호 레벨을 나타내고 다이오드 접합을 역바이어스 시키는 전압을 보유한다. 다이오드와 캐패시터가 전류누설이 없고 다른 방전장치가 캐패시터에 접속되지 않으면, 이 캐패시터는 피아크신호 레벨을 불명확하게 보유하게 된다.

상기에 기술한 피아크 검파기는 합성비데오 신호의 동기신호 성분들의 피아크 레벨을 검파하도록 AGC 회로에 상호 결합될 수 있다. AGC 제어전압은 캐패시터 양단에 나타나고 이 단들의 이득을 제어하도록 텔레비전 수신기의 RF와 IF 증폭단들에 인가된다. 선택적으로, 캐패시터 양단에 측적된 신호레벨은 변환회로에 의해 분리된 AGC 퀼러캐패시터에 이송될 수 있고, 증폭단들에 결합된다.

1978년 8월 18일에 제이·알·하포드가 “키이된 AGC 회로”란 제목으로 출원한 미합중국특허원 제934,823호에 기술된 것과 같은 AGC 회로형태에서는, 동기펄스들 사이의 피아크검파캐패시터를 방전하는 것이 바람직하고, 피아크 검파된 레벨이 분리된 AGC 퀼터캐패시터로 이송되는 동안인 특수 키잉기간 동안에만 피아크 검파기가 동기펄스들을 샘플할 수 있다. 다음의 예는 피아크 검파기가 이 형태의 AGC 회로에 이용되고  $12\mu s$ 의 키잉 기간을 갖고 있다고 가정한 것이다.

합성비데오 신호의 동기신호 성분의 피아크 검파기는 다음과 같이 생긴다.

제1a도를 참조하면, NTSC 합성비데오 신호의 수직동기 기간이 도시되어 있다. 이 파형은 수평동기펄스기간 150, 등화펄스기간 160, 및 수직동기펄스기간 170을 포함한다.

이 기간들에 포함된 동기펄스들은, 등화펄스동안 약  $2.5\mu s$ , 수평동기펄스동안  $5\mu s$ , 및 수직동기펄스동안  $27\mu s$ 의 전형적인 기간을 갖고 있다. 이 합성비데오 신호는 동기펄스들의 피아크 검파용 피아크 검파기 다이오드의 애노드에 인가된다.

신호가 다이오드의 애노드 전극에 인가될 때 캐패시터가 방전되면, 캐패시터 양단의 저전압 레벨과 입력신호 사이의 큰 전압차이로 인하여, 캐패시터가 처음으로 높은 비로 신호피아크를 향하여 충전하기 시작하게 된다. 그러나 캐패시터 양단의 전압이 입력신호의 전압에 접근하면 충전비가 감소하고, 피아크 검파기의 충전시정수가 증가하게 된다. 충전시정수는 충전비가 감소하므로서 다이오드의 캐소드전극(즉, 전류원)에서의 임피던스가 증가하는 것으로 인하여 증가한다. 충분히 긴 시간동안 충전시키면, 캐패시터는 신호피아크로 충전하게 된다. 정해진 다른 방법에서 이것이 저레벨의 전류도통으로 다이오드의 고순방향 임피던스로 되지 않으면, 캐패시터는 수  $\mu s$  동안에만 피아크 신호레벨(다이오드접합 양단의 전압강하보다 작음)<sup>9</sup>에서 떨어진  $10^9$ 내의 한 부분만의 레벨로 충전된다. 그러나, 감소하는 충전비가 계산되면 캐패시터가 전체 피아크 값을 나타내는 전압 레벨에 도달하게 하는데 충분한 시간량이 필요하게 된다는 것을 알게 된다.

피아크 검파 캐패시터상의 지수충전비 효과는 제2도에 도시되어 있다. 여기에 도시된 곡선은  $5\mu s$ 의 수평동기펄스동안, 캐패시터가  $V_{AGC}$ 로 표시한 피아크 전압레벨로 충전되는 것을 나타낸다.(수평동기펄스들이 텔레비전 계통의 등화 및 수직동기펄스들보다 숫자상으로 우세하기 차지하기 때문에, 수평동기펄스를 피아크 검파하므로서 이루어진 전압레벨은 기준레벨로 사용된다. NTSC 텔레비전 계통은 6개의 텁니를 가진 수직동기펄스, 12개의 텁니를 가진 등화펄스, 및 253개나 254개의 텁니를 가진 수평동기펄스를 포함한다).  $2.5\mu s$ 의 등화펄스기간동안, 캐패시터는 수평동기펄스에 의해 이루어진 것보다 0.7% 작은 전압레벨이나  $V_{AGC} \times 0.993$ 으로 충전하게 된다. 피아크 검파기가  $12\mu s$ 의 키잉기간동안  $27\mu s$ 의 수직동기펄스를 샘플하면, 캐패시터는 수평동기펄스에 의해 이루어진 것보다 0.17% 큰 전압레벨이나  $V_{AGC} \times 1.0017$ 에 도달하게 된다.

이 다른 전압레벨들로 인한 AGC 제어전압은 제1b도에 도시되어 있다. 여기에 도시된 파형은 제1a도의 동기펄스 기간에 대응한다. 이 파형은 제1a도의 일정한 진폭비데오 신호가, 수평동기기간 150동안  $V_{AGC}$ 의 진폭을 가진 AGC 제어전압, 등화펄스기간 160동안  $V_{AGC} \times 0.993$ 의 진폭을 가진 AGC 제어전압, 및 수직동기펄스기간 170동안  $V_{AGC} \times 1.0017$ 의 진폭을 가진 AGC 제어전압으로 되게 하는 것을 나타낸다.

그러므로, AGC 제어전압은 일정한 진폭비데오 신호용 수직동기기간동안 대부분 1%의

피아크-투-피아크(peak-to-peak) 진폭변화를 갖는다는 것을 알 수 있다. 수직동기 및 등화펄스기간 170과 160의 시간기간(각각의 세 수평선) 때문에, 이 변화는 약 1600Hz의 주파수를 갖는다.

신호강도변화를 동적으로 고정하기 위한 궤환루우프로 간주되는(RF 및 IF 증폭기, 비데오검파기 및 증폭기, 및 AGC 회로를 포함하고 있는) AGC 시스템이 단일시정수 시스템이어서 공진이 자유롭다면 이 1%진폭, 2600Hz의 효과적인 신호강도 변화비는 중요하지 않게 된다. 그러나, 전형적인 AGC 시스템은 RF 및 IF 증폭기용 AGC 지연을 제어하는 회로내의 것들과 같은 다수의 시정수와, 키네스코프 아아킹으로부터 튜우너를 보호하도록 작동하는 R-C 회로를 포함한다. 이 다수의 시정수들은 AGC 시스템의 이송함수의 근수-궤적지구(根數-軌跡地圖:root-locus plot)내에 다수의 공진 극(極)을 만들도록 결합된다.

또한, 일반적으로 AGC 시스템은 비행기동요를 보상할 수 있게 하기 위하여 상당한 량의 루우프 이득을 갖고 있다. IF와 RF 증폭기의 것인 AGC 제어전압내의 변화에 따른 이득 변화비의 변화로 인하여, 이 루우프 이득량은 상당히 변할 수 있다. 즉, 튜우너 AGC 루우프 이득만이 1 내지 100의 범위로 변할 수 있다. AGC 시스템의 공진은 루우프 이득이 함수로 변한다. 즉, 이득이 높으면, 공진주파수도 높다.

그러므로, AGC 시스템내의 공진이 2600Hz 부근으로 올라갈 수 있다. 시스템 이득의 변화가 2600Hz까지 여기되는 것은 AGC 제어전압이 변하기 때문이다. 여기되면, 이 공진들은 수직비에서의 AGC 시스템 루우프내의 발진 버어스트와 영상이 수직으로 회전하게 한다.

AGC 시스템 루우프의 복잡성과 포함된 다수의 변화 때문에, 구성 및 테스트하기 전에 AGC 시스템 내에서의 공진극들의 위치와 존재를 계산하는 것이 실제로는 불가능하다. 종종, 특수환경이 발진을 감소시키도록 여기할 때, 이 공진들의 존재를 알게 된다. 그러므로, 공진이 AGC 시스템에 반대로 영향을 미치는 것을 방지하기 위한 가장 안전한 방법은 이것들을 발진으로 여기하는 AGC 신호강도가 2600Hz로 변하지 못하게 하는 것이다.

본 발명의 원리에 따라 구성된 피아크 검파기를 포함하는 AGC 회로는 제3도에 개략적이고 계통적으로 도시되어 있다. 여기에 도시된 AGC 회로는 상기에 언급된 미합중국 특허원 제934,823호에 기술된 것과 똑같은 것이다.

제3도를 참조하면, 안테나 110은 RF 증폭기 120에 공급되는 방송국 주파수 텔레비전 신호를 수신한다.

RF 증폭기는 특수주파수 텔레비전 신호를 선택하기 위한 튜우너와, 방송국 주파수 신호를 중간주파수(IF) 신호로 바꾸기 위한 혼합기를 포함한다. IF 신호는 하나 이상의 IF 증폭기단들을 포함하는 IF 증폭회로 110에 결합된다. 증폭된 IF 신호는 증폭이 변조된 합성비데오신호를 나타나내는 비데오 검파기 140에 결합된다. 이 비데오 신호는 AGC 회로 20과 다른 신호처리회로(도시하지 않음)용 증폭된 합성비데오신호를 만드는 비데오 증폭기 4에 공급된다.

비데오 증폭기 4는 저령저항기 6과 바이패스 캐패시터 8을 포함하는 저역통과 퀼터에 의해 AGC 회로 20의 입력단자 12에 합성비데오신호를 제공한다. 단자 12에서의 합성비데오신호는 기준전위원(접지)에 연결된 콜렉터전극을 갖고 있는 트랜지스터 101의 베이스에 연결된다. 합성비데오신호는 트랜지스터 101의 에미터로부터 능동휠터지연회로 50, 임계잡음변환기 30, 및 AGC 회로 20에 결합된다. 트랜지스터 101용 공급전압은, 트랜지스터 101의 에미터로부터 공급전압원(+B)까지 결합된 저항기 114에 의해 갖추어진다.

D.C. 임계잡음반전기는 D.C. 임계값을 넣는 합성비데오신호내의 임펄스잡음에 응답하여 반전된 잡음 펄스를 만든다. 이 반전된 잡음펄스는 합성비데오신호내의 임펄스잡음의 삭제로 인하여 능동휠터지연회로 50에 의해 지연된 합성비데오신호와 합성된다. 이 잡음-해제 비데오신호는 동기신호가 발생하는 동안 피아크검파 동기분리기 40에 결합된다. 궤환캐패시터 46은 합성비데오신호의 동기신호성분들의 선단연부의 이송시간을 개량하기 위해서 능동휠터지연회로 50에 동기분리기의 입력에서의 비데오신호를 결합시킨다.

이 능동지연회로 50과 D.C. 임계잡음반전기 30은 1978년 8월 18일에 제이·알·하포드가 “잡음제거회로”란 제목으로 출원한 미합중국 특허원 제934,829호에 더욱 상세히 기술되어 있다. 피아크검파 동기분리기 40은 1978년 8월 18일에 제이·알·하포드가 “동기신호분리기회로”란 제목으로 출원한 미합중국 특허원 제934,821호에 상세하게 기술되어 있다.

동기분리기 40에 의해 생긴 동기신호들은 래칭회로 70에 결합된다. 이 래칭회로는 예를들어 수평편향 시스템내의 변압기(도시하지 않음)로부터 유도되는 키잉펄스원 54로부터 수평커션 펄스들을 수신한다. 이 수평커션 펄스들은 통상적으로, 동기신호들과 인접해 있고 도전체 264상의 AGC 회로 20에 대한 키잉신호를 발생시키기 위해서 래칭회로 70에 의해 합성된다. 수평커션 펄스들이 동기신호와 인접해 있지 않으면, 비-동기신호(out-of-sync signal)는 커션펄스들에 응답하여 도전체 266에 의해 AGC 회로에 결합된다. 이 래칭회로 70은 1978년 8월 18일에 제이·알·하포드가 “AGC 키잉신호회로”란 제목으로 출원한 미합중국 특허원 제934,835호에 상세하게 기술되어 있다.

트랜지스터 101의 에미터에서 나타난 비데오 신호는 트랜지스터 302과 304를 포함하는 입력증폭기에 저항기 306에 의해서 결합된다. 트랜지스터 302의 에미터의 전극은 저항기 308에 의해 접지로 결합되고 이것의 콜렉터전극은 트랜지스터 304의 베이스에 결합된다. 트랜지스터 302의 콜렉터 전압은, 콜렉터 전극이 +B 공급원에 결합되고 에미터전극이 저항기 312에 의해 트랜지스터 302의 콜렉터에 결합된 트랜지스터 314에 의해 갖추어진다. 트랜지스터 314의 바이어스 전류는, 트랜지스터 314의 베이스와 +B 공급원 사이에 결합된 저항기 316과, 트랜지스터 314의 베이스로부터  $V_{be}$  공급원 80에 결합된 저항기 318에 의해 갖추어진다.  $V_{be}$  공급원 80은 이미 참조한 미합중국 특허원 제934,829호에 상세하게 기술되어 있다.

반전된 비데오 신호는 트랜지스터 302의 콜렉터로부터 에미터 폴로워 형태로 접속된 이중-에미터 트랜지스터인 트랜지스터 320의 베이스에 결합된다. 트랜지스터 320의 콜렉터는 +B 공급원에 결합되고, 한 에미터전극은 트랜지스터 328의 콜렉터에 결합되며 다른 에미터전극은 저항기 322에 의해 트랜지스터 328의 베이스에 결합된다. 트랜지스터 328은 접지에 결합된 에미터전극과 순방향 바이어스된 다이오드 326과 저항기 324에 의해 접지에 결합된 베이스 전극을 갖고 있다.

트랜지스터 320의 제1에미터와 트랜지스터 328의 콜렉터 사이의 접합은 저항기 322에 의해 피아크 검파

기 캐패시터 330에 결합된다. 캐패시터 330은 저항기 332와 접지 사이에 결합된다. 또한, 저항기 322와 캐패시터 330의 접합부에 샘플링 트랜지스터 370의 베이스와 다이오드 340의 애노드가 결합된다. 다이오드 340은 저항기 342, 344 및 346의 이것의 캐소드전극으로부터 접지까지의 직렬결합에 의해 캐패시터 330을 제어 가능한 방전통로를 제공한다. 샘플링트랜지스터 370은 접지에 결합된 콜렉터전극과 트랜지스터 372의 베이스에 결합된 에미터전극을 갖고 있다.

래칭회로 70으로부터 나온 도전체 362상의 키잉펄스는 AGC 회로가 동작하게 키이하도록 스위칭 트랜지스터 350의 베이스 전극에 결합된다. 트랜지스터 350은 +B 공급원에 결합된 콜렉터전극과, 저항기 342와 344의 접합부에 결합된 에미터전극을 갖고 있다. 저항기 344와 346의 접합부는 트랜지스터 352의 베이스 전극과 다이오드 348의 애노드 전극에서의 전류 밀러(mirror)에 결합된다. 다이오드 348의 캐소드와 트랜지스터 352의 에미터 전극은 접지에 결합된다. 트랜지스터 352의 콜렉터전극은, 저항기 356과 트랜지스터 360의 베이스와의 접속점에 결합된다. 저항기 356은 +B 공급원에 결합된 애노드 전극을 갖고 있는 다이오드 354의 캐소드에 결합된다.

PNP 트랜지스터 360은 AGC 휠터 캐패시터 24용 전류원을 제공하고, 저항기 362에 의해 +B 공급원에 결합된 에미터전극과 단자 22에서 AGC 휠터 캐패시터에 결합된 콜렉터전극을 갖고 있다. 단자 22는 텔레비전 수신기내의 IF 및 RF 증폭단 120 및 130에 AGC 제어전압을 결합시키는 AGC 이송회로 400에도 결합된다.

도전체 264로부터의 키잉펄스는 저항기 374와 트랜지스터 380의 베이스와의 접합부에 결합된 콜렉터전극을 갖고 있는 트랜지스터 372의 에미터에 결합된다. 저항기 374는 다이오드 376의 애노드와 도전체 266에 결합된다. 다이오드 376의 캐소드는 접지에 결합된다.

NPN 트랜지스터 380은 AGC 휠터 캐패시터 24용 전류 싱크(sink)와 전류원 트랜지스터 360에 의해 공급된 전류를 갖추고 있다. 트랜지스터 380은 그의 접지에 결합된 에미터 전극과, AGC 휠터 캐패시터와 단자 22에서 트랜지스터 360의 콜렉터에 결합된 콜렉터전극을 갖고 있다.

동작할 때, 동기신호성분을 포함하고 있는 부행비데오신호는 트랜지스터 101에 의해 반전입력 트랜지스터 302의 베이스에 결합된다. 트랜지스터 302는 동기신호성분의 정행신호로 나타나는 곳에서 트랜지스터 320의 베이스에 이 동기신호성분만을 효과적으로 결합시키도록 바이어스된다. 약한 비데오신호나 주로 백색레벨 비데오정보를 포함하고 있는 정상적인 비데오신호는 트랜지스터 302가 포화상태로 되게 한다. 트랜지스터 302가 포화되고 이 트랜지스터의 콜렉터전극상의 전압이 이 트랜지스터의 에미터전극의 전압레벨로 떨어지면, 베어스 전류는 트랜지스터의 콜렉터로 주입되고 이 트랜지스터의 콜렉터전압이 다시 증가하게 된다. 이 과포상태는 피이크 검파기 캐패시터 330상에서 부정확한 신호레벨을 검파하므로서 야기된다. 이 바람직하지 못한 동작상태는, 트랜지스터 302가 포화레벨로 된 후에 트랜지스터 302의 콜렉터로부터 이것의 베이스-콜렉터 통로를 통하여 접지로 떨어지는 과대전류를 도통시키도록 작용하는 트랜지스터 304에 의해 방지된다.

트랜지스터 314는 트랜지스터 320의 베이스의 반전된(즉 정행) 비데오 신호의 최대전압을 8V로 제한한다. 이 전압크램프(clamp)는 피이크 검파기 캐패시터 330의 항복전압(break down voltage)이 8V를 넘지 않게 한다.

트랜지스터 320의 베이스에서의 정의 동기신호성분은 피이크 검파기 캐패시터 330이 비데오 신호의 동기신호성분의 진폭으로 충전하도록 트랜지스터가 저항기 332를 통하여 전류를 도통시킨다. 동기 팀(tip)들의 최대 진폭은 캐패시터 330상에 축적된다. 트랜지스터 350의 베이스에 인가된 키잉펄스는, 키잉펄스의 기간동안 트랜지스터 350이 바이어스 다이오드 340를 반대로 동작시키게 한다. 이것은 키잉펄스 기간동안 다이오드 340과 저항기 342, 344 및 346을 통하여 캐패시터 330이 방전하는 것을 방지한다.

캐패시터 330을 트랜지스터 320의 베이스에서의 동기펄스의 전압레벨로 충전하면, 트랜지스터 320의 제1에미터에서의 임피던스가 증가한다는 것을 알았다. 임피던스가 증가하면 지수비가 감소해서 캐패시터 330이 등화펄스와 같은 짧은 동기펄스에 대한 동기팀 이하의 값으로 충전된다.

그러므로 캐패시터 330상에 축적된 전압레벨은 펄스진폭 대신에 동기펄스기간과 진폭의 함수로 된다.

이 문제는 트랜지스터 320의 제2에미터에 의해 제어되는 본 발명의 트랜지스터 328의 동작에 의해서 해결된다. 트랜지스터 320은 이것의 두 에미터전극을 통하여 전류를 도통시키고, 트랜지스터 328은 트랜지스터 320의 제2에미터에서 나온 전류에 의해 도전상태로 구동된다. 트랜지스터 320의 제1에미터 전극에 의해서 갖추어진 전류는 캐패시터 330을 충전하는 동안 트랜지스터 328의 콜렉터와 저항기 332 사이로 나누어진다. 처음에, 트랜지스터 320에 의해 갖추어진 대부분의 전류는 캐패시터 330으로 흐르고 트랜지스터 320의 임피던스는 낮다. 캐패시터 330이 동기 팀레벨을 향해 충전되면, 이것은 트랜지스터 320으로부터 충전전류를 덜 유도하고 트랜지스터 320의 임피던스가 증가하게 된다. 트랜지스터 328은 베이스 전극이 트랜지스터 320의 베이스에서의 신호에 의해 트랜지스터 320의 베이스-에미터 강하보다 작게 구동되기 때문에 트랜지스터 328은 충전기간 전반에 걸쳐 대략 동일한 전류량을 유출시키도록 계속 동작한다. 그러므로, 트랜지스터 328은 동기펄스기간용 전류싱크로 작용하고, 트랜지스터 328에 의해 유도된 전류는 트랜지스터 320의 임피던스가 저항기 332의 임피던스보다 낮은 레벨로 증가하도록 제한한다. 이 낮은 임피던스는 캐패시터 330이 이것의 기간에 관계없이 동기펄스의 피이크진폭으로 신속하게 충전되게 한다.

동기펄스의 끝에서, 트랜지스터 320과 328은 도통 상태가 중단되고, 캐패시터 330은 다이오드 340을 통해 방전될 때까지 동기팀을 나타내는 충전레벨로 된다.

TV 진폭을 갖고 있는 동기펄스가 트랜지스터 320의 베이스에 인가되면, 트랜지스터의 에미터전극에 6.4V 레벨이 나타나고, 이 레벨은 피이크 검파기의 캐패시터 330과 저항기 332에 인가된다. 피이크 검파기에 동기펄스가 인가되기 전에 캐패시터 330이 방전되기 때문에 트랜지스터 320의 제1에미터에 의해 갖추어진 초기 충전전류는 3mA이고, 에미터 임피던스는 약 12Ω이다. 캐패시터 330 양단의 전압이 이 충전전류에 의해 증가되면, 충전전류는 지수적으로 감소하고 트랜지스터 320의 에미터 임피던스는 증가한다.

이 시간에 캐패시터 330은 6.4V의 피이크값의 98.4%인 6.3V 레벨로 되고 이 충전전류는 트랜지스터 328

의 효과를 무시한 트랜지스터 320의 제1에미터 전극에서의 임피던스가 약 500 $\Omega$ 으로 증가하도록 감소된다.

이 임피던스는 저항기 322의 2000 $\Omega$  임피던스에 비교된 것처럼 뚜렷하다. 그러나 트랜지스터 328을 고려하면, 트랜지스터 320의 베이스에서의 TV 동기펄스는, 트랜지스터 328의 공통 도전상태로 되도록 트랜지스터의 제2에미터전극을 통하여 1mA 전류가 흐르게 한다는 것을 알 수 있다.

트랜지스터 328은 동기펄스의 기간동안 이것의 콜렉터-에미터 통로를 통하여 일정한 1/2mA 전류가 도통되게 한다. 이 전류흐름의 효과는 트랜지스터 320의 제1에미터전극에서의 임피던스가 저항기 332의 2000 $\Omega$ 에 비교된 바와 같이 무시될 수 있어서 캐패시터 330을 충전하는 것이 더욱 선형비로 되게 하는 50 $\Omega$ 의 최대값으로 고정되게 하는 것이다.

상기에 언급한 바와 같이, 래칭회로 70에서 나온 키잉펄스는 트랜지스터 350이 역바이어스 다이오드 340을 동작시키게 한다. 트랜지스터 350은 트랜지스터 352의 베이스에 전류를 도통시켜서 이 트랜지스터가 동작되게 한다.

트랜지스터 350의 에미터에서 정류된 키잉신호의 레벨은, 이 레벨이 트랜지스터 370과 372의 베이스-에미터 전압에 의해  $2V_{be}$  (1.2V)로 변환되고 트랜지스터 350의 베이스-에미터 접합에 의해  $V_{be}$ 로 변환되는 것과 같이, 캐패시터 330의 전압레벨에 의해서 일부가 결정된다.

그러므로 트랜지스터 352의 베이스에 도통된 전류는 캐패시터 330상에 축적된 동기팁레벨 전압의 함수이다.

트랜지스터 352가 도통하면 트랜지스터 360이 도통하게 되므로, AGC 휠터 캐패시터 24에 충전전류를 공급한다. 트랜지스터 360에 의해 도통된 일부 또는 전체의 충전 전류는 하기애 기술하는 바와 같이 전류싱크 트랜지스터 380에 의해 AGC 휠터 캐패시터로부터 떨어져서 도통상태로 된다.

래칭회로 70에 의해 공급된 키잉펄스는 트랜지스터 372용 에미터 전류원을 갖춘다. 트랜지스터 372의 베이스는 피이크 검파기 캐패시터 330상에 축적된 전압레벨에 의해 결정된 신호를 갖는 트랜지스터 370의 에미터에 결합된다. 트랜지스터 370은 트랜지스터 372가 비교적 큰 베이스 전류를 필요로 하는 낮은 베타(bata) 트랜지스터이기 때문에 캐패시터 330과 트랜지스터 372의 베이스 사이에 결합된다.

트랜지스터 370은 캐패시터 330 상에 축적된 전하에 악영향을 미치지 않는 비교적 작은 베이스 전류를 필요로 하는 높은 베타 트랜지스터이다.

트랜지스터 372의 에미터-콜렉터 통로를 통하여 흐르는 전류는 전류싱크 트랜지스터 380이 도통하도록 이 트랜지스터의 베이스에 결합된다. 전류싱크 트랜지스터 380은, 약한 신호 상태에서 수신기의 이득이 증가될 때 AGC 휠터 캐패시터 24가 접지를 통해 방전하도록 작용한다. 이 신호상태하에서, 전류원 트랜지스터 360은 전류싱크 트랜지스터 380에 의해 도전된 것보다 작은 충전 전류를 공급하므로, AGC 휠터 캐패시터 24가 순수하게 방전하게 된다. 비데오 신호의 동기팁이 적당한 전압레벨로 있고 AGC 이득교정이 필요없으면, 전류원 트랜지스터 360에 의해 공급된 전류는 전류싱크 트랜지스터 380에 의해 도통된 전류를 정확하게 정합시키므로, AGC 휠터 캐패시터상의 전압레벨이 순수하게 변하지 않게 한다. 이 정합된 공급원과 싱크전류들은 AGC 휠터 캐패시터 24상의 전압레벨에 관계없이 동일한 크기로 된다.

래칭회로 70이 키잉기간 사이의 동작상태로 AGC 회로 20을 키잉하지 않으면, 트랜지스터 320은 캐패시터 330이 잡음 펄스의 최대진폭으로 충전하도록 하므로서 임펄스 잡음에 응답하여 동작한다. 피이크 검파기 캐패시터 330은 이때 다소의 전하를 보유하지 않는다. 왜냐하면, 트랜지스터 350이 도통하지 않고, 캐패시터 330이 저항기 342, 344 및 346을 통하여 접지로 계속 방전할 때 다이오드 340이 순방향 바이어스되기 때문이다. 이 방전 통로는 비데오 소인선 기간동안 캐패시터 330상에 임펄스 잡음펄스가 보유되지 않게 하고, 연속 키잉기간동안 AGC 회로 20이 이 보유된 전하에 응답하여 잘못 셋업되게 한다.

그러므로 이 방전통로는 AGC 회로 20내에 합성잡음보호회로의 필요성을 제거한다.

본 발명은 자동이득 제어회로 상태에서 설명되었지만, 본 발명은 디지털 전압계용 피이크 검파회로와 같은 다른 실시예에서도 똑같이 적용될 수 있다.

### (57) 청구의 범위

#### 청구항 1

도면에 도시하고 본문에 상술한 바와 같이, 충전임피던스에 직렬로 결합된 캐패시터를 포함하고 진폭변화신호의 최대편암에 응답하기에 적당한 시정수를 갖고 있는 회로를 포함하는 진폭변화신호의 최대편차를 검파하기 위한 피이크 검파샘플 및 유지회로에 있어서, 특히, 진폭변화신호의 최대편차를 통하여 캐패시터를 충전하기 위하여 충전임피던스에 결합된 출력단자와 진폭변화신호를 수신하기 위한 입력단자를 갖고 있는 반도체장치(320)과 반도체장치가 캐패시터를 충전하지 않을 때 전류가 흐르지 않게 하고 캐패시터를 충전하는 동안 캐패시터 충전전류에 보상되는 반도체를 통하는 전류성분을 흐르게 하기 위해 반도체 장치의 출력단자에 결합되고 반도체 장치의 입력단자에서의 진폭변화신호에 응답하는 제어가능한 전류싱크(328)를 특징으로 하는 피이크 검파기회로.

#### 도면

## 도면1

## 도면2

## 도면3