April 19, 1949.

C. E. HALLMARK

2,467,476

## FREQUENCY DIVIDER CIRCUIT

Filed Oct. 17, 1945

—

FIG.

FIG. 2

**INVENTOR**

CLYDE E. HALLMARK

BY

BY

**ATTORNEY**

## UNITED STATES PATENT OFFICE

2,467,476

## FREQUENCY DIVIDER CIRCUIT

Clyde E. Hallmark, Fort Wayne, Ind., assignor,

by mesne assignments, to Farnsworth Research

Corporation, a corporation of Indiana

Application October 17, 1945, Serial No. 622,730

7 Claims. (Cl. 172—281)

1

This invention relates to frequency divider circuits, and more particularly relates to a pulse operated electrical counter circuit arranged for developing output pulses at a frequency which is a submultiple of that of the input pulses.

Frequency divider circuits find wide application whenever it is desired to develop an output signal at a subharmonic of the frequency of an input signal. Frequency divider circuits or electrical counters are used, for example, in the timing unit of a television transmitter. A television timing unit is arranged to develop control signals such as blanking and synchronizing pulses recurring at the line and field frequencies. The line or horizontal synchronizing signal and the field or vertical synchronizing signal have a frequency of, for example, 15,750 cycles per second and of 60 cycles per second, respectively, in accordance with the present standards adopted by the Radio Manufacturers Association. In the timing unit of a television transmitter, waves at a frequency of 15,750 cycles are developed which must be synchronized with the 60 cycle power input. To this end the frequency of 15,750 cycles is doubled and then divided to derive a 60 cycle output signal which is compared with the 60 cycle input power supply by means of a frequency correction circuit. Thus, the vertical and horizontal synchronizing signals are synchronized at all times.

The frequency divider circuit forming part of a television timing unit conventionally comprises a chain of, for example, four multivibrators each being associated with an insulating amplifier stage. A circuit of this type is reliable in its operation but is comparatively complicated and requires a large number of amplifier tubes as well as a considerable number of frequency divider stages. Another drawback of a conventional counter circuit comprising a chain of multivibrators is that each multivibrator must be tuned or adjusted to oscillate at a predetermined frequency.

It is an object of the present invention, therefore, to provide a frequency divider circuit that is simpler than prior art frequency dividers and permits a substantial count-down ratio of the frequency of the input pulses compared to the frequency of the output pulses.

Another object of the invention is to provide an electrical counter circuit which need not be tuned or adjusted to the fundamental frequency to be divided or a subharmonic thereof, and which will permit, therefore, to derive output pulses at a subharmonic of the frequency of the input pulses in any frequency range.

2

A further object of the invention is to provide a frequency divider circuit comprising a plurality of gas diodes of the cold cathode type.

In accordance with the present invention, there is provided a frequency divider circuit comprising a plurality of unilaterally conducting devices of predetermined breakdown voltage and connected in series. A plurality of storage condensers are provided each of which is connected in shunt between a fixed reference potential source and the input of one of the unilaterally conducting devices. Means are provided for applying spaced pulses of a predetermined voltage across the first storage condenser. The capacitances of the storage condensers increase progressively from the first to the last condenser so that each of the unilaterally conducting devices is rendered conducting when the condenser in its input circuit has reached the predetermined breakdown voltage with respect to the reference potential. Finally, means are provided for deriving output pulses at a submultiple of the frequency of the input pulses.

For a better understanding of the invention, together with other and further objects thereof, reference is made to the following description, taken in connection with the accompanying drawing, and its scope will be pointed out in the appended claims.

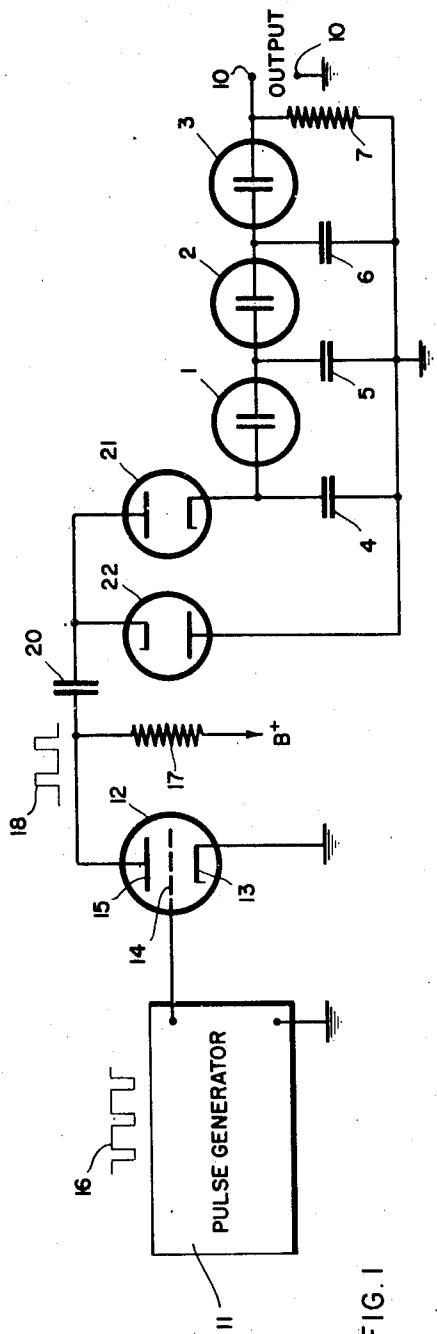

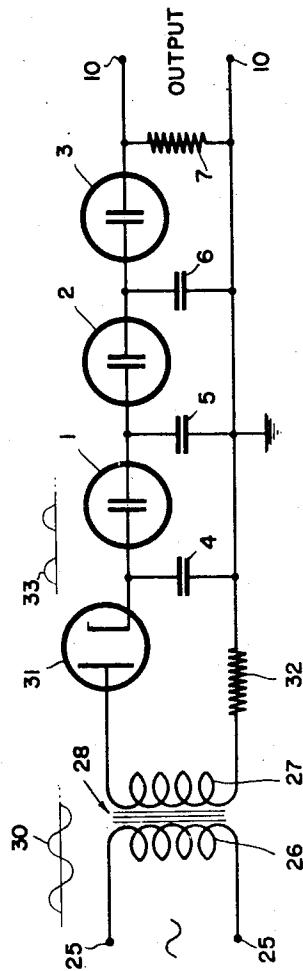

30 In the accompanying drawing, Fig. 1 is a circuit diagram of a frequency divider circuit embodying the present invention, while Fig. 2 is a circuit diagram of a modified frequency divider circuit in accordance with the invention.

35 Referring now more particularly to Fig. 1 of the drawing, there is provided a frequency divider circuit comprising three unilaterally conducting devices 1, 2 and 3 connected in series. Unilaterally conducting devices 1, 2 and 3 have a predetermined break-down voltage and preferably are gas diodes of the cold cathode type such, for example, as neon lamps. Three storage condensers 4, 5 and 6 are individually connected in shunt between ground, as indicated, and the input of diodes 1, 2 and 3, respectively. Load resistor 7 is connected between ground and the output of gas diode 3 for developing the output signal which may be obtained from terminals 10.

Means are provided for applying spaced pulses of positive voltage across the first storage condenser 4. To this end there has been illustrated a conventional circuit comprising pulse generator 11 connected to amplifier tube 12. Amplifier tube 12 may be a triode as illustrated or a pentode. Amplifier tube 12 comprises cathode 13

which is grounded as shown, control grid 14 connected to pulse generator 11 and anode 15. Pulse generator 11 develops voltage pulses of negative polarity with respect to ground, as illustrated at 16. Amplifier 12 is arranged to be normally conducting. However, when a pulse 16 of negative polarity is developed by pulse generator 11 and impressed upon control grid 14, the space current in amplifier 12 terminates. Anode 15 is connected to anode supply B+ through anode resistor 17.

One terminal of charging condenser 20 is connected to anode 15. The other terminal of condenser 20 is connected to the anode of high vacuum diode 21 and the cathode of high vacuum diode 22, both diodes being arranged in parallel. The cathode of high vacuum diode 21 is connected to the input of gas diode 1 and to storage condenser 4, while the anode of high vacuum diode 22 is connected to ground.

The frequency divider circuit illustrated in Fig. 1 operates as follows. It may be assumed that initially condensers 20, 4, 5 and 6 are all discharged. Amplifier tube 12 is arranged to be normally conducting, as pointed out hereinabove. Accordingly, the space current flowing through anode resistor 17 develops a voltage drop thereacross which is impressed upon charging condenser 20. Upon the arrival of a negative pulse 16 of sufficient amplitude on control grid 14, amplifier 12 ceases to conduct space current. Consequently, the voltage impressed upon charging condenser 20 is now equal to anode supply voltage B+ because no current flows through anode resistor 17. The positive voltage pulses developed across anode resistor 17 are indicated at 18.

High vacuum diode 21 now begins to conduct space current until the charge remaining on charging condenser 20 equals that of storage condenser 4. Upon the termination of a pulse 16, amplifier 12 again begins to conduct space current whereupon the voltage applied to charging condenser 20 is reduced. Charging condenser 20 is now discharged through high vacuum diode 22 and amplifier 12 connected in series. The right hand terminal of condenser 20 connected to high vacuum diodes 21 and 22 is brought substantially to ground potential.

It will be seen that each time a pulse 16 is impressed upon control grid 14 a certain charge is applied to storage condenser 4 through charging condenser 20. The charge applied to charging condenser 20 and storage condenser 4 is independent from the amplitude of input pulses 16 as long as the pulses are able to swing control grid 14 sufficiently negative to interrupt space current flowing through amplifier tube 12. The voltage impressed upon charging condenser 20 depends primarily upon the voltage of the anode supply B+.

Each gas diode 1, 2 and 3 has a predetermined break-down voltage. As soon as the potential of storage condenser 4, for example, has reached that break-down voltage with respect to ground, gas diode 1 begins to conduct. The charge which storage condenser 4 receives during the arrival of each pulse 16 depends upon the value of anode supply voltage B+ and the capacitances of charging condenser 20 and storage condenser 4, as is well known in the art. Thus, after one or more predetermined number of pulses 16 the voltage across storage condenser 4 will be sufficient to break down gas diode 1. Gas diode 1 will continue to conduct space current until the voltages on storage condensers 4 and 5 are substantially

equal. It is to be understood, of course, that gas diode 1 will cease to conduct space current when the voltage across storage condenser 4 equals that across storage condenser 5 minus the extinguishing voltage of gas diode 1.

After a predetermined number of input pulses 16 the voltage across storage condenser 5 will be sufficient to break down gas diode 2 whereupon storage condenser 6 begins to charge up in steps through gas diode 2. Finally when storage condenser 6 has reached the break-down voltage, all three gas diodes 1, 2 and 3 will conduct space current so that storage condensers 4, 5 and 6 are discharged simultaneously through load resistor 7 and ground. It will be understood that the count-down ratio of the frequency divider of the invention, that is the ratio of the frequency of input pulses 16 to that of the output pulses obtained from terminals 10, depends upon the capacitances of condensers 20, 4, 5 and 6. The capacitances of condensers 4, 5 and 6 should increase progressively so that the capacitance of condenser 6 divided by the capacitance of condenser 4 is equal to the count-down ratio provided that gas diode 1 fires each time an input pulse 16 is received. Otherwise the count-down ratio of the frequency of input pulses 16 compared to that of the pulses developed between ground and the output of diode 1 must be taken into account.

For a count-down ratio of 60:1 storage condensers 4, 5 and 6 may, for example, have a capacitance of .01, .1 and .6 microfarad, respectively. It may be assumed that every input pulse 16 will charge storage condenser 4 sufficiently to break down gas diode 1. After ten pulses, storage condenser 5 will have a voltage sufficient to fire gas diode 2. After sixty pulses the voltage of storage condenser 6 will be sufficient to fire gas diode 3. In that case diodes 1, 2 and 3 conduct space current simultaneously, thus discharging storage condensers 4, 5 and 6 through load resistor 7 and ground. The output pulses at one-sixtieth the frequency of the input pulses appear across load resistor 7 and may be obtained from output terminals 10. It is to be understood that any number of gas diodes may be connected in series and shunted individually by storage condensers, the number of gas diodes and condensers depending upon the desired count-down ratio.

Referring now to Fig. 2, in which like components are designated by the same reference numerals as where used in Fig. 1, there is illustrated a modified frequency divider circuit. The frequency divider circuit of Fig. 2 again comprises three gas diodes 1, 2 and 3 arranged in series and shunted individually by storage condensers 4, 5 and 6. The input pulses are impressed upon the first storage condenser 4 through a half wave rectifier circuit. An alternating current source is connected to terminals 25, and voltage variations are impressed upon primary winding 26 inductively coupled to secondary winding 27 of transformer 28. The input signal may be of sinusoidal form as shown at 30. One terminal of secondary winding 27 is connected through high vacuum diode 31 to storage condenser 4 and gas diode 1. The other terminal of secondary winding 27 is connected to ground through load resistor 32. The pulses appearing across the output of high vacuum diode 31 are illustrated at 33. It will be understood that high vacuum diode 31 is arranged as a half wave rectifier.

The frequency divider circuit of Fig. 2 operates as follows. Each pulse 33 impressed upon storage

condenser 4 will charge it to a certain voltage which preferably is equal to the break-down voltage of gas diode 1. Accordingly, every time a pulse 33 is impressed upon storage condenser 4 gas diode 1 fires and storage condenser 5 receives a certain charge. After a predetermined number of steps the voltage of storage condenser 5 has reached the break-down voltage of gas diode 2 which thereupon begins to fire and charge storage condenser 6. Finally storage condenser 6 will reach the break-down voltage of gas diode 3, whereupon all three gas diodes 1, 2 and 3 will conduct space current and discharge storage condensers 4, 5 and 6 through load resistance 7.

While there has been described what is at present considered the preferred embodiment of the invention, it will be obvious to those skilled in the art that various changes and modifications may be made therein without departing from the invention, and it is, therefore, aimed in the appended claims to cover all such changes and modifications as fall within the true spirit and scope of the invention.

What is claimed is:

1. A frequency divider circuit comprising a plurality of charge storage elements, means for applying pulses to a first one of said elements, means for connecting each of said elements with a succeeding element whenever the preceding element has received a predetermined number of charges, and means for discharging simultaneously all of said elements whenever the last one of said elements has received a predetermined number of charges.

2. A frequency divider circuit comprising a plurality of storage condensers, means for applying spaced pulses across the first one of said condensers, unilaterally conducting devices for connecting each of said condensers with a succeeding condenser whenever the preceding condenser has received a predetermined number of charges, and means including said unilaterally conducting devices for discharging simultaneously all of said condensers whenever the last one of said condensers has received a predetermined number of charges.

3. A frequency divider circuit comprising a plurality of unilaterally conducting devices of predetermined break-down voltage and connected in series, a source of fixed reference potential, a plurality of storage condensers each being connected between said source of reference potential and the input of one of said devices, means for applying spaced pulses of a predetermined voltage across the first storage condenser, the capacitances of said condensers increasing progressively from the first to the last condenser, thereby to render each of said devices conducting when the condenser in its input circuit has reached said break-down voltage with respect to said source of reference potential, and means for deriving output pulses at a submultiple of the frequency of said input pulses.

4. A frequency divider circuit comprising a plurality of gas diodes of predetermined break-down voltage and connected in series, a source of fixed reference potential, a plurality of storage condensers each being connected between said source of reference potential and the input of one of said diodes, means for applying spaced pulses of a predetermined voltage across the first storage condenser, the capacitances of said condensers increasing progressively from the first to

the last condenser, thereby to render each of said diodes conducting when the condenser in its input circuit has reached said break-down voltage with respect to said source of reference potential, and means for deriving output pulses at a submultiple of the frequency of said input pulses from the last of said diodes.

5. A frequency divider circuit comprising a plurality of cold cathode gas diodes of predetermined break-down voltage and connected in series, a source of fixed reference potential, a plurality of storage condensers each being connected between said source of reference potential and the input of one of said diodes, means for applying spaced pulses of a predetermined voltage across the first storage condenser, the capacitances of said condensers increasing progressively from the first to the last condenser, thereby to render each of said diodes conducting when the condenser in its input circuit has reached said break-down voltage with respect to said source of reference potential, and means for deriving output pulses at a submultiple of the frequency of said input pulses from the last of said diodes.

6. A frequency divider circuit comprising a plurality of unilaterally conducting devices of predetermined break-down voltage and connected in series, a source of fixed reference potential, a plurality of storage condensers each being connected between said source of reference potential and the input of one of said devices, means for applying spaced pulses of a predetermined voltage across the first storage condenser, the capacitances of said condensers increasing progressively from the first to the last condenser, thereby to render each of said devices conducting when the condenser in its input circuit has reached said break-down voltage with respect to said source of reference potential, and a load impedance connected between said source of reference potential and the last of said devices for deriving output pulses at a submultiple of the frequency of said input pulses.

7. A frequency divider circuit comprising a plurality of gas diodes of predetermined break-down voltage and connected in series, a source of fixed reference potential, a plurality of storage condensers each being connected between said source of reference potential and the input of one of said diodes, means for applying spaced pulses of a predetermined voltage across the first storage condenser, the capacitances of said condensers increasing progressively from the first to the last condenser, thereby to render each of said diodes conducting when the condenser in its input circuit has reached said break-down voltage with respect to said source of reference potential, and a load impedance connected between said source of reference potential and the last of said diodes for deriving output pulses at a submultiple of the frequency of said input pulses.

CLYDE E. HALLMARK.

#### REFERENCES CITED

The following references are of record in the file of this patent:

#### UNITED STATES PATENTS

| Number    | Name     | Date          |

|-----------|----------|---------------|

| 1,933,976 | Hanson   | Nov. 7, 1933  |

| 2,294,863 | Hadfield | Sept. 1, 1942 |

| 2,398,097 | Kent     | Apr. 9, 1946  |