RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 463 454**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21) **N° 79 20072**

(54) Dispositif de recherche de faute de logiciel pour système de traitement de données à programme enregistré.

(51) Classification internationale (Int. Cl.<sup>3</sup>). G 06 F 11/28.

(22) Date de dépôt ..... 6 août 1979.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du public de la demande ..... B.O.P.I. — « Listes » n° 8 du 20-2-1981.

(71) Déposant : Société anonyme dite : COMPAGNIE GENERALE DE CONSTRUCTIONS TELEPHONIQUES, résidant en France.

(72) Invention de : Jean-Michel Antoine, Philippe Decaesteke et Patrice Bernard Graff.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Jean Pothet,

251, rue de Vaugirard, 75740 Paris Cedex 15.

La présente invention concerne la recherche des fautes dans le programme des systèmes de traitement de données à programme enregistré et a pour objet un traceur de programme, dispositif connecté à un système de traitement de données à programme enregistré en exploitation, afin de prélever et d'enregistrer des informations circulant dans ce système. Lorsque survient une défaillance ou une condition anormale du système, ces informations sont disponibles pour la recherche de la faute de programme qui en est la cause. L'invention sera particulièrement utile dans le cas des systèmes de commutation à commande par calculateur à programme enregistré et notamment des systèmes de commutation téléphoniques de ce type.

La recherche des fautes dans les programmes opérationnels des calculateurs de commande des systèmes de commutation électronique à programme enregistré est une tâche des plus difficiles. Cette recherche est d'autant plus difficile que les programmes sont complexes, de taille importante (environ  $10^5$  instructions) et qu'il est pratiquement impossible, avant la mise en exploitation du logiciel, d'avoir trouvé toutes les fautes qu'il contient, par les moyens d'essais des programmes sur maquette ou en simulation d'environnement tels qu'ils sont réalisés en laboratoire.

Les erreurs qui subsistent après ces essais sont en général des erreurs subtiles, insidieuses qui n'apparaîtront parfois qu'après plusieurs mois de fonctionnement.

Un moyen connu de trouver de telles fautes dans les programmes d'un calculateur en exploitation consiste à disposer d'un appareil, appelé traceur, pourvu d'une mémoire rapide et capable d'enregistrer en permanence les événements logiciels se produisant en certains endroits du système : cette mémoire est remplie d'une façon continue par les données nouvelles et se vide de ses données les plus anciennes, de telle sorte qu'elle contienne en permanence une image des événements logiciels qui se sont produits dans les quelques dernières millisecondes de fonctionnement.

Un tel moyen est bien souvent inefficace : on enregistre lors de l'opération de contrôle ou traçage un nombre considérable d'informations sans rapport avec la faute que l'analyse devra éliminer. D'autre part, la capacité de la mémoire étant limitée, les informations qu'elle contient ne concernent, comme on vient de le voir, qu'un intervalle de temps très réduit. Dans la plupart des cas, il est alors impossible de déterminer l'origine de la faute qui se situe dans un passé bien plus reculé.

Pour pallier cet inconvénient, certains traceurs fonctionnent selon un mode de traçage sélectif : par l'intermédiaire d'une console de commande, l'opérateur précise les conditions de démarrage, d'enregistrement et d'arrêt du traceur. Ce dernier, connecté sur la ligne omnibus de transfert, ou bus,

d'adresse mémoire du calculateur reçoit en permanence les adresses de lecture d'instruction, ainsi que les adresses d'indirection, de lecture et d'écriture de données. Le démarrage, l'enregistrement et l'arrêt du traceur sont alors fonction des adresses d'instruction, d'indirection ou de données qui sont

5 comparées à l'adresse affichée sur la console. On limite ainsi l'enregistrement dans la mémoire du traceur aux informations circulant sur le bus d'adresse mémoire du calculateur répondant à certains critères particuliers (adresse identique à l'adresse affichée sur la console ou, par exemple, adresse comprise entre deux adresses affichées). Un tel dispositif est décrit notamment dans

10 l'article "Traceur pour calculateurs 3200 et 3202" de J.S. de BRITO & al. publié dans la revue française "COMMUTATION & ELECTRONIQUE" N° 59 (Octobre 1977).

Dans ce traceur, chaque adresse transmise sur le bus d'adresse mémoire du calculateur est inscrite dans un registre connecté à ce bus puis

15 transmise à une entrée d'un comparateur dont l'autre entrée reçoit l'adresse affichée par l'opérateur et préalablement mémorisée dans un autre registre. En fonction du résultat de la comparaison, l'adresse transmise sur le bus est alors enregistrée ou non dans la mémoire du traceur.

Ce traceur, bien qu'apportant une amélioration substantielle, ne

20 donne pas entière satisfaction par le fait même qu'il ne s'intéresse pas au contenu des instructions ni au contenu des données. Dans la plupart des cas, en effet, les instructions dont l'adresse est comprise entre deux bornes déterminées sont de nature très différente et vont donner lieu à des opérations relatives à des données elles-mêmes très différentes et enregistrées à des

25 adresses a priori indéterminées. Ce traceur est donc amené à enregistrer une fois encore des adresses d'instruction (ou des adresses de données) qu'il faudra ensuite analyser sans connaître la nature même de cette instruction ou de cette donnée. La solution choisie dans ce traceur, et qui consiste à inscrire préalablement dans un registre toute adresse transmise sur le bus

30 d'adresse mémoire du calculateur, demande trop de temps devant la rapidité du calculateur pour permettre de procéder à d'autres opérations de sélection des informations à enregistrer dans la mémoire du traceur.

La présente invention a donc pour objet un traceur de programme permettant de procéder à ces opérations complémentaires de sélection afin

35 de n'enregistrer dans la mémoire du traceur que des informations répondant à plusieurs critères à la fois, malgré les contraintes de rapidité évoquées plus haut et sans augmentation excessive de coût. A cette fin, le traceur d'invention est connecté, non seulement au bus d'adresse, mais aussi au bus de données du calculateur à surveiller. Lors de l'appel d'une instruction,

40 l'adresse apparaissant sur le bus d'adresse est fournie à un comparateur

d'adresse d'instruction et à la mémoire du traceur. De plus, l'instruction elle-même, qui apparaît sur le bus de données, est en même temps fournie à un comparateur d'instruction et à la mémoire du traceur. Les deux informations, l'adresse et l'instruction, sont inscrites dans la mémoire du traceur, dans un emplacement désigné par un compteur d'adresse d'écriture, avant même de savoir par le résultat des comparaisons, si cette inscription est utile ou non. En effet, si les résultats des comparaisons montrent que l'inscription en mémoire n'est pas requise, le compteur d'adresse d'inscription est laissé dans sa position. Par suite, à la réception de l'instruction suivante, l'inscription correspondante aura lieu à la même adresse, effaçant celle qui vient d'être faite. Par contre, si les comparaisons portant sur l'instruction et son adresse indiquent que l'inscription est justifiée, le compteur d'adresse d'écriture est incrémenté. Il désigne alors l'adresse suivante et cela suffit à préserver, dans la mémoire du traceur, les informations qui viennent d'y être inscrites.

L'adoption de ces dispositions permet d'inscrire les informations dans la mémoire du traceur sans avoir à les mémoriser préalablement dans des registres, ce qui apporte une économie de matériel, et de disposer pour ce faire de tout le temps où ces informations sont disponibles, ce qui écarte toute contrainte excessive dans le domaine de la rapidité. De plus, elle permet d'introduire dans le traceur de l'invention un deuxième processus de sélection portant sur la donnée qui sera éventuellement lue ou inscrite dans sa mémoire par le calculateur à la suite de l'instruction considérée.

A cette fin, le traceur comprend également un comparateur d'adresse de donnée et un comparateur de format de donnée, mis en service lorsque le bus mémoire du calculateur transmet une adresse de donnée et la donnée elle-même. Ainsi, dans le cas où le processus de sélection porte sur la donnée (adresse et/ou contenu de cette donnée) l'instruction correspondante et son adresse sont inscrites sans la mémoire du traceur, dans l'emplacement désigné. L'adresse de la donnée et la donnée elle-même transmises ensuite sur le bus du calculateur sont fournies respectivement au comparateur d'adresse de donnée et au comparateur de format de donnée. Si les résultats des comparaisons montrent que l'inscription en mémoire n'est pas requise, le compteur d'adresse d'inscription est laissé dans sa position et l'adresse de la donnée ainsi que son contenu ne sont pas enregistrés. Par la suite, à la réception de l'instruction suivante, l'inscription de cette instruction et de son adresse aura lieu à la même adresse, effaçant l'inscription précédente. Si les résultats des comparaisons montrent que l'inscription en mémoire est justifiée, le compteur d'adresse d'écriture est incrémenté. Il désigne alors l'adresse suivante. L'adresse de la donnée et la donnée elle-même sont alors

inscrites dans l'emplacement de la mémoire du traceur ainsi désigné par le compteur. Ce compteur est incrémenté après cette inscription. Cela suffit à préserver, dans la mémoire du traceur, les informations qui viennent d'y être inscrites.

5 Ainsi, le procédé utilisé permet d'inscrire les instructions et leurs adresses, les données correspondantes et leurs adresses sans la mémoire du traceur sans avoir à les mémoriser temporairement dans des registres. Ce procédé apporte donc une économie de matériel substantielle. De plus, il n'impose qu'une contrainte raisonnable dans le domaine de la rapidité. En

10 effet, il suffit que les circuits utilisés soient suffisamment performants pour que l'on puisse effectuer lesdites comparaisons sur l'adresse de la donnée et/ou cette donnée elle-même et incrémenter le compteur d'adresse d'inscription dans la mémoire du traceur pendant une première partie du temps de présence de ces informations sur le bus du calculateur et que la mémoire du

15 traceur soit suffisamment rapide pour que ces informations puissent y être inscrites au cours de la deuxième partie du temps de présence de ces informations sur le bus. L'expérience montre qu'il suffit que la mémoire du traceur soit aussi rapide que la mémoire la plus rapide du calculateur. Dans un mode de réalisation préféré la mémoire du traceur sera identique à celle du calculateur.

20

Le traceur de l'invention permet donc de réaliser le traçage en tenant compte en cascade de critères d'instruction (adresse et contenu) et de critères de données (adresses et contenu). De cette double possibilité portant à la fois sur les adresses et/ou les contenus des adresses, il résulte que les informations effectivement mémorisées sont en nombre considérablement réduit, ce qui facilite l'analyse déjà simplifiée par le fait qu'on enregistre non seulement les adresses mais également les données. En outre, pour une même capacité de la mémoire du traceur, l'enregistrement peut porter sur un temps de fonctionnement du calculateur beaucoup plus étendu qu'avec le traceur

30 précédemment évoqué.

Les différents objets et caractéristiques de l'invention seront maintenant exposés de façon plus détaillée dans la description qui va suivre, donnée à titre d'exemple non limitatif en se reportant aux figures annexées qui représentent :

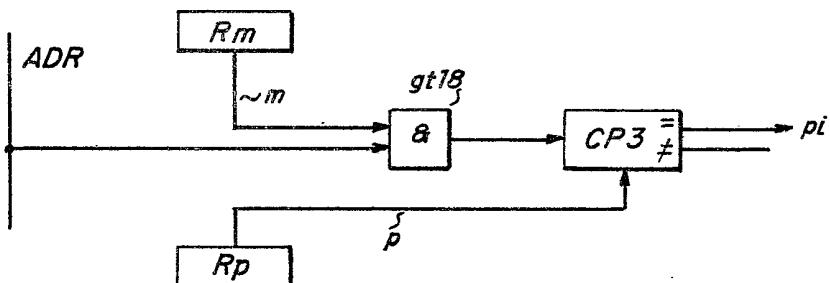

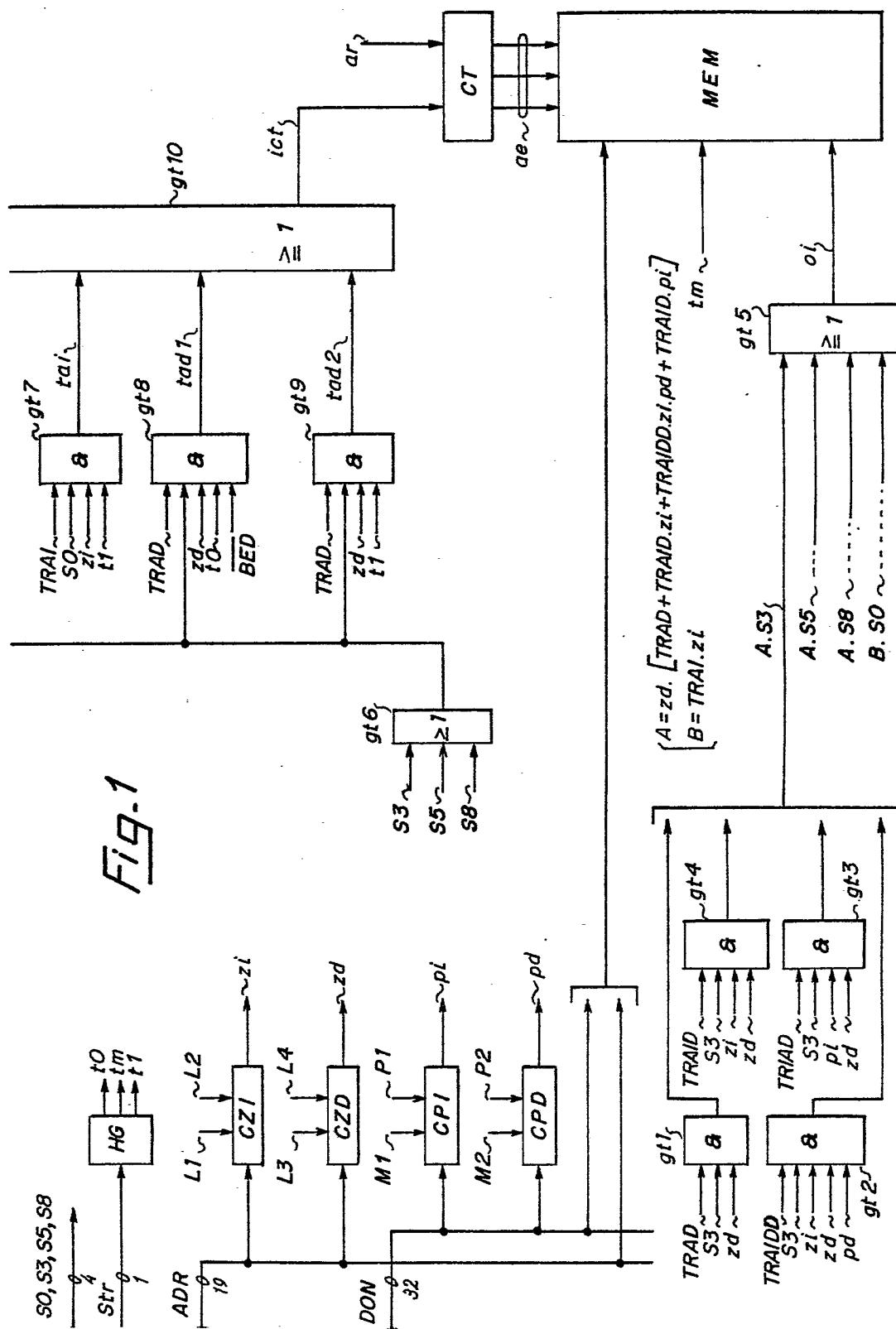

- 35 - Les figures 1 et 2, le schéma de principe d'un exemple de réalisation du traceur de programme de l'invention ;

- La figure 3, le graphique d'assemblage des figures 1 et 2 ;

- La figure 4, un tableau résumant les différentes opérations logiques réalisées par le traceur de la figure 1 dans différents modes de traçage ;

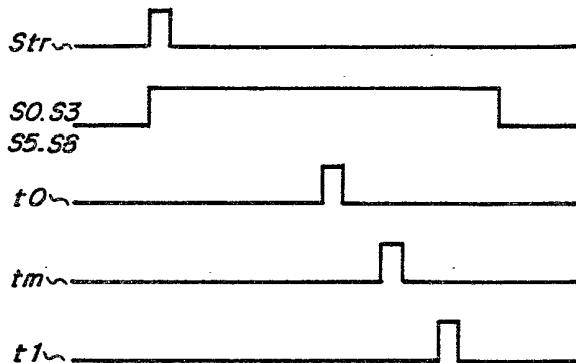

40 - La figure 5, des chronogrammes illustrant les différents signaux

fournis par l'horloge HG du traceur de la figure 1 ;

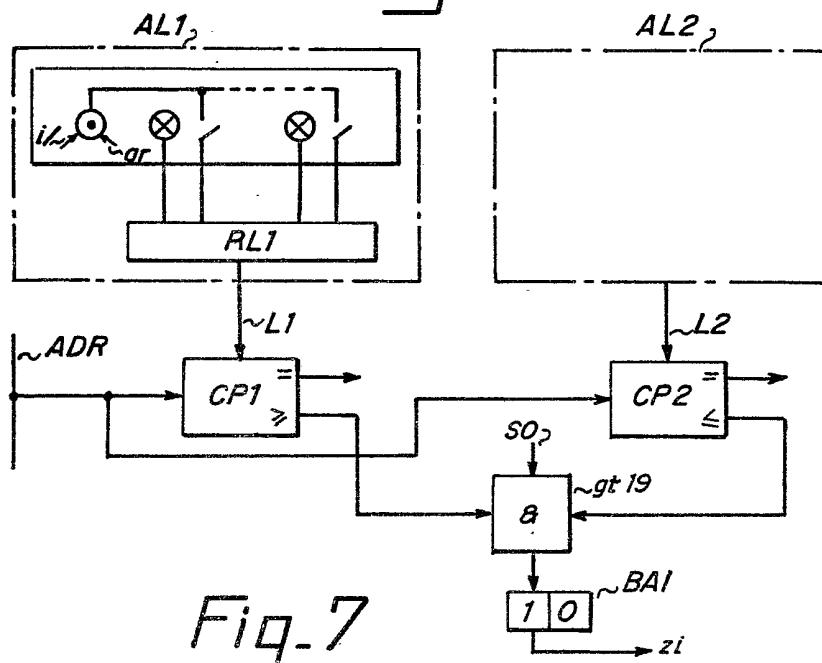

- La figure 6, un exemple de réalisation des comparateurs d'adresses CZI et CZD du traceur de la figure 1 ;

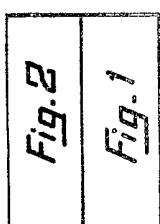

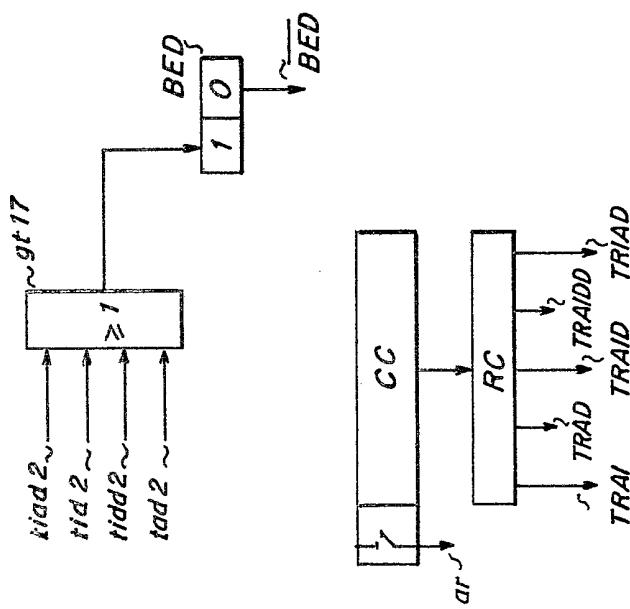

5 - La figure 7, un exemple de réalisation des comparateurs de formats CPI et CPD du traceur de la figure 1.

On décrira tout d'abord, en se reportant aux figures 1 et 2, le schéma de principe d'un exemple de réalisation du traceur de programmes de l'invention.

Le traceur de programme des figures 1 et 2, connecté en parallèle

10 sur la ligne omnibus de transfert ou bus d'adresses ADR et sur le bus de données DON d'un calculateur de commande non représenté d'un système à programme enregistré comprend notamment une console de commande et de visualisation CC, un registre de commande associé RC, une horloge HG, un comparateur d'adresses d'instructions CZI, un comparateur d'adresses de données CZD, un

15 comparateur de formats d'instructions CPI et un comparateur de formats de données CPD. Il comprend également une mémoire rapide MEM et son compteur d'adresse CT, et un ensemble de circuits logiques de commande. Cet ensemble comprend essentiellement treize portes gt1 à gt4, gt7 à gt9 et gt11 à gt16 réalisant la fonction logique ET, quatre portes gt5, gt6, gt10 et gt17

20 réalisant la fonction logique OU et un bistable BED.

On suppose, à titre d'exemple, que les adresses d'instructions et de données sont transmises sur le bus d'adresses ADR sous la forme de mots de 19 éléments binaires et que les instructions et les données sont transmises sur le bus de données DON sous la forme de mots de 32 éléments binaires.

5 La console de commande CC, de type connu, fournit notamment un signal d'arrêt ar ainsi que les différentes informations identifiant les conditions d'enregistrement choisies ou modes de traçage. Ces informations sont stockées dans le registre de commande RC qui fournit en réponse des signaux de mode de traçage TRAI, TRAD, TRAID, TRAIDD et TRIAD.

30 Le signal TRAI identifie le traçage sur reconnaissance des adresses des instructions, le signal TRAD le traçage sur reconnaissance des adresses de données. Le signal TRAID indique que le traçage a lieu lorsque les deux conditions précédentes sont réalisées, c'est-à-dire si les instructions lues à des adresses déterminées donnent lieu à l'écriture ou à la lecture de données à des adresses répondant à des critères donnés.

35 Le signal TRAIDD identifie le traçage sur reconnaissance des adresses des instructions et des adresses des données concernées par ces instructions (comme dans le cas TRAID précédent), le contenu des données répondant par ailleurs à des critères donnés. Le signal TRAID identifie le 40 traçage conditionné par le contenu des instructions et par l'adresse des

données lues ou inscrites consécutivement à ces instructions.

L'horloge HG, de type connu, est commandée par un signal de début de séquence str fourni par le calculateur non représenté avant la retransmission de chaque adresse. Le calculateur fournit également différents signaux de séquence, parmi lesquels un signal S0 lors de la transmission d'une adresse d'instruction, de la lecture de l'instruction ainsi désignée et de sa transmission sur le bus de données DON, un signal S3 lors de la transmission d'une adresse d'indirection et des signaux S5 et S8 lors de la transmission respectivement de l'adresse et du contenu d'une donnée lue et de l'adresse et du contenu d'une donnée écrite.

L'horloge HG, qui reçoit le signal de début de séquence str, fournit en réponse des signaux successifs t<sub>0</sub>, t<sub>m</sub> et t<sub>1</sub> illustrés par les chronogrammes de la figure 5 : le signal t<sub>m</sub> définit l'intervalle de temps pendant lequel on peut écrire dans la mémoire du traceur. Ce signal est précédé et suivi respectivement des signaux t<sub>0</sub> et t<sub>1</sub> qui seront utilisés notamment pour modifier les adresses d'écriture en mémoire du traceur.

Le comparateur d'adresses d'instructions CZI est un double comparateur qui reçoit, d'une part, les adresses transmises sur le bus ADR, d'autre part, deux adresses limites L1 et L2 issues de la console de commande CC. Ce comparateur d'adresses d'instructions fournit un signal d'identité d'adresse d'instruction zi de niveau de logique 1 lorsque l'adresse d'instruction transmise sur le bus ADR est comprise entre les deux adresses limites L1 et L2 déterminées par l'opérateur. Il fournit un signal zi de niveau logique 0 dans les autres cas.

Le comparateur d'adresses de données CZD est un double comparateur qui reçoit, d'une part, les adresses transmises sur le bus ADR, d'autre part, deux adresses limites L3 et L4 issues de la console de commande CC. Ce comparateur d'adresses de données fournit un signal d'identité d'adresse de données zd de niveau logique 1 lorsque l'adresse de donnée transmise sur le bus ADR est comprise entre les deux adresses limites L3 et L4. Il fournit un signal zd de niveau logique 0 dans les autres cas.

Le comparateur de formats d'instructions CPI reçoit, d'une part, les instructions transmises sur le bus DON, d'autre part, un masque d'instruction M1 et une combinaison codée ou format d'instruction P1 issus de la console de commande CC. Il fournit un signal d'identité de format d'instruction pi de niveau logique 1 lorsque le contenu de l'instruction transmise sur le bus de données DON ou la partie de ce contenu identifiée par le masque M1 est identique au format P1. Il fournit un signal pi de niveau logique 0 dans les autres cas.

Le comparateur de formats de données CPD reçoit, d'une part, les

données transmises sur le bus DON, d'autre part, un masque de donnée M2 et une combinaison codée ou format de donnée P2 issus de la console de commande CC. Il fournit un signal d'identité de format de donnée pd de niveau logique 1 lorsque le contenu de la donnée transmise sur le bus DON ou la partie de 5 cette donnée identifiée par le masque M2 est identique au format P2. Il fournit un signal pd de niveau logique 0 dans les autres cas.

La mémoire du traceur MEM est une mémoire au moins aussi rapide que la mémoire la plus rapide du calculateur et dont chaque adresse peut contenir au moins une adresse d'instruction ou de donnée (19 éléments binaires) transmise sur le bus ADR et l'instruction ou la donnée correspondante (32 éléments binaires) transmise sur le bus DON. Cette mémoire reçoit en permanence les informations circulant sur le bus d'adresses ADR et sur le bus de données DON. Ces informations sont inscrites dans la mémoire MEM, pendant la durée du signal d'écriture tm issu de l'horloge HG, à des adresses d'écriture ae fournies 15 par le compteur d'adresses CT, et sous la commande d'un signal de validation oi.

Le compteur d'adresses CT, de type connu, est remis à zéro par le signal d'arrêt ar issu de la console de commande CC.

La porte gt1, réalisant la fonction logique ET reçoit les signaux 20 TRAD, S3 et zd, la porte ET gt2 les signaux TRAIDD, S3, zi, zd et pd, la porte ET gt3 les signaux TRIAD, S3, pi et zd, et la porte ET gt4 les signaux TRAID, S3, zi et zd. Les signaux logiques respectifs de sortie de ces portes, non référencés, sont fournis à une entrée de la porte gt5 réalisant la fonction logique OU. On appelle A.S3 l'ensemble de ces quatre signaux logiques, 25 l'expression A étant égale à l'expression logique (TRAD + TRAID.zi + TRAIDD.zi.pd + TRIAD.pi).

La porte OU gt5 reçoit également des ensembles de signaux logiques A.S5, A.S8 et R.SO qui seront définis ultérieurement. Elle fournit en réponse le signal de validation oi.

30 La porte gt6, réalisant la fonction logique OU, reçoit les signaux S3, S5 et S8 fournis par le calculateur non représenté.

La porte gt7, réalisant la fonction logique ET, reçoit les signaux TRAI, SO, zi et t1. Elle fournit en réponse un signal de traçage d'adresse d'instruction toi.

35 La porte gt8, réalisant la fonction logique ET, reçoit les signaux TRAD, zd, t0, le signal de sortie de la porte OU gt6, et le signal de sortie complémentaire BED du bistable BED. Elle fournit en réponse un signal de traçage d'adresse de données tad1.

40 La porte gt9, réalisant la fonction logique ET, reçoit les signaux TRAD, zd, t1 et le signal de sortie de la porte gt6. Elle fournit en réponse

un signal de traçage d'adresse de donnée tad2.

La porte ET gt11 reçoit les signaux TRIAD, pi, zd, t1 et le signal de sortie de la porte gt6 pour fournir un signal de traçage d'instruction et d'adresse de donnée tiad2.

5 La porte ET gt12 reçoit les signaux TRIAD, pi, zd, t0, BED et le signal de sortie de la porte gt6 pour fournir un signal de traçage d'instruction et d'adresse de donnée tiad1.

La porte ET gt13 reçoit les signaux TRAID, pi, zd, t1 et le signal de sortie de la porte gt6 pour fournir un signal de traçage d'adresse d'instruction et d'adresse de donnée tid2.

10 La porte ET gt14 reçoit les signaux TRAID, pi, zd, t0, BED et le signal de sortie de la porte gt6 pour fournir un signal de traçage d'adresse d'instruction et d'adresse de donnée tid1.

15 La porte ET gt15 reçoit les signaux TRAIDD, zi, zd, pd, t1 et le signal de sortie de la porte gt6 pour fournir un signal de traçage d'adresse d'instruction et d'adresse et de contenu de donnée tidd2.

La porte ET gt16 reçoit les signaux TRAIDD, zi, zd, pd, t0, BED et le signal de sortie de la porte gt6 pour fournir un signal de traçage d'adresse d'instruction et d'adresse et de contenu de donnée tidd1.

20 La porte OU gt10 reçoit les signaux tai, tad1, tad2, tiad1, tiad2, tid1, tid2, tidd1 et tidd2 pour fournir un signal ict d'incrémentation du compteur d'adresses CT.

La porte OU gt17 reçoit les signaux tad2, tiad2, tid2 et tidd2 pour fournir un signal ral de mise en position 1 du bistable BED.

25 On décrira maintenant, en se reportant également aux figures 4 et 5, quelques cas de fonctionnement du traceur de la figure 1.

La figure 4 représente un tableau résumant les différentes opérations logiques réalisées par le traceur de la figure 1 dans les différents modes de traçage TRAI, TRAD, TRAID, TRAIDD et TRIAD précédemment définis et 30 choisis à titre d'exemple.

On décrira, tout d'abord, le fonctionnement du traceur dans le mode de traçage TRAI dans lequel l'enregistrement des informations circulant sur les bus ADR et DON est effectué lorsque l'adresse de l'instruction transmise répond à certains critères. A titre d'exemple, cette adresse doit être 35 comprise entre les deux limites L1 et L2 précédemment définies.

Les registres du traceur ainsi que le bistable BED sont remis à zéro (RZ). A l'aide de la console de commande CC, l'opérateur transmet aux circuits du traceur le signal d'arrêt ar. Ce signal remet le compteur d'adresses d'écriture CT à zéro et autorise l'envoi d'informations aux autres circuits.

40 Le registre de commande RC reçoit l'information identifiant le mode de traçage

désiré. Il fournit en réponse le signal TRAI.

Par l'intermédiaire de la console de commande CC l'opérateur fournit au comparateur d'adresses d'instructions CZI les deux adresses limites L1 et L2.

5 Le calculateur du système, dont le programme enregistré est à tester, transmet un signal de début de séquence str qui déclenche l'horloge HG. Simultanément, le signal S0 de transmission d'adresse d'instruction est fourni et une adresse d'instruction est transmise sur le bus d'adresses ADR alors que l'horloge HG fournit un signal t0 qui n'est pas utilisé.

10 L'adresse d'instruction est fournie au comparateur CZI et inscrite dans la mémoire MEM du traceur (opération illustrée dans la colonne TRAI du tableau de la figure 4 par l'expression symbolique  $ADR \rightarrow MEM$ ), dans la première adresse ( $CT = 0$ ), alors que l'horloge fournit le signal d'écriture tm. L'instruction concernée est lue dans la mémoire du calculateur à l'adresse 15 précédemment définie et retransmise sur le bus de données DON. Elle est inscrite dans la première adresse ( $CT = 0$ ) de la mémoire du traceur.

20 On suppose que cette première adresse d'instruction n'est pas comprise entre les deux limites L1 et L2. Le comparateur CZI fournit donc un signal d'identité zi de niveau logique 0. La porte OU gt5, qui reçoit des signaux A.S3, A.S5 et A.S8 au niveau logique 0 puisqu'aucun des signaux S3, 25 S5 et S8 n'est présent et qui reçoit un signal B.S0 = TRAI. zi. S0 de niveau logique 0 puisque zi est au niveau logique 0, ne fournit pas de signal de validation oi.

L'horloge HG fournit le signal t1 et ne fournit plus le signal 25 d'écriture tm.

La porte ET gt7 qui reçoit le signal zi de niveau logique 0, retransmet un signal de traçage tai de niveau logique 0.

30 La porte gt10 qui reçoit le signal de traçage tai de niveau logique 0 et les signaux de traçage tad1 et 2, tid1 et 2 et tidd1 et 2 correspondant aux autres modes de traçage donc étant au niveau logique 0, ne fournit pas de signal d'incrémentation ict au compteur d'adresses CT (zi  $\rightarrow$  ict). Le compteur CT reste à zéro.

Le signal S0 n'est plus fourni. L'horloge HG ne fournit plus le signal t1.

35 Par la suite, le calculateur retransmet une adresse d'indirection ou de lecture (écriture) de donnée accompagnée du signal S3 ou S5 (S8). Le traceur ayant reçu l'ordre TRAI de traçage d'adresses d'instructions ne s'intéresse pas à ces informations.

40 Le calculateur fournit ensuite une seconde adresse d'instruction selon le processus précédemment décrit. Cette adresse est fournie notamment

à l'entrée du comparateur CZI et est inscrite dans la mémoire MEM à l'adresse définie par le compteur CT. Ce dernier ayant été maintenu dans sa position précédente, cette seconde adresse vient s'inscrire dans l'emplacement de mémoire déjà occupé par la première adresse d'instruction qui disparaît donc 5 de la mémoire. Par la suite, il en est de même de la première instruction qui est effacée par la seconde instruction qui est inscrite dans le même emplacement.

On suppose maintenant que la seconde adresse d'instruction est comprise entre les limites L1 et L2. Le comparateur CZI fournit un signal 10 d'identité zi de niveau logique 1. La porte OU gt5 qui reçoit le signal B.SO = TRAI. zi. SO de niveau logique 1 fournit le signal de validation oi.

L'horloge HG fournit le signal t1 et ne fournit plus le signal d'écriture tm.

La porte ET gt7, dont tous les signaux d'entrée TRAI, SO, zi et t1 15 sont au niveau logique 1, fournit un signal tai de traçage d'adresse d'instruction de niveau logique 1. Ce signal est retransmis par la porte OU gt10 sous la forme d'un signal ict d'incrémentation du compteur d'adresses CT (cette opération est illustrée dans la colonne TRAI du tableau de la figure 4 par l'expression zi → + 1 → CT).

20 Le compteur d'adresses CT fournit donc une nouvelle adresse ae d'écriture dans la mémoire MEM égale à l'ancienne adresse ae augmentée d'une unité.

Le fonctionnement du traceur des figures 1 et 2 se poursuit de la façon précédemment décrite et notamment par l'écriture dans la mémoire MEM de 25 la troisième adresse d'instruction circulant sur le bus ADR dans l'emplacement de mémoire identifié par la nouvelle adresse ae. La seconde adresse d'instruction ainsi que la seconde instruction sont donc sauvegardées.

Le traceur des figures 1 et 2 procède donc à l'enregistrement systématique de l'adresse d'instruction transmise sur le bus ADR, et du contenu 30 de l'instruction transmise sur le bus DON. Si, par la suite, le ou les critères en cascade imposés par le mode de traçage désiré sont satisfaits, le compteur d'adresses CT est incrémenté et l'adresse d'instruction ainsi que son contenu sont conservés en mémoire. Dans le cas contraire, le compteur CT n'est pas incrémenté et la ou les adresses d'instructions transmises successivement sur 35 le bus ADR ainsi que leurs contenus transmis successivement sur le bus DON viennent successivement prendre la place des informations précédemment enregistrées.

Cet enregistrement est effectué quel que soit le mode de traçage choisi.

40 On décrira maintenant le fonctionnement du traceur dans le mode

de traçage TRAIDD dans lequel l'enregistrement des informations circulant sur les bus ADR et DON est effectué lorsque, pour un cycle d'opérations donné, l'adresse de l'instruction est comprise entre les deux limites L1 et L2, que l'instruction correspondante concerne la lecture d'une donnée dont l'adresse 5 est comprise entre deux limites L3 et L4, une partie de cette donnée, par exemple la tranche composée des éléments binaires de rangs 6, 7, 8 et 9, ayant une configuration ou format P2 choisie.

On ne décrira pas de nouveau le fonctionnement du traceur pendant la première phase, au cours de laquelle le calculateur fournit le signal S0. En 10 effet, on a vu que le fonctionnement était identique au fonctionnement précédemment décrit.

Dans le mode de traçage TRAIDD, l'enregistrement a lieu à la fois si les instructions, ou leurs adresses, et les données, ou leurs adresses, répondent à certains critères. On décide donc de mémoriser les résultats de 15 chaque comparateur utilisé dans un bistable. Un exemple de réalisation des circuits utilisés sera décrit ultérieurement.

On suppose donc que le compteur d'adresses CT est à zéro ainsi que les bilstables du traceur (le bistable BED en particulier) et qu'une première adresse d'instruction ainsi que l'instruction correspondante sont enregistrées 20 dans le premier emplacement de la mémoire MEM.

On suppose également que cette première adresse d'instruction est comprise entre les deux limites L1 et L2. Le comparateur CZI fournit un signal d'identité zi de niveau logique 1. Ce signal est mémorisé dans un bistable BAI (opération logique illustrée par l'expression  $zi \rightarrow 1 \rightarrow BAI$  dans la colonne 25 TRAIDD du tableau de la figure 4).

Le calculateur fournit ensuite, sur le bus d'adresse ADR, une première adresse de donnée, une adresse d'indirection par exemple. Le signal S3 est donc également fourni.

Cette adresse est fournie, d'une part, au comparateur CZD d'adresse 30 de données, d'autre part, à l'entrée de la mémoire MEM.

La donnée correspondante est lue et transmise sur le bus de données DON. Elle est fournie, d'une part, au comparateur de formats de données CPD, d'autre part, à l'entrée de la mémoire MEM.

On suppose tout d'abord que l'adresse d'indirection n'est pas 35 comprise entre les deux limites L3 et L4 et/ou que les éléments binaires de rangs respectifs 6, 7, 8 et 9 ne sont pas respectivement identiques au format P2. Le comparateur CZD et/ou le comparateur CPD fournissent alors respectivement un signal zd d'identité d'adresse de donnée et/ou un signal pd d'identité de format au niveau logique 0. Le signal logique zd.pd est donc au 40 niveau 0. L'un au moins des critères choisis n'est pas rempli et l'enregis-

trement n'a pas lieu : le compteur d'adresses CT n'est pas incrémenté (zi.zd.pd → ict). La porte ET gt2 dont l'entrée zd et/ou l'entrée pd est au niveau logique 0 fournit un signal de niveau logique 0. Les portes ET gt1, gt3 et gt4 étant commandées respectivement par les signaux TRAD, TRIAD et TRAID 5 fournissent également un signal de niveau logique 0 et la porte gt5 ne fournit pas de signal de validation oi.

L'horloge HG fournit plus le signal tm mais le signal t1, ce qui est sans effet sur le fonctionnement du traceur de la figure 1.

Le calculateur transmet ensuite, au cours d'une seconde séquence 10 précédée du signal str, une seconde adresse de donnée que l'on suppose être une seconde adresse d'indirection.

Le signal S3 est donc de nouveau fourni.

La seconde adresse est fournie, d'une part, au comparateur CZD, d'autre part, à l'entrée de la mémoire MEM.

15 La donnée correspondante est lue et transmise sur le bus de données DON . Elle est fournie d'une part, au comparateur de formats de données CPD, d'autre part, à l'entrée de la mémoire MEM.

On suppose maintenant que cette seconde adresse est comprise entre les deux limites L3 et L4 et que la tranche de données comprenant les éléments 20 binaires de rangs 6, 7, 8 et 9 est identique au format P2. Il en résulte que les comparateurs CZD et CPD fournissent respectivement des signaux zd et pd de niveau logique 1.

Les trois critères de traçage concernant respectivement l'adresse de l'instruction, l'adresse de la donnée ainsi que le contenu de cette dernière 25 sont réunis et le traceur va procéder à l'enregistrement des différentes informations circulant sur les bus ADR et DON.

L'horloge HG fournit le signal t0. La porte ET gt16 dont toutes les entrées sont au niveau logique 1 fournit un signal de traçage tidd1 de niveau 30 logique 1. Ce signal est retransmis par la porte gt10 sous la forme d'un signal ict d'incrémentation du compteur CT qui passe en position 1 (+ 1 → CT (t0) de la colonne TRAIDD du tableau de la figure 4).

La porte gt2, dont toutes les entrées sont au niveau logique 1, fournit un signal AS3 de niveau logique 1 à l'entrée de la porte gt5. Un signal de validation oi est fourni à la mémoire MEM.

35 L'horloge HG fournit le signal tm. L'adresse de la donnée ainsi que cette donnée circulant respectivement sur les bus ADR et DON sont inscrites dans la mémoire MEM à l'adresse indiquée par le compteur CT, c'est-à-dire à l'adresse suivant immédiatement celle où ont été précédemment enregistrés l'adresse de l'instruction et son contenu (ADR → MEM dans la colonne TRAIDD, 40 paragraphe 1) BED du tableau de la figure 4).

L'horloge HG fournit le signal t1. La porte gt15, dont toutes les entrées sont au niveau logique 1 fournit un signal de traçage tidd2 de niveau logique 1 à la porte gt10 qui le retransmet sous la forme d'un signal ict d'incrémentation du compteur CT qui passe donc en position 2 (+ 1 → CT (t1) dans la ligne suivante de la colonne TRAIDD de la figure 4).

La porte gt17 qui reçoit un signal tidd2 de niveau logique 1 fournit un signal ral de niveau logique 1 sur l'entrée de forçage à l'état 1 du bistable BED (1 → BED). Ce bistable fournit donc un signal complémentaire BED de niveau logique 0.

Le signal t1 n'est plus fourni et le fonctionnement du traceur se poursuit selon le même processus que l'adresse alors transmise sur le bus ADR, soit une adresse d'indirection (signal S3 fourni) ou une adresse de lecture de donnée (signal S5 fourni) ou d'écriture de donnée (signal S8 fourni). Ce processus est identique à celui qui vient d'être décrit à une exception près : dans la description qui précède, on a inscrit dans la mémoire MEM l'adresse et le contenu de l'instruction et, le compteur CT d'adresses d'écriture dans cette mémoire n'a pas été incrémenté. On incrémente donc ce compteur avant d'enregistrer l'adresse et le contenu de la donnée (+ 1 → CT (t0)). On incrémente alors le compteur CT (+ 1 → CT (t1)), l'exécution de cette incrémén-tation étant mémorisée dans le bistable BED (+ 1 → BED). Il n'est alors plus nécessaire d'incrémenter le compteur CT avant l'enregistrement de l'adresse et du contenu de la donnée qui vont maintenant être transmis respectivement sur les bus ADR et DON. On voit sur la figure 2 que la porte gt16 qui fournit un signal de traçage tidd1 de niveau logique 1 pendant l'existence du signal t0 est maintenant bloquée par le signal BED au niveau logique 0.

Le fonctionnement du traceur se poursuit donc selon le processus illustré par le paragraphe 2) BED de la colonne TRAIDD du tableau de la figure 4.

Dans ce mode particulier de traçage, deux types de fonctionnement sont à envisager : l'enregistrement est effectué soit uniquement lorsque l'adresse d'indirection répond au critère imposé (comprise entre L3 et L4), soit à partir du moment où une adresse d'indirection répond à ce critère. Dans ce dernier cas, on mémorise dans un bistable le premier passage du signal d'identité d'adresse zd au niveau logique 1. C'est ce signal mémorisé qui est alors utilisé par la suite pour commander l'enregistrement des informations circulant sur les bus ADR et DON même à l'adresse d'indirection ou de donnée suivante ne répond pas au critère imposé.

On ne décrira pas les autres modes de traçage TRAD, TRAID et TRIAD, le tableau de la figure 4 ainsi que les figures 1 et 2 étant suffisamment explicites pour permettre à l'homme de l'art d'en déduire le fonctionnement

du traceur de l'invention d'après la description qui précède.

On décrira maintenant, en se reportant au schéma de la figure 6, un exemple de réalisation des comparaisons d'adresses CZI et CZD de la figure 1.

5 On a représenté sur la figure 6, le comparateur double CZI comprenant deux comparateurs CP1 et CP2 de type connu et dont une entrée est connectée en parallèle au bus d'adresses ADR. On a également représenté des parties AL1 et AL2 de la console de commande CC (figure 2) prévues pour fournir les adresses limites L1 et L2.

10 La partie AL1 comprend notamment une porte non référencée réalisant la fonction logique ET. Cette porte, commandée par le signal d'arrêt ar, reçoit un signal il de niveau logique 1. Le signal de sortie de cette porte est fourni sur des contacts "travail" d'inverseurs de commande non référencés. Les sorties respectives de ces inverseurs sont connectées respectivement à des 15 entrées d'un registre d'affichage de limites RL1.

En présence du signal d'arrêt ar, fourni par la manœuvre d'un inverseur de la console de commande CC (figure 2), le signal il est fourni à chaque inverseur. L'opérateur fournit alors au registre RL1 une combinaison codée identifiant la limite L1, à l'aide de boutons de commande de la console CC. 20 Des voyants sont prévus pour contrôler l'état du registre selon un procédé connu.

Le contenu du registre est alors fourni à une entrée du comparateur CP1.

De la même façon, on fournit une combinaison codée identifiant la 25 limite L2 au comparateur CP2 à l'aide de la partie AL2 de la console CC.

Lorsque les deux combinaisons codées fournies sur ses entrées sont identiques, chacun des comparateurs fournit un signal de niveau logique 1 sur sa sortie d'identité (=).

30 Lorsque la combinaison codée issue du bus ADR est supérieure ou égale à la combinaison codée L1 issue du registre RL1, le comparateur CP1 fournit un signal de niveau logique 1 sur sa sortie complémentaire ( $\geq$ ).

Lorsque la combinaison codée issue du bus ADR est inférieure ou 35 égale à la combinaison codée L2 issue de la partie AL2, le comparateur CP2 fournit un signal de niveau logique 1 sur sa sortie complémentaire ( $\leq$ ).

Les signaux de sortie complémentaires respectifs des deux comparateurs CP1 et CP2 sont fournis respectivement à deux entrées d'une porte ET gt19 commandée par le signal S0. La sortie de cette porte est connectée à l'entrée de forçage à l'état 1 du bistable de mémorisation BAI qui fournit sur sa sortie directe le signal zi d'identité d'adresse d'instruction.

40 On suppose que la limite L1 est inférieure à la limite L2. Lorsque

l'adresse transmise sur le bus ADR est comprise entre ces deux limites, chaque comparateur fournit un signal complémentaire de niveau logique 1. Ce signal est retransmis, pendant l'existence du signal SO (transmission d'une adresse d'instruction) à l'entrée de forçage à l'état 1 du bistable BAI. Le signal zi d'identité d'adresse d'instruction passe et se maintient au niveau logique 1.

5 Le bistable BAI sera ramené à l'état 0 par un signal fourni sur son entrée de forçage correspondante en fin de séquence, par le signal t1.S5 ou t1.S8 par exemple.

10 Le double comparateur CZD sera identique, la porte ET gt19 étant alors commandée par le signal (S3 + S5 + S8).

Dans l'exemple choisi, le signal zi passe au niveau logique 1 si l'adresse d'instruction transmise sur le bus ADR est comprise entre les deux limites L1 et L2.

15 Quand une faute de programme est détectée, il est plus souvent judicieux de procéder à l'enregistrement des informations circulant sur les bus ADR et DON lorsque, par exemple, des données ont été lues ou écrites à la suite d'instructions obtenues à des adresses situées hors d'une zone donnée de la mémoire du calculateur. On s'intéressera donc à ces instructions et la limite supérieure L2 sera fournie au comparateur CP1, la limite inférieure L1 20 au comparateur CP2. Ainsi, le signal d'identité zi passera au niveau logique 1 et pourra donc déclencher l'enregistrement lorsque les adresses d'instruction transmises sur le bus ADR seront extérieures à la zone comprise entre les deux limites L1 et L2.

25 On décrira maintenant, en se reportant à la figure 7, un exemple de réalisation du comparateur de formats CP1 de la figure 1.

Le comparateur de formats de la figure 7 comprend un registre de masque Rm, un registre de valeur Rp, une porte gt18 réalisant la fonction logique ET et un comparateur de type connu CP3.

30 A l'aide de la console de commande CC (figure 2), l'opérateur inscrit une combinaison codée m dans le registre de masque Rm et une combinaison codée p dans le registre de valeur Rp. La sortie du registre Rm est connectée à une autre entrée de la porte gt18 dont l'autre entrée est connectée en parallèle au bus d'adresse ADR. La sortie de la porte gt18 et la sortie du registre Rp sont respectivement connectées à des entrées du comparateur CP3.

35 La porte gt18 retransmet une combinaison codée obtenue par addition logique élément binaire par élément binaire correspondant de la combinaison codée m et de l'adresse émise sur le bus ADR. Lorsque cette combinaison codée est identique à la combinaison codée p issue du registre Rp, le comparateur fournit un signal d'identité pi de niveau logique 1. Un circuit identique est 40 utilisé pour la réalisation du comparateur CPD de formats de données.

Ce dispositif, utilisé dans le traceur de l'invention, permet donc de commander le traçage pour une valeur déterminée d'une tranche quelconque d'une instruction ou d'une donnée.

Il est bien évident que la description qui précède n'a été fournie qu'à titre d'exemple non limitatif et que de nombreuses variantes peuvent être envisagées sans sortir pour autant du cadre de l'invention. On peut ainsi prévoir d'autres conditions de traçage que celles envisagées. On peut ainsi commander le traçage dans le cas où l'adresse (d'instruction ou de donnée) est extérieure à plusieurs zones déterminées. Il suffit pour cela de prévoir plusieurs comparateurs d'identité d'adresses tels que les comparateurs CZI et CZD.

REVENDICATIONS

1 - Dispositif de recherche de faute de logiciel pour système de traitement de données à programme enregistré en exploitation et dans lequel un calculateur prélève des instructions stockées dans sa mémoire à des adresses qu'il transmet sur une ligne omnibus de transfert ou bus d'adresse, ces 5 instructions étant transmises au calculateur par l'intermédiaire d'un bus de données, et où, après analyse de ces instructions, le calculateur commande la lecture ou l'écriture en mémoire de données transmises sur le bus de données à des adresses transmises sur le bus d'adresse, ce dispositif comportant notamment des moyens pour prélever les adresses d'instructions transmises sur 10 le bus d'adresse, des moyens pour analyser ces adresses et des moyens pour commander la mémorisation de ces adresses en fonction du résultat de cette première analyse, dispositif caractérisé par le fait qu'il comprend en outre, des moyens pour prélever également toutes les informations transmises sur le bus de données, des moyens pour analyser ces données et des moyens pour 15 commander la mémorisation de ces données ainsi que de leurs adresses et pour valider ladite mémorisation des adresses d'instructions en fonction à la fois des résultats de ladite première analyse et des résultats de ladite analyse de ces données.

2 - Dispositif tel que défini en 1, caractérisé par le fait qu'il 20 comprend des moyens pour mémoriser, avant ladite analyse, les adresses et les contenus d'instructions dès leurs transmissions respectives sur les bus correspondants et des moyens pour annuler cette mémorisation si l'analyse qui suit fournit un résultat non conforme au résultat recherché.

3 - Dispositif tel que défini en 1, caractérisé par le fait que les- 25 dits moyens d'analyse des données comprennent notamment un comparateur double qui reçoit, d'une part, les données transmises sur le bus de données, d'autre part, une information identifiant une partie déterminée de cette donnée et la valeur de cette partie, pour fournir un signal d'identification lorsque la valeur de la partie déterminée de la donnée est identique à ladite valeur 30 identifiée.

## PL.I/4

PL. II/4

Fig. 3

Fig. 2

PL. III/4

Fig. 4

| <i>MD</i><br><i>SQ</i> | <i>TRAI</i>                                | <i>TRAD</i>                        | <i>TRAID</i>                               | <i>TRAIDD</i>                              | <i>TRIAD</i>                               |

|------------------------|--------------------------------------------|------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|

| <i>SO</i>              | <i>RZ, HG</i>                              | <i>RZ, HG</i>                      | <i>RZ, HG</i>                              | <i>RZ, HG</i>                              | <i>RZ, HG</i>                              |

|                        | <i>ADR → MEM</i>                           | <i>ADR → MEM</i>                   | <i>ADR → MEM</i>                           | <i>ADR → MEM</i>                           | <i>ADR → MEM</i>                           |

|                        | $\overline{zi} \rightarrow \overline{ict}$ |                                    | $\overline{zi} \rightarrow \overline{ict}$ | $\overline{zi} \rightarrow \overline{ict}$ | $\overline{pi} \rightarrow \overline{ict}$ |

| <i>S3</i>              | $zi \rightarrow +1 \rightarrow CT$         |                                    | $zi \rightarrow 1 \rightarrow BAI$         | $zi \rightarrow 1 \rightarrow BAI$         | $pi \rightarrow 1 \rightarrow BPI$         |

|                        | $zd \rightarrow \overline{ict}$            | $zi.zd \rightarrow \overline{ict}$ | $zi.zd.pd \rightarrow \overline{ict}$      | $pi.zd \rightarrow \overline{ict}$         |                                            |

|                        | $zd:$                                      | $zi.zd:$                           | $zi.zd.pd:$                                | $pi.zd:$                                   |                                            |

|                        | 1) $\overline{BED}$                        | 1) $\overline{BED}$                | 1) $\overline{BED}$                        | 1) $\overline{BED}$                        |                                            |

|                        | $+1 \rightarrow CT(t0)$                    | $+1 \rightarrow CT(t0)$            | $+1 \rightarrow CT(t0)$                    | $+1 \rightarrow CT(t0)$                    |                                            |

|                        | <i>ADR → MEM</i>                           | <i>ADR → MEM</i>                   | <i>ADR → MEM</i>                           | <i>ADR → MEM</i>                           |                                            |

|                        | $+1 \rightarrow CT(t1)$                    | $+1 \rightarrow CT(t1)$            | $+1 \rightarrow CT(t1)$                    | $+1 \rightarrow CT(t1)$                    |                                            |

|                        | $1 \rightarrow BED$                        | $1 \rightarrow BED$                | $1 \rightarrow BED$                        | $1 \rightarrow BED$                        |                                            |

|                        | 2) $BED$                                   | 2) $BED$                           | 2) $BED$                                   | 2) $BED$                                   |                                            |

|                        | <i>ADR → MEM</i>                           | <i>ADR → MEM</i>                   | <i>ADR → MEM</i>                           | <i>ADR → MEM</i>                           |                                            |

| <i>S5</i>              | $+1 \rightarrow CT(t1)$                    | $+1 \rightarrow CT(t1)$            | $+1 \rightarrow CT(t1)$                    | $+1 \rightarrow CT(t1)$                    |                                            |

|                        | $1 \rightarrow BED$                        | $1 \rightarrow BED$                | $1 \rightarrow BED$                        | $1 \rightarrow BED$                        |                                            |

| <i>S8</i>              |                                            | <i>id' S3</i>                      | <i>id' S3</i>                              | <i>id' S3</i>                              | <i>id' S3</i>                              |

PL.IV/4

Fig. 5

Fig. 6

Fig. 7