(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5979530号

(P5979530)

(45) 発行日 平成28年8月24日(2016.8.24)

(24) 登録日 平成28年8月5日(2016.8.5)

(51) Int.Cl.

F 1

|              |           |      |       |   |

|--------------|-----------|------|-------|---|

| HO1L 21/338  | (2006.01) | HO1L | 29/80 | F |

| HO1L 29/812  | (2006.01) | HO1L | 29/80 | H |

| HO1L 29/778  | (2006.01) | HO1L | 29/80 | L |

| HO1L 21/3205 | (2006.01) | HO1L | 21/88 | R |

| HO1L 21/768  | (2006.01) | HO1L | 27/04 | P |

請求項の数 5 (全 12 頁) 最終頁に続く

(21) 出願番号

特願2011-235436 (P2011-235436)

(22) 出願日

平成23年10月26日(2011.10.26)

(65) 公開番号

特開2013-93477 (P2013-93477A)

(43) 公開日

平成25年5月16日(2013.5.16)

審査請求日

平成26年10月27日(2014.10.27)

(73) 特許権者 000154325

住友電工デバイス・イノベーション株式会

社

神奈川県横浜市栄区金井町1番地

(74) 代理人 100087480

弁理士 片山 修平

(72) 発明者 梶井 清

神奈川県横浜市栄区金井町1番地 住友電

工デバイス・イノベーション株式会社内

審査官 早川 朋一

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のFETそれぞれのゲートフィンガーを共通に接続するゲートバスラインの形成において、

金属層を形成する工程と、

電解めっき法により、前記ゲートバスラインの一部を除く領域上に、めっき層を形成する工程と、

前記ゲートバスラインの一部に対応する領域を覆い、前記めっき層を覆わないレジストからなるマスク層を形成する工程と、

前記マスク層と前記めっき層を用いたエッチングにより、前記ゲートバスラインの領域以外の前記金属層を除去する工程と、を含み、

前記ゲートバスラインを、前記ゲートバスラインの一部に対応する領域において、前記金属層上に前記めっき層が配置されない構成とする半導体装置の製造方法。

## 【請求項 2】

前記ゲートバスラインの一部に対応する領域を覆うマスク層は、前記ゲートバスラインの幅よりも狭い請求項1記載の半導体装置の製造方法。

## 【請求項 3】

前記ゲートバスラインには複数のゲートパッドが接続されてなり、前記ゲートバスラインの一部に対応する領域は、前記複数のゲートパッドの間に位置してなる請求項1または2のいずれか一項記載の半導体装置の製造方法。

10

20

**【請求項 4】**

前記ゲートバスラインの一部に対応する領域は、前記複数のゲートパッドまでの電気長が実質的に等しい位置に設けられてなる請求項 3 記載の半導体装置の製造方法。

**【請求項 5】**

前記金属層の最上層は Au 層である請求項 1 から 4 のいずれか一項記載の半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置の製造方法に関する。

10

**【背景技術】****【0002】**

マイクロ波、準ミリ波、ミリ波などの高周波帯域において増幅を行うのに適した半導体装置として、電界効果トランジスタ (FET : Field Effect Transistor) が知られている。FETにおいて、従来、奇モードのループ発振を抑えるために、隣接するゲートパッドの間に、エピ抵抗やチップ抵抗を電気的に接続させることが提案されている。また、例えば特許文献 1 には、ゲート・ソース間のリーク電流による発振を抑えるために、ゲートバイアス回路に発振防止回路を設ける技術が開示されている。

**【先行技術文献】****【特許文献】**

20

**【0003】**

【特許文献 1】特開平 8 - 316744 号公報

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

奇モードのループ発振を抑えるために、隣接するゲートパッドの間にチップ抵抗を電気的に接続させる場合、構成部品が増え、且つチップ抵抗を設けるスペースを確保しなければならない。また、隣接するゲートパッドの間にエピ抵抗を電気的に接続させる場合、エピ抵抗の面積を大きくしなければ奇モードのループ発振を抑えることができない。これは、エピ抵抗のシート抵抗値は、例えば 100 / と高いのに対し、奇モードのループ発振を抑えるための抵抗は、例えば 2 ~ 3 のような 10 以下の場合が望ましいためである。

30

**【0005】**

このように、エピ抵抗を用いる場合では、エピ抵抗の面積が大きくなることから、エピ抵抗となる抵抗活性領域と FET の活性領域との間のアイソレーションが取れずに、ゲートリーク電流が発生してしまう場合がある。

**【0006】**

本発明は、上記課題に鑑みなされたものであり、エピ抵抗やチップ抵抗を用いることなく、奇モードのループ発振を抑えることが可能な半導体装置の製造方法を提供することを目的とする。

40

**【課題を解決するための手段】****【0007】**

本発明は、複数の FET それぞれのゲートフィンガーを共通に接続するゲートバスラインの形成において、金属層を形成する工程と、電解めっき法により、前記ゲートバスラインの一部を除く領域上に、めっき層を形成する工程と、前記ゲートバスラインの一部に対応する領域を覆うマスク層を形成する工程と、前記マスク層を用いたエッチングにより、前記ゲートバスラインの領域以外の前記金属層を除去する工程と、を含み、前記ゲートバスラインを、前記ゲートバスラインの一部に対応する領域において、前記金属層上に前記めっき層が配置されない構成とする半導体装置の製造方法である。 本発明によれば、エピ抵抗やチップ抵抗を用いることなく、奇モードのループ発振を抑えることができる。

50

## 【0009】

上記構成において、前記ゲートバスラインの一部に対応する領域を覆うマスク層は、前記ゲートバスラインの幅よりも狭い構成とすることができる。この構成によれば、奇モードのループ発振をより確実に抑えることができる。

## 【0011】

上記構成において、前記ゲートバスラインには複数のゲートパッドが接続されてなり、前記ゲートバスラインの一部に対応する領域は、前記複数のゲートパッドの間に位置してなる構成とすることができる。この構成によれば、特性への影響を抑えつつ、奇モードのループ発振を抑えることができる。

## 【0012】

10

上記構成において、前記ゲートバスラインの前記ゲートバスラインの一部に対応する領域は、前記複数のゲートパッドまでの電気長が実質的に等しい位置に設けられてなる構成とすることができる。この構成によれば、特性への影響をより抑えつつ、奇モードのループ発振を抑えることができる。

## 【0014】

上記構成において、前記金属層の最上層はA u層である構成とすることができる。

## 【発明の効果】

## 【0016】

本発明によれば、エピ抵抗やチップ抵抗を用いることなく、奇モードのループ発振を抑えることが可能な半導体装置を得ることができる。

20

## 【図面の簡単な説明】

## 【0017】

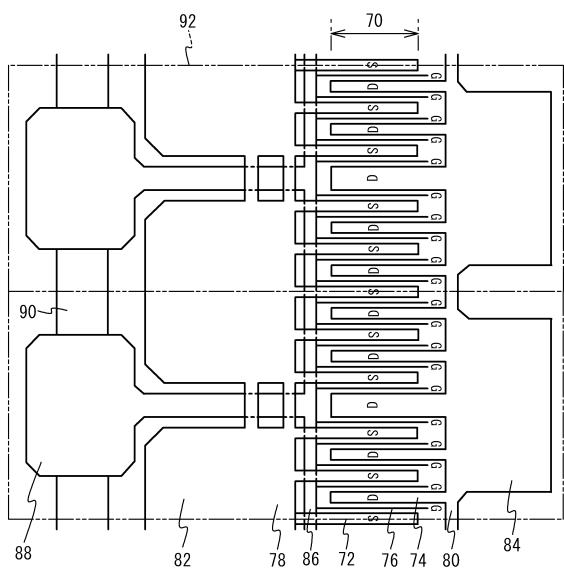

【図1】図1は比較例1に係る半導体装置の上面模式図の例である。

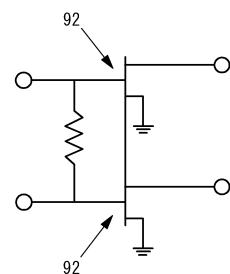

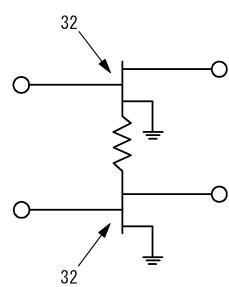

【図2】図2は比較例1に係る半導体装置の等価回路図の例である。

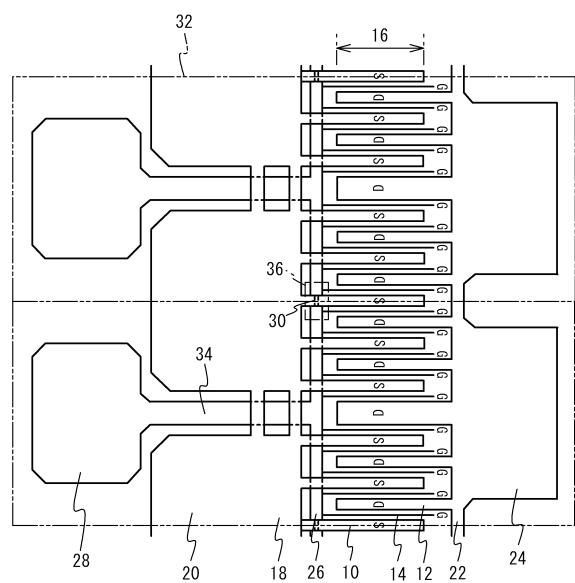

【図3】図3は実施例1に係る半導体装置の上面模式図の例である。

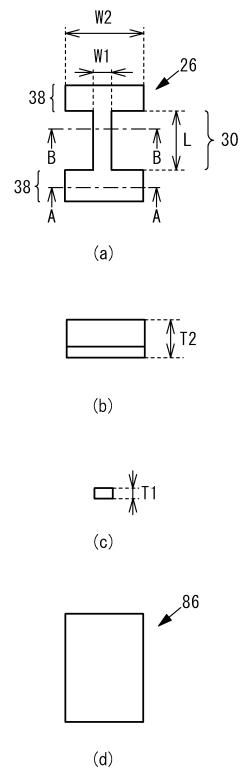

【図4】図4(a)はゲートバスラインの上面模式図の例であり、図4(b)は図4(a)のA-A間、図4(c)は図4(a)のB-B間の断面模式図の例である。図4(d)は、比較例1のゲートバスラインの上面模式図の例である。

【図5】図5は実施例1に係る半導体装置の等価回路図の例である。

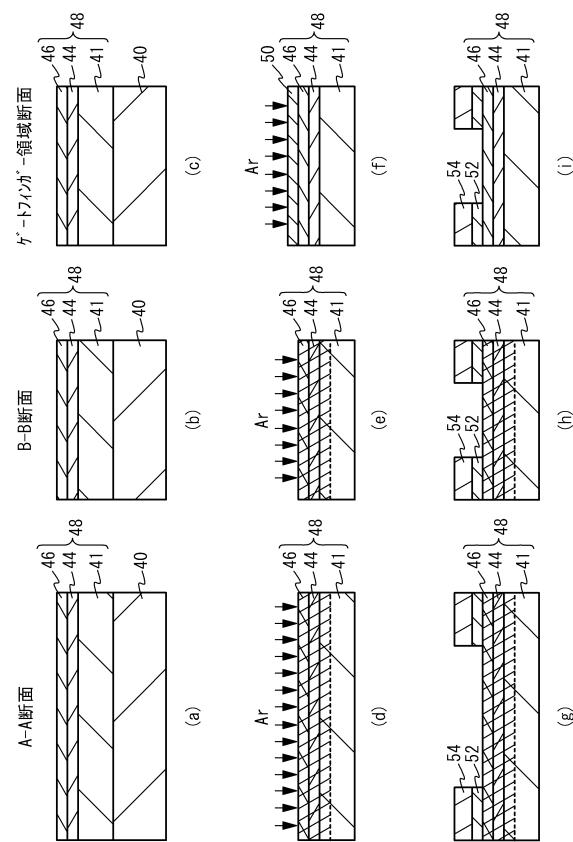

【図6】図6(a)から図6(i)は実施例1に半導体装置の製造方法を示す断面模式図(その1)の例である。

30

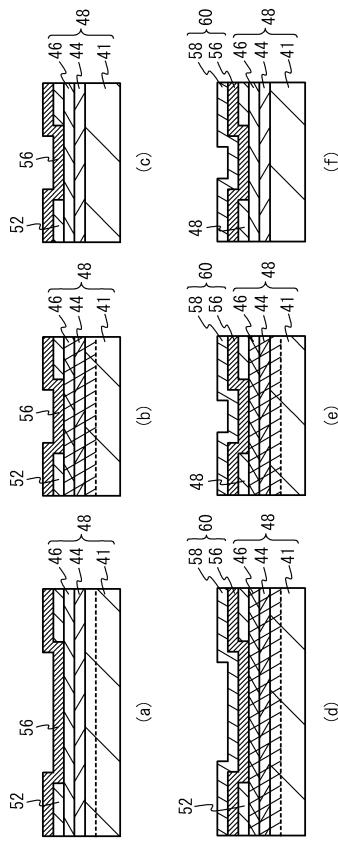

【図7】図7(a)から図7(i)は実施例1に係る半導体装置の製造方法を示す断面模式図(その2)の例である。

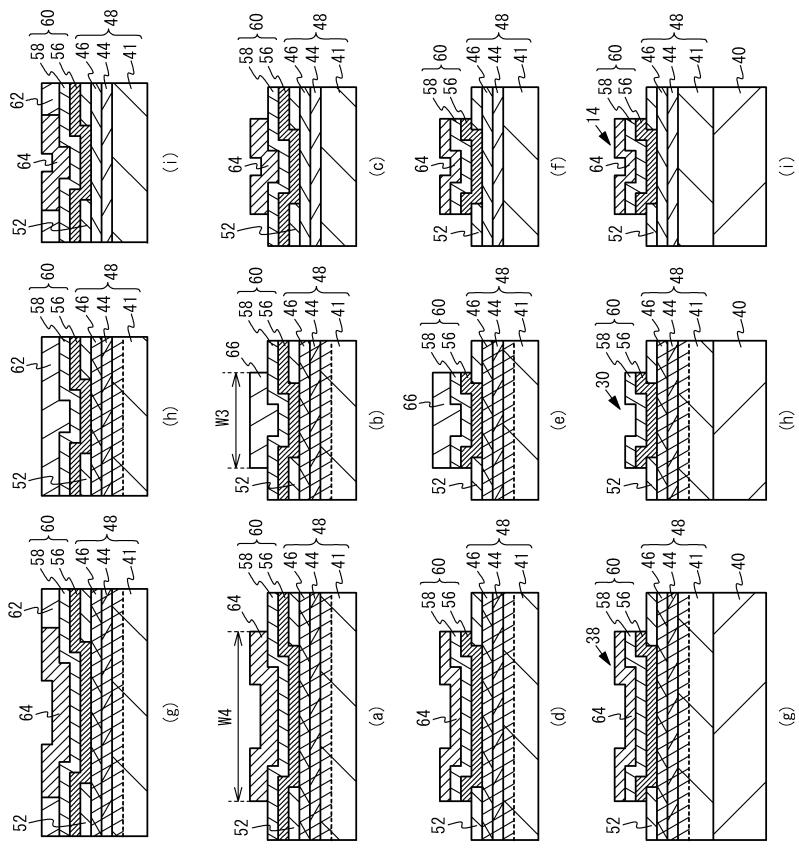

【図8】図8(a)から図8(i)は実施例1に係る半導体装置の製造方法を示す断面模式図(その3)の例である。

## 【発明を実施するための形態】

## 【0018】

まず、比較例1に係る半導体装置について説明する。比較例1に係る半導体装置は、奇モードのループ発振を抑えるために、隣接するゲートパッドの間にエピ抵抗を電気的に接続させた場合の例である。図1は、比較例1に係る半導体装置の上面模式図の例である。図1を参照して、半導体基板上に形成された半導体層の活性領域70上に、複数のソースフィンガー72、複数のドレインフィンガー74及び複数のゲートフィンガー76が設かれている。なお、活性領域とは、ソースフィンガー、ドレインフィンガー及びゲートフィンガーが交差する領域であって、半導体層が電気的に活性化した領域をいう。

40

## 【0019】

複数のソースフィンガー72は、ソースバスライン78により互いに接続している。複数のドレインフィンガー74は、ドレインバスライン80により互いに接続している。ソースバスライン78には複数のソースパッド82が接続され、ドレインバスライン80には複数のドレインパッド84が接続されている。

## 【0020】

50

複数のゲートフィンガー 7 6 は、ゲートバスライン 8 6 により互いに接続されている。ゲートバスライン 8 6 には、複数のゲートパッド 8 8 が接続されている。複数のゲートパッド 8 8 のうち隣接するゲートパッド 8 8 の間に、エピ抵抗 9 0 が電気的に接続されている。ここで、複数のゲートパッド 8 8 の周期に合わせた F E T 群を単位 F E T 9 2 とする。

#### 【 0 0 2 1 】

図 2 は、比較例 1 に係る半導体装置の等価回路図の例である。図 2 を参照して、隣接する単位 F E T 9 2 のゲート間に抵抗が付加されている。これは、図 1 で説明したように、隣接するゲートパッド 8 8 の間にエピ抵抗 9 0 を電気的に接続させたためである。これにより、比較例 1 によれば、奇モードのループ発振を抑えることが可能となる。

10

#### 【 0 0 2 2 】

しかしながら、発明が解決しようとする課題で述べたように、奇モードのループ発振を抑えるため、エピ抵抗 9 0 が 1 0 以下となるようにすると、エピ抵抗 9 0 の抵抗活性領域の面積が大きくなってしまう。このため、抵抗活性領域と F E T の活性領域 7 0 との間のアイソレーションが取れずに、ゲートリーコ電流が発生する場合がある。そこで、このような課題を解決するために、エピ抵抗を用いることなく、奇モードのループ発振を抑制することが可能な半導体装置について説明する。

#### 【 実施例 1 】

#### 【 0 0 2 3 】

図 3 は、実施例 1 に係る半導体装置の上面模式図の例である。図 3 を参照して、半導体基板上に形成された半導体層上に、複数のソースフィンガー 1 0 、複数のドレインフィンガー 1 2 及び複数のゲートフィンガー 1 4 が設けられている。複数のソースフィンガー 1 0 は、活性領域 1 6 上に互いに並列に設けられている。複数のドレインフィンガー 1 2 は、ソースフィンガー 1 0 と交互に配置されるように、活性領域 1 6 上に互いに並列に設けられている。複数のゲートフィンガー 1 4 は、ソースフィンガー 1 0 とドレインフィンガー 1 2 との間にそれぞれ配置されるように、活性領域 1 6 上に互いに並列に設けられている。これにより、ゲートフィンガー 1 4 とその両側に設けられたソースフィンガー 1 0 及びドレインフィンガー 1 2 とからなる複数の F E T が並列に接続されている。

20

#### 【 0 0 2 4 】

複数のソースフィンガー 1 0 は、活性領域 1 6 の外側でソースバスライン 1 8 により共通に束ねられて互いに接続している。ソースバスライン 1 8 には、複数のソースパッド 2 0 が等間隔で接続されている。同様に、複数のドレインフィンガー 1 2 は、活性領域 1 6 の外側でドレインバスライン 2 2 により共通に束ねられて互いに接続している。ドレインバスライン 2 2 には、複数のドレインパッド 2 4 が等間隔で接続されている。ソースバスライン 1 8 及びソースパッド 2 0 とドレインバスライン 2 2 及びドレインパッド 2 4 とは、活性領域 1 6 を挟んで反対側に設けられている。

30

#### 【 0 0 2 5 】

複数のゲートフィンガー 1 4 は、活性領域 1 6 の外側でゲートバスライン 2 6 により共通に束ねられて互いに接続している。ゲートバスライン 2 6 には、複数のゲートパッド 2 8 が等間隔で接続されている。ゲートバスライン 2 6 は、隣接するゲートパッド 2 8 の間からゲートバスライン 2 6 側に延伸させた領域内で、幅が狭くなった狭幅部分 3 0 を有する。ここで、複数のゲートパッド 2 8 の周期に合わせた F E T 群を単位 F E T 3 2 とする。

40

#### 【 0 0 2 6 】

ゲートバスライン 2 6 及びゲートパッド 2 8 は、活性領域 1 6 に対してソースバスライン 1 8 及びソースパッド 2 0 と同じ側に設けられている。このため、ソースフィンガー 1 0 とゲートバスライン 2 6 とが交差する領域は、ソースフィンガー 1 0 とゲートバスライン 2 6 とが電気的に接続されないよう、その間に絶縁膜を挟んだ構造、又は空気を挟んだエアブリッジ構造となっている。また、ゲートバスライン 2 6 からゲートパッド 2 8 へと引き出す配線 3 4 とソースバスライン 1 8 とが交差する領域も、絶縁膜を間に挟んだ構造

50

、又は空気を間に挟んだエアブリッジ構造となっている。

#### 【0027】

ここで、ゲートバスライン26についてより詳細に説明する。図4(a)は、図3の領域36におけるゲートバスライン26の上面模式図の例である。図4(b)は、図4(a)のA-A間に断面模式図の例であり、図4(c)は、図4(a)のB-B間に断面模式図の例である。また、比較のために、図4(d)に、比較例1のゲートバスライン86の上面模式図の例を示す。図4(d)を参照して、比較例1では、ゲートバスライン86は、一定の幅及び一定の厚さで延伸しており、幅は例えば $10\mu m$ で、厚さは例えば $1\mu m$ である。一方、図4(a)から図4(c)を参照して、実施例1では、ゲートバスライン26は、幅が狭くなった狭幅部分30を有する。狭幅部分30の長さLは例えば $15\mu m$ であり、幅W1は例えば $1\mu m$ であり、厚さT1は例えば $0.2\mu m$ である。狭幅部分30以外の部分(以下、幅広部分38と称す場合がある)での幅W2は例えば $10\mu m$ であり、厚さT2は例えば $1\mu m$ である。

10

#### 【0028】

図5は、実施例1に係る半導体装置の等価回路図の例である。図5を参照して、隣接する単位FET32の間に抵抗が付加されている。これは、ゲートバスライン26の一部に狭幅部分30を設けたことにより、狭幅部分30で抵抗が高くなつたことによるものである。例えばゲートバスライン26がAuからなる場合に、狭幅部分30の長さLを $15\mu m$ 、幅W1を $1\mu m$ 、厚さT1を $0.2\mu m$ とすることで、狭幅部分30の抵抗を2程度にすることができる。これにより、奇モードのループ発振を抑えることができる。

20

#### 【0029】

次に、図6(a)から図8(i)を用いて、実施例1に係る半導体装置の製造方法について説明する。図6(a)から図8(i)では、図4(a)のA-A間に相当する断面、図4(a)のB-B間に相当する断面及びゲートフィンガーが形成される領域の断面を用いて製造方法を説明する。

#### 【0030】

図6(a)から図6(c)を参照して、GaN基板からなる半導体基板40上に、例えばMOCVD(有機金属気相成長)法を用いて、i型GaN層41、n<sup>-</sup>A1GaN層44及びn型GaN層46を順次堆積する。これにより、半導体基板40上に、i型GaN層41、n<sup>-</sup>A1GaN層44及びn型GaN層46を含む半導体層48が形成される。なお、以下の図6(d)から図8(f)においては、図の簡略化のために、半導体基板40の図示は省略する。

30

#### 【0031】

図6(d)から図6(f)を参照して、活性領域16となるべき領域を、例えばレジストからなるマスク層50で覆い、マスク層50をマスクにしてAr(アルゴン)を注入する。これにより、活性領域16となるべき領域以外の領域の半導体層48を不活性化させる。

#### 【0032】

図6(g)から図6(i)を参照して、マスク層50を除去した後、半導体層48上に、例えばCVD(化学気相成長)法を用いて、窒化シリコン膜52を堆積する。続いて、窒化シリコン膜52上にレジスト54を形成し、ゲートフィンガー14やゲートバスライン26などを形成すべき領域の窒化シリコン膜52が露出するように、レジスト54をパターニングする。パターニング後、レジスト54をマスクとして、例えばドライエッチング法を用いて、窒化シリコン膜52をエッチングして除去する。

40

#### 【0033】

図7(a)から図7(c)を参照して、レジスト54を除去した後、半導体層48上及び窒化シリコン膜52上に、例えば真空蒸着法を用いて、厚さ $50nm$ のNi(ニッケル)層と厚さ $20nm$ のPd(パラジウム)層を堆積する。Ni層とPd層とを合わせて層56とする。図7(d)から図7(f)を参照して、層56のPd層上に、例えば真空蒸着法を用いて、厚さ $0.2\mu m$ のAu層58を堆積する。これらにより、半導体層48上

50

に、N<sub>i</sub>層とPd層とを合わせた層56及びAu層58を含む金属層60が形成される。

【0034】

図7(g)から図7(i)を参照して、Au層58上にレジストを形成し、ゲートバスライン26の幅広部分38が形成されるべき領域とゲートフィンガー14が形成されるべき領域とに開口を有するよう、レジストをパターニングして第1マスク層62を形成する。つまり、第1マスク層62は、ゲートバスライン26が形成されるべき領域のうち狭幅部分30が形成されるべき領域を覆い、幅広部分38が形成されるべき領域を開口するように形成される。その後、第1マスク層62をマスクとして、例えば電解めっき法を用いて、厚さ2μmのAuからなるめっき層64を形成する。

【0035】

図8(a)から図8(c)を参照して、第1マスク層62を除去した後、再度、Au層58上及びめっき層64上にレジストを形成する。そして、ゲートバスライン26の狭幅部分30が形成されるべき領域を覆うように、レジストをパターニングして第2マスク層66を形成する。第2マスク層66の幅W3は、ゲートバスライン26の幅広部分38に形成されためっき層64の幅W4よりも狭くなるように形成する。

【0036】

図8(d)から図8(f)を参照して、めっき層64と第2マスク層66とをマスクとして、例えばドライエッティング法を用いて、金属層60をエッティングして除去する。これにより、金属層60の側面とめっき層64の側面とは同一面を形成することになる。図8(g)から図8(i)を参照して、第2マスク層66を除去する。これにより、狭幅部分30と幅広部分38とを有するゲートバスライン26が形成される。また、ゲートバスライン26と同時にゲートフィンガー14が形成される。

【0037】

実施例1によれば、図7(a)から図7(f)のように、半導体層48上に金属層60を形成する。図8(a)及び図8(b)のように、ゲートバスライン26のパターンのうち一部分を除いたパターンを有するめっき層64と、一部分の領域を被覆すると共に、めっき層64が形成された領域におけるゲートバスライン26の幅よりも狭い幅の第2マスク層66を形成する。図8(d)及び図8(e)のように、めっき層64と第2マスク層66をマスクに金属層60をパターニングして、狭幅部分30を有するゲートバスライン26を形成する。

【0038】

これにより、図5で説明したように、エピ抵抗やチップ抵抗を用いることなく、奇モードのループ発振を抑制することが可能な半導体装置を得ることができる。したがって、チップ抵抗の場合に生じていた構成部品数の増加やエピ抵抗の場合に生じていたゲートリーク電流の発生などは起こらない。また、図5のように、抵抗はゲートに直列に接続されるわけではなく、利得特性の劣化を招くことを抑制できる。さらに、ゲートバスライン26の一部の幅を狭くすることから、ゲートの対地容量を減らすことができる。さらに、隣接する単位FET32間を最短距離で接続することができるため、単位FET32間の位相バランスが崩れ難く、単位FET32同士の出力は同相となり、単位FET32の出力を足し合わせたときの合成効率が上がる。

【0039】

奇モードのループ発振を抑制するには、ゲートバスライン26の狭幅部分30における抵抗を、例えば10以下のような低抵抗に精度良く合わせ込むことが求められる。例えば、狭幅部分30にもめっき層を形成し、めっき層をマスクに金属層60を除去する場合、最後に狭幅部分30のめっき層を除去しなければならず、狭幅部分30の抵抗がばらついてしまう。これに対し、図8(b)及び図8(e)のように、狭幅部分30にめっき層を形成せずに第2マスク層66を形成し、第2マスク層66をマスクに金属層60を除去することで、狭幅部分30の抵抗を低抵抗に精度良く合わせ込むことができる。これにより、奇モードのループ発振をより確実に抑制することができる。

【0040】

10

20

30

40

50

また、図8(a)及び図8(d)のように、ゲートバスライン26の幅広部分38では、めっき層64上に第2マスク層66を形成せずに、めっき層64をマスクに金属層60を除去している。例えば、めっき層64を覆って金属層60上にレジストを形成し、めっき層64上と金属層60上とにレジストを残存させる場合、めっき層64の厚さが厚いことから、めっき層64上と金属層60上とで露光での焦点が合わずパターニングが困難となる。つまり、レジストを精度良くパターニングすることが難しくなる。このため、図8(a)及び図8(b)のように、めっき層64上にはレジストを残存せずに、金属層60上にのみレジストが残存するようにパターニングをして第2マスク層66を形成している。これにより、第2マスク層66を精度良くパターニングすることができ、狭幅部分30の抵抗を低抵抗に精度良く合わせ込むことができる。よって、奇モードのループ発振をより確実に抑制することができる。10

#### 【0041】

図7(g)及び図7(h)のように、めっき層64は、ゲートバスライン26のパターンのうち一部分を除いたパターンの開口を有する第1マスク層62を形成し、第1マスク層62をマスクにして金属層60上に形成することが好ましい。

#### 【0042】

図3のように、ゲートバスライン26の一部分の領域である狭幅部分30が、ゲートパッド28の間に位置するように設けられることが好ましい。隣接するゲートパッド28の間のゲートバスライン26には電流があまり流れないとため、狭幅部分30を形成しても特性にはあまり影響を与えないためである。つまり、特性への影響を抑えつつ、奇モードのループ発振を抑えることができるためである。このことから、狭幅部分30は、複数のゲートパッド28までの電気長が実質的に等しい位置に設けられることがより好ましい。つまり、隣接するゲートパッド28それぞれから狭幅部分30までの電気長が等しくなることがより好ましい。ゲートパッド28からの電気長が等しい位置でのゲートバスライン26には電流がほとんど流れないとため、特性への影響をより抑えつつ、奇モードのループ発振を抑えることができるためである。20

#### 【0043】

図8(a)及び図8(d)のように、めっき層64をマスクとしたエッチングにより金属層60を除去することから、エッチング後のめっき層64の厚さは、エッチング前に比べて薄くなる。このように、めっき層64の厚さが薄くなることによるゲートバスライン26の抵抗増を考慮すると、めっき層64を $1\text{ }\mu\text{m} \sim 2\text{ }\mu\text{m}$ の厚さに形成することが好ましく、 $1.2\text{ }\mu\text{m} \sim 1.8\text{ }\mu\text{m}$ の厚さに形成することがより好ましい。また、エッチング後のめっき層64は、 $0.5\text{ }\mu\text{m} \sim 1\text{ }\mu\text{m}$ の厚さにすることが好ましく、 $0.7\text{ }\mu\text{m} \sim 0.8\text{ }\mu\text{m}$ の厚さにすることがより好ましい。30

#### 【0044】

図7(a)から図7(f)のように、金属層60として半導体層48側からN*i*層とP*d*層(層56)とA*u*層58とを順次積層させる場合が好ましい。また、図8(d)から図8(f)のように、めっき層64と第2マスク層66とをマスクにして、ドライエッチング法により金属層60を除去する場合が好ましい。ドライエッチング法により金属層60を除去することで、ゲートバスライン26の幅を精度良く制御することができる。つまり、狭幅部分30の幅を精度良く制御でき、狭幅部分30の抵抗を低抵抗に精度良く合わせ込むことができる。また、図7(g)から図7(i)では、めっき層64は電解めっき法により形成する場合を例に示したが、無電解めっき法により形成する場合でもよい。40

#### 【0045】

図7(f)のように、金属層60はゲートフィンガー14を形成する領域にも形成され、図7(i)のように、めっき層64はゲートフィンガー14のパターンをもって形成される。そして、図8(f)のように、ゲートバスライン26の形成と同時に、めっき層64をマスクにゲートフィンガー14における金属層60をパターニングすることが好ましい。つまり、ゲートバスライン26とゲートフィンガー14とを同じ工程で同時に形成する場合が好ましい。これにより、ゲートバスライン26とゲートフィンガー14とを、少50

ない工程数で製造することができ、コストの低減を実現できる。なお、ゲートバスライン 26とゲートフィンガー 14とを別々の工程で製造する場合でもよい。また、実施例 1では、図 3 のように、隣接する単位 FET 32 の間で、ゲートバスライン 26 に狭幅部分 30 を 1箇所設けた場合を例に示したが、この場合に限られず、2箇所、3箇所など複数箇所設ける場合でもよい。

#### 【0046】

実施例 1 では、ゲートバスライン 26 は、隣接する単位 FET 32 の間に狭幅部分 30 を有する場合を例に説明したが、この場合に限られる訳ではない。ゲートバスライン 26 の一部分の厚さを薄くすることで、隣接する単位 FET 32 の間に抵抗が付加されるよう 10 にしてもよい。このようなゲートバスラインは、半導体層上に金属層を形成した後、ゲートバスラインのパターンのうち一部分を除いたパターンを有するめっき層と、一部分の領域を被覆するマスク層と、をマスクにして金属層をパターニングすることで形成できる。

#### 【0047】

実施例 1 では、半導体基板 40 は GaN 基板である場合を例に示したが、この場合に限られず、例えば SiC 基板、Si 基板、GaAs 基板の場合でもよい。また、半導体層 48 は、i 型 GaN 層 41、n+AlGaN 層 44 及び n 型 GaN 層 46 からなる場合を例に示したが、この場合に限られる訳ではない。半導体層 48 は、窒素を含む III-V 族化合物半導体層または砒素を含む III-V 族化合物半導体層の場合でもよい。ここで、窒素を含む III-V 族化合物半導体の例として、例えば GaN、InN、AlN、AlGaN、InGaN、InAlN、AlInGaN などが挙げられる。また、砒素を含む III-V 族化合物半導体の例として、例えば GaAs、InAs、AlAs、InGaAs、AlGaAs、InAlGaAs などが挙げられる。 20

#### 【0048】

実施例 1 では、半導体装置が GaN 系 FET である場合を例に示したが、これに限られる訳ではない。窒素を含む III-V 族化合物半導体を用いた FET、HEMT の場合でもよい。また、GaAs 系 FET のような、砒素を含む III-V 族化合物半導体を用いた FET、HEMT の場合でもよい。GaAs 系 FET の場合では、半導体層上に設ける金属層は以下の方法により形成することができる。半導体層上に、例えばスパッタ法を用いて、厚さ 0.15 μm の WSi (タンゲステンシリサイド) 層を堆積する。WSi 層上に、例えばスパッタ法を用いて、厚さ 0.2 μm の Au 層を堆積する。これにより、半導体層上に、WSi 層及び Au 層を含む金属層を形成することができる。 30

#### 【0049】

以上、本発明の実施例について詳述したが、本発明はかかる特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

#### 【符号の説明】

#### 【0050】

- 10 ソースフィンガー

- 12 ドレインフィンガー

- 14 ゲートフィンガー

- 16 活性領域

- 18 ソースバスライン

- 20 ソースパッド

- 22 ドレインバスライン

- 24 ドレインパッド

- 26 ゲートバスライン

- 28 ゲートパッド

- 30 狹幅部分

- 32 単位 FET

- 34 配線

10

20

30

40

50

|     |                 |    |

|-----|-----------------|----|

| 3 8 | 幅広部分            |    |

| 4 0 | 半導体基板           |    |

| 4 1 | i 型 G a N 層     |    |

| 4 4 | n - A l G a N 層 |    |

| 4 6 | n 型 G a N 層     |    |

| 4 8 | 半導体層            |    |

| 5 2 | 窒化シリコン膜         |    |

| 5 4 | レジスト            |    |

| 5 6 | 層               |    |

| 5 8 | A u 層           | 10 |

| 6 0 | 金属層             |    |

| 6 2 | 第 1 マスク層        |    |

| 6 4 | めっき層            |    |

| 6 6 | 第 2 マスク層        |    |

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(51)Int.Cl. F I

H 01L 23/532 (2006.01) H 01L 27/04 H

H 01L 21/822 (2006.01)

H 01L 27/04 (2006.01)

(56)参考文献 特開平11-103072(JP,A)

特開2000-022089(JP,A)

特開平05-275373(JP,A)

特開平01-181574(JP,A)

## (58)調査した分野(Int.Cl., DB名)

H 01L 21/337 - 21/338

H 01L 27/095 - 27/098

H 01L 29/775 - 29/778

H 01L 29/80 - 29/812

H 01L 21/28 - 21/288

H 01L 21/44 - 21/445

H 01L 29/40 - 29/51

H 01L 21/3205

H 01L 21/768

H 01L 27/04