(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4276817号

(P4276817)

(45) 発行日 平成21年6月10日(2009.6.10)

(24) 登録日 平成21年3月13日(2009.3.13)

(51) Int.Cl.

H04N 9/07 (2006.01)

H04N 5/335 (2006.01)

F 1

HO 4 N 9/07

HO 4 N 5/335

HO 4 N 5/335A

P

V

請求項の数 5 (全 20 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2002-154185 (P2002-154185)  |

| (22) 出願日  | 平成14年5月28日 (2002.5.28)        |

| (65) 公開番号 | 特開2003-348607 (P2003-348607A) |

| (43) 公開日  | 平成15年12月5日 (2003.12.5)        |

| 審査請求日     | 平成17年5月30日 (2005.5.30)        |

前置審査

|           |                                             |

|-----------|---------------------------------------------|

| (73) 特許権者 | 000000376<br>オリンパス株式会社<br>東京都渋谷区幡ヶ谷2丁目43番2号 |

| (74) 代理人  | 100058479<br>弁理士 鈴江 武彦                      |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                      |

| (74) 代理人  | 100091351<br>弁理士 河野 哲                       |

| (74) 代理人  | 100088683<br>弁理士 中村 誠                       |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                      |

| (74) 代理人  | 100075672<br>弁理士 峰 隆司                       |

最終頁に続く

(54) 【発明の名称】撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

被写体像をカラー撮像するための色フィルタを備えた撮像素子と、

前記撮像素子を $2/3$ 画素間隔で $3 \times 3$ 箇所に周期的に変位させ、それぞれの変位位置

において前記撮像素子より前記被写体像の画像信号を出力させる変位手段と、

前記変位手段による各変位位置における前記撮像素子の画像信号が入力されるとともに

、該画像信号に基づき前記撮像素子の欠陥画素を特定し、該欠陥画素の画素データの階調

を0に置き換え、この画像信号を再配置して画像合成する画像処理手段と、

前記画像処理手段により出力される画像信号の画像ずらし位置を $3 \times 3$ 画素の構成とするとき、真中の画素に対し左右斜め上下方向に位置する欠陥画素に対しては、上下左右同色の4画素の信号レベルの和に $1/2$ を乗じた補正値を求め、前記真中の画素に対し上下左右方向に位置する欠陥画素に対しては、上下左右同色の4画素の信号レベルを加算した補正値を求め、前記真中に位置される欠陥画素に対しては、左右4画素間隔離れた位置にある同色の2画素の信号レベルの和に $1/2$ を乗じた補正値を求め、これら3つの補正値を用いて、それぞれ対応する欠陥画像の補正処理を行う欠陥画素補正手段と

を具備したことを特徴とする撮像装置。

## 【請求項 2】

前記欠陥画素補正手段は、前記画像処理手段により合成された画像の欠陥画素に対し、

色の判別情報と前記変位手段による変位位置に応じて異なる補正処理を行うことを特徴とする

請求項1記載の撮像装置。

**【請求項 3】**

前記欠陥画素補正手段は、前記色の判別情報により欠陥画素がG(緑)と判断した場合は、該欠陥画素に対して上下左右同色の4画素の信号レベルの和に1/4を乗じた補正值を求め、該補正值により補正処理を行うことを特徴とする請求項2記載の撮像装置。

**【請求項 4】**

前記欠陥画素補正手段は、さらに位置情報変換手段を有し、該位置情報変換手段により画素ずらし後の画像信号の位置情報を変換して画像信号を複数に分割し、これら分割された画像信号を順に処理することを特徴とする請求項1記載の撮像装置。

**【請求項 5】**

前記撮像素子に被写体像を投射する顕微鏡と、

10

前記被写体像を前記撮像素子に投射するか否かを選択する遮光手段と、

前記遮光手段により前記撮像素子への被写体像の投射を遮光した状態において、前記撮像素子より出力される画像信号の各画素の欠陥を検出する欠陥画素検出手段と、

をさらに有することを特徴とする請求項1記載の撮像装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、画素欠陥補正機能を有するデジタルカメラ(電子スチルカメラ)などの撮像装置に関するものである。

**【0002】**

20

**【従来の技術】**

一般に半導体により形成されるCCD等の固体撮像素子は、局所的な結晶欠陥等によって画素劣化することが知られている。

**【0003】**

このような画素劣化に対し画素欠陥補正を行う方法として、例えば、特開2000-59799号公報に開示されるように、欠陥画素周囲の上下左右の隣接する4画素に着目し、これら4画素により欠陥画素を補間することで欠陥画素を補償し、画素劣化を抑止するようにしたものが考えられている。

**【0004】**

このような画素欠陥補正の方法によれば、隣接する画素は同様な情報をもつのが通例であるため、これら隣接する画素を用いた補間による解像度の劣化はさほどなく有効な結果が得られる。

30

**【0005】**

ところで、近年、2次元固体撮像素子を使用したデジタルカメラ(電子スチルカメラ)などの撮像装置が一般に普及してきているが、このような撮像装置にあっては、さらに解像度の高い画像が求められるようになっている。

**【0006】**

そこで、高い解像度を得るための手段として、例えば、特開平8-251604号公報に開示されるように撮像素子を2次元方向に変位させて撮像し、それらを合成する画素ずらし方式を採用することにより、高精細な画像を得るような方法が用いられるようになっている。

40

**【0007】**

しかしながら、このような画素ずらし方式について、上述した欠陥画素周囲の上下左右の隣接する4画素により欠陥画素を補間して欠陥画素補正を行う方法を採用すると、欠陥画素を隣接する欠陥画素自身で補間することになるため、画像の劣化を抑止することが困難となる。

**【0008】**

このような問題に対しては、例えば、特開平7-322151号公報に開示されるように、1画素以上離れた大きな間隔で画素ずらしを行うことで、合成後の画像に欠陥画素が隣接して配置されないようにし、欠陥画素補償の際に、隣接する欠陥画素自身で補間するこ

50

とがなく、常に正常な画素による補間によって画像の劣化を抑止できるようにした欠陥画素補正方法も考えられている。

#### 【0009】

##### 【発明が解決しようとする課題】

ところが、撮像時の撮像素子の変位量を大きくすることは、欠陥画素の補償効果を高めることができるもの、撮像素子を1画素以上離れた遠くまで移動させるため、撮像素子の移動誤差が大きくなつて、画像劣化の原因となるおそれがある。また、撮像素子を変位させるものとして、ピエゾ素子などの圧電素子が用いられるが、大きな変位量を得るには、駆動電圧も高める必要があるため、駆動回路が大型化するという問題も生じる。

#### 【0010】

本発明は上記事情に鑑みてなされたもので、隣接画素による欠陥画素補正をより正確に行い、撮像素子の変位による誤差を小さくして画像劣化を抑えることのできる撮像装置を提供することにある。

#### 【0011】

##### 【課題を解決するための手段】

請求項1記載の発明は、被写体像をカラー撮像するための色フィルタを備えた撮像素子と、前記撮像素子を $2/3$ 画素間隔で $3 \times 3$ 箇所に周期的に変位させ、それぞれの変位位置において前記撮像素子より前記被写体像の画像信号を出力させる変位手段と、前記変位手段による各変位位置における前記撮像素子の画像信号が入力されるとともに、該画像信号に基づき前記撮像素子の欠陥画素を特定し、該欠陥画素の画素データの階調を0に置き換え、この画像信号を再配置して画像合成する画像処理手段と、前記画像処理手段により出力される画像信号の画素ずらし位置を $3 \times 3$ 画素の構成とするとき、真中の画素に対し左右斜め上下方向に位置する欠陥画素に対しては、上下左右同色の4画素の信号レベルの和に $1/2$ を乗じた補正值を求め、前記真中の画素に対し上下左右方向に位置する欠陥画素に対しては、上下左右同色の4画素の信号レベルを加算した補正值を求め、前記真中に位置される欠陥画素に対しては、左右4画素間隔離れた位置にある同色の2画素の信号レベルの和に $1/2$ を乗じた補正值を求め、これら3つの補正值を用いて、それぞれ対応する欠陥画像の補正処理を行う欠陥画素補正手段とを具備したことを特徴としている。

#### 【0014】

請求項2記載の発明は、請求項1記載の発明において、前記欠陥画素補正手段は、前記画像処理手段により合成された画像の欠陥画素に対し、色の判別情報と前記変位手段による変位位置に応じて異なる補正処理を行うことを特徴としている。

#### 【0015】

請求項3記載の発明は、請求項2記載の発明において前記欠陥画素補正手段は、前記色の判別情報により欠陥画素がG(緑)と判断した場合は、該欠陥画素に対して上下左右同色の4画素の信号レベルの和に $1/4$ を乗じた補正值を求め、該補正值により補正処理を行うことを特徴としている。

#### 【0016】

請求項4記載の発明は、請求項1記載の発明において、前記欠陥画素補正手段は、さらに位置情報変換手段を有し、該位置情報変換手段により画素ずらし後の画像信号の位置情報を変換して画像信号を複数に分割し、これら分割された画像信号を順に処理することを特徴としている。

#### 【0017】

請求項5記載の発明は、請求項1記載の発明において、前記撮像素子に被写体像を投射する顕微鏡と、前記被写体像を前記撮像素子に投射するか否かを選択する遮光手段と、前記遮光手段により前記撮像素子への被写体像の投射を遮光した状態において、前記撮像素子より出力される画像信号の各画素の欠陥を検出する欠陥画素検出手段と、をさらに有することを特徴としている。

#### 【0019】

この結果、本発明によれば、画素ずらし位置に応じて欠陥画素の補正処理を異ならすこと

10

20

30

40

50

で、より正確な欠陥画素補正を行うことができ、また、画素ずらしの幅も1画素以内と小さくできるので、撮像素子の変位による誤差による画像劣化も同時に抑制することができる。

#### 【0020】

また、本発明によれば、G(緑)の欠陥画素については、正常な同色隣接画素で補正することができるので、画像の解像度に大きく影響するG(緑)の欠陥画素に対して正確な補正を実現できる。

#### 【0021】

さらに、本発明によれば、画像信号を分割したことで、1ライン幅を小さくできるので、少ない容量のものを使用して同等な処理を行うことができる。

10

#### 【0022】

さらにまた、本発明によれば、補正処理は、暗ノイズの目立つ画素についても行うことができるので、顕微鏡において、蛍光観察などの暗い試料の撮影の場合に、画像ノイズを減少させることができる。

#### 【0023】

##### 【発明の実施の形態】

以下、本発明の実施の形態を図面に従い説明する。

#### 【0024】

##### (第1の実施の形態)

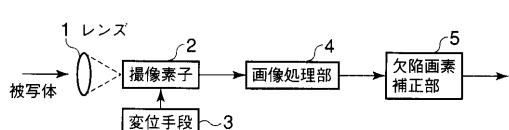

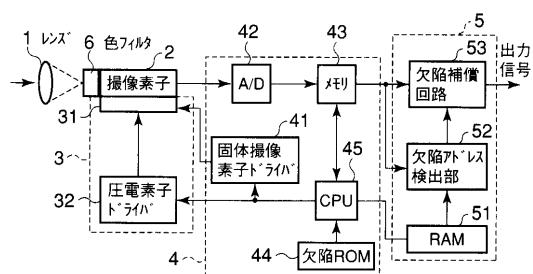

図1は、本発明が適用される撮像装置の概略構成を示すものである。図1において、1は撮像レンズで、この撮像レンズを通った被写体像がCCDからなる撮像素子2の撮像面に結像される。撮像素子2は、撮像面に結像された被写体像を光電変換し、アナログ画像信号として画像処理手段の画像処理部4に出力する。

20

#### 【0025】

撮像素子2には、変位手段3が接続されている。変位手段3は、ピエゾ素子などの圧電素子を有するものである。撮像素子2は、圧電素子の動作により、周期的に変位され、それぞれの変位位置ごとに被写体像の画像信号を出力する。これにより、画像処理部4には、撮像素子2の変位位置毎の画像信号が入力される。

#### 【0026】

画像処理部4は、被写体の変位位置毎に画像信号を読み出し再配置を行い、1枚の画像に合成する。画像処理部4には、欠陥画素補正手段としての欠陥画素補正部5が接続されている。この欠陥画素補正部5は、画像処理部4において合成された画像中の欠陥画素に対して変位手段3による変位位置に応じた欠陥画素の補正を行うようになっている。

30

#### 【0027】

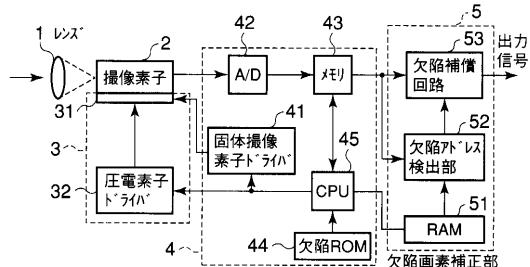

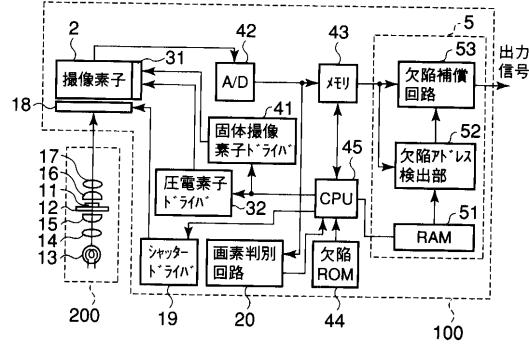

図2は、このように構成された撮像装置をさらに詳細に説明するための図で、図1と同一部分には同符号を付している。

#### 【0028】

この場合、変位手段3は、ピエゾ素子等の圧電素子31と、この圧電素子31を駆動する圧電素子ドライバ32により構成され、圧電素子ドライバ32により駆動される圧電素子31により撮像素子2を周期的に変位させ、それぞれの変位位置での被写体像の画像信号を出力させる。

40

#### 【0029】

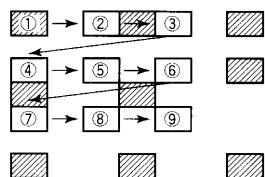

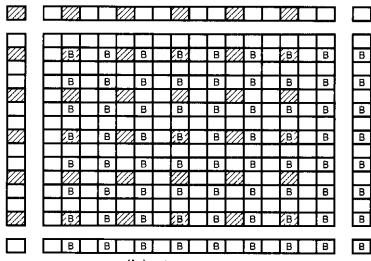

ここでの撮像素子2は、圧電素子ドライバ32により駆動される圧電素子31により、図3に示すように、基準画素位置1に対して2/3画素間隔ずつ、1 2 ...

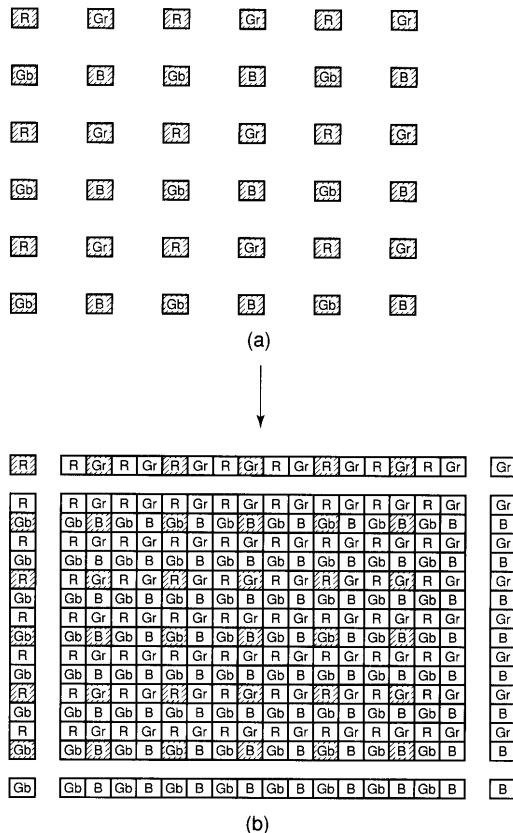

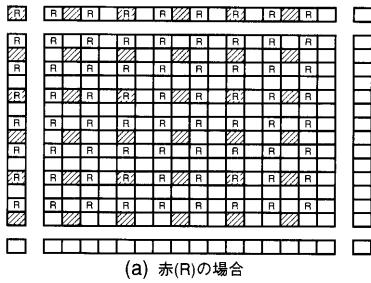

8 9 の順番で、垂直、水平方向に各々3箇所で、 $3 \times 3$ の合計9箇所に画素ずらしを行い、これら変位位置毎に被写体像の画像信号を出力するようになっている。図4(a)(b)は、画素ずらし前後の画素の色配列を表したもので、同図(a)に示す画素ずらし前のR,G,Bの画素の色配列に対して、図3に示す手順に従って2/3画素間隔で9箇所に画素ずらしを行った後の画像は、同図(b)に示すようになり、R,G,Bの色配列は変わらずに、水平、垂直方向共に約3倍の画素数になる。

50

**【 0 0 3 0 】**

図2に戻って、画像処理部4は、固体撮像素子ドライバ41、A/D変換器42、メモリ43、欠陥ROM44およびCPU45から構成されている。

**【 0 0 3 1 】**

固体撮像素子ドライバ41は、撮像素子2を所定のタイミング信号に基づいた露出時間で駆動し、被写体像をアナログ画像信号として出力させるものである。A/D変換器42は、撮像素子2より出力されるアナログ画像信号をデジタル画像信号に変換するものである。メモリ43は、CPU45からの制御信号によってA/D変換器42を通ってデジタル化された画像信号を画素ずらし位置ごとに格納するようにしている。欠陥ROM44は、撮像素子2固有の欠陥画素位置のアドレスがあらかじめ格納されている。また、CPU45は、画素ずらし位置毎にメモリ43に格納した画像信号を画素ごとに読み出し再配置して、1枚の画像として合成した後、画像信号、画素ずらし位置を表わす変位位置信号および画素のアドレス(位置情報)を欠陥画素補正部5に出力するようにしている。10

**【 0 0 3 2 】**

欠陥画素補正部5は、RAM51、欠陥アドレス検出部52および欠陥補償回路53から構成されている。

**【 0 0 3 3 】**

RAM51は、画像処理部4の欠陥ROM44にあらかじめ格納されている撮像素子2固有の欠陥画素位置のアドレス、つまり欠陥画素アドレスをCPU45を通して書き込むものである。欠陥アドレス検出部52は、RAM51に格納された欠陥画素アドレスと、画像処理部4のCPU45を通して入力される画像信号の各画素のアドレス(位置情報)とを比較し、両者が一致したときに欠陥画素を検出したと判断して、欠陥検出信号を欠陥補償回路53に出力するようにしている。欠陥補償回路53は、画像処理部4のCPU45を通して画像信号とともに、この画像信号の画素のずらし位置を示す変位位置信号が入力されており、欠陥アドレス検出部52からの欠陥検出信号を検出しないときは、画像信号に何も処理を施すことなく出力し、欠陥検出信号を検出したときは、変位位置信号に応じた処理により欠陥画素を補正するようになっている。20

**【 0 0 3 4 】**

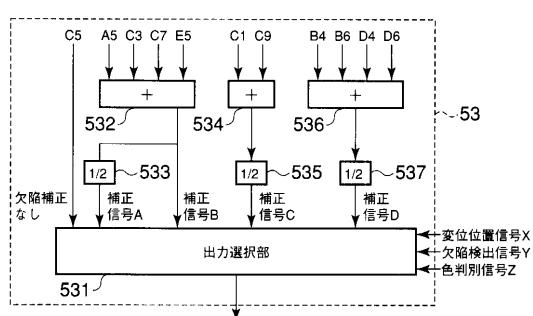

次に、このような欠陥補償回路53で行う欠陥画素の補正処理について説明する。

**【 0 0 3 5 】**

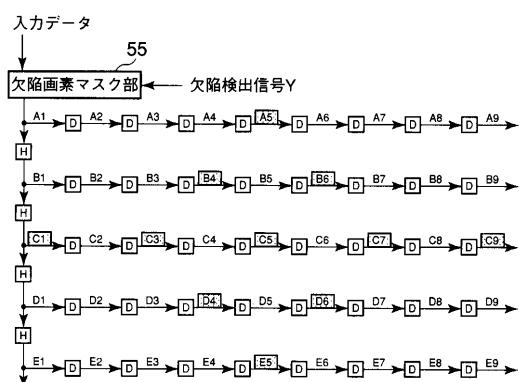

図5、図6は、欠陥補償回路53の概略構成を示している。図5の欠陥画素マスク部55は、欠陥アドレス検出部52から入力される欠陥検出信号Yに基いて、入力画像データが欠陥画素であると判定した時に、画素データの階調を0に置き換えて出力する。従って、これにより後段の回路における欠陥画素はすべて階調0となる。また、図5において、(H)はラインバッファ、(D)はD-FFである。これらラインバッファ(H)およびD-FF(D)には、それぞれCLK端子(未図示)がつけられており、1CLKごとに画像信号を転送する。30

**【 0 0 3 6 】**

そして、CLKに同期して1画素ずつ入力される画像信号について1~4回ラインバッファ(H)を通すことによって、画素信号A1に対して1~4ライン遅延した画素信号B1、C1、D1、E1を生成する。また、これら画素信号A1、B1、C1、D1、E1について複数回D-FF(D)を通することで、画像信号に対して4ライン+8CLKまで遅延したA1~A9、B1~B9、C1~C9、D1~D9、E1~E9の画素信号を生成する。こうすることで、同一時間帯で5×9の画素範囲の任意の画像信号を参照することができ、Ai、Bi、Ci、Di、Ei(i=1~9)について各画素信号のレベルを観測できる。40

**【 0 0 3 7 】**

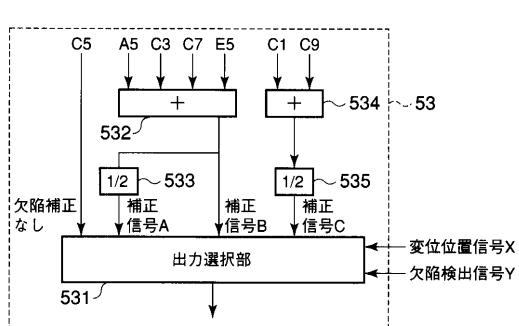

図6は、欠陥補償回路53における欠陥画素の補正を行う回路のブロック図である。図面中の符号C5、A5、C3、C7、E5、C1、C9は、図5に示す5×9の画素範囲中の画素信号を表している。このうちの画素信号C5は、直接出力選択部531に入力され50

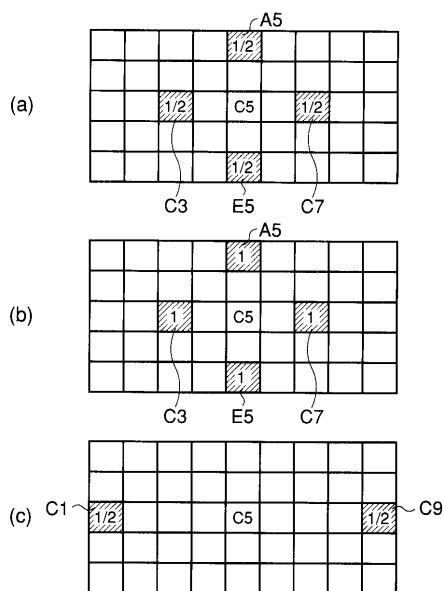

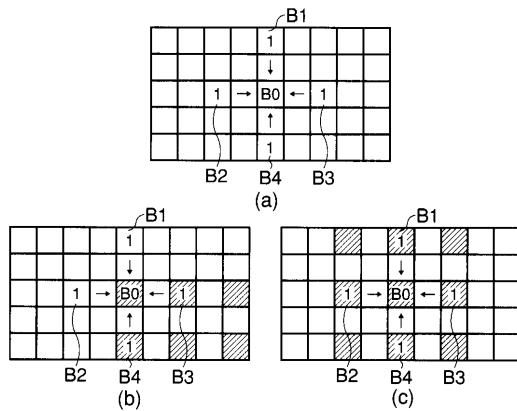

ている。また、画素信号 A 5、C 3、C 7、E 5 は、加算器 532 に入力され、この加算器 532 の和出力は、1/2 乗算器 533 を介して補正信号 A として出力選択部 531 に入力され、また、加算器 532 の出力は、補正信号 B として直接出力選択部 531 に入力される。さらに、画素信号 C 1、C 9 は、加算器 534 に入力され、この加算器 534 の和出力は 1/2 乗算器 535 を介して補正信号 C として出力選択部 531 に入力される。これにより、画素信号 C 5 が中心画素に対応するものとすると、補正信号 A は、図 7 (a) に示すように上下左右同色の 4 画素の画素信号 A 5、C 3、C 7、E 5 の信号レベルの和に 1/2 を乗じた値と等しく、補正信号 B は、図 7 (b) に示すように上下左右同色の 4 画素の画素信号 A 5、C 3、C 7、E 5 の信号レベルを加算した値に等しく、さらに補正信号 C は、図 7 (c) に示すように左右 4 画素間隔離れた位置にある同色の 2 画素の画素信号 C 1、C 9 の信号レベルの和に 1/2 を乗じた値に等しくなる。10

#### 【0038】

出力選択部 531 には、画像処理部 4 の CPU 45 を通して入力される変位位置信号 X と欠陥アドレス検出部 52 から入力される欠陥検出信号 Y が与えられている。出力選択部 531 は、欠陥検出信号 Y が与えられないときは、画素信号 C 5 をそのまま出力する。また、欠陥検出信号 Y が与えられると、このとき入力される変位位置信号 X の種類に応じて、補正信号 A、B、C のいずれかにより画素補正処理を行う。つまり、出力選択部 531 は、図 8 に示すテーブルが用意されていて、変位位置信号 X が図 3 に示す画素ずらし位置 1, 3, 7, 9 に相当するものである場合は補正信号 A、画素ずらし位置 2, 4, 6, 8 に相当するものである場合は補正信号 B、画素ずらし位置 5 に相当するものである場合は補正信号 C をそれぞれ選択し、これら補正信号 A、B、C により欠陥画素の補正処理を行う。20

#### 【0039】

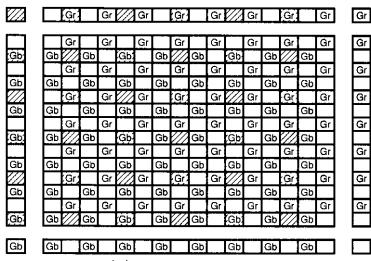

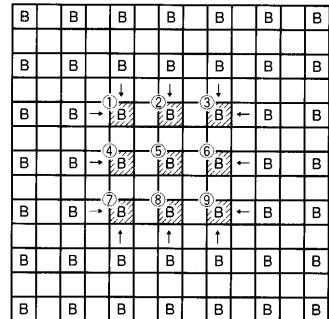

次に、このような欠陥補償回路 53 による欠陥画素補正をさらに詳細に説明する。図 9 (a) (b) (c) は、図 4 で述べた画素ずらし後の画素をそれぞれ R、B、G の色別に抜き出したものである。ここで、図 9 (b) に示す B (青) の画素に着目すると、ある 1 画素に欠陥があった場合、図 3 で述べた画素ずらしによって、図 10 中の斜線部分で示す 9 個所の画素 B (青) に欠陥が含まれることになる。

#### 【0040】

図 11 は、従来用いられている欠陥画素補正方法を示したものであり、この方法によれば、同図 (a) に示すように、欠陥画素 B 0 に対して、その位置に関係なく上下左右に隣接する同色の 4 画素 B 1 ~ B 4 によって補正する。これにより、例えば同図 (b) に示すように着目する画素 B 0 が欠陥 9箇所の左上である場合は、上下左右に隣接する同色の 4 画素 B 1 ~ B 4 のうち画素 B 3、B 4 が欠陥画素 (図示斜線部分) として含まれ、また、同図 (c) に示すように着目する画素 B 0 が欠陥 9箇所の真中にある場合は、上下左右に隣接する同色の 4 画素 B 1 ~ B 4 の全てが欠陥画素 (図示斜線部分) となる。このため、これらの方法で欠陥画素補正処理を実行すると、欠陥位置により処理結果に相違が生じ、一様な効果を期待することが困難となる。30

#### 【0041】

これに対して、本発明においては、変位位置信号 X が図 3 に示す画素ずらし位置 1, 3, 7, 9 に相当する場合は、図 10 に示すように同色の隣接 4 画素中 2 画素に(出力階調が 0 の)欠陥画素 (斜線部分で示す) が含まれるため、補正信号 A (補正值) は正常な同色隣接 2 画素の平均値と等しくなる。例えば、画素ずらし位置 1 では、図 7 (a) に示す上下左右同色の 4 画素の画素信号 A 5、C 3、C 7、E 5 のうち画素信号 C 7、E 5 が欠陥画素となって出力階調が 0 となるので、補正信号 A (補正值) は、正常な同色隣接 2 画素の画素信号 A 5、C 3 の平均値として求められる。画素ずらし位置 3, 7, 9 についても同様で、補正信号 A (補正值) は、正常な同色隣接 2 画素の平均値として求められる。40

#### 【0042】

また、変位位置信号 X が図 3 に示す画素ずらし位置 2, 4, 6, 8 に相当50

する場合は、図 10 に示すように同色の隣接 4 画素中 3 画素に(出力階調が 0 の)欠陥画素(斜線部分で示す)が含まれるため、補正信号 B(補正值)は、正常な同色隣接 1 画素の値と等しくなる。例えば、画素ずらし位置 2 では、図 7 (b) に示す上下左右同色の 4 画素の画素信号 A5、C3、C7、E5 のうち画素信号 C3、C7、E5 が欠陥画素となって出力階調が 0 となるので、補正信号 B(補正值)は、正常な同色隣接 1 画素の画素信号 A5 の値として求められる。画素ずらし位置 4, 6, 8 についても同様で、補正信号 B(補正值)は、正常な同色隣接 1 画素の値として求められる。

#### 【0043】

さらに、変位位置信号 X が図 3 に示す画素ずらし位置 5 に相当する場合は、図 10 に示すように同色の隣接 4 画素すべてが(出力階調が 0 の)欠陥画素(斜線部分で示す)であるため、補正信号 C(補正值)は、最も近傍の正常な同色 2 画素の平均値と等しくなる。例えば、画素ずらし位置 5 では、図 7 (c) に示す上下左右同色の 4 画素の画素信号 A5、C3、C7、E5 すべてが欠陥画素となって出力階調が 0 となるので、補正信号 C(補正值)は、最も近傍の正常な同色 2 画素の画素信号 C1、C9 の平均値として求められる。

#### 【0044】

その後、これら画素ずらし位置に応じて異なる補正信号 A、B、C を用いて欠陥画素の補正を行うようにすれば、いずれの変位位置においても、それぞれの欠陥画素を同色の画素信号により一様に補正することができる。

#### 【0045】

従って、このようにすれば、画素ずらし位置に応じて欠陥画素の補正処理を異ならすことによって、より正確な欠陥画素補正を行うことができる。また、画素ずらしの幅も 1 画素以内と小さいため、撮像素子の変位による誤差も小さくでき、変位誤差による画像劣化も同時に抑制することができる。

#### 【0046】

なお、本実施の形態においては、上下左右同色の画素信号がすべて欠陥画素の場合、補正值を左右近傍の正常な同色画素によって求めたが、ラインバッファの数を増やした場合、上下近傍の正常な同色画素によって求めることが可能である。また、ラインバッファとともに遅延素子 (D - F F) の個数も可変とすることで、任意の位置の画像信号をもとにした補正值を求めることができる。

#### 【0047】

##### (第 2 の実施の形態)

次に、本発明の第 2 の実施の形態について説明する。

#### 【0048】

この第 2 の実施の形態の特徴は、色フィルタを有し、各色毎に欠陥画素補正方法を変えることにある。

#### 【0049】

図 12 は、本発明の第 2 の実施の形態の概略構成を示すもので、図 2 と同一部分には、同符号を付している。

#### 【0050】

この場合、撮像素子 2 には、色の判別情報を取得するための色フィルタ 6 がアレイ状に設けられている。その他は、図 2 と同様である。

#### 【0051】

このような構成において、色フィルタ 6 を通って撮像素子 2 に結像された被写体像は、撮像素子 2 によって光電変換された後、画像処理部 4 に入力される。この場合、撮像素子 2 は、圧電素子ドライバ 32 により駆動される圧電素子 31 により垂直、水平方向に各々 3 個所、計 9 箇所に画素ずらしが行われており、これら変位位置毎の画像信号が色の判別情報とともに画像処理部 4 に入力される。

#### 【0052】

画像処理部 4 では、撮像素子 2 から入力される画像信号によって 1 枚の画として合成した

10

20

30

40

50

後、画像信号、画像信号の変位位置信号、各画素のアドレス(位置情報)および色判別の情報を欠陥補償回路53に出力する。

#### 【0053】

欠陥補償回路53は、図5で述べた回路構成により、画像信号に対して4ライン+8CLKまで遅延したA1～A9、B1～B9、C1～C9、D1～D9、E1～E9の画素信号を生成する。

#### 【0054】

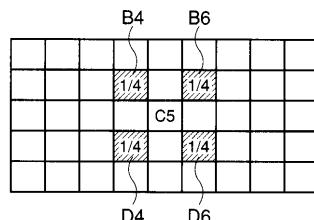

図13は、欠陥補償回路53における欠陥画素の補正を行う回路のブロック図である。図面中の符号C5、A5、C3、C7、E5、C1、C9、B4、B6、D4、D6は、図5に示す5×9画素範囲の中の画素信号を表している。このうちの画素信号C5、A5、C3、C7、E5、C1、C9に対しては、図6で述べたと同様な補正信号A、B、Cを生成するための回路が構成されている。また、画素信号B4、B6、D4、D6は、加算器536に入力され、この加算器536の和出力は1/4乗算器537を介して補正信号Dとして出力選択部531に入力される。これにより、画素信号C5が中心画素に対応するものとすると、補正信号Dは、図14に示すように左右斜め上下同色の4画素の画素信号B4、B6、D4、D6の信号レベルの和に1/4を乗じた値に等しくなる。

10

#### 【0055】

また、出力選択部531は、画像処理部4から入力される変位位置信号Xと欠陥アドレス検出部52から入力される欠陥検出信号Yの他に、さらに画像処理部4から入力される色判別信号Zが与えられている。出力選択部531は、欠陥検出信号Yが与えられないときは、画素信号C5をそのまま出力する。また、欠陥検出信号Yが与えられると、このとき入力される変位位置信号Xと色判別信号Zの種類に応じて、補正信号A、B、C、Dのいずれかにより画素補正処理を行う。つまり、出力選択部531は、図15に示すテーブルが用意されていて、色判別信号ZがR(赤)あるいはB(青)のときは、変位位置信号Xが、図3に示す画素ずらし位置1, 3, 7, 9に相当するものである場合は補正信号A、画素ずらし位置2, 4, 6, 8に相当するものである場合は補正信号B、画素ずらし位置5に相当するものである場合は補正信号Cをそれぞれ選択し、さらに、色判別信号ZがG(緑)のときは、補正信号Dを選択し、これら補正信号A、B、C、Dにより欠陥画素の補正処理を行う。

20

#### 【0056】

この場合、色判別信号ZがR(赤)あるいはB(青)のときの欠陥画素の補正処理方法は、第1の実施の形態と同様になる。すなわち、変位位置信号Xが図3に示す画素ずらし位置1, 3, 7, 9に相当する場合は、図10に示すように同色の隣接4画素中2画素に(出力階調が0の)欠陥画素(斜線部分で示す)が含まれるため、補正信号A(補正值)は正常な同色隣接2画素の平均値として求められる。また、変位位置信号Xが図3に示す画素ずらし位置2, 4, 6, 8に相当する場合は、図10に示すように同色の隣接4画素中3画素に(出力階調が0の)欠陥画素(斜線部分で示す)が含まれるため、補正信号B(補正值)は、正常な同色隣接1画素の値として求められる。さらに、変位位置信号Xが図3に示す画素ずらし位置5に相当する場合は、図10に示すように同色の隣接4画素すべてが(出力階調が0の)欠陥画素(斜線部分で示す)であるため、補正信号C(補正值)は、最も近傍の正常な同色2画素の平均値として求められる。

30

#### 【0057】

一方、色判別信号ZがG(緑)の場合の欠陥画素の補正方法は、第1の実施の形態と異なる。図9は、図4で述べた画素ずらし後の画素をそれぞれR、B、Gの色別に抜き出したものであるが、このうちの図9(c)に示すGの画素に着目すると、同図(a)(b)に示すRやBの画素と比較して画素数が多く、画素ずらし後のGの同色の画素は斜めに隣接する位置に存在する。

40

#### 【0058】

そこで、色判別信号ZがG(緑)の場合は、変位位置信号Xに関係なく、補正信号Dを、図14に示すように左右斜め上下同色の4画素の画素信号B4、B6、D4、D6の信号レ

50

ペルの和に  $1 / 4$  を乗じた値として求め、この補正信号 D を用いて欠陥画素の補正処理を行う。

#### 【0059】

従って、このようにすれば、 $2 / 3$  画素間隔で 9箇所に変位する画素ずらし方式においては、G(緑)の欠陥画素については、正常な同色隣接画素で補正することができるので、画像の解像度に大きく影響する G(緑)の欠陥画素に対して正確な補正を実現でき、画像解像度の低下を抑止することができる。

#### 【0060】

##### (第3の実施の形態)

次に、本発明の第3の実施の形態について説明する。

10

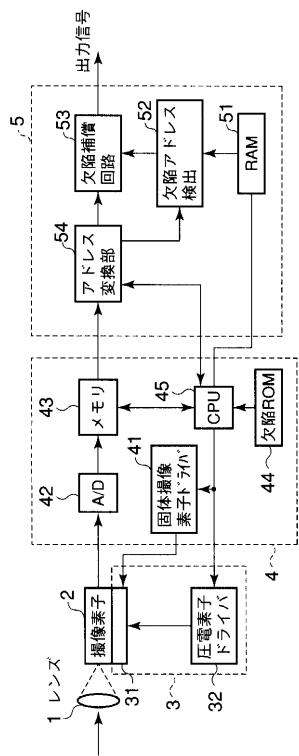

#### 【0061】

この第3の実施の形態の特徴は、画像処理部から出力される画素ずらし後の画像のアドレスを変換することによって画像データを分割し、分割した画像信号毎に順次欠陥画素の補正を行うことにある。

#### 【0062】

図16は、本発明の第3の実施の形態の概略構成を示すもので、図2と同一部分には、同符号を付している。

#### 【0063】

この場合、欠陥画素補正部5は、位置情報変換手段としてのアドレス変換部54が設けられている。このアドレス変換部54は、CPU45とデータの送受信を行いつつ欠陥ROM44に格納されたテーブルに基づいて画素ずらし後の画像信号アドレスと欠陥画素アドレスを変換することで画像信号を複数に分割し、これら分割した画像信号とアドレスを順次欠陥補償回路53に出力するようになっている。その他は、図2と同様である。

20

#### 【0064】

このような構成において、レンズ1を通って撮像素子2に結像された被写体像は、撮像素子2によって光電変換され、さらに圧電素子31により垂直、水平方向に各々3個所、計9箇所に画素ずらしが行われた後、画像処理部4に入力される。そして、画像処理部4において第1の実施の形態で述べたと同様な手順で1枚の画像を合成した後、画像信号、画像信号の変位位置信号、各画素のアドレス(位置情報)をアドレス変換部54に出力する。

#### 【0065】

アドレス変換部54では、CPU45とデータの送受信を行いつつ欠陥ROM44に格納された各種のテーブルにしたがって画素ずらし後の画像信号アドレスと欠陥画素アドレスを変更して、複数の画像信号に分割し、これら分割した画像信号とアドレスを順次欠陥補償回路53に出力する。欠陥補償回路53は、アドレス変換部54から入力された分割された画像信号とそのアドレスに基づいて第1の実施の形態で述べたと同様な手順で欠陥画素の補正を行い、その結果を出力する。

30

#### 【0066】

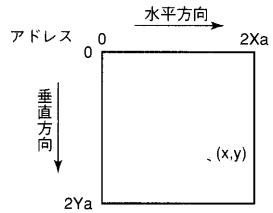

ここで、アドレス変換部54におけるアドレス変換の手順を詳細に説明する。図17は、画素ずらし後の垂直方向 $2Y_a \times$ 平行方向 $2X_a$ の画素数を有する画像であり、アドレスは $(0 \sim 2X_a, 0 \sim 2Y_a)$ に割り当てられている。

40

#### 【0067】

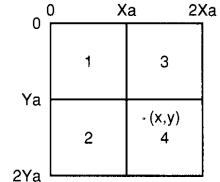

まず、この画像信号を図18に示すように高さ $X_a$ 、幅 $Y_a$ の画像に4分割する場合について述べる。

#### 【0068】

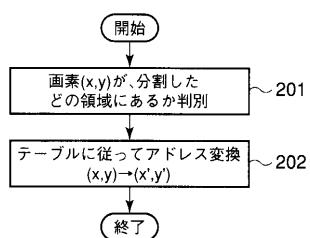

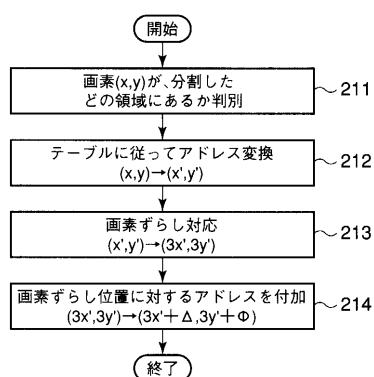

図20は、アドレス変換の処理手順を表したフローチャートを示すもので、最初に、ステップ201で、入力された画素の位置( $x, y$ )が、分割した4つの領域のいずれに属するかを図22に示すテーブルに基づいて判断する。ここで、例えば、 $x < X_a, y < Y_a$ であるならば、画素位置は、領域1に存在すると判断する。次に、ステップ202で、図23に示すテーブルに基づいて各領域ごとに画像信号を変換する。すなわち、画素が領域1にあると判断したときは、アドレスを変換せずにそのまま出力する。また、画

50

素が領域 2 にあると判断したときは、水平方向のアドレス  $x$  は変えず垂直方向のアドレス  $y$  を  $y' = y - Y_a$  に変換する。領域 3 4 の場合も同様の方法で変換する。

#### 【0069】

例えば、 $(X_a, Y_a) = (1000, 1000)$  のとき、画素  $(x, y) = (1200, 1500)$  のアドレスは  $X_a < 1200, Y_a < 1500$  であるから領域 4 にあると判断され、アドレスは、 $(1200 - 1000, 1500 - 1000) = (200, 500)$  に変換する。

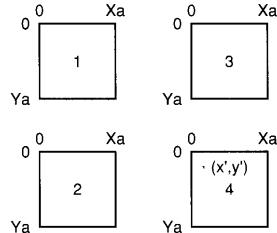

#### 【0070】

このようにして画像信号のアドレスは、上述した処理の実行によって図 19 に示すように各分割領域の左端上を  $(0, 0)$  とした水平方向画素数  $X_a$ 、垂直方向画素数  $Y_a$  の領域のアドレスに変換される。

10

#### 【0071】

次に、分割した画像信号に対して欠陥補正を行うために、欠陥画素アドレスを変換する手順について述べる。

#### 【0072】

この場合、欠陥画素は、撮像素子 2 毎に固有に存在するものであり、欠陥画素アドレスは画素ずらし前の位置情報として表されている。したがって、画素ずらし後の画像に対して欠陥画素補正処理を行うためには、欠陥画素アドレスも変換する必要がある。

#### 【0073】

ここで撮像素子 2 の画素数が水平、垂直方向にそれぞれ  $2X_a', 2Y_a'$  であるとする。

20

#### 【0074】

図 21 は、欠陥 ROM 44 に格納された欠陥画素アドレスを変換する処理手順を表したフローチャートを示すもので、まず、ステップ 211 で、欠陥画素  $(x, y)$  が画像全体の分割したどの領域に存在するかを判断する。次に、ステップ 212 で、テーブルに基づいた領域ごとのアドレス変換を行う。この領域ごとにアドレス変換するまでの処理手順は、 $X_a \sim X_a', Y_a \sim Y_a'$  と置き換えることで、上述した画像信号のアドレス変換の場合と同様である。

#### 【0075】

次に、ステップ 213 で、画素ずらしに対応させる処理を行う。この場合、上述した実施の形態と同様に 9 点に画素ずらしを行うとき、解像度(画素数)が水平、垂直方向にそれぞれ 3 倍になるため、図 24 に示すテーブルの変換式に基づいてすべての領域 1 ~ 4 のアドレスを 3 倍した値にする。

30

#### 【0076】

そして、ステップ 214 で、画素ずらし位置に対応するアドレスを付加する。この場合、欠陥画素についても、図 3 に示したように 2 / 3 画素ずつ 9 点に変位すると、これら位置のすべてが欠陥画素となるため、図 25 に示すテーブルのアドレス変換式に、図 26 に示すテーブルの画素ずらし位置 2 ~ 9 の、 $\cdot$  を代入し、これら算出された 8 つのアドレスを欠陥画素アドレスとして新たに加え、欠陥画素補正部 5 の RAM 51 に格納する。

#### 【0077】

40

このようにした一連の処理を通して、画素ずらし後の画像も幅  $X_a$ 、高さ  $Y_a$  の領域に 4 分割され、画像信号、欠陥画素アドレスとともに  $0 \sim X_a, 0 \sim Y_a$  の範囲に変換される。すなわち、1 ライン、1 フレームの幅が、それぞれ  $X_a, Y_a$  に置換される。

#### 【0078】

そして、これらアドレス変換された画像信号と欠陥画素アドレスは、順次欠陥補償回路 53 に入力されるが、この場合、欠陥補償回路 53 には、幅  $2X_a$ 、高さ  $2Y_a$  の画像信号が一度に入力されるのではなく、変換されたアドレス  $0 \sim X_a, 0 \sim Y_a$  の画像信号が順次 4 回に分けて入力される。

#### 【0079】

従って、このようにすれば、図 5 に示す欠陥補償回路 53 中のラインバッファ (H) は、

50

画像信号を分割したことで、1ライン幅を小さくできるので、少ない容量のものを使用しても同等な処理を行うことができる。つまり、本実施の形態によれば、画素ずらし後の高解像度の画像信号を分割し、分割した各画像毎に順次画像欠陥補償処理を行うことで、画素ずらし前の欠陥情報から、画素ずらし後の画素欠陥補正処理を低容量のメモリで実現することができる。

#### 【0080】

なお、この実施の形態では、2/3画素変位の9点画素ずらしに適応した例を述べたが、画素ずらしの変位量、回数の異なる画素ずらし機構を有する撮像装置に適用することも可能である。また、画像信号の分割数も、任意に変更することもできる。

#### 【0081】

10

#### (第4の実施の形態)

次に、本発明の第4実施例について説明する。

#### 【0082】

この第4の実施の形態の特徴は、撮像装置を顕微鏡に取り付け、暗電流の大きい画素を検出して補正を行うことにある。

#### 【0083】

図27は、本発明の第4の実施の形態の概略構成を示すもので、図2と同一部分には、同符号を付している。

#### 【0084】

20

この場合、本発明の撮像装置100には、顕微鏡200が接続されている。顕微鏡200は、被写体となる試料11がステージ12上に載置されている。試料11には、ステージ12の下方に配置されたハロゲンランプ等の光源13から発せられる光が照明光学系14、コンデンサレンズ15を通って照射される。

#### 【0085】

試料11を透過、散乱した光による像は、対物レンズ16によって拡大され、投影レンズ17によって撮像素子2の撮像面に投射される。

#### 【0086】

30

撮像素子2の撮像面の前面には、遮光手段としてのシャッター18が配置されている。シャッター18には、シャッタードライバ19が接続されている。このシャッタードライバ19は、CPU45から送信される信号に応じて駆動され、シャッター18を開閉させる。

#### 【0087】

撮像素子2は、圧電素子ドライバ32により駆動される圧電素子31により周期的に垂直、水平方向に各々3箇所、計9箇所に画素ずらしを行い、これら変位位置での被写体像の画像信号を出力する。

#### 【0088】

撮像素子2より出力される画像信号は、A/D変換器42でデジタル画像信号に変換され、メモリ43に入力される。また、A/D変換器42の出力信号（デジタル画像信号）は、欠陥画素検出手段としての欠陥画素検出回路20にも入力される。

#### 【0089】

40

欠陥画素検出回路20は、あらかじめ所定レベル（TH）の輝度が設定されていて、この所定レベル（TH）を超えるレベルの暗電流を検出すると、その画素位置（アドレス）をCPU45を介して欠陥画素補正部5のRAM51に格納させるようにしている。

#### 【0090】

その他は、図2と同様である。

#### 【0091】

このような構成において、いま、観察者が撮像装置100の電源をオンすると、CPU45は、シャッター18を閉じた状態で、固体撮像素子ドライバ41と圧電素子ドライバ32に信号を送信し、撮像素子2を変位させて垂直、水平方向に各々3箇所、計9箇所に画素ずらしを行い、これら変位位置での被写体像の画像信号をA/D変換器42に入力する

50

。

**【 0 0 9 2 】**

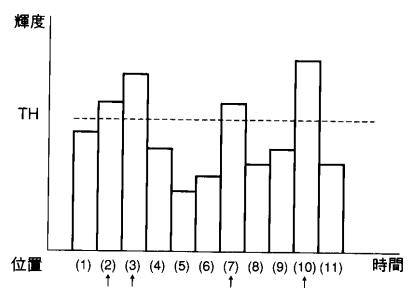

A / D 変換器 4 2 では、入力された画像信号をデジタル信号に変換したのち、図 2 8 に示すように撮像素子 2 の全画素領域の各画素位置 (1) (2) ... 毎の輝度信号として欠陥画素検出回路 2 0 に入力する。この時の A / D 変換器 4 2 の出力信号は、シャッター 1 8 が閉じ状態にあって撮像素子 2 から出力されるもので、撮像素子 2 の暗電流レベルである。

**【 0 0 9 3 】**

欠陥画素検出回路 2 0 は、図 2 8 に示すように、あらかじめ所定レベル (T H) の輝度が設定されていて、この所定レベル (T H) を超えるような輝度レベルの暗電流を検出すると、その画素位置 (アドレス) を C P U 4 5 を介して欠陥画素補正部 5 の R A M 5 1 に格納する。この場合、図 2 8 では、画素位置 (2) (3) (7) (10) ... での暗電流の輝度レベルが所定レベル (T H) を超えており、これらの画素位置 (アドレス) が C P U 4 5 を介して欠陥画素補正部 5 の R A M 5 1 に格納される。

10

**【 0 0 9 4 】**

このようにして、欠陥画素検出回路 2 0 において、撮像素子 2 の全画素領域の画像信号 (暗電流) について輝度レベルの検出が行われる。その後、C P U 4 5 は、欠陥 R O M 4 4 にあらかじめ格納された欠陥画素アドレスも R A M 5 1 に格納する。

**【 0 0 9 5 】**

また、C P U 4 5 は、シャッタードライバ 1 9 に信号を送信し、シャッター 1 8 を開ける。シャッター 1 8 を開けると、この直後から、撮像素子 2 には顕微鏡 2 0 0 からの試料 1 1 の像が投影される。

20

**【 0 0 9 6 】**

また、C P U 4 5 より固体撮像素子ドライバ 4 1 と圧電素子ドライバ 3 2 に信号を送信し、撮像素子 2 を変位させて垂直、水平方向に各々 3 個所、計 9 箇所に画素ずらしを行い、これら変位位置での画像信号を A / D 変換器 4 2 を介してデジタル化した後、メモリ 4 3 に格納する。

**【 0 0 9 7 】**

この状態では、C P U 4 5 は、欠陥画素検出回路 2 0 を作動させない。

**【 0 0 9 8 】**

欠陥アドレス検出部 5 2 では、メモリ 4 3 から出力される画像信号のアドレスと R A M 5 1 に格納されたアドレスを比較し、一致したときに検出信号を欠陥補償回路 5 3 に送信する。欠陥補償回路 5 3 は、欠陥アドレス検出部 5 2 の検出信号を受信したとき、補正処理を行った画像信号を出力し、検出信号を受信しないときは、メモリ 4 3 から入力された画像信号をそのまま出力する。ここで欠陥補償回路 5 3 における補正処理は、上述した第 1 の実施の形態と同様である。

30

**【 0 0 9 9 】**

この場合、R A M 5 1 には欠陥 R O M 4 4 にあらかじめ格納された欠陥画素だけでなく、欠陥画素検出回路 2 0 によって暗電流が所定レベルより大きいと判断された画素のアドレスも格納されている。

**【 0 1 0 0 】**

40

これにより、欠陥補償回路 5 3 での補正処理は、欠陥画素だけでなく暗ノイズの目立つ画素についても行われるようになるため、顕微鏡 2 0 0 において、蛍光観察などの暗い試料 1 1 に対して撮影を行うような場合に、画像のノイズを大幅に減少させることができる。

**【 0 1 0 1 】**

なお、本実施例においては、電源をオンした時に暗電流の大きい画素を検出したが、検出条件を可変とし、撮像中も所定の時間毎に補正対象画素を検出して R A M 5 1 に格納されたアドレスを書き換えるようにすれば、時間変化する暗電流だけでなく挨等の移動する画像ノイズに対しても補正を行うことができる。また、撮像素子 2 への遮光手段はシャッター 1 8 に限らず、光源 1 3 自身のオン / オフ制御、光学フィルターなどの挿入によっても実現できる。さらに、欠陥画素は、あらかじめ欠陥 R O M 4 4 にその位置情報を格納せず

50

に、欠陥画素検出回路 20 に欠陥画素の検出条件を与えることにより、撮像中に検出することも可能である。このとき、撮像素子 2 に固有の欠陥画素に対して欠陥 ROM 44 の中身を変更する必要がなくなり、経年変化する欠陥画素に対しても正しく補正することが可能になる。

#### 【0102】

その他、本発明は、上記実施の形態に限定されるものでなく、実施段階では、その要旨を変更しない範囲で種々変形することが可能である。

#### 【0103】

さらに、上記実施の形態には、種々の段階の発明が含まれており、開示されている複数の構成要件における適宜な組み合わせにより種々の発明が抽出できる。例えば、実施の形態に示されている全構成要件から幾つかの構成要件が削除されても、発明が解決しようとする課題の欄で述べた課題を解決でき、発明の効果の欄で述べられている効果が得られる場合には、この構成要件が削除された構成が発明として抽出できる。10

#### 【0104】

##### 【発明の効果】

以上述べたように本発明によれば、隣接画素による欠陥画素補正をより正確に行い、撮像素子の変位による誤差を小さくして画像劣化を抑えることのできる撮像装置および方法を提供できる。

##### 【図面の簡単な説明】

- 【図 1】本発明の第 1 の実施の形態の撮像装置の概略構成を示す図。20

- 【図 2】第 1 の実施の形態の撮像装置をさらに詳細に説明する概略構成を示す図。

- 【図 3】第 1 の実施の形態の画素ずらし方法による画素の変位状態を示す図。

- 【図 4】第 1 の実施の形態での画素ずらし前後の画素の色配列を表した図。

- 【図 5】第 1 の実施の形態の欠陥画素補償回路の概略構成を示す図。

- 【図 6】第 1 の実施の形態の欠陥補償回路における欠陥画素の補間を行う回路のブロック図。

- 【図 7】第 1 の実施の形態の欠陥画素の画素ずらし位置別の欠陥補正方法を説明するための図。

- 【図 8】第 1 の実施の形態の出力選択部に用意されたテーブルを示す図。

- 【図 9】第 1 の実施の形態の画素ずらし後の画素をそれぞれ R、B、G の色別に抜き出した場合の画素配置を示す図。30

- 【図 10】第 1 の実施の形態の画素ずらし後の欠陥画素の配置例を示す図。

- 【図 11】第 1 の実施の形態の比較例としての従来用いられている欠陥画素補正方法を説明するための図。

- 【図 12】本発明の第 2 の実施の形態の概略構成を示す図。

- 【図 13】第 2 の実施の形態の欠陥補償回路における欠陥画素の補正を行う回路のブロック図。

- 【図 14】第 2 の実施の形態の欠陥画素補正方法を説明するための図。

- 【図 15】第 2 の実施の形態の出力選択部に用意されたテーブルを示す図。

- 【図 16】本発明の第 3 の実施の形態の概略構成を示す図。40

- 【図 17】第 3 の実施の形態のアドレス変換部におけるアドレス変換の手順を説明するための図。

- 【図 18】第 3 の実施の形態のアドレス変換部におけるアドレス変換の手順を説明するための図。

- 【図 19】第 3 の実施の形態のアドレス変換部におけるアドレス変換の手順を説明するための図。

- 【図 20】第 3 の実施の形態のアドレス変換部におけるアドレス変換の手順を説明するためのフローチャート。

- 【図 21】第 3 の実施の形態のアドレス変換部におけるアドレス変換の手順を説明するためのフローチャート。50

【図22】第3の実施の形態の欠陥ROMに格納されたテーブル例を示す図。

【図23】第3の実施の形態の欠陥ROMに格納されたテーブル例を示す図。

【図24】第3の実施の形態の欠陥ROMに格納されたテーブル例を示す図。

【図25】第3の実施の形態の欠陥ROMに格納されたテーブル例を示す図。

【図26】第3の実施の形態の欠陥ROMに格納されたテーブル例を示す図。

【図27】本発明の第4の実施の形態の概略構成を示す図。

【図28】第4の実施の形態の欠陥画素検出回路に設定された所定レベル(TH)と画像信号の輝度レベルの関係を説明する図。

【符号の説明】

|                           |    |

|---------------------------|----|

| 1 ... レンズ                 | 10 |

| 2 ... 撮像素子                |    |

| 3 ... 変位手段                |    |

| 3 1 ... 圧電素子              |    |

| 3 2 ... 圧電素子ドライバ          |    |

| 4 ... 画像処理部               |    |

| 4 1 ... 固体撮像素子ドライバ        |    |

| 4 2 ... A / D 変換器         |    |

| 4 3 ... メモリ               |    |

| 4 4 ... 欠陥ROM             |    |

| 4 5 ... CPU               | 20 |

| 5 ... 欠陥画素補正部             |    |

| 6 ... 色フィルタ               |    |

| 1 1 ... 試料                |    |

| 1 2 ... ステージ              |    |

| 1 3 ... 光源                |    |

| 1 4 ... 照明光学系             |    |

| 1 5 ... コンデンサレンズ          |    |

| 1 6 ... 対物レンズ             |    |

| 1 7 ... 投影レンズ             |    |

| 1 8 ... シャッター             | 30 |

| 1 9 ... シャッタードライバ         |    |

| 2 0 ... 欠陥画素検出回路          |    |

| 5 1 ... RAM               |    |

| 5 2 ... 欠陥アドレス検出部         |    |

| 5 3 ... 欠陥補償回路            |    |

| 5 3 1 ... 出力選択部           |    |

| 5 3 2、5 3 4、5 3 6 ... 加算器 |    |

| 5 3 3、5 3 5、5 3 7 ... 乗算器 |    |

| 5 4 ... アドレス変換部           |    |

| 1 0 0 ... 撮像装置            | 40 |

| 2 0 0 ... 顕微鏡             |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

| 補正信号 | 演算                          | 画素づらし位置         |

|------|-----------------------------|-----------------|

| A    | $(C_5 + C_3 + C_7 + E_5)/2$ | (1),(9),(3),(7) |

| B    | $C_5 + C_3 + C_7 + E_5$     | (2),(4),(6),(8) |

| C    | $(C_1 + C_9)/2$             | (5)             |

【図9】

(a) 赤(R)の場合

(b) 青(B)の場合

(c) 緑(Gr,Gb)の場合

【図10】

【図11】

【図12】

【図14】

【図13】

【図15】

| 補正信号 | 演算                | 画素ずらし位置    | 色    |

|------|-------------------|------------|------|

| A    | $(C5+C3+C7+E5)/2$ | ①, ⑨, ③, ⑦ | R, B |

| B    | $C5+C3+C7+E5$     | ②, ④, ⑥, ⑧ | R, B |

| C    | $(C1+C9)/2$       | ⑤          | R, B |

| D    | $(B4+B6+D4+D6)/4$ | —          | G    |

【図16】

【図17】

【図18】

【図19】

【図20】

【図22】

| 領域 | 条件                                   |

|----|--------------------------------------|

| 1  | $x : Xa \text{未満}, y : Ya \text{未満}$ |

| 2  | $x : Xa \text{未満}, y : Ya \text{以上}$ |

| 3  | $x : Xa \text{以上}, y : Ya \text{未満}$ |

| 4  | $x : Xa \text{以上}, y : Ya \text{以上}$ |

【図21】

【図23】

| 領域 | 変換            |               |

|----|---------------|---------------|

| 1  | $x' = x$      | $y' = y$      |

| 2  | $x' = x$      | $y' = y - Ya$ |

| 3  | $x' = x - Xa$ | $y' = y$      |

| 4  | $x' = x - Xa$ | $y' = y - Ya$ |

【図24】

| 領域 | 変換式(画素ずらし基準位置)           |

|----|--------------------------|

| 1  | $(3x, 3y)$               |

| 2  | $(3x, 3(y - Ya))$        |

| 3  | $(3(x - Xa), 3y)$        |

| 4  | $(3(x - Xa), 3(y - Ya))$ |

【図25】

| 領域 | アドレス変換式                                    |

|----|--------------------------------------------|

| 1  | $(3x + \Delta, 3y + \Phi)$                 |

| 2  | $(3x + \Delta, 3(y - Ya) + \Phi)$          |

| 3  | $(3x(x - Xa) + \Delta, 3y + \Phi)$         |

| 4  | $(3x(x - Xa) + \Delta, 3y(y - Ya) + \Phi)$ |

【図26】

【図27】

【図28】

| 画素ずらし位置 | $\Delta$ | $\Phi$ |

|---------|----------|--------|

| 1       | 0        | 0      |

| 2       | 2        | 0      |

| 3       | 4        | 0      |

| 4       | 0        | 2      |

| 5       | 2        | 2      |

| 6       | 4        | 2      |

| 7       | 0        | 4      |

| 8       | 2        | 4      |

| 9       | 4        | 4      |

---

フロントページの続き

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100101812

弁理士 勝村 紘

(74)代理人 100092196

弁理士 橋本 良郎

(74)代理人 100100952

弁理士 風間 鉄也

(74)代理人 100070437

弁理士 河井 将次

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(74)代理人 100127144

弁理士 市原 卓三

(74)代理人 100141933

弁理士 山下 元

(72)発明者 岸田 浩徳

東京都渋谷区幡ヶ谷2丁目43番2号 オリンパス光学工業株式会社内

(72)発明者 桜井 順三

東京都渋谷区幡ヶ谷2丁目43番2号 オリンパス光学工業株式会社内

審査官 松田 岳士

(56)参考文献 特開平07-322151(JP,A)

特開平03-236689(JP,A)

特開平05-236358(JP,A)

特開平11-220661(JP,A)

特開平11-262025(JP,A)

特開平11-018097(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 9/04 - 9/11

(20)

JP 4276817 B2 2009.6.10

H04N 5/30 - 5/335