(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-142138

(P2007-142138A)

(43) 公開日 平成19年6月7日(2007.6.7)

|                          |              |             |

|--------------------------|--------------|-------------|

| (51) Int.CI.             | F 1          | テーマコード (参考) |

| HO 1 L 23/52 (2006.01)   | HO 1 L 21/88 | T 4 M 1 O 4 |

| HO 1 L 21/3205 (2006.01) | HO 1 L 29/50 | M 5 F O 3 3 |

| HO 1 L 29/417 (2006.01)  |              |             |

審査請求 未請求 請求項の数 8 O L (全 12 頁)

|           |                              |          |                                                                                                                     |

|-----------|------------------------------|----------|---------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2005-333656 (P2005-333656) | (71) 出願人 | 000006013<br>三菱電機株式会社<br>東京都千代田区丸の内二丁目7番3号                                                                          |

| (22) 出願日  | 平成17年11月18日 (2005.11.18)     | (74) 代理人 | 100101454<br>弁理士 山田 卓二                                                                                              |

|           |                              | (74) 代理人 | 100112911<br>弁理士 中野 晴夫                                                                                              |

|           |                              | (72) 発明者 | 橋崎 敦司<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内                                                                                |

|           |                              |          | F ターム (参考) 4M104 AA01 BB02 BB14 CC01 CC05<br>DD34 DD37 DD52 DD53 EE05<br>EE18 FF07 FF13 GG09 GG10<br>GG14 GG18 HH20 |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】 ダイレクトリードボンディング方式の半導体装置において、金属膜を形成する位置がゲート配線側にずれた場合のゲート配線の破損を防止する。

【解決手段】 ダイレクトリードボンディング方式の半導体装置が、半導体基板と、半導体基板の表面に設けられた表面電極と、半導体基板の表面に表面電極に沿って設けられたゲート配線と、表面電極の上に設けられた金属膜と、金属膜の上に取り付けられたリード端子とを含む。ゲート配線はポリイミド膜に覆われ、金属膜はポリイミド膜の上まで延在する。

【選択図】図 7

**【特許請求の範囲】****【請求項 1】**

ダイレクトリードボンディング方式の半導体装置であって、

半導体基板と、

該半導体基板の表面に設けられた表面電極と、

該半導体基板の表面に該表面電極に沿って設けられたゲート配線と、

該表面電極の上に設けられた金属膜と、

該金属膜の上に取り付けられたリード端子とを含み、

該ゲート配線がポリイミド膜に覆われ、該金属膜が該ポリイミド膜の上まで延在したこ

とを特徴とする半導体装置。

10

**【請求項 2】**

ダイレクトリードボンディング方式の半導体装置であって、

半導体基板と、

該半導体基板の表面に設けられた表面電極と、

該半導体基板の表面に該表面電極に沿って設けられたゲート配線と、

該表面電極の上に設けられた金属膜と、

該金属膜の上に取り付けられたリード端子とを含み、

該ゲート配線がポリイミド膜に覆われたことを特徴とする半導体装置。

**【請求項 3】**

上記半導体基板の表面にオプション素子が設けられ、該オプション素子も上記ポリイミドで覆われたことを特徴とする請求項 1 または 2 に記載の半導体装置。

20

**【請求項 4】**

上記ゲート電極と上記ポリイミド膜との間に、オーバーコート膜が設けられたことを特徴とする請求項 1 または 2 に記載の半導体装置。

**【請求項 5】**

上記ポリイミド膜の膜厚が、略 10 μm から 略 50 μm であることを特徴とする請求項 1 または 2 に記載の半導体装置。

30

**【請求項 6】**

上記半導体基板の表面に上記ゲート配線に接続されたゲート電極が設けられ、該ゲート電極上に設けられた金属膜にリード端子が取り付けられたことを特徴とする請求項 1 または 2 に記載の半導体装置。

**【請求項 7】**

上記金属膜が、蒸着法、スパッタ法、およびメッキ法から選択される一の方法で形成されたことを特徴とする請求項 1 または 2 に記載の半導体装置。

**【請求項 8】**

上記半導体基板の裏面に裏面電極が設けられ、上記表面電極と該裏面電極との間を流れる電流が、上記ゲート配線で制御されることを特徴とする請求項 1 または 2 に記載の半導体装置。

40

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置に関し、特に、ダイレクトリードボンディング方式の半導体装置に関する。

**【背景技術】****【0002】**

近年、電力用半導体装置であるパワーMOSFET (Metal Oxide Semiconductor Field Effect Transistor) やIGBT (Insulated Gate Bipolar Transistor) では、電力損失を低減するために、エミッタ電極とリード端子とをボンディングワイヤを介して接続する代わりに、両電極を直接接続するダイレクトリードボンディング方式が用いられる。

50

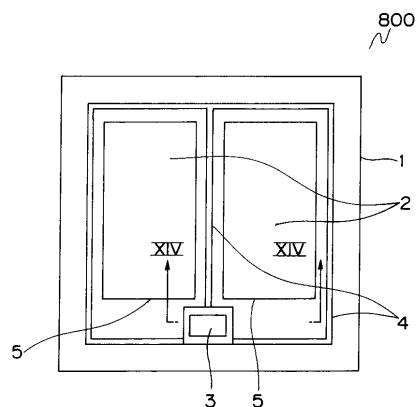

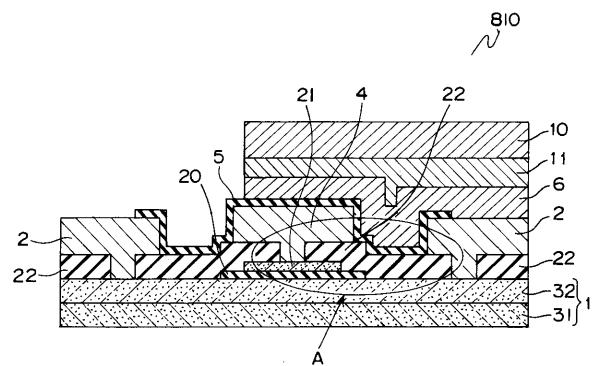

## 【0003】

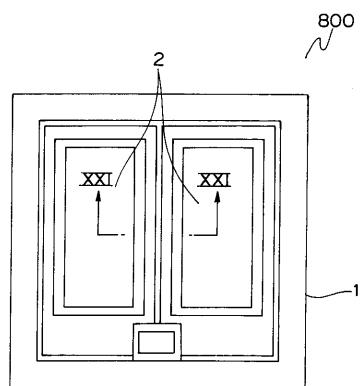

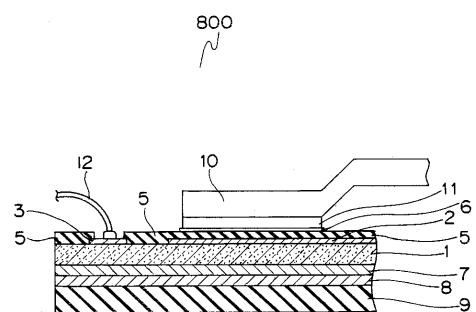

図19は、全体が800で表される、従来構造の半導体装置の上面図であり、図20は、図19をXIV-XIV方向に見た場合の断面図である。図20において、理解を容易にするために、図の右半分においてポリイミド膜13は省略してある。

図19、20に示すように、半導体装置800はIGBT等の半導体チップ1を含む。半導体チップ1の表面には、エミッタ電極2と、ゲート電極3に接続されたゲート配線4とが設けられている。エミッタ電極2とゲート電極3の周囲、および半導体チップ1の表面を覆うように、オーバーコート膜5が設けられている。また、エミッタ電極2の上には金属膜6が設けられ、その上に半田層11を介してリード端子10が接続されている（図19には、金属膜6、リード端子10、半田層11は示さず）。

10

## 【0004】

一方、半導体チップ1の裏面にはコレクタ電極7が設けられている。半導体チップ1は、表面に回路パターン（図示せず）が形成された基板9の上に、半田層8を介して接続されている。

## 【0005】

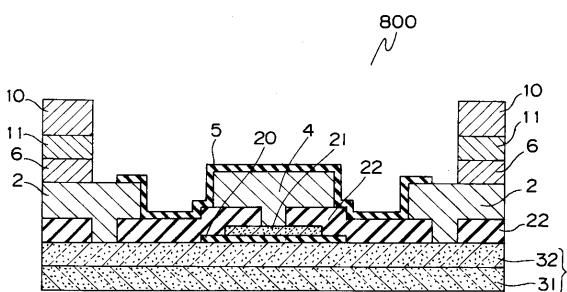

図21は、金属膜6を形成した状態の、従来の半導体装置800の上面図であり、図22は、図21をXXI-XXI方向に見た場合の断面図である（図21には、リード端子10、半田層11は示さず）。図19、20と同一符号は、同一又は相当箇所を示す。図21、22は、エミッタ電極2に対して、金属膜6、リード端子10および半田層11の位置合わせが正確に行われた場合である。

20

なお、図22に示すように、詳しく見れば、半導体基板1の上には、下敷酸化膜20を介してポリシリコン配線21が設けられ、その上にゲート配線4が設けられている。また、エミッタ電極2とゲート配線4との間には層間絶縁膜22が設けられている。

## 【特許文献1】特開平4-133474号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0006】

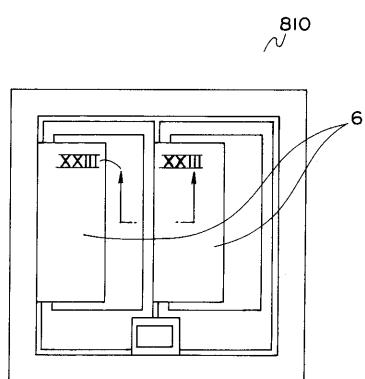

半導体装置800の製造工程では、エミッタ電極2に対して、金属膜6を形成する位置がずれる場合がある。図23は、エミッタ電極2に対して、金属膜6の位置が左側にずれた場合の上面図であり、図24は、図23をXXII-XXII方向に見た場合の断面図（半田層11、リード端子10を除く）である。図23、24中、図19、20と同一符号は、同一又は相当箇所を示す。

30

## 【0007】

図24の半導体装置810に示すように、金属膜6を形成する位置がゲート配線4の上にずれた場合、金属膜6の上に半田層11でリード端子10を接合する工程でゲート配線4に応力や熱が加わり、ゲート電極4の破損が発生していた。また、破損に至らない場合でも、後発的な破損の原因となり、信頼性低下の原因となっていた。

## 【0008】

そこで、本発明は、ダイレクトリードボンディング方式の半導体装置において、金属膜を形成する位置がゲート配線側にずれた場合の、ゲート配線の破損を防止した半導体装置の提供を目的とする。

40

## 【課題を解決するための手段】

## 【0009】

本発明は、ダイレクトリードボンディング方式の半導体装置であって、半導体基板と、半導体基板の表面に設けられた表面電極と、半導体基板の表面に表面電極に沿って設けられたゲート配線と、表面電極の上に設けられた金属膜と、金属膜の上に取り付けられたリード端子とを含み、ゲート配線がポリイミド膜に覆われ、金属膜がポリイミド膜の上まで延在したことを特徴とする。

## 【発明の効果】

## 【0010】

50

以上のように、本発明にかかる半導体装置では、ダイレクトリードボンディング方式でリード電極を取り付ける際のゲート配線の損傷を防止し、信頼性の高い半導体装置の提供が可能となる。

#### 【発明を実施するための最良の形態】

##### 【0011】

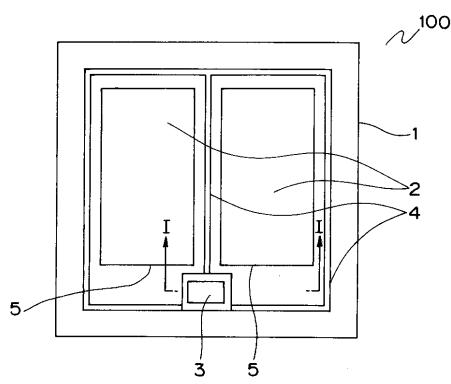

###### 実施の形態1.

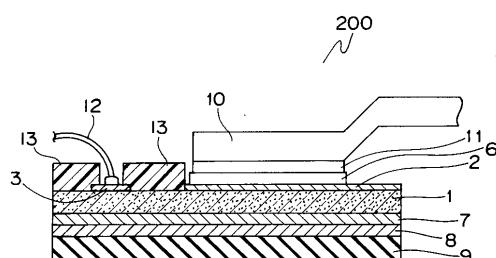

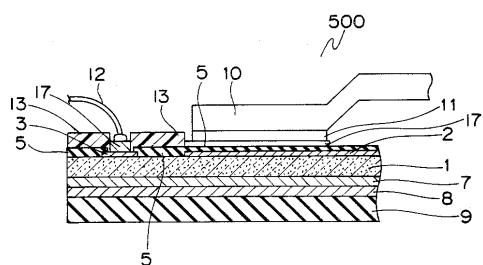

図1は、全体が100で表される、本実施の形態1にかかるダイレクトリードボンディング方式を用いた半導体装置の上面図であり、ポリイミド膜形成前の状態を示す。図2は、図1をI-I方向に見た場合の断面図であり、理解を容易にするために、図の右半分においてポリイミド膜13は省略してある。

10

##### 【0012】

半導体装置100はIGBT等の半導体チップ1を含む。半導体チップ1の表面には、エミッタ電極(表面電極)2と、ゲート電極3が設けられている。これらの電極は、例えばアルミニウムから形成される。ゲート電極3には、例えばアルミニウムからなるゲート配線4が接続されている。ゲート電極3の上には、例えばアルミニウムからなるボンディングワイヤ12が接合されている。

##### 【0013】

エミッタ電極2とゲート電極3の周囲、および半導体チップ1の表面を覆うように、例えば酸化シリコンや窒化シリコンからなるオーバーコート膜5が設けられている。

エミッタ電極2の上には、例えばTi/Ni/Auの3層構造からなる金属膜6が設けられている。エミッタ電極2上に選択的に金属膜6を形成するためには、半導体チップ1を含むウエハの表面にメタルマスクなどを貼りあわせて金属を蒸着する方法が用いられる。金属膜6のうち、Tiはエミッタ電極2とのオーム特性を向上させるため、Niは半田層11との接続剤として、AuはNiの酸化防止剤としての役割を果たす。

なお、金属膜6として、Ti/Ni/Auの3層構造以外に、Al/Mo/Ni/AuやAl/Ti/Ni/Auなどの積層構造を用いてもかまわない。

##### 【0014】

なお、金属層6の形成には、スパッタ法を用いることもできる(以下の実施の形態においても同じ)。

##### 【0015】

金属層6の上には、Ag-Sn等の半田層11を介して板状のリード端子10が接続されている。リード端子10の材料には、例えば銅が用いられる。リード端子11は、半導体装置100の外部との接続端子となる。

30

##### 【0016】

一方、半導体チップ1の裏面には、例えばAl/Mo/Ni/Auの4層膜からなるコレクタ電極(裏面電極)7が設けられている。半導体チップ1は、表面に回路パターン(図示せず)が形成された基板9の上に、Ag-Sn等の半田層8を介して接続されている。基板9は、例えばアルミナから形成される。

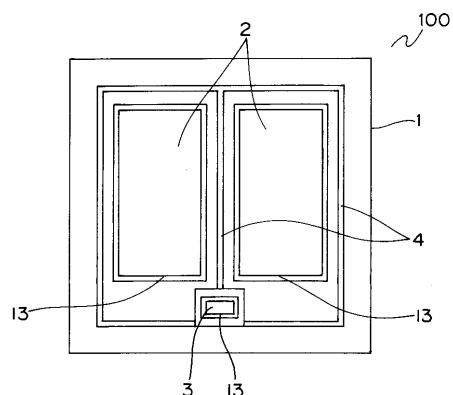

##### 【0017】

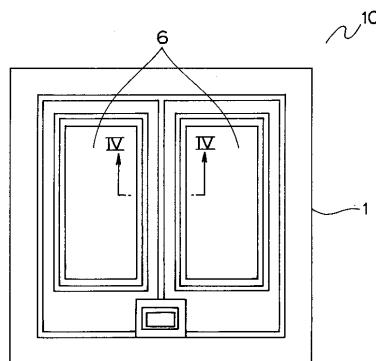

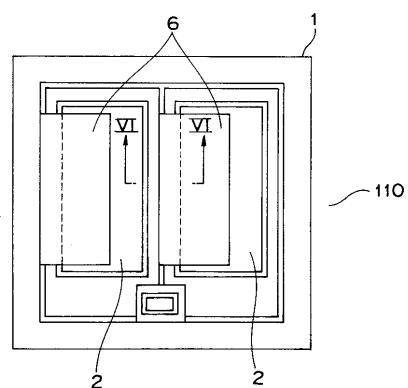

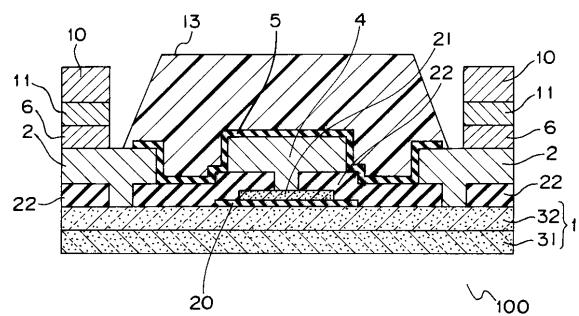

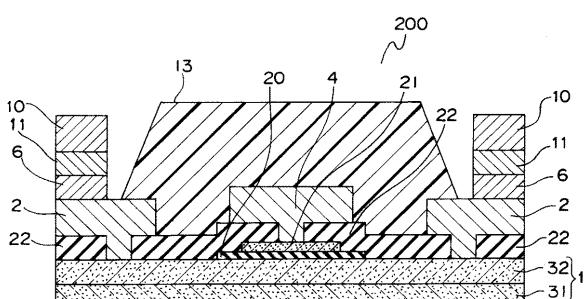

図3は、ポリイミド膜13を形成した後の上面図であり、図4は、更に、金属層6を形成した後の上面図である。また、図5は、図4をIV-IV方向に見た場合の断面図であり、金属層6の上には、半田11を介してリード端子10が取り付けられている。

40

##### 【0018】

なお、図5に示すように、詳しく見れば、半導体チップ1の上に下敷酸化膜20を介してポリシリコン配線21が設けられ、その上にゲート配線4が設けられている。また、エミッタ電極2とゲート配線4との間には、例えば酸化シリコンからなる層間絶縁膜22が設けられている。また、半導体チップ1は、n型エピタキシャル層31とp型ウエル領域32からなる。

##### 【0019】

半導体装置100では、ゲート配線4を覆うようにオーバーコート膜5が設けられ、更

50

にその上にポリイミド膜13が設けている。ポリイミド膜13の膜厚は、例えば、略10μm～略50μm程度が好ましい。

#### 【0020】

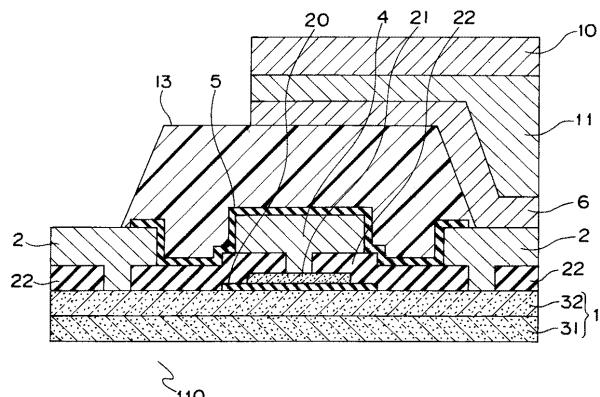

図3～5は、エミッタ電極2に対して、金属層6の位置合わせが正確に行われた場合であるが、一方、図6、7は、エミッタ電極2に対して金属層6がゲート配線4側（図6、7では左側）にずれて形成された場合を示す。このように、位置合わせが多少ずれた場合でも、素子性能に影響がなければ良品として使用可能である。

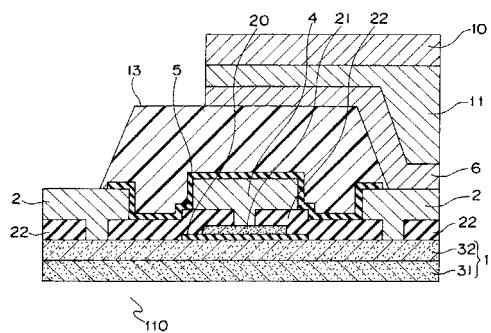

#### 【0021】

図6は、全体が110で表される、本実施の形態にかかる他の半導体装置の上面図であり、図7は、図6をV I - V I方向に見た場合の断面図である。図6、7中、図1～5と同一符号は、同一又は相当箇所を示す。

#### 【0022】

半導体装置110では、ゲート配線4、エミッタ電極2が形成された後に、オーバーコート層5が形成され、続いてポリイミド膜13が形成される。オーバーコート層5、ポリイミド膜13は、通常のフォトリソグラフィ法、エッチング法を用いて形成される。

更に、ポリイミド膜13の形成後にメタルマスクを用いて金属層6が蒸着されるが、半導体装置110では、メタルマスクの位置がゲート配線4側にずれ、金属層6がポリイミド膜13の上まで延びて形成されている。この結果、金属層6の上に形成される半田層11、リード電極10が、ともにポリイミド膜13に重なった構成となる。

#### 【0023】

半導体装置110では、ポリイミド膜13を形成することにより、ゲート配線4近傍の段差を無くしている。このため、エミッタ電極2の外部に延びた金属膜6がゲート配線4の近傍に形成された場合でも、半田層11でリード電極10を接合する際に段差部で発生する熱応力を低減でき、ゲート配線4の損傷を防止できる。

#### 【0024】

また、ポリイミド膜13が緩衝材となってかかる熱応力を吸収することによっても、ゲート配線4の損傷を防止できる。

#### 【0025】

なお、図7では、ゲート電極4の真上に金属膜6、半田層11、およびリード端子10が延在しているが、位置合わせのずれが小さく、ゲート電極4の真上まで金属膜6等が延びない場合であっても、ポリイミド膜13を用いることにより、ゲート配線4の損傷を防止できる。

#### 【0026】

実施の形態2.

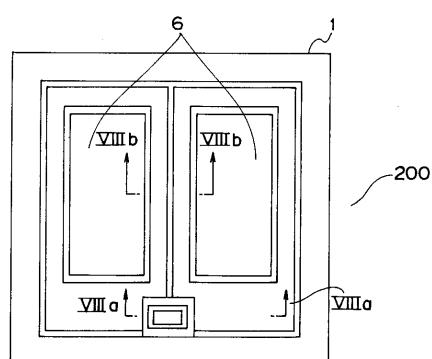

図8は、全体が200で表される、本実施の形態2にかかる半導体装置の上面図であり、図9は、図8をV I I I a - V I I I a方向に見た場合の断面図である。また、図10は、図8をV I I I b - V I I I b方向に見た場合の断面図である。図9の右半分において、ポリイミド膜13は省略してある。図8～10において、図1～5と同一符号は、同一又は想到箇所を示す。

#### 【0027】

本実施の形態2にかかる半導体装置200では、上述の半導体装置100に比較してオーバーコート層5の無い構造となっている。他の構成は、半導体装置100と同じである。

#### 【0028】

このように、半導体装置200ではポリイミド膜13が保護膜としての機能を有するため、オーバーコート層5は設けないこととしている。これにより、オーバーコート層5の形成工程が省略でき、製造工程の簡素化、製造コストの低減が可能となる。

#### 【0029】

実施の形態3.

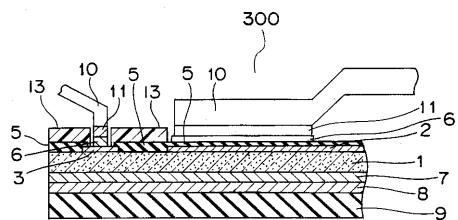

図11は、全体が300で表される、本実施の形態3にかかる半導体装置の断面図であ

10

20

30

40

50

る。図11中、図2と同一符号は、同一又は相当箇所を示す。

【0030】

半導体装置100が、ゲート電極3に対して、ボンディングワイヤ12を接続する構造であるのに対し、半導体装置300は、ゲート電極3の上にも金属層6が設けられ、その上に半田層11を介してリード端子10が接続された構造となっている。

【0031】

金属層6は、エミッタ電極2の上の金属層6と同じ工程で、例えばメタルマスクを用いた蒸着法で形成される。半田層11、リード端子10にも、エミッタ電極2と同じくAg-Sn半田、銅リードがそれぞれ用いられる。

【0032】

このように、ゲート電極3との接続にもリードボンディング方式を用いることにより、ゲート電極3への入力部における抵抗を小さくできる。

【0033】

なお、本実施の形態3にかかるリードボンディング方式のゲート配線は、上述の半導体装置100、200のいずれにも適用可能である。

も同様の効果示す。

【0034】

実施の形態4.

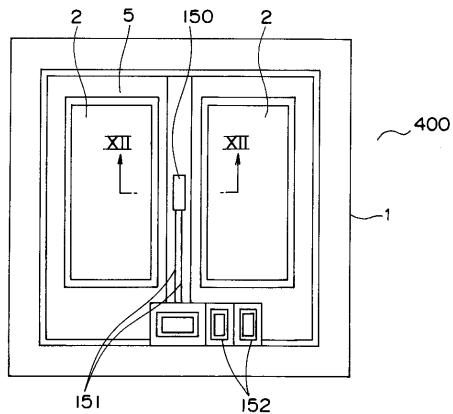

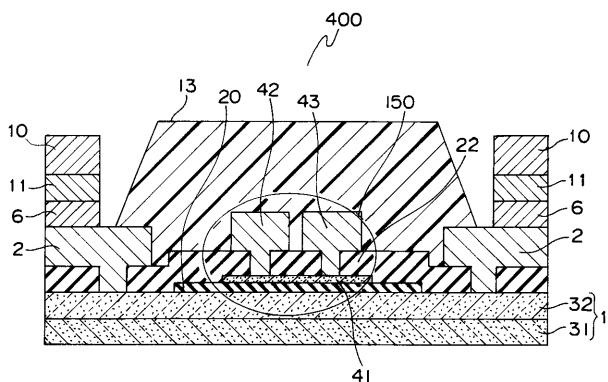

図12は、全体が400で表される、本実施の形態4にかかる半導体装置の上面図であり、図13は、図12をXII-XII方向に見た場合の断面図である。図12、13中、図1、2と同一符号は、同一又は相当箇所を示す。

【0035】

本実施の形態4は、ポリイミド膜13を、半導体装置のゲート配線以外のオプション素子にも適用したものであり、半導体装置400は、半導体装置100のゲート配線(図示せず)に加えて、オプション素子として温度センサ素子150を有する。

【0036】

図12に示すように、半導体装置400は、エミッタ電極2に挟まれた位置に温度センサ部150を有する。図13に示すように、温度センサ素子150は、多結晶シリコンからなるダイオード41と、ダイオード41のカソードに接続されたカソード電極42、およびアノードに接続されたアノード電極43からなる。

【0037】

カソード電極42、アノード電極43は、配線151を介して電極部152に接続されている。これにより、温度変化に伴うダイオード41の抵抗値の変化を電極部152から読み出して温度センサ素子150の温度を検出する。

【0038】

図13に示すように、本実施の形態4にかかる半導体装置400では、温度センサ素子150を覆うようにポリイミド膜13が形成されている。ポリイミド膜13の膜厚は、10μm~50μm程度である。

【0039】

この結果、実施の形態1の図7に示した場合と同様に、金属層6がエミッタ電極2の上から温度センサ素子150方向にずれて形成された場合でも、ポリイミド膜13が保護膜、緩衝材として機能し、半田層11でリード電極10を接合する際の、温度センサ素子150の破損を防止できる。

【0040】

なお、オプション素子には、温度センサ素子150以外に、電流センサ素子等が含まれる。

【0041】

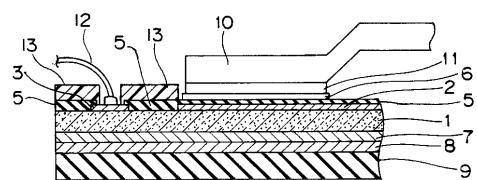

実施の形態5.

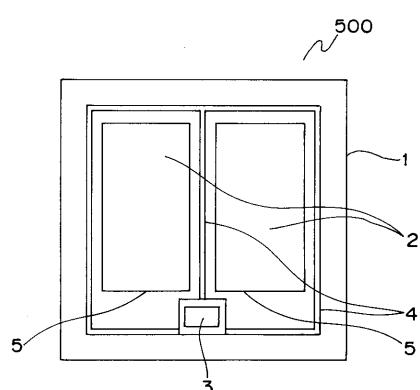

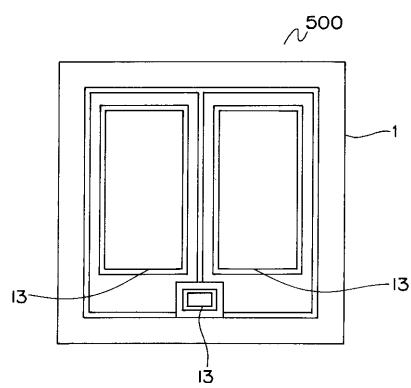

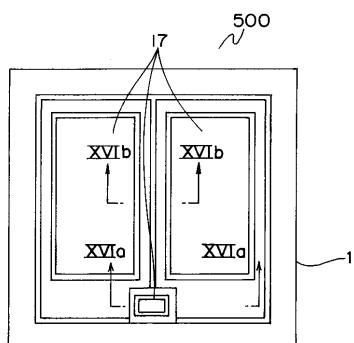

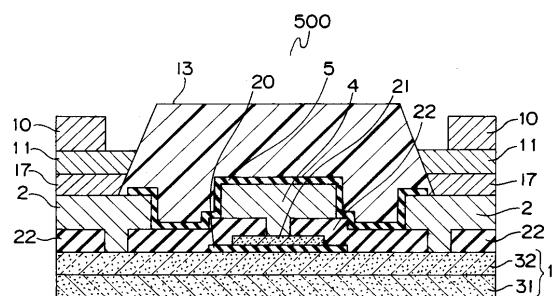

図14~16は、全体が500で表される、本実施の形態にかかる半導体装置の上面図であり、図17、18は、それぞれ、図16をXVII-XVII方向、XVII-XV

10

20

30

40

50

I b 方向に見た場合の断面図である。図 14 ~ 18において、図 1、2 と同一符号は、同一又は相当箇所を示す。

#### 【0042】

図 14 ~ 16 に示すように、半導体装置 500 では、エミッタ電極 2 を形成した(図 14)後に、エミッタ電極 2、ゲート電極 3 の中央部を除いた部分をポリイミド膜 13 で覆う(図 15)。ポリイミド膜 13 の形成には、通常のフォトリソグラフィ法等が用いられる。続いて、メッキ法を用いて、ポリイミド膜 13 に覆われていないエミッタ電極 2 の表面に金属膜 17 を形成する(図 16)。

#### 【0043】

このように、金属膜 17 をメッキ法で形成することにより、ポリイミド膜 13 に覆われずに露出したエミッタ電極 2 の表面に選択的に金属膜 17 を形成することができる。この結果、金属膜 17 を形成する際に、ウエハとメタルマスクとの位置合わせが不要となるとともに、マスク合わせのズレも発生しない。また、エミッタ電極 2 とゲート電極 3 の上に、同時に金属膜が形成できる。

#### 【0044】

なお、図 18 に示すように、本実施の形態にかかる半導体装置 500 では、金属膜 17 がメッキ法で形成されるため、金属膜 17、半田層 11 は、ポリイミド膜 13 の側壁に接して形成される。この場合も、ポリイミド膜 13 が緩衝材として機能するため、ゲート配線 4 の損傷を防止できる。

#### 【0045】

以上のように、実施の形態 1 ~ 5 では、半導体チップとして IGBT を用いる場合について説明したが、パワー MOSFET を用いる場合にも適用できる。横型のパワー MOSFET に適用する場合は、ゲート配線を挟む電極がソース / ドレイン電極となる。

また、本発明は、その他のパワー半導体チップであるダイオード、CSTBT(三菱電機製 IGBT)などを用いる場合にも適用できる。

更に、パワー半導体チップ以外の、HVIC(High Voltage IC)や LSI などの集積回路にも同様に適用することができる。

#### 【図面の簡単な説明】

#### 【0046】

【図 1】本発明の実施の形態 1 にかかる半導体装置の上面図である。

【図 2】本発明の実施の形態 1 にかかる半導体装置の断面図である。

【図 3】本発明の実施の形態 1 にかかる半導体装置の上面図である。

【図 4】本発明の実施の形態 1 にかかる半導体装置の上面図である。

【図 5】本発明の実施の形態 1 にかかる半導体装置の断面図である。

【図 6】本発明の実施の形態 1 にかかる他の半導体装置の上面図である。

【図 7】本発明の実施の形態 1 にかかる他の半導体装置の断面図である。

【図 8】本発明の実施の形態 2 にかかる半導体装置の上面図である。

【図 9】本発明の実施の形態 2 にかかる半導体装置の断面図である。

【図 10】本発明の実施の形態 2 にかかる半導体装置の断面図である。

【図 11】本発明の実施の形態 3 にかかる半導体装置の断面図である。

【図 12】本発明の実施の形態 4 にかかる半導体装置の上面図である。

【図 13】本発明の実施の形態 4 にかかる半導体装置の断面図である。

【図 14】本発明の実施の形態 5 にかかる半導体装置の上面図である。

【図 15】本発明の実施の形態 5 にかかる半導体装置の上面図である。

【図 16】本発明の実施の形態 5 にかかる半導体装置の上面図である。

【図 17】本発明の実施の形態 5 にかかる半導体装置の断面図である。

【図 18】本発明の実施の形態 5 にかかる半導体装置の断面図である。

【図 19】従来の半導体装置の上面図である。

【図 20】従来の半導体装置の断面図である。

【図 21】従来の半導体装置の上面図である。

10

20

30

40

50

【図22】従来の半導体装置の断面図である。

【図23】従来の半導体装置の上面図である。

【図24】従来の半導体装置の断面図である。

【符号の説明】

【0047】

1 半導体チップ、2 エミッタ電極、3 ゲート電極、4 ゲート配線、5 オーバーコート膜、6 金属膜、7 コレクタ電極、8 はんだ層、9 基板、10 リード端子、11 はんだ層、12 ボンディングワイヤ、13 ポリイミド膜、100 半導体装置。

【図1】

【図3】

【図2】

【図4】

【図6】

【図5】

【図7】

【図9】

【図8】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図17】

【図16】

【図18】

【図19】

【図21】

【図20】

【図22】

【図23】

【図24】

---

フロントページの続き

F ターム(参考) 5F033 HH07 HH08 HH13 HH18 HH20 KK07 KK08 KK13 KK20 MM08

PP15 PP19 PP27 PP28 RR04 RR06 RR22 VV07 XX19