(19) 日本国特許庁(JP)

(12) 特 許 公 報(B2)

(11) 特許番号

特許第5010239号

(P5010239)

(45) 発行日 平成24年8月29日(2012.8.29)

(24) 登録日 平成24年6月8日(2012.6.8)

(51) Int.Cl.

*H03F* 3/68 (2006.01)

*H03F* 3/70 (2006.01)

F 1

HO3F 3/68

HO3F 3/70

B

## 譜求項の数 6 外国語出願 (全 22 頁)

|              |                               |           |                                                                    |

|--------------|-------------------------------|-----------|--------------------------------------------------------------------|

| (21) 出願番号    | 特願2006-299309 (P2006-299309)  | (73) 特許権者 | 502188642<br>マーベル ワールド トレード リミテッド                                  |

| (22) 出願日     | 平成18年11月2日 (2006.11.2)        |           |                                                                    |

| (65) 公開番号    | 特開2007-129720 (P2007-129720A) |           | バルバドス国 ビービー14027, セントマイケル、ブリトンズ ヒル、ガンサイ                            |

| (43) 公開日     | 平成19年5月24日 (2007.5.24)        |           | トロード、エル ホライズン                                                      |

| 審査請求日        | 平成21年10月29日 (2009.10.29)      | (74) 代理人  | 100094318<br>弁理士 山田 行一                                             |

| (31) 優先権主張番号 | 60/799282                     | (74) 代理人  | 100123995<br>弁理士 野田 雅一                                             |

| (32) 優先日     | 平成18年5月10日 (2006.5.10)        | (72) 発明者  | セハット スタージャ<br>アメリカ合衆国, カリフォルニア州, ロス<br>アルトス ヒルズ, エレナ ロード 2<br>7330 |

| (33) 優先権主張国  | 米国(US)                        |           |                                                                    |

| (31) 優先権主張番号 | 60/820878                     |           |                                                                    |

| (32) 優先日     | 平成18年7月31日 (2006.7.31)        |           |                                                                    |

| (33) 優先権主張国  | 米国(US)                        |           |                                                                    |

| (31) 優先権主張番号 | 11/503436                     |           |                                                                    |

| (32) 優先日     | 平成18年8月11日 (2006.8.11)        |           |                                                                    |

| (33) 優先権主張国  | 米国(US)                        |           |                                                                    |

最終頁に続く

(54) 【発明の名称】補償付き増幅器

(57) 【特許請求の範囲】

【請求項1】

( i ) 入力信号を受けるように構成された入力及び ( i i ) 電圧源からの供給電圧を受けるように構成された出力を有する第 1 の増幅器と、

前記第1の増幅器の前記出力に接続する入力を有する第2の増幅器と、

第1端及び第2端を有する第1のキャパシタであって、該第1のキャパシタの該第1端は前記第1の増幅器の前記入力に接続する、該第1のキャパシタと、

第1端及び第2端を有する第2のキャパシタであって、該第2のキャパシタの該第1端は前記第1の増幅器の前記出力に接続する、該第2のキャパシタと、

第1端及び第2端を有する抵抗であって、該抵抗の該第1端は第1の電圧源に接続されており、該抵抗の該第2端は前記第2のキャパシタの前記第2端に接続されている、該抵抗と、

制御端子、前記抵抗の前記第2端及び前記第2のキャパシタの前記第2端に接続する第1の端子、並びに、前記第1のキャパシタの前記第2端に接続する第2の端子を有する第1のトランジスタと、

入力及び出力を有する電流源であって、該電流源の該入力は前記第1のキャパシタの前記第2端及び前記第1のトランジスタの前記第2の端子に接続されており、該電流源の該出力は電圧基準に接続されている、該電流源と、

を備え、

前記第1のトランジスタは、前記第1のキャパシタと前記第1の増幅器の出力との間に

接続されている、増幅器システム。

【請求項 2】

前記第1の増幅器の前記出力と第2の電圧源との間に接続された別の電流源を更に備える、請求項1に記載の増幅器システム。

【請求項 3】

前記第1及び第2の増幅器が、演算トランスコンダクタンス増幅器を含む、請求項1に記載の増幅器システム。

【請求項 4】

前記第1のキャパシタの前記第1端は、前記第1の増幅器の前記入力に直接接続されている、請求項1に記載の増幅器システム。 10

【請求項 5】

前記第1のキャパシタは、前記第1の増幅器の前記入力と前記電圧基準との間に接続されている、請求項1に記載の増幅器システム。

【請求項 6】

前記第1の電圧源の電圧が前記第2の電圧源の電圧と異なる、請求項2に記載の増幅器システム。

【発明の詳細な説明】

【関連出願の相互参照】

【0001】

[0001]本願は、2006年7月31日に出願された米国仮出願第60/820,878号及び2006年5月10日に出願された米国仮出願第60/799,282号の利益を主張するものであり、2005年11月2日に出願された米国特許出願第11/264,921号の一部継続出願である。上記出願の開示内容は、その全体を参照することによって本明細書に組み込む。 20

【発明の分野】

【0002】

[0002]本発明は、増幅器に関するものであり、特に、補償付き増幅器に関するものである。

【発明の背景】

【0003】

[0003]増幅器は、1段以上のステージを含むことがある。各ステージは利得を提供する増幅器を含むことがある。周波数が増加するにつれて、増幅器によって提供される利得は低下し、このことが増幅器の帯域幅を制限する。電子計算デバイスの動作周波数が増加するにつれて、高帯域幅、高利得、そして低雑音を有する増幅器が徐々に重要になってきている。 30

【0004】

[0004]ミラー補償は、利得ステージの実効入力キャパシタンスを増加させることによって、利得ステージの主要極をより低い周波数へ移動させる従来型の周波数補償技術である。ミラー補償回路は、ミラーエフェクトを利用するミラーキャパシタンスを含む。ミラーキャパシタンスがフィードバック構成に接続される場合に、キャパシタンスは増幅器の入力にでは非常に大きく見える。主要極は、この方法を用いてより低い周波数へ移されるが、システムの利得及び帯域幅は依然として多少制限されている。 40

【0005】

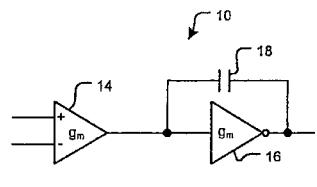

[0005]ここで、図1及び2を参照する。これらの図は、ミラー補償付きの増幅器回路10を示しており、当該回路10は、第1の増幅器14及び第2の増幅器16を含んでいる。第1の増幅器14の出力は、第2の増幅器16の入力に接続している。ミラーキャパシタンス18の第1の端部は、第2の増幅器16の入力に接続しており、ミラーキャパシタンス18の第2の端部は、第2の増幅器16の出力に接続している。

【0006】

[0006]増幅器回路10の入力電圧は、第1の増幅器14の入力に印加される。増幅器回 50

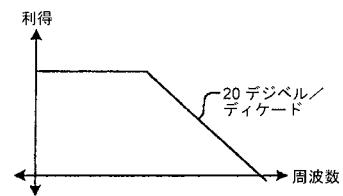

路 10 の出力電圧は、第 2 の増幅器 16 の出力から参照される。ミラー補償の結果、第 2 の増幅器 16 のトランスコンダクタンス  $g_m$  が増大され、このことが増幅器回路 10 の帯域幅を増大する。図 2 において見ることができるように、ミラー補償付きの増幅器の利得は 20 dB / decade の傾きを有する。

#### 【0007】

[0007] 増幅器はスイッチドキャパシタ入力信号と共に使用されることもある。スイッチドキャパシタ入力信号は、アナログ・デジタル変換器 (ADC)、デジタル・アナログ変換器 (DAC)、フィルタ、及び / 又は、その他の回路で生成される。図 1 に示すような従来型の増幅器は、特にスイッチドキャパシタ入力信号に対して、許容可能な雑音レベルで十分な利得及び帯域幅を提供することが難しいときがある。

10

#### 【発明の概要】

#### 【0008】

[0008] 増幅器システムは、第 1 の増幅器、第 2 の増幅器、第 1 のキャパシタ、及び第 1 のトランジスタを備える。第 1 の増幅器は、入力及び出力を有する。第 2 の増幅器は、第 1 の増幅器の出力に接続する入力を有する。第 1 のキャパシタは第 1 の増幅器の入力に接続する一端を有する。第 1 のトランジスタは、制御端子、第 1 の増幅器の出力に接続する第 1 の端子、及び第 1 のキャパシタの他端に接続する第 2 の端子を有する。

#### 【0009】

[0009] 別の特徴において、増幅器システムは、第 1 のトランジスタの第 2 の端子に接続する第 1 の電流源を更に備える。

20

#### 【0010】

[0010] 別の特徴において、増幅器システムは、第 1 のトランジスタの第 1 の端子に接続する第 2 の電流源を更に備える。

#### 【0011】

[0011] 別の特徴において、増幅器システムは、第 1 のトランジスタの第 2 の端子に接続する第 1 の電流源と、第 1 のトランジスタの第 1 の端子に接続する第 2 の電流源とを更に備える。

#### 【0012】

[0012] 別の特徴において、第 1 及び第 2 の増幅器は、演算トランスコンダクタンス増幅器を含む。

30

#### 【0013】

[0013] 別の特徴において、第 1 及び第 2 の増幅器は、演算増幅器を含む。

#### 【0014】

[0014] 更に別の特徴において、増幅器システムは、第 1 の増幅器、第 2 の増幅器、第 1 のキャパシタ、第 2 のキャパシタ、及び第 1 のトランジスタを備える。第 1 の増幅器は、入力及び出力を有する。第 2 の増幅器は、第 1 の増幅器の出力に接続する入力を有する。第 1 のキャパシタは、第 1 の増幅器の入力に接続する一端を有する。第 2 のキャパシタは、第 2 の増幅器の入力に接続する一端を有する。第 1 のトランジスタは、制御端子、第 2 のキャパシタの他端に接続する第 1 の端子、及び第 1 のキャパシタの他端に接続する第 2 の端子を有する。

40

#### 【0015】

[0015] 別の特徴において、増幅器システムは、第 1 のトランジスタの第 2 の端子に接続する第 1 の電流源を更に備える。

#### 【0016】

[0016] 別の特徴において、増幅器システムは、第 2 の増幅器の入力に接続する第 2 の電流源を更に備える。

#### 【0017】

[0017] 別の特徴において、増幅器システムは、第 1 のトランジスタの第 2 の端子に接続する第 1 の電流源と、第 2 の増幅器の入力に接続する第 2 の電流源と、を更に備える。

#### 【0018】

50

[0018]別の特徴において、第1及び第2の増幅器は演算トランスクタンス増幅器を含む。

【0019】

[0019]別の特徴において、第1及び第2の増幅器は演算増幅器を含む。

【0020】

[0020]更に別の特徴において、増幅器システムは、入力及び出力を有する第1の増幅手段と、第1の増幅手段の出力に接続する入力を有する第2の増幅手段と、第1の増幅手段の入力に接続する一端を有する第1のキャパシタンス手段と、制御端子、第1の増幅手段の出力に接続する第1の端子、及び第1のキャパシタンス手段の他端に接続する第2の端子を有する第1のトランジスタと、を備える。

10

【0021】

[0021]別の特徴において、増幅器システムは、第1のトランジスタの第2の端子に接続する第1の電流源手段を更に備える。

【0022】

[0022]別の特徴において、増幅器システムは、第1のトランジスタの第1の端子に接続する第2の電流源手段を更に備える。

【0023】

[0023]別の特徴において、増幅器システムは、第1のトランジスタの第2の端子に接続する第1の電流源手段と、第1のトランジスタの第1の端子に接続する第2の電流源手段とをさらに備える。

20

【0024】

[0024]別の特徴において、第1及び第2の増幅手段は、演算トランスクタンス増幅器を含む。

【0025】

[0025]別の特徴において、第1及び第2の増幅手段は、演算増幅器を含む。

【0026】

[0026]更に別の特徴において、増幅器システムは、入力及び出力を有する増幅用の第1の増幅手段と、第1の増幅手段の出力に接続する入力を有する増幅用の第2の増幅手段と、第1の増幅手段の入力に接続する一端を有するキャパシタを提供する第1のキャパシタンス手段と、第2の増幅手段の入力に接続する一端を有するキャパシタを提供する第2のキャパシタンス手段と、制御端子、第2のキャパシタンス手段の他端に接続する第1の端子、及び第1のキャパシタンス手段の他端に接続する第2の端子を有する第1のトランジスタと、を備える。

30

【0027】

[0027]別の特徴において、増幅器システムは、電流を供給し第1のトランジスタの第2の端子に接続する第1の電流源手段を更に備える。

【0028】

[0028]別の特徴において、増幅器システムは、電流を供給し第2の増幅手段の入力に接続する第2の電流源手段を更に備える。

【0029】

40

[0029]別の特徴において、増幅器システムは、電流を供給し第1のトランジスタの第2の端子に接続する第1の電流源手段と、電流を供給し第2の増幅器の入力に接続する第2の電流源手段と、を更に備える。

【0030】

[0030]別の特徴において、第1及び第2の増幅手段は、演算トランスクタンス増幅器を含む。

【0031】

[0031]別の特徴において、第1及び第2の増幅手段は、演算増幅器を含む。

【0032】

[0032]本発明の更なる適用範囲は、以下に記載する詳細な説明から明白になる。詳細な

50

説明及び具体的な実施例は、発明の好ましい実施形態を示すが、例示の目的だけを意図するものであり、発明の範囲を制限することを意図するものではないことを理解すべきである。

### 【0033】

[0033]本発明は、詳細な説明及び添付図面からより完全に理解されよう。

### 【好ましい実施形態の詳細な説明】

### 【0034】

[0059]以下の（複数の）好ましい実施形態の説明は、本質的に単なる例示であり、決して発明、発明の応用、又は、発明の使用を制限することを意図するものではない。本明細書で使用されるように、モジュール、回路、及び／又は、装置という用語は、特定用途向け集積回路（ASIC）、電子回路、一つ以上のソフトウェア又はファームウェアプログラムを実行するプロセッサ（共有、専用、又は、グループ）及びメモリ、組み合わせ論理回路、並びに／若しくは、上記の機能を提供するその他の適当なコンポーネントを指す。本明細書で使用されるように、A、B、及びCのうちの少なくとも一つという語句は、非排他的論理和を使用する論理的な（A又はB又はC）を意味するように解釈されるべきである。方法中のステップは本発明の原理を変更することなく異なる順序で実行してよいことを理解すべきである。明確にするために、同じ参照番号を類似した要素を特定するために図面中で使用する。

10

### 【0035】

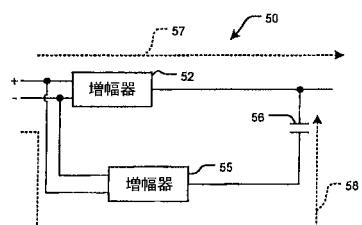

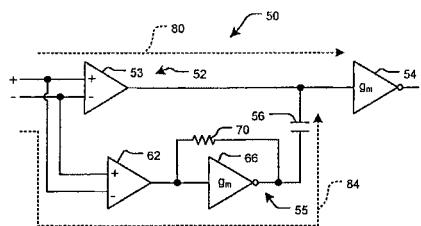

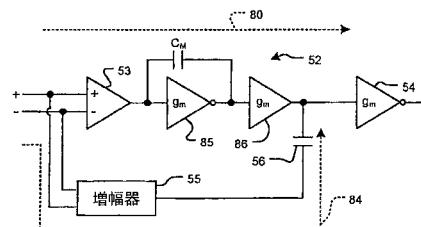

[0060]次に図3Aを参照する。この図は、本発明による補償付きの増幅器回路50の電気回路図を示している。増幅器回路の特定の実施例を示して説明するが、他の組み合わせも考えられる。増幅器回路50は、入力及び出力を有する第1の増幅器モジュール52を含む。増幅器モジュール52の入力は、増幅器モジュール55の入力に接続している。増幅器モジュール55の出力は、キャパシタ56によって増幅器モジュール52の出力に接続されている。

20

### 【0036】

[0061]増幅器モジュール55は、増幅器52の利得より小さい利得を有していてもよい。増幅器モジュール52は、100以上の利得を有していてもよい。増幅器モジュール55は、100未満の利得を有していてもよい。幾つかの実装形態では、増幅器モジュール55の利得は、実質的に100未満である。増幅器モジュール55は、非常に大きい帯域幅及び小さい出力インピーダンスを有していてもよい。増幅器モジュール55は、増幅器モジュール52の帯域幅より大きい帯域幅を有する。増幅器モジュール52の出力インピーダンスは、増幅器モジュール55の出力インピーダンスより大きくてよい。増幅器モジュール55は、トランスインピーダンス増幅器を含んでいてもよい。増幅器回路50は、第1のDCパス57及び第2の高周波パス58を有している。

30

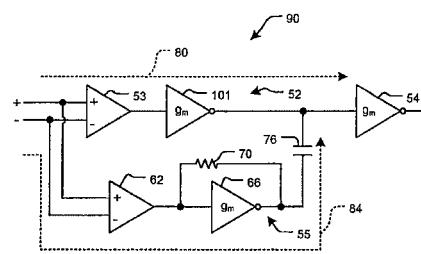

### 【0037】

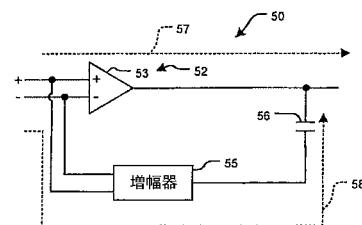

[0062]次に図3B～3Dを参照する。増幅器の種々の組み合わせを、増幅器回路50の増幅器モジュール52及び55に使用することが可能である。特定の実施例が示されているが、他の組み合わせも考えられる。図3Bでは、増幅器モジュール52は、増幅器53を含んでいてもよい。図3Cでは、増幅器モジュール55は、トランスインピーダンス増幅器を含んでいてもよい。図3Dでは、増幅器モジュール52は、ミラー補償増幅器を含んでいてもよい。更に別の変形態様も考えられる。

40

### 【0038】

[0063]図3Cを再び参照する。増幅器回路50は、増幅器モジュール52を含んでおり、このモジュール52は、第1の増幅器53を含んでおり、当該第1の増幅器53は、第2の増幅器54の入力に接続する出力を有している。増幅器53の入力は、増幅器モジュール55に接続している。増幅器モジュール55は、増幅器62、増幅器66、及びフィードバック抵抗70を含んでいる。増幅器62の出力は、増幅器66の入力に接続されている。フィードバック抵抗70は、増幅器66の入力と増幅器66の出力との間に接続されている。容量素子56は、増幅器66の出力を増幅器54の入力に容量的に接続してい

50

る。増幅器 5 3 及び 5 4 は、DC 利得バス 8 0 を提供する。DC 利得バス 8 0 の利得は、追加の増幅器を使用して調整可能である。増幅器 6 2 及び 6 6 、並びにキャパシタ 5 6 は、高周波利得バス 8 4 を提供する。

#### 【0039】

[0064] 次に、図 3 D を参照する。増幅器モジュール 5 2 は、増幅器 5 3 と、容量性フィードバック  $C_M$  を有するミラー補償増幅器 8 5 と、を含んでいてもよい。追加の増幅器 8 6 は、ミラー補償増幅器 8 5 の出力と増幅器 5 4 の入力との間に設けられている。更に別の組み合わせも考えられる。

#### 【0040】

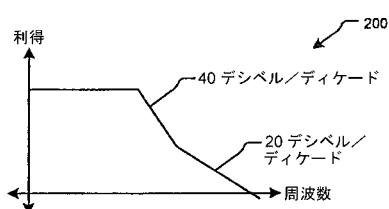

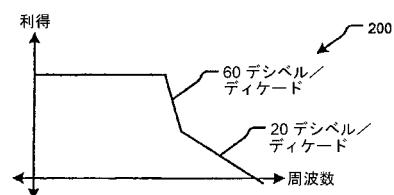

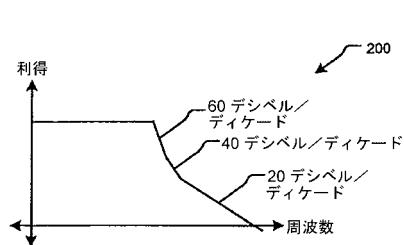

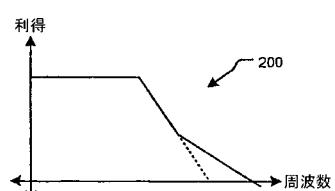

[0065] 次に、図 4 A ~ 4 C を参照する。これらの図は、増幅器回路の利得及び帯域幅を説明する例示的なグラフを示している。理解できるように、図 3 A における増幅器回路 5 0 は、更なる帯域幅をより高い利得値で有している。利得の傾きは、40 dB / decade に増加されており、これによって、利得が、後に、しかしそれ急速に低下する。追加の利得ステージは、傾きを 60 dB / decade に、図 4 B に示されるように、更に増加させる。ステージ及び / 又は構造次第では、利得帯域幅応答の領域は、図 4 C に示されるように、20、40、60 dB / decade 等の傾きを有することがある。

10

#### 【0041】

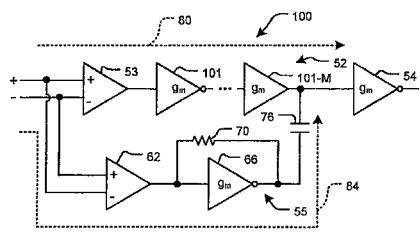

[0066] 次に、図 5 及び 6 を参照する。これらの図は、補償及び追加の利得付きの別の増幅器の電気回路図を示している。1台以上の追加の増幅器を DC 利得バス 8 0 に設けて、更なる利得を提供してもよい。図 5 では、増幅器回路 9 0 は、増幅器 5 3 及び 1 0 1 を含んでおり、当該増幅器 5 3 及び 1 0 1 は、増幅器 9 0 の入力と増幅器 5 4 との間に接続されている。図 6 では、増幅器回路 1 0 0 は、一以上の追加の増幅器 1 0 1 - M を含んでおり、当該増幅器 1 0 1 - M は、増幅器 5 2 - 2 と 5 4 との間に接続されている。なお、M は 1 より大きい整数である。理解できるように、追加の増幅器ステージを DC パスに追加して、必要に応じて更なる利得を提供してもよい。

20

#### 【0042】

[0067] 本発明による増幅器回路は、低周波数と高周波数の両者で利得を向上し、整定時間を向上している。増幅器回路は、各ステージを非カスコード構成にすることができるので、低電圧で動作しながら高利得を有している。

30

#### 【0043】

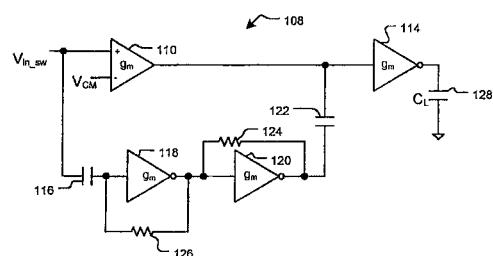

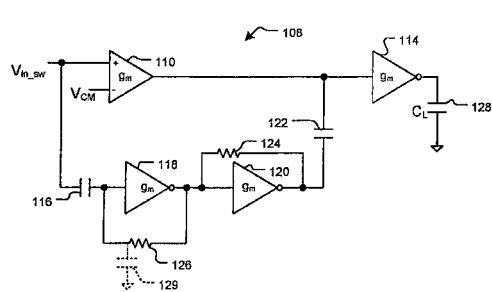

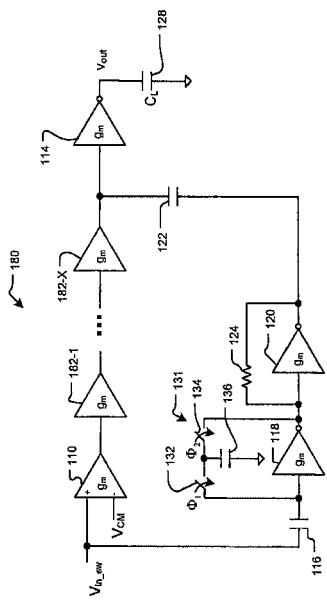

[0068] 次に、図 7 A 及び 7 B を参照する。増幅器回路 1 0 8 は、入力と、増幅器 1 1 4 の入力に接続された出力とを有する増幅器 1 1 0 を含んでいる。増幅器 1 1 0 の入力は、キャパシタ 1 1 6 によって増幅器 1 1 8 の入力に接続されている。増幅器 1 1 8 の出力は、増幅器 1 2 0 の入力に接続されている。増幅器 1 2 0 の出力は、キャパシタ 1 2 2 によって増幅器 1 1 4 の入力に接続されている。

40

#### 【0044】

[0069] フィードバック抵抗 1 2 4 は、増幅器 1 2 0 の入力と出力に接続されている。フィードバック抵抗 1 2 6 は、増幅器 1 1 8 の入力と出力に接続されている。フィードバック抵抗 1 2 6 は、高抵抗値を有していてもよい。例えば、このフィードバック抵抗は、抵抗 1 2 4 の抵抗値より高い抵抗値を有していてもよい。フィードバック抵抗 1 2 6 は、非常に高い抵抗、例えば、略無限大に近い抵抗を有していてもよい。負荷キャパシタ 1 2 8 を、増幅器 1 1 4 の出力に接続してもよい。図 7 B では、比較的高いフィードバック抵抗 1 2 8 に関連した寄生容量 1 2 9 が、回路の帯域幅を制限する傾向がある。

50

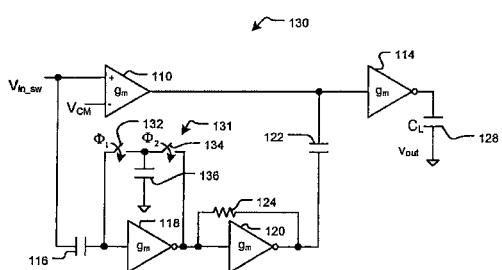

#### 【0045】

[0070] 図 7 C に、本発明による増幅器回路 1 3 0 を示す。増幅器回路 1 3 0 は、スイッチドキャパシタを備えて、寄生容量に伴う問題無しに高フィードバック抵抗 1 2 6 をシミュレートしてもよい。増幅器回路 1 3 0 は、増幅器 1 1 4 の入力に接続された出力を有する増幅器 1 1 0 を備えている。増幅器 1 1 0 の入力は、キャパシタ 1 1 6 によって増幅器 1 1 8 の入力にも接続されている。増幅器 1 1 8 の出力は、増幅器 1 2 0 の入力に接続されている。増幅器 1 2 0 の出力は、キャパシタ 1 2 2 によって増幅器 1 1 4 の入力に接続

50

されている。

#### 【0046】

[0071] 増幅器 118 の入力及び出力は、スイッチドキャパシタ回路 131 に接続してもよい。スイッチドキャパシタ回路 131 は、第 1 のスイッチ 132 及び第 2 のスイッチ 134 を有している。キャパシタ 136 は、スイッチ 132 及び 134 と、グランドのような基準電位との間に接続されている。第 1 のフェーズ<sub>1</sub> の間に、第 1 のスイッチ 132 が閉じられ、第 2 のスイッチ 134 が開かれて、キャパシタ 136 が充電される。第 2 のフェーズ<sub>2</sub> の間に、第 1 のスイッチ 132 が開かれ、第 2 のスイッチ 134 が閉じられ、これによってキャパシタ 136 を放電させる。第 1 及び第 2 のフェーズは、スイッチド入力の第 1 及び第 2 のフェーズに対応し、及び／又は、その逆に対応してもよい。

10 フィードバック抵抗 124 は、増幅器 120 の入力と出力に接続されている。負荷キャパシタ 146 を増幅器 114 の出力に接続してもよい。幾つかの用途では、増幅器 130 はスイッチド入力を受けてもよい。スイッチド入力は、容量性 ADC、DAC、フィルタなどに見られるようなスイッチドキャパシティブ入力であってもよい。

#### 【0047】

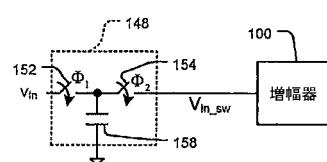

[0072] 次に、図 8 及び 9 を参照する。これらの図は、スイッチドキャパシタ回路 148 と図 7C の増幅器 130 とを備える例示的な回路を示している。増幅器回路 130 への入力電圧は、スイッチドキャパシティブ入力であってもよい。スイッチドキャパシティブ入力は、フィルタ、デジタル・アナログ変換器 (DAC)、アナログ・デジタル変換器 (ADC)、及びその他の回路のような回路において生成されてもよい。理解できるように、その他のタイプの入力及び／又は他のスイッチドキャパシタ回路を使用してもよい。スイッチドキャパシタ回路 148 は、第 1 のスイッチ 152 及び第 2 のスイッチ 154 を有している。キャパシタ 158 は、スイッチ 152 及び 154 と、グランドのような基準電位との間に接続されている。第 1 のフェーズ<sub>1</sub> の間に、第 1 のスイッチ 152 が閉じられ、第 2 のスイッチ 154 が開かれて、キャパシタ 158 が充電される。第 2 のフェーズ<sub>2</sub> の間に、第 1 のスイッチ 152 が開かれ、第 2 のスイッチ 154 が閉じられて、キャパシタ 158 が増幅器 100 を介して放電する。

20

#### 【0048】

[0073] 次に、図 10 を参照する。増幅器回路 180 は、図 7C に示した増幅器回路と類似しており、増幅器 182-1、182-2、...、182-X を更に備えている。ここで、X はゼロより大きい整数である。追加の増幅器 182 は、図 4 に示した領域 200 における利得帯域幅応答の傾きを増加させる傾向がある。

30

#### 【0049】

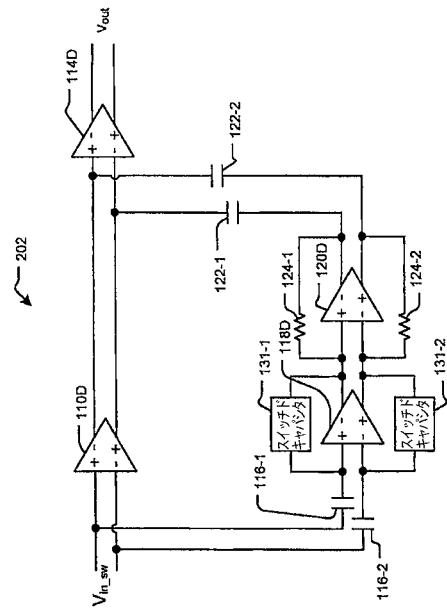

[0074] 上記の増幅器回路は、いずれも差動モードで構成することが可能である。例えば、ここで図 11 を参照すると、図 7C の増幅器が差動モードで構成されている。本明細書に記載されているその他の増幅器も同様に差動モードで構成してもよい。同図は、差動スイッチド入力を受ける本発明による増幅器 202 を示している。増幅器 202 は、差動増幅器 110D を備えており、当該増幅器 110D は、差動増幅器 114D の差動入力に接続された差動出力を有している。差動増幅器 110D の差動入力は、キャパシタ 116-1 及び 116-2 によって差動増幅器 118D の差動入力に更に接続されている。差動増幅器 118D の差動出力は、差動増幅器 120D の差動入力に接続されている。差動増幅器 120D の差動出力は、キャパシタ 122-1 及び 122-2 によって差動増幅器 114D の差動入力に接続されている。

40

#### 【0050】

[0075] 差動増幅器 118D の差動入力及び差動出力は、スイッチドキャパシタ回路 131-1 及び 131-2 に接続している。負荷キャパシタ（図示せず）を、差動増幅器 114D の差動出力に接続してもよい。

#### 【0051】

[0076] 本明細書で説明した増幅器は、増幅器、演算増幅器、演算トランスコンダクタンス増幅器 (OTA)、ミラー補償付き増幅器、及び／又は、その他の適当な増幅器であつ

50

てもよい。OTAはトランスコンダクタンスタイプのデバイスである。入力電圧は、トランスコンダクタンス $g_m$ に基づいて出力電流を制御する。換言すると、OTAは電圧制御型電流源(VCCS)であり、電圧制御型電圧源(VCVS)である従来型の増幅器(オペアンプ)とは著しく異なる。

#### 【0052】

[0077] OTAのトランスコンダクタンスパラメータは、増幅器バイアス電流によって制御される。この制御されたトランスコンダクタンスから、出力電流は、入力ピンの間の印加電圧差の関数になる。OTAと従来型のオペアンプとの間には二つの主要な相違点がある。第一に、OTAは電流源であるので、装置の出力インピーダンスが高い。その一方、オペアンプの出力インピーダンスは非常に低い。第二に、OTAを使用して、負フィードバックを利用しない回路を設計することが可能である。換言すると、装置パラメータに対する回路の性能の感度を下げるためにフィードバックを利用しない。

10

#### 【0053】

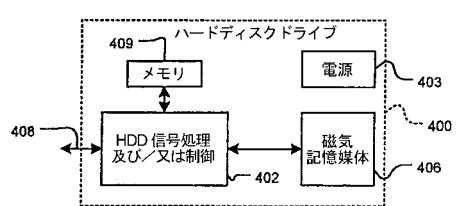

[0078] 次に、図12A～12Gを参照する。これらの図は、本発明の種々の例示的な実装形態を示している。ここで、図12Aを参照する。本発明を、ハードディスクドライブ400内の増幅器、ADC、DAC、フィルタ及びその他の回路に実装することが可能である。幾つかの実装形態では、HDD400内の信号処理及び/又は制御回路402、及び/又は、その他の回路(図示せず)は、データを処理し、符号化及び/又は暗号化を実行し、計算を実行し、並びに/若しくは、磁気記憶媒体406へ出力され、及び/又は、磁気記憶媒体406から入力されるデータをフォーマット化する。

20

#### 【0054】

[0079] HDD400は、一以上の有線又は無線通信リンク408を介して、コンピュータ、携帯情報端末のような携帯型計算装置、携帯電話機、メディア又はMP3プレーヤー等のようなホスト装置(図示せず)、及び/又は、その他の装置と通信する。HDD400は、例えば、ランダムアクセスメモリ(RAM)、フラッシュメモリのような低遅延の不揮発性メモリ、リードオンリーメモリ(ROM)、及び/又は、その他の適当な電子データ記憶装置などのメモリ409に接続される。

#### 【0055】

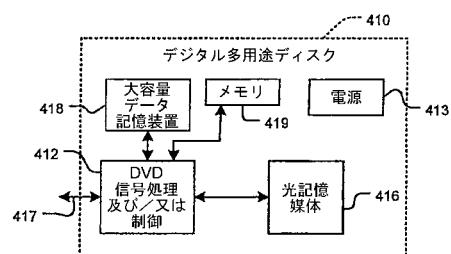

[0080] 次に、図12Bを参照する。本発明を、デジタル多用途ディスク(DVD)ドライブ410の増幅器、ADC、DAC、フィルタ及びその他の回路において実装することが可能である。信号処理及び/又は制御回路412、及び/又は、DVD410内のその他の回路(図示せず)は、データを処理し、符号化及び/又は暗号化を実行し、計算を実行し、及び/又は、光記憶媒体416へ出力され、及び/又は、磁気記憶媒体416から入力されるデータをフォーマット化する。幾つかの実装形態では、信号処理及び/又は制御回路412、及び/又は、DVD410内のその他の回路(図示せず)は、符号化及び/又は復号化、並びに/若しくは、DVDドライブに関連した任意の別の信号処理機能のようなその他の機能を更に実行する。

30

#### 【0056】

[0081] DVDドライブ410は、コンピュータ、テレビ、又は、その他の装置のような出力装置(図示せず)と、一以上の有線又は無線通信リンク417を介して、通信してもよい。DVD410は、不揮発性方式でデータを記憶する大容量記憶装置418と通信してもよい。大容量記憶装置418は、ハードディスクドライブ(HDD)を含む。HDDは図12Aに示された構造を有していてもよい。HDDは、約1.8インチより小さい直徑を有する1枚以上のプラッタを含むミニHDDであってもよい。DVD410は、例えば、RAM、ROM、フラッシュメモリのような低遅延の不揮発性メモリ、及び/又は、その他の適当な電子データ記憶装置などのメモリ419に接続されてもよい。

40

#### 【0057】

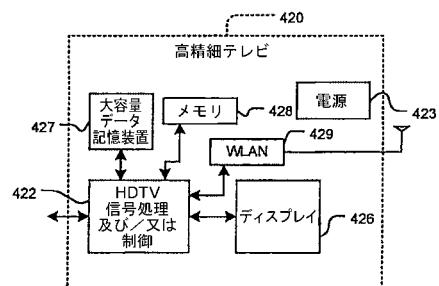

[0082] 次に、図12Cを参照する。本発明を、高精細テレビ(HDTV)420の増幅器、ADC、DAC、フィルタ及びその他の回路において実装することが可能である。HDTV420は、有線又は無線のいずれかのフォーマットでHDTV入力信号を受信し、

50

ディスプレイ 428 のための HDTV 出力信号を生成する。幾つかの実装形態では、信号処理回路及び／又は制御回路 422、及び／又は、HTV 420 のその他の回路（図示せず）は、データを処理し、符号化及び／又は暗号化を実行し、計算を実行し、データをフォーマット化し、並びに／若しくは、要求され得るその他のタイプの HDTV 处理を実行してもよい。

#### 【0058】

[0083] HTV 420 は、光及び／又は磁気記憶装置のような不揮発性方式でデータを記憶する大容量データ記憶装置 427 と通信してもよい。少なくとも 1 台の HDD は図 12A に示された構造を有していてもよく、及び／又は、少なくとも 1 台の DVD は図 12B に示された構造を有していてもよい。HDD は、約 1.8 インチより小さい直径を有する 1 枚以上のプラッタを含むミニ HDD でもよい。HTV 420 は、例えば、RAM、ROM、フラッシュメモリのような低遅延の不揮発性メモリ、及び／又は、その他の適当な電子データ記憶装置などのメモリ 428 に接続されてもよい。HTV 420 は、WLAN ネットワークインターフェイス 429 を介して WLAN との接続もサポートしてもよい。

10

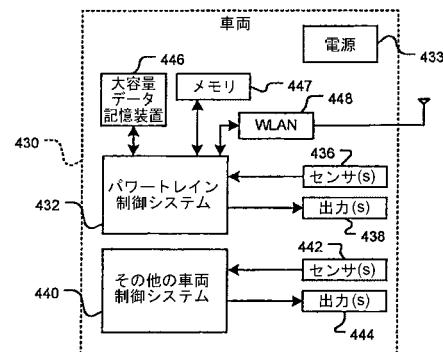

#### 【0059】

[0084] 次に、図 12D を参照する。本発明は、車両 430 の制御システムの増幅器、ADC、DAC、フィルタ、及びその他の回路、WLAN インターフェイス、車両制御システムの大容量データ記憶装置、並びに／若しくは、電源 433 において、実装してもよく、及び／又は、それらにおいて実施されてもよい。幾つかの実装形態では、本発明は、パワートレイン制御システム 432 を実施する。パワートレイン制御システム 432 は、温度センサ、圧力センサ、回転センサ、気流センサ、及び／又は、その他の適当なセンサのような 1 台以上のセンサから入力を受信し、及び／又は、エンジン動作パラメータ、伝達動作パラメータ、及び／又は、その他の制御信号のような 1 以上の出力制御信号を生成する。

20

#### 【0060】

[0085] 本発明を、車両 430 の他の制御システム 440 において実装してもよい。制御システム 440 も同様に、入力センサ 442 から信号を受信してもよく、1 以上の出力装置 444 へ制御信号を出力してもよい。幾つかの実装形態では、制御システム 440 は、アンチロックブレーキングシステム（ABS）と、ナビゲーションシステムと、テレマティクスシステムと、車両テレマティクスシステムと、車線離脱システムと、適応クルーズ制御システムと、ステレオ、DVD、コンパクトディスクなどのような車両エンターテイメントシステムの一部分であってもよい。更に別の実装形態も考えられる。

30

#### 【0061】

[0086] パワートレイン制御システム 432 は、不揮発性方式でデータを記憶する大容量データ記憶装置 446 と通信してもよい。大容量データ記憶装置 446 は、例えば、ハードディスクドライブ HDD 及び／又は DVD のような光及び／又は磁気ディスク記憶装置を含んでもよい。少なくとも 1 台の HDD は図 12A に示された構造を有していてもよく、及び／又は、少なくとも 1 台の DVD は図 12B に示された構造を有していてもよい。HDD は、約 1.8 インチより小さい直径を有する 1 枚以上のプラッタを含むミニ HDD であってもよい。パワートレイン制御システム 432 は、例えば、RAM、ROM、フラッシュメモリのような低遅延の不揮発性メモリ、及び／又は、その他の適当な電子データ記憶装置などのメモリ 447 に接続されてもよい。パワートレイン制御システム 432 は、WLAN ネットワークインターフェイス 448 を介して WLAN との接続もサポートしてもよい。制御システム 440 は、また、大容量データ記憶装置、メモリ、及び／又は、WLAN インターフェイス（すべて図示されていない）を更に備えてもよい。

40

#### 【0062】

[0087] 次に、図 12E を参照する。本発明を、セルラー・アンテナ 451 を含み得る携帯電話機 450 の増幅器、ADC、DAC、フィルタ、及びその他の回路において実装することができる。幾つかの実装形態では、携帯電話機 450 は、マイクロホン 456、スピ

50

ーカー及び／又はオーディオ出力ジャックのようなオーディオ出力 458、ディスプレイ 460、並びに／若しくは、キーパッド、ポインティングデバイス、音声作動及び／又はその他の入力装置のような入力装置 462 を含む。信号処理及び／又は制御回路 452、及び／又は、携帯電話機 450 内のその他の回路（図示せず）は、データを処理し、符号化及び／又は暗号化を実行し、計算を実行し、データをフォーマット化し、及び／又は、その他の携帯電話機能を実行してもよい。

#### 【0063】

[0088] 携帯電話機 450 は、例えば、ハードディスクドライブ HDD 及び／又は DVD といった光及び／又は磁気ディスク記憶装置のような不揮発性方式でデータを記憶する大容量データ記憶装置 464 と通信してもよい。少なくとも 1 台の HDD は図 12A に示された構造を有し、及び／又は、少なくとも 1 台の DVD は図 12B に示された構造を有していてもよい。HDD は、約 1.8 インチより小さい直径を有する 1 枚以上のプラッタを含むミニ HDD であってもよい。携帯電話機 450 は、例えば、RAM、ROM、フラッシュメモリのような低遅延の不揮発性メモリ、及び／又は、その他の適当な電子データ記憶装置などのメモリ 466 に接続されてもよい。携帯電話機 450 は、また、WLAN ネットワークインターフェイス 468 を介して WLAN との接続をサポートしてもよい。10

#### 【0064】

[0089] 次に、図 12F を参照する。本発明を、セットトップボックス 480 の増幅器、ADC、DAC、フィルタ、及びその他の回路において実装してもよい。セットトップボックス 480 は、ブロードバンドソースのようなソースから信号を受信し、テレビ、及び／又は、モニタ、並びに／若しくは、他のビデオ及び／又はオーディオ出力装置といったディスプレイ 488 に適した標準、及び／又は、高精細のオーディオ／ビデオ信号を出力する。信号処理及び／又は制御回路 484、及び／又は、セットトップボックス 480 内のその他の回路（図示せず）は、データを処理し、符号化及び／又は暗号化を実行し、計算を実行し、データをフォーマット化し、及び／又は、その他のセットトップボックス機能を実行してもよい。20

#### 【0065】

[0090] セットトップボックス 480 は、不揮発性方式でデータを記憶する大容量データ記憶装置 490 と通信してもよい。大容量データ記憶装置 490 は、例えば、ハードディスクドライブ HDD 及び／又は DVD のような光及び／又は磁気ディスク記憶装置を含んでもよい。少なくとも 1 台の HDD は図 12A に示された構造を有し、及び／又は、少なくとも 1 台の DVD は図 12B に示された構造を有していてもよい。HDD は、約 1.8 インチより小さい直径を有する 1 枚以上のプラッタを含むミニ HDD であってもよい。セットトップボックス 480 は、例えば、RAM、ROM、フラッシュメモリのような低遅延の不揮発性メモリ、及び／又は、他の適当な電子データ記憶装置などのメモリ 4124 に接続されていてもよい。セットトップボックス 480 は、また、WLAN ネットワークインターフェイス 4126 を介して WLAN との接続をサポートしてもよい。30

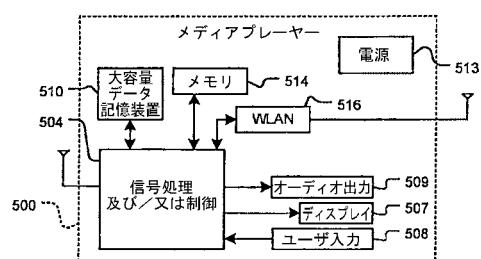

#### 【0066】

[0091] 次に、図 12G を参照する。本発明を、メディアプレーヤー 500 の増幅器、ADC、DAC、フィルタ、及びその他の回路において実装することが可能である。幾つかの実装形態では、メディアプレーヤー 500 は、ディスプレイ 507、及び／又は、キーパッド、タッチパッドなどのユーザ入力 508 を含む。幾つかの実装形態では、メディアプレーヤー 500 は、グラフィカルユーザインターフェイス（GUI）を採用してもよい。GUI は、通常、ディスプレイ 507 及び／又はユーザ入力 508 を介するメニュー、ドロップダウンメニュー、アイコン、及び／又は、ポイントアンドクリックインターフェイスを採用する。メディアプレーヤー 500 は、スピーカー及び／又はオーディオ出力ジャックのようなオーディオ出力 509 を更に含む。信号処理及び／又は制御回路 504、及び／又は、メディアプレーヤー 500 のその他の回路（図示せず）は、データを処理し、符号化及び／又は暗号化を実行し、計算を実行し、データをフォーマット化し、及び／又は、他のメディアプレーヤー機能を実行してもよい。4050

## 【0067】

[0092] メディアプレーヤー 500 は、圧縮オーディオ及び／又はビデオコンテンツのようなデータを不揮発性方式で記憶する大容量データ記憶装置 510 と通信してもよい。幾つかの実装形態では、圧縮オーディオファイルは、MP3 フォーマット、及び／又は、その他の適当な圧縮オーディオ及び／又はビデオフォーマットに準拠したファイルを含む。大容量データ記憶装置は、例えば、ハードディスクドライブ HDD 及び／又は DVD のような光及び／又は磁気ディスク記憶装置を含んでいてもよい。少なくとも 1 台の HDD は図 12A に示された構造を有し、及び／又は、少なくとも 1 台の DVD は図 12B に示された構造を有していてもよい。HDD は、約 1.8 インチより小さい直径を有する 1 枚以上のプラッタを含むミニ HDD であってもよい。メディアプレーヤー 500 は、例えば、RAM、ROM、フラッシュメモリのような低遅延の不揮発性メモリ、及び／又は、その他の適当な電子データ記憶装置などのメモリ 514 に接続されていてもよい。メディアプレーヤー 500 は、また、WLAN ネットワークインターフェイス 516 を介して WLAN との接続をサポートしてもよい。上記の実装形態に加えて、更に他の実装形態も考えられる。10

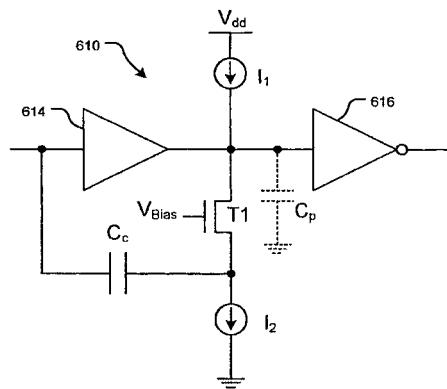

## 【0068】

[0093] 次に、図 13 を参照する。この図は、補償付きの別の代替的な増幅器システム 610 の電気回路図を示している。増幅器システム 610 は、第 1 の増幅器ステージ 614 と、第 2 の増幅器ステージ 616 と、を含んでいる。第 1 の増幅器ステージ 614 の入力は、第 1 のキャパシタ  $C_c$  の一端に接続している。増幅器ステージ 614 の出力は、第 2 の増幅器ステージ 616 の入力に接続されている。20

## 【0069】

[0094] 第 1 のトランジスタ T1 の第 1 の端子は、第 1 の増幅器ステージ 614 の出力に接続されている。トランジスタ T1 の第 2 の端子は、第 1 のキャパシタ  $C_c$  の他端及び電流源  $I_2$  に接続されている。別の電流源  $I_1$  は、第 1 の増幅器ステージ 614 の出力に接続されている。電流源  $I_1$  は、第 1 の電圧基準  $V_{dd}$  に接続していてもよい。寄生容量  $C_p$  が、第 2 の増幅器ステージ 616 の入力に存在する。電圧バイアス  $V_{bias}$  は、トランジスタ T1 の制御端子へ入力される。

## 【0070】

[0095] 増幅器ステージ 614 及び 618 の一方は反転増幅器であってもよい。電流源  $I_1$  及び  $I_2$  は、それぞれ、実質的に等しい電流の大きさのソース及びシンクを行ってもよい。トランジスタ T1 は、CMOS トランジスタであってもよく、その他の適当なトランジスタであってもよい。増幅器の実効利得は、 $C_c / C_p$  に略等しい。図 13 の増幅器システム 610 は、フィードフォワード利得付きの類似の増幅器より高い帯域幅と低い雑音を有する傾向がある。この回路は、共通ゲート電流増幅器構造で構成されている。30

## 【0071】

[0096] 次に、図 14 を参照する。この図は、図 13 の増幅器の例示的な利得及び帯域幅を説明するグラフを示している。増幅器システム 610 は、上述した利得及び帯域幅と類似した利得／帯域幅特性を有する。

## 【0072】

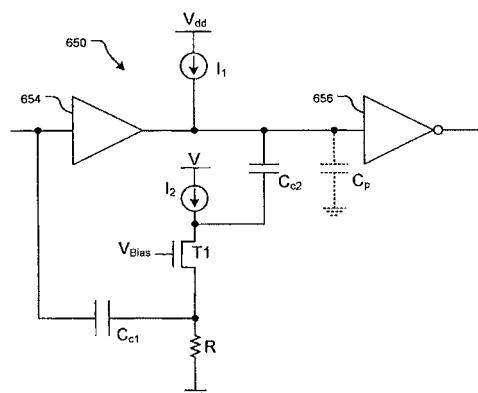

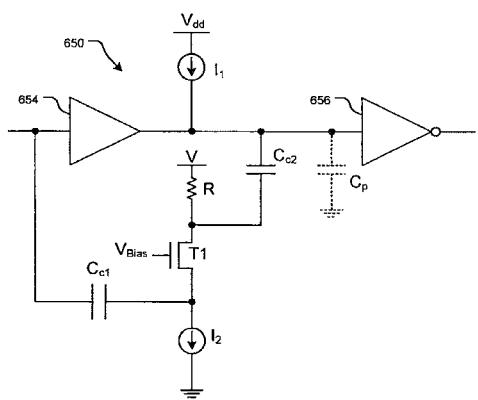

[0097] 次に、図 15A 及び 15B を参照する。これらの図は、補償付きの他の代替的な増幅器システム 650 の電気回路図を示している。図 15A では、増幅器システム 650 が、第 1 の増幅器ステージ 654 及び第 2 の増幅器ステージ 656 を備えている。第 1 の増幅器ステージ 654 の入力は、第 1 のキャパシタ  $C_{c1}$  の一端に接続している。増幅器ステージ 654 の出力は、第 2 の増幅器ステージ 656 の入力に接続されている。40

## 【0073】

[0098] トランジスタ T1 の第 2 の端子は、第 1 のキャパシタ  $C_{c1}$  の他端及び抵抗 R に接続されている。トランジスタ T1 の第 1 の端子は、電流源  $I_2$ 、及びキャパシタ  $C_{c2}$  の一端に接続している。キャパシタ  $C_{c2}$  の他端は、第 1 の増幅器ステージ 654 の出力、及び第 2 の増幅器ステージ 656 の入力に接続している。別の電流源  $I_1$  は第 1 の増幅50

器ステージ 654 の出力に接続されている。寄生容量  $C_p$  が、第 2 の増幅器ステージ 656 の入力に存在する。

【0074】

[0099] 増幅器システム 650 は、電流源  $I_1$  及び  $I_2$  が等しい電流レベルを提供しない場合に生じる問題に対処可能である。トランジスタ T1 の第 1 の端子は、電流源  $I_2$  に接続されており、第 1 の増幅器ステージ 654 の出力及び第 2 の増幅器ステージ 656 の入力に容量的に接続されている。第 1 の電圧基準  $V_{dd}$  及び第 2 の電圧基準  $V$  は、実質的に等しい電圧基準であっても、又は、異なる電圧基準であってもよい。高周波では、この増幅器システムの利得は、図 13 の増幅器システムに類似する。

【0075】

10

[0100] 図 15B は、代替の適切な構成を示している。抵抗 R と電流源  $I_2$  の相対的な位置は、図 15A に示されたものの逆である。換言すると、抵抗 R の一端は電圧基準 V に接続しており、抵抗 R の反対端はトランジスタ T1 の第 1 の端子及びキャパシタ  $C_{c2}$  に接続している。電流源  $I_2$  は、トランジスタ T1 の第 2 の端子及びキャパシタ  $C_{c1}$  の他端に接続している。

【0076】

[0101] 本明細書で説明した増幅器は、増幅器、演算増幅器、演算トランスコンダクタンス増幅器 (OTA)、ミラー補償付き増幅器、及び / 又は、その他の適当な増幅器であってもよい。

【0077】

20

[0101] 当業者は、以上の説明から、本発明の広い教示を種々の態様で実施し得ることを認識できる。したがって、本発明を特定の実施例との関連において説明したが、図面、明細書、及び特許請求の範囲を詳しく検討することによって、その他の変更が当業者に明白になるので、本発明の真の範囲はそのように限定されるべきではない。

【図面の簡単な説明】

【0078】

【図 1】 従来技術によるミラー補償付き増幅器の電気回路図である。

【図 2】 図 1 の増幅器の利得及び帯域幅を説明するグラフである。

【図 3A】 本発明による例示的な補償付き増幅器の電気回路図である。

【図 3B】 本発明による例示的な補償付き増幅器の電気回路図である。

30

【図 3C】 本発明による例示的な補償付き増幅器の電気回路図である。

【図 3D】 本発明による例示的な補償付き増幅器の電気回路図である。

【図 4A】 増幅器の例示的な利得及び帯域幅を説明するグラフである。

【図 4B】 増幅器の例示的な利得及び帯域幅を説明するグラフである。

【図 4C】 増幅器の例示的な利得及び帯域幅を説明するグラフである。

【図 5】 本発明による補償ステージ及び追加の利得ステージ付きの増幅器の電気回路図である。

【図 6】 本発明による補償ステージ及び追加の利得ステージ付きの増幅器の電気回路図である。

【図 7A】 本発明による例示的な増幅器の電気回路図である。

40

【図 7B】 寄生容量付きの図 7A の増幅器の電気回路図である。

【図 7C】 スイッチドキャパシタ回路付きの本発明による増幅器の電気回路図である。

【図 8】 図 7C のスイッチドキャパシタ回路及び増幅器を備える例示的なスイッチド入力を説明する機能ブロック図である。

【図 9】 例示的なスイッチドキャパシタ回路を説明する機能ブロック図及び電気回路図である。

【図 10】 追加の増幅器ステージをもつ図 7C の増幅器の電気回路図である。

【図 11】 差動モードで構成された図 7C の増幅器の電気回路図である。

【図 12A】 ハードディスクドライブの機能ブロック図である。

【図 12B】 デジタル多用途ディスク (DVD) の機能ブロック図である。

50

【図12C】高精細テレビの機能ブロック図である。

【図12D】車両制御システムの機能ブロック図である。

【図12E】携帯電話機の機能ブロック図である。

【図12F】セットトップボックスの機能ブロック図である。

【図12G】メディアプレーヤーの機能ブロック図である。

【図13】別の代替的な補償付き増幅器の電気回路図である

【図14】図13の増幅器の例示的な利得及び帯域幅を説明するグラフである。

【図15A】その他の代替的な補償付き増幅器の電気回路図である。

【図15B】その他の代替的な補償付き増幅器の電気回路図である。

【符号の説明】

10

【0079】

10, 50, 90, 100, 108, 130, 180...増幅器回路、14, 16, 53、

62, 66, 101, 101-M, 110, 114, 118, 120, 182-1, 18

2-2, 182-X, 202...増幅器、18...ミラー容量、52, 55...増幅器モジュール、

56, 116, 116-1, 116-2, 122, 122-1, 122-2, 158

...キャパシタ、57...第1のDCパス、58...第2の高周波パス、70, 124, 126

...フィードバック抵抗、80...DC利得パス、84...高周波利得パス、85...ミラー補償

増幅器、110D, 114D, 118D, 120D...差動増幅器、128, 146...負荷

容量、129...寄生容量、131, 131-1, 131-2, 148...スイッチドキャパ

シタ回路、132, 134, 152, 154...スイッチ、200...領域、400...ハード

ディスクドライブ、402, 412, 422, 452, 484, 504...信号処理及び/

又は制御回路、406...磁気記憶媒体、408, 417...通信リンク、409, 419,

428, 447, 466, 494, 514...メモリ、410...デジタル多用途ディスク、

416...光記憶媒体、418...大容量記憶装置、420...高精細テレビ、426, 460

, 488, 507...ディスプレイ、427, 446, 464, 490, 510...大容量デ

ータ記憶装置、429, 448, 468, 496, 516...WLANネットワークインタ

ーフェイス、430...車両、432...パワートレイン制御システム、440...その他の制

御システム、442...入力センサ、444...出力装置、450...携帯電話機、451...セ

ルラーアンテナ、456...マイクロホン、458, 509...オーディオ出力、462...入

力装置、480...セットトップボックス、500...メディアプレーヤー、508...ユーザ

入力、610, 650...増幅器システム、614, 616, 654, 656...増幅器ステ

ージ。

20

30

【図1】

【図2】

【図3A】

【図3B】

【図 3 C】

【図 3 D】

【図 4 A】

【図 4 B】

【図4C】

【図5】

【図6】

【図7A】

【図 7 B】

【図 7 C】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12A】

【図 12B】

【図 1 2 C】

【図 1 2 D】

【図 1 2 G】

【図 1 3】

【図 1 4】

【図 1 5 A】

【図 1 5 B】

---

フロントページの続き

(31)優先権主張番号 11/264921

(32)優先日 平成17年11月2日(2005.11.2)

(33)優先権主張国 米国(US)

(72)発明者 ファーボッド アラム

アメリカ合衆国, カリフォルニア州, ロス アルトス ヒルズ, シャーロック ロード 2776

0

審査官 安井 雅史

(56)参考文献 米国特許第05990748(US, A)

特開2000-261265(JP, A)

特開昭59-091716(JP, A)

特開昭60-233914(JP, A)

特開昭57-005404(JP, A)

特開昭62-098809(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03F 1/00 - 3/45, 3/50 - 3/52,

3/62 - 3/64, 3/68 - 3/72